High-Performance, Low-Power, 32-Bit Precision32<sup>™</sup>

USB MCU Family with up to 256 kB of Flash

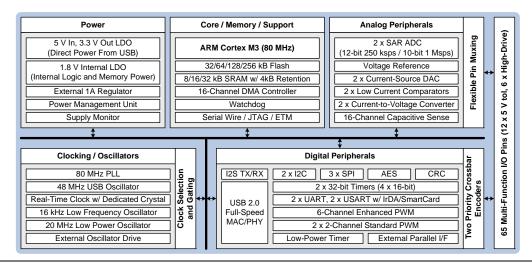

### 32-bit ARM® Cortex™-M3 CPU

- 80 MHz maximum frequency

- Single-cycle multiplication, hardware division support

- Nested vectored interrupt control (NVIC) with 16 priority levels

### Memory

- 32-256 kB Flash, in-system programmable

- 8-32 kB SRAM (including 4 kB retention SRAM)

- 16-channel DMA controller

- External bus interface supports up to 16 MB of external memory and a parallel LCD interface with QVGA resolution

### **Power Management**

- Low drop-out (LDO) regulator

- Power-on reset circuit and brownout detectors

- 5-to-3.3 V 150 mA regulator supports direct USB power

- Adjustable external regulator supports up to 3.6 V, 1000 mA

- Multiple power modes supported for low power optimization

#### **Low Power Features**

- 85 nA current mode with voltage supply monitor enabled

- Low-current RTC: 350 nA internal LFO, 620 nA external crystal

- 12 μs wakeup (lowest power mode); 1.5 μs analog setting time

- 275 µA/MHz active current

- Clocks can be gated off from unused peripherals to save power

- Flexible clock divider: Reduce operational frequency up to 128x

### **Clock Sources**

- Internal oscillator with PLL: 23-80 MHz, reduced EMI mode

- USB internal 48 MHz oscillator supports crystal-less operation

- Low power internal oscillator: 20 MHz and 2.5 MHz modes

- Low frequency internal oscillator: 16.4 kHz

- External oscillators: Crystal, RC, C, CMOS and RTC Crystal

### Temperature Range: -40 to +85 °C

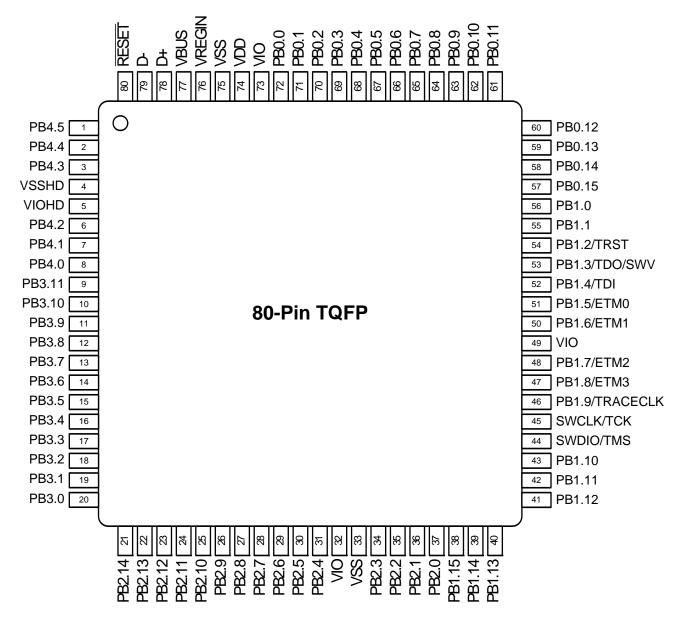

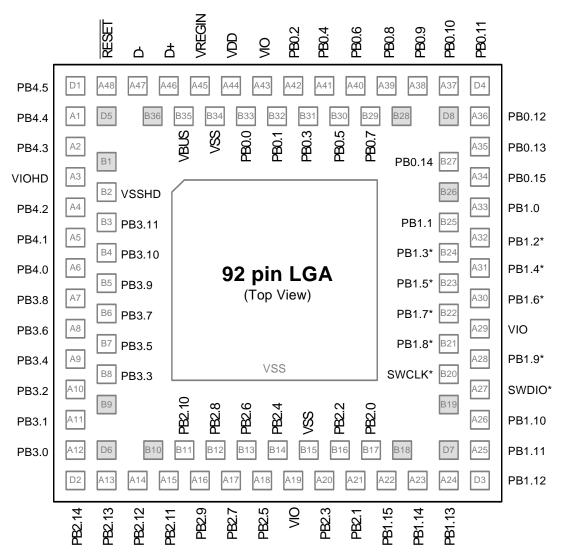

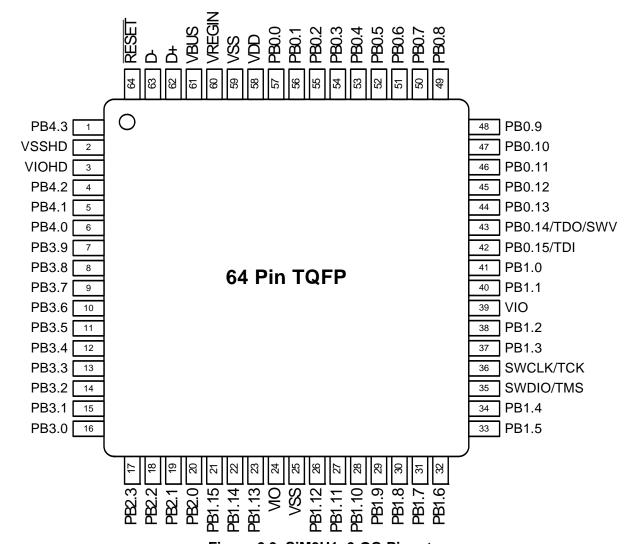

## **Package Options**

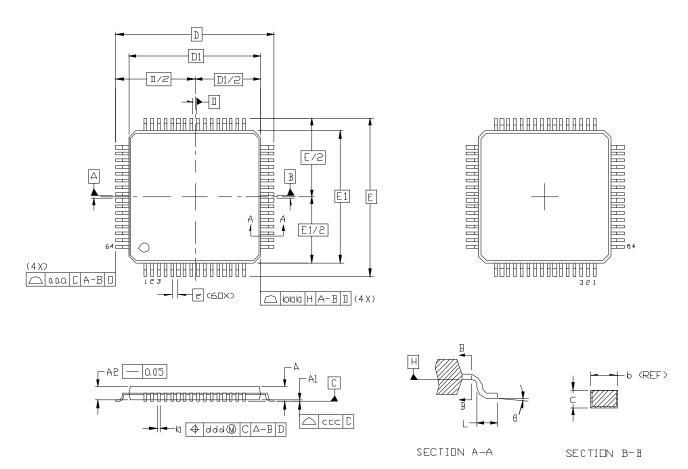

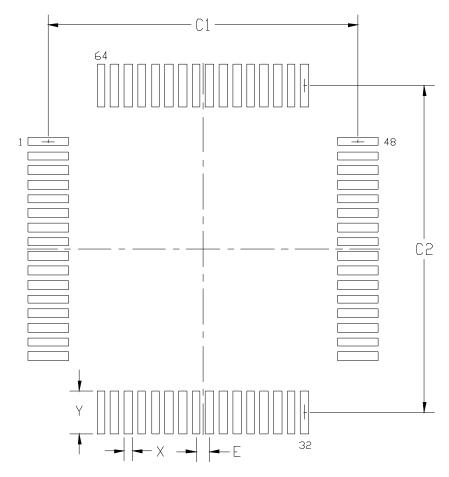

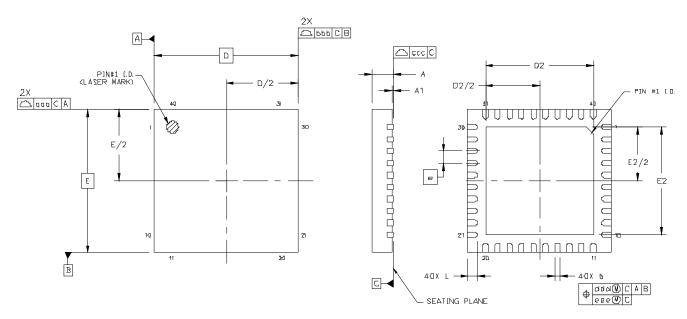

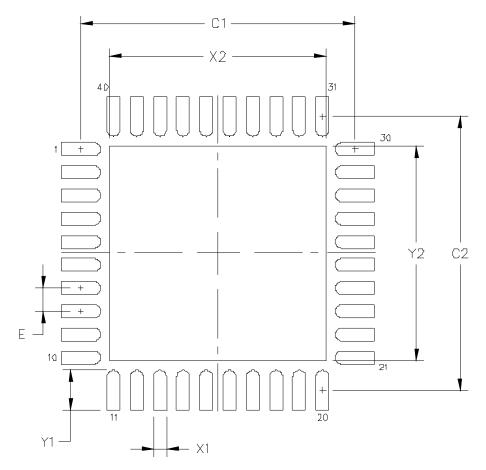

- QFN options: 40-pin (6 x 6 mm), 64-pin (9 x 9 mm)

- TQFP options: 64-pin (10 x 10 mm), 80-pin (12 x 12 mm)

- LGA option: 92-pin (7 x 7 mm)

### **Analog Peripherals**

- 2 x 12-Bit Analog-to-Digital Converters: Up to 250 ksps 12-bit mode or 1 Msps 10-bit mode, internal or external reference

- 2 x 10-Bit Current-mode Digital-to-Analog Converters, fourword buffer enables 12-bit operation

- 2 x Low-current comparators

- 16-Channel Capacitance-to-Digital: Fast, <1 μA wake-on-touch

- 2 x Current-to-Voltage Converter, up to 6 mA input range

### **Digital and Communication Peripherals**

- USB 2.0-compliant full speed with 10 endpoints, 2 kB buffer, oscillator with automatic frequency correction, and transceiver; no external components needed

- 2 x USARTs and 2 x UARTs with IrDA and ISO7816 SmartCard

- 3 x SPIs, 2 x I2C, I<sup>2</sup>S (receive and transmit), 16/32-bit CRC

- 128/192/256-bit Hardware AES Encryption

#### Timers/Counters

- 2 x 32-bit or 4 x 16-bit timers with capture/compare

- 2 x 16-bit, 2-channel counters with capture/compare/PWM

- 16-bit, 6-channel counter with capture/compare/PWM and dead-time controller with differential outputs

- 16-bit low power timer/pulse counter operational in sleep

- 32-bit real time clock (RTC) with multiple alarms

- Watchdog timer

### Up to 65 Flexible I/O

- Up to 59 contiguous GPIO with two priority crossbars providing flexibility in pin assignments; 12 x 5 V tolerant GPIO

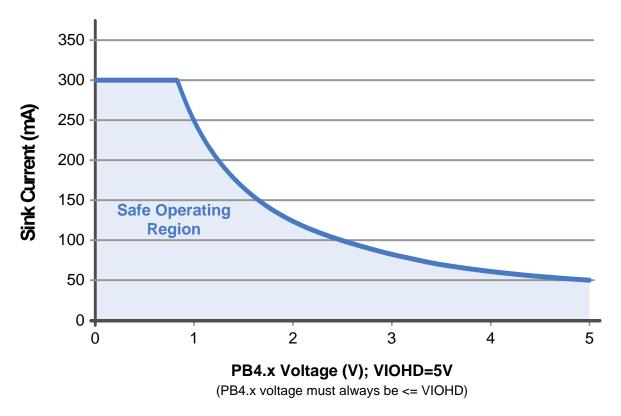

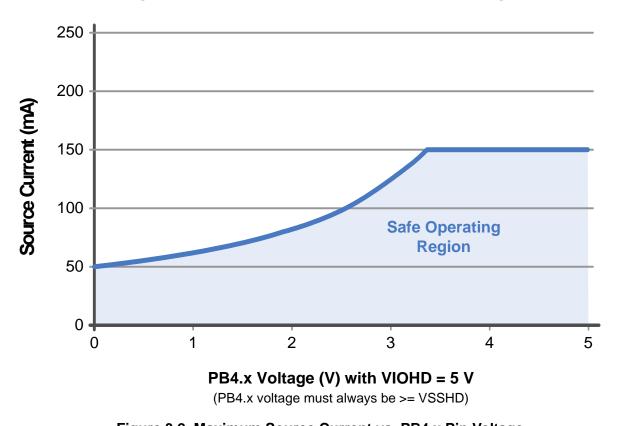

- Up to 6 programmable high drive capable (5–300 mA, 1.8–6 V)

I/O can drive LEDs, power MOSFETs, buzzers, etc.

#### On-Chip Debugging

- Serial wire debug (SWD) or JTAG (no boundary scan), serial wire viewer (SWV)

- Cortex-M3 embedded trace macrocell (ETM)

### **Supply Voltage**

- 2.7 to 5.5 V (regulator enabled)

- 1.8 to 3.6 V (regulator disabled)

# **Table of Contents**

| 1. | Related Documents and Conventions                     |    |

|----|-------------------------------------------------------|----|

|    | 1.1. Related Documents                                |    |

|    | 1.1.1. SiM3U1xx/SiM3C1xx Reference Manual             |    |

|    | 1.1.2. Hardware Access Layer (HAL) API Description    |    |

|    | 1.1.3. ARM Cortex-M3 Reference Manual                 |    |

|    | 1.2. Conventions                                      |    |

| 2. | Typical Connection Diagrams                           |    |

|    | 2.1. Power                                            |    |

| 3. | Electrical Specifications                             |    |

|    | 3.1. Electrical Characteristics                       |    |

|    | 3.2. Thermal Conditions                               |    |

| _  | 3.3. Absolute Maximum Ratings                         |    |

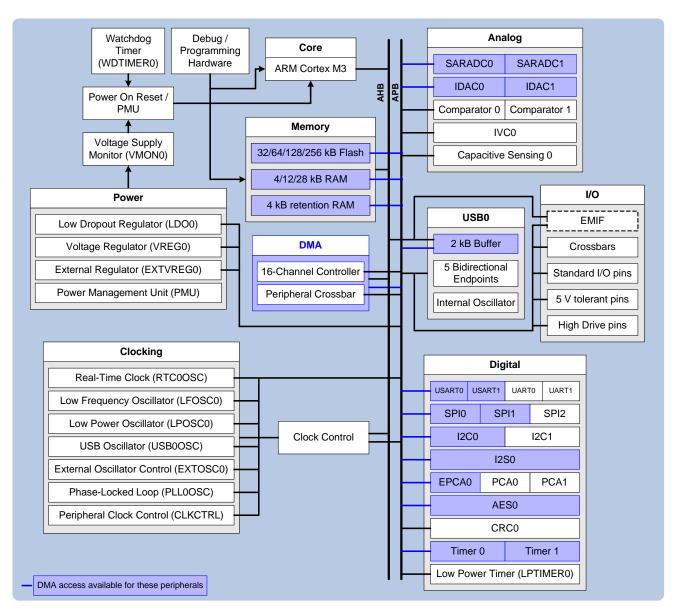

| 4. | Precision32™ SiM3U1xx System Overview                 |    |

|    | 4.1. Power                                            |    |

|    | 4.1.1. LDO and Voltage Regulator (VREG0)              |    |

|    | 4.1.2. Voltage Supply Monitor (VMON0)                 |    |

|    | 4.1.3. External Regulator (EXTVREG0)                  |    |

|    | 4.1.4. Power Management Unit (PMU)                    |    |

|    | 4.1.5. Device Power Modes                             |    |

|    | 4.2. I/O                                              |    |

|    | 4.2.1. General Features                               |    |

|    | 4.2.2. High Drive Pins (PB4)                          | 39 |

|    | 4.2.3. 5 V Tolerant Pins (PB3)                        |    |

|    | 4.2.4. Crossbars                                      |    |

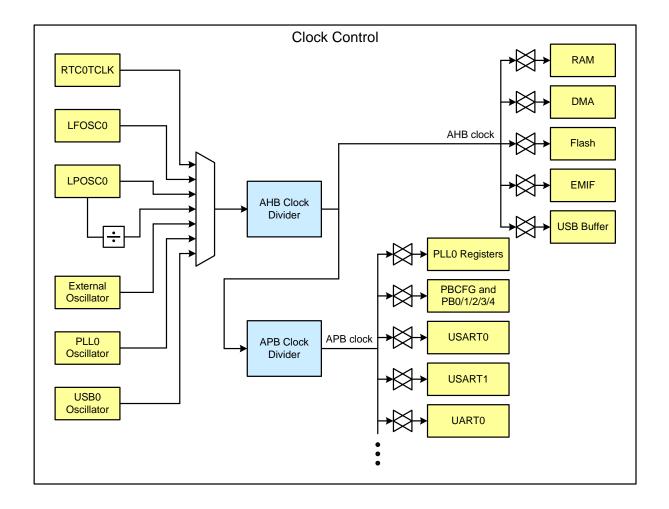

|    | 4.3. Clocking                                         |    |

|    | 4.3.1. PLL (PLL0)                                     |    |

|    | 4.3.2. Low Power Oscillator (LPOSCO)                  |    |

|    | 4.3.3. Low Frequency Oscillator (LFOSC0)              |    |

|    | 4.3.4. External Oscillators (EXTOSC0)                 |    |

|    | 4.4. Data Peripherals                                 |    |

|    | 4.4.1. 16-Channel DMA Controller                      |    |

|    | 4.4.2. 128/192/256-bit Hardware AES Encryption (AES0) |    |

|    | 4.4.3. 16/32-bit CRC (CRC0)                           |    |

|    | 4.5. Counters/Timers and PWM(5D0A6. B0A6. B0A4)       |    |

|    | 4.5.1. Programmable Counter Array (EPCA0, PCA0, PCA1) |    |

|    | 4.5.2. 32-bit Timer (TIMER0, TIMER1)                  |    |

|    | 4.5.3. Real-Time Clock (RTC0)                         |    |

|    | 4.5.4. Low Power Timer (LPTIMER0)                     |    |

|    | 4.5.5. Watchdog Timer (WDTIMER0)                      |    |

|    | 4.6. Communications Peripherals                       |    |

|    | 4.6.1. External Memory Interface (EMIF0)              |    |

|    | 4.6.2. USB0                                           |    |

|    | 4.6.3. USART (USARTO, USART1)                         |    |

|    | 4.6.4. UART (UART0, UART1)                            | 46 |

|    |                                                       |    |

|    | 4.6.5. SPI (SPI0, SPI1)                                              | 46         |

|----|----------------------------------------------------------------------|------------|

|    | 4.6.6. I2C (I2C0, I2C1)                                              |            |

|    | 4.6.7. I2S (I2S0)                                                    | 47         |

|    | 4.7. Analog                                                          |            |

|    | 4.7.1. 12-Bit Analog-to-Digital Converters (SARADC0, SARADC1)        | 48         |

|    | 4.7.2. Sample Sync Generator (SSG0)                                  | 48         |

|    | 4.7.3. 10-Bit Digital-to-Analog Converter (IDAC0, IDAC1)             | 48         |

|    | 4.7.4. 16-Channel Capacitance-to-Digital Converter (CAPSENSE0)       | 49         |

|    | 4.7.5. Low Current Comparators (CMP0, CMP1)                          |            |

|    | 4.7.6. Current-to-Voltage Converter (IVC0)                           | 49         |

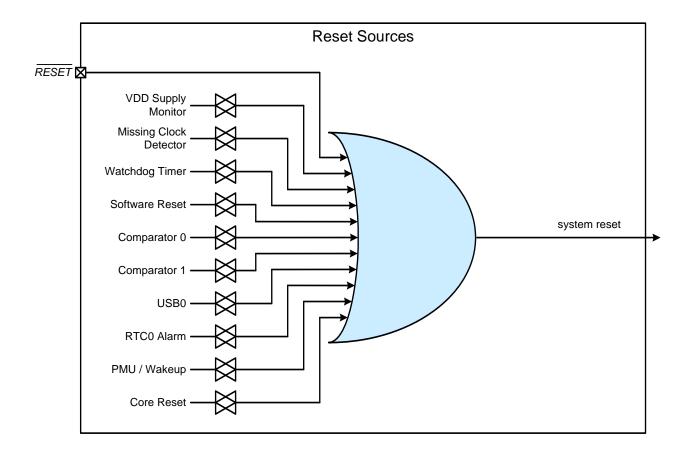

|    | 4.8. Reset Sources                                                   | 50         |

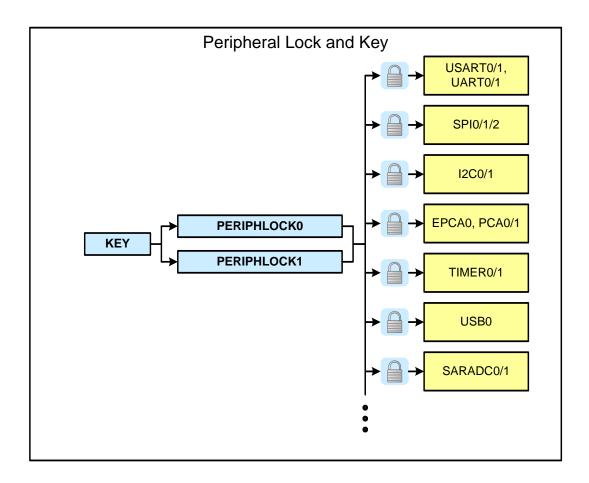

|    | 4.9. Security                                                        | 51         |

|    | 4.10.On-Chip Debugging                                               | 51         |

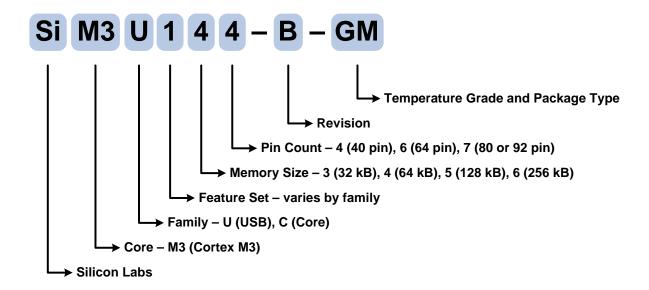

| 5. | Ordering Information                                                 | 52         |

| 6. | Pin Definitions and Packaging Information                            |            |

|    | 6.1. SiM3U1x7 Pin Definitions                                        | 54         |

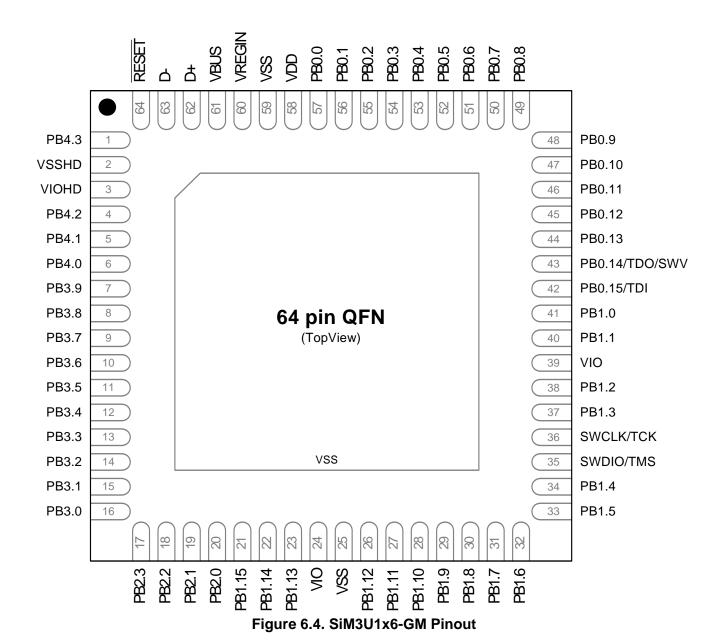

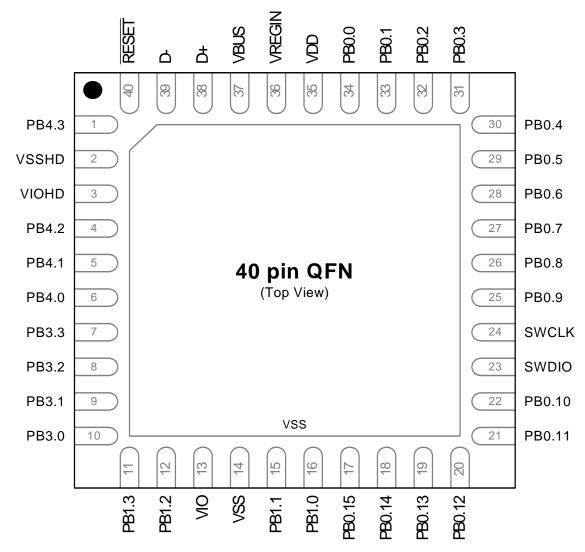

|    | 6.2. SiM3U1x6 Pin Definitions                                        | 62         |

|    | 6.3. SiM3U1x4 Pin Definitions                                        |            |

|    | 6.4. LGA-92 Package Specifications                                   |            |

|    | 6.4.1. LGA-92 Solder Mask Design                                     | 75         |

|    | 6.4.2. LGA-92 Stencil Design                                         | 75         |

|    | 6.4.3. LGA-92 Card Assembly                                          | 75         |

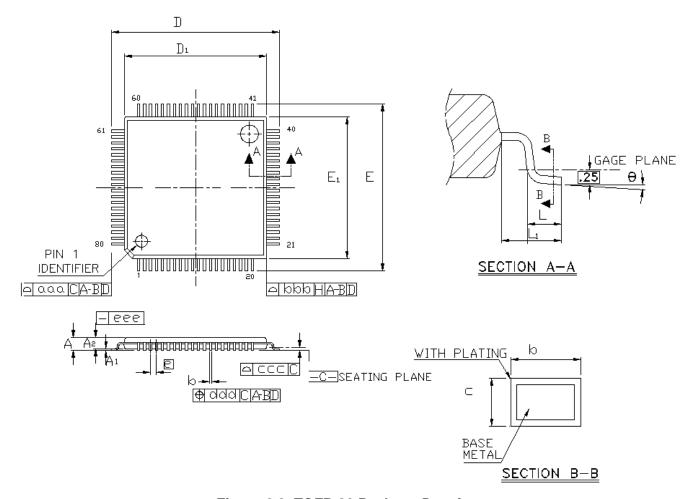

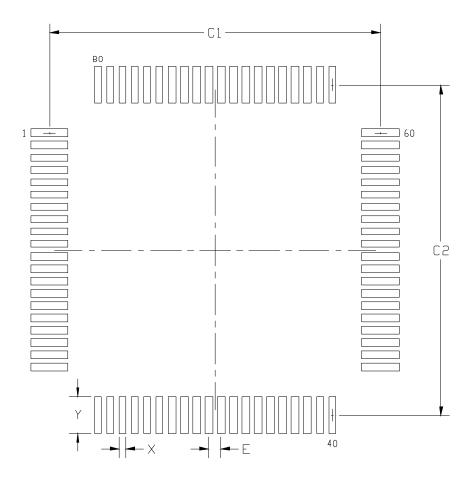

|    | 6.5. TQFP-80 Package Specifications                                  |            |

|    | 6.5.1. TQFP-80 Solder Mask Design                                    |            |

|    | 6.5.2. TQFP-80 Stencil Design                                        |            |

|    | 6.5.3. TQFP-80 Card Assembly                                         |            |

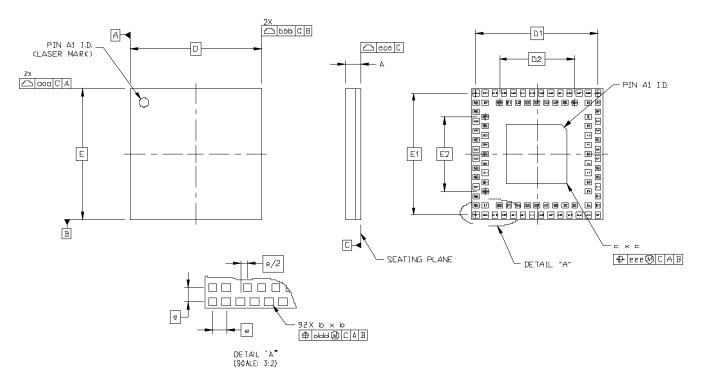

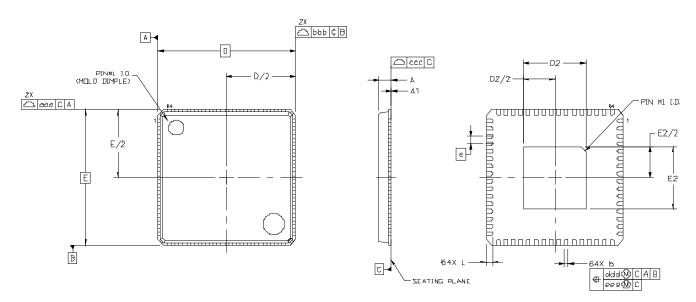

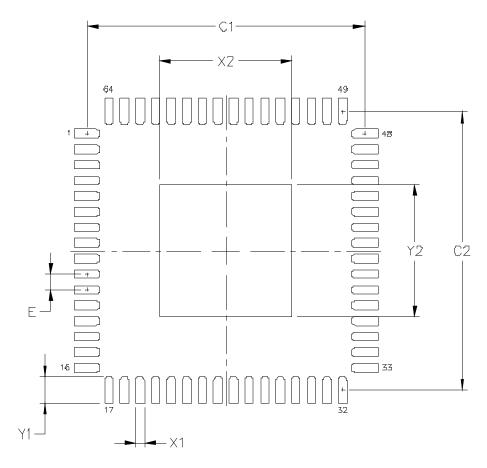

|    | 6.6. QFN-64 Package Specifications                                   |            |

|    | 6.6.1. QFN-64 Solder Mask Design                                     |            |

|    | 6.6.2. QFN-64 Stencil Design                                         |            |

|    | 6.6.3. QFN-64 Card Assembly                                          |            |

|    | 6.7. TQFP-64 Package Specifications                                  |            |

|    | 6.7.1. TQFP-64 Solder Mask Design                                    |            |

|    | 6.7.2. TQFP-64 Stencil Design                                        |            |

|    | 6.7.3. TQFP-64 Card Assembly                                         |            |

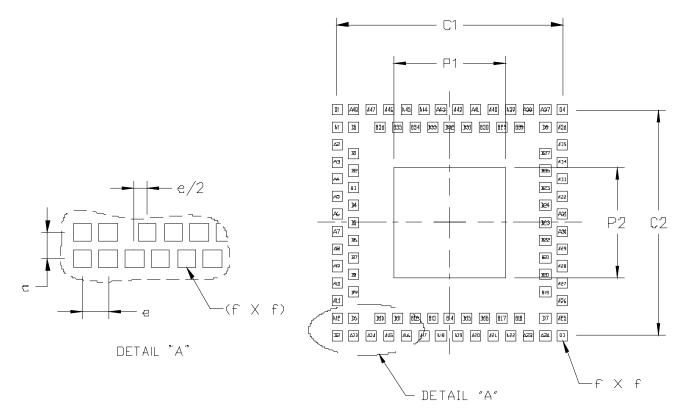

|    | 6.8. QFN-40 Package Specifications                                   |            |

|    | 6.8.1. QFN-40 Solder Mask Design                                     |            |

|    | 6.8.2. QFN-40 Stencil Design                                         |            |

| _  | 6.8.3. QFN-40 Card Assembly                                          |            |

| 7. | Revision Specific Behavior                                           |            |

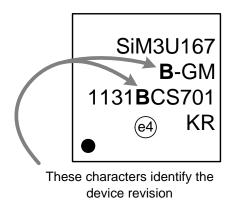

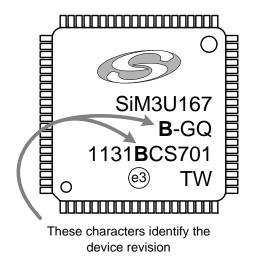

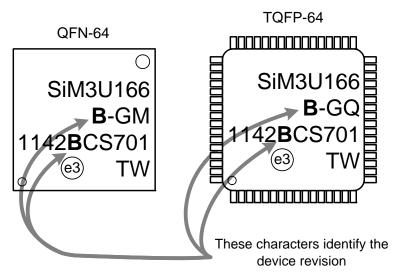

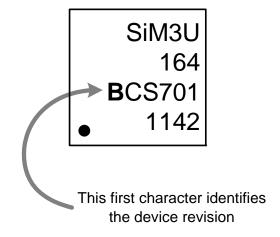

|    | 7.1. Revision Identification                                         |            |

|    | 7.2. Comparator Rising/Falling Edge Flags in Debug Mode (CMP0, CMP1) |            |

|    | 7.2.1. Problem                                                       |            |

|    | 7.2.2. Impacts                                                       |            |

|    | 7.2.3. Workaround                                                    |            |

| _  | 7.2.4. Resolution                                                    |            |

|    | ocument Change List                                                  | 92<br>94   |

|    | //////////////////////////////////////                               | <u>9</u> 4 |

# 1. Related Documents and Conventions

### 1.1. Related Documents

This data sheet accompanies several documents to provide the complete description of the SiM3U1xx device family.

### 1.1.1. SiM3U1xx/SiM3C1xx Reference Manual

The Silicon Laboratories SiM3U1xx/SiM3C1xx Reference Manual provides detailed functional descriptions for the SiM3U1xx devices.

### 1.1.2. Hardware Access Layer (HAL) API Description

The Silicon Laboratories Hardware Access Layer (HAL) API provides C-language functions to modify and read each bit in the SiM3U1xx devices. This description can be found in the SiM3xxxx HAL API Reference Manual.

#### 1.1.3. ARM Cortex-M3 Reference Manual

The ARM-specific features like the Nested Vector Interrupt Controller are described in the ARM Cortex-M3 reference documentation. The online reference manual can be found here: http://infocenter.arm.com/help/topic/com.arm.doc.subset.cortexm.m3/index.html#cortexm3.

### 1.2. Conventions

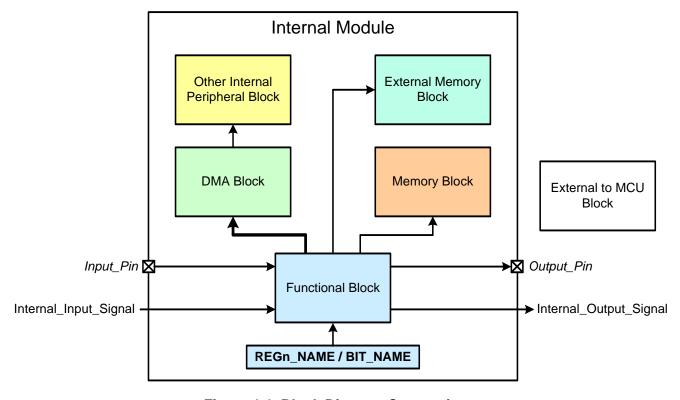

The block diagrams in this document use the following formatting conventions:

Figure 1.1. Block Diagram Conventions

# 2. Typical Connection Diagrams

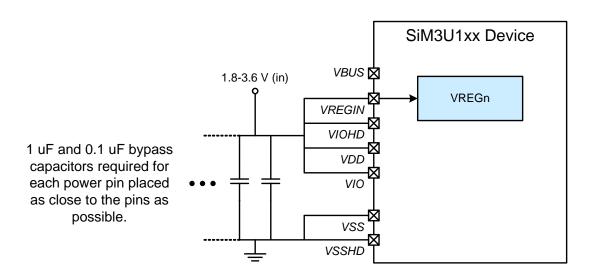

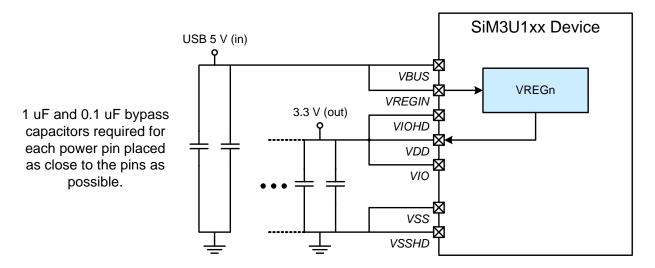

This section provides typical connection diagrams for SiM3U1xx devices.

### 2.1. Power

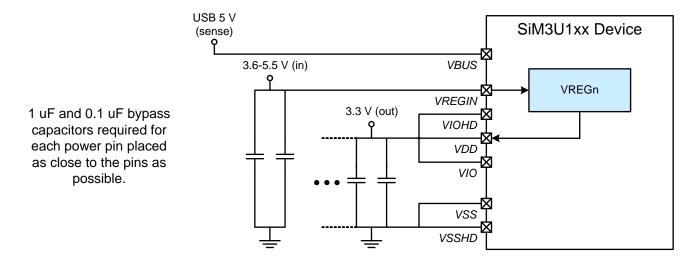

Figure 2.1 shows a typical connection diagram for the power pins of the SiM3U1xx devices when the internal regulator is in use and USB is not used.

Figure 2.1. Connection Diagram with Voltage Regulator Used and No USB

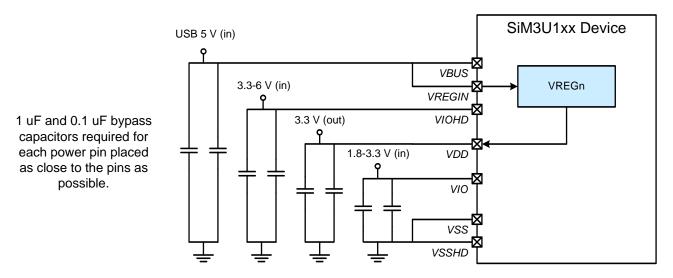

Figure 2.2 shows a typical connection diagram for the power pins of the SiM3U1xx devices when the internal regulator and USB are not used.

Figure 2.2. Connection Diagram with Voltage Regulator Not Used and No USB

Figure 2.3 shows a typical connection diagram for the power pins of the SiM3U1xx devices when the internal regulator used and USB is connected (bus-powered).

Figure 2.3. Connection Diagram with Voltage Regulator Used and USB Connected (Bus-Powered)

Figure 2.4 shows a typical connection diagram for the power pins of the SiM3U1xx devices when the internal regulator used and USB is connected (self-powered). The VBUS signal is used to detect when USB is connected to a host device.

Figure 2.4. Connection Diagram with Voltage Regulator Used and USB Connected (Self-Powered)

Figure 2.5 shows a typical connection diagram for the power pins of the SiM3U1xx devices when the internal regulator used, USB is connected (bus-powered), and the VIO and VIOHD pins are sourced from separate supplies.

Figure 2.5. Connection Diagram with Voltage Regulator Used, USB Connected (Bus-Powered), and I/O Powered Separately

# 3. Electrical Specifications

# 3.1. Electrical Characteristics

All electrical parameters in all tables are specified under the conditions listed in Table 3.1, unless stated otherwise.

**Table 3.1. Recommended Operating Conditions**

| Parameter                                            | Symbol             | Test Condition                       | Min               | Тур | Max                                                  | Unit |

|------------------------------------------------------|--------------------|--------------------------------------|-------------------|-----|------------------------------------------------------|------|

| Operating Supply Voltage on VDD                      | V <sub>DD</sub>    |                                      | 1.8               | _   | 3.6                                                  | V    |

| Operating Supply Voltage on VREGIN                   | V <sub>REGIN</sub> | EXTVREG0 Not<br>Used                 | 4                 | _   | 5.5                                                  | V    |

|                                                      |                    | EXTVREG0 Used                        | 3.0               | _   | 3.6                                                  | V    |

| Operating Supply Voltage on VIO                      | V <sub>IO</sub>    |                                      | 1.8               | _   | V <sub>DD</sub>                                      | ٧    |

| Operating Supply Voltage on VIOHD                    | V <sub>IOHD</sub>  | HV Mode (default)                    | 2.7               | _   | 6.0                                                  | ٧    |

|                                                      |                    | LV Mode                              | 1.8               | _   | 3.6                                                  | V    |

| Voltage on I/O pins, Port Bank 0, 1 and 2 I/O        | V <sub>IN</sub>    |                                      | V <sub>SS</sub>   | _   | V <sub>IO</sub>                                      | V    |

| Voltage on I/O pins, Port Bank 3 I/O and RESET       | V <sub>IN</sub>    | SiM3U1x7<br>PB3.0-PB3.7 and<br>RESET | V <sub>SS</sub>   | _   | V <sub>IO</sub> +2.0                                 | V    |

|                                                      |                    | SiM3U1x7<br>PB3.8-PB3.11             | V <sub>SS</sub>   | _   | Lowest of V <sub>IO</sub> +2.0 or V <sub>REGIN</sub> | V    |

|                                                      |                    | SiM3U1x6<br>PB3.0-PB3.5 and<br>RESET | V <sub>SS</sub>   | _   | V <sub>IO</sub> +2.0                                 | V    |

|                                                      |                    | SiM3U1x6<br>PB3.6-PB3.9              | V <sub>SS</sub>   | _   | Lowest of V <sub>IO</sub> +2.0 or V <sub>REGIN</sub> | V    |

|                                                      |                    | SiM3U1x4<br>RESET                    | V <sub>SS</sub>   | _   | V <sub>IO</sub> +2.0                                 | V    |

|                                                      |                    | SiM3U1x4<br>PB3.0-PB3.3              | V <sub>SS</sub>   | _   | Lowest of V <sub>IO</sub> +2.0 or V <sub>REGIN</sub> | V    |

| Voltage on I/O pins, Port Bank 4 I/O                 | V <sub>IN</sub>    |                                      | V <sub>SSHD</sub> | _   | V <sub>IOHD</sub>                                    | V    |

| System Clock Frequency (AHB)                         | f <sub>AHB</sub>   |                                      | 0                 | _   | 80                                                   | MHz  |

| Peripheral Clock Frequency (APB)                     | f <sub>APB</sub>   |                                      | 0                 | _   | 50                                                   | MHz  |

| Operating Ambient Temperature                        | T <sub>A</sub>     |                                      | -40               | _   | 85                                                   | °C   |

| Operating Junction Temperature                       | TJ                 |                                      | -40               | _   | 105                                                  | °C   |

| Note: All voltages with respect to V <sub>SS</sub> . |                    |                                      |                   |     |                                                      |      |

**Table 3.2. Power Consumption**

| Parameter                                                                  | Symbol          | Test Condition                                            | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------------|-----------------|-----------------------------------------------------------|-----|------|------|------|

| Digital Core Supply Current                                                |                 |                                                           |     |      | 1    | i.   |

| Normal Mode <sup>2,3,4,5</sup> —Full speed with code executing from Flash, | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz   | _   | 33   | 36.5 | mA   |

| peripheral clocks ON                                                       |                 | $F_{AHB} = F_{APB} = 48 \text{ MHz}$                      | _   | 28.5 | 31   | mA   |

|                                                                            |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 20 MHz              | _   | 10.5 | 13.3 | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 2.5 \text{ MHz}$                     | _   | 2.0  | 3.8  | mA   |

| Normal Mode <sup>2,3,4,5</sup> —Full speed with code executing from Flash, | I <sub>DD</sub> | $F_{AHB} = 80 \text{ MHz},$<br>$F_{APB} = 40 \text{ MHz}$ | _   | 22   | 24.9 | mA   |

| peripheral clocks OFF                                                      |                 | $F_{AHB} = F_{APB} = 48 \text{ MHz}$                      | _   | 14.5 | 17.2 | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 20 \text{ MHz}$                      | _   | 7.8  | 10   | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 2.5 \text{ MHz}$                     | _   | 1.2  | 3    | mA   |

| Power Mode 1 <sup>2,3,4,6</sup> —Full speed with code executing from RAM,  | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz   | _   | 30.5 | 35.5 | mA   |

| peripheral clocks ON                                                       |                 | $F_{AHB} = F_{APB} = 48 \text{ MHz}$                      | _   | 26.8 | _    | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 20 \text{ MHz}$                      | _   | 8.5  | _    | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 2.5 \text{ MHz}$                     | _   | 1.7  | _    | mA   |

| Power Mode 1 <sup>2,3,4,6</sup> —Full speed with code executing from RAM,  | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz   | _   | 20   | 23   | mA   |

| peripheral clocks OFF                                                      |                 | $F_{AHB} = F_{APB} = 48 \text{ MHz}$                      | _   | 13   | _    | mA   |

|                                                                            |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 20 MHz              | _   | 5.3  | _    | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 2.5 \text{ MHz}$                     | _   | 1.0  | _    | mA   |

| Power Mode 2 <sup>2,3,4</sup> —Core halted with peripheral clocks ON       | I <sub>DD</sub> | $F_{AHB} = 80 \text{ MHz},$<br>$F_{APB} = 40 \text{ MHz}$ | _   | 19   | 22   | mA   |

|                                                                            |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 48 MHz              | _   | 19   | _    | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 20 \text{ MHz}$                      | _   | 7.8  | _    | mA   |

|                                                                            |                 | $F_{AHB} = F_{APB} = 2.5 \text{ MHz}$                     | _   | 1.3  | _    | mA   |

- 1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

- 2. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLLOOSC (>48 MHz), USBOOSC (48 MHz) or LPOSCO (<48 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz, 1 wait state for 48 MHz, and 0 wait states at 20 MHz or less.

- 6. RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

- 8. Bias current only. Does not include dynamic current from oscillator running at speed.

Table 3.2. Power Consumption (Continued)

| Parameter                                                                      | Symbol              | Test Condition                                                                | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| Power Mode 3 <sup>2,3</sup>                                                    | I <sub>DD</sub>     | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 25 °C                               | _   | 175 | _   | μA   |

|                                                                                |                     | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                               | _   | 250 | _   | μA   |

| Power Mode 9 <sup>2,3</sup> —Low Power Shutdown with VREG0 disabled,           | I <sub>DD</sub>     | RTC Disabled,<br>V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 25 °C              | _   | 85  | _   | nA   |

| powered through VDD and VIO                                                    |                     | RTC w/ 16.4 kHz LFO,<br>V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 25 °C       | _   | 350 | _   | nA   |

|                                                                                |                     | RTC w/ 32.768 kHz Crystal,<br>V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 25 °C | _   | 620 | _   | nA   |

|                                                                                |                     | RTC Disabled,<br>V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C              | _   | 145 | _   | nA   |

|                                                                                |                     | RTC w/ 16.4 kHz LFO,<br>V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C       | _   | 500 | _   | nA   |

|                                                                                |                     | RTC w/ 32.768 kHz Crystal,<br>V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C | _   | 800 | _   | nA   |

| Power Mode 9 <sup>2,3</sup> —Low Power Shutdown with VREG0 in low-             | I <sub>VREGIN</sub> | RTC Disabled,<br>VREGIN = 5 V, T <sub>A</sub> = 25 °C                         | _   | 300 | _   | nA   |

| power mode, VDD and VIO pow-<br>ered through VREG0<br>(Includes VREG0 current) |                     | RTC w/ 16.4 kHz LFO,<br>VREGIN = 5 V, T <sub>A</sub> = 25 °C                  | _   | 650 | _   | nA   |

|                                                                                |                     | RTC w/ 32.768 kHz Crystal,<br>VREGIN = 5 V, T <sub>A</sub> = 25 °C            | _   | 950 | _   | nA   |

| VIOHD Current                                                                  | I <sub>VIOHD</sub>  | HV Mode (default)                                                             | _   | 2.5 | 5   | μA   |

| (High-drive I/O disabled)                                                      |                     | LV Mode                                                                       | _   | 2   | _   | nA   |

#### Notes:

- 1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

- 2. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLLOOSC (>48 MHz), USBOOSC (48 MHz) or LPOSCO (<48 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz, 1 wait state for 48 MHz, and 0 wait states at 20 MHz or less.

- 6. RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

- 8. Bias current only. Does not include dynamic current from oscillator running at speed.

**Table 3.2. Power Consumption (Continued)**

| Parameter                         | Symbol               | Test Condition                                               | Min | Тур  | Max  | Unit |

|-----------------------------------|----------------------|--------------------------------------------------------------|-----|------|------|------|

| Analog Peripheral Supply Current  | ts                   |                                                              |     |      |      |      |

| Voltage Regulator (VREG0)         | I <sub>VREGIN</sub>  | Normal Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 0, SUSEN = 0  | _   | 300  | _    | μA   |

|                                   |                      | Normal Mode, T <sub>A</sub> = 85 °C<br>BGDIS = 0, SUSEN = 0  | _   | _    | 650  | μA   |

|                                   |                      | Suspend Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 0, SUSEN = 1 | _   | 75   | _    | μA   |

|                                   |                      | Suspend Mode, T <sub>A</sub> = 85 °C<br>BGDIS = 0, SUSEN = 1 | _   | _    | 115  | μA   |

|                                   |                      | Sleep Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 1, SUSEN = X   | _   | 90   | _    | nA   |

|                                   |                      | Sleep Mode, T <sub>A</sub> = 85 °C<br>BGDIS = 1, SUSEN = X   | _   | _    | 500  | nA   |

| Voltage Regulator (VREG0) Sense   | I <sub>VRSENSE</sub> | SENSEEN = 1                                                  | _   | 3    | _    | μA   |

| External Regulator (EXTVREG0)     | I <sub>EXTVREG</sub> | Regulator                                                    | _   | 215  | 250  | μΑ   |

|                                   |                      | Current Sensor                                               | _   | 7    | _    | μΑ   |

| PLL0 Oscillator (PLL0OSC)         | I <sub>PLLOSC</sub>  | Operating at 80 MHz                                          | _   | 1.75 | 1.86 | mA   |

| USB0 Oscillator (USB0OSC)         | I <sub>USBOSC</sub>  | Operating at 48 MHz                                          | _   | 770  | 830  | μA   |

| USB0 Transceiver (USB0)           | I <sub>USB</sub>     | Operating at 48 MHz,<br>Full-Speed USB                       | _   | 3.9  | _    | mA   |

| Low-Power Oscillator (LPOSC0)     | I <sub>LPOSC</sub>   | Operating at 20 MHz                                          | _   | 190  | _    | μA   |

|                                   |                      | Operating at 2.5 MHz                                         | _   | 40   | _    | μA   |

| Low-Frequency Oscillator (LFOSC0) | I <sub>LFOSC</sub>   | Operating at 16.4 kHz,<br>T <sub>A</sub> = 25 °C             |     | 215  |      | nA   |

|                                   |                      | Operating at 16.4 kHz,<br>T <sub>A</sub> = 85 °C             | _   | _    | 500  | nA   |

- 1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

- 2. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLLOOSC (>48 MHz), USBOOSC (48 MHz) or LPOSCO (<48 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz, 1 wait state for 48 MHz, and 0 wait states at 20 MHz or less.

- 6. RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

- 8. Bias current only. Does not include dynamic current from oscillator running at speed.

**Table 3.2. Power Consumption (Continued)**

| Parameter                                  | Symbol              | Test Condition                                    | Min | Тур | Max | Unit |

|--------------------------------------------|---------------------|---------------------------------------------------|-----|-----|-----|------|

| External Oscillator (EXTOSC0) <sup>8</sup> | I <sub>EXTOSC</sub> | FREQCN = 111                                      | _   | 3.8 | 4.7 | mA   |

|                                            |                     | FREQCN = 110                                      | _   | 840 | 950 | μA   |

|                                            |                     | FREQCN = 101                                      | _   | 185 | 220 | μA   |

|                                            |                     | FREQCN = 100                                      | _   | 65  | 80  | μA   |

|                                            |                     | FREQCN = 011                                      | _   | 25  | 30  | μA   |

|                                            |                     | FREQCN = 010                                      | _   | 10  | 15  | μA   |

|                                            |                     | FREQCN = 001                                      | _   | 5   | 10  | μA   |

|                                            |                     | FREQCN = 000                                      | _   | 3   | 8   | μA   |

| SARADC0,<br>SARADC1                        | I <sub>SARADC</sub> | Sampling at 1 Msps, highest power mode settings.  | _   | 1.2 | 1.5 | mA   |

|                                            |                     | Sampling at 250 ksps, lowest power mode settings. | _   | 390 | 510 | μA   |

| Temperature Sensor                         | I <sub>TSENSE</sub> |                                                   | _   | 75  | 105 | μA   |

| Internal SAR Reference                     | I <sub>REFFS</sub>  | Normal Power Mode                                 | _   | 680 | 750 | μA   |

| internal SAK Reference                     |                     | Low Power Mode                                    | _   | 160 | 190 | μA   |

| VREF0                                      | I <sub>REFP</sub>   |                                                   | _   | 75  | 100 | μA   |

| Comparator 0 (CMP0),                       | I <sub>CMP</sub>    | CMPMD = 11                                        | _   | 0.5 | _   | μA   |

| Comparator 1 (CMP1)                        |                     | CMPMD = 10                                        | _   | 3   | _   | μA   |

|                                            |                     | CMPMD = 01                                        | _   | 10  | _   | μA   |

|                                            |                     | CMPMD = 00                                        | _   | 25  | _   | μA   |

| Capacitive Sensing (CAPSENSE0)             | I <sub>CS</sub>     | Continuous Conversions                            | _   | 55  | 80  | μA   |

| IDAC0 <sup>7</sup> ,<br>IDAC1 <sup>7</sup> | I <sub>IDAC</sub>   |                                                   | _   | 75  | 90  | μA   |

| IVC0 <sup>7</sup>                          | I <sub>IVC</sub>    | I <sub>IN</sub> = 0                               | _   | 1.5 | 2.5 | μA   |

| Voltage Supply Monitor (VMON0)             | I <sub>VMON</sub>   |                                                   | _   | 15  | 25  | μA   |

#### Notes:

- 1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

- 2. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLLOSC (>48 MHz), USBOSC (48 MHz) or LPOSCO (<48 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz, 1 wait state for 48 MHz, and 0 wait states at 20 MHz or less.

- **6.** RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

- 8. Bias current only. Does not include dynamic current from oscillator running at speed.

**Table 3.2. Power Consumption (Continued)**

| Parameter            | Symbol               | Test Condition | Min | Тур | Max | Unit |

|----------------------|----------------------|----------------|-----|-----|-----|------|

| Flash Current on VDD |                      |                |     |     |     |      |

| Write Operation      | I <sub>FLASH-W</sub> |                | _   | _   | 8   | mA   |

| Erase Operation      | I <sub>FLASH-E</sub> |                | _   | _   | 15  | mA   |

- 1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

- 2. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLL0OSC (>48 MHz), USB0OSC (48 MHz) or LPOSC0 (<48 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz, 1 wait state for 48 MHz, and 0 wait states at 20 MHz or less.

- 6. RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

- 8. Bias current only. Does not include dynamic current from oscillator running at speed.

## **Table 3.3. Power Mode Wake Up Times**

| Parameter                   | Symbol             | Conditions | Min | Тур | Max | Units  |

|-----------------------------|--------------------|------------|-----|-----|-----|--------|

| Power Mode 2 Wake Time      | t <sub>PM2</sub>   |            | 4   | _   | 5   | clocks |

| Power Mode 3 Fast Wake Time | t <sub>PM3FW</sub> |            | _   | 425 | _   | μs     |

| Power Mode 9 Wake Time      | t <sub>PM9</sub>   |            | _   | 12  | _   | μs     |

**Table 3.4. Reset and Supply Monitor**

| Parameter                                                         | Symbol            | Test Condition                                          | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------|-------------------|---------------------------------------------------------|------|------|------|------|

| V <sub>DD</sub> High Supply Monitor Threshold                     | $V_{VDDMH}$       | Early Warning                                           | 2.10 | 2.20 | 2.30 | V    |

| (VDDHITHEN = 1)                                                   |                   | Reset                                                   | 1.95 | 2.05 | 2.1  | V    |

| V <sub>DD</sub> Low Supply Monitor Threshold                      | $V_{VDDML}$       | Early Warning                                           | 1.81 | 1.85 | 1.88 | V    |

| (VDDHITHEN = 0)                                                   |                   | Reset                                                   | 1.70 | 1.74 | 1.77 | V    |

| V <sub>REGIN</sub> Supply Monitor Threshold                       | $V_{VREGM}$       | Early Warning                                           | 4.2  | 4.4  | 4.6  | V    |

| Power-On Reset (POR) Threshold                                    | V <sub>POR</sub>  | Rising Voltage on V <sub>DD</sub>                       | _    | 1.4  | _    | V    |

|                                                                   |                   | Falling Voltage on V <sub>DD</sub>                      | 0.8  | 1    | 1.3  | V    |

| V <sub>DD</sub> Ramp Time                                         | t <sub>RMP</sub>  | Time to V <sub>DD</sub> ≥ 1.8 V                         | 10   | _    | 3000 | μs   |

| Reset Delay from POR                                              | t <sub>POR</sub>  | Relative to V <sub>DD</sub> ≥ V <sub>POR</sub>          | 3    | _    | 100  | ms   |

| Reset Delay from non-POR source                                   | t <sub>RST</sub>  | Time between release of reset source and code execution | _    | 10   | _    | μs   |

| RESET Low Time to Generate Reset                                  | t <sub>RSTL</sub> |                                                         | 50   | _    | _    | ns   |

| Missing Clock Detector Response Time (final rising edge to reset) | t <sub>MCD</sub>  | F <sub>AHB</sub> > 1 MHz                                | _    | 0.4  | 1    | ms   |

| Missing Clock Detector Trigger<br>Frequency                       | F <sub>MCD</sub>  |                                                         | _    | 7.5  | 13   | kHz  |

| V <sub>DD</sub> Supply Monitor Turn-On Time                       | t <sub>MON</sub>  |                                                         | _    | 2    | _    | μs   |

**Table 3.5. On-Chip Regulators**

| Parameter                         | Symbol             | Test Condition                                                                  | Min  | Тур  | Max | Unit  |

|-----------------------------------|--------------------|---------------------------------------------------------------------------------|------|------|-----|-------|

| 3.3 V Regulator Characteristics ( | VREG0, Supp        | olied from VREGIN Pin)                                                          |      |      |     | +     |

| Output Voltage (at VDD pin)       | V <sub>DDOUT</sub> | $4 \le V_{REGIN} \le 5.5$<br>BGDIS = 0, SUSEN = 0                               | 3.15 | 3.3  | 3.4 | V     |

|                                   |                    | $4 \le V_{REGIN} \le 5.5$<br>BGDIS = 0, SUSEN = 1                               | 3.15 | 3.3  | 3.4 | V     |

|                                   |                    | $4 \le V_{REGIN} \le 5.5$<br>BGDIS = 1, SUSEN = X<br>$I_{DDOUT} = 500 \mu A$    | 2.3  | 2.8  | 3.6 | V     |

|                                   |                    | $4 \le V_{REGIN} \le 5.5$<br>BGDIS = 1, SUSEN = X<br>$I_{DDOUT} = 5 \text{ mA}$ | 2.1  | 2.65 | 3.3 | V     |

| Output Current (at VDD pin)*      | I <sub>DDOUT</sub> | $4 \le V_{REGIN} \le 5.5$<br>BGDIS = 0, SUSEN = X                               | _    | _    | 150 | mA    |

|                                   |                    | $4 \le V_{REGIN} \le 5.5$<br>BGDIS = 1, SUSEN = X                               | _    | _    | 5   | mA    |

| Output Load Regulation            | V <sub>DDLR</sub>  | BGDIS = 0                                                                       | _    | 0.1  | 1   | mV/mA |

| Output Capacitance                | C <sub>VDD</sub>   |                                                                                 | 1    | _    | 10  | μF    |

\*Note: Total current VREG0 is capable of providing. Any current consumed by the SiM3U1xx reduces the current available to external devices powered from VDD.

Table 3.6. External Regulator

| Parameter                              | Symbol                                         | Test Condition                                       | Min                         | Тур                          | Max                | Unit  |

|----------------------------------------|------------------------------------------------|------------------------------------------------------|-----------------------------|------------------------------|--------------------|-------|

| Input Voltage Range (at VRE-GIN)       | V <sub>REGIN</sub>                             |                                                      | 3.0                         | _                            | 3.6                | V     |

| Output Voltage (at<br>EXREGOUT)        | V <sub>EXREGOUT</sub>                          | Programmable in 100 mV steps                         | 1.8                         | _                            | 3.6                | V     |

| NPN Current Drive                      | I <sub>NPN</sub>                               | 400 mV Dropout                                       | 12                          | _                            |                    | mA    |

| PNP Current Drive                      | I <sub>PNP</sub>                               | V <sub>EXREGBD</sub> > V <sub>REGIN</sub> -<br>1.5 V | -6                          | _                            | _                  | mA    |

| EXREGBD Voltage (PNP<br>Mode)          | V <sub>EXREGBD</sub>                           | V <sub>REGIN</sub> >= 3.5 V                          | V <sub>REGIN</sub><br>– 2.0 | _                            | _                  | V     |

|                                        |                                                | V <sub>REGIN</sub> < 3.5 V                           | 1.5                         | _                            |                    | V     |

| Standalone Mode Output<br>Current      | I <sub>EXTREGBD</sub>                          | 400mV Dropout                                        | _                           | _                            | 11.5               | mA    |

| External Capacitance with External BJT | C <sub>BJT</sub>                               |                                                      | 4.7                         | _                            | _                  | μF    |

| Standalone Mode Load Regulation        | LR <sub>STAND</sub> -<br>ALONE                 |                                                      | _                           | 1                            | _                  | mV/mA |

| Standalone Mode External Capacitance   | C <sub>STAND</sub> -<br>ALONE                  |                                                      | 47                          | _                            | _                  | nF    |

| Current Limit Range                    | I <sub>LIMIT</sub>                             | 1 Ω Sense Resistor                                   | 10                          | _                            | 720                | mA    |

| Current Limit Accuracy                 |                                                |                                                      | _                           | _                            | 10                 | %     |

| Foldback Limit Accuracy                |                                                |                                                      | _                           | _                            | 20                 | %     |

| Current Sense Resistor                 | R <sub>SENSE</sub>                             |                                                      | _                           | _                            | 1                  | Ω     |

| Internal Pull-Down                     | R <sub>PD</sub>                                |                                                      | _                           | 5                            | _                  | kΩ    |

| Internal Pull-Up                       | R <sub>PU</sub>                                |                                                      | _                           | 10                           | 1                  | kΩ    |

| Current Sensor                         |                                                |                                                      |                             |                              |                    |       |

| Sensing Pin Voltage                    | V <sub>EXTREGSP</sub><br>V <sub>EXTREGSN</sub> | Measured at EXTREGSP or EXTREGSN pin                 | 2.2                         | _                            | V <sub>REGIN</sub> | V     |

| Differential Sensing Voltage           | V <sub>DIFF</sub>                              | (V <sub>EXTREGSP</sub> -<br>V <sub>EXTREGSN</sub> )  | 10                          | _                            | 1600               | mV    |

| Current at EXTREGSN Pin                | I <sub>EXTREGSN</sub>                          |                                                      | _                           | 8                            | _                  | μΑ    |

| Current at EXTREGSP Pin                | I <sub>EXTREGSP</sub>                          |                                                      | _                           | V <sub>DIFF</sub> x 200 + 12 | _                  | μА    |

**Table 3.7. Flash Memory**

| Parameter                                  | Symbol             | Test Condition                    | Min | Тур  | Max | Unit   |

|--------------------------------------------|--------------------|-----------------------------------|-----|------|-----|--------|

| Write Time <sup>1</sup>                    | t <sub>WRITE</sub> | One 16-bit Half Word              | 20  | 21   | 22  | μs     |

| Erase Time <sup>1</sup>                    | t <sub>ERASE</sub> | One Page                          | 20  | 21   | 22  | ms     |

|                                            | t <sub>ERALL</sub> | Full Device                       | 20  | 21   | 22  | ms     |

| V <sub>DD</sub> Voltage During Programming | V <sub>PROG</sub>  |                                   | 1.8 | _    | 3.6 | V      |

| Endurance (Write/Erase Cycles)             | N <sub>WE</sub>    |                                   | 20k | 100k | _   | Cycles |

| Retention <sup>2</sup>                     | t <sub>RET</sub>   | T <sub>A</sub> = 25 °C, 1k Cycles | 10  | 100  | _   | Years  |

- 1. Does not include sequencing time before and after the write/erase operation, which may take up to 35 µs. During a sequential write operation, this extra time is only taken prior to the first write and after the last write.

- 2. Additional Data Retention Information is published in the Quarterly Quality and Reliability Report.

**Table 3.8. Internal Oscillators**

| Parameter                            | Symbol                 | Test Condition                                                                | Min   | Тур | Max   | Unit   |  |  |  |

|--------------------------------------|------------------------|-------------------------------------------------------------------------------|-------|-----|-------|--------|--|--|--|

| USB Oscillator (USB0OSC)             |                        |                                                                               |       |     |       |        |  |  |  |

| Oscillator Frequency                 | f <sub>USB0OSC</sub>   | No Clock Recovery,<br>Full Temperature and<br>Supply Range                    | 47.3  | 48  | 48.7  | MHz    |  |  |  |

|                                      |                        | No Clock Recovery,<br>$T_A = 25 ^{\circ}\text{C},$<br>$V_{DD} = 3.3 \text{V}$ | 47.5  | 48  | 48.5  | MHz    |  |  |  |

|                                      |                        | USB Active with Clock<br>Recovery,<br>Full Temperature and<br>Supply Range    | 47.88 | 48  | 48.12 | MHz    |  |  |  |

| Power Supply Sensitivity             | PSS <sub>USBOOSC</sub> | T <sub>A</sub> = 25 °C                                                        | _     | 175 | _     | ppm/V  |  |  |  |

| Temperature Sensitivity              | TS <sub>USBOOSC</sub>  | V <sub>DD</sub> = 3.3 V                                                       |       | 45  | _     | ppm/°C |  |  |  |

| Phase-Locked Loop (PLL0OSC)          |                        |                                                                               |       |     |       |        |  |  |  |

| Calibrated Output Frequency*         | f <sub>PLL0OSC</sub>   | Full Temperature and Supply Range                                             | 77    | 79  | 80    | MHz    |  |  |  |

| Power Supply Sensitivity*            | PSS <sub>PLL0OSC</sub> | T <sub>A</sub> = 25 °C,<br>Fout = 79 MHz                                      | _     | 430 | _     | ppm/V  |  |  |  |

| Temperature Sensitivity*             | TS <sub>PLL0OSC</sub>  | V <sub>DD</sub> = 3.3 V,<br>Fout = 79 MHz                                     | _     | 95  | _     | ppm/°C |  |  |  |

| Adjustable Output Frequency<br>Range | f <sub>PLL0OSC</sub>   |                                                                               | 23    | _   | 80    | MHz    |  |  |  |

Table 3.8. Internal Oscillators (Continued)

| Parameter                                   | Symbol                | Test Condition                                                                              | Min   | Тур  | Max   | Unit   |

|---------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------|-------|------|-------|--------|

| Lock Time                                   | t <sub>PLL0LOCK</sub> | $f_{REF} = 48 \text{ MHz},$<br>$f_{PLL0OSC} = 80 \text{ MHz},$<br>M=59, N=99,<br>LOCKTH = 0 | _     | 1.7  | _     | μs     |

|                                             |                       | $f_{REF} = 20 \text{ MHz},$<br>$f_{PLL0OSC} = 80 \text{ MHz},$<br>M=24, N=99,<br>LOCKTH = 0 | _     | 1.7  | _     | μs     |

|                                             |                       | f <sub>REF</sub> = 32 kHz,<br>f <sub>PLL0OSC</sub> = 80 MHz,<br>M=0, N=2440,<br>LOCKTH = 0  | _     | 91   | _     | μs     |

| Low Power Oscillator (LPOSC0)               |                       |                                                                                             |       |      |       |        |

| Oscillator Frequency                        | f <sub>LPOSC</sub>    | Full Temperature and Supply Range                                                           | 19    | 20   | 21    | MHz    |

|                                             |                       | T <sub>A</sub> = 25 °C,<br>V <sub>DD</sub> = 3.3 V                                          | 19.5  | 20   | 20.5  | MHz    |

| Divided Oscillator Frequency                | f <sub>LPOSCD</sub>   | Full Temperature and Supply Range                                                           | 2.375 | 2.5  | 2.625 | MHz    |

| Power Supply Sensitivity                    | PSS <sub>LPOSC</sub>  | T <sub>A</sub> = 25 °C                                                                      | _     | 0.5  | _     | %/V    |

| Temperature Sensitivity                     | TS <sub>LPOSC</sub>   | V <sub>DD</sub> = 3.3 V                                                                     |       | 55   | _     | ppm/°C |

| Low Frequency Oscillator (LFOS              | SC0)                  |                                                                                             |       |      |       |        |

| Oscillator Frequency                        | f <sub>LFOSC</sub>    | Full Temperature and Supply Range                                                           | 13.4  | 16.4 | 19.7  | kHz    |

|                                             |                       | T <sub>A</sub> = 25 °C,<br>V <sub>DD</sub> = 3.3 V                                          | 15.8  | 16.4 | 17.3  | kHz    |

| Power Supply Sensitivity                    | PSS <sub>LFOSC</sub>  | T <sub>A</sub> = 25 °C                                                                      | _     | 2.4  | _     | %/V    |

| Temperature Sensitivity                     | TS <sub>LFOSC</sub>   | V <sub>DD</sub> = 3.3 V                                                                     | _     | 0.2  | _     | %/°C   |

| RTC0 Oscillator (RTC0OSC)                   | 1                     | 1                                                                                           |       |      | ı     |        |

| Missing Clock Detector Trigger<br>Frequency | f <sub>RTCMCD</sub>   |                                                                                             | _     | 8    | 15    | kHz    |

| RTC Robust Duty Cycle Range                 | DC <sub>RTC</sub>     |                                                                                             | 25    | _    | 55    | %      |

| *Note: PLL0OSC in free-running osci         | lator mode            |                                                                                             |       |      |       |        |

**Table 3.9. External Oscillator**

| Parameter                                         | Symbol             | Test Condition | Min  | Тур | Max | Unit |  |

|---------------------------------------------------|--------------------|----------------|------|-----|-----|------|--|

| External Input CMOS Clock<br>Frequency*           | f <sub>CMOS</sub>  |                | 0    | _   | 50  | MHz  |  |

| External Input CMOS Clock High Time               | t <sub>CMOSH</sub> |                | 9    | _   | _   | ns   |  |

| External Input CMOS Clock Low Time                | t <sub>CMOSL</sub> |                | 9    | _   | _   | ns   |  |

| External Crystal Clock Frequency                  | f <sub>XTAL</sub>  |                | 0.01 | _   | 30  | MHz  |  |

| *Note: Minimum of 10 kHz during debug operations. |                    |                |      |     |     |      |  |

Table 3.10. SAR ADC

| Parameter                        | Symbol              | Test Condition                                                   | Min | Тур   | Max                | Unit |

|----------------------------------|---------------------|------------------------------------------------------------------|-----|-------|--------------------|------|

| Resolution                       | N <sub>bits</sub>   | 12 Bit Mode                                                      |     | 12    |                    | Bits |

|                                  |                     | 10 Bit Mode                                                      |     | 10    |                    | Bits |

| Supply Voltage Requirements      | V <sub>ADC</sub>    | High Speed Mode                                                  | 2.2 | _     | 3.6                | V    |

| (VDD)                            |                     | Low Power Mode                                                   | 1.8 | _     | 3.6                | V    |

| Throughput Rate                  | f <sub>S</sub>      | 12 Bit Mode                                                      | _   | _     | 250                | ksps |

| (High Speed Mode)                |                     | 10 Bit Mode                                                      | _   | _     | 1                  | Msps |

| Throughput Rate                  | f <sub>S</sub>      | 12 Bit Mode                                                      | _   | _     | 62.5               | ksps |

| (Low Power Mode)                 |                     | 10 Bit Mode                                                      | _   | _     | 250                | ksps |

| Tracking Time                    | t <sub>TRK</sub>    | High Speed Mode                                                  | 230 | _     | _                  | ns   |

|                                  |                     | Low Power Mode                                                   | 450 | _     | _                  | ns   |

| SAR Clock Frequency              | f <sub>SAR</sub>    | High Speed Mode                                                  | _   | _     | 16.24              | MHz  |

|                                  |                     | Low Power Mode                                                   | _   | _     | 4                  | MHz  |

| Conversion Time                  | t <sub>CNV</sub>    | 10-Bit Conversion,<br>SAR Clock = 16 MHz,<br>APB Clock = 40 MHz. |     | 762.5 |                    |      |

| Sample/Hold Capacitor            | C <sub>SAR</sub>    | Gain = 1                                                         | _   | 5     | _                  | pF   |

|                                  |                     | Gain = 0.5                                                       | _   | 2.5   | _                  | pF   |

| Input Pin Capacitance            | C <sub>IN</sub>     | High Quality Inputs                                              | _   | 18    | _                  | pF   |

|                                  |                     | Normal Inputs                                                    | _   | 20    | _                  | pF   |

| Input Mux Impedance              | R <sub>MUX</sub>    | High Quality Inputs                                              | _   | 300   | _                  | Ω    |

|                                  |                     | Normal Inputs                                                    | _   | 550   | _                  | Ω    |

| Voltage Reference Range          | V <sub>REF</sub>    |                                                                  | 1   | _     | $V_{DD}$           | V    |

| Input Voltage Range <sup>1</sup> | V <sub>IN</sub>     | Gain = 1                                                         | 0   | _     | V <sub>REF</sub>   | V    |

|                                  |                     | Gain = 0.5                                                       | 0   | _     | 2xV <sub>REF</sub> | V    |

| Power Supply Rejection Ratio     | PSRR <sub>ADC</sub> |                                                                  | _   | 70    | _                  | dB   |

| DC Performance                   |                     |                                                                  | •   |       |                    |      |

| Integral Nonlinearity            | INL                 | 12 Bit Mode <sup>2</sup>                                         | _   | ±1    | ±1.9               | LSB  |

|                                  |                     | 10 Bit Mode                                                      | _   | ±0.2  | ±0.5               | LSB  |

## Notes:

- 1. Absolute input pin voltage is limited by the lower of the supply at VDD and VIO.

- 2. INL and DNL specifications for 12-bit mode do not include the first or last four ADC codes.

- 3. The maximum code in 12-bit mode is 0xFFFC. The Slope Error is referenced from the maximum code.

Table 3.10. SAR ADC (Continued)

| Parameter                                                                            | Symbol            | Test Condition           | Min   | Тур   | Max  | Unit   |  |  |  |

|--------------------------------------------------------------------------------------|-------------------|--------------------------|-------|-------|------|--------|--|--|--|

| Differential Nonlinearity                                                            | DNL               | 12 Bit Mode <sup>2</sup> | -1    | ±0.7  | 1.8  | LSB    |  |  |  |

| (Guaranteed Monotonic)                                                               |                   | 10 Bit Mode              | _     | ±0.2  | ±0.5 | LSB    |  |  |  |

| Offset Error (using VREFGND)                                                         | E <sub>OFF</sub>  | 12 Bit Mode, VREF =2.4 V | -2    | 0     | 2    | LSB    |  |  |  |

|                                                                                      |                   | 10 Bit Mode, VREF =2.4 V | -1    | 0     | 1    | LSB    |  |  |  |

| Offset Temperatue Coefficient                                                        | TC <sub>OFF</sub> |                          | _     | 0.004 | _    | LSB/°C |  |  |  |

| Slope Error <sup>3</sup>                                                             | E <sub>M</sub>    | 12 Bit Mode              | -0.07 | -0.02 | 0.02 | %      |  |  |  |

| Dynamic Performance with 10 kHz Sine Wave Input 1dB below full scale, Max throughput |                   |                          |       |       |      |        |  |  |  |

| Signal-to-Noise                                                                      | SNR               | 12 Bit Mode              | 62    | 66    | _    | dB     |  |  |  |

|                                                                                      |                   | 10 Bit Mode              | 58    | 60    | _    | dB     |  |  |  |

| Signal-to-Noise Plus Distortion                                                      | SNDR              | 12 Bit Mode              | 62    | 66    | _    | dB     |  |  |  |

|                                                                                      |                   | 10 Bit Mode              | 58    | 60    | _    | dB     |  |  |  |

| Total Harmonic Distortion (Up to                                                     | THD               | 12 Bit Mode              | _     | 78    | _    | dB     |  |  |  |

| 5th Harmonic)                                                                        |                   | 10 Bit Mode              | _     | 77    | _    | dB     |  |  |  |

| Spurious-Free Dynamic Range                                                          | SFDR              | 12 Bit Mode              | _     | -79   | _    | dB     |  |  |  |

|                                                                                      |                   | 10 Bit Mode              | _     | -74   | _    | dB     |  |  |  |

- 1. Absolute input pin voltage is limited by the lower of the supply at VDD and VIO.

- 2. INL and DNL specifications for 12-bit mode do not include the first or last four ADC codes.

- 3. The maximum code in 12-bit mode is 0xFFFC. The Slope Error is referenced from the maximum code.

Table 3.11. IDAC

| Parameter                                        | Symbol            | Test Condition           | Min  | Тур   | Max                   | Unit   |

|--------------------------------------------------|-------------------|--------------------------|------|-------|-----------------------|--------|

| Static Performance                               |                   |                          | L    |       |                       |        |

| Resolution                                       | N <sub>bits</sub> |                          |      | 10    |                       | Bits   |

| Integral Nonlinearity                            | INL               |                          | _    | ±0.5  | ±2                    | LSB    |

| Differential Nonlinearity (Guaranteed Monotonic) | DNL               |                          | _    | ±0.5  | ±1                    | LSB    |

| Output Compliance Range                          | V <sub>OCR</sub>  |                          | _    | _     | V <sub>DD</sub> – 1.0 | V      |

| Full Scale Output Current                        | I <sub>OUT</sub>  | 2 mA Range               | 2.0  | 2.046 | 2.10                  | mA     |

|                                                  |                   | 1 mA Range               | 0.99 | 1.023 | 1.05                  | mA     |

|                                                  |                   | 0.5 mA Range             | 493  | 511.5 | 525                   | μA     |

| Offset Error                                     | E <sub>OFF</sub>  |                          | _    | 250   | _                     | nA     |

| Full Scale Error Tempco                          | TC <sub>FS</sub>  | 2 mA Range               | _    | 100   | _                     | ppm/°C |

| VDD Power Supply Rejection Ratio                 |                   | 2 mA Range               | _    | -220  | _                     | ppm/V  |

| Test Load Impedance (to V <sub>SS</sub> )        | R <sub>TEST</sub> |                          | _    | 1     | _                     | kΩ     |

| Dynamic Performance                              |                   |                          |      |       |                       |        |

| Output Settling Time to 1/2 LSB                  |                   | min output to max output | _    | 1.2   | _                     | μs     |

| Startup Time                                     |                   |                          | _    | 3     | _                     | μs     |

**Table 3.12. Capacitive Sense**

| Parameter                                      | Symbol              | Test Condition                 | Min | Тур | Max | Unit |

|------------------------------------------------|---------------------|--------------------------------|-----|-----|-----|------|

| Single Conversion Time (Default Configuration) | t <sub>single</sub> | 12-bit Mode                    | _   | 25  | _   | μs   |

|                                                |                     | 13-bit Mode                    | _   | 27  | _   | μs   |

|                                                | _                   | 14-bit Mode                    | _   | 29  | _   | μs   |

|                                                |                     | 16-bit Mode                    | _   | 33  | _   | μs   |

| Maximum External Capacitive Load               | C <sub>L</sub>      | Highest Gain Setting (default) | _   | 45  | _   | pF   |

|                                                |                     | Lowest Gain Setting            | _   | 500 | _   | pF   |

| Maximum External Series Impedance              | C <sub>L</sub>      | Highest Gain Setting (default) | _   | 50  | _   | kΩ   |

Table 3.13. Current-to-Voltage Converter (IVC)

| Parameter                      | Symbol              | Test Condition                       | Min  | Тур  | Max  | Unit  |

|--------------------------------|---------------------|--------------------------------------|------|------|------|-------|

| Supply Voltage (VDD)           | V <sub>DDIVC</sub>  |                                      | 2.2  | _    | 3.6  | V     |

| Input Pin Voltage              | V <sub>IN</sub>     |                                      | 2.2  | _    | VDD  | V     |

| Minimum Input Current (source) | I <sub>IN</sub>     |                                      | 100  | _    | _    | μA    |

| Integral Nonlinearity          | INL <sub>IVC</sub>  |                                      | -0.6 | _    | 0.6  | %     |

| Full Scale Output              | V <sub>IVCOUT</sub> |                                      | _    | 1.65 | _    | V     |

| Slope                          | M <sub>IVC</sub>    | Input Range 1 mA<br>(INxRANGE = 101) | 1.55 | 1.65 | 1.75 | V/mA  |

|                                |                     | Input Range 2 mA<br>(INxRANGE = 100) | 795  | 830  | 860  | mV/mA |

|                                |                     | Input Range 3 mA<br>(INxRANGE = 011) | 525  | 550  | 570  | mV/mA |

|                                |                     | Input Range 4 mA<br>(INxRANGE = 010) | 390  | 415  | 430  | mV/mA |

|                                |                     | Input Range 5 mA<br>(INxRANGE = 001) | 315  | 330  | 340  | mV/mA |

|                                |                     | Input Range 6 mA<br>(INxRANGE = 000) | 260  | 275  | 285  | mV/mA |

| Settling Time to 0.1%          | V <sub>IVCOUT</sub> |                                      | _    | _    | 500  | ns    |

**Table 3.14. Voltage Reference Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Symbol                | Test Condition                                                                                                | Min    | Тур    | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unit   |

|-----------------------|---------------------------------------------------------------------------------------------------------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| nce                   | 1                                                                                                             |        |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| V <sub>REFFS</sub>    | -40 to +85 °C,<br>V <sub>DD</sub> = 1.8-3.6 V                                                                 | 1.62   | 1.65   | 1.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V      |

| TC <sub>REFFS</sub>   |                                                                                                               | _      | 50     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ppm/°C |

| t <sub>REFFS</sub>    |                                                                                                               | _      | _      | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | μs     |

| PSRR <sub>REFFS</sub> |                                                                                                               | _      | 400    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ppm/V  |