# 1.8V Nanopower Comparator with Internal 1.245V Reference

### **FEATURES**

- ♦ Second-source for MAX917

- ♦ Guaranteed to Operate Down to +1.8V

- ♦ Ultra-Low Supply Current: 750nA

- ♦ Internal 1.245V ±1.5% Reference

- ♦ Input Voltage Range Extends 200mV Outside-the-Rails

- ♦ No Phase Reversal for Overdriven Inputs

- ♦ Push-pull Output

- ♦ Crowbar-Current-Free Switching

- ◆ Internal Hysteresis for Clean Switching

- ♦ 5-pin SOT23 and 8-pin SOIC Packaging

# **APPLICATIONS**

2-Cell Battery Monitoring/Management Medical Instruments Threshold Detectors/Discriminators Sensing at Ground or Supply Line Ultra-Low-Power Systems Mobile Communications Telemetry and Remote Systems

### **DESCRIPTION**

The TSM917 nanopower analog comparator is electrically and form-factor identical to the MAX917 analog comparator. Ideally suited for all 2-cell battery-management/monitoring applications, this 5-pin SOT23 analog comparator guarantees +1.8V operation, draws very little supply current, and has a robust input stage that can tolerate input voltages beyond its power supply. The TSM917 draws 750nA of supply current and includes an on-board 1.245V ±1.5% reference.

The TSM917's push-pull output drivers were designed to drive 8mA loads from one supply rail to the other supply rail. The TSM917 is also available in an 8-pin SOIC package.

# TYPICAL APPLICATION CIRCUIT

+3.3V R4 6.2MΩ 5  $V_{CC}$ R1 R3 390kΩ 190kΩ 3 IN+ OUT O OUT R2 10MΩ R5 4 IN- (REF) 1 390kΩ TSM917EUK **REF** 1.245V

Nanopower 2.9V V<sub>CC</sub> Threshold Detector

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (Vcc to VEE)+6                              | ٧  |

|------------------------------------------------------------|----|

| Voltage Inputs (IN+, IN-, REF) (VEE - 0.3V) to (Vcc + 0.3V | /) |

| Output Voltage                                             |    |

| TSM917(V <sub>EE</sub> - 0.3V) to (V <sub>CC</sub> + 0.3V  | /) |

| Current Into Input Pins±20m/                               | Α  |

| Output Current±50m/                                        | Α  |

| Output Short-Circuit Duration10                            | S  |

| Continuous Power Dissipation ( $T_A = +70$ °C) |                |

|------------------------------------------------|----------------|

| 5-Pin SC70 (Derate 2.5mW/°C above +70°C        | c) 200mW       |

| 8-Pin SOIC (Derate 5.88mW/°C above +70°        | C) 471mW       |

| Operating Temperature Range                    | -40°C to +85°C |

| Junction Temperature                           | +150°C         |

| Storage Temperature Range6                     | 65°C to +150°C |

| Lead Temperature (soldering, 10s)              | +300°          |

Electrical and thermal stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to any absolute maximum rating conditions for extended periods may affect device reliability and lifetime.

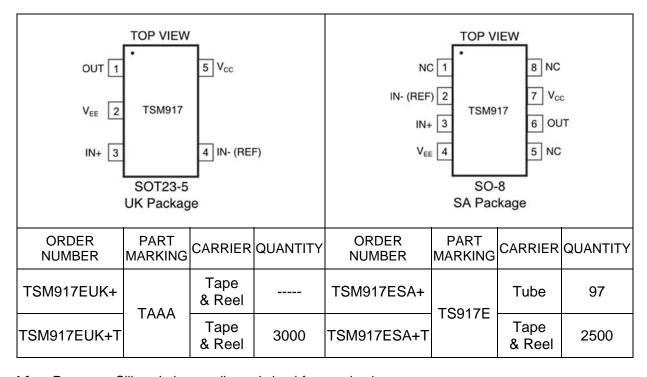

### PACKAGE/ORDERING INFORMATION

Lead-free Program: Silicon Labs supplies only lead-free packaging.

Consult Silicon Labs for products specified with wider operating temperature ranges.

Page 2 TSM917 Rev. 1.0

### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = +5V,  $V_{EE}$  = 0V,  $V_{IN+}$  =  $V_{REF}$ ,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C. See Note 1.

| PARAMETER                                 | SYMBOL                                       | CONDITIONS                                 | MIN                                                      | TYP                   | MAX   | UNITS             |        |

|-------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------------------------|-----------------------|-------|-------------------|--------|

| Supply Voltage Range                      | V <sub>cc</sub>                              | Inferred from the PSRR test                | T <sub>A</sub> = +25°C                                   | 1.8                   |       | 5.5               | V      |

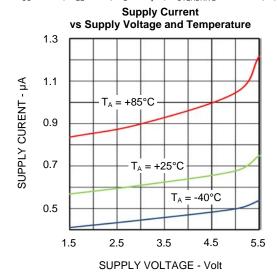

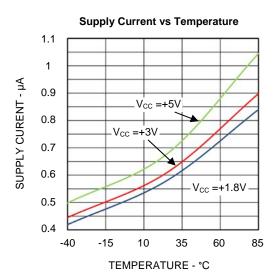

|                                           |                                              | V <sub>CC</sub> = 1.6V                     | $T_A = +25^{\circ}C$                                     |                       | 0.75  |                   |        |

| Supply Current                            | I <sub>CC</sub>                              | $V_{CC} = 5V$                              | $T_A = +25^{\circ}C$                                     |                       | 0.80  | 1.30              | μΑ     |

|                                           |                                              | $V_{CC} = 5V$ $T_A = T_{MIN}$ to $T_{MAX}$ |                                                          | V <sub>EE</sub> - 0.2 |       | 1.60              |        |

| IN+ Voltage Range                         | $V_{IN+}$                                    | Inferred from the output sw                | Inferred from the output swing test                      |                       |       | $V_{CC} + 0.2$    | V      |

| Input Offset Voltage                      | Vos                                          | (Note 2)                                   | $T_A = +25^{\circ}C$ $T_A = T_{MIN} \text{ to } T_{MAX}$ |                       | 1     | 5<br>10           | mV     |

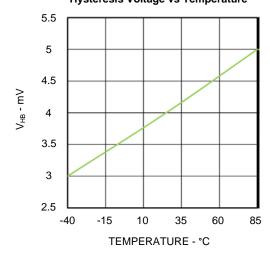

| Input-Referred Hysteresis                 | $V_{HB}$                                     | (Note 3)                                   |                                                          |                       | 4     |                   | mV     |

| Input Bias Current                        | I <sub>B</sub>                               | T <sub>A</sub> = +25°C                     |                                                          |                       | 0.15  | 1                 | nA     |

| -                                         |                                              | $T_A = T_{MIN}$ to $T_{MAX}$               |                                                          |                       |       | 2                 |        |

| Power-Supply Rejection Ratio              | PSRR                                         | $V_{CC} = 1.8V \text{ to } 5.5V$           | 1-                                                       |                       | 0.1   | 1                 | mV/V   |

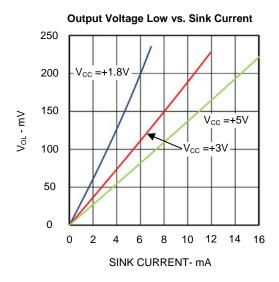

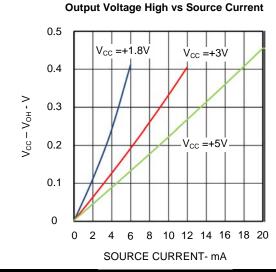

|                                           |                                              | $V_{CC} = 5V$ ,                            | $T_A = +25^{\circ}C$                                     |                       | 190   | 400               |        |

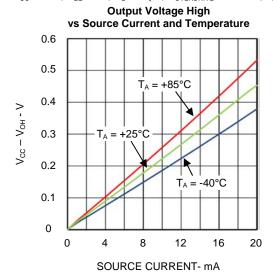

| Output-Voltage Swing High                 | V <sub>CC</sub> - V <sub>OH</sub>            | I <sub>SOURCE</sub> = 8mA                  | $T_A = T_{MIN}$ to $T_{MAX}$                             |                       |       | 500               | mV     |

| Carpar voltage Ownig riigii               | 00 5                                         | $V_{CC} = 1.8V$ ,                          | $T_A = +25^{\circ}C$                                     |                       | 55    | 200               |        |

|                                           |                                              | I <sub>SOURCE</sub> = 1mA                  | $T_A = T_{MIN}$ to $T_{MAX}$                             |                       | 400   | 300               |        |

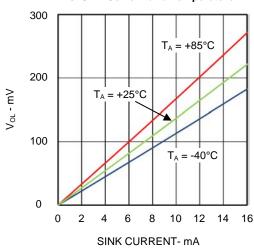

| Output-Voltage Swing Low                  |                                              | $V_{CC} = 5V$ , $I_{SINK} = 8mA$           | $T_A = +25^{\circ}C$                                     |                       | 190   | 400               |        |

|                                           | $V_{OL}$                                     |                                            | $T_A = T_{MIN}$ to $T_{MAX}$<br>$T_A = +25$ °C           |                       | 55    | 500<br>200        | mV     |

|                                           |                                              | $V_{CC} = 1.8V$ ,<br>$I_{SINK} = 1mA$      |                                                          |                       | 55    | 300               |        |

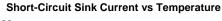

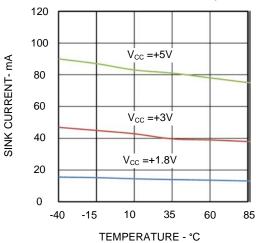

|                                           |                                              |                                            | $T_A = T_{MIN}$ to $T_{MAX}$<br>$V_{CC} = 5V$            |                       | 95    | 300               | mA     |

|                                           | I <sub>sc</sub>                              | Sourcing, Vo = VEE                         | $V_{CC} = 3V$ $V_{CC} = 1.8V$                            |                       | 8     |                   |        |

| Output Short-Circuit Current              |                                              |                                            | $V_{CC} = 1.6V$ $V_{CC} = 5V$                            |                       | 98    |                   |        |

|                                           |                                              | Sinking, $V_0 = V_{CC}$                    | $V_{CC} = 1.8V$                                          |                       | 10    |                   |        |

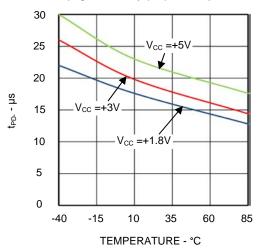

| High-to-Low Propagation Delay             |                                              | V <sub>CC</sub> = 1.8V                     | VCC = 1.0 V                                              |                       | 17    |                   |        |

| (Note 4)                                  | t <sub>PD</sub> -                            | $V_{CC} = 1.6V$ $V_{CC} = 5V$              |                                                          |                       | 22    |                   | μs     |

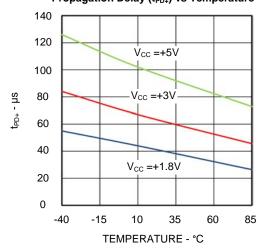

| Low-to-High Propagation Delay             |                                              | $V_{CC} = 1.8$                             |                                                          |                       | 30    |                   |        |

| (Note 4)                                  | t <sub>PD+</sub>                             |                                            | $V_{CC} = 5V$                                            |                       | 95    |                   | μs     |

| Rise Time                                 | t <sub>RISE</sub>                            | C <sub>L</sub> = 15pF                      |                                                          |                       | 6     |                   | μs     |

| Fall Time                                 | t <sub>FALL</sub>                            | C <sub>L</sub> = 15pF                      |                                                          |                       | 4     |                   | μs     |

| Power-Up Time                             | t <sub>ON</sub>                              |                                            |                                                          |                       | 1.2   |                   | ms     |

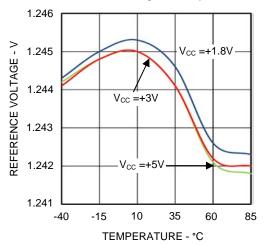

| Reference Voltage                         | $V_{REF}$                                    | $T_A = +25^{\circ}C$                       |                                                          | 1.227                 | 1.245 | 1.263             | - V    |

| 9                                         | V REF                                        | $T_A = T_{MIN}$ to $T_{MAX}$               |                                                          | 1.200                 |       | 1.290             |        |

| Reference Voltage Temperature Coefficient | TCV <sub>REF</sub>                           |                                            |                                                          |                       | 95    |                   | ppm/°C |

| Reference Output Voltage                  |                                              | BW = 10Hz to 100kHz                        |                                                          | 600                   |       | \/                |        |

| Noise                                     | e <sub>n</sub>                               | BW = 10Hz to 100kHz, CRE                   |                                                          | 215                   |       | μV <sub>RMS</sub> |        |

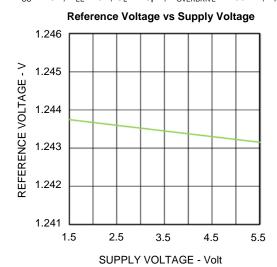

| Reference Line Regulation                 | $\Delta V_{\text{REF}}/\Delta V_{\text{CC}}$ | $V_{CC} = 1.8V \text{ to } 5.5V$           |                                                          |                       | 0.1   |                   | mV/V   |

| Reference Load Regulation                 | $\Delta V_{REF} / \Delta I_{OUT}$            | $\Delta I_{OUT} = 10nA$                    |                                                          | ±0.2                  |       | mV/nA             |        |

- Note 1: All specifications are 100% tested at  $T_A = +25$ °C. Specification limits over temperature ( $T_A = T_{MIN}$  to  $T_{MAX}$ ) are guaranteed by design, not production tested.

- Note 2: V<sub>OS</sub> is defined as the center of the hysteresis band at the input.

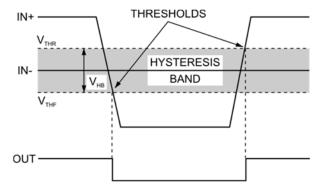

- Note 3: The hysteresis-related trip points are defined by the edges of the hysteresis band, measured with respect to the center of the hysteresis band (i.e., Vos) (See Figure 2).

- Note 4: Specified with an input overdrive (V<sub>OVERDRIVE</sub>) of 100mV, and load capacitance of C<sub>L</sub> = 15pF. V<sub>OVERDRIVE</sub> is defined above and beyond the offset voltage and hysteresis of the comparator input. For the TSM917, reference voltage error should also be added.

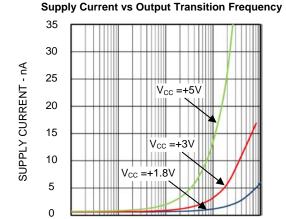

$V_{\text{CC}} = +5 \text{V}; \ V_{\text{EE}} = 0 \text{V}; \ C_{\text{L}} = 15 \text{pF}; \ V_{\text{OVERDRIVE}} = 100 \text{mV}; \ T_{\text{A}} = +25 ^{\circ}\text{C}, \ unless \ otherwise \ noted.$

10

100

**OUTPUT TRANSITION FREQUENCY - Hz**

1k

10k

Page 4 TSM917 Rev. 1.0

$V_{\text{CC}} = +5 \text{V}; \ V_{\text{EE}} = 0 \text{V}; \ C_{\text{L}} = 15 \text{pF}; \ V_{\text{OVERDRIVE}} = 100 \text{mV}; \ T_{\text{A}} = +25 ^{\circ}\text{C}, \ unless \ otherwise \ noted.$

#### **Short-Circuit Source Current vs Temperature**

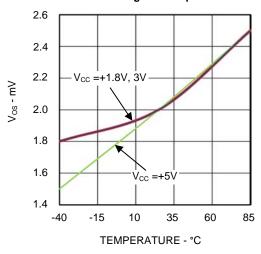

#### Offset Voltage vs Temperature

#### Hysteresis Voltage vs Temperature

#### Reference Voltage vs Temperature

$V_{CC} = +5V; \ V_{EE} = 0V; \ C_L = 15pF; \ V_{OVERDRIVE} = 100mV; \ T_A = +25^{\circ}C, \ unless \ otherwise \ noted.$

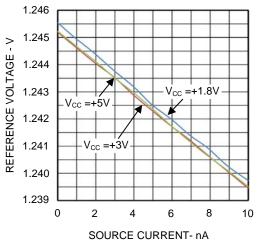

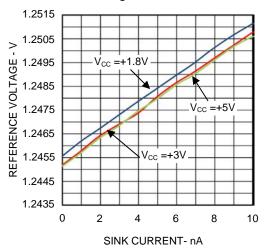

### Reference Voltage vs Reference Source Current

#### Reference Voltage vs Reference Sink Current

#### Propagation Delay (t<sub>PD-</sub>) vs Temperature

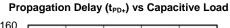

### Propagation Delay (t<sub>PD+</sub>) vs Temperature

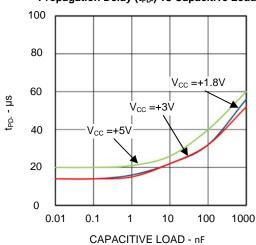

#### Propagation Delay (t<sub>PD-</sub>) vs Capacitive Load

Page 6 TSM917 Rev. 1.0

# **TSM917**

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{CC}$  = +5V;  $V_{EE}$  = 0V;  $C_L$  = 15pF;  $V_{OVERDRIVE}$  = 100mV;  $T_A$  = +25°C, unless otherwise noted.

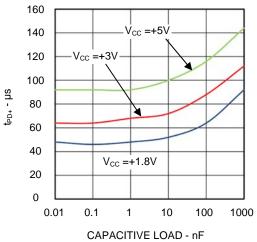

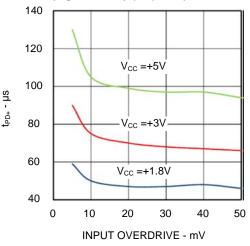

#### Propagation Delay (t<sub>PD-</sub>) vs Input Overdrive

#### Propagation Delay (t<sub>PD+</sub>) vs Input Overdrive

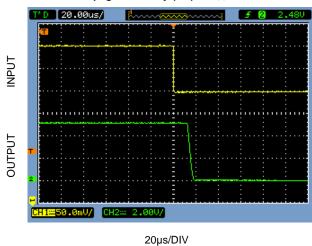

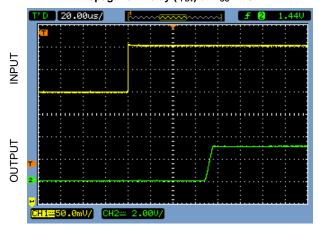

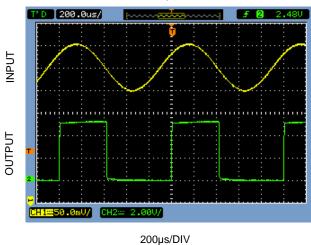

Propagation Delay ( $t_{PD}$ ) at  $V_{CC} = +5V$

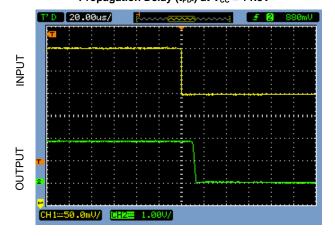

Propagation Delay  $(t_{PD+})$  at  $V_{CC} = +5V$

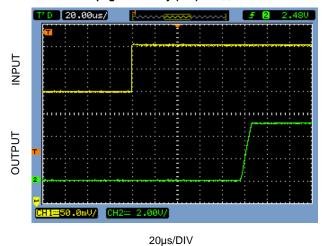

Propagation Delay ( $t_{PD}$ ) at  $V_{CC} = +3V$

20µs/DIV

$V_{CC}$  = +5V;  $V_{EE}$  = 0V;  $C_L$  = 15pF;  $V_{OVERDRIVE}$  = 100mV;  $T_A$  = +25°C, unless otherwise noted.

### Propagation Delay $(t_{PD+})$ at $V_{CC} = +3V$

20µs/DIV

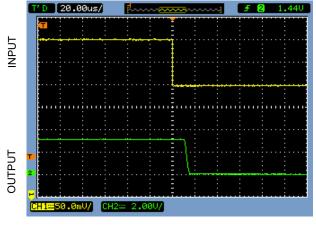

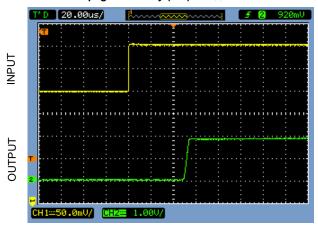

#### Propagation Delay ( $t_{PD}$ ) at $V_{CC} = +1.8V$

20µs/DIV

#### Propagation Delay ( $t_{PD+}$ ) at $V_{CC} = +1.8V$

20µs/DIV

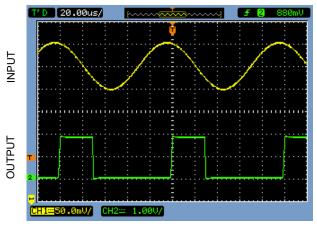

10kHz Transient Response at V<sub>CC</sub> = +1.8V

20µs/DIV

#### 1kHz Transient Response at V<sub>cc</sub> = +5V

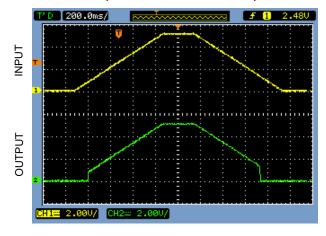

Power-Up/Power-Down Transient Response

0.2s/DIV

Page 8 TSM917 Rev. 1.0

# **PIN FUNCTIONS**

| TSM            | 1917          |      |                                          |

|----------------|---------------|------|------------------------------------------|

| 5-pin<br>SOT23 | 8-pin<br>SOIC | NAME | FUNCTION                                 |

| 1              | 6             | OUT  | Comparator Output                        |

| 2              | 4             | VEE  | Negative Supply Voltage                  |

| 3              | 3             | IN+  | Comparator Noninverting Input            |

| 4              | 2             | REF  | 1.245V Reference Output and              |

| 4              |               | KEF  | Comparator Inverting Input               |

| 5              | 7             | VCC  | Positive Supply Voltage                  |

| _              | _             | IN-  | Comparator Inverting Input               |

| _              | 1, 5, 8       | NC   | No Connection. Not internally connected. |

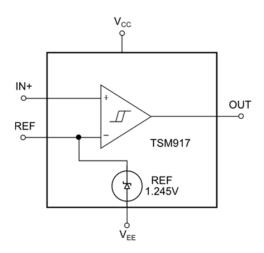

### **BLOCK DIAGRAMS**

# **DESCRIPTION OF OPERATION**

Guaranteed to operate from +1.8V supplies, the TSM917 analog comparator only draws 750nA supply current, features a robust input stage that can tolerate input voltages 200mV beyond the power supply rails, and includes an on-board +1.245V ±1.5% voltage reference. To insure clean output switching behavior, the TSM917 features 4mV internal hysteresis. The TSM917's push-pull output drivers were designed to minimize supply-current surges while driving ±8mA loads with rail-to-rail output swings.

#### **Input Stage Circuitry**

The robust design of the analog comparator's input stage can accommodate any differential input voltage from  $V_{\text{EE}}$  - 0.2V to  $V_{\text{CC}}$  + 0.2V. Input bias currents are typically ±0.15nA so long as the applied input voltage remains between the supply rails. ESD protection diodes - connected internally to the supply rails - protect comparator inputs against overvoltage conditions. However, if the applied input voltage exceeds either or both supply rails, an increase in input current can occur when these ESD protection diodes start to conduct.

#### **Output Stage Circuitry**

Many conventional analog comparators can draw orders of magnitude higher supply current when switching. Because of this behavior, additional power supply bypass capacitance may be required to provide additional charge storage during switching. The design of the TSM917's rail-to-rail output stage implements a technique that virtually eliminates supply-current surges when output transitions occur. As shown on Page 4 of the Typical Operating Characteristics, the supply-current change as a function of output transition frequency exhibited by this analog comparator family is very small. Material benefits of this attribute to batterypower applications are the increase in operating time and in reducing the size of power-supply filter capacitors.

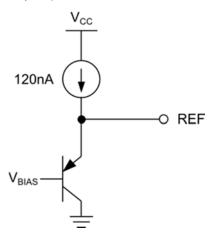

#### TSM917's Internal +1.245V VREF

The TSM917's internal +1.245V voltage reference exhibits a typical temperature coefficient of 95ppm/°C over the full -40°C to +85°C temperature range. An equivalent circuit for the reference section is illustrated in Figure 1. Since the output impedance of the voltage reference is typically  $200k\Omega$ , its output

can be bypassed with a low-leakage capacitor and is stable for any capacitive load. An external buffer –

**Figure 1**: TSM917's Internal V<sub>REF</sub> Output Equivalent Circuit

such as the TS1001 – can be used to buffer the voltage reference output for higher output current drive or to reduce reference output impedance.

### **APPLICATIONS INFORMATION**

#### Low-Voltage, Low-Power Operation

Because it was designed specifically for any lowpower, battery-operated application, the TSM917 analog comparator is an excellent choice. Under nominal conditions, approximate operating times for this analog comparator is illustrated in Table 1 for a number of battery types and their corresponding charge capacities.

#### **Internal Hysteresis**

As a result of circuit noise or unintended parasitic feedback, many analog comparators often break into

oscillation within their linear region of operation especially when the applied differential input voltage approaches 0V (zero volt). Externally-introduced hysteresis is a well-established technique to stabilizing analog comparator behavior and requires external components. As shown in Figure 2, adding comparator hysteresis creates two trip points: V<sub>THR</sub> (for the rising input voltage) and V<sub>THF</sub> (for the falling input voltage). The hysteresis band (V<sub>HB</sub>) is defined as the voltage difference between the two trip points. When a comparator's input voltages are equal, hysteresis effectively forces one comparator input to

Table 1: Battery Applications using the TSM917

| BATTERY TYPE                       | RECHARGEABLE | V <sub>FRESH</sub> (V) | V <sub>END-OF-LIFE</sub> (V) | CAPACITY, AA<br>SIZE (mA-h) | TSM917<br>OPERATING TIME<br>(hrs) |

|------------------------------------|--------------|------------------------|------------------------------|-----------------------------|-----------------------------------|

| Alkaline (2 Cells)                 | No           | 3.0                    | 1.8                          | 2000                        | 2.5 x 10 <sup>6</sup>             |

| Nickel-Cadmium (2 Cells)           | Yes          | 2.4                    | 1.8                          | 750                         | 937,500                           |

| Lithium-Ion (1 Cell)               | Yes          | 3.5                    | 2.7                          | 1000                        | 1.25 x 10 <sup>6</sup>            |

| Nickel-Metal- Hydride (2<br>Cells) | Yes          | 2.4                    | 1.8                          | 1000                        | 1.25 x 10 <sup>6</sup>            |

Page 10 TSM917 Rev. 1.0

move quickly past the other input, moving the input out of the region where oscillation occurs. Figure 2 illustrates the case in which an IN- input is a fixed voltage and an IN+ is varied. If the input signals were reversed, the figure would be the same with an inverted output. To save cost and external pcb area, an internal 4mV hysteresis circuit was added to the TSM917.

Figure 2: TSM917's Threshold Hysteresis Band

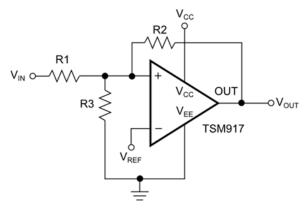

#### Adding Hysteresis to the TSM917

The TSM917 exhibits an internal hysteresis band  $(V_{HB})$  of 4mV. Additional hysteresis can be generated with three external resistors using positive feedbackas shown in Figure 3. Unfortunately, this method also reduces the hysteresis response time. The design procedure below can be used to calculate resistor values.

**Figure 3**: Using Three Resistors Introduces Additional Hysteresis in the TSM917.

Setting R2. As the leakage current at the IN pin is under 2nA, the current through R2 should be at least 0.2µA to minimize offset voltage errors caused by the input leakage current. The current through R2 at the trip point is (VREF - VOUT)/R2.

In solving for R2, there are two formulas – one each for the two possible output states:

$$R2 = V_{REF}/I_{R2}$$

or

$$R2 = (V_{CC} - V_{REF})/I_{R2}$$

From the results of the two formulae, the smaller of the two resulting resistor values is chosen. For example, when using the TSM917 (V<sub>REF</sub> = 1.245V) at a V<sub>CC</sub> = 3.3V and if I<sub>R2</sub> = 0.2µA is chosen, then the formulae above produce two resistor values: 6.23M $\Omega$  and 10.24M $\Omega$  - the 6.2M $\Omega$  standard value for R2 is selected.

- 2) Next, the desired hysteresis band (V<sub>HYSB</sub>) is set. In this example, V<sub>HYSB</sub> is set to 100mV.

- Resistor R1 is calculated according to the following equation:

$$R1 = R2 \times (V_{HB}/V_{CC})$$

and substituting the values selected in 1) and 2) above yields:

$$R1 = 6.2M\Omega \times (100mV/3.3V) = 187.88k\Omega$$

The  $187k\Omega$  standard value for R1 is selected.

- 4) The trip point for V<sub>IN</sub> rising (V<sub>THR</sub>) is chosen such that V<sub>THR</sub> > V<sub>REF</sub> x (R1 + R2)/R2 (where V<sub>THF</sub> is the trip point for V<sub>IN</sub> falling). This is the threshold voltage at which the comparator switches its output from low to high as V<sub>IN</sub> rises above the trip point. In this example, V<sub>THR</sub> is set to 3V.

- 5) With the V<sub>THR</sub> from Step 4 above, resistor R3 is then computed as follows:

$$R3 = 1/[V_{THR}/(V_{REF} \times R1) - (1/R1) - (1/R2)]$$

R3 =

$$1/[3V/(1.245V \times 187kΩ) - (1/187kΩ)$$

-  $(1/6.2MΩ)] = 135.56kΩ$

In this example, a  $137k\Omega$ , 1% standard value resistor is selected for R3.

# **TSM917**

6) The trip voltages and hysteresis band should be verified as follows:

For  $V_{IN}$  rising:  $V_{THR} = V_{REF} \times R1 \times [(1/R1) + (1/R2) + (1/R3)] = 3V$

For  $V_{IN}$  falling:  $V_{THF} = V_{THR} - (R1 \times V_{CC}/R2) = 2.9V$

and Hysteresis Band = V<sub>THR</sub> - V<sub>THF</sub> = 100mV

### PC Board Layout and Power-Supply Bypassing

While power-supply bypass capacitors are not typically required, it is always good engineering practice to use 0.1uF bypass capacitors close to the device's power supply pins when the power supply impedance is high, the power supply leads are long, or there is excessive noise on the power supply traces. To reduce stray capacitance, it is also good engineering practice to make signal trace lengths as short as possible. Also recommended are a ground plane and surface mount resistors and capacitors.

Page 12 TSM917 Rev. 1.0

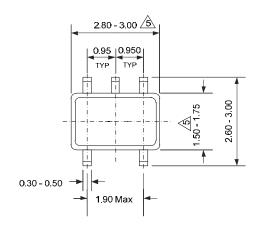

# PACKAGE OUTLINE DRAWING

# 5-Pin SOT23 Package Outline Drawing

(N.B., Drawings are not to scale)

#### NOTES:

- 1. Dimensions and tolerances are as per ANSI Y14.5M, 1982.

- 2. Package surface to be matte finish VDI 11~13.

- 3. Die is facing up mold and facing down for trim/form, ie, reverse trim/form.

- 4. The foot length measuring is based on the gauge plane method.

5. Dimensions are exclusive of mold flash and gate burr.

- 6. Dimensions are exclusive of solder plating.

- 7. All dimensions are in mm.

- 8. This part is compliant with EIAJ spec. and JEDEC MO-178 AA

- Lead span/stand off height/coplanarity are considered as special characteristic.

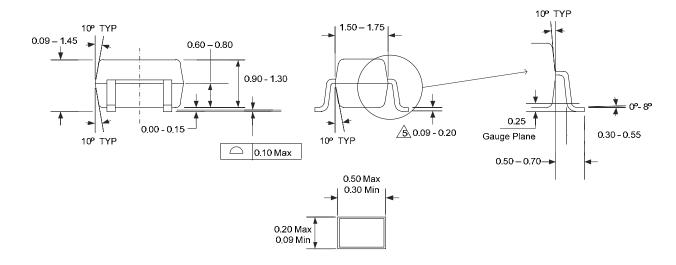

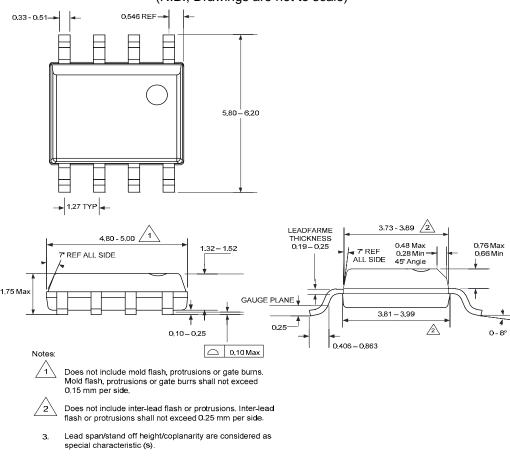

### PACKAGE OUTLINE DRAWING

### 8-Pin SOIC Package Outline Drawing

(N.B., Drawings are not to scale)

- Controlling dimensions are in mm.

- 5. This part is compliant with JEDEC specification MS-012

- Lead span/stand off height/coplanarity are considered as Special characteristic.

#### **Patent Notice**

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analog-intensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### Trademark Information

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analog Comparators category:

Click to view products by Silicon Labs manufacturer:

Other Similar products are found below:

SC2903VDR2G LM2901SNG LM339SNG UPC272G2-A 55122 5962-8757203IA NTE911 5962-8751601DA LM339EDR2G NTE922 LM2903M/TR MAX49140AXK/V+T LM2903F-E2 MCP6544-EP LM2901EDR2G TS391SN2T1G LM111JG LM139ADT LM239APT HMC675LC3CTR MAX9024AUD+ LT6700HVIS6-2#TRMPBF ADCMP394ARZ-RL7 LM339AMX LTC1440IMS8#PBF AZV331KSTR-G1 LTC1841IS8#PBF LTC1440CN8#PBF LTC1542CS8#PBF LTC1445CS#PBF TL331VSN4T3G LT6700IDCB-1#TRMPBF LTC1042CN8#PBF LTC1540CMS8#PBF ADCMP607BCPZ-R7 LT1720CDD#PBF LTC1040CN#PBF LT6700MPDCB-1#TRMPBF LT6700IDCB-3#TRMPBF LTC1440IS8#PBF S-89431ACNC-HBVTFG NTE1718 NTE943 NTE943M NTE943SM TA75S393F,LF(T ALD2301APAL ALD2302APAL TSX3704IYPT AD790JNZ