Ag6400 POE+ Power-Sourcing-Equipment Module

# 1. Features

- Compliant with IEEE802.3at Type 1 & Type 2

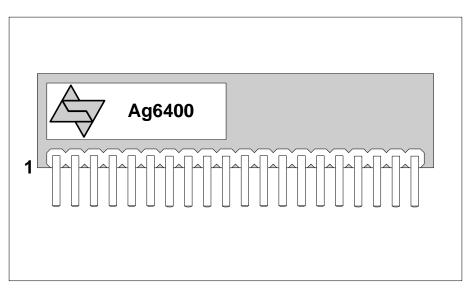

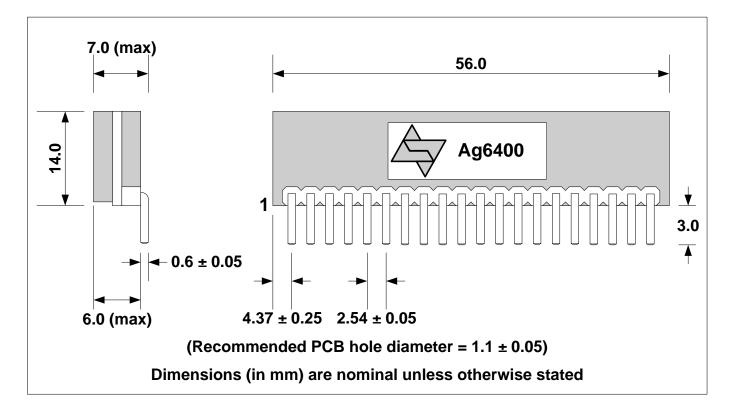

- Small SIL package size 56mm (L) x 14mm (H)

- Low cost

- Four independent PSE outputs, capable of up to 30W each

- Minimal (low cost) external components required

- Programmable current limits

- > Per Port Current/Voltage monitoring

# 2. Description

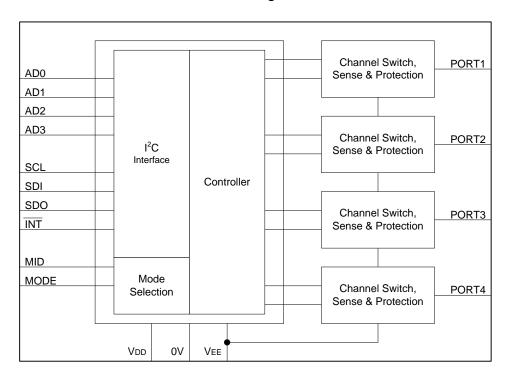

The Ag6400 is a quad Power Sourcing Equipment (PSE) module designed for use in IEEE802.3at Type 1 and Type 2 Power over Ethernet (PoE) applications.

Capable of providing up to 30W per port, Ag6400 is aimed at applications requiring PSE functionality such as IP switches, routers and hubs, CCTV DVR, home networking and industrial ethernet.

Ag6400 is a self-contained module, requiring just a few external components to provide a great deal of control and feedback over each Powered Device (PD) that is connected to the PSE.

# **Table of Contents**

| 1. Features                                                             |    |

|-------------------------------------------------------------------------|----|

| 2. Description                                                          |    |

| Table of Contents                                                       |    |

| Table of Figures                                                        |    |

| 3. Ag6400 Product Selector                                              | 4  |

| 4. Pin Description                                                      | 5  |

| 5. Functional Description                                               |    |

| 5.1 Power Supplies                                                      |    |

| 5.2 Output Ports                                                        | 6  |

| 5.3 Selection Inputs                                                    |    |

| 5.3.1 MID                                                               |    |

| 5.3.2 MODE                                                              |    |

| 5.4 I <sup>2</sup> C Interface                                          |    |

| 5.4.1 I <sup>2</sup> C Timing                                           |    |

| 5.4.2 I <sup>2</sup> C Module Address                                   |    |

| 6. Signature and Classification                                         |    |

| 6.1 Signature Detection                                                 |    |

| 6.2 Classification                                                      |    |

| 6.3 Current Cutoff and Limits                                           |    |

| 7. Software Mode                                                        |    |

| 7.1 Register Map                                                        |    |

| 7.1.1 Interrupt Registers                                               |    |

| 7.1.2 Event Registers                                                   |    |

| 7.1.3 Status Registers                                                  |    |

| 7.1.4 Configuration Registers                                           |    |

| 7.1.5 Action Registers                                                  |    |

| 7.1.6 Timing Limit Registers                                            |    |

| 7.1.7 Measurement Registers                                             |    |

| 7.1.8 Power Management Registers                                        |    |

| 7.2 System Software                                                     |    |

| 7.2.1 Initialisation                                                    |    |

| 7.2.1 Detection – Signature and Classification                          |    |

| 7.2.2 Detection – Signature and Classification<br>7.2.3 PD Disconnected |    |

|                                                                         |    |

| 8. Protection                                                           |    |

| 9. Electrical Characteristics                                           |    |

| 9.1 Absolute Maximum Ratings <sup>1</sup>                               |    |

| 9.2 Recommended Operating Conditions                                    |    |

| 9.3 Electrical Characteristics                                          |    |

| 9.4 Timing Characteristics                                              |    |

| 10. Package                                                             | 40 |

# **Table of Figures**

| Figure 1: Block Diagram                                    | 4  |

|------------------------------------------------------------|----|

| Figure 2: Ag6400 Package Format                            |    |

| Figure 3: Power Supply Connections                         |    |

| Figure 4: Typical Connection Diagram                       | 7  |

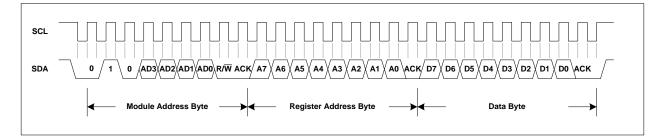

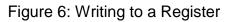

| Figure 5: I <sup>2</sup> C Interface Timing                |    |

| Figure 6: Writing to a Register                            | 8  |

| Figure 7: Read a Register                                  | 9  |

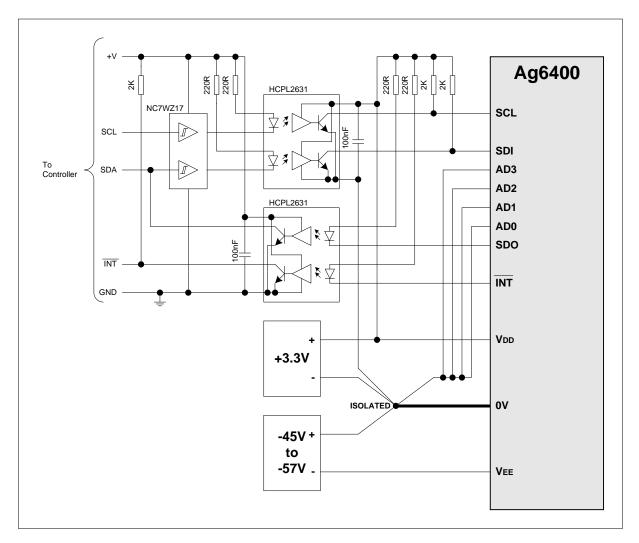

| Figure 8: Isolated I <sup>2</sup> C bus                    | 9  |

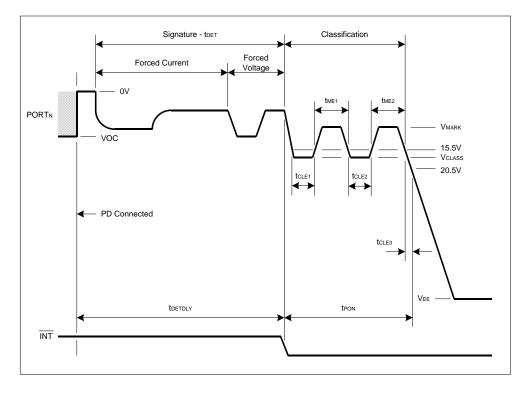

| Figure 9: Signature, Class and Turn-On Timing - Type 2 PD  | 10 |

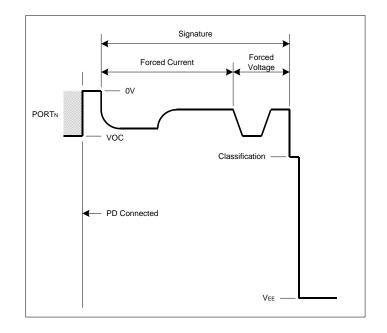

| Figure 10: Signature, Class and Turn-On Timing - Type 1 PD | 11 |

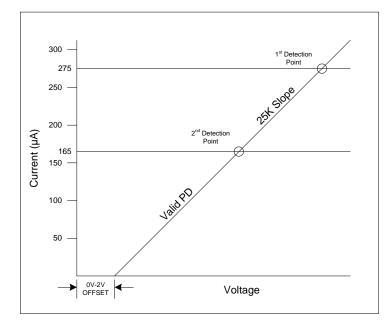

| Figure 11: Signature Slope                                 | 12 |

|                                                            |    |

Ag6400

# 3. Ag6400 Product Selector

| Part Numbert | Marking | Variant / Date<br>code * |

|--------------|---------|--------------------------|

| Ag6400-S     | Ag6400  | ww/yy                    |

ww/yy represents date code on manufacture. ww - Week yy-Year

† The Ag6400 fully meets the requirements of the RoHS directive 2002/95/EC on the restriction of hazardous substances in electronic equipment.

Table 1: Ordering Information

#### Figure 1: Block Diagram

# Figure 2: Ag6400 Package Format

# 4. Pin Description

| Pin # | Name            | Description                                                                                                                                                                     |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>DD</sub> | <b>Logic Power Supply.</b> This pin connects to an isolated +3.3V power supply; relative to the 0V.                                                                             |

| 2     | 0V              | <b>0V.</b> This pin is the return path for the isolated $V_{DD}$ and $V_{EE}$ power                                                                                             |

| 3     |                 | supplies, and the PORT1 - 4 outputs.                                                                                                                                            |

| 4     | N               | Main Power Supply. This pin connects to an isolated -45V to -                                                                                                                   |

| 5     | V <sub>EE</sub> | 57V supply; relative to the 0V.                                                                                                                                                 |

| 6     | MODE            | <b>Mode Select Input.</b> A Logic 1 on this pin will set the Ag6400 in Hardware mode. A Logic 0 on this pin will set the Ag6400 in Software mode. Internally pulled down to 0V. |

| 7     | MID             | <b>Midspan Mode Input.</b> A Logic 1 on the pin will set the Ag6400 to act as a PSE Midspan. Internally pulled down to 0V.                                                      |

| 8     | /INT            | <b>Interrupt Output.</b> This open drain output will pull low when one of the programmed interrupt events has occurred.                                                         |

| 9     | SDO             | <b>Serial Data Output.</b> This open drain output is used in conjunction with the SDI and SCL pins to for the I <sup>2</sup> C bus.                                             |

| 10    | SCL             | <b>Serial Clock Input.</b> This high impedance input pin connects to the I <sup>2</sup> C bus clock.                                                                            |

| 11    | SDI             | <b>Serial Data Input.</b> This high impedance input pin is used in conjunction with the SDO and SCL pins to for the I <sup>2</sup> C bus.                                       |

| 12    | AD3             | Address Input Bit 3. The input is used in conjunction with AD0, AD1 and AD2 to set the $I^2C$ address of the Ag6400.                                                            |

| 13    | AD2             | Address Input Bit 2. The input is used in conjunction with AD0, AD1 and AD3 to set the $I^2C$ address of the Ag6400.                                                            |

| 14    | AD1             | Address Input Bit 1. The input is used in conjunction with AD0, AD2 and AD3 to set the $I^2C$ address of the Ag6400.                                                            |

| 15    | AD0             | Address Input Bit 0. The input is used in conjunction with AD1, AD2 and AD3 to set the $I^2C$ address of the Ag6400.                                                            |

| 16    | NC              | No Connection.                                                                                                                                                                  |

| 17    | PORT1           | <b>PORT1 Output.</b> This output pin monitors the line and supplies power to valid powered device.                                                                              |

| 18    | PORT2           | <b>PORT2 Output.</b> This output pin monitors the line and supplies power to valid powered device.                                                                              |

| 19    | PORT3           | <b>PORT3 Output.</b> This output pin monitors the line and supplies power to valid powered device.                                                                              |

| 20    | PORT4           | <b>PORT4 Output.</b> This output pin monitors the line and supplies power to valid powered device.                                                                              |

# 5. Functional Description

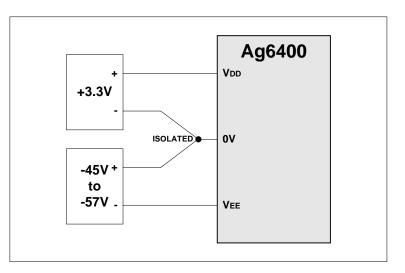

### 5.1 Power Supplies

The Ag6400 requires two power supplies  $V_{DD}$  and  $V_{EE}$ , it is very important that the  $V_{DD}$  supply is powered up before the  $V_{EE}$  supply. Failure to do so may result in damage to the controller chip on the module.

To conform to the IEEE802.3at specification, both  $V_{DD}$  and  $V_{EE}$  must be isolated from ground, as shown in Figure 3.

Figure 3: Power Supply Connections

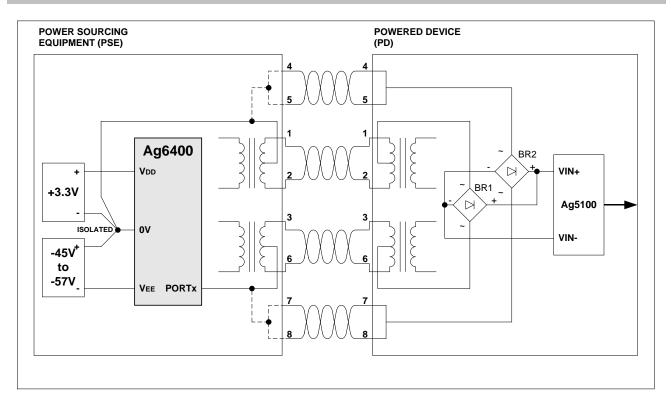

### 5.2 Output Ports

Each output port can be connected directly to the centre-tap of an IEEE802.3at compliant data transformer or to the spare pair connection for 10/100BASE-T applications, as shown in Figure 4. For 1000BASE-T (Gigabit) Ethernet applications all four cable pairs require magnetics, this is explained in more detail in application note "ANX-1000BASE-T-CONNECTIONS".

It is important that the (return) star point is kept as close to the 0V pins (on the module) as possible.

Figure 4: Typical Connection Diagram

### **5.3 Selection Inputs**

The Ag6400 has two mode selection input pins – "MID" and "MODE".

#### 5.3.1 MID

To use the Ag6400 as a Midspan device, the MID pin must be set to a Logic 1 during power up (setting Midspan mode). This mode continues to support the 2-event classification and includes a two second back-off timer between port detection cycles. For Endpoint devices the MID pin must be set to Logic 0.

#### 5.3.2 MODE

When the Ag6400 is powered up with Logic 1 applied to the MODE pin, the Ag6400 will be set in Hardware mode (this is the easiest mode to use).

In Hardware mode the Ag6400 does not require any user intervention. It will automatically detect and classify ports, apply power after successful detections, and remove power from disconnected ports. For most applications it is recommended to use Hardware Mode.

The Cutoff Current ( $I_{CUT}$ ) and Current Limit ( $I_{LIM}$ ) parameters are set in accordance with the detected classification, see Table 2.

|                  | Class 1 |     | Class 2 |     | Class 3 | or 0 | Class 4 (two event) |     |  |

|------------------|---------|-----|---------|-----|---------|------|---------------------|-----|--|

|                  | current | hex | current | hex | current | hex  | current             | hex |  |

| I <sub>CUT</sub> | 112mA   | C6h | 206mA   | CBh | 375mA   | D4h  | 638mA               | E2h |  |

| I <sub>LIM</sub> | 425mA   | 80h | 425mA   | 80h | 425mA   | 80h  | 850mA               | C0h |  |

Table 2: Hardware Mode Current Settings

When the Ag6400 is powered up with Logic 0 applied to the MODE pin, the Ag6400 will be set in Software mode and is fully controlled using the  $I^2C$  interface. The Ag6400 should be set in this mode if the Data Link Layer classification is required.

## 5.4 I<sup>2</sup>C Interface

The Ag6400 is a slave device, with four pins available to connect to an  $I^2C$  interface – SDI, SDO, SCL and /INT. The module can communicate with a master device using the  $I^2C$  bus standard. To implement a standard bidirectional SDA bus, the SDO and SDI must be connected together. These pins have been separated to make it easier to connect them to opto-couplers to implement an isolation barrier, as shown in Figure 8.

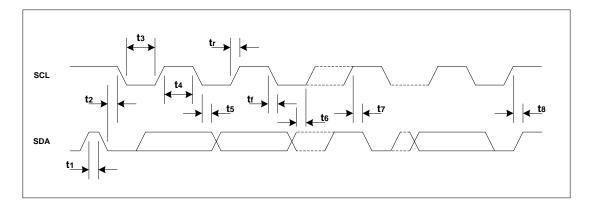

### 5.4.1 I<sup>2</sup>C Timing

The following Figures show the timing relationship between the SCL and SDA signals.

Figure 5: I<sup>2</sup>C Interface Timing

Figure 6 shows how to write to a register.

Figure 7 shows how to read a register.

Figure 7: Read a Register

The Ag6400 is non-isolated, so to fully conform to the IEEE specification the  $V_{DD}$  and  $V_{EE}$  supplies must be isolated from chassis ground. If the controller is powered by a ground referenced power supply, then the I<sup>2</sup>C bus must be isolated. Although the output ports (on one or more Ag6400's) do not have to be isolated from each other. Figure 8 shows how the I<sup>2</sup>C bus can be implemented by using opto-isolators to form an isolation barrier, where the controller GND is isolated from the Ag6400 0V.

Figure 8: Isolated I<sup>2</sup>C bus

### 5.4.2 I<sup>2</sup>C Module Address

The module address is programmed by using the AD0 to AD3 pins, allowing several Ag6400 modules to be connected to the  $I^2C$  bus; Table 3 shows the address format.

| Module Address | MSB |   |   |     |     |     |     | LSB |

|----------------|-----|---|---|-----|-----|-----|-----|-----|

|                | 0   | 1 | 0 | AD3 | AD2 | AD1 | AD0 | R/W |

#### Table 3: Module Address

In the example shown in Figure 8, AD0 to AD3 are all connected to 0V (Logic 0). Therefore to write to the module the base address is 40h "01000000" (even), to read from the module the address is 41h, base address + 1 (odd). Each ADn input has an internal  $50k\Omega$  pull-up resistor

The interrupt pin (/INT) is only updated between I<sup>2</sup>C trans-actions and the SDA and SCL line must be set to Logic 1 when the bus is not in use.

# 6. Signature and Classification

The Ag6400 will automatically perform the Signature and Classification in Hardware or Software mode (when enabled). Figure 9 shows the full timing sequence for a Type 2 Powered Device (PD).

Figure 9: Signature, Class and Turn-On Timing - Type 2 PD The Ag6400 has a different response when connected to a Type 1 PD, see Figure 10 (Hardware mode).

© Silver Telecom 2018

Figure 10: Signature, Class and Turn-On Timing - Type 1 PD

The IEEE802.3at separates the power handling into two basic categories "Type 1" and "Type 2". In simple terms Type 1 handles power requirements up to 15.4W and is comparable with the IEEE802.3af specification. Type 2 handles the power levels above this, which is commonly referred to as POE+.

### 6.1 Signature Detection

To ensure that the Ag6400 does not apply power to a non PoE enabled device the output port first checks for a valid PoE signature. The PD should present  $25k\Omega$  (23.75k $\Omega$  to 26.25k $\Omega$ ) Signature resistance, but this usually has a dc offset from the polarity protection circuit (0V to 2V).

The Ag6400 checks for a  $25k\Omega$  slope and the dc offset voltage by using a 4 point detection method. The first and second points are measured by forcing a current; if these are valid the port will continue with the third and fourth points which force a voltage. From these points the resistive slope and the offset voltage is calculated and tested.

Figure 11 shows a valid signature slope. If the first forced current result measures <1V, the test will be aborted and the relevant port status register bits 0 to 2 will report a "Short Circuit". A full list of the port status register signature bit setting is shown in Table 4.

Figure 11: Signature Slope

|   | Bits |   | Description                                         |

|---|------|---|-----------------------------------------------------|

| 2 | 1    | 0 | Description                                         |

| 0 | 0    | 0 | Unknown                                             |

| 0 | 0    | 1 | Short circuit                                       |

| 0 | 1    | 0 | PD Input Capacitance (C <sub>PD</sub> ) is too high |

| 0 | 1    | 1 | Signature Resistance (R <sub>SIG</sub> ) is too low |

| 1 | 0    | 0 | Signature is valid                                  |

| 1 | 0    | 1 | R <sub>SIG</sub> is too high                        |

| 1 | 1    | 0 | Open circuit                                        |

| 1 | 1    | 1 | Port offset voltage is too high                     |

Table 4: Port Status Register – Signature Bits 0 - 2

### 6.2 Classification

On completion of a valid signature, the Ag6400 will then interrogate the PD to see if a classification signature is present. The classification signature is used to determine the amount of power the PD will draw and limits the output power accordingly (see Table 5). It is optional for the PD to present a classification signature and the Ag6400 will default to Class 0 if the PD does not present one.

The PD presents a classification signature in the form of a constant current load when a PSE port applies a voltage between 15.5V to 20.5V.

Table 5 shows the measured current limits that the Ag6400 uses to assign a classification value.

| Measured Current | Classification |

|------------------|----------------|

| 0mA to 6.5mA     | Class 0        |

| >6.5mA to 14.5mA | Class 1        |

| >14.5mA to 23mA  | Class 2        |

| >23mA to 33mA    | Class 3        |

| >33mA to 48mA    | Class 4        |

| >48mA            | Over Current   |

#### Table 5: Classification Table

The classification result is reported in bits 4 to 6 of the port status register; these are shown in Table 6.

|   | Bits |   | Description  |

|---|------|---|--------------|

| 6 | 5    | 4 | Description  |

| 0 | 0    | 0 | Unknown      |

| 0 | 0    | 1 | Class 1      |

| 0 | 1    | 0 | Class 2      |

| 0 | 1    | 1 | Class 3      |

| 1 | 0    | 0 | Class 4      |

| 1 | 0    | 1 | Reserved     |

| 1 | 1    | 0 | Class 0      |

| 1 | 1    | 1 | Over Current |

Table 6: Port Status Register - Classification Bits 4 - 6

The Ag6400 supports 2-event classification required to supply the higher power to a Type 2 PD. When the port detects a Class 4 current, it backs off to a mark voltage level and then makes a second classification measurement. Providing both measurements draw Class 4 current the Ag6400 will set that port to deliver the power levels shown in Table 2.

### 6.3 Current Cutoff and Limits

When a port has successfully completed the Signature and Classification; the main power will be turned on. The main power is current limited by two parameters  $I_{CUT}$  and  $I_{LIM}$ . Table 2 show the values assigned to these parameters in Hardware mode. These are the recommend values that should set in Software mode.

The I<sub>LIM</sub> parameter sets the maximum current that can be delivered from a port. If this is set to 850mA and the PD attempts to draw 1A, then the Ag6400 will current limit that port at 850mA. Table 7 gives a list of I<sub>LIM</sub> current limit settings that can be programmed into the lim<sub>N</sub> registers; the Type 1 and Type 2 default parameters are highlighted.

| I <sub>LIM</sub> (mA) | Setting (hex) |

|-----------------------|---------------|

| 106                   | 88            |

| 213                   | 08            |

| 359                   | 89            |

| 425                   | 80            |

| 531                   | 8A            |

| 638                   | 90            |

| 744                   | 9A            |

| 850                   | C0            |

| 956                   | CA            |

| 1063                  | D0            |

| 1169                  | DA            |

| 1275                  | D1            |

| 1381                  | DB            |

| 1488                  | 49            |

| 1700                  | 40            |

Table 7: I<sub>LIM</sub> Current Limit Settings

The second parameter is  $I_{CUT}$ , this lower than  $I_{LIM}$  and sets the cutoff operating current for a port. Short transients are allowed to exceed  $I_{CUT}$  (limited by  $I_{LIM}$ ), to handle load step changes from the PD. But if the PD continually exceeds  $I_{CUT}$  the Ag6400 will shut down that port.

The  $i_{CUT}$  registers have a 6 bit resolution, in normal mode the Least Significant Bit (LSB) = 18.75mA, giving a programming range up to 1181mA. These registers also have a double bit and when this is cleared (= 0), the LSB = 37.5mA, increasing the programming range up to 2363mA.

# 7. Software Mode

If you require the Ag6400 to respond to the Data Link Layer (DLL) communication noted in the IEEE802.3at specification, the Ag6400 must be configured in software mode. In hardware mode providing the Ag6400 sees a Class 4 signature it will automatically supply the higher output current (see Table 2). The PSE uses the DLL communication to confirm that the product is indeed a Type 2 product but this is not required for compliance.

The detail of the Data Link Layer structure is detailed in the IEEE802.3at specification.

### 7.1 Register Map

The Register Map is shown in Table 8, the following list shows the R/W codes: -

CoR = Clear on Read: Register cleared after a read (writing to the register has no effect).

R/W = Read/Write: Register can be read (without affecting the register) or written to.

RO = Read Only: Register can be read without affecting the register (writing to the register has no effect).

SO = Set Only: Register can be written to (data read from the register is meaningless).

$Ag6400 \\ \texttt{POE+Power-Sourcing-Equipment Module} \\$

| Addr             | Name                                     | R/W        | Bit 7              | Bit 6                                      | Bit 5                    | Bit 4              | Bit 3                                    | Bit 2                                    | Bit 1                                    | Bit 0                                    | Mode = 0  | Mode = 1               |

|------------------|------------------------------------------|------------|--------------------|--------------------------------------------|--------------------------|--------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-----------|------------------------|

| Interrupt<br>00h | Registers<br>int                         | RO         | eupply             | tor:                                       | to -                     | class              | det                                      | dis                                      | nad                                      | per                                      | 1000 0000 | 1000 0000              |

| 00h              | intmask                                  | R/W        | supply<br>supply   | t <sub>start</sub>                         | t <sub>CUT</sub>         | class              | det                                      | dis                                      | pgd<br>pgd                               | per<br>per                               | 1000 0000 | 1110 0100              |

| Event Re         |                                          | 1011       | ouppiy             | START                                      | ·C01                     | 01000              | 401                                      | alo                                      | pgu                                      | - poi                                    | 1000 0000 | 1110 0100              |

| 02h              | per                                      | RO         | pgd4               | pgd3                                       | pgd2                     | pgd1               | psc4                                     | psc3                                     | psc2                                     | psc1                                     | 0000 0000 | 0000 0000              |

| 03h              | per_cor                                  | CoR        | pgd4               | pgd3                                       | pgd2                     | pgd1               | psc4                                     | psc3                                     | psc2                                     | psc1                                     | 0000 0000 | 0000 0000              |

| 04h              | det                                      | RO         | class4             | class3                                     | class2                   | class1             | sig4                                     | sig3                                     | sig2                                     | sig1                                     | 0000 0000 | 0000 0000              |

| 05h              | det_cor                                  | CoR        | class4             | class3                                     | class2                   | class1             | sig4                                     | sig3                                     | sig2                                     | sig1                                     | 0000 0000 | 0000 0000              |

| 06h<br>07h       | fer<br>fer_cor                           | RO<br>CoR  | dis4<br>dis4       | dis3<br>dis3                               | dis2<br>dis2             | dis1<br>dis1       | t <sub>CUT</sub> 4<br>t <sub>CUT</sub> 4 | t <sub>CUT</sub> 3<br>t <sub>CUT</sub> 3 | t <sub>CUT</sub> 2<br>t <sub>CUT</sub> 2 | t <sub>CUT</sub> 1<br>t <sub>CUT</sub> 1 | 0000 0000 | 0000 0000              |

| 07h<br>08h       | tsr                                      | RO         | t <sub>LIM</sub> 4 | t <sub>LIM</sub> 3                         | t <sub>LIM</sub> 2       | t <sub>LIM</sub> 1 | t <sub>START</sub> 4                     | t <sub>START</sub> 3                     | t <sub>START</sub> 2                     | t <sub>START</sub> 1                     | 0000 0000 | 0000 0000              |

| 09h              | tsr cor                                  | CoR        | t <sub>LIM</sub> 4 | t <sub>LIM</sub> 3                         | t <sub>LIM</sub> 2       | t <sub>LIM</sub> 1 | t <sub>START</sub> 4                     | t <sub>START</sub> 3                     | t <sub>START</sub> 2                     | t <sub>START</sub> 1                     | 0000 0000 | 0000 0000              |

| 0Ah              | ser                                      | RO         | temp               | -                                          | uvlo3                    | uvlo48             | -                                        | -                                        | -                                        | -                                        | 0011 0010 | 0011 0010              |

| 0Bh              | ser_cor                                  | CoR        | temp               | -                                          | uvlo3                    | uvlo48             | -                                        | -                                        | -                                        | -                                        | 0011 0010 | 0011 0010              |

| Status Re        |                                          |            |                    |                                            |                          |                    |                                          |                                          |                                          |                                          |           |                        |

| 0Ch              | psr1                                     | RO<br>RO   | -                  |                                            | class[2:0]               |                    | -                                        |                                          | detect[2:0]                              |                                          | 0000 0000 | 0000 0000              |

| 0Dh<br>0Eh       | psr2<br>psr3                             | RO         | -                  |                                            | class[2:0]<br>class[2:0] |                    | -                                        |                                          | detect[2:0]<br>detect[2:0]               |                                          | 0000 0000 | 0000 0000              |

| 0Eh              | psr3                                     | RO         | -                  |                                            | class[2:0]               |                    | -                                        |                                          | detect[2:0]                              |                                          | 0000 0000 | 0000 0000              |

| 10h              | pwsr                                     | RO         | pg4                | pg3                                        | pg2                      | pg1                | pe4                                      | pe3                                      | pe2                                      | pe1                                      | 0000 0000 | 0000 0000              |

| 11h              | pinsr                                    | RO         | -                  | -                                          | ad3                      | ad2                | ad1                                      | ad0                                      | mid                                      | mode                                     | 00xx xxx0 | 00xx xxx1              |

|                  | ation Registers                          |            |                    |                                            |                          |                    |                                          |                                          |                                          |                                          |           |                        |

| 12h              | omr                                      | R/W        |                    | 4[1:0]                                     |                          | 3[1:0]             |                                          | 2[1:0]                                   |                                          | 1[1:0]                                   | 0000 0000 | 1111 1111              |

| 13h              | disenr                                   | R/W        | e_ac4              | e_ac3                                      | e_ac2                    | e_ac1              | dc4                                      | dc3                                      | dc2                                      | dc1                                      | 0000 0000 | 1111 0000              |

| 14h<br>15h       | dcenr<br>midspan                         | R/W<br>R/W | cep4               | cep3<br>-                                  | cep2                     | cep1               | dep4<br>mid4                             | dep3<br>mid3                             | dep2<br>mid2                             | dep1<br>mid1                             | 0000 0000 | 1111 1111<br>0000 MMMM |

| 16h              | tcr                                      | R/W        | -                  | -                                          |                          | <br>⊤[1:0]         |                                          | [1:0]                                    | t <sub>DIS</sub>                         |                                          | 0000 0000 | 0000 0000              |

| 17h              | conf                                     | R/W        | inten              | detchg                                     |                          | -                  | -                                        | -                                        | -                                        | -                                        | 1010 0000 | 1010 0000              |

| Action Re        |                                          |            |                    | Ň                                          |                          |                    |                                          |                                          |                                          |                                          |           | •                      |

| 18h              | detar                                    | SO         | cls4               | cls3                                       | cls2                     | cls1               | det4                                     | det3                                     | det2                                     | det1                                     | 0000 0000 | 0000 0000              |

| 19h              | pwr                                      | SO         | off4               | off3                                       | off2                     | off1               | on4                                      | on3                                      | on2                                      | on1                                      | 0000 0000 | 0000 0000              |

| 1Ah              | reset                                    | SO         | allclr             | allclr intclr - allrst rst4 rst3 rst2 rst1 |                          |                    |                                          |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 1Eh              | ing Registers<br>tlim12                  | R/W        |                    | t <sub>LIM</sub> 2                         | [3.0]                    |                    |                                          | t1                                       | [3:0]                                    |                                          | 0000 0000 | 0000 0000              |

| 1Fh              | tlim34                                   | R/W        |                    |                                            | [3:0]                    |                    |                                          |                                          | [3:0]<br>8[3:0]                          |                                          | 0000 0000 | 0000 0000              |

|                  | surement Reg                             |            |                    | CIN .                                      | [0:0]                    |                    |                                          | SCIME.                                   | ,[0:0]                                   |                                          | 0000 0000 | 0000 0000              |

| 30h              | ip1lsb                                   | RO         |                    |                                            |                          | ip1ls              | b[7:0]                                   |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 31h              | ip1msb                                   | RO         |                    |                                            |                          |                    | sb[7:0]                                  |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 32h              | vp1lsb                                   | RO         |                    |                                            |                          |                    | b[7:0]                                   |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 33h<br>34h       | vp1msb<br>ip2lsb                         | RO<br>RO   |                    |                                            |                          | vp2m:              | b[7:0]                                   |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 34h<br>35h       | ip2isb                                   | RO         |                    |                                            |                          |                    | sb[7:0]                                  |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 36h              | vp2lsb                                   | RO         |                    |                                            |                          | vp2ls              |                                          |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 37h              | vp2msb                                   | RO         |                    |                                            |                          | vp2m               |                                          |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 38h              | ip3lsb                                   | RO         |                    |                                            |                          | ip3ls              |                                          |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 39h              | ip3msb                                   | RO         |                    |                                            |                          | ip3ms              |                                          |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 3Ah<br>3Bh       | vp3lsb                                   | RO<br>RO   |                    |                                            |                          |                    | b[7:0]                                   |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 3Ch              | vp3msb<br>ip4lsb                         | RO         |                    |                                            |                          |                    | sb[7:0]<br>b[7:0]                        |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 3Dh              | ip4msb                                   | RO         |                    |                                            |                          | -                  | sb[7:0]                                  |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 3Eh              | vp4lsb                                   | RO         |                    |                                            |                          | vp4ls              |                                          |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 3Fh              | vp4msb                                   | RO         |                    |                                            |                          |                    | sb[7:0]                                  |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

|                  | anagement Re                             | 0          |                    |                                            |                          |                    |                                          |                                          |                                          |                                          |           |                        |

| 44h              | pen                                      | R/W        | -                  | -                                          | -                        | -                  | pen4                                     | pen3                                     | pen2                                     | pen1                                     | 0000 0000 | 0000 1111              |

| 46h              | pm1                                      | R/W        | -                  | -                                          | -                        | -                  |                                          | -<br>[5:0]                               | legen1                                   | cl4en1                                   | 0000 0000 | 0000 0001 1101 0100    |

| 47h<br>48h       | i <sub>сuт</sub> 1<br>i <sub>LIM</sub> 1 | R/W<br>R/W | rdis               | cutdbl                                     | 1                        | i I                | <u>Iсит</u><br>[7:0]                     | [5:0]                                    |                                          |                                          | 0001 0100 | 0000 0000              |

| 49h              | pstat1                                   | R/W        | -                  | -                                          | -                        | 'LIMI<br>-         | 7.0j<br>-                                | -                                        | -                                        | cl4det1                                  | 0000 0000 | 0000 0000              |

| 4Bh              | potati<br>pm2                            | R/W        | -                  | -                                          | -                        | -                  | -                                        | -                                        | legen2                                   | cl4en2                                   | 0000 0000 | 0000 0001              |

| 4Ch              | i <sub>сuт</sub> 2                       | R/W        | rdis               | cutdbl                                     |                          | ·                  | і <sub>с</sub> ит                        | [5:0]                                    |                                          | ·                                        | 0001 0100 | 1101 0100              |

| 4Dh              | i <sub>LIM</sub> 2                       | R/W        |                    |                                            |                          | İ <sub>LIM</sub>   | 7:0]                                     |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 4Eh              | pstat2                                   | R/W        | -                  | -                                          | -                        | -                  | -                                        | -                                        | -                                        | cl4det2                                  | 0000 0000 | 0000 0000              |

| 50h              | pm3                                      | R/W        | -                  | -                                          | -                        | -                  | -                                        | -                                        | legen3                                   | cl4en3                                   | 0000 0000 | 0000 0001              |

| 51h<br>52h       | i <sub>CUT</sub> 3                       | R/W<br>R/W | rdis               | cutdbl                                     |                          | i. 1               | I <sub>сит</sub><br>[7:0]                | [5:0]                                    |                                          |                                          | 0001 0100 | 1101 0100<br>0000 0000 |

| 52n<br>53h       | i <sub>LIM</sub> 3<br>pstat3             | R/W        | -                  | -                                          | -                        | ILIM               | 7:0j<br>-                                | -                                        | -                                        | cl4det3                                  | 0000 0000 | 0000 0000              |

| 55h              | pstat3                                   | R/W        | -                  | -                                          | -                        | -                  | -                                        | -                                        | legen4                                   | cl4det3                                  | 0000 0000 | 0000 0000              |

| 56h              | i <sub>cut</sub> 4                       | R/W        | rdis               | cutdbl                                     |                          | •                  | İ <sub>сит</sub>                         | [5:0]                                    |                                          |                                          | 0001 0100 | 1101 0100              |

|                  | i <sub>LIM</sub> 4                       | R/W        |                    |                                            |                          | i <sub>LIM</sub>   |                                          |                                          |                                          |                                          | 0000 0000 | 0000 0000              |

| 57h<br>58h       | pstat4                                   | R/W        | -                  | -                                          |                          | -                  |                                          | -                                        |                                          | cl4det4                                  | 0000 0000 | 0000 0000              |

### Table 8: Register Map

M = State of the MID pin.

#### 7.1.1 Interrupt Registers

There are two registers that are directly associated with the Ag6400 interrupt:-

int (Address 00h): Interrupt Status Register.

This is a Read only register; that monitors the status of the event registers.

| bit 7  | bit 6              | bit 5            | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|--------|--------------------|------------------|-------|-------|-------|-------|-------|

| supply | t <sub>START</sub> | t <sub>CUT</sub> | class | det   | dis   | pgd   | per   |

| Bits | Symbol             | Description                                                                                          |

|------|--------------------|------------------------------------------------------------------------------------------------------|

| 0    | per                | Power Enable Interrupt: Set if any of the power event interrupt register (02h) psc <sub>N</sub>      |

|      |                    | bits are set.                                                                                        |

| 1    | pgd                | Power Good Interrupt: Set if any of the power event interrupt register (02h) $pgd_N$                 |

|      |                    | bits are set.                                                                                        |

| 2    | dis                | Disconnect Interrupt: Set if any of the event interrupt register (06h) t <sub>CUTN</sub> bits are    |

|      |                    | set.                                                                                                 |

| 3    | det                | Detect Interrupt: Set if any of the detect event register (04h) sig <sub>N</sub> bits are set.       |

| 4    | class              | Class Interrupt: Set if any of the detect event register (04h) class <sub>N</sub> bits are set.      |

| 5    | t <sub>CUT</sub>   | $t_{CUT}$ Interrupt: Set if any of the $t_{CUT}$ event register (06h) dis <sub>N</sub> bits are set  |

| 6    | t <sub>START</sub> | t <sub>START</sub> Interrupt: Set if any of the t <sub>START</sub> event register (08h) bits are set |

| 7    | supply             | Power Interrupt: Set if any of the supply event register (0Ah) bits are set                          |

#### intmask (Address 01h): Interrupt Mask Register.

This is a Read/Write register; that controls which events will pull the /INT pin low.

| bit 7  | bit 6              | bit 5            | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|--------|--------------------|------------------|-------|-------|-------|-------|-------|

| supply | t <sub>START</sub> | t <sub>CUT</sub> | class | det   | dis   | pgd   | per   |

| Bits | Symbol             | Description                                            |

|------|--------------------|--------------------------------------------------------|

| 0    | per                | A Power Enable event will pull the /INT pin low.       |

| 1    | pgd                | A Power Good event will pull the /INT pin low.         |

| 2    | dis                | A Disconnect event will pull the /INT pin low.         |

| 3    | det                | A Detect event will pull the /INT pin low.             |

| 4    | class              | A Class event will pull the /INT pin low.              |

| 5    | t <sub>cut</sub>   | A t <sub>CUT</sub> event will pull the /INT pin low.   |

| 6    | t <sub>START</sub> | A t <sub>START</sub> event will pull the /INT pin low. |

| 7    | supply             | A Supply event will pull the /INT pin low.             |

### 7.1.2 Event Registers

There are ten event registers that are associated with the Ag6400 interrupt registers:-

per (Address 02h): Power Event Register.

This is a Read only register; the four lower bits indicate if a port has been turned on or off. The four upper bits indicate if the power good status has changed (see pwsr register 10h).

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| pgd4  | pgd3  | pgd2  | pgd1  | psc4  | psc3  | psc2  | psc1  |

| Bits | Symbol | Description                |

|------|--------|----------------------------|

| 0    | psc1   | Port 1 power status change |

| 1    | psc2   | Port 2 power status change |

| 2    | psc3   | Port 3 power status change |

| 3    | psc4   | Port 4 power status change |

| 4    | pgd1   | Port 1 power good change   |

| 5    | pgd2   | Port 2 power good change   |

| 6    | pgd3   | Port 3 power good change   |

| 7    | pgd4   | Port 4 power good change   |

#### per\_cor (Address 03h): Power Event Register.

This is a Clear on Read register; it is identical to "per" register (02h) except that reading from this register clears both the "per" and "per\_cor" registers.

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| pgd4  | pgd3  | pgd2  | pgd1  | psc4  | psc3  | psc2  | psc1  |

| Bits | Symbol | Description                |  |  |  |  |  |

|------|--------|----------------------------|--|--|--|--|--|

| 0    | psc1   | Port 1 power status change |  |  |  |  |  |

| 1    | psc2   | Port 2 power status change |  |  |  |  |  |

| 2    | psc3   | Port 3 power status change |  |  |  |  |  |

| 3    | psc4   | Port 4 power status change |  |  |  |  |  |

| 4    | pgd1   | Port 1 power good change   |  |  |  |  |  |

| 5    | pgd2   | Port 2 power good change   |  |  |  |  |  |

| 6    | pgd3   | Port 3 power good change   |  |  |  |  |  |

| 7    | pgd4   | Port 4 power good change   |  |  |  |  |  |

#### det (Address 04h): Detect and Classification Event Register.

This is a Read only register; the four lower bits indicate that the port signature detection has completed. The four upper bits indicate that the port classification has completed. The results for each port are shown in the  $psr_N$  registers (0Ch to 0Fh).

| bit 7  | bit 6  | bit 5  | bit 4  | bit 3 | bit 2 | bit 1 | bit 0 |

|--------|--------|--------|--------|-------|-------|-------|-------|

| class4 | class3 | class2 | class1 | sig4  | sig3  | sig2  | sig1  |

| Bits | Symbol | Description                         |

|------|--------|-------------------------------------|

| 0    | sig1   | Port 1 signature detection complete |

| 1    | sig2   | Port 2 signature detection complete |

| 2    | sig3   | Port 3 signature detection complete |

| 3    | sig4   | Port 4 signature detection complete |

| 4    | class1 | Port 1 classification complete      |

| 5    | class2 | Port 2 classification complete      |

| 6    | class3 | Port 3 classification complete      |

| 7    | class4 | Port 4 classification complete      |

det\_cor (Address 05h): Detect and Classification Event Register.

This is a Clear on Read register; it is identical to "det" register (04h) except that reading from this register clears both the "det" and "det\_cor" registers.

| bit 7  | bit 6  | bit 5  | bit 4  | bit 3 | bit 2 | bit 1 | bit 0 |

|--------|--------|--------|--------|-------|-------|-------|-------|

| class4 | class3 | class2 | class1 | sig4  | sig3  | sig2  | sig1  |

| Bits | Symbol | Description                         |

|------|--------|-------------------------------------|

| 0    | sig1   | Port 1 signature detection complete |

| 1    | sig2   | Port 2 signature detection complete |

| 2    | sig3   | Port 3 signature detection complete |

| 3    | sig4   | Port 4 signature detection complete |

| 4    | class1 | Port 1 classification complete      |

| 5    | class2 | Port 2 classification complete      |

| 6    | class3 | Port 3 classification complete      |

| 7    | class4 | Port 4 classification complete      |

#### fer (Address 06h): Fault Event Register.

This is a Read only register; the four lower bits indicate that the port has been turned off because the port current was above  $i_{CUT}$ . The upper four bits are set when the port current falls below 5mA.

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3              | bit 2              | bit 1              | bit 0              |

|-------|-------|-------|-------|--------------------|--------------------|--------------------|--------------------|

| dis4  | dis3  | dis2  | dis1  | t <sub>CUT</sub> 4 | t <sub>CUT</sub> 3 | t <sub>CUT</sub> 2 | t <sub>CUT</sub> 1 |

| Bits | Symbol             | Description                                                                |  |  |  |  |  |

|------|--------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| 0    | t <sub>CUT</sub> 1 | Port 1 over-current timeout. While the port was powered the output current |  |  |  |  |  |

|      |                    | exceeded (i <sub>CUT</sub> ) for longer than (t <sub>CUT</sub> )           |  |  |  |  |  |

| 1    | t <sub>CUT</sub> 2 | Port 2 over-current timeout                                                |  |  |  |  |  |

| 2    | t <sub>CUT</sub> 3 | Port 3 over-current timeout                                                |  |  |  |  |  |

| 3    | t <sub>CUT</sub> 4 | Port 4 over-current timeout                                                |  |  |  |  |  |

| 4    | dis1               | Port 1 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

| 5    | dis2               | Port 2 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

| 6    | dis3               | Port 3 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

| 7    | dis4               | Port 4 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

#### fer\_cor (Address 07h): Fault Event Register.

This is a Clear on Read register; it is identical to "fer" register (06h) except that reading from this register clears both the "fer" and "fer\_cor" registers.

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3              | bit 2              | bit 1              | bit 0              |

|-------|-------|-------|-------|--------------------|--------------------|--------------------|--------------------|

| dis4  | dis3  | dis2  | dis1  | t <sub>CUT</sub> 4 | t <sub>CUT</sub> 3 | t <sub>CUT</sub> 2 | t <sub>CUT</sub> 1 |

| Bits | Symbol             | Description                                                                |  |  |  |  |  |

|------|--------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| 0    | t <sub>cut</sub> 1 | Port 1 over-current timeout. While the port was powered the output current |  |  |  |  |  |

|      |                    | exceeded (i <sub>CUT</sub> ) for longer than (t <sub>CUT</sub> )           |  |  |  |  |  |

| 1    | t <sub>CUT</sub> 2 | Port 2 over-current timeout                                                |  |  |  |  |  |

| 2    | t <sub>CUT</sub> 3 | Port 3 over-current timeout                                                |  |  |  |  |  |

| 3    | t <sub>CUT</sub> 4 | Port 4 over-current timeout                                                |  |  |  |  |  |

| 4    | dis1               | Port 1 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

| 5    | dis2               | Port 2 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

| 6    | dis3               | Port 3 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

| 7    | dis4               | Port 4 disconnect timeout (t <sub>DIS</sub> )                              |  |  |  |  |  |

#### tsr (Address 08h): t<sub>START</sub> Event Register.

This is a Read only register; the four lower bits indicate an over-current fault. The upper four bits indicate that the port has been turned off because the port current was above  $i_{LIM}$ .

| bit 7              | bit 6              | bit 5              | bit 4              | bit 3                | bit 2                | bit 1                | bit 0                |

|--------------------|--------------------|--------------------|--------------------|----------------------|----------------------|----------------------|----------------------|

| t <sub>LIM</sub> 4 | t <sub>LIM</sub> 3 | t <sub>LIM</sub> 2 | t <sub>LIM</sub> 1 | t <sub>START</sub> 4 | t <sub>START</sub> 3 | t <sub>START</sub> 2 | t <sub>START</sub> 1 |

| Bits | Symbol               | Description                                                                                            |

|------|----------------------|--------------------------------------------------------------------------------------------------------|

| 0    | t <sub>START</sub> 1 | Port 1 start-up over-current timeout (t <sub>START</sub> ). While turning on the port the PD has       |

|      |                      | drawn more than 375mA for longer than t <sub>START</sub> causing the port to turn off                  |

| 1    | t <sub>START</sub> 2 | Port 2 start-up over-current timeout (t <sub>START</sub> )                                             |

| 2    | t <sub>START</sub> 3 | Port 3 start-up over-current timeout (t <sub>START</sub> )                                             |

| 3    | t <sub>START</sub> 4 | Port 4 start-up over-current timeout (t <sub>START</sub> )                                             |

| 4    | t <sub>LIM</sub> 1   | Port 1 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 1 field of the tlim12 register (1Eh)                                                  |

| 5    | t <sub>LIM</sub> 2   | Port 2 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 2 field of the tlim12 register (1Eh)                                                  |

| 6    | t <sub>LIM</sub> 3   | Port 3 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 3 field of the tlim34 register (1Fh)                                                  |

| 7    | t <sub>LIM</sub> 4   | Port 4 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 4 field of the tlim34 register (1Fh)                                                  |

#### tsr\_cor (Address 09h): t<sub>START</sub> Event Register.

This is a Clear on Read register; it is identical to "tsr" register (08h) except that reading from this register clears both the "tsr" and "tsr\_cor" registers.

| bit 7              | bit 6              | bit 5              | bit 4              | bit 3                | bit 2                | bit 1                | bit 0                |

|--------------------|--------------------|--------------------|--------------------|----------------------|----------------------|----------------------|----------------------|

| t <sub>LIM</sub> 4 | t <sub>LIM</sub> 3 | t <sub>LIM</sub> 2 | t <sub>LIM</sub> 1 | t <sub>START</sub> 4 | t <sub>START</sub> 3 | t <sub>START</sub> 2 | t <sub>START</sub> 1 |

| Bits | Symbol               | Description                                                                                            |

|------|----------------------|--------------------------------------------------------------------------------------------------------|

| 0    | t <sub>START</sub> 1 | Port 1 start-up over-current timeout (t <sub>START</sub> ). While turning on the port the PD has       |

|      |                      | drawn more than 375mA for longer than t <sub>START</sub> causing the port to turn off                  |

| 1    | t <sub>START</sub> 2 | Port 2 start-up over-current timeout (t <sub>START</sub> )                                             |

| 2    | t <sub>START</sub> 3 | Port 3 start-up over-current timeout (t <sub>START</sub> )                                             |

| 3    | t <sub>START</sub> 4 | Port 4 start-up over-current timeout (t <sub>START</sub> )                                             |

| 4    | t <sub>LIM</sub> 1   | Port 1 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 1 field of the tlim12 register (1Eh)                                                  |

| 5    | t <sub>LIM</sub> 2   | Port 2 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 2 field of the tlim12 register (1Eh)                                                  |

| 6    | t <sub>LIM</sub> 3   | Port 3 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 3 field of the tlim34 register (1Fh)                                                  |

| 7    | t <sub>LIM</sub> 4   | Port 4 current limit timeout. The length of the current limit (t <sub>LIM</sub> ) is controlled by the |

|      |                      | t <sub>LIM</sub> 4 field of the tlim34 register (1Fh)                                                  |

#### ser (Address 0Ah): Supply Event Register.

This is a Read only register; the bits in this register are set when a problem occurs with the power supplies or temperature.

| bit 7 | bit 6 | bit 5 | bit 4  | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|--------|-------|-------|-------|-------|

| temp  | -     | uvlo3 | uvlo48 | -     | -     | -     | -     |

| Bits | Symbol | Description                                                                                                                 |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 0    | -      | Reserved                                                                                                                    |

| 1    | -      | Reserved                                                                                                                    |

| 2    | -      | Reserved                                                                                                                    |

| 3    | -      | Reserved                                                                                                                    |

| 4    | uvlo48 | V <sub>EE</sub> Under Voltage Lock Out (UVLO). Set when the V <sub>EE</sub> supply is too low for normal operation.         |

| 5    | uvlo3  | V <sub>DD</sub> UVLO. Set when the V <sub>DD</sub> supply is too low for normal operation.                                  |

| 6    | -      | Reserved                                                                                                                    |

| 7    | temp   | Over Temperature. Set when the controller temperature is too high. If set, signature and class must be re-enabled manually. |

#### ser\_cor (Address 0Bh): Supply Event Register.

This is a Clear on Read register; it is identical to "ser" register (0Ah) except that reading from this register clears both the "ser" and "ser\_cor" registers.

| bit 7 | bit 6 | bit 5 | bit 4  | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|--------|-------|-------|-------|-------|

| temp  | -     | uvlo3 | uvlo48 | -     | -     | -     | -     |

| Bits | Symbol | Description                                                                                                                 |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 0    | -      | Reserved                                                                                                                    |

| 1    | -      | Reserved                                                                                                                    |

| 2    | -      | Reserved                                                                                                                    |

| 3    | -      | Reserved                                                                                                                    |

| 4    | uvlo48 | V <sub>EE</sub> Under Voltage Lock Out (UVLO). Set when the V <sub>EE</sub> supply is too low for normal operation.         |

| 5    | uvlo3  | $V_{DD}$ UVLO. Set when the $V_{DD}$ supply is too low for normal operation.                                                |

| 6    | -      | Reserved                                                                                                                    |

| 7    | temp   | Over Temperature. Set when the controller temperature is too high. If set, signature and class must be re-enabled manually. |

### 7.1.3 Status Registers

There are six status registers that are used by the Ag6400:-

#### psr1 (Address 0Ch): Port1 Status Register.

This is a Read only register; that shows the results of the signature and classification measurements for Port 1.

| bit 7 | bit 6      | bit 5 | bit 4 | bit 3 | bit 2 | bit 1       | bit 0 |

|-------|------------|-------|-------|-------|-------|-------------|-------|

| -     | class[2:0] |       |       | -     |       | detect[2:0] |       |

| Bits | Symbol | Description  |

|------|--------|--------------|

| 2:0  | detect | See Table 9  |

| 3    | -      | Reserved     |

| 6:4  | class  | See Table 10 |

| 7    | -      | Reserved     |

|           | detect[2:0] |           |                       |

|-----------|-------------|-----------|-----------------------|

| detect[2] | detect[1]   | detect[0] | Description           |

| 0         | 0           | 0         | Unknown               |

| 0         | 0           | 1         | Short                 |

| 0         | 1           | 0         | Cpd too high          |

| 0         | 1           | 1         | R <sub>SIG</sub> low  |

| 1         | 0           | 0         | Good                  |

| 1         | 0           | 1         | R <sub>siG</sub> high |

| 1         | 1           | 0         | Open                  |

| 1         | 1           | 1         | Reserved              |

Table 9: Signature Results

| -         |            |           |              |

|-----------|------------|-----------|--------------|

|           | class[2:0] |           |              |

| detect[2] | detect[1]  | detect[0] | Description  |

| 0         | 0          | 0         | Unknown      |

| 0         | 0          | 1         | Class 1      |

| 0         | 1          | 0         | Class 2      |

| 0         | 1          | 1         | Class 3      |

| 1         | 0          | 0         | Class 4      |

| 1         | 0          | 1         | Reserved     |

| 1         | 1          | 0         | Class 0      |

| 1         | 1          | 1         | Over Current |

Table 10: Classification Results

#### psr2 (Address 0Dh): Port2 Status Register.

This is a Read only register; that shows the results of the signature and classification measurements for Port 2.

See psr1 for full details.

psr3 (Address 0Eh): Port3 Status Register.

This is a Read only register; that shows the results of the signature and classification measurements for Port 3.

See psr1 for full details.

psr4 (Address 0Fh): Port4 Status Register.

This is a Read only register; that shows the results of the signature and classification measurements for Port 3.

See psr1 for full details.

### pwsr (Address 10h): Power Status Register.

This is a Read only register; that shows the power status of each port.

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| pg4   | pg3   | pg2   | pg1   | pe4   | pe3   | pe2   | pe1   |

| Bits | Symbol | Description             |  |  |  |

|------|--------|-------------------------|--|--|--|

| 0    | pe1    | Power enabled on port 1 |  |  |  |

| 1    | pe2    | Power enabled on port 2 |  |  |  |

| 2    | pe3    | Power enabled on port 3 |  |  |  |

| 3    | pe4    | Power enabled on port 4 |  |  |  |

| 4    | pg1    | Power good on port 1    |  |  |  |

| 5    | pg2    | Power good on port 2    |  |  |  |

| 6    | pg3    | Power good on port 3    |  |  |  |

| 7    | pg4    | Power good on port 4    |  |  |  |

#### pinsr (Address 11h): Pin Status Register.

This is a Read only register; that shows the logic state of the hardware input pin.

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | -     | ad3   | ad2   | ad1   | ad0   | mid   | mode  |

| Bits | Symbol | Description          |

|------|--------|----------------------|

| 0    | mode   | MODE pin logic state |

| 1    | mid    | MID pin logic state  |

| 2    | ad0    | AD0 pin logic state  |

| 3    | ad1    | AD1 pin logic state  |

| 4    | ad2    | AD2 pin logic state  |

| 5    | ad3    | AD3 pin logic state  |

| 6    | -      | Reserved             |

| 7    | -      | Reserved             |

#### 7.1.4 Configuration Registers

There are six configuration registers that are used by the Ag6400:-

omr (Address 12h): Operating Mode Register.

This is a Read/Write register; that shows and can set the operating mode of the Ag6400.

| bit 7               | bit 6 | bit 5 | bit 4  | bit 3 | bit 2  | bit 1 | bit 0 |

|---------------------|-------|-------|--------|-------|--------|-------|-------|

| omp4[1:0] omp3[1:0] |       | omp2  | 2[1:0] | omp   | 1[1:0] |       |       |

| Bits | Symbol | Description            |

|------|--------|------------------------|

| 1:0  | omp1   | Operating mode, port 1 |

| 3:2  | omp2   | Operating mode, port 2 |

| 5:4  | omp3   | Operating mode, port 3 |

| 7:6  | omp4   | Operating mode, port 4 |

| omp₁                 | <sub>v</sub> [1:0]   |             |

|----------------------|----------------------|-------------|

| omp <sub>N</sub> [1] | omp <sub>N</sub> [0] | Description |

| 0                    | 0                    | Shutdown    |

| 0                    | 1                    | Manual*     |

| 1                    | 0                    | Software    |

| 1                    | 1                    | Hardware    |

Table 11: Classification Results

\*Note: The Manual mode is a further extension of Software mode, where the Ag6400 require full control over the I<sup>2</sup>C Bus.

disenr (Address 13h): Disconnect Sensing Enable Register.

This is a Read/Write register; that enables the port disconnect feature of the Ag6400. When using DC disconnect, if the port current is <5mA (for t<sub>DIS</sub>) the port will be turned off.

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| e-ac4 | e-ac3 | e-ac2 | e-ac1 | dc4   | dc3   | dc2   | dc1   |

| Bits | Symbol | Description                      |  |  |  |

|------|--------|----------------------------------|--|--|--|

| 0    | dc1    | Enables DC disconnect on port 1  |  |  |  |

| 1    | dc2    | Enables DC disconnect on port 2  |  |  |  |

| 2    | dc3    | Enables DC disconnect on port 3  |  |  |  |

| 3    | dc4    | Enables DC disconnect on port 4  |  |  |  |

| 4    | e-ac1  | Emulates AC disconnect on port 1 |  |  |  |

| 5    | e-ac2  | Emulates AC disconnect on port 2 |  |  |  |

| 6    | e-ac3  | Emulates AC disconnect on port 3 |  |  |  |

| 7    | e-ac4  | Emulates AC disconnect on port 4 |  |  |  |

#### dcenr (Address 14h): Detect and Class Enable Register.

This is a Read/Write register; that enables the PD signature and classification on each port. These bits can also be set by writing to the "detar" register (18h). The behaviour of this port will depend on the settings on the "omr" register (12h).

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| cep4  | сер3  | cep2  | cep1  | dep4  | dep3  | dep2  | dep1  |

| Bits | Symbol | Description                      |

|------|--------|----------------------------------|

| 0    | dep1   | Enable signature on port 1*      |

| 1    | dep2   | Enable signature on port 2*      |

| 2    | dep3   | Enable signature on port 3*      |

| 3    | dep4   | Enable signature on port 4*      |

| 4    | cep1   | Enable classification on port 1* |