# STT-MRAM Datasheet PM002MNIA

Version:1.3

Nov. 2022

Shanghai Siproin Microelectronics

http://www.siproin.com

# **Table of Contents**

| 1   |        | res                                |                 |

|-----|--------|------------------------------------|-----------------|

| 2   | Pin In | formation                          | 2               |

|     | 2.1    | SOP8                               | 2               |

| 3   | Pin D  | escription                         |                 |

| 4   |        | tion Flow                          |                 |

| 5   | SPI m  | ode commands                       | . 4             |

| -   | 5.1    | Control Command Operation          | 5               |

|     | 5.2    | Reset Operation                    | 5               |

|     | 5.3    | Mode Register Write Command Timing | 5<br>6          |

|     | 5.4    | Mode Register Read Command Timing  | o               |

|     | 5.5    | SPI Write Command Timing           | o<br>6          |

|     | 5.6    | SPI Read Command Timing            |                 |

|     | 5.7    | SPI QuadWrite Command Timing       | . /<br>Q        |

|     | 5.8    | SPI QuadRead Command Timing        | o<br>Q          |

|     | 5.9    | SPI Unique ID Operation            | o               |

| 6   |        | node commands                      | ラ<br>10         |

| 6   | 6.1    | Control Command Operation          | 10              |

|     | 6.2    |                                    |                 |

|     |        | Reset Operation                    | 11              |

|     | 6.3    | Mode Register Write Command Timing | 11              |

|     | 6.4    | Mode Register Read Command Timing  | 12              |

|     | 6.5    | QPI Write Command Timing           | 13              |

|     | 6.6    | QPI Read Command Timing            | 14              |

| _   | 6.7    | QPI Unique ID Operation            | 14              |

| 7   |        | Register Definition                | 15              |

|     | 7.1    | Mode Register#1 (MR#1)             | 15              |

|     | 7.2    | Mode Register#2 (MR#2)             | 16              |

|     | 7.3    | Mode Register#3 (MR#3)             | 16              |

| 8   | Power  | r Mode                             |                 |

|     | 8.1    | Power-on                           | 17              |

|     | 8.2    | Sleep                              | 18              |

|     | 8.3    | Wake-up                            | 18              |

| 9   | Input/ | Output Timing                      | 18              |

| 10  | Electr | ical Specifications                | 19              |

| 11  | DC/A   | C characteristic                   | 19              |

|     | 11.1   | Operating Conditions               |                 |

|     | 11.2   | DC Characteristics                 | 20              |

|     | 11.3   | Pin Capacitance                    |                 |

|     | 11.4   | AC Characteristics                 | $\frac{-1}{21}$ |

|     | 11.5   | Power Up Timing                    | $\frac{1}{2}$   |

| 12  | _      | Information                        |                 |

| 13  |        | ge Outline Drawing                 |                 |

| 1 ) |        | nent Revision History              |                 |

|     | Docui  | 11011t 1XC v 151011 1115t01 y      | ∠∪              |

#### 1 Features

The PM002M is Mbit of SPI/QPI (serial/quad parallel interface) MRAM device. This device is configurable as 1 bit I/O separate or 4 bits I/O common interface. The PM002M has MRAM technology in memory array. The data in the memory array will be sustained with data retention greater than 20 years.

#### **Density**

2Mbits

#### **Fast SPI interface**

- Up to 50MHz clock frequency @SPI SDR

- Up to 50MHz clock frequency @QPI SDR

- Support standard SPI, Quad SPI mode

- Write no delay

- Support SPI mode0 and mode3

#### Single voltage operation

• Typical Voltage: 3.3V Vcc=2.7V~3.6V

#### **Data protection**

• Software protection mode with BP0,BP1 in mode register#1

#### **Power consumption**

- Sleep current 2uA (Typical value)

- Standby current 2mA (Typical value)

- Active current 4.3mA (Typical value @SPI 50MHz)

#### Reliability

- Data retention >20years @85°C

- P/E cycle up to 108

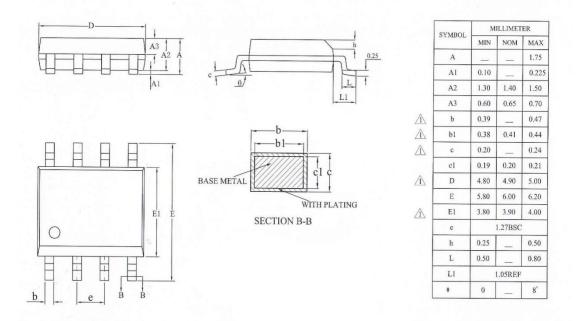

#### **Package**

• SOP8\_150MIL

#### Temperature range

Junction temperature: -40°C~85°C

1

# 2 Pin Information

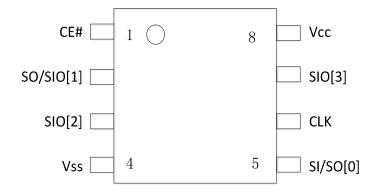

#### 2.1 SOP8

Figure 1: Package Information

# 3 Pin Description

**Table1: Pin Description**

| Symbol    | Signal Type | SPI Mode                                                                            | QPI Mode |  |

|-----------|-------------|-------------------------------------------------------------------------------------|----------|--|

| СЕ#       | Input       | Chip select signal, Active low. When CE in is high, Memory will be in standby state |          |  |

| SO/SIO[1] | I/O         | Serial output I/O[1]                                                                |          |  |

| SIO[2]    | I/O         | I/O[2]* I/O[2]                                                                      |          |  |

| Vss       | Ground      | Core Supply Ground                                                                  |          |  |

| SI/SO[0]  | I/O         | Serial intput                                                                       | I/O[0]   |  |

| CLK       | Input       | Clock Signal                                                                        |          |  |

| SIO[3]    | I/O         | I/O[3]* I/O[3]                                                                      |          |  |

| Vcc       | Power       | Core Power Supply                                                                   |          |  |

<sup>\*</sup>Fast read Quad access and Quad write access in SPI Mode use SIO[2] and SIO[3]; Recommend to pull down Vcc or to GND if no use of SIO[2] and SIO[3] in SPI Mode;

# 4 Operation Flow

According SPI protocol, the first 8 bits of DI is COMMAND (op\_code), which define which operation the memory will do. The following 24bits (3 bytes) are address phase, which defined the memory array row address and column address. According current array density, PM002M use 17 of 24 address to feed in memory address, and left spare MSB bit with '0'.

Every command sequence starts with a one-byte command code. Depending on the command, this might be followed by 3-byte (24-bit) address plus dummy cycles and data byte(s).

All commands, addresses, and dummy bits are shifted in of the PM002M device with the most significant bit first. The data bits are also shifted in or out of the PM002M with the most significant bit.

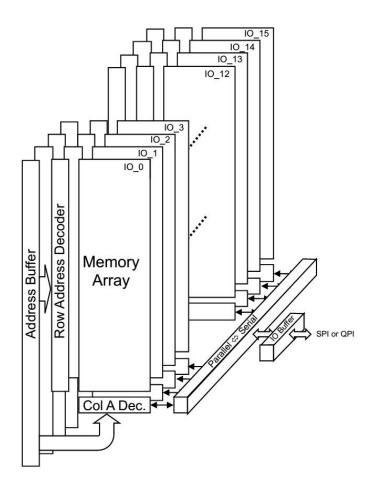

The figure below explains relation between internal memory array organization and external I/O. This device has 16 internal I/O plates. Once memory read or write operation starts, these 16 internal I/O plates works parallelly. Because of this internal memory plates organization, the minimum burst access for read or write operation becomes 2 Bytes access.

Figure 2: Operation Flow

# 5 SPI mode commands

**Table 2: SPI Mode Commands**

| C1                  |       |         |         | SPI M   | lode        |          |         |

|---------------------|-------|---------|---------|---------|-------------|----------|---------|

| Command             | Byte1 | Byte2   | Byte3   | Byte4   | Byte5       | Byte6    | Byte7   |

| Number of Clocks    | 8     | 8(or 2) | 8(or 2) | 8(or 2) | 8(or 2)     | 8(or 2)  | 8(or 2) |

| Mode Register Write | B1H   | A23-A16 | A16-A8  | A7-A0   | Value#n     |          |         |

| Mode Register Read  | В5Н   | A23-A16 | A16-A8  | A7-A0   | Value#n     |          |         |

| Write               | 02H   | A23-A16 | A16-A8  | A7-A0   | D15-D8      | D7-D0    |         |

| Quad Write          | 38H   | A23-A16 | A16-A8  | A7-A0   | D15-D8      | D7-D0    |         |

| Read                | 03H   | A23-A16 | A16-A8  | A7-A0   | Dummy(0~12) | D15-D8   | D7-D0   |

| Quad Read           | EBH   | A23-A16 | A16-A8  | A7-A0   | Dummy(0~12) | D15-D8   | D7-D0   |

| Write Enable        | 06H   |         |         |         |             |          |         |

| Write Disable       | 04H   |         |         |         |             |          |         |

| Entry To Deep       |       |         |         |         |             |          |         |

| PowerDown           | В9Н   |         |         |         |             |          |         |

| Exit From Deep      |       |         |         |         |             |          |         |

| PowerDown           | ABH   |         |         |         |             |          |         |

| Read Unique ID      | 9FH   | 0H      | 0H      | 0H      |             | 16 Bytes |         |

| Register            | 7111  | OII     | OII     | 011     |             | 10 Bytes |         |

| Enter QPI Mode      | 35H   |         |         |         |             |          |         |

| Reset Enable        | 66H   |         |         |         |             |          |         |

| Reset               | 99H   |         |         |         |             |          |         |

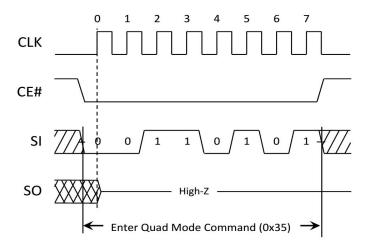

## **5.1 Control Command Operation**

Control command include WriteEnable,WriteDisable,Entry To Sleep,Exit From Sleep,

Enter QPI Mode. For example Enter QPI Mode:

Figure 3: Enter QPI Command Timing

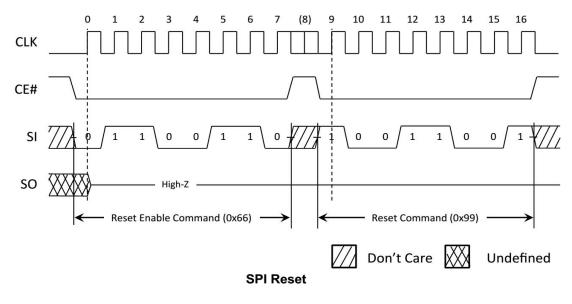

## **5.2 Reset Operation**

**Figure 4: SPI Reset Operation Timing**

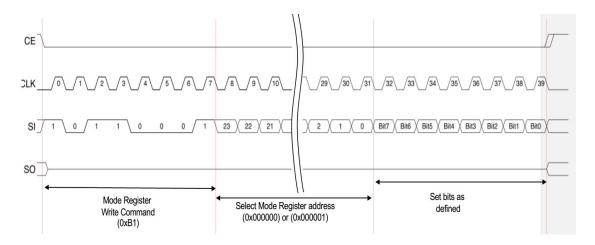

## 5.3 Mode Register Write Command Timing

Figure 5: SPI Mode Register Write Command Timing

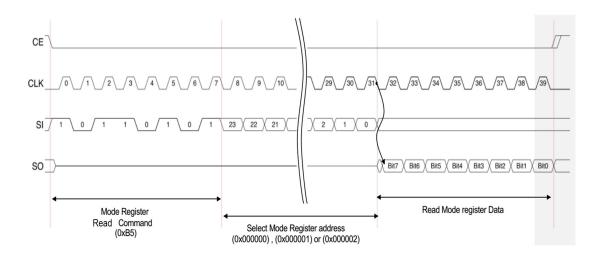

## 5.4 Mode Register Read Command Timing

Figure 6: SPI Mode Register Read Command Timing

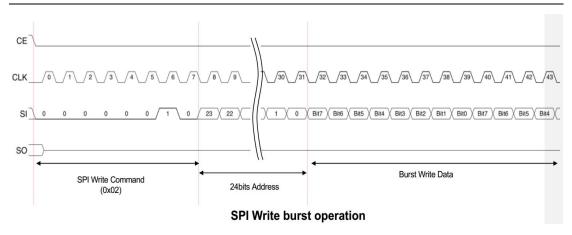

#### 5.5 SPI Write Command Timing

The first byte(Bit7~Bit0) means IO 15~IO 8, the followed byte(Bit7~Bit0) means IO 7~IO 0.

Figure 7: SPI Write Command Timing

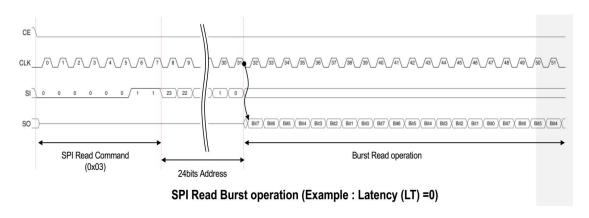

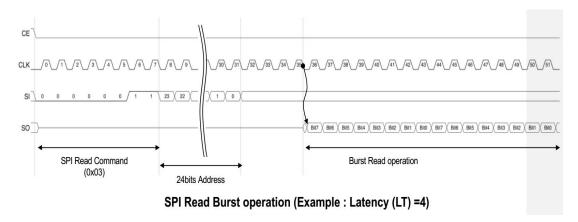

# 5.6 SPI Read Command Timing

The first byte(Bit7~Bit0) means IO\_15~IO\_8, the followed byte(Bit7~Bit0) means IO\_7~IO\_0 .

Figure 8: SPI Read Command Timing (Example: Latency(LT)=0)

Figure 9: SPI Read Command Timing (Example: Latency(LT)=4)

#### 5.7 SPI QuadWrite Command Timing

The first byte(Bit7~Bit0) means IO\_15~IO\_8, the followed byte(Bit7~Bit0) means IO\_7~IO\_0 .

**SPI Quad Write burst operation**

Figure 10: SPI QuadWrite Command Timing

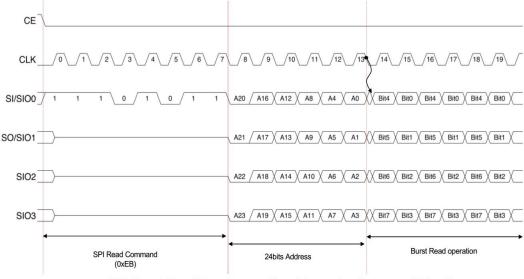

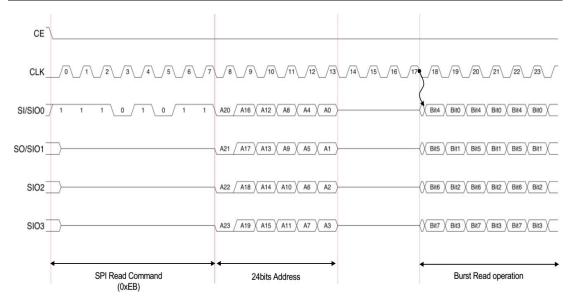

#### 5.8 SPI QuadRead Command Timing

The first byte(Bit7~Bit0) means IO\_15~IO\_8, the followed byte(Bit7~Bit0) means IO\_7~IO\_0 .

SPI Quad Read Burst operation (Example : Latency (LT) =0)

Figure 11: SPI QuadRead Command Timing (Example: Latency(LT)=0)

SPI Quad Read Burst operation (Example : Latency (LT) =4)

Figure 12: SPI QuadRead Command Timing (Example: Latency(LT)=4)

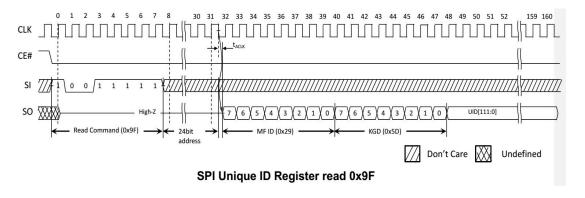

## 5.9 SPI Unique ID Operation

The two bytes are used for Manufacture ID (0x29, 0x55) and the two bytes can be read by SPI instruction.

Figure 13: SPI Unique ID Read Command Timing

# 6 QPI mode commands

**Table 3: QPI Mode Commands**

| C                   | QPI Mode |         |        |       |             |         |       |  |

|---------------------|----------|---------|--------|-------|-------------|---------|-------|--|

| Command             | Byte1    | Byte2   | Byte3  | Byte4 | Byte5       | Byte6   | Byte7 |  |

| Number of Clocks    | 2        | 2       | 2      | 2     | 2           | 2       | 2     |  |

| Mode Register Write | B1H      | A23-A16 | A16-A8 | A7-A0 | Value#n     |         |       |  |

| Mode Register Read  | В5Н      | A23-A16 | A16-A8 | A7-A0 | Dummy(2)    | Value#n |       |  |

| Write               | 02H      | A23-A16 | A16-A8 | A7-A0 | D15-D8      | D7-D0   |       |  |

| Read                | 03H      | A23-A16 | A16-A8 | A7-A0 | Dummy(0~12) | D15-D8  | D7-D0 |  |

| Write Enable        | 06H      |         |        |       |             |         |       |  |

| Write Disable       | 04H      |         |        |       |             |         |       |  |

| Entry To Deep       |          |         |        |       |             |         |       |  |

| PowerDown           | В9Н      |         |        |       |             |         |       |  |

| Exit From Deep      |          |         |        |       |             |         |       |  |

| PowerDown           | ABH      |         |        |       |             |         |       |  |

| Read Unique ID      | 9FH      | 0H      | 0H     | 0H    | 16 Bytes    |         |       |  |

| Register            | 91.11    | 011     | 011    | 011   | 1,          |         |       |  |

| Exit QPI Mode       | F5H      |         |        |       |             |         |       |  |

| Reset Enable        | 66H      |         |        |       |             |         |       |  |

| Reset               | 99H      |         |        |       |             |         |       |  |

At power up, QPI mode is disabled.

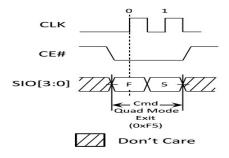

## **6.1 Control Command Operation**

Control command include Write Enable, Write Disable, Entry To Sleep, Exit From Sleep,

Exit QPI Mode. For example Exit QPI Mode:

Figure 14: Exit QPI Command Timing

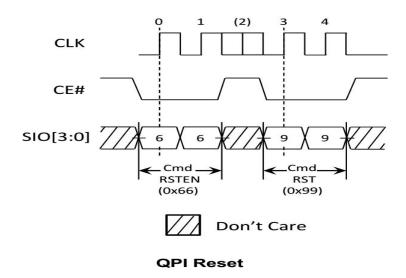

## **6.2 Reset Operation**

**Figure 15: QPI Reset Operation Timing**

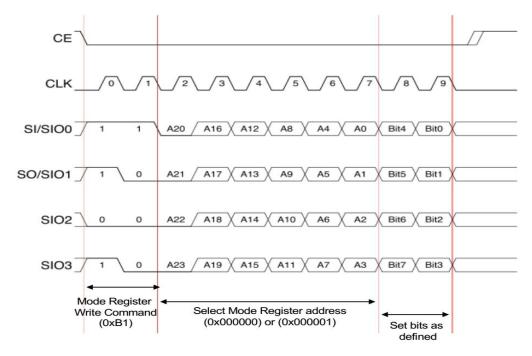

## 6.3 Mode Register Write Command Timing

Figure 16: QPI Mode Register Write Command Timing

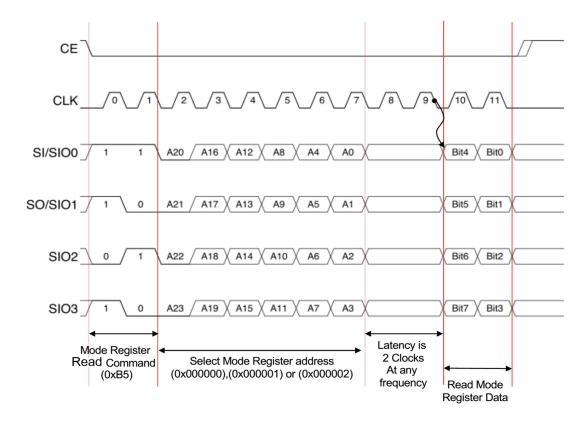

## 6.4 Mode Register Read Command Timing

Figure 17: QPI Mode Register Read Command Timing

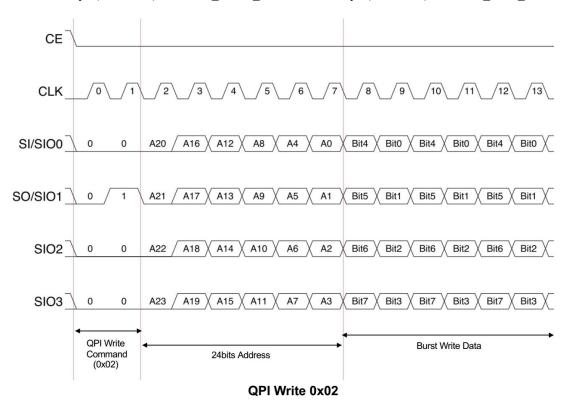

## 6.5 QPI Write Command Timing

The first byte(Bit7~Bit0) means IO\_15~IO\_8, the followed byte(Bit7~Bit0) means IO\_7~IO\_0 .

Figure 18: QPI Write Command Timing

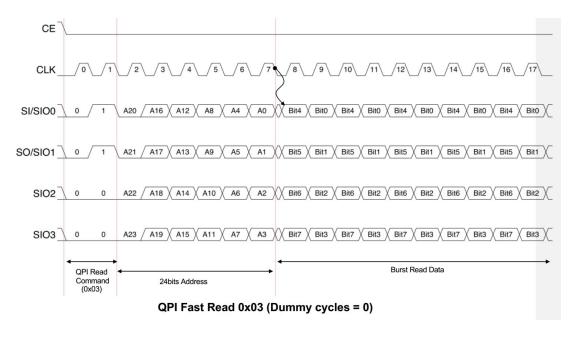

## 6.6 QPI Read Command Timing

The first byte(Bit7~Bit0) means IO\_15~IO\_8, the followed byte(Bit7~Bit0) means IO\_7~IO\_0 .

Figure 19: QPI Read Command Timing (Example: Dummy cycles=0)

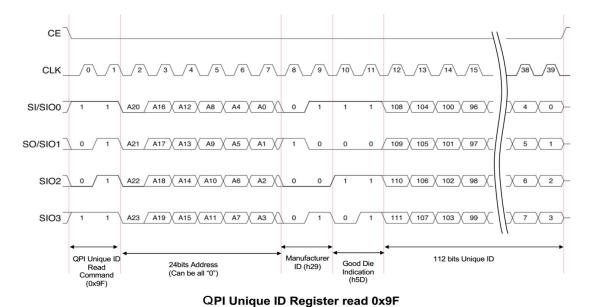

## 6.7 QPI Unique ID Operation

The two bytes are used for Manufacture ID (0x29, 0x55) and the two bytes can be read by SPI instruction.

Figure 20: QPI Unique ID Read Command Timing

# 7 Mode Register Definition

For PM002M chip, three Mode Registers are provided, that are, MR1, MR2,MR3. Each register is accessed by MRWR and MRRD commands combined with 3-Bytes Register Address and 1-Byte Value respectively.

Table 4: Mode Register Definition

|      | Address | Feature Da | Feature Data Bits Definition |    |      |      |     |     |   | Note |

|------|---------|------------|------------------------------|----|------|------|-----|-----|---|------|

|      |         | 7          | 6                            | 5  | 4    | 3    | 2   | 1   | 0 |      |

| MR#1 | 0x0000  | MRWD       |                              | -  |      | BP1  | BP0 | WEC |   | RW   |

| MR#2 | 0x0001  |            |                              | 1  | LT1  | LT0  |     | -   |   | RW   |

| MR#3 | 0x0002  |            | D1                           | D0 | REV1 | REV0 |     |     |   | R    |

#### 7.1 Mode Register#1 (MR#1)

This register defines Write protection function. When this device will be used as partial nonvolatile memory. There are protected area and unprotected area which are defined by BP1(Bit3) and BP0 (Bit2). The combination of MRWD(Bit7) and WEC(Bit1) defines how write protection applies to those protected area, unprotected area and Mode Register.

**Table 5: Write Protection Combination**

| WEC | MRWD | Protected area | Unprotected area | Mode<br>Register | Note    |

|-----|------|----------------|------------------|------------------|---------|

| 0   | 0    | Writable       | Writable         | Writable         | Default |

| 0   | 1    | Protected      | Writable         | Protected        |         |

| 1   | 0    | Protected      | Writable         | Writable         |         |

| 1   | 1    | Protected      | Protected        | Protected        |         |

Table 6: Protected and unprotected area

| BP1 | BP0 | Protected area | Unprotected area | Note    |

|-----|-----|----------------|------------------|---------|

| 0   | 0   | None           | ALL              | Default |

| 0   | 1   | Upper 1/4      | Lower 3/4        |         |

| 1   | 0   | Upper 1/2      | Lower 1/2        |         |

| 1   | 1   | ALL            | None             |         |

Note : Lower half is h[00FFFF]~h[000000], and Higher half is h[01FFFF]~h[010000] Lower 1/4 means h[007FFF]~h[000000]. Lower 3/4 means h[017FFF]~h[000000]

## 7.2 Mode Register#2 (MR#2)

MR#2 defines Read operation. Especially, the latency (number of dummy cycles) between the end of read address input to the first data output in Bit4 and Bit3.

The default value of other RFU bits in MR#2 are "0".

**Table 7: Read Latency definition**

| LT1 | LT0 | Number of<br>Dummy<br>Clock | Max Clock<br>Frequency<br>(SPI Mode) | Max Clock<br>Frequency<br>(QPI Mode) | Note    |

|-----|-----|-----------------------------|--------------------------------------|--------------------------------------|---------|

| 0   | 0   | 0                           | 50Mhz                                | 50Mhz                                | Default |

| 0   | 1   | 4                           | 50Mhz                                | 50Mhz                                |         |

| 1   | 0   | 8                           | 50Mhz                                | 50Mhz                                |         |

| 1   | 1   | 12                          | 50Mhz                                | 50Mhz                                |         |

#### 7.3 Mode Register#3 (MR#3)

MR#3 defines density of the products and revision of the products.

D1 and D0 bits in Bit6 and 5 in MR#3 define memory density of this device. Bit4 and 3 in MR#3 define revision of the device. The default value of other RFU bits in MR#3 are "0".

**Table 8: Density Bits**

| D1 | D0 | Density | Note    |

|----|----|---------|---------|

| 0  | 0  | 2Mbit   | Default |

| 0  | 1  | RFU     |         |

| 1  | 0  | RFU     |         |

| 1  | 1  | RFU     |         |

**Table 9: Revision**

| Rev1 | Rev0 | Revision | Note    |

|------|------|----------|---------|

| 0    | 0    | 0        | Default |

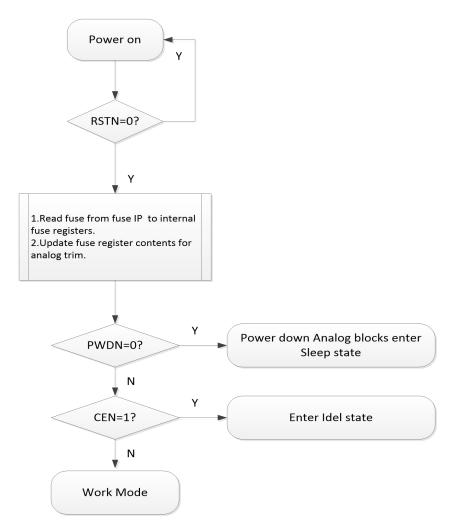

## 8 Power Mode

This device provides four kind of low power mode, Read, Write, Standby, Sleep.

During normal work mode, there are read and write. when CE# high, the arrays enter into the Standby mode, which internal regular are still on, but the device cannot receive the command and the data in SI/SO will be not available. When host issue EntryToSleep command, the device will enter into the Sleep mode, in this situation, the internal logic and voltage regular will be off, when host issue the ExitFromSleep command, the device will execute the wake-up sequence to the Standby mode.

This device has four states, that is power-on sequence, normal work mode, sleep mode and wake-up sequence

#### 8.1 Power-on

When powering on, the power-on sequence begins, it is composed of three stage as below:

Analog block active

#### **Fuse-recall**

During this stage, the device internal logic loads the fuse bits form EFUSE to trim registers..

#### Analog block ready

In Fuse-recall stage, the analog blocks' trim bits are updated by fuse registers, and it takes some times to stable..

#### 8.2 Sleep

Sleep is a low power mode. During this mode, all internal regulators were closed to saving the power consumption. Host can issue command EntryTo Sleep to make device enter into this stage.

#### 8.3 Wake-up

Wake-up make the internal analog blocks active It doesn't need do initialization like fuse-recall, only need analog modules stable stage.

# 9 Input/Output Timing

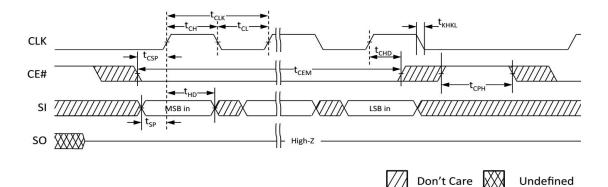

Figure 22: Input Timing

Figure 23: Output Timing

# 10 Electrical Specifications

This device contains circuitry to protect the inputs against damage caused by high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage greater than maximum rated voltages to these high-impedance (Hi-Z) circuits.

The device also contains protection against external magnetic fields. Precautions should be taken to avoid application of any magnetic field more intense than the maximum field intensity specified in the maximum ratings.

**Table 10: Electrical Specifications**

| Symbol        | Parameter                                     | Conditions       | Value       | Unit |

|---------------|-----------------------------------------------|------------------|-------------|------|

| Vcc           | Supply Voltage                                |                  | -0.5 to 4   | V    |

| Vin           | Voltage on any pin                            |                  | -0.5 to Vcc | V    |

| Iout          | Output current per pin                        | ±4               | mA          |      |

| Tbias         | Temperature under bias                        | Commercial Grade | -40 to 85   | °C   |

| Tstg          | Storage Temperature                           | -55 to 125       | °C          |      |

| Tlead         | Lead temperature during solder(               | 260              | °C          |      |

| Hmax_write    | Maximum magnetic field during write           | Write            | 4,000       | A/m  |

| Hmax_read     | Maximum magnetic field during read or standby | Read or Standby  | 40,000      | A/m  |

| Hmax_poweroff | Maximum magnetic field during power off       | Power off        | 40,000      | A/m  |

<sup>\*</sup>Note1:We recommend programming of the device after reflow. Data written before reflow cannot be guaranteed

WARNING:Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, magnetic etc.) in excess of absolute maximum ratings. Do not exceed these ratings. Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet.

## 11 DC/AC characteristic

This section presents the DC and AC characteristics of the device. The values for the DC and AC parameters indicated in the following tables are derived from tests under the operating and measurement conditions also indicated in the relevant tables. Designers should be aware that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

# 11.1 Operating Conditions

**Table 11: Operating Conditions**

| Symbol | Parameter                         | Min | Max | Unit |

|--------|-----------------------------------|-----|-----|------|

| Vcc    | Voltage Supply                    | 2.7 | 3.6 | V    |

| Tax    | Operating Temperature(commercial) | -40 | 85  | °C   |

## 11.2 DC Characteristics

**Table 12: DC Characteristics**

| Symbol           | Parameter              | <b>Test Conditions</b> |             | Min  | Typ. | Max     | Uni |

|------------------|------------------------|------------------------|-------------|------|------|---------|-----|

| Ili              | Input leakage current  |                        |             |      |      | ±1      | μА  |

| Ilo              | Output Leakage current |                        |             |      |      | ±1      | μА  |

| Islp             | Sleep Current          |                        |             |      | 2    | 13      | uA  |

| I <sub>SBY</sub> | Standby current        |                        |             |      | 2    | 2.7     | mA  |

| Icc              | Active Current S       |                        | CLK = 1MHz  |      | 2.25 |         | mA  |

|                  |                        |                        | CLK = 10MHz |      | 2.5  |         | mA  |

|                  |                        |                        | CLK = 20MHz |      | 3    | 4.8     | mA  |

|                  |                        | CLK = 50MHz            |             | 4.3  | 6.9  | mA      |     |

|                  |                        | QPI<br>Write/Read      | CLK = 1MHz  |      | 2.5  |         | mA  |

|                  |                        | ,, Inc. Read           | CLK = 10MHz |      | 4    |         | mA  |

|                  |                        |                        | CLK = 20MHz |      | 5    | 7       | mA  |

|                  |                        |                        | CLK = 50MHz |      | 7    | 9       | mA  |

| VIL              | Input low voltage      |                        |             | -0.3 |      | 0.8     | V   |

| VIH              | Input high voltage     |                        |             | 2.0  |      | Vcc+0.3 | V   |

| Vol              | Output low voltage     | IoL = 4mA              |             |      |      | 0.4     | V   |

| Voh              | Output high voltage    | I <sub>OH</sub> = -4mA |             | 2.4  |      |         | V   |

## 11.3 Pin Capacitance

**Table 13: Pin Capacitance**

| Symbol | Parameter                          | Typical | Max | Unit |

|--------|------------------------------------|---------|-----|------|

| Cp*    | VCC/VSS power external capacitance |         | 10  | uF   |

| Cin    | Control input capacitance          | -       | 8   | pF   |

| Сю     | IO capacitance                     | -       | 12  | pF   |

| CLOAD  | Load capacitance                   | -       | 32  | pF   |

\*Note: The external capacitor Cp at the Vcc/Vss is recommended  $\leq 10\mu F$ ; If Cp >  $10\mu F$ , reading datas may be unstable when Vcc return to the normal operating voltage from power down. In this case, for the datas are read reliably, suggest to operate the highest address to write ID(0x29, 0x55) data within the specified working voltage range, and then confirm this ID data before operating on the chip. If the ID data is wrong, need to send 0xB9 (sleep) and 0xAB (wake-up),so the chip will be read reliably; Otherwise, when power up and down frequently, the hardware circuit ensures that the chip starting voltage is lower than Vs (0.3V), when Vcc up from down.

#### 11.4 AC Characteristics

**Table 14: AC Characteristics**

| Ck.l    | December                           | 50Mhz |     | TI.*4 |

|---------|------------------------------------|-------|-----|-------|

| Symbol  | Parameter                          |       | Max | Unit  |

| tCLK    | CLK period                         | 20    |     | ns    |

| tCH/tCL | Clock high/low width               |       |     | ns    |

| tKHKL   | CLK rise or fall time              |       | 1.5 | ns    |

| tCPH    | CE# High between subsequent burst  |       |     | ns    |

| tCSP    | CE# Setup time to CLK rising edge  |       |     | ns    |

| tCHD    | CE# Hold time from CLK rising edge |       |     | ns    |

| tSP     | Setup time to active CLK edge      |       |     | ns    |

| tHD     | Hold time from active CLK edge     |       |     | ns    |

| tHZ     | Chip disable to DQ output high-Z   |       | 6   | ns    |

| tACLK  | CLK to output delay                         | 8   | 10 | ns |

|--------|---------------------------------------------|-----|----|----|

| tKOH   | Data hold time from clock falling edge      | 1.5 |    | ns |

| tRST   | Reset recovery time after Operation command | 150 |    | us |

| tESLP  | Sleep entry time from Sleep command         |     | 40 | us |

| tRSLP  | Recovery time from Sleep exit command       | 1   |    | ms |

| tERSLP | Sleep entry to exit command                 | 1   |    | ms |

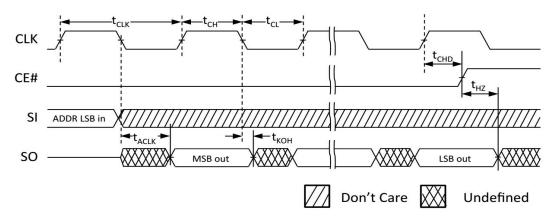

#### 11.5 Power Up Timing

To provide protection for data during initial power up, power loss or brownout, when ever  $V_{cc}$  falls below VCC (min) the device cannot be selected (CE# is restricted from going low) and the device is inhibited from Read or Write operations.

#### **Power Up Delay Time**

During initial power up or when recovering from brownout or power loss, a power up delay time (tPU) must be added from their specified minimum voltages (Vcc(min)) to normal operations may commence. This time is required to insure that the device internal voltages have stabilized.

tPU is measured from the time that Vcc have reached their specified minimum voltages. and the device will finish fuse-recall and analog blocks are stable to work.

Table 15: Power-Up Initial Voltages and Delay Timing

| Symbol | Parameter             | Min | Max | Unit |

|--------|-----------------------|-----|-----|------|

| Vs     | Chip Starting Voltage | -   | 0.3 | V    |

| t PU   | Power Up delay time   | 1.5 | -   | ms   |

Figure 24: Power-Up Timing and Voltage Levels

# 12 Order Information

| Orderable Device | Density | Typical voltage | Interface | Package<br>Type | Op Temp(℃) | Package<br>Qty |

|------------------|---------|-----------------|-----------|-----------------|------------|----------------|

| PM002MNIATU      | 2Mbits  | 3.3V            | SPI/QPI   | SOP8_150mil     | -40 to 85  | 100/Tube       |

| PM002MNIATR      | 2Mbits  | 3.3V            | SPI/QPI   | SOP8_150mil     | -40 to 85  | 2500/Reel      |

# Top Side Marking

Type: PM002MNI Version: A

Y: Year WW:Week

# 13 Package Outline Drawing

Figure 25: Package Outline for SOP8 150MIL

#### **Document Revision History**

| Version | Date       | Author | Brief Description of Changes                     |

|---------|------------|--------|--------------------------------------------------|

| V1.0    | 2022-05-05 | Ding   | Define Max Frequency, modify Feature/DC/AC,      |

|         |            |        | parameter, cancel ddr read/write timing          |

| V1.1    | 2022-05-24 | Ding   | modify Electrical Specifications, modify Note    |

|         |            |        | on Use, modify Package description               |

| V1.2    | 2022-08-22 | Justin | modify Vin description in Table10, Delete Vccq   |

|         |            |        | description in Table11, modify Table15 and       |

|         |            |        | Figure24                                         |

| V1.3    | 2022-11-01 | Justin | Modify ID(0x29, 0x55) description in Chapter 5.9 |

|         |            |        | and Chapter 5.9, Modify Hmax_read description in |

|         |            |        | Table10,                                         |

|         |            |        | define tRST in Table14,modify Chapter 11.3,      |

|         |            |        | modifyChapter 11.5                               |

#### **DISCLAIMER**

The information in the usage specification is correct at the time of publication, Siproin has the right to change and interpret the specification, and reserves the right to modify the product without prior notice. Users can obtain the latest version information from our Company website or other effective channels before confirmation, and confirm the relevant information is complete and up to date. With any semiconductor product, there is a certain possibility of failure or failure under certain conditions. The buyer is responsible for complying with safety standards and taking safety measures when using the product for system design and complete machine manufacturing. The product is not authorized to be used as a critical component in life-saving or life-sustaining products or systems, in order to avoid potential failure risks that may cause personal injury or property loss.

Siproin hereby provides the quality information to you but makes no claims, promises or guarantees about the accuracy, completeness, or adequacy of the information herein. The information contained herein is provided on an "AS IS" basis without any warranty, and Siproin assumes no obligation to provide support of any kind or otherwise maintain the information. Siproin disclaims any representation that the information does not infringe any intellectual property rights or proprietary rights of any third Parties.

#### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by Siproin manufacturer:

Other Similar products are found below:

CY6116A-35DMB GS8161Z36DD-200I RMLV0408EGSB-4S2#AA0 IS64WV3216BLL-15CTLA3 IS66WVE4M16ECLL-70BLI K6T4008C1B-GB70 AS6C8016-55BIN AS7C164A-15PCN MT48LC4M16A2TG-7E IS66WVE2M16ECLL-70BLI IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC CY7C1460KV25-200BZI CY7C1373KV33-100AXC CY7C1381KVE33-133AXI CY7C1382KV33-167AXC CY7C4121KV13-600FCXC 8602501XA 5962-3829430MUA 5962-8866201YA 5962-9062007MXA 70T3519S133BC GS882Z18CD-150I 8413202RA 5962-8866208YA 5962-8866203YA IS66WVC2M16ECLL-7010BLI 7140LA35PDG CY7C1382KV33-200AXC CY7C1380KV33-250AXC AS6C8016-55BINTR CY7C1373KV33-133AXI AS7C34096B-10TIN AS6C8016-55TIN IS62WV25616EALL-55TLI CY7C1460KV25-200BZXI CY7C1460KV25-167BZXI 71421LA55JI8 CY62158G30-45ZSXI CY62157G30-45ZXI IS66WVC2M16EALL-7010BLI R1LP0108ESN-5SI#S1 R1LV0216BSB-5SI#S1 R1LP0408DSB-5SI#S1 RMLV0408EGSA-4S2#KA1 M68AW031AM70N6E M68AW127BM70NK6 PM002MNIATR 71V016SA15YGI8