High Frequency, Single Chip, SOT23 Oscillator

### Features

- Any frequency between 115 MHz to 137 MHz accurate to 6 decimal places of accuracy

- Operating temperature from -40°C to 85°C. Refer to SiT2019 for -40°C to 125°C and SiT2021 for -55°C to 125°C options

- Excellent total frequency stability as low as ±20 PPM

- Low power consumption of 4.9 mA typical at 1.8V

- LVCMOS/LVTTL compatible output

- 5-pin SOT23-5: 2.9 mm x 2.8 mm

- RoHS and REACH compliant, Pb-free, Halogen-free and Antimony-free

- For AEC-Q100 oscillators, refer to SiT2024 and SiT2025

## **Electrical Specifications**

### Table 1. Electrical Characteristics

### **Applications**

- GEPON, network switches, routers, servers, embedded systems, industrial and medical devices

- Ethernet, PCI-E, DDR, etc.

All Min and Max limits are specified over temperature and rated operating voltage with 15 pF output load unless otherwise stated. Typical values are at 25°C and nominal supply voltage.

| Parameters                  | Symbol                        | Min. | Тур.        | Max.       | Unit        | Condition                                                                                               |  |  |  |  |

|-----------------------------|-------------------------------|------|-------------|------------|-------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

|                             |                               |      |             | Frequency  | Range       |                                                                                                         |  |  |  |  |

| Output Frequency Range      | f                             | 115  | -           | 137        | MHz         |                                                                                                         |  |  |  |  |

|                             | Frequency Stability and Aging |      |             |            |             |                                                                                                         |  |  |  |  |

| Frequency Stability         | F_stab                        | -20  | -           | +20        | PPM         | Inclusive of Initial tolerance at 25°C, 1st year aging at 25°C, and                                     |  |  |  |  |

|                             |                               | -25  | -           | +25        | PPM         | variations over operating temperature, rated power supply voltage and load (15 pF $\pm$ 10%).           |  |  |  |  |

|                             |                               | -50  | -           | +50        | PPM         |                                                                                                         |  |  |  |  |

|                             |                               |      | Opera       | ting Tempe | erature Rai | nge                                                                                                     |  |  |  |  |

| Operating Temperature Range | T_use                         | -20  | -           | +70        | °C          | Extended Commercial                                                                                     |  |  |  |  |

| (Ambient)                   |                               | -40  | -           | +85        | °C          | Industrial                                                                                              |  |  |  |  |

|                             |                               | S    | upply Volta | age and Cu | irrent Cons | sumption                                                                                                |  |  |  |  |

| Supply Voltage              | Vdd                           | 1.62 | 1.8         | 1.98       | V           |                                                                                                         |  |  |  |  |

|                             |                               | 2.25 | 2.5         | 2.75       | V           |                                                                                                         |  |  |  |  |

|                             |                               | 2.52 | 2.8         | 3.08       | V           |                                                                                                         |  |  |  |  |

|                             |                               | 2.7  | 3.0         | 3.3        | V           |                                                                                                         |  |  |  |  |

|                             |                               | 2.97 | 3.3         | 3.63       | V           |                                                                                                         |  |  |  |  |

|                             |                               | 2.25 | -           | 3.63       | V           |                                                                                                         |  |  |  |  |

| Current Consumption         | ldd                           | -    | 6.2         | 7.5        | mA          | No load condition, f = 125 MHz, Vdd = 2.8V, 3.0V, 3.3V or 2.25 to 3.63V                                 |  |  |  |  |

|                             |                               | I    | 5.5         | 6.4        | mA          | No load condition, $f = 125 \text{ MHz}$ , Vdd = 2.5V                                                   |  |  |  |  |

|                             |                               | I    | 4.9         | 5.6        | mA          | No load condition, f = 125 MHz, Vdd = 1.8V                                                              |  |  |  |  |

| OE Disable Current          | I_od                          | -    | -           | 4.3        | mA          | Vdd = 2.5V to 3.3V, OE = Low, Output in high Z state                                                    |  |  |  |  |

|                             |                               | -    | -           | 4.1        | mA          | Vdd = 1.8V, OE = Low, Output in high Z state                                                            |  |  |  |  |

| Standby Current             | I_std                         | -    | 2.6         | 4.3        | μΑ          | Vdd = 2.8V to 3.3V, $\overline{ST}$ = Low, Output is weakly pulled down                                 |  |  |  |  |

|                             |                               | -    | 1.4         | 2.5        | μA          | Vdd = 2.5V, $\overline{ST}$ = Low, Output is weakly pulled down                                         |  |  |  |  |

|                             |                               | -    | 0.6         | 1.3        | μA          | Vdd = 1.8V, $\overline{ST}$ = Low, Output is weakly pulled down                                         |  |  |  |  |

|                             |                               |      | LVCMC       | S Output ( | Characteris |                                                                                                         |  |  |  |  |

| Duty Cycle                  | DC                            | 45   | -           | 55         | %           | All Vdds                                                                                                |  |  |  |  |

| Rise/Fall Time              | Tr, Tf                        | -    | 1.0         | 2.0        | ns          | Vdd = 2.5V, 2.8V, 3.0V or 3.3V, 20% - 80%                                                               |  |  |  |  |

|                             |                               | -    | 1.3         | 2.5        | ns          | Vdd =1.8V, 20% - 80%                                                                                    |  |  |  |  |

|                             |                               | _    | 1.0         | 2.0        | ns          | Vdd = 2.25V - 3.63V, 20% - 80%                                                                          |  |  |  |  |

| Output High Voltage         | VOH                           | 90%  | -           | -          | Vdd         | IOH = -4 mA (Vdd = 3.0V or 3.3V)<br>IOH = -3 mA (Vdd = 2.8V and Vdd = 2.5V)<br>IOH = -2 mA (Vdd = 1.8V) |  |  |  |  |

| Output Low Voltage          | VOL                           | -    | -           | 10%        | Vdd         | IOL = 4 mA (Vdd = 3.0V or 3.3V)<br>IOL = 3 mA (Vdd = 2.8V and Vdd = 2.5V)<br>IOL = 2 mA (Vdd = 1.8V)    |  |  |  |  |

### Table 1. Electrical Characteristics (continued)

| Parameters                 | Symbol   | Min. | Тур.  | Max.       | Unit       | Condition                                                                |

|----------------------------|----------|------|-------|------------|------------|--------------------------------------------------------------------------|

|                            |          |      | In    | put Chara  | cteristics |                                                                          |

| Input High Voltage         | VIH      | 70%  | -     | -          | Vdd        | Pin 1, OE or ST                                                          |

| Input Low Voltage          | VIL      | -    | -     | 30%        | Vdd        | Pin 1, OE or ST                                                          |

| Input Pull-up Impedance    | Z_in     | 50   | 87    | 150        | kΩ         | Pin 1, OE logic high or logic low, or $\overline{ST}$ logic high         |

|                            |          | 2    | -     | -          | MΩ         | Pin 1, ST logic low                                                      |

|                            |          |      | Start | up and Res | sume Timi  | ng                                                                       |

| Startup Time               | T_start  | -    | -     | 5          | ms         | Measured from the time Vdd reaches its rated minimum value               |

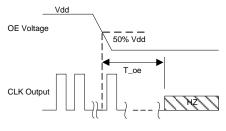

| Enable/Disable Time        | T_oe     | -    | -     | 130        | ns         | f = 115 MHz.<br>For other frequencies, T_oe = 100 ns + 3 * clock periods |

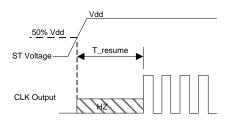

| Resume Time                | T_resume | -    | -     | 5          | ms         | Measured from the time $\overline{ST}$ pin crosses 50% threshold         |

|                            |          |      |       | Jitte      | er         |                                                                          |

| RMS Period Jitter          | T_jitt   | -    | 1.9   | 3          | ps         | f = 125 MHz, Vdd = 2.5V, 2.8V, 3.0V or 3.3V                              |

|                            |          | -    | 1.6   | 4          | ps         | f = 125 MHz, Vdd = 1.8V                                                  |

| Peak-to-peak Period Jitter | T_pk     | -    | 12    | 20         | ps         | f = 125 MHz, Vdd = 2.5V, 2.8V, 3.0V or 3.3V                              |

|                            |          | -    | 14    | 30         | ps         | f = 125 MHz, Vdd = 1.8V                                                  |

| RMS Phase Jitter (random)  | T_phj    | -    | 0.5   | 0.9        | ps         | Integration bandwidth = 900 kHz to 7.5 MHz                               |

|                            |          | -    | 1.3   | 2          | ps         | Integration bandwidth = 12 kHz to 20 MHz                                 |

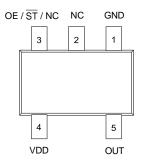

### **Table 2. Pin Description**

| Pin    | Symbol        | Functionality         |                                                                                                                                                            |  |  |  |

|--------|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1      | GND           | Power                 | Electrical ground                                                                                                                                          |  |  |  |

| 2      | NC            | No Connect No connect |                                                                                                                                                            |  |  |  |

| Output |               | Output Enable         | H <sup>[1]</sup> : specified frequency output<br>L: output is high impedance. Only output driver is disabled.                                              |  |  |  |

| 3      | 3 OE / ST /NC | Standby               | H or Open <sup>[1]</sup> : specified frequency output<br>L: output is low (weak pull down). Device goes to sleep mode.<br>Supply current reduces to I_std. |  |  |  |

|        |               | No Connect            | Any voltage between 0 and Vdd or Open <sup>[1]</sup> :<br>Specified frequency output. Pin 3 has no function.                                               |  |  |  |

| 4      | VDD           | Power                 | Power supply voltage <sup>[2]</sup>                                                                                                                        |  |  |  |

| 5      | OUT           | Output                | Oscillator output                                                                                                                                          |  |  |  |

### **Top View**

**Si**Time

### Figure 1. Pin Assignments

Notes:

In OE or ST mode, a pull-up resistor of 10 kΩ or less is recommended if pin 3 is not externally driven. If pin 3 needs to be left floating, use the NC option.

2. A capacitor of value 0.1  $\mu F$  or higher between Vdd and GND is required.

### Table 3. Absolute Maximum Limits

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                                            | Min. | Max. | Unit |

|----------------------------------------------------------------------|------|------|------|

| StorageTemperature                                                   | -65  | 150  | °C   |

| Vdd                                                                  | -0.5 | 4    | V    |

| Electrostatic Discharge                                              | -    | 2000 | V    |

| Soldering Temperature (follow standard Pb free soldering guidelines) | _    | 260  | °C   |

| Junction Temperature <sup>[3]</sup>                                  | -    | 150  | °C   |

Note:

3. Exceeding this temperature for extended period of time may damage the device.

### Table 4. Thermal Consideration<sup>[4]</sup>

| Package | θJA, 4 Layer Board<br>(°C/W) | θJC, Bottom<br>(°C/W) |

|---------|------------------------------|-----------------------|

| SOT23-5 | 421                          | 175                   |

Note:

4. Refer to JESD51 for  $\theta_{JA}$  and  $\theta_{JC}$  definitions, and reference layout used to determine the  $\theta_{JA}$  and  $\theta_{JC}$  values in the above table.

### Table 5. Maximum Operating Junction Temperature<sup>[5]</sup>

| Max Operating Temperature (ambient) | Maximum Operating Junction Temperature |  |  |

|-------------------------------------|----------------------------------------|--|--|

| 70°C                                | 80°C                                   |  |  |

| 85°C                                | 95°C                                   |  |  |

Note:

5. Datasheet specifications are not guaranteed if junction temperature exceeds the maximum operating junction temperature.

### **Table 6. Environmental Compliance**

| Parameter                  | Condition/Test Method    |  |  |

|----------------------------|--------------------------|--|--|

| Mechanical Shock           | MIL-STD-883F, Method2002 |  |  |

| Mechanical Vibration       | MIL-STD-883F, Method2007 |  |  |

| Temperature Cycle          | JESD22, Method A104      |  |  |

| Solderability              | MIL-STD-883F, Method2003 |  |  |

| Moisture Sensitivity Level | MSL1 @ 260°C             |  |  |

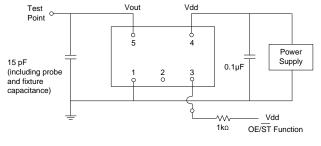

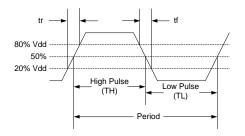

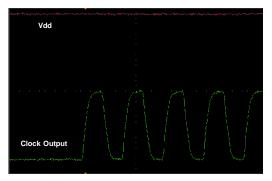

## Test Circuit and Waveform<sup>[6]</sup>

Figure 2. Test Circuit

### Note:

6. Duty Cycle is computed as Duty Cycle = TH/Period.

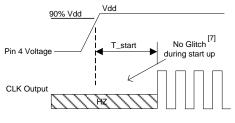

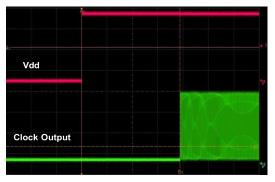

## **Timing Diagrams**

T\_start: Time to start from power-off

### Figure 4. Startup Timing (OE/ST Mode)

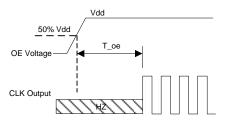

T\_oe: Time to re-enable the clock output

### Figure 6. OE Enable Timing (OE Mode Only)

Note:

7. SiT2002 has "no runt" pulses and "no glitch" output during startup or resume.

Figure 3. Output Waveform

T\_resume: Time to resume from ST

### Figure 5. Standby Resume Timing (ST Mode Only)

T\_oe: Time to put the output in High Z mode

### Figure 7. OE Disable Timing (OE Mode Only)

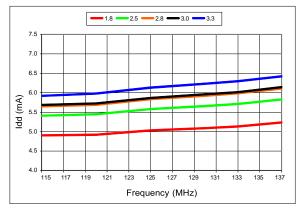

# Performance Plots<sup>[8]</sup>

Figure 8. Idd vs Frequency

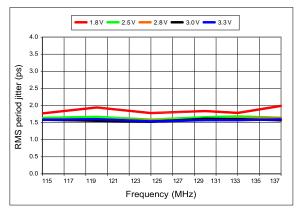

Figure 10. RMS Period Jitter vs Frequency

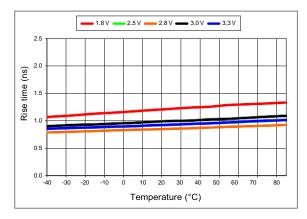

Figure 12. 20%-80% Rise Time vs Temperature

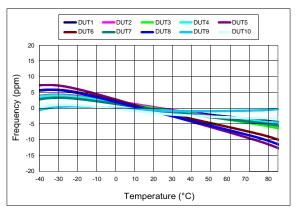

Figure 9. Frequency vs Temperature, 1.8V

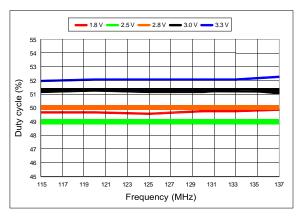

Figure 11. Duty Cycle vs Frequency

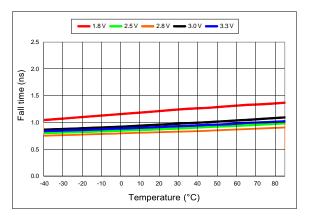

Figure 13. 20%-80% Fall Time vs Temperature

## Performance Plots<sup>[8]</sup>

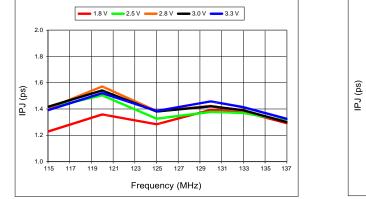

Figure 14. RMS Integrated Phase Jitter Random (12 kHz to 20 MHz) vs Frequency<sup>[9]</sup>

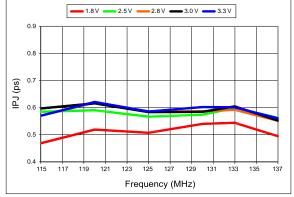

Figure 15. RMS Integrated Phase Jitter Random (900 kHz to 20 MHz) vs Frequency<sup>[9]</sup>

#### Notes:

- 8. All plots are measured with 15 pF load at room temperature, unless otherwise stated.

- 9. Phase noise plots are measured with Agilent E5052B signal source analyzer.

## **Programmable Drive Strength**

The SiT2002 includes a programmable drive strength feature to provide a simple, flexible tool to optimize the clock rise/fall time for specific applications. Benefits from the programmable drive strength feature are:

- Improves system radiated electromagnetic interference (EMI) by slowing down the clock rise/fall time.

- Improves the downstream clock receiver's (RX) jitter by decreasing (speeding up) the clock rise/fall time.

- Ability to drive large capacitive loads while maintaining full swing with sharp edge rates.

For more detailed information about rise/fall time control and drive strength selection, see the SiTime Application Notes section.

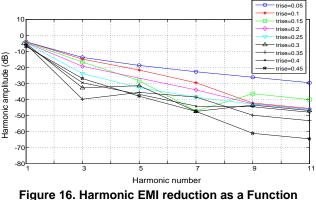

### Reduction by Slowing Rise/Fall Time

Figure 16 shows the harmonic power reduction as the rise/fall times are increased (slowed down). The rise/fall times are expressed as a ratio of the clock period. For the ratio of 0.05, the signal is very close to a square wave. For the ratio of 0.45, the rise/fall times are very close to near-triangular waveform. These results, for example, show that the  $11^{th}$  clock harmonic can be reduced by 35 dB if the rise/fall edge is increased from 5% of the period to 45% of the period.

Figure 16. Harmonic EMI reduction as a Function of Slower Rise/Fall Time

### Jitter Reduction with Faster Rise/Fall Time

Power supply noise can be a source of jitter for the downstream chipset. One way to reduce this jitter is to speed up the rise/fall time of the input clock. Some chipsets may also require faster rise/fall time in order to reduce their sensitivity to this type of jitter. Refer to the Rise/Fall Time Tables (Table 7 to 11) to determine the proper drive strength.

### **High Output Load Capability**

The rise/fall time of the input clock varies as a function of the actual capacitive load the clock drives. At any given drive strength, the rise/fall time becomes slower as the output load increases. As an example, for a 3.3V SiT2002 device with default drive strength setting, the typical rise/fall time is 1ns for 15 pF output load. The typical rise/fall time slows down to 2.6 ns when the output load increases to 45 pF. One can choose to speed up the rise/fall time to 1.83 ns by then increasing the drive strength setting on the SiT2002.

The SiT2002 can support up to 30 pF maximum capacitive loads with drive strength settings. Refer to the Rise/Tall Time Tables (Table 7 to 11) to determine the proper drive strength for the desired combination of output load vs. rise/fall time.

### SiT2002 Drive Strength Selection

Tables 7 through 11 define the rise/fall time for a given capacitive load and supply voltage.

- 1. Select the table that matches the SiT2002 nominal supply voltage (1.8V, 2.5V, 2.8V, 3.0V, 3.3V).

- 2. Select the capacitive load column that matches the application requirement (5 pF to 30 pF)

- **3.** Under the capacitive load column, select the desired rise/fall times.

- 4. The left-most column represents the part number code for the corresponding drive strength.

- 5. Add the drive strength code to the part number for ordering purposes.

### Calculating Maximum Frequency

Based on the rise and fall time data given in Tables 7 through 11, the maximum frequency the oscillator can operate with guaranteed full swing of the output voltage over temperature can be determined as follows:

Max Frequency =

$$\frac{1}{5 \text{ x Trf}_{20/80}}$$

where  $\ensuremath{\mathsf{Trf}}\xspace_{20}$  is the typical value for 20%-80% rise/fall time.

### Example 1

Calculate f<sub>MAX</sub> for the following condition:

- Vdd = 3.3V (Table 11)

- Capacitive Load: 30 pF

- Desired Tr/f time = 1.31 ns (rise/fall time part number code = F)

Part number for the above example:

SiT2002BIF12-18E-137.000000

Drive strength code is inserted here. Default setting is "-"

# Rise/Fall Time (20% to 80%) vs C<sub>LOAD</sub> Tables

# Table 7. Vdd = 1.8V Rise/Fall Times for Specific $C_{LOAD}$

| Rise/Fall Time Typ (ns) |      |       |       |  |  |

|-------------------------|------|-------|-------|--|--|

| Drive Strength \ CLOAD  | 5 pF | 15 pF | 30 pF |  |  |

| Т                       | 0.93 | n/a   | n/a   |  |  |

| E                       | 0.78 | n/a   | n/a   |  |  |

| U                       | 0.70 | 1.48  | n/a   |  |  |

| F or "-": default       | 0.65 | 1.30  | n/a   |  |  |

# Table 9. Vdd = 2.8V Rise/Fall Times for Specific $C_{LOAD}$

| Rise/Fall Time Typ (ns) |      |       |       |  |  |

|-------------------------|------|-------|-------|--|--|

| Drive Strength \ CLOAD  | 5 pF | 15 pF | 30 pF |  |  |

| R                       | 1.29 | n/a   | n/a   |  |  |

| В                       | 0.97 | n/a   | n/a   |  |  |

| Т                       | 0.55 | 1.12  | n/a   |  |  |

| E                       | 0.44 | 1.00  | n/a   |  |  |

| U or "-": default       | 0.34 | 0.88  | n/a   |  |  |

| F                       | 0.29 | 0.81  | 1.48  |  |  |

# Table 11. Vdd = 3.3V Rise/Fall Times for Specific $C_{LOAD}$

| Rise/Fall Time Typ(ns)             |      |       |       |  |  |

|------------------------------------|------|-------|-------|--|--|

| Drive Strength \ C <sub>LOAD</sub> | 5 pF | 15 pF | 30 pF |  |  |

| R                                  | 1.16 | n/a   | n/a   |  |  |

| В                                  | 0.81 | n/a   | n/a   |  |  |

| T or "-": default                  | 0.46 | 1.00  | n/a   |  |  |

| E                                  | 0.33 | 0.87  | n/a   |  |  |

| U                                  | 0.28 | 0.79  | 1.46  |  |  |

| F                                  | 0.25 | 0.72  | 1.31  |  |  |

### Note:

10. "n/a" in Table 7 to Table 11 indicates that the resulting rise/fall time from the respective combination of the drive strength and output load does not provide rail-to-rail swing and is not available.

# Table 8. Vdd = 2.5V Rise/Fall Times for Specific $C_{LOAD}$

| Rise/Fall Time Typ (ns) |      |       |       |  |  |

|-------------------------|------|-------|-------|--|--|

| Drive Strength \ CLOAD  | 5 pF | 15 pF | 30 pF |  |  |

| R                       | 1.45 | n/a   | n/a   |  |  |

| В                       | 1.09 | n/a   | n/a   |  |  |

| Т                       | 0.62 | 1.28  | n/a   |  |  |

| E                       | 0.54 | 1.00  | n/a   |  |  |

| U or "-": default       | 0.43 | 0.96  | n/a   |  |  |

| F                       | 0.34 | 0.88  | n/a   |  |  |

# Table 10. Vdd = 3.0V Rise/Fall Times for Specific $C_{LOAD}$

| Rise/Fall Time Typ (ns)            |      |       |       |  |  |

|------------------------------------|------|-------|-------|--|--|

| Drive Strength \ C <sub>LOAD</sub> | 5 pF | 15 pF | 30 pF |  |  |

| R                                  | 1.22 | n/a   | n/a   |  |  |

| В                                  | 0.89 | n/a   | n/a   |  |  |

| T or "-": default                  | 0.51 | 1.00  | n/a   |  |  |

| E                                  | 0.38 | 0.92  | n/a   |  |  |

| U                                  | 0.30 | 0.83  | n/a   |  |  |

| F                                  | 0.27 | 0.76  | 1.39  |  |  |

# Pin 1 Configuration Options (OE, ST, or NC)

Pin 3 of the SiT2002 can be factory-programmed to support three modes: Output Enable (OE), standby ( $\overline{ST}$ ) or No Connect (NC). These modes can also be programmed with the Time Machine using field programmable devices.

### Output Enable (OE) Mode

In the OE mode, applying logic Low to the OE pin only disables the output driver and puts it in Hi-Z mode. The core of the device continues to operate normally. Power consumption is reduced due to the inactivity of the output. When the OE pin is pulled High, the output is typically enabled in <1 $\mu$ s.

### Standby (ST) Mode

In the  $\overline{ST}$  mode, a device enters into the standby mode when Pin 3 pulled Low. All internal circuits of the device are turned off. The current is reduced to a standby current, typically in the range of a few  $\mu$ A. When  $\overline{ST}$  is pulled High, the device goes through the "resume" process, which can take up to 5 ms.

### No Connect (NC) Mode

In the NC mode, the device always operates in its normal mode and outputs the specified frequency regardless of the logic level on pin 3.

Table 12 below summarizes the key relevant parameters in the operation of the device in OE,  $\overline{ST}$ , or NC mode.

|                                                  | OE     | ST                | NC     |

|--------------------------------------------------|--------|-------------------|--------|

| Active current 20 MHz (max, 1.8V)                | 5.6 mA | 5.6 mA            | 5.6 mA |

| OE disable current (max. 1.8V)                   | 4.1 mA | N/A               | N/A    |

| Standby current (typical 1.8V)                   | N/A    | 0.6 uA            | N/A    |

| OE enable time at 110 MHz (max)                  | 130 ns | N/A               | N/A    |

| Resume time from standby<br>(max, all frequency) | N/A    | 5 ms              | N/A    |

| Output driver in OE<br>disable/standby mode      | High Z | weak<br>pull-down | N/A    |

### Table 12. OE vs. ST vs. NC

### **Output on Startup and Resume**

The SiT2002 comes with gated output. Its clock output is accurate to the rated frequency stability within the first pulse from initial device startup or resume from the standby mode.

In addition, the SiT2002 supports "no runt" pulses and "no glitch" output during startup or resume as shown in the waveform captures in Figure 17 and Figure 18.

Figure 17. Startup Waveform vs. Vdd

Figure 18. Startup Waveform vs. Vdd (Zoomed-in View of Figure 17)

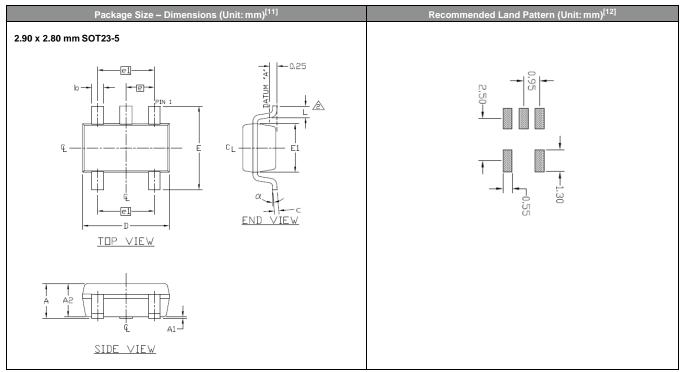

## **Dimensions and Patterns**

#### Notes:

- 11. Top marking: Y denotes manufacturing origin and XXXX denotes manufacturing lot number. The value of "Y" will depend on the assembly location of the device.

- 12. A capacitor value of 0.1  $\mu F$  between Vdd and GND is required.

### Table 13. Dimension Table

| Symbol | Min.      | Nom. | Max. |  |

|--------|-----------|------|------|--|

| A      | 0.90      | 1.27 | 1.45 |  |

| A1     | 0.00      | 0.07 | 0.15 |  |

| A2     | 0.90      | 1.20 | 1.30 |  |

| b      | 0.30      | 0.35 | 0.50 |  |

| С      | 0.14      | 0.15 | 0.20 |  |

| D      | 2.75      | 2.90 | 3.05 |  |

| E      | 2.60      | 2.80 | 3.00 |  |

| E1     | 1.45      | 1.60 | 1.75 |  |

| L      | 0.30      | 0.38 | 0.55 |  |

| L1     | 0.25 REF  |      |      |  |

| е      | 0.95 BSC. |      |      |  |

| e1     | 1.90 BSC. |      |      |  |

| α      | 0° 0° 0°  |      |      |  |

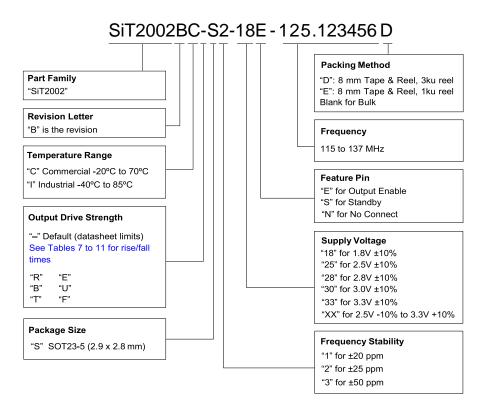

## **Ordering Information**

The Part No. Guide is for reference only. To customize and build an exact part number, use the SiTime Part Number Generator.

### Table 14. Additional Information

| Document                          | Description                                                                                              | Download Link                                                 |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

| Time Machine II                   | MEMS oscillator programmer http://www.sitime.com/support/time-machine-oscillator-pro                     |                                                               |  |

| Field Programmable<br>Oscillators | Devices that can be programmable in the field by<br>Time Machine II                                      | http://www.sitime.com/products/field-programmable-oscillators |  |

| Manufacturing Notes               | Tape & Reel dimension, reflow profile and other<br>manufacturing related info                            | http://www.sitime.com/manufacturing-notes                     |  |

| Qualification Reports             | RoHS report, reliability reports, composition reports                                                    | http://www.sitime.com/support/quality-and-reliability         |  |

| Performance Reports               | Additional performance data such as phase noise, current consumption and jitter for selected frequencies | http://www.sitime.com/support/performance-measurement-report  |  |

| Termination Techniques            | Termination design recommendations                                                                       | http://www.sitime.com/support/application-notes               |  |

| Layout Techniques                 | Layout recommendations                                                                                   | http://www.sitime.com/support/application-notes               |  |

### Table 15. Revision History

| Revision | Release Date | Change Summary                                              |  |

|----------|--------------|-------------------------------------------------------------|--|

| 1.0      | 05/14/2015   | Final Production Release                                    |  |

| 1.01     | 09/29/2015   | Revised the dimension table                                 |  |

| 1.02     | 04/19/2018   | Changed Clock Generator to SOT23 Oscillator                 |  |

|          |              | Updated logo and company address, other page layout changes |  |

### SiTime Corporation, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | Phone: +1-408-328-4400 | Fax: +1-408-328-4439

© SiTime Corporation 2015-2018. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) being subjected to unusual physical, thermal, or electrical stress.

Disclaimer: SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. Products sold by SiTime are not suitable or intended to be used in a life support application or component, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

CRITICAL USE EXCLUSION POLICY

BUYER AGREES NOT TO USE SITIME'S PRODUCTS FOR ANY APPLICATION OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.

# **Supplemental Information**

The Supplemental Information section is not part of the datasheet and is for informational purposes only.

### **Best Reliability**

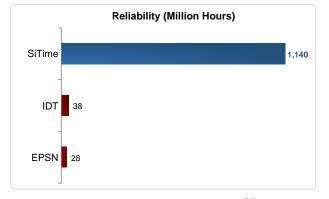

Silicon is inherently more reliable than quartz. Unlike quartz suppliers, SiTime has in-house MEMS and analog CMOS expertise, which allows SiTime to develop the most reliable products. Figure 1 shows a comparison with quartz technology.

### Why is SiTime MEMS Best in Class:

- SiTime's MEMS resonators are vacuum sealed using an advanced EpiSeal<sup>™</sup> process, which eliminates foreign particles and improves long term aging and reliability

- World-class MEMS and CMOS design expertise

Figure 1. Reliability Comparison<sup>[1]</sup>

### Best Aging

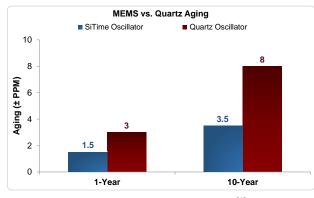

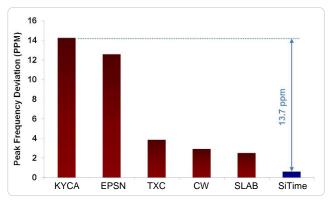

Unlike quartz, MEMS oscillators have excellent long term aging performance which is why every new SiTime product specifies 10-year aging. A comparison is shown in Figure 2.

### Why is SiTime MEMS Best in Class:

- SiTime's MEMS resonators are vacuum sealed using an advanced EpiSeal<sup>™</sup> process, which eliminates foreign particles and improves long term aging and reliability

- Inherently better immunity of electrostatically driven MEMS resonator

Figure 2. Aging Comparison<sup>[2]</sup>

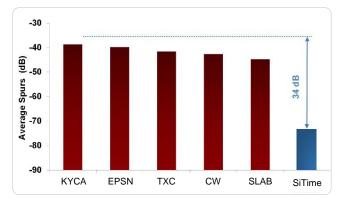

### Best Electro Magnetic Susceptibility (EMS)

SiTime's oscillators in plastic packages are up to 54 times more immune to external electromagnetic fields than quartz oscillators as shown in Figure 3.

### Why is SiTime MEMS Best in Class:

- Internal differential architecture for best common mode noise rejection

- Electrostatically driven MEMS resonator is more immune to EMS

Figure 3. Electro Magnetic Susceptibility (EMS)<sup>[3]</sup>

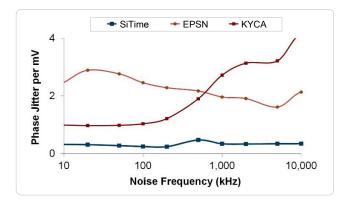

### **Best Power Supply Noise Rejection**

SiTime's MEMS oscillators are more resilient against noise on the power supply. A comparison is shown in Figure 4.

### Why is SiTime MEMS Best in Class:

- On-chip regulators and internal differential architecture for common mode noise rejection

- MEMS resonator is paired with advanced analog CMOS IC

Figure 4. Power Supply Noise Rejection<sup>[4]</sup>

### **Best Vibration Robustness**

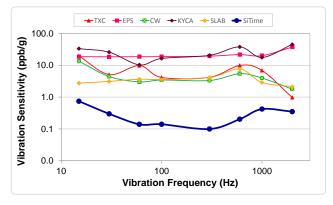

High-vibration environments are all around us. All electronics, from handheld devices to enterprise servers and storage systems are subject to vibration. Figure 5 shows a comparison of vibration robustness.

### Why is SiTime MEMS Best in Class:

- The moving mass of SiTime's MEMS resonators is up to 3000 times smaller than quartz

- Center-anchored MEMS resonator is the most robust design

Figure 5. Vibration Robustness<sup>[5]</sup>

#### Figure labels:

- TXC = TXC

- Epson = EPSN

- Connor Winfield = CW

- Kyocera = KYCA

- SiLabs = SLAB

- SiTime = EpiSeal MEMS

### **Best Shock Robustness**

SiTime's oscillators can withstand at least  $50,000 \ g$  shock. They all maintain their electrical performance in operation during shock events. A comparison with quartz devices is shown in Figure 6.

### Why is SiTime MEMS Best in Class:

- The moving mass of SiTime's MEMS resonators is up to 3000 times smaller than guartz

- Center-anchored MEMS resonator is the most robust design

Figure 6. Shock Robustness<sup>[6]</sup>

#### Notes:

- 1. Data source: Reliability documents of named companies.

- 2. Data source: SiTime and quartz oscillator devices datasheets.

- 3. Test conditions for Electro Magnetic Susceptibility (EMS):

- According to IEC EN61000-4.3 (Electromagnetic compatibility standard)

- Field strength: 3V/m

- Radiated signal modulation: AM 1 kHz at 80% depth

- Carrier frequency scan: 80 MHz 1 GHz in 1% steps

- Antenna polarization: Vertical

DUT position: Center aligned to antenna

### Devices used in this test:

| Label        | Manufacturer    | Part Number                 | Technology                             |

|--------------|-----------------|-----------------------------|----------------------------------------|

| EpiSeal MEMS | SiTime          | SiT9120AC-1D2-33E156.250000 | MEMS + PLL                             |

| EPSN         | Epson           | EG-2102CA156.2500M-PHPAL3   | Quartz, SAW                            |

| TXC          | TXC             | BB-156.250MBE-T             | Quartz, 3 <sup>rd</sup> Overtone       |

| CW           | Conner Winfield | P123-156.25M                | Quartz, 3 <sup>rd</sup> Overtone       |

| KYCA         | AVX Kyocera     | KC7050T156.250P30E00        | Quartz, SAW                            |

| SLAB         | SiLab           | 590AB-BDG                   | Quartz, 3 <sup>rd</sup> Overtone + PLL |

4. 50 mV pk-pk Sinusoidal voltage.

### Devices used in this test:

| Label        | Manufacturer | Part Number                | Technology |

|--------------|--------------|----------------------------|------------|

| EpiSeal MEMS | SiTime       | SiT8208AI-33-33E-25.000000 | MEMS + PLL |

| NDK          | NDK          | NZ2523SB-25.6M             | Quartz     |

| KYCA         | AVX Kyocera  | KC2016B25M0C1GE00          | Quartz     |

| EPSN         | Epson        | SG-310SCF-25M0-MB3         | Quartz     |

5. Devices used in this test:

same as EMS test stated in Note 3.

- 6. Test conditions for shock test:

- MIL-STD-883F Method 2002

- Condition A: half sine wave shock pulse, 500-g, 1ms

- Continuous frequency measurement in 100 µs gate time for 10 seconds

- Devices used in this test:

same as EMS test stated in Note 3.

7. Additional data, including setup and detailed results, is available upon request to qualified customer. Please contact productsupport@sitime.com.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Standard Clock Oscillators category:

Click to view products by SiTime manufacturer:

Other Similar products are found below :

601252F335-12F335-25F535L-33.333F535L-50ASV-20.000MHZ-LR-TECS-2018-160-BN-TRMXO45HS-2C-66.6666MHZSiT1602BI-22-33E-50.000000ESiT8209AI-32-33E-125.00000SIT8918AA-11-33S-50.000000GSM4420TEV-40.0M-T1KF335-24F335-40F535L-10F535L-12F535L-16F535L-24F535L-27F535L-48PE7744DW-100.0MCSX-750FCC14745600TASF1-3.686MHZ-N-K-SXO57CTECNA3M6864ECS-2100A-147.4601251EP16E7E2H26.000MTRSIT8918AA-11-33S-16.00000GXO30039120AC-2D2-33E212.5000009102AI-243N25E100.000008208AC-82-18E-25.00000ASDK2-32.768KHZ-LR-T38008AI-72-XXE-24.545454E8004AC-13-33E-133.33000XAS-4.9152-16-SMD-TRASFL1-48.000MHZ-LC-TSIT8920AM-31-33E-25.0000DSC1028DI2-019.20009121AC-2C3-25E100.000009102AI-233N33E100.00000X9102AI-233N25E200.000009102AI-232H25S125.000009102AI-133N25E200.000009102AC-283N25E200.000009001AC-33-33E1-30.000XLH536125.000JS4I3921AI-2CF-33NZ125.000005730-1SFPXA000010