# 1Gb/2Gb/4Gb, 3V, SPI SLC NAND Flash Memory for Embedded

### **Distinctive Characteristics**

#### ■ Density

□ 1Gb / 2Gb / 4Gb

#### ■ Architecture

□ Page size:

1 Gb: (2048 + 64) bytes; 64-byte spare area

1 Gb: (2048 + 128) bytes; 128-byte spare area

2 Gb/4 Gb: (2048 + 128) bytes; 128-byte spare area

□ Block size: 64 Pages

1 Gb: 128 KB + 4 KB 1 Gb: 128 KB + 8 KB 2 Gb / 4 Gb: 128 KB + 8 KB

#### Plane size

Gb: 1024 blocks per plane or (128 MB + 4 MB)

Gb: 1024 blocks per plane or (128 MB + 8 MB)

Gb: 1024 blocks per plane or (128 MB + 8 MB)

Gb: 2048 blocks per plane or (256 MB + 16 MB)

#### Device Size

1 Gb: 1 plane per device or 128 Mbyte2 Gb: 2 planes per device or 256 Mbyte4 Gb: 2 planes per device or 512 Mbyte

#### **Performance**

#### ■ Page Read / Program

☐ Read Page Time (tR): 45 µs (Typ)

□ Program time: 350 µs (Typ)

#### ■ Block Erase

□ Block Erase time: 4.0 ms (Typ)

#### ■ Reliability

□ 80,000 Program / Erase cycles (Typ)

☐ 10 Year Data Retention (Typ)

$\hfill\Box$  Blocks 0-7 are good at the time of shipment

#### NAND Flash interface

Supports Serial Peripheral Interface (SPI)

#### ■ Supply Voltage

$\Box$  3.3-V device:  $V_{CC} = 2.7 \text{ V} \sim 3.6 \text{ V}$

#### ■ Security

One Time Programmable (OTP) area

Serial number (unique ID) (Contact factory for support)

Hardware program/erase disabled during power transition

□ Volatile and Permanent Block Protection

#### Additional features

On- chip ECC correction Program and Erase

□ Supports single I/O, Dual I/O, Quad I/O

Support Frequency up to 104MHZ

Supports Clock Polarity and phase modes 0 and 3

#### ■ Electronic signature

■ Manufacturer ID:01h

#### Operating temperature

□ Industrial: -40 °C to 85 °C

□ Industrial Plus: -40 °C to 105 °C

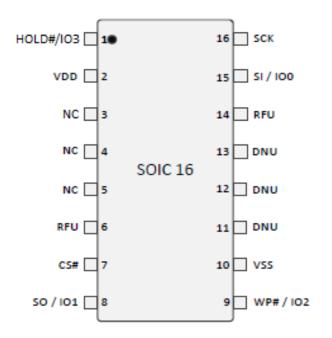

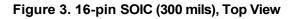

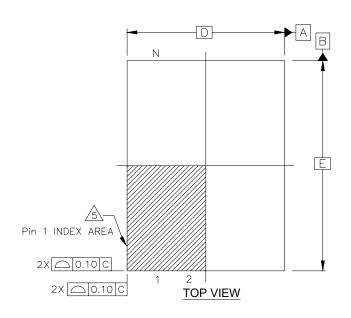

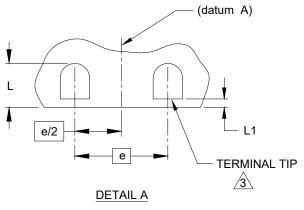

### Package options

Pb-free and low halogen

■ 8-Pin LGA 6 × 8 mm

□ 16-Pin SOIC 300 mils

□ 24-Ball FBGA 8 × 6 mm

## **Contents**

| 1.    | General Description                           | 3    |

|-------|-----------------------------------------------|------|

| 1.1   | Logic Diagram                                 | 4    |

| 1.2   | Connection Diagram                            | 5    |

| 1.3   | Pin Description                               | 6    |

| 1.4   | Block Diagram                                 |      |

| 1.5   | Array Organization                            | 7    |

| 1.6   | Memory Addressing                             | 9    |

| 2.    | Bus Operation                                 | .10  |

| 2.1   | SPI Modes                                     | . 10 |

| 2.2   | SPI Protocol                                  | . 10 |

| 3.    | Command Set                                   | 11   |

| 3.1   | Power up and Reset Commands                   | 13   |

| 3.2   | Write Enable and Write Disable Commands       | 13   |

| 3.3   | Hardware Write Protection                     | 13   |

| 3.4   | Read Operation                                | 13   |

| 3.5   | Page Program Operation                        | 13   |

| 3.6   | Feature Operations                            |      |

|       | Set Feature                                   |      |

| 3.6.2 | Get Feature                                   |      |

| 3.7   | Feature Registers                             | 15   |

| 3.8   | Read ID                                       |      |

|       | Read Unique ID                                |      |

|       | One Time Programming OTP                      |      |

| 3.10. | 1Read OTP                                     | 18   |

| 3.10. | 2Program OTP                                  | 18   |

| 3.10. | 3OTP Program Prevention                       | 19   |

| 3.11  | Internal Data Move                            | 19   |

| 3.12  | Read Parameter Page                           | 20   |

| 4.    | Electrical Characteristics                    | 23   |

| 4.1   | Valid Blocks                                  |      |

| 4.2   | Absolute Maximum Ratings                      | 23   |

| 4.3   | Recommended Operating Conditions              | 23   |

| 4.4   | AC Test Conditions                            |      |

| 4.5   | AC Characteristics                            |      |

| 4.6   | DC Characteristics                            | 26   |

| 4.7   | Pin Capacitance                               | . 27 |

| 4.8   | Program / Erase Characteristics               | 27   |

| 5.    | Security Features                             | 28   |

| 5.1   | Volatile Block Protection Overview            |      |

| 5.2   | Permanent Block Protection Overview           |      |

| 5.3   | Permanent Block Protection Lock-Down Sequence |      |

| 5.4   | Block Protection Status Command               |      |

| 5.5   | Block Lock Status Register                    |      |

| 6.   | Timing Diagrams                                                           | .36  |

|------|---------------------------------------------------------------------------|------|

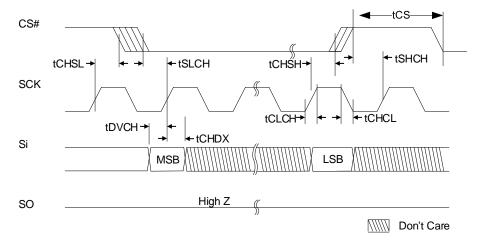

| 6.1  | SPI Clock Timing                                                          | .36  |

| 6.2  | Serial Input Timing                                                       | .36  |

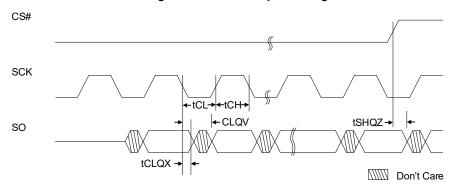

| 6.3  | Serial Output Timing                                                      | .36  |

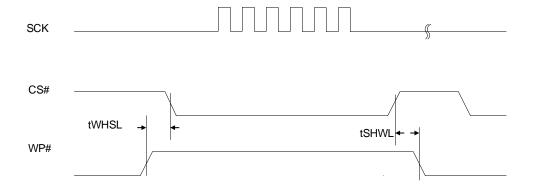

| 6.4  | WP# Timing                                                                | .37  |

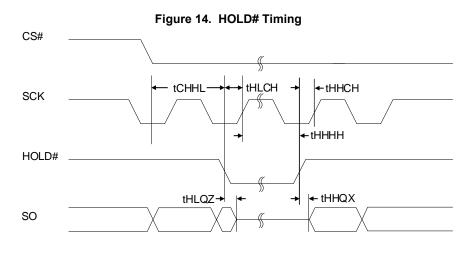

| 6.5  | HOLD# Timing                                                              |      |

| 6.6  | Block Erase/Program Execute/ Page read Timing                             | 38   |

| 6.7  | Read Buffer 1X (03h or 0Bh)Timing                                         |      |

| 6.8  | Fast Read Dual Output Buffer 2X (3Bh) Timing                              | .39  |

| 6.9  | Fast Read Quad Output Buffer 2X (6Bh) Timing                              | . 39 |

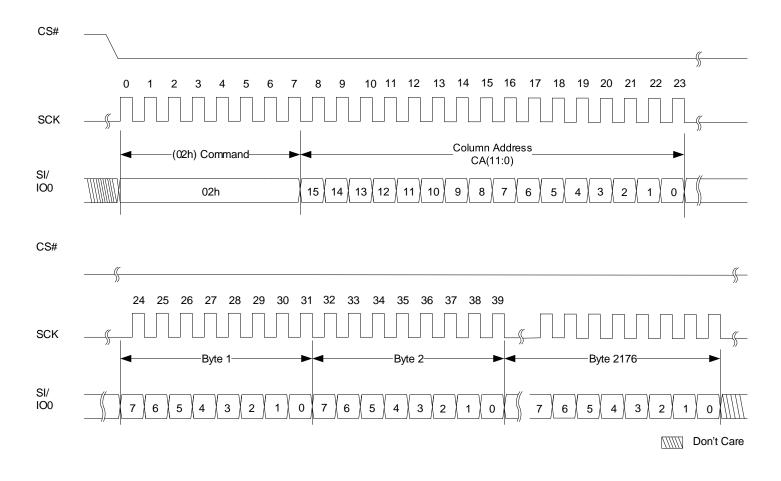

| 6.10 | Program Load 1X (02h) and Program Load Random Data 1X (84h) buffer Timing | 40   |

|      | Quad Program Data Load 4X (32h) and Quad Program                          |      |

|      | Load Random Data 1X (34h) buffer Timing                                   |      |

|      | Small Data Input. Guidelines                                              |      |

|      | Fast Read Dual IO 2X(BBh)-Timing                                          |      |

| 6.14 | Fast Read Quad I/O 4X (EBh) Timing                                        | .43  |

| 6.15 | Power-up Timing                                                           | .44  |

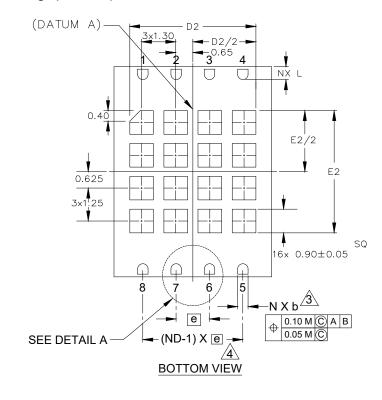

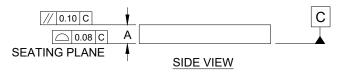

| 7.   | Physical Interface                                                        | 45   |

| 7.1  | Physical Diagrams                                                         | 45   |

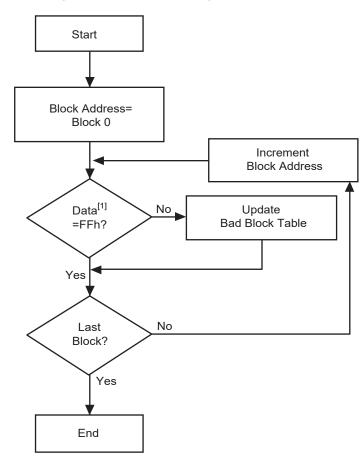

| 8.   | Error Management                                                          | 48   |

| 8.1  | System Bad Block Replacement                                              | 48   |

| 8.2  | Bad Block Management                                                      | 49   |

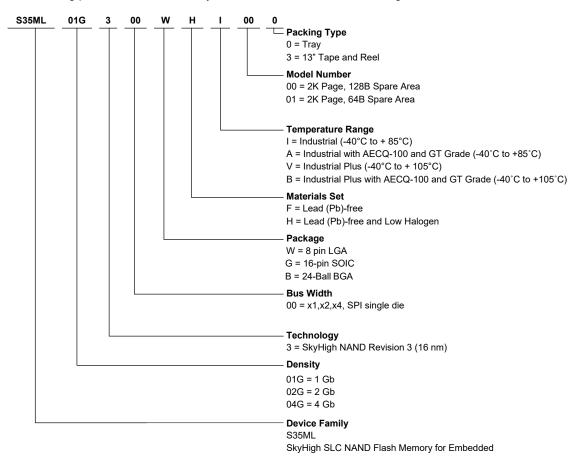

| 9.   | Ordering Information                                                      | 50   |

|      | Document History                                                          | 51   |

## 1. General Description

The S35ML01G3 / S35ML02G3 / S35ML04G3 SPI devices are offered with a 3.3-V VCC power supply, and with industry standard Serial Peripheral Interface (SPI). Its NAND cell provides the most cost-effective solution for the solid state mass storage market with low pin count and a modified SPI-NOR command set to address NAND specific functions and features.

The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data iserased. The page size for the 1Gb/2Gb/4Gb SPI devices is (2048 + 128 spare) bytes and for the 1Gb device with 64 bytes spare option is (2048 + 64 spare) bytes. SkyHigh SPI NAND family is designed with powerful internal ECC engine. To protect the system bus from transmission errors, the implementation of a 1 bit ECC is recommended.

Like all other 2-kB page NAND flash devices, a program operation typically writes 2 KB (×8) in 350 µs and an erase operation can typically be performed in 4ms on a 128-kB block.

The on-chip Program/Erase Controller automates all read, program, and erase functions including pulse repetition, where required, and internal verification and margining of data.

SkyHigh's SPI device offers many useful features including first page auto-load on power-up. SkyHigh's SPI NAND Flash has six signal lines in addition to VCC and GND pins. The signal lines are: SCK, SI, SO, CS, HOLD#, WP#.

The devices are available in the LGA- 8 pins (6 x 8 mm), SOIC- 16 pins (300 mil), FBGA- 24 pins (8 x 6 mm) packages and come with the following security features:

- OTP (one time programmable) area, which is a restricted access area where sensitive data/code can be stored permanently.

- Serial number (unique identifier), which allows the devices to be uniquely identified. Contact factory for support of this feature.

- Volatile and Permanent Block Protection.

Document Number: 002-19205 Rev. H Page 3 of 51

Table 1. Product List

| Device    | Density (bits) | Number of Planes | Number of Blocks<br>per Plane |

|-----------|----------------|------------------|-------------------------------|

| S35ML01G3 | 1 Gb           | 1                | 1024                          |

| S35ML02G3 | 2 Gb           | 2                | 1024                          |

| S35ML04G3 | 4 Gb           | 2                | 2048                          |

Note 1): Since Dual plane operation are not supported in SPI, therefore the whole array is described in number of blocks. The planes are reflected in this document to match the physical implementation.

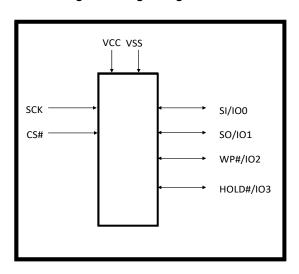

## 1.1 Logic Diagram

Figure 1. Logic Diagram

Table 2. Signal Names

| Signal<br>Name | Туре   | Description                                                                  |

|----------------|--------|------------------------------------------------------------------------------|

| CS#            | Input  | Chip Select                                                                  |

| SI/IO0         | I/O    | Serial Input for single bit data commands or I/O0 for Dual or Quad commands. |

|                |        | Serial Output for single bit data commands. I/O1 for Dual or                 |

| SO/IO1         | I/O    | Quad commands.                                                               |

| WP#/IO2        | I/O    | Write Protect when not in Quad mode, I/O2 when in Quad                       |

| HOLD#/IO3      | I/O    | Hold Input / I/O3 when in Quad mode                                          |

| SCK            | Input  | Serial Clock Input                                                           |

| VCC            | Supply | Power Supply                                                                 |

| VSS            | Supply | Ground                                                                       |

| NC             | Unuse  | No Connection                                                                |

| DNU            | Reserv | Do not use                                                                   |

#### Notes:

<sup>1.</sup> A 0.1 µF capacitor should be connected between the VCC Supply Voltage pin and the Vss Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

<sup>2.</sup> An internal voltage detector disables all functions whenever VCC is below 1.8V to protect the device from any involuntary program/erase during power transitions.

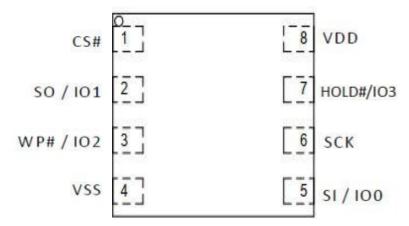

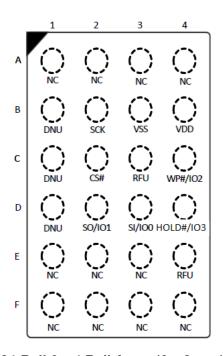

### 1.2 Connection Diagram

Figure 2. 8-pin LGA package (6 x 8 mm), Top View

Figure 4. 24-Ball 6 x 4 Ball Array (6 x 8 mm), Top View

## 1.3 Pin Description

Table 3. Pin Description

| Signal<br>Name | Туре     | Description                                                                  |

|----------------|----------|------------------------------------------------------------------------------|

| CS#            | Input    | Chip Select                                                                  |

| SI/IO0         | I/O      | Serial Input for single bit data commands or I/O0 for Dual or Quad commands. |

| SO/IO1         | I/O      | Serial Output for single bit data commands. I/O1 for Dual or Quad commands.  |

| WP#/IO2        | I/O      | Write Protect when not in Quad mode, I/O2 when in Quad mode                  |

| HOLD#/IO3      | I/O      | Hold Input / I/O3 when in Quad mode                                          |

| SCK            | Input    | Serial Clock Input                                                           |

| VCC            | Supply   | Power Supply                                                                 |

| VSS            | Supply   | Ground                                                                       |

| NC             | Unused   | No Connection                                                                |

| DNU            | Reserved | Do not use                                                                   |

#### Notes:

- 1. A 0.1  $\mu$ F capacitor should be connected between the VCC Supply Voltage pin and the Vss Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

- 2. An internal voltage detector disables all functions whenever VCC is below 1.8V to protect the device from any involuntary program/erase during power transitions.

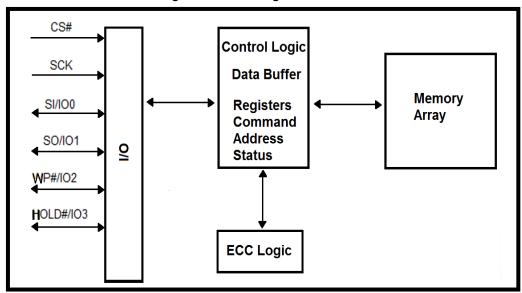

## 1.4 Block Diagram

Figure 5. Block Diagram

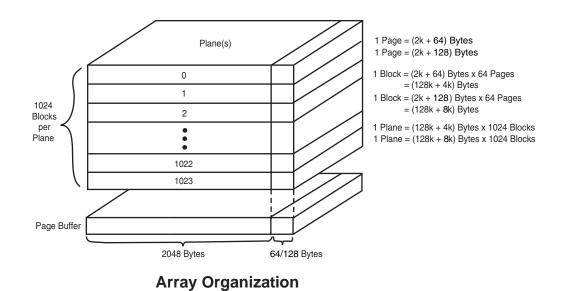

## 1.5 Array Organization

Figure 6. Array Organization — S35ML01G3

Note 1): S35ML01G3 is offered with 64 bytes spare are and 128 bytes spare area options.

Document Number: 002-19205 Rev. H Page 7 of 51

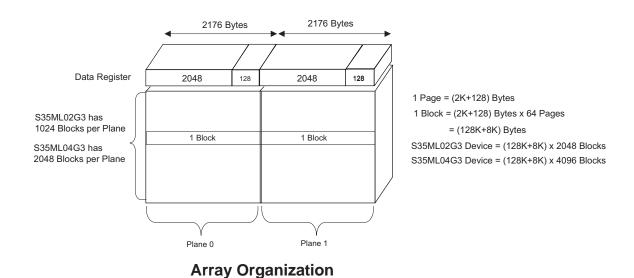

## 1.5 Array Organization

Figure 6.1 Array Organization— S35ML02G3 / S35ML04G3

Note 1): Since Dual plane operation are not supported in SPI, therefore the whole array is described in number of blocks. The planes are reflected in this document to match the physical implementation.

Document Number: 002-19205 Rev. H Page 8 of 51

## 1.6 Memory Addressing

Table 4. Memory Array organization

|                       | Device and Array organization |     |        |                     |                   |                     |                                   |     |                      | Address bits |            |            |

|-----------------------|-------------------------------|-----|--------|---------------------|-------------------|---------------------|-----------------------------------|-----|----------------------|--------------|------------|------------|

| Density_<br>Page Size | Page Size                     | Die | Planes | #block<br>per plane | Page<br>per block | Spare Byte per page | Spare Byte<br>per partial<br>page | NOP | Partial<br>Word Size | CA<br>bits   | PA<br>bits | BA<br>bits |

| 01Gb_2KB              | 2KB                           | 1   | 1      | 1024                | 64                | 64                  | 16                                | 4   | 512B                 | 12           | 6          | 10         |

| 01Gb_2KB              | 2KB                           | 1   | 1      | 1024                | 64                | 128                 | 32                                | 4   | 512B                 | 12           | 6          | 10         |

| 02Gb_2KB              | 2KB                           | 1   | 2      | 1024                | 64                | 128                 | 32                                | 4   | 512B                 | 12           | 6          | 11         |

| 04Gb_2KB              | 2KB                           | 1   | 2      | 2048                | 64                | 128                 | 32                                | 4   | 512B                 | 12           | 6          | 12         |

#### Notes:

- 1. CAb= Column Address bit.

- 2. PAb = Page Address bit.

- 3. BAb = Block Address bit.

Table 5: Address phase cycles for buffer and array operations

|                      | Address Cycle Map                                                              |                  |              |             |          |         |         |         |             |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------|------------------|--------------|-------------|----------|---------|---------|---------|-------------|--|--|--|--|

| Bus Cycle            | SI                                                                             | SI[7] (MSB)      | SI[6]        | SI[5]       | SI[4]    | SI[3]   | SI[2]   | SI[1]   | SI[0] (LSB) |  |  |  |  |

| Buffer Operation: Lo | Buffer Operation: Load Pin inputs Data to Buffer or Data Buffer to Output Pins |                  |              |             |          |         |         |         |             |  |  |  |  |

| 1 <sup>st</sup>      | CA[15:8]                                                                       | Low              | Low          | Low         | Low      | CAx[11] | CAx[10] | CAx[9]  | CAx[8]      |  |  |  |  |

| 2 <sup>nd</sup>      | CA[7:0]                                                                        | CAx[7]           | CAx[6]       | CAx[5]      | CAx[4]   | CAx[3]  | CAx[2]  | CAx[1]  | CAx[0]      |  |  |  |  |

| Array Operation: Loa | ad Data Array                                                                  | to buffer or Pro | ogram Data i | from buffer | to Array |         |         |         |             |  |  |  |  |

| Bus Cycle            | SI                                                                             | SI[7] (MSB)      | SI[6]        | SI[5]       | SI[4]    | SI[3]   | SI[2]   | SI[1]   | SI[0] (LSB) |  |  |  |  |

| 1 <sup>st</sup>      | PA[23:16]                                                                      | Low              | Low          | Low         | Low      | low     | Low     | BAx[11] | BAx[10]     |  |  |  |  |

| 2 <sup>nd</sup>      | PA[15:8]                                                                       | BAx[9]           | BAx[8]       | BAx[7]      | BAx[6]   | BAx[5]  | BAx[4]  | BAx[3]  | BAx[2]      |  |  |  |  |

| 3 <sup>rd</sup>      | PA[7:0]                                                                        | BAx[1]           | BAx[0]       | PAx[5]      | PAx[4]   | PAx[3]  | PAx[2]  | PAx[1]  | PAx[0]      |  |  |  |  |

#### Notes:

- 1. CAx = Column Address bit. If CA[11]=1 then CA[10:7] must Low

- 2. PAx = Page Address bit.

- 3. BAx = Block Address bit.

Since Dual plane operation are not supported in SPI, therefore the whole array is described in number of blocks. The planes are reflected in this document to match the physical implementation.

| Density_Page Size | #of<br>Dies | #<br>Planes | #Blocks<br>per plane | BA[13:0]              | Plane Selection |

|-------------------|-------------|-------------|----------------------|-----------------------|-----------------|

| 01Gb_2KB          | 1           | 1.          | 1024                 | BA[13:10]=L, BA[9:0]  | N/A             |

| 02Gb_2KB          | 1           | 2           | 1024                 | BA[13:11]=L, BA[10:0] | BA[0]           |

| 04Gb_2KB          | 1           | 2           | 2048                 | BA[13:12]=L, BA[11:0] | BA[0]           |

Document Number: 002-19205 Rev. H Page 9 of 51

### 2. Bus Operation

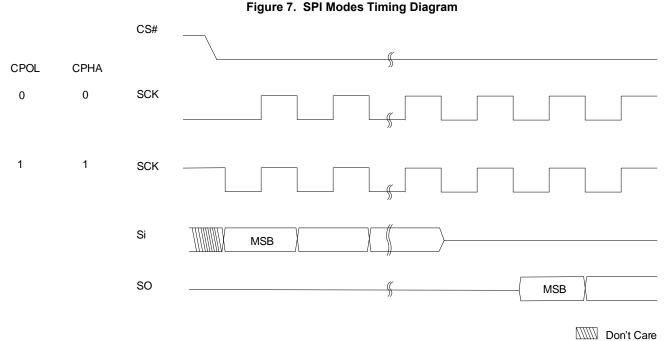

### 2.1 SPI Modes

The SPI NAND can be driven by a micro-controller with its SPI interface running in either of the two following clocking modes: **Mode 0** with Clock Polarity (CPOL) = 0 and, Clock Phase (CPHA) = 0

Mode 3 with CPOL = 1 and, CPHA = 1

For these two modes, input data into the device is always latched in on the rising edge of the SCK signal and the output data is always available from the falling edge of the SCK clock signal.

The difference between the two modes is the clock polarity when the bus master is in standby mode and not transferring any data.

SCK will stay at logic low state with CPOL = 0, CPHA = 0

SCK will stay at logic high state w ith CPOL = 1, CPHA = 1

2.1 SPI Protocols

#### Standard (Traditional) SPI

Standard SPI NAND Flash supports a serial peripheral interface with 4 signals bus: Serial Clock (SCLK), Chip Select (CS#), Serial Data Input (SI) Serial Data Output (SO).

### **Dual SPI**

SPI NAND Flash supports Dual SPI operation when using the x2 and dual IO commands. These commands allow data to be transferred to or from the device at two times the rate of the standard SPI. When using the Dual SPI command the SI and SO pins become bidirectional I/O pins: SI/IO0, SO/IO1

#### **Quad SPI**

SPI NAND Flash supports Quad SPI operation when using the x4 and Quad IO commands. These commands allow data to be transferred to or from the device at four times the rate of the standard SPI. When using the Quad SPI command the SI, SO, WP#, HOLD# pins become bidirectional I/O pins: SI/IO0, SI/IO1, WP#/IO2, HOLD#/IO3

## 3. Command Set

Table 6 : Command Set

| Command                                             | Op Code       | Byte 2                                         | Byte 3 | Byte 4                                        | Byte 5   | Byte 6   | Byte 7 | Notes                                         |

|-----------------------------------------------------|---------------|------------------------------------------------|--------|-----------------------------------------------|----------|----------|--------|-----------------------------------------------|

| Reset                                               | FFh           |                                                |        |                                               |          |          |        |                                               |

| Write Enable                                        | 06h           |                                                |        |                                               |          |          |        |                                               |

| Write Disable                                       | 04h           |                                                |        |                                               |          |          |        |                                               |

| Get Feature                                         | 0Fh           | CA7-0                                          | D7-0   |                                               |          |          |        |                                               |

| Set Feature                                         | 1Fh           | CA7-0                                          | D7-0   |                                               |          |          |        |                                               |

| Read ID                                             | 9Fh           | 8 Dummy<br>clock cycles<br>(So Ouput<br>HighZ) | D7-0   | D7-0                                          |          |          |        |                                               |

| Block Erase                                         | D8h           | PA23-16                                        | PA15-8 | PA7-0                                         |          |          |        |                                               |

|                                                     |               |                                                | Arr    | ay operations                                 |          |          |        |                                               |

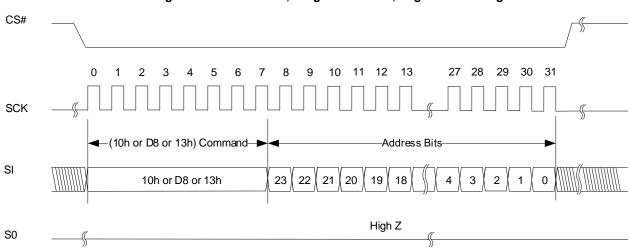

| Program<br>Execute                                  | 10h           | PA23-16                                        | PA15-8 | PA7-0                                         |          |          |        |                                               |

| Page Read                                           | 13h           | PA23-16                                        | PA15-8 | PA7-0                                         |          |          |        |                                               |

|                                                     |               |                                                | Buf    | fer operations                                |          |          |        |                                               |

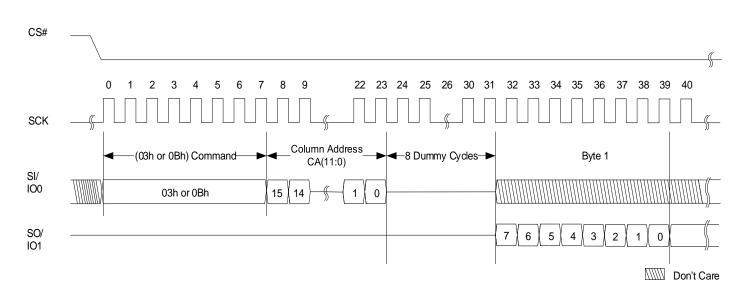

| Read Buffer 1X                                      | 03h or<br>0Bh | CA15-8                                         | CA7-0  | 8 Dummy<br>clock cycles<br>(Outputs<br>HighZ) | D7-0     | D7-0     |        |                                               |

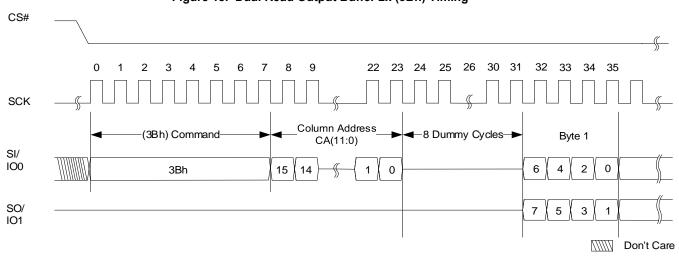

| Dual Read<br>Output 2X                              | 3Bh           | CA15-8                                         | CA7-0  | 8 Dummy<br>cycles<br>(HighZ)                  | D7-0(2X) | D7-0(2X) |        | 4 clock cycles to<br>output 1 Byte of<br>Data |

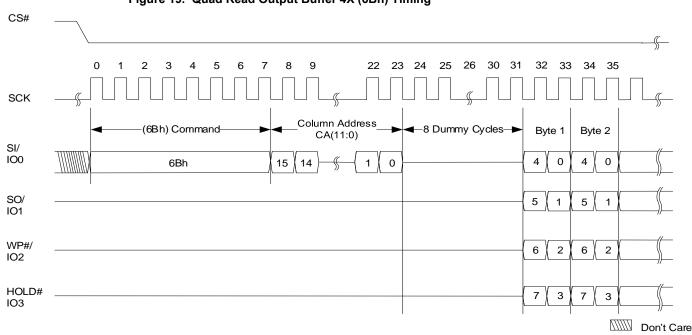

| Quad Read<br>Output 4X                              | 6Bh           | CA15-8                                         | CA7-0  | 8 Dummy<br>clock cycles<br>(outputs<br>HighZ) | D7-0(4X) | D7-0(4X) |        | 2 clock cycles to<br>output 1 Byte of<br>Data |

| Program Load<br>1X                                  | 02h           | CA15-8                                         | CA7-0  | D7-0                                          | D7-0     | D7-0     |        |                                               |

| Program Load<br>Random Data<br>1X ( <b>Note 1</b> ) | 84h           | CA15-8                                         | CA7-0  | D7-0                                          | D7-0     | D7-0     |        |                                               |

### Command Set-cont'd

| Fast Read Dual<br>I/O                                       | BBh | CA15-8(2X) | CA7-0(2X) | 8 Dummy<br>clock cycles<br>(outputs High Z)<br>(Note 4) | D7-0(2X)                                      | D7-0(2X) |                                              |

|-------------------------------------------------------------|-----|------------|-----------|---------------------------------------------------------|-----------------------------------------------|----------|----------------------------------------------|

| Fast Read Quad<br>I/O                                       | EBh | CA15-8(4X) | CA7-0(4X) | 8 Dummy<br>clock cycles<br>(outputs High Z)<br>(Note 4) | D7-0(4X)                                      | D7-0(4X) |                                              |

| Quad Program<br>Data Load 4X                                | 32h | CA15-8     | CA7-0     | D7-0(4X)                                                | D7-0(4X)                                      | D7-0(4X) | 2 clock cycles to<br>input 1 Byte<br>Data    |

| Quad Program<br>Data Load<br>Random 4X<br>( <b>Note 2</b> ) | 34h | CA15-8     | CA7-0     | D7-0(4X)                                                | D7-0(4X)                                      | D7-0(4X) | 2 clock cycles to<br>input 1 Byte of<br>Data |

|                                                             |     |            | Block Pro | otection operation                                      | es                                            |          |                                              |

| Block<br>Protection<br>Status                               | 7Ah | PA23-16    | PA15-8    | PA7-0                                                   | 8 Dummy<br>clock cycles<br>(Outputs<br>HighZ) | D7-0     |                                              |

| Program PBP Setting (Note 3)                                | 2Ch | PBPA23-16  | PBPA15-8  | PBPA7-0                                                 |                                               |          |                                              |

#### Notes:

- 1. The Program Load random data (84h) operation is similar to Program Load 02h. The 84h command does not clear the data buffer to an all FFh value and will only update the data bytes specified by the command input sequence while the rest of the input buffer remains unchanged. The host must always consider chunks of 32 bytes starting from address 0 to accommodate internal ECC requirements.

- 2. The Quad Program Load (32h) operation is similar to Quad Program Load random data (34h). The 34h command does not clear the data buffer to an all FFh value and will only update the data bytes specified by the command input sequence while the rest of the input buffer remains unchanged. The host must always consider chunks of 32 bytes starting from address 0 to accommodate internal ECC requirements.

- 3. PBPA 23-0 address cycle mapping is described in the Security Features section.

- 4. The number of dummy cycles is 8 cycles for 01Gb/02Gb/04Gb.

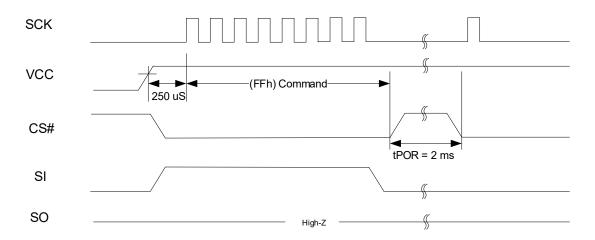

### 3.1 Power up and Reset Commands

During Power on Reset, the first page data of page0 is auto-loaded to the buffer register.

The reset command FFh, does not clear the feature registers but does clear the configuration register bits CONFIG[2:0] placing the device in normal operation.

### 3.2 Write Enable and Write Disable Commands

A WRITE\_EN (06h) command needs to be issued before any OTP, Program Execute and Block Erase operation. A WRITE\_DIS (04h) command is also provided to clear the WSEL bit in the status register (see GET FEATURES and SET FEATURES section).

### 3.3 Hardware Write Protection

Hardware write protection prevents the block protection state from hardware modifications.

The following command sequence enables hardware write protection: The SET FEATURE command is issued on feature address A0h. Then, the Config\_Protect\_en bit-state is set to 0 as the default after power up.

The BRWD bit is operated in conjunction with Config\_Protect\_en bit. When BRWD is set to 1 and WP# is LOW, none of the other block protect register A0h bits [7:2] can be set. The block lock state cannot be changed, regardless of what is unlocked or locked. Also, when the WP#/Hold# disable bit is set to 1, the hardware protected mode is disabled. The default value of BRWD and Config\_Protect\_en bits = 0 after power up.

### 3.4 Read Operation

The PAGE READ (13h) command uses 24-bit address to transfers data from the NAND Flash array to the Data register. After the block/page address is registered, the device starts the transfer from the main array to the data register. During this data transfer busy time of tR, the 0Fh GET FEATURES command can be issued to monitor the operation.

Following successful completion of PAGE READ, one of the following READ commands must be issued to read data out of data buffer:

- 03h or 0Bh (READ buffer 1X)

- 3Bh (Dual Read Output 2X)

- 6Bh (Quad READ Output 4X)

- BBh (Fast READ Dual I/O)

- EBh (Fast READ Quad I/O)

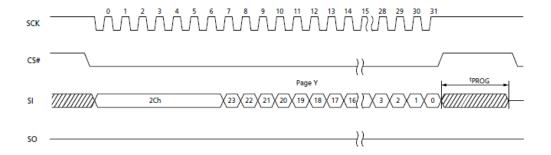

## 3.5 Page Program Operation

A PAGE PROGRAM operation sequence enables the host to input 1 byte to 2176 bytes of data (Page size: 2048 + 128 spare bytes) or 1 byte to 2112 bytes (Page size: 2048 + 64 spare bytes) of data to the data register, and moves the data from the data register to the specified block and page address in the array. Four partial-page programs are allowed on a single page. If more than 2176 bytes are loaded, the additional bytes will be ignored by the data register. The page program sequence starts by issuing 06h (Write Enable Command) followed by 02h (Program Load Command) and 10h (Program Execute Command). the 0Fh GET FEATURES command can be issued to monitor the operation.

Document Number: 002-19205 Rev. H Page 13 of 51

Don't Care

## 3.6 Feature Operations

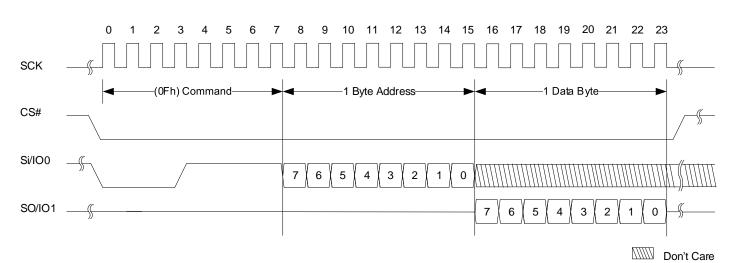

### 3.6.1 Set Features

The SET FEATURE command uses a 1-byte feature address to specify the feature to be modified.

O 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

SCK

(1Fh) Command

1 Byte Address

1 Data Byte

SI/IO0

High-Z

Figure 8. SET FEATURE Timing Diagram

### 3.6.2 Get Features

The GET FEATURE command uses a 1-byte feature address to specify the feature to be read.

Figure 9. GET FEATURE Timing Diagram

### 3.7 Feature Registers

There are 3 registers with the following addresses: A0h,B0h and C0h. While the Set Feature commands may only writes in some of the registers, the Get Feature commands allows reading back the content of all these registers. During Get Feature operation, the same status register is continuously outputed until CS# goes high.

The feature registers are volatile. Each POR will reset these registers to the default value. The Reset (FFh) only clears the configuration bits (B0[7,1,0]) to zero.

Table 7 : Feature Address A0h (Block Protect Register R/W, protected when WP# pin = 0)

| Bit | Symbol                         | Parameter                       | Default | Description                                                                                                                                                                                                                                                                                                             |

|-----|--------------------------------|---------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BRWD <sup>1</sup>              | Block Register Write<br>Disable | 0       | 1b: Disable update of the A0[7:0] when WP# Low Ob: Enable update of the A0[7:0] (Default)                                                                                                                                                                                                                               |

| 6   | AVBP_BL[3] <sup>1</sup>        | AVBP Lock 3                     | 1       | Volatile Block protection based on                                                                                                                                                                                                                                                                                      |

| 5   | AVBP_BL[2] <sup>1</sup>        | AVBP Lock 2                     | 1       | addressable blocks in the device                                                                                                                                                                                                                                                                                        |

| 4   | AVBP_BL[1] <sup>1</sup>        | AVBP Lock 1                     | 1       | 0000b: All Blocks Unlocked                                                                                                                                                                                                                                                                                              |

| 3   | AVBP_BL[0] <sup>1</sup>        | AVBP Lock 0                     | 1       | 0001b: 1/1024 Blocks Locked 0010b: 1/512 Blocks Locked 0011b: 1/256 Blocks Locked 0100b: 1/128 Blocks Locked 0101b: 1/64 Blocks Locked 0110b: 1/32 Blocks Locked 0111b: 1/16 Blocks Locked 1000b: 1/8 Blocks Locked 1001b: 1/4 Blocks Locked 1011b: All Blocks Locked 1011b: All Blocks Locked 1111b: All Blocks Locked |

| 2   | AVBP_BL_U <sup>1</sup>         | AVBP Lock Upper/Lower range     | 1       | 1: Protect Upper blocks 0: Protect Lower blocks                                                                                                                                                                                                                                                                         |

| 1   | Config_Protect_en <sup>1</sup> | WP#/Config_Protect enable       | 0       |                                                                                                                                                                                                                                                                                                                         |

| 0   | Reserved                       | Reserved                        | 0       |                                                                                                                                                                                                                                                                                                                         |

Table 8 : Feature Address A0h protection

|        | WP# pin     | 0 | 1            | 1              | 1            | 1            |

|--------|-------------|---|--------------|----------------|--------------|--------------|

| State  | A0h[7]=BRWD | Χ | 0            | 0              | 1            | 1            |

|        | A0h[1]      | Χ | 0            | 1              | 1            | 0            |

|        | A0h[1]      | R | W/R          | W/R            | W/R          | W/R          |

| Effect |             |   | A0h[7:2] = R | A0h[7:2] = W/R | A0h[7:2] = R | A0h[7:2] = R |

| Ellect | A0h[7:2]    | R | Protected By | AUN[/:2] = W/R | Protected By | Protected By |

|        |             |   | A0h[1]=0     |                | A0h[7]=1     | A0h[1]=0     |

1) A0h[1]= 0

A0h[7:2] R/W: Write operation depends on WP#, A0h[1], and A0h[7] values

- 2) For Data Security, bit (A0h[1]) must be enabled first before block unlock region is set

- 3) Feature address A0h command is allowed to be issued in OIP Ready status

Page 16 of 51

Table 9 : Feature Address B0h (Configuration Register R/W, protected when WP# pin = 0)

| Bit | Symbol     | Parameter                | Default | Description                                                                                                                                                                   |

|-----|------------|--------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Config[2]  | Configuration bit 2      | 0       | Config[2:0]                                                                                                                                                                   |

| 6   | Config[1]  | Configuration bit 1      | 0       | 000: (default) Normal Operation 010: Access OTP Area/parameter page / Unique ID (Note 1) 110: Access to OTP data protection bit to lock OTP area 111: Access to PBP lock-down |

| 5   | AVBP_LD_EN | Advance Lock down enable | 0       | 1: AVBP_Lock down is enabled A0[7:0] and B0[5] are locked until power down.  0: AVB_Lock_down is disabled                                                                     |

| 4   | ECC_Enable | ECC_Enable               | 1       | Must be always set to 1                                                                                                                                                       |

| 3   | Reserved   | Reserved                 | 0       |                                                                                                                                                                               |

| 2   | Reserved   | Reserved                 | 0       |                                                                                                                                                                               |

| 1   | Config[0]  | Configuration bit 0      | 0       | See Config[2:1] description                                                                                                                                                   |

| 0   | Reserved   | Reserved                 | 0       |                                                                                                                                                                               |

<sup>1)</sup> AVBP\_LD\_EN when set to 1, this bit along with the Block Protection register [6:0] can only be cleared during POR

<sup>2)</sup> Feature address B0h command is allowed to be issued in OIP Ready status

Table 10 : Feature Address C0h (Status Register R Only)

| Bit | Symbol   | Parameter                  | Default | Description                                                                                                           |

|-----|----------|----------------------------|---------|-----------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Reserved                   | 0       |                                                                                                                       |

| 6   | Reserved | Reserved                   | 0       |                                                                                                                       |

| 5   | ECCS1    | ECC status                 | 0       | 11 = 5-6 (Rewrite recommended)<br>10 = 3-4 errors corrected                                                           |

| 4   | ECCS0    | register[1:0] <sup>1</sup> | 0       | 01 = 1-2 errors corrected<br>00 = Normal or uncorrectable                                                             |

| 3   | P_Fail   | Program fail               | 0       | Program failure occurred     Operation passed                                                                         |

| 2   | E_Fail   | Erase fail                 | 0       | 1: Erase Failure occurred 0: Operation passed                                                                         |

| 1   | WEL      | Write enable latch         | 0       | 1: Write Enabled<br>0: Write Disabled                                                                                 |

| 0   | OIP      | Operation in progress      | 0       | Device is busy with executing commands:     Reset, Program Execute, Page Read, Block     Erase     O: Device is ready |

<sup>1:</sup> SR [5:4] defines the number of corrections.

Document Number: 002-19205 Rev. H Page 17 of 51

<sup>2.</sup> A Program and Erase fails include a block being protected (Array blocks + OTP) for 1Gb/2Gb densities

A Program fail does not include OTP block for 4Gb density

### 3.8 Read ID

| Byte | Description     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Value |

|------|-----------------|---|---|---|---|---|---|---|---|-------|

| 0    | Manufacturer ID | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 01h   |

| 1    | Device ID: 01G  | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 15h   |

| 1    | Device ID: 02G  | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 25h   |

| 1    | Device ID: 04G  | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 35h   |

### 3.9 Read Unique ID

#### Read Unique ID located in OTP page 0

- Use SET FEATURES command (1Fh) with feature address B0h and data value of 50h for ECC enabled

- Page Read command (13h) with Block/Page address:

- 0x180 for unique ID (OTP page 0)

- -GET FEATURE command (0Fh) with feature address C0h to check OIP bit ready

- Read Buffer (03h) command to read the data out

- Use SET FEATURES command (1Fh) with feature address B0h and data value with Config[2:0] = 000b to exit.

- Or use RESET (FFh) command to clear the configuration bits and return to normal mode.

### 3.10 One\_Time Programmable (OTP)

The device contains a one-time programmable (OTP) area, that consists of (62 pages), accessed by SET/GET FEATURES commands

### 3.10.1 OTP Read

### OTP Read: 62 pages accessible for user data located in Block #6 from page 2 to page 63

- Use SET FEATURES command (1Fh) with feature address B0h and data value of 50h.

- Page Read command (13h) with Block/Page address (0x182h-0x19Fh)

GET FEATURE command (0Fh) with feature address C0h to check OIP bit ready

- Read Buffer (03h) command to read the data out

- Use SET FEATURES command (1Fh) with feature address B0h and data value with Config[2:0] = 000b to exit

- Or use RESET (FFh) command to clear the configuration bits and return to normal mode.

### 3.10.2 OTP Program

### OTPProgram: 62 pages accessible for user data located in Block 6 from page 2 to page 63

- Use SET FEATURES command (1Fh) with feature address B0h and data value of 50h for ECC enabled

- Use Write Enable command 06h

- Program using Load command x1 (02h), Quad Program Data Load (32h) or random program data load with data

- Program Execute command x1 (10h) with Block/Page address (0x182h-0x19Fh)

- Use GET FEATURE command (0Fh) with feature address C0h to check OIP bit ready

- Use SET FEATURES command (1Fh) with feature address B0h and value with Config[2:0] = 000b to exit

- After tPROG time, use GET FEATURE command (0Fh) with feature address C0h to verify P Fail bit is not set.

Document Number: 002-19205 Rev. H Page 18 of 51

### 3.10.3 OTP Data Protection and Program Prevention

This mode is used to prevent further programming of the pages in the OTP area. The following sequence is used to protect and prevent further programming of the OTP area:

- Use SET FEATURES command (1Fh) with feature address B0h and Config [2:0] = 110b

- Use Write Enable command 06h

- Program execute command (10h) with row address 00h

- Verify until OIP bit not busy and P\_FAIL bit 0 using GET FEATURE command (0Fh) with status register address (C0h)

### 3.11 Internal Data Move (S35ML02G3, S35ML04G3)

The copy back feature is intended to quickly and efficiently rewrite data stored in one page without utilizing an external memory. Since the time-consuming cycles of serial access and re-loading cycles are removed, the system performance is greatly improved. The benefit is especially obvious when a portion of a block needs to

be updated and the rest of the block also needs to be copied to the newly assigned free block. For S35ML02G3/ S35ML04G3, the source and destination pages in the Copy Back Program sequence must belong to the same device plane (same BA[0]). If the random data is not sequential, another PROGRAM LOAD RANDOM DATA (84h) command must be issued with the new column address.

The internal data move command sequence is as follows:

- Page Read command (13h)

- Write Enable command (06h)

- Program Load Random Data command (84h)

- Program Execute command (10h)

- Get Feature command (0Fh) Read the Status

Document Number: 002-19205 Rev. H Page 19 of 51

## 3.12 Read Parameter Page

- Use SET FEATURES command (1Fh) with feature address B0h and data value of 50h for ECC enabled

- Page Read command (13h) with Block/Page address:

- 0x181 for Parameter Page (located OTP page 1)

- GET FEATURE command (0Fh) with feature address C0h to check OIP bit ready

- Read Buffer (03h) command to read the data out

- Use SET FEATURES command (1Fh) with feature address B0h and data value with Config[2:0] = 000b to exit

- Or use RESET (FFh) command to clear the configuration bits and return to normal mode.

**Table 11: Parameter Page Description**

| Byte  | O/M | Description                                                                                                                                                                                                                                                                                | Values                                                                                         |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|       |     | Revision Information and Features Block                                                                                                                                                                                                                                                    | ·                                                                                              |

| 0-3   | М   | Parameter page signature                                                                                                                                                                                                                                                                   | 4Fh, 4Eh, 46h, 49h                                                                             |

| 4-5   | М   | Revision number  2-15 Reserved (0)  1 1 = supports ONFI version 1.0  0 Reserved (0)                                                                                                                                                                                                        | 00h, 00h                                                                                       |

| 6-7   | М   | Features supported  5-15 Reserved (0)  4 1 = supports odd to even page Copyback  3 1 = supports interleaved operations  2 1 = supports non-sequential page programming  1 1 = supports multiple LUN operations  0 1 = supports 16-bit data bus width                                       | 00h, 00h                                                                                       |

| 8-9   | М   | Optional commands supported  6-15 Reserved (0)  5 1 = supports Read Unique ID (contact factory)  4 1 = supports Copyback  3 1 = supports Read Status Enhanced  2 1 = supports Get Features and Set Features  1 1 = supports Read Cache commands  0 1 = supports Page Cache Program command | ML01G3: 24h, 00h<br>ML02G3 / ML04G3: 34h, 00                                                   |

| 10-31 |     | Reserved (0)                                                                                                                                                                                                                                                                               | 00h                                                                                            |

|       | L   | Manufacturer Information Block                                                                                                                                                                                                                                                             | •                                                                                              |

| 32-43 | М   | Device manufacturer (12 ASCII characters)                                                                                                                                                                                                                                                  | 53h, 50h, 41h, 4Eh, 53h, 49h, 4Fh, 4Eh,<br>20h, 20h, 20h, 20h                                  |

| 44-63 | М   | Device model (20 ASCII characters)                                                                                                                                                                                                                                                         | \$35ML01G3: 53h, 33h, 35h, 4Dh, 4Ch, 30h, 31h, 47h, 33h, 20h, 20h, 20h, 20h, 20h, 20h, 20h, 20 |

| 64    | М   | JEDEC manufacturer ID                                                                                                                                                                                                                                                                      | 01h                                                                                            |

| 65-66 | 0   | Date code                                                                                                                                                                                                                                                                                  | 00h                                                                                            |

| 67-79 |     | Reserved (0)                                                                                                                                                                                                                                                                               | 00h                                                                                            |

|       |     | Memory Organization Block                                                                                                                                                                                                                                                                  |                                                                                                |

| 80-83 | М   | Number of data bytes per page                                                                                                                                                                                                                                                              | 00h, 08h, 00h, 00h                                                                             |

Document Number: 002-19205 Rev. H Page 20 of 51

**Table 11. Parameter Page Description (Continued)**

| Byte    | O/M | Description                                                                                                                                                                                                                              | Values                                                                                                |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 84-85   | М   | Number of spare bytes per page                                                                                                                                                                                                           | S35ML01G3 (64B spare): 40h, 00h<br>S35ML01G3 (128B spare): 80h, 00h<br>S35ML02G3/ S35ML04G3 :80h, 00h |

| 86-89   | М   | Number of data bytes per partial page                                                                                                                                                                                                    | 00h, 02h, 00h, 00h                                                                                    |

| 90-91   | М   | Number of spare bytes per partial page                                                                                                                                                                                                   | S35ML01G3 (64B spare): 10h, 00h<br>S35ML01G3 (128B spare): 20h, 00h<br>S35ML02G3/ S35ML04G3: 20h, 00h |

| 92-95   | М   | Number of pages per block                                                                                                                                                                                                                | 40h, 00h, 00h, 00h                                                                                    |

| 96-99   | М   | Number of blocks per logical unit (LUN)                                                                                                                                                                                                  | \$35ML01G3: 00h, 04h, 00h, 00h<br>\$35ML02G3: 00h, 08h, 00h, 00h<br>\$35ML04G3: 00h, 10h, 00h, 00h    |

| 100     | M   | Number of logical units (LUNs)                                                                                                                                                                                                           | 01h                                                                                                   |

| 101     | М   | Number of address cycles 4-7 Column address cycles 0-3 Row address cycles                                                                                                                                                                | 00h                                                                                                   |

| 102     | М   | Number of bits per cell                                                                                                                                                                                                                  | 01h                                                                                                   |

| 103-104 | М   | Bad blocks maximum per LUN                                                                                                                                                                                                               | S35ML01G3: 14h, 00h<br>S35ML02G3: 28h, 00h<br>S35ML04G3: 50h, 00h                                     |

| 105-106 | М   | Block endurance                                                                                                                                                                                                                          | 08h, 04h (–40°C to 85°C)<br>06h, 04h (–40°C to 105°C)                                                 |

| 107     | M   | Guaranteed valid blocks at beginning of target                                                                                                                                                                                           | 08h                                                                                                   |

| 108-109 | М   | Block endurance for guaranteed valid blocks                                                                                                                                                                                              | 00h, 00h                                                                                              |

| 110     | М   | Number of programs per page                                                                                                                                                                                                              | 04h                                                                                                   |

| 111     | М   | Partial programming attributes 5-7 Reserved 4 1 = partial page layout is partial page data followed by partial page spare 1-3 Reserved 0 1 = partial page programming has constraints                                                    | 00h                                                                                                   |

| 112     | М   | Number of bits ECC correctability                                                                                                                                                                                                        | 00h                                                                                                   |

| 113     | М   | Number of interleaved address bits 4-7 Reserved (0) 0-3 Number of interleaved address bits                                                                                                                                               | 00h, 00h                                                                                              |

| 114     | 0   | Interleaved operation attributes  4-7 Reserved (0)  3 Address restrictions for program cache  2 1 = program cache supported  1 1 = no block address restrictions  0 Overlapped / concurrent interleaving support                         | 00h, 00h                                                                                              |

| 115-127 |     | Reserved (0)                                                                                                                                                                                                                             | 00h                                                                                                   |

|         |     | Electrical Parameters Block                                                                                                                                                                                                              |                                                                                                       |

| 128     | М   | I/O pin capacitance                                                                                                                                                                                                                      | 0Ah                                                                                                   |

| 129-130 | М   | Timing mode support 6-15 Reserved (0) 5 1 = supports timing mode 5 4 1 = supports timing mode 4 3 1 = supports timing mode 3 2 1 = supports timing mode 2 1 1 = supports timing mode 1 0 1 = supports timing mode 0, shall be 1          | 00h, 00h                                                                                              |

| 131-132 | 0   | Program cache timing mode support  6-15 Reserved (0)  5 1 = supports timing mode 5  4 1 = supports timing mode 4  3 1 = supports timing mode 3  2 1 = supports timing mode 2  1 1 = supports timing mode 1  0 1 = supports timing mode 0 | 00h, 00h                                                                                              |

| 133-134 | M   | t <sub>PROG</sub> Maximum page program time (µs)                                                                                                                                                                                         | 58h, 02h                                                                                              |

**Table 11. Parameter Page Description (Continued)**

| Byte    | O/M | Description                                            | Values                                                                                                                                                                   |

|---------|-----|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 135-136 | М   | t <sub>BERS</sub> Maximum block erase time (μs)        | 10h, 27h                                                                                                                                                                 |

| 137-138 | М   | t <sub>R</sub> Maximum page read time (μs)             | FAh, 00h                                                                                                                                                                 |

| 139-140 | М   | t <sub>CCS</sub> Minimum Change Column setup time (ns) | 00h, 00h                                                                                                                                                                 |

| 141-163 |     | Reserved (0)                                           | 00h                                                                                                                                                                      |

|         |     | Vendor Block                                           |                                                                                                                                                                          |

| 164-165 | М   | Vendor specific Revision number                        | 00h                                                                                                                                                                      |

| 166-253 |     | Vendor specific                                        | 00h                                                                                                                                                                      |

|         |     |                                                        | 01G3/64B spare (-40°C to 85°C):1Eh, 94h<br>01G3/64B spare (-40°C to 105°C):94h,BCh<br>01G3/128B spare(-40°C to 85°C):B0h, D2h<br>01G3/128B spare(-40°C to 105°C):3Ah,FAh |

| 254-255 | М   | Integrity CRC                                          | 02G3 (-40°C to 85°C): 7Bh, 66h<br>02G3 (-40°C to 105°C): F1h, 4Eh                                                                                                        |

|         |     |                                                        | 04G3 (-40°C to 85°C) : 05h, 2Dh<br>04G3 (-40°C to 105°C) : 8Fh, 05h                                                                                                      |

|         |     | Redundant Parameter Pages                              |                                                                                                                                                                          |

| 256-511 | М   | Value of bytes 0-255                                   | Repeat Value of bytes 0-255                                                                                                                                              |

| 512-767 | М   | Value of bytes 0-255                                   | Repeat Value of bytes 0-255                                                                                                                                              |

| 768+    | 0   | Additional redundant parameter pages                   | FFh                                                                                                                                                                      |

### Note:

1. O" Stands for Optional, "M" for Mandatory, "N/A" for Not Applicable.

Document Number: 002-19205 Rev. H Page 22 of 51

### 4. ElectricalCharacteristics

### 4.1 Valid Blocks

Table 12. Valid Blocks

| Device    | Symbol          | Min  | Тур | Max  | Unit   |

|-----------|-----------------|------|-----|------|--------|

| S35ML01G3 | $N_{VB}$        | 1004 | _   | 1024 | Blocks |

| S35ML02G3 | N <sub>VB</sub> | 2008 | _   | 2048 | Blocks |

| S35ML04G3 | N <sub>VB</sub> | 4016 | _   | 4096 | Blocks |

### 4.2 Absolute Maximum Ratings

Table 13: Absolute Maximum Ratings

| Parameter               | Symbol | Test conditions | Min  | Тур | Max | Units | Comments |

|-------------------------|--------|-----------------|------|-----|-----|-------|----------|

| Temperature under Bias  | TBIAS  |                 | -50  |     | 125 | °C    |          |

| Storage Temperature     | TSTG   |                 | -65  |     | 150 | °C    |          |

| Input or Output Voltage | VIO    |                 | -0.6 |     | 4.6 | V     |          |

| (3.3V)                  |        |                 |      |     |     |       |          |

| Supply Voltage (3.3V)   | VCC    |                 | -0.6 |     | 4.6 | V     |          |

#### Notes

- 2. Minimum Voltage may undershoot to -2V during transition and for less than 20 ns during transitions.

- 3. Maximum Voltage may overshoot to VCC +2.0V during transition and for less than 20 ns during transitions.

## 4.3 Recommended Operating Conditions

Table 14: Recommended Operating Conditions

| Parameter             | Symbol | Min | Тур | Max | Units |

|-----------------------|--------|-----|-----|-----|-------|

| Vcc Supply Voltage    | Vcc    | 2.7 | 3.3 | 3.6 | V     |

| Ground Supply Voltage | Vss    | 0   | 0   | 0   | V     |

### 4.4 AC Test Conditions

Table 15: AC Test Conditions

| Parameter                      | Value                     |

|--------------------------------|---------------------------|

| Input Pulse Levels             | 0.0 V to V <sub>CC</sub>  |

| Input Rise and Fall Times      | 5 ns                      |

| Input and Output Timing Levels | V <sub>CC</sub> /2        |

| Output Load (2.7V - 3.6V)      | 1 TTL Gate and CL = 30 pF |

Document Number: 002-19205 Rev. H Page 23 of 51

<sup>1.</sup> Except for the rating "Operating Temperature Range", stresses above those listed in the table Absolute Maximum Ratings "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

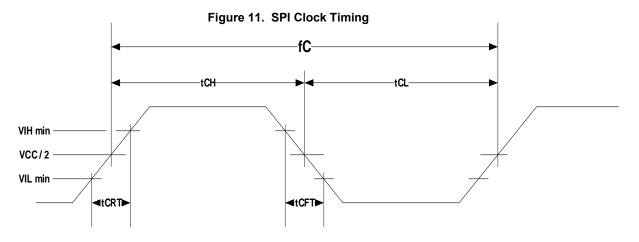

## 4.5 AC Characteristics

**Table 16:** AC Characteristics

| Symbol         | SPI-NOR<br>Symbol | Parameter                 | Min   | Тур | Max | Unit |

|----------------|-------------------|---------------------------|-------|-----|-----|------|

| fC             |                   | Serial Clock Frequency    |       |     | 104 | MHz  |

| tCH            | tWH               | Serial Clock High Time    | 4.316 |     |     | ns   |

| tCL            | tWL               | Serial Clock Low Time     | 4.316 |     |     | ns   |

| tCLCH          | tCRT              | Serial Clock Rise Time    | 1.3   |     |     | V/ns |

| tCHCL          | tCFT              | Serial Clock Fall Time    | 1.3   |     |     | V/ns |

| tSLCH          |                   | CS# Active Setup Time     | 4.316 |     |     | ns   |

| tCHSH          |                   | CS# Active Hold Time      | 4.316 |     |     | ns   |

| tSHCH          |                   | CS# Not Active Setup Time | 2.877 |     |     | ns   |

| tCHSL          |                   | CS# Not Active Hold Time  | 2.877 |     |     | ns   |

| tSHSL /<br>tCS |                   | CS# High Time             | 30    |     |     | ns   |

| tSHQZ          | tDIS              | Output Disable Time       |       |     | 10  | ns   |

## AC Characteristics- cont'd

| tCLQX | tHO    | Output Hold Time                                            | 2    |    |               | ns |

|-------|--------|-------------------------------------------------------------|------|----|---------------|----|

| tDVCH | tSUDAT | Data In Setup Time                                          | 2.5  |    |               | ns |

| tCHDX | tHD    | Data In Hold Time                                           | 1.75 |    |               | ns |

| tHLCH |        | Hold# Low Setup Time relative to Clock                      | 5    |    |               | ns |

| tHHCH |        | Hold# High Setup Time relative to Clock                     | 5    |    |               | ns |

| tCHHL |        | Hold# High Hold Time relative to Clock                      | 5    |    |               | ns |

| tCHHH |        | Hold# Low Hold Time relative to Clock                       | 5    |    |               | ns |

| tHLQZ |        | Hold# Low To High-Z Output                                  |      |    | 12            | ns |

| tHHQX |        | Hold# High To Output                                        |      |    | 9             | ns |

| tCLQV | tV     | Clock Low To Output Valid                                   |      |    | 7<br>(Note 2) | ns |

| tWHSL | tWPS   | WP# Setup Time Before CS# Low                               | 20   |    |               | ns |

| tSHWL | tWPH   | WP# Hold Time After CS# High                                | 100  |    |               | ns |

| tRST  |        | Device Reset Time (Ready/Read/Program/Erase)                |      |    | 5/6/10/500    | μs |

| tR    |        | Data transfer from cell to register tR with internal ECC on |      | 45 | 250           | μs |

Note 1: VCC = 2.7V - 3.6V

Note 2: The maximum value for tCLQV at 105°C = 7.5ns

## 4.6 DC Characteristics

Table 17: DC Characteristics and Operating Conditions

| Parameter                         | Symbol | Test Conditions              | Min       | Тур | Max       | Units |

|-----------------------------------|--------|------------------------------|-----------|-----|-----------|-------|

| Standby current                   | ICC1   | CS# = VIH,<br>Vin= 0V or VCC |           | 10  | 50        | uA    |

| Read Current                      | ICC2   |                              |           | 25  | 35        | mA    |

| Array program current             | ICC3   |                              |           | 20  | 25        | mA    |

| Array erase current               | ICC4   |                              |           | 20  | 25        | mA    |

| Input leakage current             | ILI    |                              |           |     | ±10       | uA    |

| Output leakage current ILO        | ILO    |                              |           |     | ±10       | uA    |

| DC Input high voltage             | VIH    |                              | VCC * 0.8 | 8   | VCC + 0.3 | V     |

| DC Input low voltage              | VIL    |                              | -0.3      |     | VCC * 0.2 | V     |

| Output high voltage               | VOH    | IOH=-400 μA                  | 2.4       |     |           | V     |

| Output low voltage                | VOL    | IOL=2.1mA                    |           |     | 0.4       | V     |

| Erase and program lockout voltage | VLKO   |                              |           | 1.8 |           | V     |

## 4.7 Pin Capacitance

**Table 18:** Pin Capacitance (TA = 25°C, f = 1.0 MHZ)

| Parameter      | Symbol          | Test Condition       | Min | Max | Unit |

|----------------|-----------------|----------------------|-----|-----|------|

| Input          | C <sub>IN</sub> | V <sub>IN</sub> = 0V | _   | 10  | pF   |

| Input / Output | C <sub>IO</sub> | V <sub>IL</sub> = 0V | _   | 10  | pF   |

## 4.8 Program / Erase Characteristics

**Table 19:** Program / Erase Characteristics

| Parameter                                                        | Description | Min | Тур | Max | Unit   |

|------------------------------------------------------------------|-------------|-----|-----|-----|--------|

| Program Time                                                     | tPROG       |     | 350 | 600 | uS     |

| Block Erase Time                                                 | tBERS       |     | 4   | 10  | ms     |

| Number of partial Program Cycles in the same page (Main + Spare) | NOP         |     |     | 4   | Cycles |

| Power on Reset Time                                              | tPOR        |     |     | 2   | ms     |

Document Number: 002-19205 Rev. H Page 27 of 51

## 5. Security Features

The security features below provide block protection from program and erase operations. Two security methods are described below:

Advanced Volatile Block Protection (AVBP)

The AVBP parameter settings are stored in registers that can accessed through Set and Get features commands. Power cycling will reset the settings to the default status (all blocks protected on power up). This AVBP method can protect one range of contiguous blocks. The Set Feature command must be issued to alter the state of the AVBP. After power-up, the device is in the locked state by default.

· Permanent Block Protection (PBP)

The PBP parameter settings will be maintained after a power cycle. The PBP method can protect up to 64 blocks (blocks 0 to 63) organized in groups of 4 contiguous blocks. Each group can be protected individually and are permanently protected.

### 5.1 Volatile Block Protection (VBP) Overview

The AVBP feature can protect all blocks, or one selected range of contiguous blocks, from erase and program operations. After a power-cycle, all blocks are protected as the AVBP\_BL[3:0] bits are high (see Block protection feature register (A0h).)The SET FEATURE command must be issued to alter the state of block protection. A Reset command will not reset the A0h register and therefore will not modify the block protection state. When a PROGRAM/ERASE command is issued to a locked block, a status register P\_Fail bit or E\_Fail bit will beset to indicate the operation failure.

Document Number: 002-19205 Rev. H Page 28 of 51

The following tables provides block protection range addresses for each device densities and page size.

Table 20: AVBP block protection range (Address Min and Max)

1Gb, 2KB page devices