### **General Description**

The AAT4712 is a programmed, current limited P-channel MOSFET power switch designed for high-side load-switching applications for SSD memory buffer saving solutions. With the programmed current limit, the AAT4712 ensures that the power ratings of the host are not exceeded and balances the system load and supercap charging current automatically to provide enough system load current in top-priority. The integrated discharge path control assures that the system load can still be supported in the short term when the input power has not fully charged the supercap. The current limit is programmed by an external resistor allowing  $\pm 10\%$  accuracy at room temperature.

The AAT4712 integrates discharge path for SYS (to system load) from VCC input or OUT input (connect to supercap). The low  $R_{DS(ON)}$  from OUT to SYS prolongs the supercap backup time when VCC drops below a threshold voltage which is programmed by an external resistor from ADJ to ground.

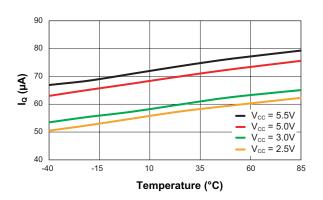

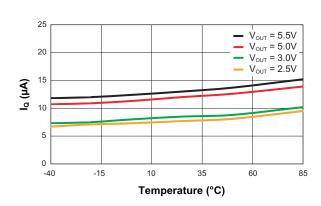

The AAT4712 incorporates a POK function which can indicate system input power good. An ADJ pin is provided with the addition of an external resistor for setting the input power good detect threshold. The AAT4712 also incorporates a supercap charge ready (RDY) indicate function. The quiescent supply current is typically a low 70µA from the discharge path of VCC to SYS.

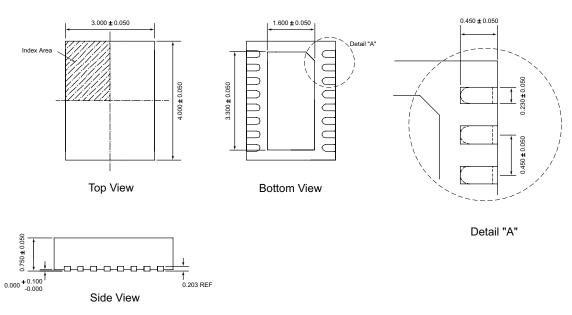

The AAT4712 is available in a 16-pin TDFN34 package and is specified over a -40 to 85°C temperature range.

#### **Features**

- V<sub>CC</sub> Range: 2.5V 5.5V

- Input Current Limits:

- 150mA 2400mA

- ±10% Current Accuracy at 2A Input Current Limit Setting

- Low Quiescent Current:

- 70µA Typical (VCC Input)

- 12μA Typical (OUT Input)

- Under-Voltage Lockout

- Integrated Discharge Path for SYS (to System Load) from VCC Input or OUT Input (Connect to Supercap)

- Maximum  $100m\Omega$  R<sub>DS(ON)</sub> from OUT to SYS at 5V V<sub>CC</sub>

- · Reverse Blocking Protection

- Power Loop Current Reduction

- Over-Temperature Protection

- SYS Short Circuit Protection

- Input Power Good Detect Threshold Setting (ADJ)

- Input Power Good Indicate (POK)

- Supercap Charge Ready (RDY) Output

- Temperature Range: -40 to 85°C

- 16-Pin TDFN34 Package

### **Applications**

• SSD

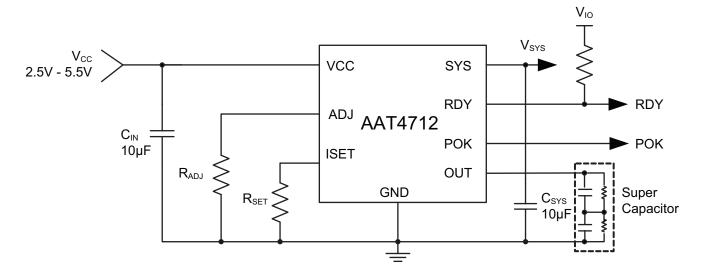

## **Typical Application**

## Power Path with Input Current Limit and Capacitor Charger

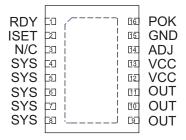

## **Pin Descriptions**

| Pin #         | Symbol | Function                                                                                                                                                                              |  |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1             | RDY    | Supercap charge ready output, initiated when the capacitor is 98% charged. Open drain, active high.                                                                                   |  |

| 2             | ISET   | nput current-limit set input. A resistor from ISET to ground is necessary and sets the maximum curent limit for the switch. The current limit can be programmed from 150mA to 2000mA. |  |

| 3             | N/C    | No connect.                                                                                                                                                                           |  |

| 4, 5, 6, 7, 8 | SYS    | ystem power output supplied from the VCC input or OUT input.                                                                                                                          |  |

| 9, 10, 11     | OUT    | onnect to super capacitor from OUT to GND.                                                                                                                                            |  |

| 12, 13        | VCC    | Input pins to the P-channel MOSFET source. Connect a 10µF capacitor from VCC to GND.                                                                                                  |  |

| 14            | ADJ    | Input power good detect threshold. An internal $50k\Omega$ resistor is integrated between ADJ and VCC.                                                                                |  |

| 15            | GND    | Device ground connection.                                                                                                                                                             |  |

| 16            | POK    | Input power good indicator. Push pull, active high.                                                                                                                                   |  |

## **Pin Configuration**

TDFN34-16 (Top View)

## Power Path with Input Current Limit and Capacitor Charger

## Absolute Maximum Ratings<sup>1</sup>

| Symbol                                                 | Description                              | Value                        | Units |

|--------------------------------------------------------|------------------------------------------|------------------------------|-------|

| V <sub>P</sub>                                         | VCC, OUT to GND                          | -0.3 to 6                    | V     |

| V <sub>RDY</sub> , V <sub>POK</sub> , V <sub>ADJ</sub> | RDY, POK, ADJ to GND                     | -0.3 to V <sub>P</sub> + 0.3 | V     |

| V <sub>ISET</sub> , V <sub>SYS</sub>                   | ISET, SYS to GND                         | -0.3 to V <sub>P</sub> + 0.3 | V     |

| $I_{MAX}$                                              | Maximum Continuous Switch Current        | 2.5                          | Α     |

| T <sub>1</sub>                                         | Operating Junction Temperature Range     | -40 to 150                   | °C    |

| T <sub>STG</sub>                                       | Storage Temperature                      | -40 to 150                   | °C    |

| T <sub>LEAD</sub>                                      | Maximum Soldering Temperature (at Leads) | 300                          | °C    |

## Thermal Characteristics<sup>2</sup>

| Symbol         | Description                             | Value | Units |

|----------------|-----------------------------------------|-------|-------|

| $\Theta_{JA}$  | Maximum Thermal Resistance <sup>3</sup> | 50    | °C/W  |

| P <sub>D</sub> | Maximum Power Dissipation <sup>3</sup>  | 2     | W     |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

<sup>2.</sup> Mounted on a FR4 board.

<sup>3.</sup> Derate 50mW/°C above 25°C.

## Power Path with Input Current Limit and Capacitor Charger

## **Electrical Characteristics<sup>1</sup>**

$V_{CC}$  = 2.5V to 5.5V,  $T_A$  = -40°C to 85°C unless otherwise noted. Typical values are at  $T_A$  = 25°C

| Symbol                  | Description                             | Conditions                                                     | Min                    | Тур  | Max  | Units                |

|-------------------------|-----------------------------------------|----------------------------------------------------------------|------------------------|------|------|----------------------|

| $V_{CC}$                | Normal Operation Voltage                |                                                                | 2.5                    |      | 5.5  | V                    |

| $I_Q$                   | V <sub>CC</sub> Quiescent Current       | I <sub>OUT</sub> = 0, No Load at SYS Pin                       |                        | 70   | 120  | μΑ                   |

| $I_{OUT\_OP}$           | OUT Operating Current                   | $V_{OUT} = 5V$ , $V_{CC} = GND$ , No Load at SYS Pin           |                        | 12   | 30   | μΑ                   |

|                         | V <sub>CC</sub> Under-Voltage Lockout   | Falling Edge                                                   |                        | 2.1  | 2.4  | V                    |

| $V_{UVLO\_VCC}$         | V <sub>CC</sub> Offder-Voltage Lockout  | Hysteresis                                                     |                        | 150  |      | mV                   |

| V <sub>UVLO_OUT</sub>   | OUT Under-Voltage Lockout               | Falling Edge                                                   |                        | 1.8  | 2    | V                    |

| V UVLO_OUT              | Our officer voltage Lockout             | Hysteresis                                                     |                        | 250  |      | mV                   |

| R <sub>DS(ON)_SWA</sub> | V <sub>CC</sub> to SYS On-Resistance    | $V_{CC} = 5V$ , $R_{SET} = 1.24M\Omega$ , $I_{LOAD} = 600mA$   |                        | 50   | 100  | mΩ                   |

| TOS(ON)_SWA             | VCC to 313 off Resistance               | $V_{CC} = 3.3V$ , $R_{SET} = 1.24M\Omega$ , $I_{LOAD} = 600mA$ |                        | 65   | 120  | 11122                |

| R                       | V <sub>CC</sub> to OUT On-Resistance    | $V_{CC} = 5V$ , $R_{SET} = 1.24M\Omega$ , $I_{LOAD} = 600mA$   |                        | 140  | 300  | $m\Omega$            |

| R <sub>DS(ON)_SWB</sub> |                                         | $V_{CC} = 3.3V$ , $R_{SET} = 1.24M\Omega$ , $I_{LOAD} = 600mA$ |                        | 160  | 320  | 11152                |

| R <sub>DS(ON)_SWC</sub> | OUT to SYS On-Resistance                | $V_{OUT} = 3V \sim 5V$                                         |                        |      | 100  | mΩ                   |

| I <sub>LIMHACC</sub>    | Input High Current Limit Accuracy       | $R_{SET} = 1.24M\Omega$ , $T_A = 25$ °C                        | 1800                   | 2000 | 2200 | mA                   |

| $I_{LIM(MIN)}$          | Minimum Input Current Limit             |                                                                |                        | 150  |      | mA                   |

| $T_{RESP}$              | Current Limit Response Time             | $V_{CC} = 5V$ , $R_{SET} = 1.24M\Omega$                        |                        | 2    |      | μs                   |

| $T_{DEL(OFF)}$          | Turn-Off Delay Time                     | $V_{CC} = 5V$                                                  |                        | 0.4  | 10   | μs                   |

| T <sub>sw</sub>         | OUT to SYS Switch Turn On Response Time | VCC Voltage Step-Down Signal from 5V to 4.5V                   |                        | 6    |      | μs                   |

| $V_{ADJ}$               | ADJ Pin Voltage with Trigger Comparator |                                                                |                        | 1.2  |      | V                    |

| T <sub>DETECT</sub>     | ADJ Pin Detect Delay Time               | ADJ Voltage Step Down Signal from 1.3V to 1.1V                 |                        | 2    |      | μs                   |

| $V_{POK(L)}$            | Output Low Voltage                      | ADJ ≤ 1.2V                                                     |                        |      | 0.4  | V                    |

| V <sub>POK(H)</sub>     | Output High Voltage                     | ADJ > 1.2V                                                     | 0.8<br>V <sub>cc</sub> |      |      | V                    |

| $V_{RDY}$               | Supercap Charge Ready Trip Threshold    | V <sub>OUT</sub> Rising, T <sub>A</sub> = 25°C                 |                        | 98   |      | % of V <sub>cc</sub> |

| $V_{RDYSYS}$            | Supercap Charge Ready Hysteresis        |                                                                |                        | 200  |      | mV                   |

| $V_{RDY(L)}$            | RDY Output Low Voltage                  | RDY Pin Sinks 1mA                                              |                        |      | 0.4  | V                    |

| OTMP                    | Shutdown Temperature                    |                                                                |                        | 150  |      | °C                   |

| T <sub>HYS</sub>        | Over-Temperature Shutdown Hysteresis    |                                                                |                        | 15   |      | °C                   |

<sup>1.</sup> The AAT4712 is guaranteed to meet performance specifications over the -40°C to 85°C operating temperature range and is assured by design, characterization and correlation with statistical process controls.

## Power Path with Input Current Limit and Capacitor Charger

## **Typical Characteristics**

#### V<sub>cc</sub> Quiescent Current vs. Temperature

#### **V**<sub>OUT</sub> Quiescent Current vs. Temperature

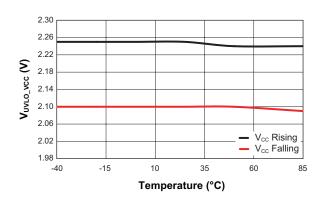

$V_{\text{UVLO\_VCC}}$  vs. Temperature

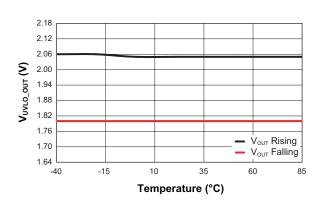

V<sub>UVLO OUT</sub> vs. Temperature

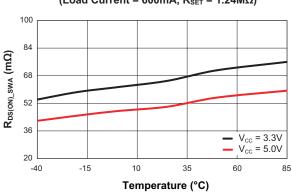

$R_{DS(ON)\_SWA}$  vs. Temperature (Load Current = 600mA,  $R_{SET}$  = 1.24M $\Omega$ )

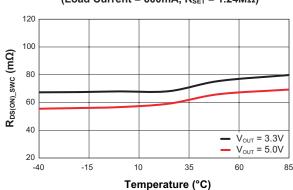

$R_{DS(ON)\_SWC}$  vs. Temperature (Load Current = 600mA,  $R_{SET}$  = 1.24M $\Omega$ )

## Power Path with Input Current Limit and Capacitor Charger

## **Typical Characteristics**

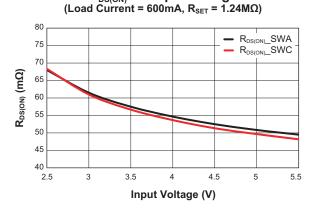

R<sub>DS(ON)</sub> vs. Input Voltage

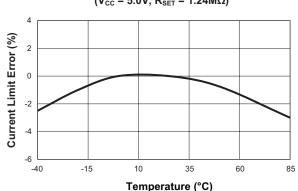

Current Limit Error vs. Temperature (V<sub>CC</sub> = 5.0V, R<sub>SET</sub> = 1.24MΩ)

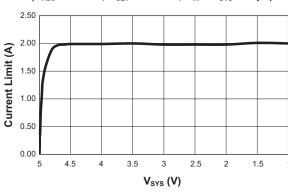

Current Limit vs. SYS Voltage  $(R_{ADJ} = 18.2k\Omega, R_{SET} = 1.24M\Omega, C_{IN} = C_{SYS} = 10\mu F)$

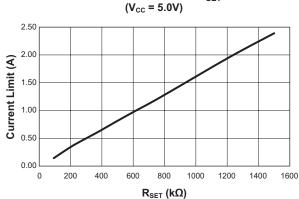

Current Limit vs. R<sub>SET</sub> (V<sub>cc</sub> = 5.0V)

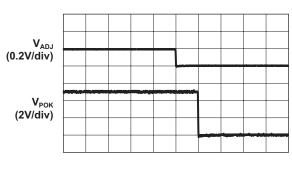

ADJ Detect Delay Time  $(V_{CC} = 5.0V, R_{SET} = 1.24M\Omega)$

Time (0.8µs/div)

POK Delay Time  $(R_{ADJ} = 18.2k\Omega)$

Time (100µs/div)

## **Typical Characteristics**

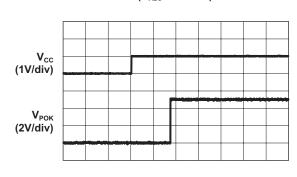

# RDY Delay Time From High to Low $(V_{CC} = 5.0V, R_{SET} = 1.24M\Omega)$

Time (2µs/div)

# RDY Delay Time From Low to High $(V_{CC} = 5.0V, R_{SET} = 1.24M\Omega)$

Time (100µs/div)

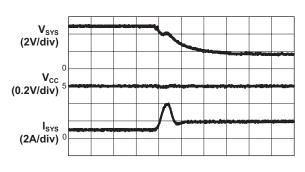

# Current Limit Response ( $V_{CC}$ = 5.0V, $R_{SET}$ = 1.24M $\Omega$ , $R_{LOAD}$ = 5 $\Omega$ to 1 $\Omega$ )

Time (20µs/div)

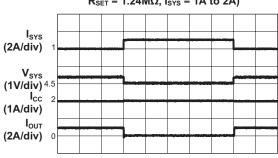

#### Load Transient ( $V_{CC} = 5.0V$ , $V_{OUT} = 2.0V$ , $R_{SET} = 1.24M\Omega$ , $I_{SYS} = 1A$ to 2A)

Time (10ms/div)

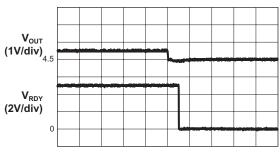

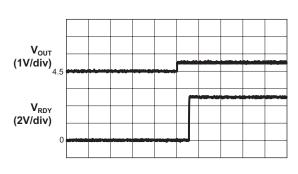

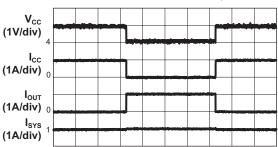

## Discharge Path Switching ( $V_{OUT} = 5.0V$ , $R_{SET} = 1.24M\Omega$ , $R_{ADJ} = 18.2k\Omega$ ,

$(V_{OUT} = 5.0V, R_{SET} = 1.24M\Omega, R_{ADJ} = 18.2k\Omega, V_{CC} = 5V \text{ to } 4V, 1A \text{ Load})$

Time (100ms/div)

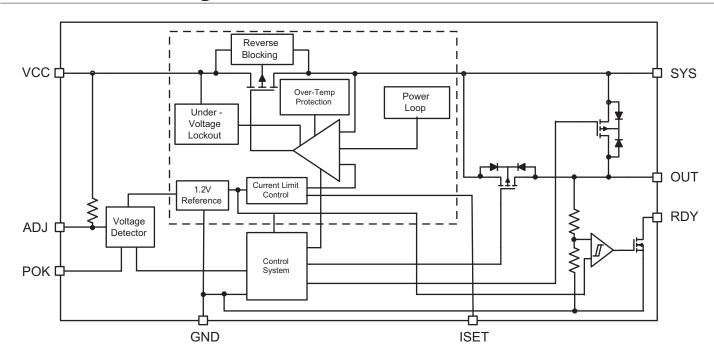

### **Functional Block Diagram**

## **Functional Description**

The AAT4712 is an integrated P-channel MOSFET load switch with adjustable current limits, integrated discharge path, over temperature protection, a power loop and a super capacitor charger. The input current limit control is combined with an over-temperature thermal limit and power loop circuit to provide a comprehensive system to protect the load switch and its supply from load conditions exceeding the supply specifications. The AAT4712 integrates the discharge path for SYS (to system load) from the VCC input or OUT input (connected to supercap) determined by whether VCC is higher than the programmed threshold setting by ADJ through an external resistor.

The input current is limited and is programmed by an external resistor for both system load and supercapacitor charging; system load always has higher priority. The device decreases supercapacitor charging current to provide more current to system load when the system load increases and keeps the host power rating from exceeding the input current limit.

The integrated over-temperature circuits act independently of the input current limit. The device input current limit is activated when the output load current exceeds an internal threshold level. The input current limit threshold in each case is determined by external resistors connected between the ISET pin and ground. The minimum input current limit threshold is specified by  $I_{\text{LIM}(\text{MIN})}.$  If the load condition maintains the device in current limit and the chip temperature reaches a critical point, then an internal power loop will reduce the current to a safe level.

VCC pin under-voltage lockout circuitry ensures that the  $V_{\text{CC}}$  supply is high enough for correct operation of the IC. OUT pin under-voltage lockout circuitry ensures that the  $V_{\text{OUT}}$  supply is high enough for correct operation of the IC when no VCC input power or  $V_{\text{CC}}$  below UVLO voltage. An integrated POK function is adopted to indicate the system input power good.

#### **Setting the Input Current Limit**

The AAT4712 current limit is set via the ISET resistor. The ISET node operates within a window of 0.6V to 1.2V for resistor values ranging from  $93.75k\Omega$  to  $1.5M\Omega$ . Resistor values outside this range are not recommended. The ISET source current varies with the resistor value as shown in Table 1.

$$V_{ISET} = R_{SET} \cdot I_{ISET} = 0.6V \text{ to } 1.2V$$

If the set pin is open circuit or allowed to exceed 2V, all power devices are disabled and the input is disconnected from the output.

#### SYS Load and Capacitor Charge

The input current limit is equal to the SYS current plus the OUT charging current. If the SYS current increases/ decreases, the OUT charging current will automatically decrease/increase accordingly by the device control loop. For example, if the input current limit is programmed to 1A and the SYS load current is 0.5A, then the OUT charging current is 0.5A; if the SYS load current increases to 0.8A, the OUT current decreases to 0.2A accordingly; if the SYS load current decreases to 0.2A, the OUT current increases to 0.8A dynamically.

#### **Discharge Path Control**

When the input voltage drops below the power good detect threshold programmed by the external resistor from ADJ pin to GND and the OUT pin voltage is greater than the  $V_{UVLO\ OUT}$  and SYS pin voltage, the AAT4712 turns on the OUT to SYS switch discharge path after 6µs (T<sub>SW</sub>) response time, then turns off the path of VCC to the SYS P-channel load switch. The OUT to SYS switch remains continuously on until the OUT pin voltage falls below V<sub>UVIO OUT</sub>.

#### **Power Loop**

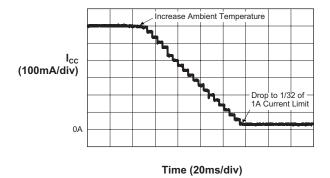

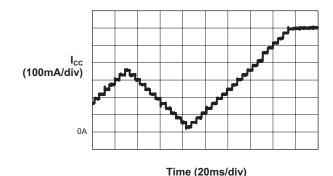

The AAT4712's power loop limits the load current if device power dissipation becomes excessive. The power loop decreases the load current gradually to 1/32 of the current limit set point when the die temperature exceeds 130°C. The load current then increases in increments of 1/32 of the current limit set point until the set current limit point is reached or the die temperature exceeds 130°C. Figures 1 and 2 show the the power loop function as the device temperature increases and decreases at a 1A current limit setting.

| R <sub>SET</sub> Range (Ω) | I <sub>ISET</sub> (μA) | I <sub>LIM</sub> /V <sub>ISET</sub> (A/V) | Current Limit Range (A) | Current Limit              |

|----------------------------|------------------------|-------------------------------------------|-------------------------|----------------------------|

| 1.5M - 750k                | 0.8                    | 2                                         | 2.4-1.2                 | R <sub>SET</sub> *0.8*2    |

| 750k - 375k                | 1.6                    | 1                                         | 1.2-0.6                 | R <sub>SET</sub> *1.6*1    |

| 375k - 187.5k              | 3.2                    | 0.5                                       | 0.6-0.3                 | R <sub>SET</sub> *3.2*0.5  |

| 187.5k - 93.75k            | 6.4                    | 0.25                                      | 0.3-0.15                | R <sub>SET</sub> *6.4*0.25 |

Table 1: R<sub>SET</sub> Values for Setting the Input Current.

Figure 1: AAT4712 Power Loop Function at 1A Current Limit with Ambient Temperature Increasing. Current Limit with Ambient Temperature Decreasing.

Figure 2: AAT4712 Power Loop Function at 1A

The delay time between die temperature measurements varies depending on the load current limit set point. The delay ranges from 0.5ms for a 150mA current limit set point to 4ms for a 2.4A current limit set point.

#### **Over-Temperature Protection**

If the die temperature rises quickly enough to exceed the power loop regulated temperature, over-temperature shutdown disables the device. The over-temperature threshold is 150°C. After over-temperature shutdown, soft start is initiated once the die temperature drops to 135°C.

#### Power OK Indicator (POK)

On initial power-up, if VCC is higher than the power good detect threshold programmed by the external resistor from the ADJ pin to GND, the POK signal switches from low to high after  $2\mu s$  delay time ( $T_{DETECT}$ ) to indicate input power good.

If VCC drops below the power good detect point, the POK signal switches from high to low after  $2\mu s$  delay time ( $T_{DETECT}$ ).

### **Capacitor Charge Ready Indicator (RDY)**

The internal comparator senses the OUT voltage and delivers a high level as ready signal to the external microcontroller when the OUT voltage reaches 98% of the VCC voltage with fixed 200mV hysteresis.

The capacitor charge ready pin (RDY) is an open drain output. A external pull up resistor with a typical value of  $100k\Omega$  is required.

## **Application Information**

#### **Input Current Limit Setting**

The input current limit is programmed by  $R_{\text{SET}}$  from ISET to ground in the range from 150mA to 2.4A. The current limit limits the maximum current of both VCC to SYS and VCC to OUT. The  $R_{\text{SET}}$  can be calculated by:

$$R_{SET} = \frac{I_{LIM}}{1.6}$$

(Current in A, resistance in k $\Omega$ )

Table 2 lists some 1% standard metal film resistor values for current limit settings from 150mA to 2.4A.

| R <sub>SET</sub> (kΩ) | Current Limit (A) |

|-----------------------|-------------------|

| 1500                  | 2.4               |

| 1240                  | 2                 |

| 1000                  | 1.6               |

| 750                   | 1.2               |

| 620                   | 1                 |

| 499                   | 0.8               |

| 374                   | 0.6               |

| 249                   | 0.4               |

| 187                   | 0.3               |

| 93.1                  | 0.15              |

Table 2: Recommended Current Limit R<sub>SET</sub> Values.

### **Power Good Detect Threshold Setting**

The power good detect threshold ( $V_{POK\_TH}$ ) determines the point at which the discharge path changes from VCC – SYS to OUT – SYS if the OUT pin voltage is above  $V_{UVLO\_OUT}$  and the SYS pin voltage. The power good detect threshold is programmed by the external resistor  $R_{ADJ}$  connected from the ADJ pin to GND. The  $R_{ADJ}$  value can be calculated by:

$$R_{ADJ} = \frac{60}{V_{POK TH} - 1.2}$$

(Voltage in V, resistance in k $\Omega$ )

Table 3 summarizes some 1% standard metal film resistor values for various  $V_{\text{POK\_TH}}$  settings.

| R <sub>ADJ</sub> (kΩ) | V <sub>POK_TH</sub> (V) |

|-----------------------|-------------------------|

| 15.8                  | 5.0                     |

| 18.2                  | 4.5                     |

| 20.5                  | 4.0                     |

| 26.1                  | 3.5                     |

| 33.2                  | 3.0                     |

| 47                    | 2.5                     |

Table 3: Recommended Resistor Values for  $V_{POK\_TH}$  Settings.

#### **Discharge Path Control**

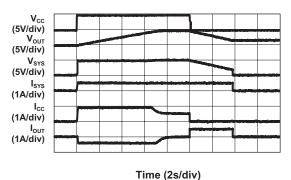

As the AAT4712 powers the system load, the device automatically selects VCC or OUT as the power source. OUT is designed to connect a supercapacitor as a backup source. Figure 3 shows the discharge path control operation at 1A current limit setting. When VCC is powered on from zero to 5V, the SYS voltage also rises to 5V and 500mA current is passed through from VCC to SYS as system load. With the 1A current limit, the additional 500mA is used to charge the supercapacitor via IOUT as shown. After 3.5 seconds, the 550mF supercapacitor is fully charged; the charging current decreases to zero, and ICC current decreases to 500mA. When VCC drops from 5V to zero, the backup power source VOUT provides the 500mA load current to SYS until the supercapacitor voltage is discharged to below the UVLO voltage threshold (typ. 1.8V).

Figure 3: Discharge Path Control with 550mF Supercapacitor at 1A Current Limit Setting and 500mA System Load.

#### **Reverse Blocking**

The internal reverse blocking comparator disconnects the VCC to SYS path by turning off the power PMOSFETs when SYS is higher than VCC minus 18mV, preventing any reverse current from the system load to the input. With 22mV hysteresis, the VCC to SYS path will be reconnected by turning on the power PMOSFETs when the SYS voltage drops to VIN minus 40mV. The reverse blocking comparator has a typical 5µs delay time, which may lead to output voltage ripple on the SYS output at light load. Increasing the SYS output capacitor value can improve the output voltage ripple when the application has special SYS voltage ripple requirements.

#### Input Capacitor

A 10 $\mu$ F capacitor is typically recommended for  $C_{IN}$ .  $C_{IN}$  should be located as close to the device VCC pin as practically possible. Ceramic, tantalum, or aluminum electrolytic capacitors may be selected for  $C_{IN}$ . There is no specific capacitor equivalent series resistance (ESR) requirement for  $C_{IN}$ . However, for higher current operation, ceramic capacitors are recommended for  $C_{IN}$  due to their inherent capability over tantalum capacitors to withstand input current surges from low impedance sources.

#### **System Output Capacitor**

A small output capacitance of approximately  $10\mu F$  is required at the system output. The output capacitor helps to filter the SYS voltage when the device works between reverse blocking and normal operation. For higher output voltage ripple requirements at light load (below 1/3 current limit), a greater output capacitor value is required.

#### **OUT Supercapacitor**

The AAT4712's OUT pin is designed to connect a supercapacitor to ground to give the system a backup when VCC experiences short power interrupts. A supercapacitor offers high capacitance in a small package; it adopts special electrodes and some electrolyte. Three types of electrode materials are suitable for the supercapacitor: high surface area activated carbons, metal oxide, and conducting polymers. The first option is the lowest cost to manufacture; the electrolyte usually is aqueous or organic. An aqueous electrolyte offers low internal resis-

tance but limits the voltage to 1V; the organic allows 2.5V of charge but has higher internal resistance. For higher voltage applications, supercapacitors are connected in series. To prevent any cell from charging overvoltage, a balance resistor is required on a string of more than three cells.

Three parameters should be considered when selecting a supercapacitor. These parameters are capacitance, rated voltage, and ESR. Table 4 shows some recommended supercapacitors. Other parameters such as temperature range, RMS current, leakage current, etc. should also be considered during the system design.

#### **SYS Short Circuit Protection**

The series pass power MOSFET from VCC to SYS limits the current to a low level after the SYS output shorts to ground to protect the device and downstream components. During the fault condition, the power loop is still active to monitor the die temperature and reduce the current when the die temperature exceeds 130°C. Once the short-circuit fault is removed, the SYS voltage recovers to the normal value automatically.

The AAT4712 also includes short-circuit protection circuitry for the discharge path from OUT to SYS to avoid large current discharging through the device over a long term and avoid damage to the device.

#### **PCB Layout Recommendations**

For proper thermal management and to take advantage of the low  $R_{\text{DS(ON)}}$  of the AAT4712, certain circuit board layout rules should be followed:

- 1.  $V_{CC}$ ,  $V_{OUT}$ , and  $V_{SYS}$  should be routed using wide traces.

- 2. GND should be connected to a ground plane. The ground plane area connected to the ground pins should be made as large as possible.

- 3. For best performance,  $C_{\text{IN}}$  and  $C_{\text{SYS}}$  should be placed close to the VCC and SYS pins.

- 4. For maximum power dissipation of the AAT4712 TDFN package, the exposed pad should be soldered to the board ground plane to further increase local heat dissipation. A ground pad below the exposed pad is strongly recommended.

| Manufacturer | Part Number          | Capacitance (mF) | Rated Voltage (V) | ESR<br>(mΩ) | Size LxWxH (mm) |

|--------------|----------------------|------------------|-------------------|-------------|-----------------|

|              | HS 203F              | 250              | 5.5               | 70          | 39x17x2.15      |

| Cap-xx       | HS 211F              | 370              | 5.5               | 55          | 39x17x2.9       |

|              | HS 206F              | 600              | 5.5               | 70          | 39x17x2.4       |

|              | HW 207F              | 450              | 5.5               | 100         | 28.5x17x2.9     |

| TDK          | EDLC152344-551-2F-30 | 550              | 5.5               | 30          | 44x23x1.5       |

| IDK          | EDLC262020-501-2F-50 | 500              | 5.5               | 50          | 20x20x2.6       |

**Table 4: Recommended Supercapacitors**

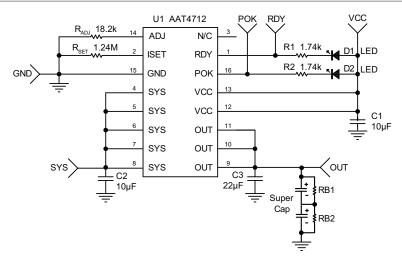

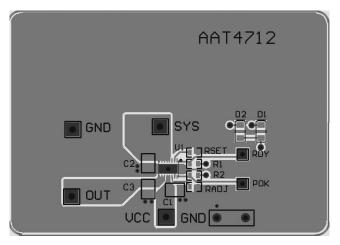

### **Evaluation Board Schematic**

Figure 4: AAT4712 Evaluation Board Schematic.

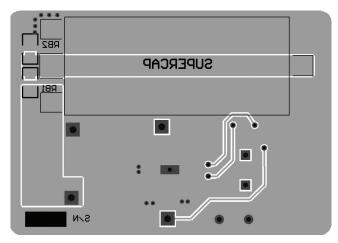

### **Evaluation Board Layout**

a: Top Side

b: Bottom Side

Figure 5: AAT4712 Evaluation Board Layout.

| Component          | Part Number      | Description                                   | Manufacturer |  |

|--------------------|------------------|-----------------------------------------------|--------------|--|

| U1                 | AAT4712          | Current Limited Switch with Capacitor Charger | Skyworks     |  |

| R1,R2              | RC0603FR-071K74L | Res 1.74KΩ 1/10W 1% 0603 SMD                  |              |  |

| R <sub>SET</sub>   | RC0603FR-071M24L | Res 1.24MΩ 1/10W 1% 0603 SMD                  | Yageo        |  |

| R <sub>ADJ</sub>   | RC0603FR-0718K2L | Res 18.2KΩ 1/10W 1% 0603 SMD                  |              |  |

| C1, C2             | GRM21BR61C106K   | Cap Ceramic 10µF 0805 X5R 16V 10%             | Murata       |  |

| C3                 | GRM21BR60J226M   | Cap Ceramic 22µF 0805 X5R 6.3V 20%            | Murata       |  |

| D1, D2             | 0805KRCT         | Red LED 0805                                  | НВ           |  |

| SUPERCAP, RB1, RB2 | Not populated    |                                               |              |  |

Table 5: AAT4712 Evaluation Board Bill of Materials.

## **Ordering Information**

| Package   | Marking¹ | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|----------|------------------------------------------|

| TDFN34-16 | G9XYY    | AAT4712IRN-T1                            |

Skyworks Green<sup>TM</sup> products are compliant with all applicable legislation and are halogen-free. For additional information, refer to *Skyworks Definition of Green*<sup>TM</sup>, document number SQ04-0074.

### Package Information<sup>3</sup>

#### TDFN34-16

All dimensions in millimeters.

- 1. XYY = assembly and date code.

- 2. Sample stock is generally held on part numbers listed in BOLD.

- 3. The leadless package family, which includes QFN, TQFN, DFN, TDFN and STDFN, has exposed copper (unplated) at the end of the lead terminals due to the manufacturing process. A solder fillet at the exposed copper edge cannot be guaranteed and is not required to ensure a proper bottom solder connection.

Copyright © 2012 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks hange its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.

Skyworks, the Skyworks symbol, and "Breakthrough Simplicity" are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by Skyworks manufacturer:

Other Similar products are found below:

TCK111G,LF(S FPF1018 DS1222 TCK2065G,LF SZNCP3712ASNT3G MIC2033-05BYMT-T5 MIC2033-12AYMT-T5 MIC2033-05BYM6-T5 SLG5NT1437VTR SZNCP3712ASNT1G DML1008LDS-7 KTS1670EDA-TR KTS1640QGDV-TR KTS1641QGDV-TR NCV459MNWTBG FPF2260ATMX U6513A MIC2012YM-TR MAX14919ATP+ MC33882PEP TPS2021IDRQ1 TPS2104DBVR MIC2098-1YMT-TR MIC94062YMT TR MP6231DN-LF MIC2026-2YM MIC2075-2YM MIC2095-2YMT-TR MIC94068YML-TR SIP32461DB-T2-GE1 NCP335FCT2G TCK105G,LF(S AP2151DSG-13 MIC94094YC6-TR MIC94093YC6-TR MIC94064YC6-TR MIC2505-1YM MIC94305YMT-TR MIC94081YFT-TR MIC94042YFL-TR MIC94041YFL-TR MIC2005-1.2YM6-TR TPS2032QDRQ1 SIP32510DT-T1-GE3 NCP333FCT2G NCP331SNT1G TPS2092DR TPS2063DR TPS2042P MIC2008YML-TR