# SONiX Technology Co., Ltd.

# SN8F5702 Series Datasheet

8051-based Microcontroller

SN8F5702 SN8F570200 SN8F570202 SN8F570210 SN8F570211 SN8F570212 SN8F570213

## **1** Device Overview

#### 1.1 Features

- Enhanced 8051 microcontroller with reduced instruction cycle time (up to 12 times 80C51)

- Up to 32 MHz flexible CPU frequency

- Internal 32 MHz Clock Generator (IHRC)

- 4 KB non-volatileflash memory (IROM) with in-system program support

- 256 bytes internal RAM (IRAM)

- 13 interrupt sources with priority levels control and unique interrupt vectors

- 12 internal interrupts

- 1external interrupts: INTO

- 1 set of DPTR

- 2 set 8/16-bit timers with 4 operation modes

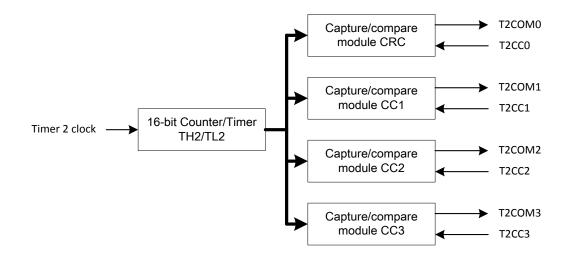

- 1set16-bit timers with 4 comparison output (PWM) and capture channels

#### **1.2 Applications**

- Brushless DC motor

- Home automation

#### **1.3 Features Selection Table**

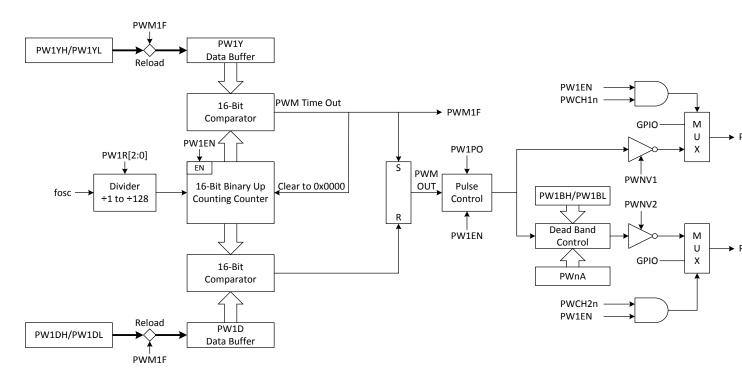

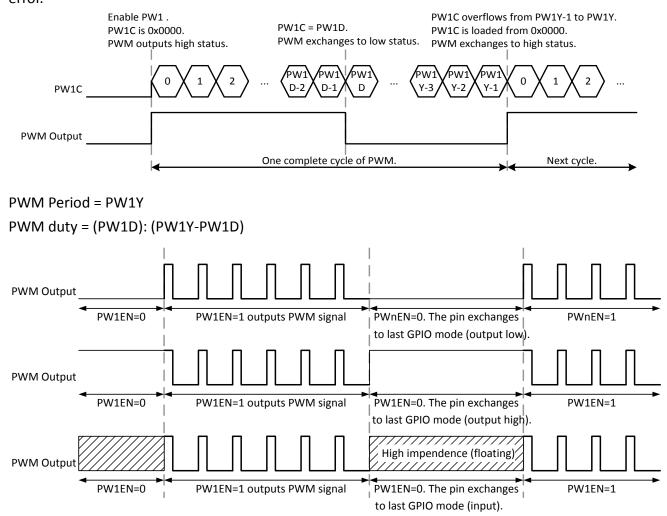

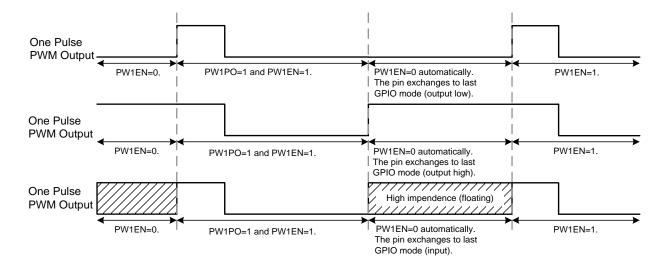

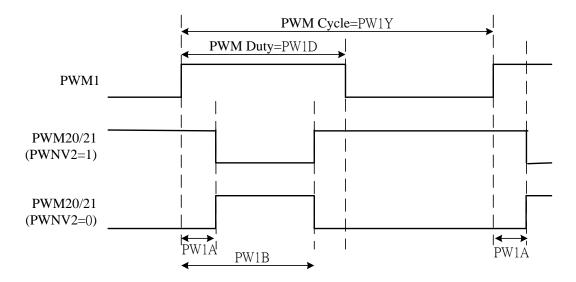

- 1set16-bit PWM generators:

- each PWM generator has 4output channels with inverters and dead-band control

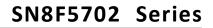

- **12-bit SAR ADC** with 10 external and2internal channels, and 4 internal reference voltages

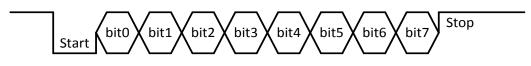

- SPI, UART, I2C interface with SMBus Support

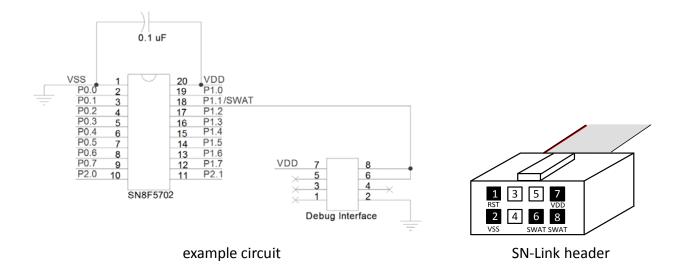

- On-Chip Debug Support:

Single-wire debug interface

2hardware breakpoints

Unlimited software breakpoints

ROM data security/protection

- Watchdog and programmable external reset

- 1.8V low voltage detectors

- Wide supply voltage (1.8 V 5.5 V) and temperature (-40 °C to 85 °C) range

- Household

- Other

|            | 0/1 | PWM<br>Channels | 12C | SPI | UART                      | ADC ext.<br>Channels | OPA | CMP | Ext. INT | Package<br>Types              |

|------------|-----|-----------------|-----|-----|---------------------------|----------------------|-----|-----|----------|-------------------------------|

| SN8F5702   | 18  | 8               | V   | V   | V                         | 10                   | -   | -   | 1        | DIP20,SOP20<br>TSSOP20, QFN20 |

| SN8F570212 | 14  | 6               | V   | V   | TX <sup>*(1)</sup>        | 8                    | -   | -   | 1        | SOP16,TSSOP16,<br>QFN16       |

| SN8F570210 | 12  | 5               | -   | -   | V                         | 6                    | _   | -   | 1        | SOP14                         |

| SN8F570211 | 12  | 5               | V   | -   | TX <sup>*(1)</sup>        | 6                    | -   | -   | 1        | SOP14                         |

| SN8F570213 | 12  | 5               | -   | -   | V                         | 6                    | -   | -   | 1        | SOP14                         |

| SN8F570200 | 8   | 3               | -   | -   | <b>TX</b> <sup>*(1)</sup> | 5                    | -   | -   | 1        | MSOP10                        |

| SN8F570202 | 6   | 3               | -   | -   | TX <sup>*(1)</sup>        | 4                    | -   | _   | 1        | SOP8                          |

\*(1)Only support UART TX mode.

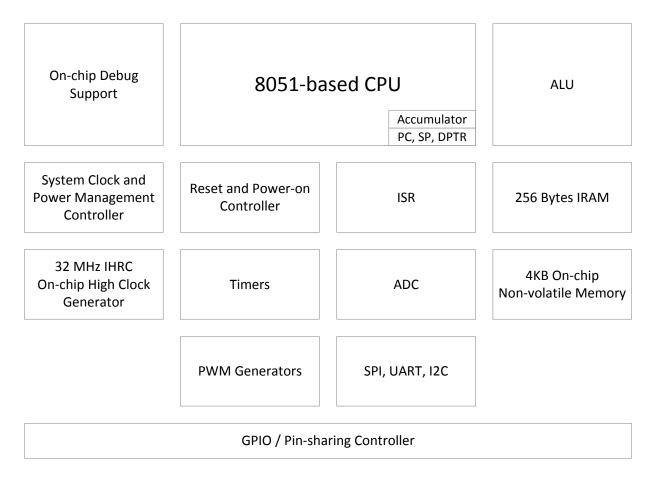

# 1.4 Block Diagram

# 2 Table of Contents

| 1  | Device Overview                   | 2    |

|----|-----------------------------------|------|

| 2  | Table of Contents                 | 4    |

| 3  | Revision History                  | 5    |

| 4  | Pin Assignments                   | 7    |

| 5  | CPU                               | . 15 |

| 6  | Special Function Registers        | . 21 |

| 7  | Reset and Power-on Controller     | . 29 |

| 8  | System Clock and Power Management | . 35 |

| 9  | System Operating Mode             | . 43 |

| 10 | Interrupt                         | . 48 |

| 11 | GPIO                              | . 59 |

| 12 | External Interrupt                | . 63 |

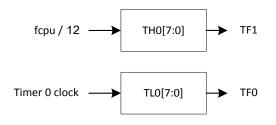

| 13 | Timer 0 and Timer 1               | . 65 |

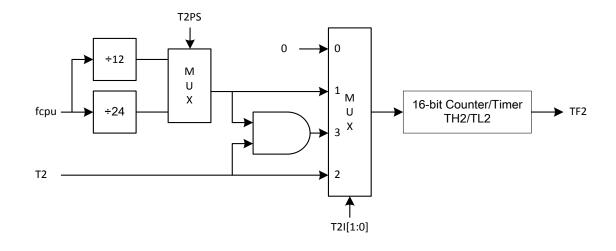

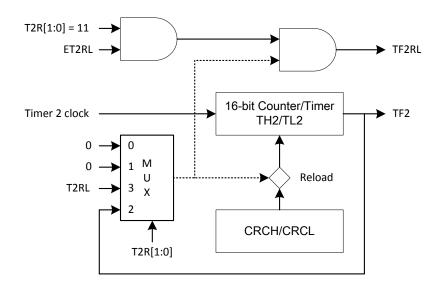

| 14 | Timer 2                           | . 72 |

| 15 | PWM                               | . 82 |

| 16 | ADC                               | . 90 |

| 17 | UART                              | 101  |

| 18 | SPI                               | 110  |

| 19 | I2C                               | 116  |

| 20 | In-System Program                 | 130  |

| 21 | Electrical Characteristics        | 134  |

| 22 | Instruction Set                   | 137  |

| 23 | Development Environment           | 142  |

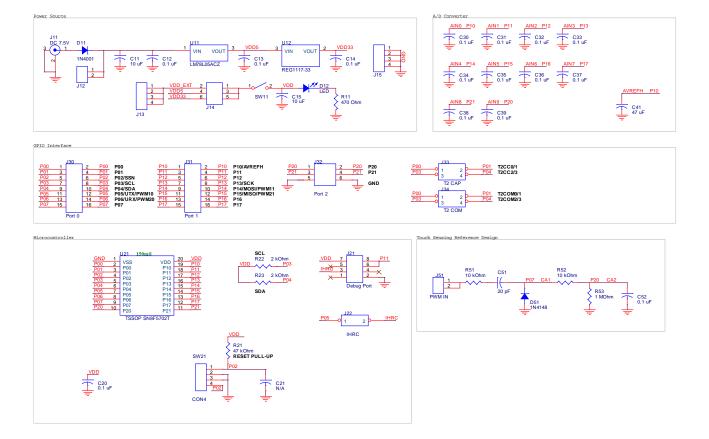

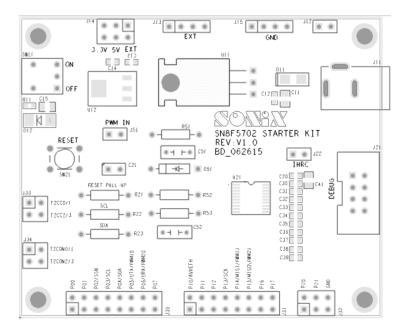

| 24 | SN8F5702 Starter-Kit              | 144  |

| 25 | ROM Programming Pin               | 147  |

| 26 | Ordering Information              | 152  |

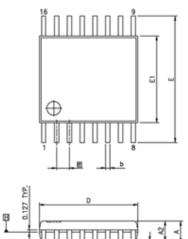

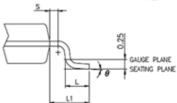

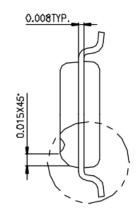

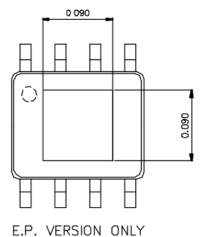

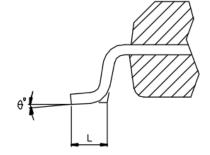

| 27 | Package Information               | 154  |

| 28 | Appendix: Reference Document      | 164  |

# 3 Revision History

| Revision | Date      | Description                                                       |

|----------|-----------|-------------------------------------------------------------------|

| 1.0      | Sep.2015  | First issue                                                       |

| 1.1      | Oct. 2015 | 1. Modify timer section and electrical characteristic section.    |

|          |           | 2. Modify SN8F57023/SN8F57024 pin assignment.                     |

|          |           | 3. Add program memory security section, special function register |

|          |           | section and noise filter section.                                 |

|          |           | 4. Modify minimum requirement in debug interface section.         |

|          |           | 5. Update electrical characteristics                              |

| 1.2      | Nov. 2015 | 1. Update package type                                            |

| 1.3      | Nov. 2015 | 1. SN8F57021 was renamed SN8F570210.                              |

|          |           | 2. SN8F57022 was renamed SN8F570200.                              |

|          |           | 3. SN8F57023 was renamed SN8F570211.                              |

|          |           | 4. SN8F57024 was renamed SN8F570212.                              |

| 1.4      | Nov. 2015 | 1. Modify SN8F570200 pin assignment                               |

| 1.5      | Dec. 2015 | 1. Modify electrical characteristic in IHRC section.              |

|          |           | 2. Add power saving description in UART/SPI/I2C section.          |

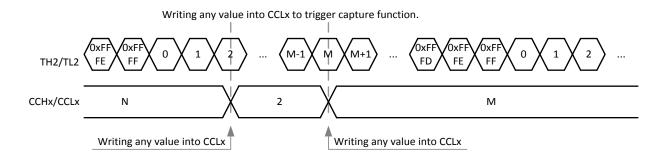

| 1.6      | Apr. 2016 | 1. Add Timer 2 capture function waveform to illustrate operation. |

|          |           | 2. Special Function Registers adds Register Declaration section.  |

|          |           | 3. Add Appendix: Reference Document chapter.                      |

|          |           | 4. Add ROM Programming Pin chapter.                               |

|          |           | 5. Add QFN20 and SOP14 package type.                              |

| 1.7      | Aug. 2016 | 1. I2C example modify.                                            |

|          |           | 2. Modify Power Management section and In-System Program          |

|          |           | section.                                                          |

|          |           | 3. Modify PW1M & PW1YH/L registersdescription.                    |

|          |           | 4. Add SOP8 package type.                                         |

|          |           | 5. Add ADC internal reference range.                              |

| 1.8      | Nov. 2016 | 1. Modify feature table and I2C status code.                      |

|          |           | 2. Add UART Baud Rate Table, WDT description in watchdog reset    |

|          |           | section and QFN16 package type.                                   |

| 1.9      | Dec. 2016 | 1. Modify electrical characteristic section.                      |

| 2.0      | Sep. 2017 | 1. Add pincircuitdiagrams section.                                |

|          |           | 2. Add package information.                                       |

| 2.1      | Nov. 2017 | 1. Modify LVD related content.                                    |

| 2.2      | Dec. 2017 | 1. Add design note description.                                   |

| 2.3      | Jul.2018  | 1. Modify QFN16 3x3 dimension.                                    |

| 2.  | Modify POOC register in UART section.                          |

|-----|----------------------------------------------------------------|

| 3.  | Repair an error, omission, etc.                                |

| 4.  | Add Pin Characteristic section.                                |

| 5.  | Modify Internal & External RAM section description.            |

| 6.  | Modify Program Memory section description.                     |

| 7.  | Modify Configuration of Reset and Power-on Controller section  |

|     | description.                                                   |

| 8.  | Modify System clock section description.                       |

| 9.  | Add High Speed Clock and Real time clocksection.               |

| 10. | Add System clock timing section.                               |

| 11. | Add System Operating Mode chapter.                             |

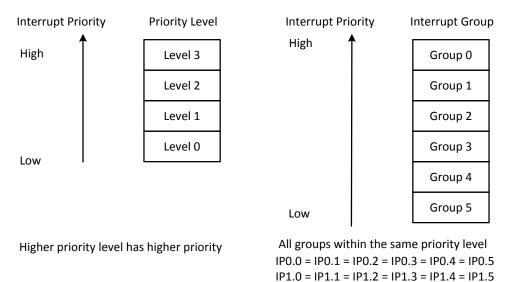

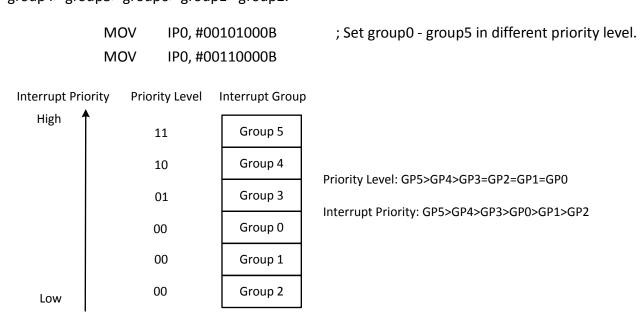

| 12. | Modify Interrupt Priority section description.                 |

| 13. | Interrupt chapter adds example section.                        |

| 14. | Modify UART chapter description and baud rate table.           |

| 15. | I2C chapter adds protocol description diagram and modifies the |

|     | clock rate table.                                              |

| 16. | Debug Interface chapter was renamed Development                |

|     | Environment chapter. Modify Development Environment            |

|     | chapter description. Add Development Tool section.             |

| 17. | Add SN5702 Starter-kit chapter.                                |

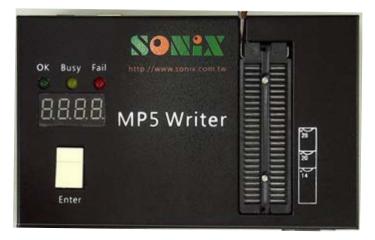

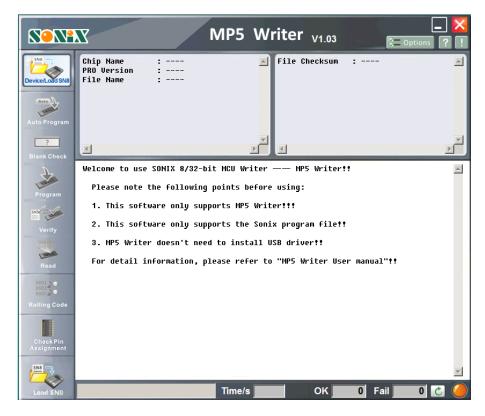

| 18. | Modify ROM Programming Pin chapter description. Add MP5        |

|     | Hardware Connecting, SN-Link ISP Programming and SN-Link ISP   |

|     | Programming Pin Mapping sections.                              |

| 19. | Update Device Nomenclature section.                            |

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of the part.

#### 4 Pin Assignments

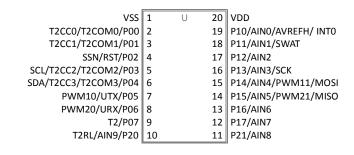

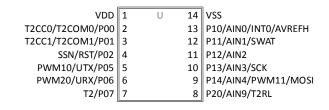

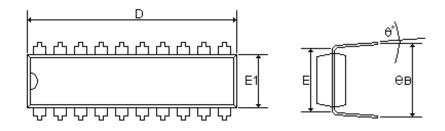

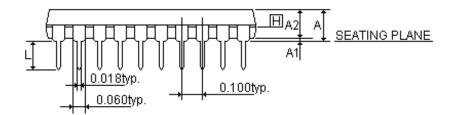

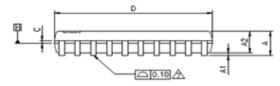

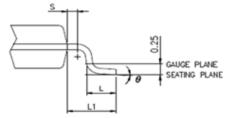

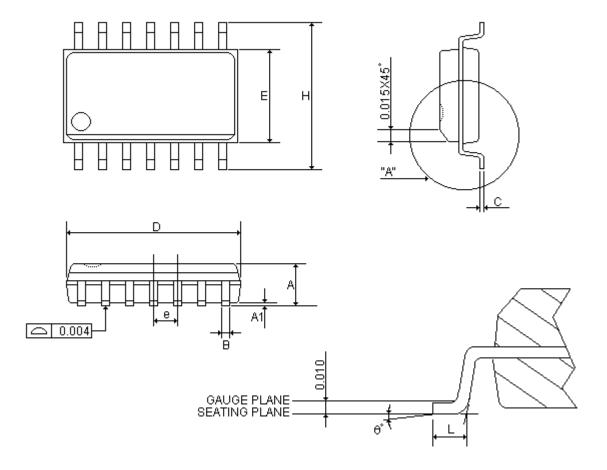

# 4.1 SN8F5702P/S/T (DIP20/SOP20/TSSOP20)

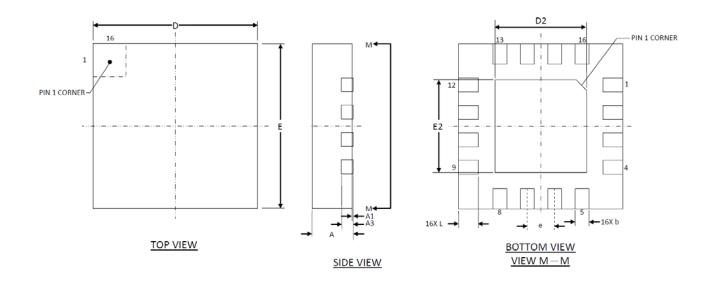

## 4.2 SN8F5702J (QFN20)

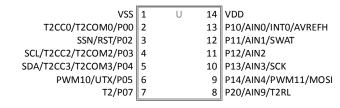

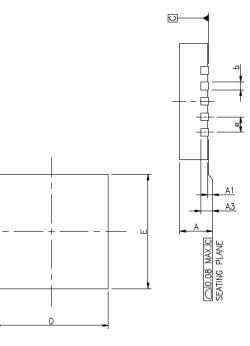

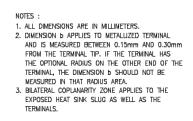

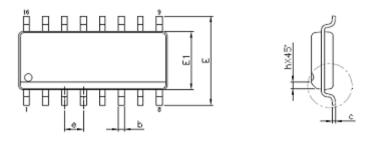

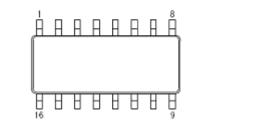

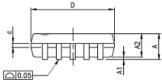

#### 4.3 SN8F570210S (SOP14)

## 4.4 SN8F570211S (SOP14)

#### 4.5 SN8F570213S (SOP14)

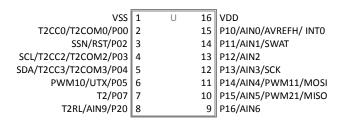

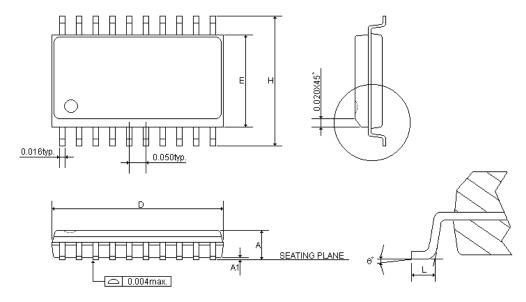

## 4.6 SN8F570212S/T (SOP16/TSSOP16)

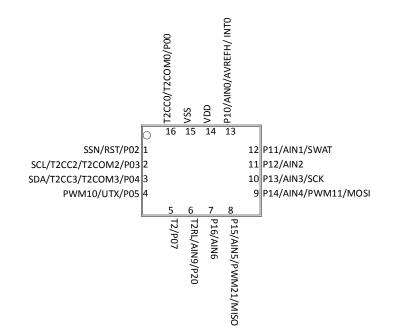

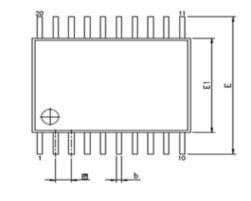

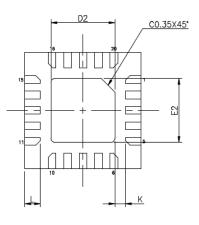

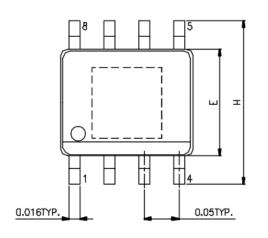

#### 4.7 SN8F570212J (QFN16)

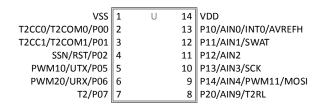

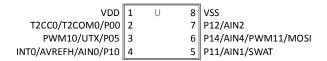

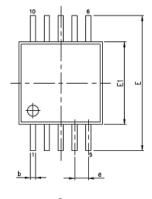

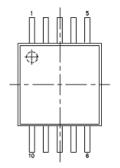

# 4.8 SN8F570200A (MSOP10)

| VDD              | 1 | U | 10 | P10/AIN0/AVREFH/ INT0 |

|------------------|---|---|----|-----------------------|

| VSS              |   |   | 9  | P11/AIN1/SWAT         |

| T2CC0/T2COM0/P00 | 3 |   | 8  | P12/AIN2              |

| SSN/RST/P02      | 4 |   | 7  | P13/AIN3/SCK          |

| PWM10/UTX/P05    | 5 |   | 6  | P14/AIN4/PWM11/MOSI   |

# 4.9 SN8F570202S (SOP8)

# 4.10 Pin Descriptions

#### **Power Pins**

| Pin Name | Туре  | Description  |  |  |  |  |

|----------|-------|--------------|--|--|--|--|

| VDD      | Power | Power supply |  |  |  |  |

| VSS      | Power | Ground (0 V) |  |  |  |  |

#### Port 0

| Pin Name | Туре           | Description                                    |

|----------|----------------|------------------------------------------------|

| P0.0     | Digital I/O    | GPIO                                           |

| T2COM0   | Digital Output | Timer 2: compare 0 output                      |

| T2CC0    | Digital Input  | Timer 2:capture0 input                         |

| P0.1     | Digital I/O    | GPIO                                           |

| T2COM1   | Digital Output | Timer 2: compare 1 output                      |

| T2CC1    | Digital Input  | Timer 2:capture 1 input                        |

| P0.2     | Digital I/O    | GPIO                                           |

| Reset    | Digital Input  | System reset (active low)                      |

| SSN      | Digital Input  | SPI: salve selection pin (slave mode)          |

| P0.3     | Digital I/O    | GPIO                                           |

| T2COM2   | Digital Output | Timer 2: compare 2 output                      |

| T2CC2    | Digital Input  | Timer 2:capture 2 input                        |

| SCL      | Digital I/O    | I2C: clock output (master) clock input (slave) |

| P0.4     | Digital I/O    | GPIO                                           |

| T2COM3   | Digital Output | Timer 2: compare 3 output                      |

| T2CC3    | Digital Input  | Timer 2:capture 3 input                        |

| SDA      | Digital I/O    | I2C: data pin                                  |

| P0.5     | Digital I/O    | GPIO                                           |

| UTX      | Digital Output | UART: transmission pin                         |

| PWM10    | Digital Output | PWM: programmable PWM output                   |

| P0.6     | Digital I/O    | GPIO                                           |

| URX      | Digital Input  | UART: reception pin                            |

| PWM20    | Digital Output | PWM: programmable PWM output                   |

| P0.7     | Digital I/O    | GPIO                                           |

| T2       | Digital Input  | Timer 2: event counter input                   |

# SN8F5702 Series

| Port 1   |                |                                                      |

|----------|----------------|------------------------------------------------------|

| Pin Name | Туре           | Description                                          |

| P1.0     | Digital I/O    | GPIO                                                 |

| AINO     | Analog Input   | ADC: input channel 0                                 |

| INTO     | Digital Input  | INTO: external interrupt 0                           |

| AVREFH   | Analog Input   | ADC: external reference voltage                      |

| P1.1     | Digital I/O    | GPIO                                                 |

| AIN1     | Analog Input   | ADC: input channel 1                                 |

| SWAT     | Digital I/O    | Debug interface                                      |

| P1.2     | Digital I/O    | GPIO                                                 |

| AIN2     | Analog Input   | ADC: input channel 2                                 |

| P1.3     | Digital I/O    | GPIO                                                 |

| AIN3     | Analog Input   | ADC: input channel 3                                 |

| SCK      | Digital I/O    | SPI: clock output (master) clock input (slave)       |

| P1.4     | Digital I/O    | GPIO                                                 |

| AIN4     | Analog Input   | ADC: input channel 4                                 |

| MOSI     | Digital I/O    | SPI: transmission pin (master) reception pin (slave) |

| PWM11    | Digital Output | PWM: programmable PWM output                         |

| P1.5     | Digital I/O    | GPIO                                                 |

| AIN5     | Analog Input   | ADC: input channel 5                                 |

| MISO     | Digital I/O    | SPI: reception pin (master) transmission pin (slave) |

| PWM21    | Digital Output | PWM: programmable PWM output                         |

| P1.6     | Digital I/O    | GPIO                                                 |

| AIN6     | Analog Input   | ADC: input channel 6                                 |

| P1.7     | Digital I/O    | GPIO                                                 |

| AIN7     | Analog Input   | ADC: input channel 7                                 |

#### Port 2

| Pin Name | Туре          | Description                   |

|----------|---------------|-------------------------------|

| P2.0     | Digital I/O   | GPIO                          |

| AIN9     | Analog Input  | ADC: input channel 9          |

| T2RL     | Digital Input | Timer 2: reload trigger input |

| P2.1     | Digital I/O   | GPIO                          |

| AIN8     | Analog Input  | ADC: input channel 8          |

# 4.11 Pin Characteristic

| Port | Open-<br>Drain | Sink<br>Current<br>100mA<br>VSS+1.5V | Sink<br>Current<br>20mA<br>VSS+0.5V | External<br>Interrupt | Wakeup<br>(Level<br>change) | Shared Pin       |

|------|----------------|--------------------------------------|-------------------------------------|-----------------------|-----------------------------|------------------|

| P0.0 |                | V                                    | -                                   | -                     | V                           | T2CC0/T2COM0     |

| P0.1 |                | V                                    | -                                   | -                     | V                           | T2CC1/T2COM1     |

| P0.2 | -              | V                                    | -                                   | -                     | V                           | SSN/RST          |

| P0.3 | -              | V                                    | -                                   | -                     | V                           | SCL/T2CC2/T2COM2 |

| P0.4 | -              | V                                    | -                                   | -                     | V                           | SDA/T2CC3/T2COM3 |

| P0.5 | V              | V                                    | -                                   | -                     | V                           | PWM10/UTX        |

| P0.6 | V              | V                                    | -                                   | -                     | V                           | PWM20/URX        |

| P0.7 | -              | -                                    | V                                   | -                     | V                           | T2               |

| P1.0 | -              | -                                    | V                                   | V                     | V                           | AIN0/AVREFH/INT0 |

| P1.1 | -              | -                                    | V                                   | -                     | V                           | AIN1/SWAT        |

| P1.2 | -              | -                                    | V                                   | -                     | V                           | AIN2             |

| P1.3 | V              | -                                    | V                                   | -                     | V                           | AIN3/SCK         |

| P1.4 | V              | -                                    | V                                   | -                     | V                           | AIN4/PWM11/MOSI  |

| P1.5 | V              | -                                    | V                                   | -                     | V                           | AIN5/PWM21/MISO  |

| P1.6 | -              | -                                    | V                                   | -                     | V                           | AIN6             |

| P1.7 | -              | -                                    | V                                   | -                     | V                           | AIN7             |

| P2.0 | -              | -                                    | V                                   | -                     | -                           | T2RL/AIN9        |

| P2.1 | -              | -                                    | V                                   | -                     | -                           | AIN8             |

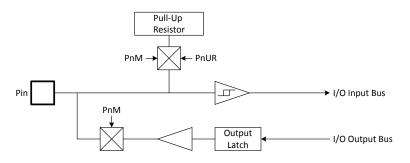

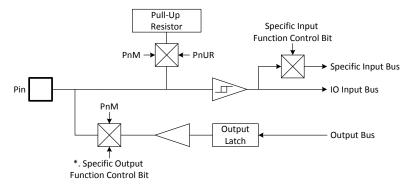

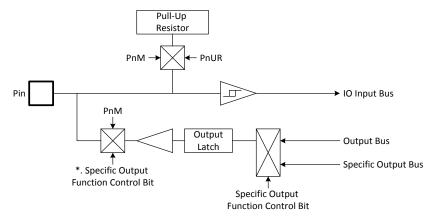

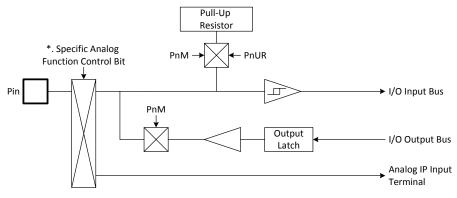

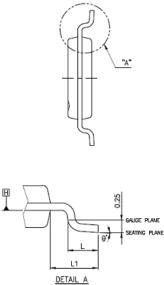

# 4.12 Pin Circuit Diagrams

Normal Bi-direction I/O Pin.

Bi-direction I/O Pin Shared with Specific Digital Input Function, e.g. INTO, Event counter, SIO, UART.

$^{*}.$  Some specific functions switch I/O direction directly, not through PnM register.

Bi-direction I/O Pin Shared with Specific Digital Output Function, e.g. PWM, SIO, UART.

\*. Some specific functions switch I/O direction directly, not through PnM register.

Bi-direction I/O Pin Shared with Specific Analog Input Function, e.g. ADC.

\*. Some specific functions switch I/O direction directly, not through PnM register.

# 5 CPU

SN8F5000 family is an enhanced 8051 microcontroller (MCU). It is fully compatible with MCS-51 instructions, hence the ability to cooperate with modern development environment (e.g. Keil C51).Generally speaking, SN8F5000 CPU has 9.4 to 12.1 times faster than the original 8051 at the same frequency.

# 5.1 Memory Organization

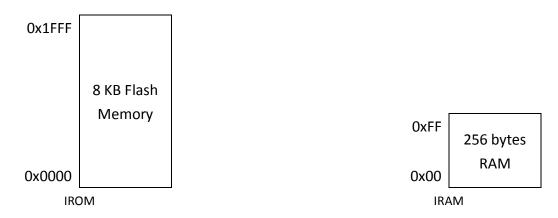

SN8F5702 builds in two on-chip memories: internal RAM (IRAM) and program memory (IROM). The internal RAM is a 256-byte RAM which has higher access performance (direct and indirect addressing). By contrast, the external RAM has 256-byte of size, but it requires a longer access period. The program memory is a 8 KB non-volatile memory and has a maximum 8 MHz speed limitation.

# 5.2 Internal RAM (IRAM)

256 X 8-bit RAM (Internal Data Memory)

| Address      | RAM Location         |                           |                                                  |

|--------------|----------------------|---------------------------|--------------------------------------------------|

| 000h<br>01Fh | Work Register Area   |                           | 00h-7Fh of RAM is direct and indirect access RAM |

| 020h<br>02Fh | Bit Addressable Area |                           |                                                  |

| 030h         |                      |                           |                                                  |

|              | General Purpose Area |                           |                                                  |

| <br>07Fh     |                      |                           | _                                                |

| 080h         |                      |                           | 080h-0FFh store special                          |

|              | General Purpose Area | Special Function Register | function registers.                              |

|              | (Indirect Access)    | (Direct Access)           |                                                  |

| 0FFh         |                      |                           | End of Bank 0                                    |

The 256-byte data RAM in internal data memory is a standard 8051 RAM access configuration. The upper 128-byte RAM is general purpose RAM and can configure by direct addressing access and indirect addressing access. The lower 128-byte can be indirect access RAM in general purpose or direct access RAM in special function register (SFR).

- 0x0000-0x007F: General purpose RAM contains work register area and bit addressable area.

In this area, direct or indirect addressing can be used.

- 0x0000-0x001F: Work register area includes 4-bank. Each bank has 8 work registers (R0 R7) which is selected by RS0/RS1 in PSW register.

- 0x0020-0x002F: Bit addressable area.

In the bit addressable area, user can read or write any single bit in this range by using the unique address for that bit. Supports 16bytes bit addressable RAM area giving 128 addressable bits. Each bit has individual address in the range from 00H to 7FH. Thus, the bit can be addressed directly. Bit0 of the byte 20H has bit address 00H and Bit 7 of the byte 20H has bit address 07H. Bit0 of the byte 2FH has bit address 78H and Bit 7 of the byte 2FH has bit address 7FH. When set "SETB 42H", it means the bit2 of the byte 28H is set.

|                      | Byte Address | Bite 0 | Bite 1 | Bite 2 | Bite 3 | Bite 4 | Bite 5 | Bite 6 | Bite 7 |

|----------------------|--------------|--------|--------|--------|--------|--------|--------|--------|--------|

|                      | 0x20         | 0x00   | 0x01   | 0x02   | 0x03   | 0x04   | 0x05   | 0x06   | 0x07   |

|                      | 0x21         | 0x08   | 0x09   | 0x0A   | 0x0B   | 0x0C   | 0x0D   | 0x0E   | 0x0F   |

|                      | 0x22         | 0x10   | 0x11   | 0x12   | 0x13   | 0x14   | 0x15   | 0x16   | 0x17   |

|                      | 0x23         | 0x18   | 0x19   | 0x1A   | 0x1B   | 0x1C   | 0x1D   | 0x1E   | 0x1F   |

| IJ                   | 0x24         | 0x20   | 0x21   | 0x22   | 0x23   | 0x24   | 0x25   | 0x26   | 0x27   |

| Bit Addressable Area | 0x25         | 0x28   | 0x29   | 0x2A   | 0x2B   | 0x2C   | 0x2D   | 0x2E   | 0x2F   |

| ble                  | 0x26         | 0x30   | 0x31   | 0x32   | 0x33   | 0x34   | 0x35   | 0x36   | 0x37   |

| essa                 | 0x27         | 0x38   | 0x39   | 0x3A   | 0x3B   | 0x3C   | 0x3D   | 0x3E   | 0x3F   |

| ddre                 | 0x28         | 0x40   | 0x41   | 0x42   | 0x43   | 0x44   | 0x45   | 0x46   | 0x47   |

| lit A                | 0x29         | 0x48   | 0x49   | 0x4A   | 0x4B   | 0x4C   | 0x4D   | 0x4E   | 0x4F   |

| •                    | 0x2A         | 0x50   | 0x51   | 0x52   | 0x53   | 0x54   | 0x55   | 0x56   | 0x57   |

|                      | 0x2B         | 0x58   | 0x59   | 0x5A   | 0x5B   | 0x5C   | 0x5D   | 0x5E   | 0x5F   |

|                      | 0x2C         | 0x60   | 0x61   | 0x62   | 0x63   | 0x64   | 0x65   | 0x66   | 0x67   |

|                      | 0x2D         | 0x68   | 0x69   | 0x6A   | 0x6B   | 0x6C   | 0x6D   | 0x6E   | 0x6F   |

|                      | 0x2E         | 0x70   | 0x71   | 0x72   | 0x73   | 0x74   | 0x75   | 0x76   | 0x77   |

|                      | 0x2F         | 0x78   | 0x79   | 0x7A   | 0x7B   | 0x7C   | 0x7D   | 0x7E   | 0x7F   |

0x0080~0x00FF: General purpose area in indirect addressing access or special function register in direct addressing access.

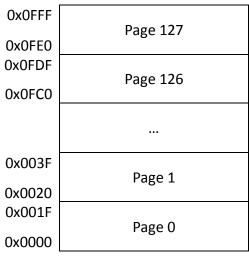

# 5.3 Program Memory (IROM)

The program memory is a non-volatile storage area where stores code, look-up ROM table, and other data with occasional modification. It can be updated by debug tools like SN-Link3, and a program can also self-update via in-system program process (refer to In-system Program).

| Address | ROM                     | Comment             |

|---------|-------------------------|---------------------|

| 0000H   | Reset vector            | Reset vector        |

| 0001H   |                         | User program        |

| 0002H   | General purpose area    |                     |

| 0003H   | INT0 Interrupt vector   | Interrupt vector    |

| 000BH   | TIMER0 Interrupt vector |                     |

| 001BH   | TIMER1 Interrupt vector | _                   |

| 0023H   | UART Interrupt vector   |                     |

| 002BH   | TIMER2Interrupt vector  | _                   |

| 0043H   | I2C Interrupt vector    | _                   |

| 004BH   | SPI Interrupt vector    |                     |

| 0053H   | T2COM0 Interrupt vector |                     |

| 005BH   | T2COM1 Interrupt vector |                     |

| 0063H   | T2COM2 Interrupt vector |                     |

| 006BH   | T2COM3Interrupt vector  |                     |

| 0083H   | PWM1 Interrupt vector   |                     |

| 008BH   | ADC Interrupt vector    |                     |

| 008CH   |                         | User program        |

|         |                         |                     |

|         | General purpose area    |                     |

|         |                         |                     |

|         |                         | End of user program |

| 0FF6H   |                         |                     |

| 0FF7H   |                         |                     |

|         | Reserved                |                     |

| OFFEH   |                         |                     |

| OFFFH   |                         |                     |

The ROM includes reset vector, Interrupt vector, general purpose area and reserved area. The reset vector is program beginning address. The interrupt vector is the head of interrupt service routine when any interrupt occurring. The general purpose area is main program area including main loop, sub-routines and data table.

- 0x0000 Reset vector: Program counter points to 0x0000 after any reset events (power on reset, reset pin reset, watchdog reset, LVD reset...).

- 0x0001~0x0002: General purpose area to process system reset operation.

- 0x0003~0x008B: Multi interrupt vector area. Each of interrupt events has a unique interrupt vector.

- 0x008C~0x0FBF: General purpose area for user program and ISP (EEPROM function).

- 0x0FC0~0x0FF5: General purpose area for user program. Do not execute ISP.

- 0x0FF6~0x0FFF: Reserved area. Do not execute ISP.

ROM security rule is all address ROM data protected and outputs 0x0000.

# 5.4 Program Memory Security

The SN8F5702 provides security options at the disposal of the designer to prevent unauthorized access to information stored in FLASH memory. When enable security option, the ROM code is secured and not dumped complete ROM contents. ROM security rule is all address ROM data protected and outputs 0x00.

# 5.5 Data Pointer

A data pointer helps to specify the IROM address while performing MOVC instructions. The microcontroller has one set of data pointer (DPH/DPL).

# 5.6 Stack

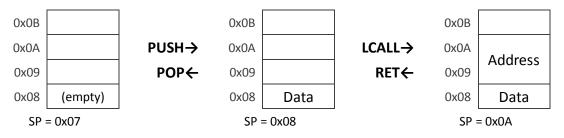

Stack can be assigned to any area of internal RAM (IRAM). However, it requires manual assignment to ensure its area does not overlap other RAM's variables. An overflow and underflow stack could also mistakenly overwrite other RAM's variables; thus, these factors should be considered while arrange the size of stack.

By default, stack pointer (SP register) points to 0x07 which means the stack area begin at IRAM address 0x08. In other word, if a planned stack area is assigned from IRAM address 0xC0, the appropriate SP register is anticipated to set at 0xBF after system reset.

An assembly PUSH instruction costs one byte of stack. LCALL, ACALL instructions and interrupt respectively costs two bytes stack. POP-instruction decreases one count, and a RET/RETI subtract two counts of stack pointer.

\* Note: Stack and IRAM share the same area, Keil C51 compiler will not display "error" or "warning" when overlap condition is occurred so user must pay attention.

# 5.7 Stack and Data Pointer Register

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit O |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| SP       | SP7   | SP6   | SP5   | SP4   | SP3   | SP2   | SP1   | SP0   |

| DPL      | DPL7  | DPL6  | DPL5  | DPL4  | DPL3  | DPL2  | DPL1  | DPL0  |

| DPH      | DPH7  | DPH6  | DPH5  | DPH4  | DPH3  | DPH2  | DPH1  | DPH0  |

# SP Register (0x81)

| Bit | Field | Туре | Initial | Description   |

|-----|-------|------|---------|---------------|

| 70  | SP    | R/W  | 0x07    | Stack pointer |

#### DPL Register (0x82)

| Bit | Field    | Туре | Initial | Description       |

|-----|----------|------|---------|-------------------|

| 70  | DPL[7:0] | R/W  | 0x00    | Low byte of DPTR0 |

#### DPH Register (0x83)

| Bit | Field    | Туре | Initial | Description        |

|-----|----------|------|---------|--------------------|

| 70  | DPH[7:0] | R/W  | 0x00    | High byte of DPTR0 |

# 6 Special Function Registers

# 6.1 Special Function Register Memory Map

| BIN<br>HEX | 000    | 001   | 010    | 011    | 100    | 101    | 110    | 111    |

|------------|--------|-------|--------|--------|--------|--------|--------|--------|

| F8         | -      | POM   | P1M    | P2M    | -      | -      | -      | PFLAG  |

| FO         | В      | POUR  | P1UR   | P2UR   | -      | -      | -      | SRST   |

| E8         | -      | -     | -      | -      | -      | -      | -      | -      |

| EO         | ACC    | SPSTA | SPCON  | SPDAT  | POOC   | CLKSEL | CLKCMD | TCON0  |

| D8         | SOCON2 | -     | I2CDAT | I2CADR | I2CCON | I2CSTA | SMBSEL | SMBDST |

| D0         | PSW    | IEN4  | ADM    | ADB    | ADR    | VREFH  | P1CON  | -      |

| C8         | T2CON  | -     | CRCL   | CRCH   | TL2    | TH2    | -      | -      |

| CO         | IRCON  | CCEN  | CCL1   | CCH1   | CCL2   | CCH2   | CCL3   | ССН3   |

| B8         | IEN1   | IP1   | SORELH | PW1DH  | PW1DL  | PW1A   | PW1CH  | IRCON2 |

| BO         | -      | -     | -      | -      | -      | -      | -      | -      |

| A8         | IENO   | IP0   | SORELL | PW1M   | PW1YL  | PW1YH  | PW1BL  | PW1BH  |

| AO         | P2     | -     | -      | -      | -      | -      | -      | -      |

| 98         | SOCON  | SOBUF | IEN2   | -      | -      | POCON  | P2CON  | -      |

| 90         | P1     | P1W   | -      | -      | PECMD  | PEROML | PEROMH | PERAM  |

| 88         | TCON   | TMOD  | TLO    | TL1    | TH0    | TH1    | CKCON  | PEDGE  |

| 80         | PO     | SP    | DPL    | DPH    | -      | -      | WDTR   | PCON   |

Note: All SFRs in the left-most column are bit-addressable. (Every 0x0/0x8-ending SFR addresses are bit-addressable).

# 6.2 Special Function register Description

## 0x80 - 0x9F Registers Description

| Pogistor | Address | Description                                |

|----------|---------|--------------------------------------------|

| Register |         | Description                                |

| PO       | 0x80    | Port 0 data buffer.                        |

| SP       | 0x81    | Stack pointer register.                    |

| DPL      | 0x82    | Data pointer 0 low byte register.          |

| DPH      | 0x83    | Data pointer 0 high byte register.         |

| -        | 0x84    |                                            |

| -        | 0x85    |                                            |

| WDTR     | 0x86    | Watchdog timer clear register.             |

| PCON     | 0x87    | System mode register.                      |

| TCON     | 0x88    | Timer 0 / 1 controls register.             |

| TMOD     | 0x89    | Timer 0 / 1 mode register.                 |

| TL0      | 0x8A    | Timer 0 counting low byte register.        |

| TL1      | 0x8B    | Timer 1 counting low byte register.        |

| TH0      | 0x8C    | Timer 0 counting high byte register.       |

| TH1      | 0x8D    | Timer 1 counting high byte register.       |

| CKCON    | 0x8E    | Extended cycle controls register.          |

| PEDGE    | 0x8F    | External interrupt edge controls register. |

| P1       | 0x90    | Port 1 data buffer.                        |

| P1W      | 0x91    | Port 1 wake-up controls register.          |

| -        | 0x92    |                                            |

| -        | 0x93    |                                            |

| PECMD    | 0x94    | In-System Programcommand register.         |

| PEROML   | 0x95    | In-System Program ROM address low byte     |

| PEROMH   | 0x96    | In-System Program ROM address high byte    |

| PERAM    | 0x97    | In-System Program RAM mapping address      |

| SOCON    | 0x98    | UART control register.                     |

| SOBUF    | 0x99    | UART data buffer.                          |

| IEN2     | 0x9A    | Interrupts enable register                 |

| -        | 0x9B    | -                                          |

| -        | 0x9C    | -                                          |

| POCON    | 0x9D    | Port Oconfiguration controls register.     |

| P2CON    | 0x9E    | Port 2configuration controls register.     |

| -        | 0x9F    | _                                          |

|          |         |                                            |

#### **0xA0 - 0xBF Registers Description**

| Register | Address | Description                                      |

|----------|---------|--------------------------------------------------|

| P2       | 0xA0    | Port 2 data buffer                               |

| -        | 0xA1    | -                                                |

| -        | 0xA2    | _                                                |

| -        | 0xA3    | _                                                |

| -        | 0xA4    | _                                                |

| -        | 0xA5    | _                                                |

| -        | 0xA6    | _                                                |

| -        | 0xA7    | -                                                |

| IEN0     | 0xA8    | Interrupts enable register                       |

| IP0      | 0xA9    | Interrupts priority register.                    |

| SORELL   | 0xAA    | UART reload low byte register.                   |

| PW1M     | 0xAB    | PW1 controls register.                           |

| PW1YL    | 0xAC    | PW1 cycle controls buffer low byte.              |

| PW1YH    | 0xAD    | PW1 cycle controls buffer high byte.             |

| PW1BL    | 0xAE    | PW1 B point dead band controls buffer low byte.  |

| PW1BH    | 0xAF    | PW1 B point dead band controls buffer high byte. |

| -        | 0xB0    | -                                                |

| -        | 0xB1    | -                                                |

| -        | 0xB2    | -                                                |

| -        | 0xB3    | -                                                |

| -        | 0xB4    | -                                                |

| -        | 0xB5    | -                                                |

| -        | 0xB6    | -                                                |

| -        | 0xB7    | -                                                |

| IEN1     | 0xB8    | Interrupts enable register                       |

| IP1      | 0xB9    | Interrupts priority register.                    |

| SORELH   | 0xBA    | UART reload high byte register.                  |

| PW1DL    | OxBB    | PW1 duty controls buffer low byte.               |

| PW1DH    | 0xBC    | PW1 duty controls buffer high byte.              |

| PW1A     | 0xBD    | PW1 A point dead band controls buffer.           |

| PW1CH    | OxBE    | PW1 channel control buffer.                      |

| IRCON2   | 0xBF    | Interrupts request register.                     |

|          |         |                                                  |

#### **0xC0 - 0xDF Registers Description**

| Register | Address | Description                                                            |

|----------|---------|------------------------------------------------------------------------|

| IRCON    | 0xC0    | Interrupts request register.                                           |

| CCEN     | 0xC1    | Timer 2 Compare /capture enable register.                              |

| CCL1     | 0xC2    | Timer 2 Compare /capture module 1 low byte register.                   |

| CCH1     | 0xC3    | Timer 2 Compare /capture module 1 high byte register.                  |

| CCL2     | 0xC4    | Timer 2 Compare /capture module 2 low byte register.                   |

| CCH2     | 0xC5    | Timer 2 Compare /capture module 2 high byte register.                  |

| CCL3     | 0xC6    | Timer 2 Compare /capture module 3 low byte register.                   |

| CCH3     | 0xC7    | Timer 2 Compare /capture module 3 high byte register.                  |

| T2CON    | 0xC8    | Timer 2 controls register.                                             |

| -        | 0xC9    | -                                                                      |

| CRCL     | 0xCA    | Timer 2 Compare/capture module 0 & reload function low byte register.  |

| CRCH     | 0xCB    | Timer 2 Compare/capture module 0 & reload function high byte register. |

| TL2      | 0xCC    | Timer 2 counting low byte register.                                    |

| TH2      | 0xCD    | Timer 2 counting high byte register.                                   |

| -        | 0xCE    | -                                                                      |

| -        | 0xCF    | -                                                                      |

| PSW      | 0xD0    | System flag register.                                                  |

| IEN4     | 0xD1    | Interrupts enable register                                             |

| ADM      | 0xD2    | ADC controls register.                                                 |

| ADB      | 0xD3    | ADC data buffer.                                                       |

| ADR      | 0xD4    | ADC resolution selects register.                                       |

| VREFH    | 0xD5    | ADC reference voltage controls register.                               |

| P1CON    | 0xD6    | Port 1 configuration controls register.                                |

| -        | 0xD7    | -                                                                      |

| SOCON2   | 0xD8    | UART baud rate controls register.                                      |

| -        | 0xD9    | -                                                                      |

| I2CDAT   | 0xDA    | I2C data buffer.                                                       |

| I2CADR   | 0xDB    | Own I2C slave address.                                                 |

| I2CCON   | 0xDC    | I2C interface operation control register.                              |

| I2CSTA   | 0xDD    | I2C Status Code.                                                       |

| SMBSEL   | 0xDE    | SMBus mode controls register.                                          |

| SMBDST   | 0xDF    | SMBus internal timeout register.                                       |

#### **0xE0 - 0xFF** Registers Description

| Register | Address     | Description                                      |

|----------|-------------|--------------------------------------------------|

| ACC      | 0xE0        | Accumulator register.                            |

| SPSTA    | 0xE1        | SPI statuses register.                           |

| SPCON    | 0xE2        | SPI control register.                            |

| SPDAT    | 0xE3        | SPI data buffer.                                 |

| POOC     | 0xE4        | Open drain controls register.                    |

| CLKSEL   | 0xE5        | Clock switch selects register.                   |

| CLKCMD   | 0xE6        | Clock switch controls Register.                  |

| TCON0    | 0xE7        | Timer 0 / 1 clock controls register.             |

| -        | 0xE8        |                                                  |

| -        | 0xE9        |                                                  |

| -        | 0xEA        | -                                                |

| -        | OxEB        | -                                                |

| -        | 0xEC        | -                                                |

| -        | 0xED        | -                                                |

| -        | <b>OxEE</b> | -                                                |

| -        | <b>OxEF</b> | -                                                |

| В        | 0xF0        | Multiplication/ division instructiondata buffer. |

| POUR     | 0xF1        | Port 0 pull-up resister controls register.       |

| P1UR     | 0xF2        | Port 1 pull-up resister controls register.       |

| P2UR     | 0xF3        | Port 2 pull-up resister controls register.       |

| -        | 0xF4        | -                                                |

| -        | 0xF5        | -                                                |

| -        | 0xF6        | -                                                |

| SRST     | 0xF7        | Software reset controlsregister.                 |

| -        | 0xF8        | -                                                |

| POM      | 0xF9        | Port 0 input/output mode register.               |

| P1M      | 0xFA        | Port 1 input/output mode register.               |

| P2M      | 0xFB        | Port 2 input/output mode register.               |

| -        | 0xFC        | -                                                |

| -        | 0xFD        | -                                                |

| _        | 0xFE        | -                                                |

| PFLAG    | 0xFF        | Reset flag register.                             |

|          |             |                                                  |

## 6.3 System Registers

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit O |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| ACC      | ACC7  | ACC6  | ACC5  | ACC4  | ACC3  | ACC2  | ACC1  | ACC0  |

| В        | B7    | B6    | B5    | B4    | B3    | B2    | B1    | B0    |

| PSW      | CY    | AC    | FO    | RS1   | RSO   | OV    | F1    | Р     |

#### ACC Register (0xE0)

| Bit | Field    | Туре | Initial | Description                                              |

|-----|----------|------|---------|----------------------------------------------------------|

| 70  | ACC[7:0] | R/W  | 0x00    | The ACC is an 8-bit data register responsible for        |

|     |          |      |         | transferring or manipulating data between ALU and data   |

|     |          |      |         | memory. If the result of operating is overflow (OV) or   |

|     |          |      |         | there is carry (C or AC) and parity (P) occurrence, then |

|     |          |      |         | these flags will be set to PSW register.                 |

#### B Register (0xF0)

| Bit | Field  | Туре | Initial | Description                                                 |

|-----|--------|------|---------|-------------------------------------------------------------|

| 70  | B[7:0] | R/W  | 0x00    | The B register is used during multiplying and division      |

|     |        |      |         | instructions. It can also be used as a scratch-pad register |

|     |        |      |         | to hold temporary data.                                     |

#### PSW Register (0xD0)

| Bit | Field   | Туре | Initial | Description                                               |

|-----|---------|------|---------|-----------------------------------------------------------|

| 7   | CY      | R/W  | 0       | Carry flag.                                               |

|     |         |      |         | 0: Addition without carry, subtraction with borrowing     |

|     |         |      |         | signal, rotation with shifting out logic "0", comparison  |

|     |         |      |         | result < 0.                                               |

|     |         |      |         | 1: Addition with carry, subtraction without borrowing,    |

|     |         |      |         | rotation with shifting out logic "1", comparison          |

|     |         |      |         | result ≥ 0.                                               |

| 6   | AC      | R/W  | 0       | Auxiliary carry flag.                                     |

|     |         |      |         | 0: If there is no a carry-out from 3rd bit of Accumulator |

|     |         |      |         | in BCD operations.                                        |

|     |         |      |         | 1: If there is a carry-out from 3rd bit of Accumulator in |

|     |         |      |         | BCD operations.                                           |

| 5   | FO      | R/W  | 0       | General purpose flag 0. General purpose flag available    |

|     |         |      |         | for user.                                                 |

| 43  | RS[1:0] | R/W  | 00      | Register bank select control bit, used to select working  |

|     |         |      |         | register bank.                                            |

|     |         |      |         | 00: 00H – 07H (Bnak0)                                     |

|     |         |      |         | 01: 08H – 0FH (Bnak1)                                     |

|     |         |      |         | 10: 10H – 17H (Bnak2)                                     |

|     |         |      |         | 11: 18H – 1FH (Bnak3)                                     |

| 2   | OV      | R/W  | 0       | Overflow flag.                                            |

|     |         |      |         | 0: Non-overflow in Accumulator during arithmetic          |

|     |         |      |         | Operations.                                               |

|     |         |      |         | 1: overflow in Accumulator during arithmetic              |

|     |         |      |         | Operations.                                               |

| 1   | F1      | R/W  | 0       | General purpose flag 1. General purpose flag available    |

|     |         |      |         | for user.                                                 |

| 0   | Р       | R    | 0       | Parity flag. Reflects the number of '1's in the           |

|     |         |      |         | Accumulator.                                              |

|     |         |      |         | 0: if Accumulator contains an even number of '1's.        |

|     |         |      |         | 1: Accumulator contains an odd number of '1's.            |

## 6.4 RegisterDeclaration

SN8F5702 has many registers to control various functions, but SFR name is not predefined in the C51 / A51 compiler. To make programming easier and therefore need to add header files to declare SFR name.

When using the assembly code programs, please add the following sentence.

- 1 \$NOMOD51;Do not recognize the 8051-specific predefined special register.

- 2 #include<SN8F5702.H>

When using the C code programs, please add the following sentence.

1 #include<SN8F5702.H>

After adding the header file, user can use name of registers to program. During compilation, the compiler will register name translate into register position through the header file.

Different devices need to use a different header file to declare, but the option file is to use the same.

| Device     | Header file  | Options file         |

|------------|--------------|----------------------|

| SN8F5702   | SN8F5702.h   |                      |

| SN8F570200 | SN8F570200.h |                      |

| SN8F570202 | SN8F570202.h |                      |

| SN8F570210 | SN8F570210.h | OPTIONS_SN8F5702.A51 |

| SN8F570211 | SN8F570211.h |                      |

| SN8F570212 | SN8F570212.h |                      |

| SN8F570213 | SN8F570213.h |                      |

#### 7 Reset and Power-on Controller

The reset and power-on controller has four reset sources: low voltage detectors (LVDs), watchdog, programmable external reset pin, and software reset. The first three sources would trigger an additional power-on sequence. Subsequently, the microcontroller initializes all registers and starts program execution with its reset vector (ROM address 0x0000).

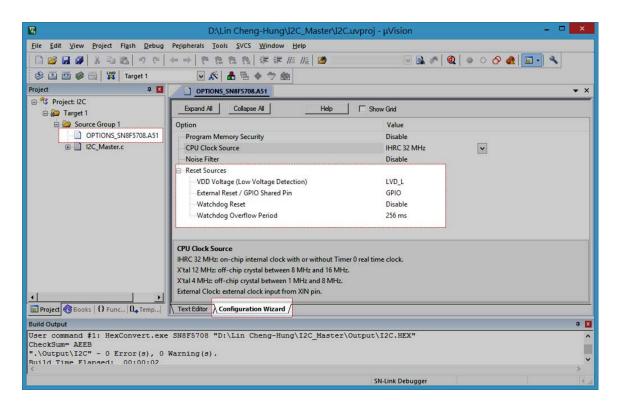

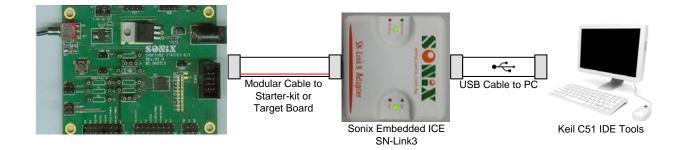

#### 7.1 Configuration of Reset and Power-on Controller

SONiXpublishes an *OPTIONS\_SN8F5702.A51 file* in *SN-Link Driver for Keil C51.exe* (downloadable on cooperative website: www.sonix.com.tw). Thisoptions file contains appropriate parameters of reset sources and CPU clock source selection, and is strongly recommended to add to Keil project. *SN8F5000 Debug Tool Manual* provides the further detail of this configuration.

- Program Memory Security

- CPU Clock Source

- Noise Filter

- Reset Source : VDD Voltage (Low Voltage Detection)

- Reset Source : External Reset / GPIO Shared Pin

- Reset Source : Watchdog Reset& Overflow Period

The code option is the system hardware configurations including oscillator type, noise filter option, watchdog timer operation, LVD option, reset pin option and flash ROM security control. The code option items are as following table:

| Code Option       | Content                 | Function Description                             |  |

|-------------------|-------------------------|--------------------------------------------------|--|

| Program Memory    | Security Disable        | Disable ROM code Security function               |  |

| Security          | Security Enable         | Enable ROM code Security function                |  |

| CPU Clock Source  | IHRC 32MHz              | High speed internal 32MHz RC.                    |  |

| LVD               | LVD_L                   | LVD will reset chip if VDD is below 1.8V         |  |

| External Reset    | Reset with De-bounce    | Enable External reset pin with De-bounce         |  |

|                   | Reset without De-bounce | Enable External reset pin without De-bounce      |  |

|                   | GPIO with P02           | Enable P02                                       |  |

| Watchdog Reset    | Always                  | Watchdog timer is always on enable even in       |  |

|                   |                         | STOP mode and IDLE mode                          |  |

|                   | Enable                  | Enable watchdog timer. Watchdog timer            |  |

|                   |                         | stops in STOP mode and IDLE mode                 |  |

|                   | Disable                 | Disable Watchdog function                        |  |

| Watchdog Overflow | 64ms                    | Watchdog timer clock source F <sub>ILRC</sub> /4 |  |

| Period            | 128ms                   | Watchdog timer clock source F <sub>ILRC</sub> /8 |  |

|                   | 256ms                   | Watchdog timer clock source $F_{ILRC}$ /16       |  |

|                   | 512ms                   | Watchdog timer clock source $F_{ILRC}$ /32       |  |

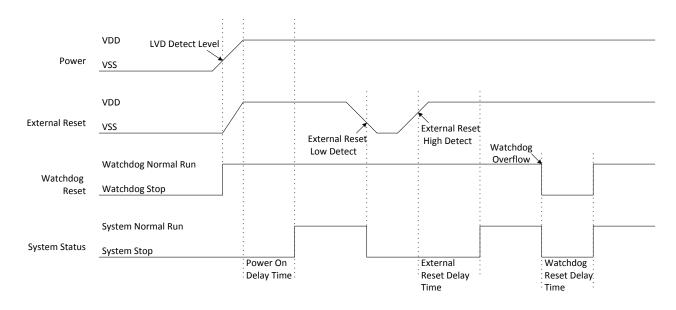

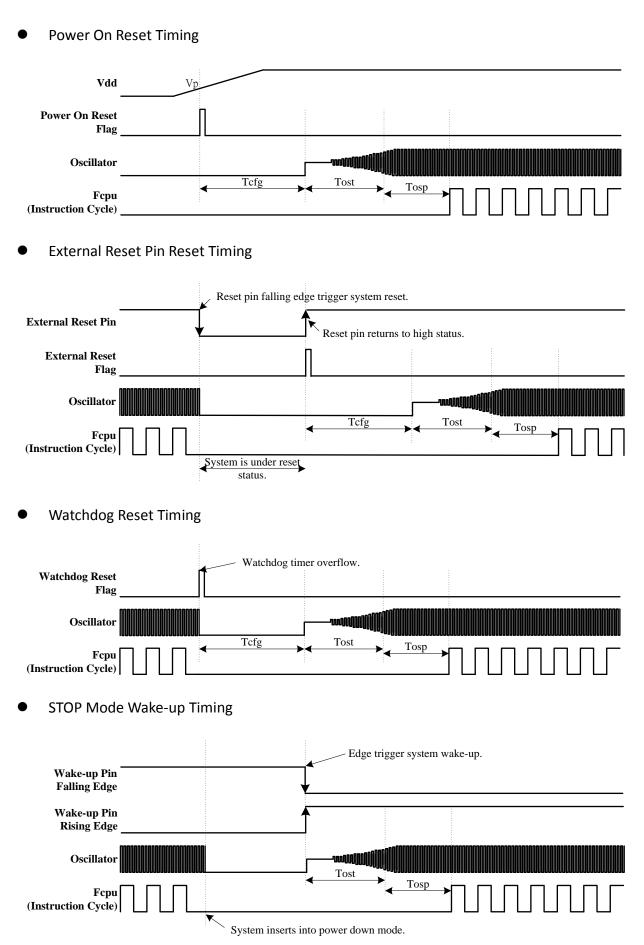

# 7.2 Power-on Sequence

A power-on sequence would be triggered by LVD, watchdog, and external reset pin. It takes place between the end of reset signal and program execution. Overall, it includes two stages: power stabilization period, and clock stabilization period.

The power stabilization period spends 5 msin typical condition. Afterward the microcontroller fetches CPU Clock Source selectionautomatically. The selected clock source would be driven, and the system counts 4096 times of the clock period to ensure its reliability.

Note: In high power noise environment, user can put 10ohm resistor in the front of 0.1uF capacitor& VDD PAD to suppress power noise and avoid IC damage.

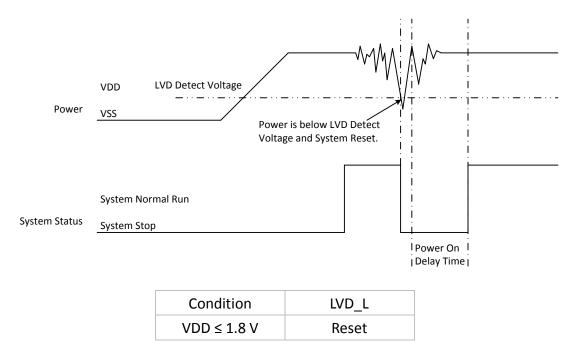

# 7.3 LVD Reset

The low voltage detectors monitor VDD pin's voltage at only one level: 1.8 V. Depend on low voltage detection configuration, the comparison result can be seen as a system reset signal. The table below lists low voltage detection configuration, LVD\_L, and the results of VDD pin's condition.

# 7.4 Watchdog Reset

Watchdog is a periodic reset signal generator for the purpose of monitoring the execution flow. Its internal timer is expected to be cleared in a check point of program flow; therefore, the actual reset signal would be generated only after a software problem occurs. Writing 0x5A to WDTR is the proper method to place a check point in program.

1 WDTR =  $0 \times 5A$ ;

Watchdog timer interval time = 256 \* 1/ (Internal Low-Speed oscillator frequency/WDT Pre-scalar) = 256 / ( $F_{ILRC}$ /WDT Pre-scaler) ...sec

| Internal low-speed        | WDT                   | Watchdog interval time |

|---------------------------|-----------------------|------------------------|

| oscillator                | pre-scaler            |                        |

|                           | F <sub>ILRC</sub> /4  | 256/(16000/4)=64ms     |

| F 10 ku-                  | F <sub>ILRC</sub> /8  | 256/(16000/8)=128ms    |

| F <sub>ILRC</sub> =16 kHz | F <sub>ILRC</sub> /16 | 256/(16000/16)=256ms   |

|                           | F <sub>ILRC</sub> /32 | 256/(16000/32)=512ms   |

The operation mode of watchdog is configurable in options file:

Always mode counts its internal timer in all CPU operation modes (normal, IDLE, SLEEP);

**Enable mode** counts its internal timer during CPU stays in normal mode, and it would not trigger watchdog reset in IDLE and STOP modes;

**Disable mode** suspends its internal timer at all CPU modes, and the watchdog would not trigger in this condition.

When watchdog is operating in always mode, the system will consume additional power.

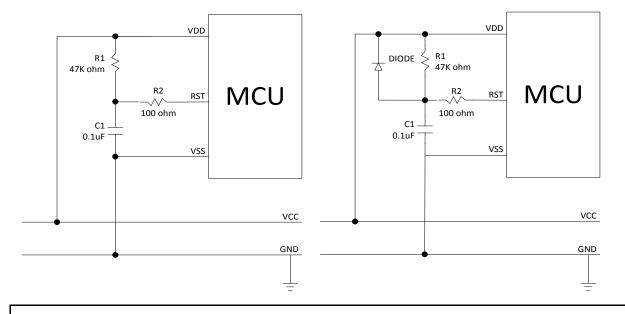

# 7.5 External Reset Pin

Programmable external reset pin is configurable in *options file*. Once it is enabled, it monitors its shared pin's logic level. A logical low (lower than 30% of VDD) would immediatelytrigger system reset until the input is recovered to high (lager than 70% of VDD).

An optional de-bounce period can improve reset signal's stability. Instead of immediate reset, the system reset requires an8-ms-long logic low to avoid bouncing from a button key. Any signal lower than de-bounce period would not affect the CPU's execution.

#### \* Note:

1. The reset circuit is no any protection against unusual power or brown out reset on the left side of the figure.

2. The R2 100 ohm resistor of "Simply reset circuit" and "Diode & RC reset circuit" is necessary to limit any current flowing into reset pin from external capacitor C in the event of reset pin breakdown due to Electrostatic Discharge (ESD) or Electrical Over-stress (EOS) on the right side of the figure.

#### 7.6 Software Reset

A software reset would be generated after consecutively set SRSTREQ register. As a result, this procedure enables firmware'sability reset microcontroller (e.g. reset after firmware update). The following sample C code repeatedly set the least bit of SRST register to perform software reset.

```

1 SRST = 0x01;

2 SRST = 0x01;

```

| 7.7 | <b>Reset and</b> | Power-on Con | troller Registers |

|-----|------------------|--------------|-------------------|

|-----|------------------|--------------|-------------------|

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit O   |

|----------|-------|-------|-------|-------|-------|-------|-------|---------|

| PFLAG    | POR   | WDT   | RST   | -     | -     | -     | -     | -       |

| SRST     | -     | -     | -     | -     | -     | -     | -     | SRSTREQ |

| WDTR     | WDTR7 | WDTR6 | WDTR5 | WDTR4 | WDTR3 | WDTR2 | WDTR1 | WDTR0   |

#### **PFLAG Register**

| Bit | Field    | Туре | Initial | Description                                              |

|-----|----------|------|---------|----------------------------------------------------------|

| 7   | POR      | R    | -       | This bit is automatically set if the microcontroller has |

|     |          |      |         | been reset by LVD.                                       |

| 6   | WDT      | R    | -       | This bit is automatically set if the microcontroller has |

|     |          |      |         | been reset by watchdog.                                  |

| 5   | RST      | R    | -       | This bit is automatically set if the microcontroller has |

|     |          |      |         | been reset by external reset pin.                        |

| 43  | Reserved | R    | 0       |                                                          |

| 02  | Reserved | R    | 0       |                                                          |

|     |          |      |         |                                                          |

#### SRST Register

|     | -        |      |         |                                                     |

|-----|----------|------|---------|-----------------------------------------------------|

| Bit | Field    | Туре | Initial | Description                                         |

| 71  | Reserved | R    | 0       |                                                     |

| 0   | SRSTREQ  | R/W  | 0       | Consecutively set this bit for two times to trigger |

|     |          |      |         | software reset.                                     |

#### WDTR Register (0x86)

| Bit | Field     | Туре | Initial | Description                                           |

|-----|-----------|------|---------|-------------------------------------------------------|

| 70  | WDTR[7:0] | W    | -       | Watchdog clear is controlled by WDTR register. Moving |

|     |           |      |         | 0x5A data into WDTR is to reset watchdog timer.       |

#### 8 System Clock and Power Management

For power saving purpose, the microcontroller built in three different operation modes: normal, IDLE, and STOP mode.

The normal mode means that CPU and peripheral functions are under normally execution. The system clock is based on the combination of source selection, clock divider, and program memory wait state. IDLE mode is the situation that temporarily suspends CPU clock and its execution, yet it remains peripherals' functionality (e.g. timers, PWM, SPI, UART, and I2C). By contrast, STOP mode disables all functions and clock generator until a wakeup signal to return normal mode.

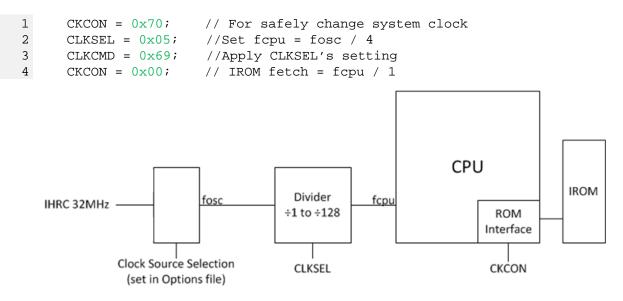

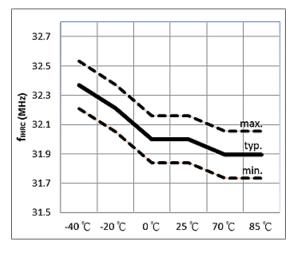

#### 8.1 System Clock

The microcontroller includes an on-chip clock generator (IHRC 32MHz). The reset and power-on controller automatically loads clock source selection during power-on sequence. Therefore, the selected clock source is seen as 'fosc' domain which is a fixed frequency at any time.

Subsequently, the selected clock source (fosc) is divided by 1 to 128 times which is controlled by CLKSEL register. The CPU input the divided clock as its operation base (named fcpu). Applying CLKSEL's setting when CLKCMD register be written0x69.

ROM interface is built in between CPU and IROM (program memory). It optionally extends the data fetching cycle in order to support lower speed program memory. For example if the CPU is anticipated to run at 32 MHz and the IROM has to run at 8 MHz, three extended cyclemust be placed by CKCON register.

IROM fetching cycle =

$$\frac{\text{fcpu}}{\text{PWSC}[2:0]+1} \le 8\text{MHz}, \text{PWSC}[2:0] = 0 \sim 7$$

\* Note: For user develop program in C language or assembly,the first line of the program "must be set" CKCON = 0x70and then set CLKSEL= 0x07~0x00, CLKMD= 0x69, CKCON= 0x00~0x70, this priority cannot be modified.

System clock rate and program memory extended cycle limitation as follows.

| Code Option<br>CPU Clock Source | Fcpu = CLKSEL[2:0]                                                                                                      | IROM Fetch = CKCON[6:4]                                                                                                                                       |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IHRC32M                         | Only Support<br>000 =fosc / 128<br>001 =fosc / 64<br>010 =fosc / 32<br>011 =fosc / 16<br>100 =fosc / 8<br>101 =fosc / 4 | Support<br>000 =fcpu / 1=>Recommend!<br>001 =fcpu / 2<br>010 =fcpu / 3<br>011 =fcpu / 4<br>100 =fcpu / 5<br>101 =fcpu / 6<br>110 = fcpu / 7<br>111 = fcpu / 8 |

# 8.2 High Speed Clock and Real time clock

High-speed clock only has internal clock. The internal high-speed oscillator is 32MHz RC type. These high-speed oscillators are selected by *SN8F5702\_OPTIONS.A51*.

• IHRC32M: The system high-speed clock source is internal high-speed 32MHz RC type oscillator.

# 8.3 Power Management

After the end of reset signal and power-on sequence, the CPU starts program execution at the speed of fcpu. Overall, the CPU and all peripherals are functional in this situation (categorized as normal mode).

The least two bits of PCON register (IDLE at bit 0 and STOP at bit 1) control the microcontroller's power management unit.

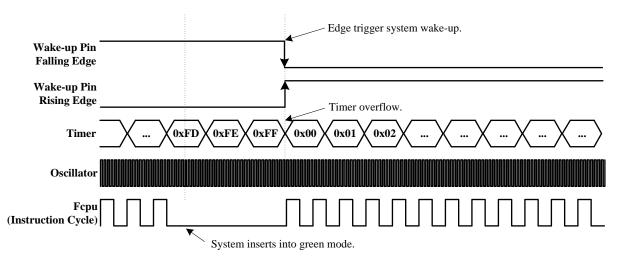

If IDLE bit is set by program, only CPU clock source would be gated. Consequently, peripheral functions (such as timers, PWM, and I2C) and clock generator (IHRC 32 MHz) remain execution in this status. Any change from PO/P1 input and interrupt events can make the microcontroller turns

back to normal mode, and the IDLE bit would be cleared automatically.

- Any function can work in IDLE mode. Only CPU is suspended

- The IDLE mode wake-up sources are P0/P1 level change trigger and any interrupt event.

If STOP bit is set, by contrast, CPU, peripheral functions, and clock generator are suspended. Data storage in registers and RAM would be kept in this mode. Any change from PO/P1 can wake up the microcontroller and resume system's execution. STOP bit would be cleared automatically.

- CPU, peripheral functions, and clock generator are suspended.

- The STOP mode wake-up source is P0/P1 level change trigger.

For user who is develop program in C language, IDLE and STOP macros is strongly recommended to control the microcontroller's system mode, instead of set IDLE and STOP bits directly.

- 1 IDLE(); 2 STOP();

- \* Note: Into IDLE mode or STOP mode by "Assembly Language" must be using MOV instruction.

## 8.4 System Clock Timing

| Parameter                   | Symbol | Description                                                                                                                                                                                                                                                                                                                 | Typical                                                                                                                              |

|-----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Hardware configuration time | Tcfg   | 131072*F <sub>IHRC</sub>                                                                                                                                                                                                                                                                                                    | 4.096ms @<br>F <sub>IHRC</sub> = 32MHz                                                                                               |

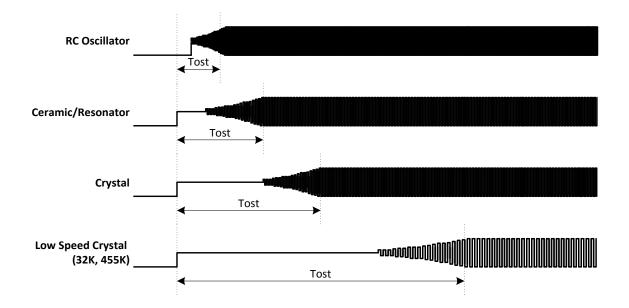

| Oscillator start up time    | Tost   | The start-up time is depended on<br>oscillator's material, factory and<br>architecture. Normally, the low-speed<br>oscillator's start-up time is lower than<br>high-speed oscillator. The RC type<br>oscillator's start-up time is faster than<br>crystal type oscillator.                                                  | -                                                                                                                                    |

| Oscillator warm-up<br>time  | Tosp   | Oscillator warm-up time of reset condition.<br>2048*F <sub>hosc+</sub> 5*F <sub>ILRC</sub><br>(Power on reset, LVD reset, watchdog reset,<br>external reset pin active.)                                                                                                                                                    | 825us @ F <sub>hosc</sub> =<br>4MHz<br>441us @ F <sub>hosc</sub> =<br>16MHz<br>377us @ F <sub>hosc</sub> =<br>32MHz                  |

|                             |        | Oscillator warm-up time of power down<br>mode wake-up condition.<br>2048*F <sub>hosc+</sub> 5*F <sub>ILRC</sub> Crystal/resonator<br>type oscillator, e.g. 32768Hz crystal, 4MHz<br>crystal, 16MHz crystal<br>64*F <sub>hosc+</sub> 5*F <sub>ILRC</sub> RC type oscillator, e.g.<br>internal high-speed RC type oscillator. | X'tal:<br>825us @ F <sub>hosc</sub> =<br>4MHz<br>441us @ F <sub>hosc</sub> =<br>16MHz<br>RC:<br>315us @ F <sub>hosc</sub> =<br>32MHz |

#### • IDLE Mode Wake-up Timing

#### • Oscillator Start-up Time

The start-up time is depended on oscillator's material, factory and architecture. Normally, the low-speed oscillator's start-up time is lower than high-speed oscillator.

## 8.5 System Clock and Power Management Registers

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit O          |

|----------|-------|-------|-------|-------|-------|---------|---------|----------------|

| CKCON    | -     | PWSC2 | PWSC1 | PWSC0 | ESYN  | EWSC2   | EWSC1   | EWSC0          |

| CLKSEL   | -     | -     | -     | -     | -     | CLKSEL2 | CLKSEL1 | <b>CLKSELO</b> |

| CLKCMD   | CMD7  | CMD6  | CMD5  | CMD4  | CMD3  | CMD2    | CMD1    | CMD0           |

| PCON     | SMOD  | -     | -     | -     | -     | GF0     | STOP    | IDLE           |

| P1W      | P17W  | P16W  | P15W  | P14W  | P13W  | P12W    | P11W    | P10W           |

## **CKCON Register (0x8E)**

| Bit  | Field     | Туре | Initial | Description                                         |

|------|-----------|------|---------|-----------------------------------------------------|

| 7    | Reserved  | R    | 0       |                                                     |

| 64   | PWSC[2:0] | R/W  | 111     | Extended cycle(s) applied to reading program memory |

|      |           |      |         | 000: non                                            |

|      |           |      |         | 001: 1 cycle                                        |

|      |           |      |         | 010: 2 cycles                                       |

|      |           |      |         | 011: 3 cycles                                       |

|      |           |      |         | 100: 4 cycles                                       |

|      |           |      |         | 101: 5 cycles                                       |

|      |           |      |         | 110: 6 cycles                                       |

|      |           |      |         | 111: 7 cycles                                       |

| Else | Reserved  | R    | 0001    |                                                     |

## **CLKSEL Register (0xE5)**

|     |             | -    |         |                                            |

|-----|-------------|------|---------|--------------------------------------------|

| Bit | Field       | Туре | Initial | Description                                |

| 73  | Reserved    | R    | 0x00    |                                            |

| 20  | CLKSEL[2:0] | R/W  | 111     | CLKSEL would be applied by writing CLKCMD. |

|     |             |      |         | 000: fcpu = fosc / 128                     |

|     |             |      |         | 001: fcpu = fosc / 64                      |

|     |             |      |         | 010: fcpu = fosc / 32                      |

|     |             |      |         | 011: fcpu = fosc / 16                      |

|     |             |      |         | 100: fcpu = fosc / 8                       |

|     |             |      |         | 101: fcpu = fosc / 4                       |

|     |             |      |         | 110: fcpu = fosc / 2                       |

|     |             |      |         | 111: fcpu = fosc / 1                       |

#### CLKCMD Register (0xE6)

| Bit | Field    | Туре | Initial | Description                             |

|-----|----------|------|---------|-----------------------------------------|

| 70  | CMD[7:0] | W    | 0x00    | Writing 0x69 to apply CLKSEL's setting. |

## PCON Register (0x87)

| Bit | Field    | Туре | Initial | Description                            |

|-----|----------|------|---------|----------------------------------------|

| 7   |          |      |         | Refer to other chapter(s)              |

| 63  | Reserved | R    | 0x00    |                                        |

| 2   | GF0      | R/W  | 0       | General Purpose Flag                   |

| 1   | STOP     | R/W  | 0       | 1: Microcontroller switch to STOP mode |

| 0   | IDLE     | R/W  | 0       | 1: Microcontroller switch to IDLE mode |

|     |          |      |         |                                        |

### P1W Register (0x91)

| Bit | Field        | Туре | Initial | Description                          |

|-----|--------------|------|---------|--------------------------------------|

| 70  | 0 P1nW R/W 0 |      | 0       | 0: Disable P1.n wakeup functionality |

|     |              |      |         | 1: Enable P1.n wakeup functionality  |

## 9 System Operating Mode

The chip builds in three operating mode for difference clock rate and power saving reason. These modes control oscillators, op-code operation and analog peripheral devices' operation.

- Normal mode: System high-speed operating mode

- IDLE mode: System idle mode (Green mode)

- STOP mode: System power saving mode (Sleep mode)

#### One of Reset trigger source active

The operating mode clock control as following table:

| OperatingMode           | Normal Mode       | IDLE Mode             | STOP Mode                |  |

|-------------------------|-------------------|-----------------------|--------------------------|--|

| IHRC                    | IHRC: Running     | IHRC: Running         | Stop                     |  |

| IIIIC                   | Ext. OSC: Disable | Ext. OSC: Disable     | Stop                     |  |

| ILRC                    | Running           | Running               | Watchdog always: Running |  |

| ILKC                    | Kunning           | Kunning               | Other : stop             |  |

| CPU instruction         | Executing         | Stop                  | Stop                     |  |

| Timer 0                 | Active by TR0     | Active by TR0         | Inactive                 |  |

| (Timer, Event counter)  | Active by TRO     | Active by TRO         | mactive                  |  |

| Timer 1                 | Active by TR1     | Active by TR1         | Inactivo                 |  |

| (Timer, Event counter)  | ACLIVE BY TKI     | Active by TKI         | Inactive                 |  |

| Timer 2                 | Active as enable  | Active as enable      | Inactive                 |  |

| (Timer, capture, T2COM) | Active as enable  | Active as enable      |                          |  |

| PWM                     | Active as enable  | Active as enable      | Inactive                 |  |

| UART                    | Active as enable  | Active as enable      | Inactive                 |  |

| SPI                     | Active as enable  | Active as enable      | Inactive                 |  |

| I2C                     | Active as enable  | Active as enable      | Inactive                 |  |

| ADC                     | Active as enable  | Active as enable      | Inactive                 |  |

| Watchdog timor          | By Watchdog       | By Watchdog           | By Watchdog              |  |

| Watchdog timer          | Code option       | Code option           | Code option              |  |

| Internal interrupt      | All active        | All active            | All inactive             |  |

| External interrupt      | All active        | All active            | All inactive             |  |

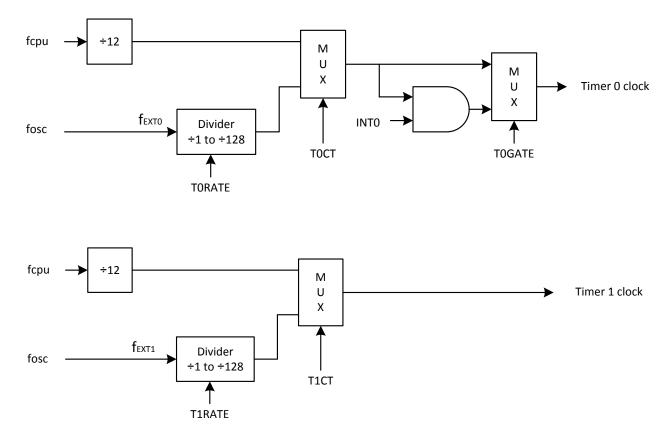

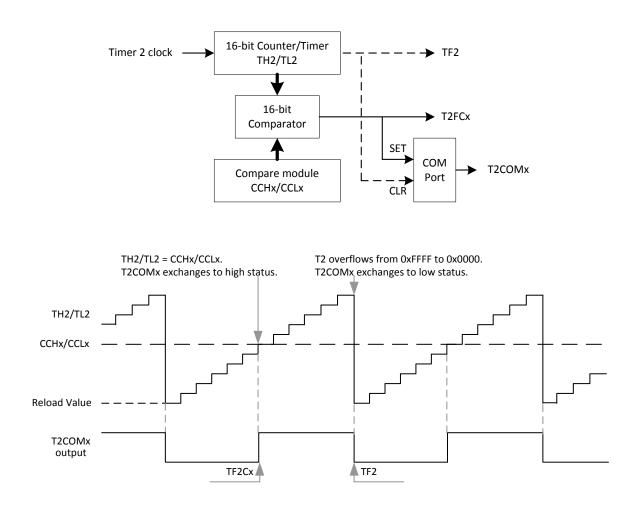

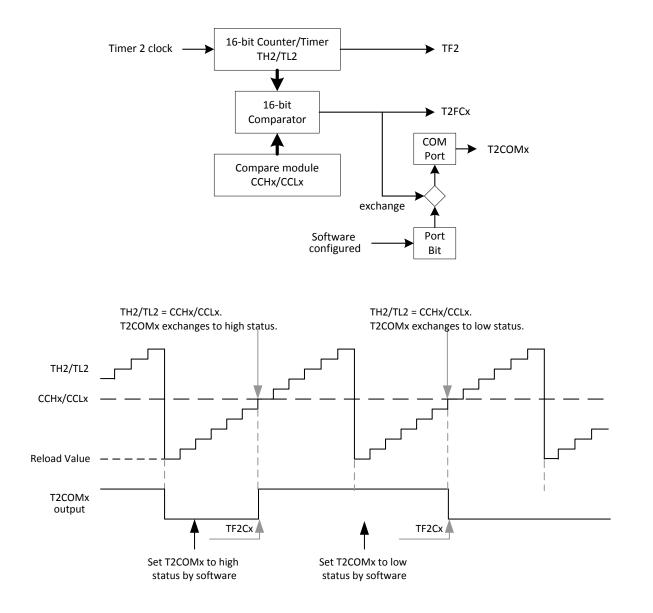

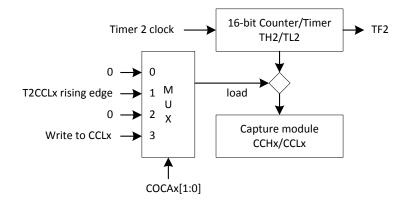

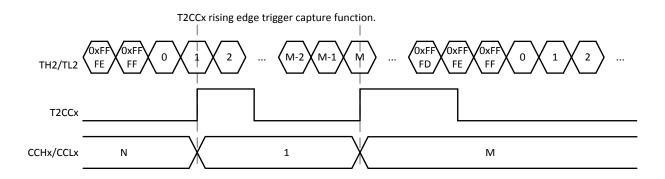

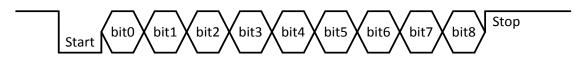

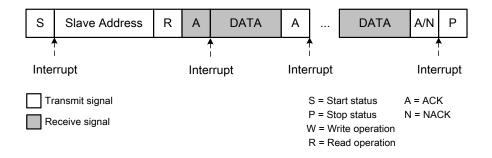

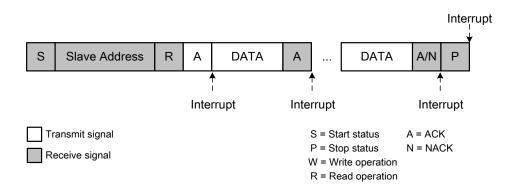

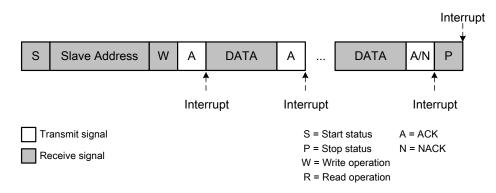

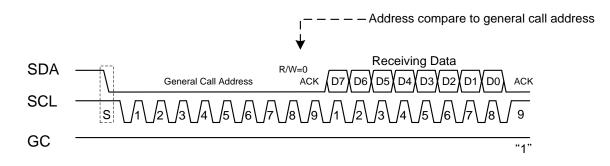

|                         |                   | PO, P1, Reset,All     |                          |  |