# UM1839 User manual

EVALSTGAP1S: demonstration board for STGAP1S galvanically isolated single gate driver

#### Introduction

The STGAP1S gapDRIVE™ is a galvanically isolated single gate driver for N-channel MOSFETs and IGBTs with advanced protection, configuration and diagnostic features. The architecture of the STGAP1S isolates the channel from the control and the low voltage interface circuitry through a true galvanic isolation.

The EVALSTGAP1S board allows evaluating all of the STGAP1S features while driving a power switch with a voltage rating up to 1500 V. Power switches in both TO-220 and TO-247 packages can be evaluated, and the board allows the connection of a heatsink in order to exploit the ability of the STGAP1S to handle very high power applications.

In combination with the STEVAL-PCC009V2 communication board and the gapDRIVE™ evaluation software, the board allows to easily enable, configure or disable all of the driver's protection and control features through the SPI interface. Advanced diagnostic is also available thanks to the driver's status registers that can be accessed through the SPI.

Multiple boards can be connected together and share the same logic supply voltage and control signals in order to evaluate half bridge, interleaved or even more complex topologies. The board allows implementing the SPI daisy chain when more than one device is used.

Figure 1. EVALSTGAP1S demonstration board

November 2014 DocID027168 Rev 1 1/18

Contents UM1839

# **Contents**

| 1 | Hardware description and configuration |          |                                                             | 3  |

|---|----------------------------------------|----------|-------------------------------------------------------------|----|

| 2 | Con                                    | nection  | of two EVALSTGAP1S boards                                   | 6  |

| 3 | Gett                                   | ing star | ted                                                         | 10 |

|   | 3.1                                    | Using    | EVALSTGAP1S in standalone mode                              | 10 |

|   |                                        | 3.1.1    | Check list                                                  | 10 |

|   |                                        | 3.1.2    | EVALSTGAP1S board setup example                             | 10 |

|   |                                        | 3.1.3    | EVALSTGAP1S board in standalone mode                        | 10 |

|   |                                        | 3.1.4    | EVALSTGAP1S default parameters                              | 11 |

|   | 3.2                                    |          | EVALSTGAP1S with STEVAL-PCC009V2 and STGAP1S ation software | 11 |

|   |                                        | 3.2.1    | Check list                                                  | 11 |

|   |                                        | 3.2.2    | Single EVALSTGAP1S board setup example                      | 11 |

|   |                                        | 3.2.3    | Connection to STEVAL-PCC009V2 interface board               | 12 |

|   |                                        | 3.2.4    | Using two EVALSTGAP1S boards in daisy chain configuration   | 15 |

| 4 | Revi                                   | sion his | story                                                       | 17 |

## 1 Hardware description and configuration

The STGAP1S features an SPI interface that is used to set the device parameters, enable or disable the device functions and for advanced diagnostic. However for an easy device evaluation it is also possible to operate the STGAP1S without using the SPI interface. In this case the driver works with default configuration values and protections. For more details refer to Section 3.1: Using EVALSTGAP1S in standalone mode on page 10.

Table 1. STGAP1S electrical specifications

| Symbol                 | Parameter                                            | Min.                       | Max.                | Unit |

|------------------------|------------------------------------------------------|----------------------------|---------------------|------|

| VH                     | Positive supply voltage (VH vs. GNDISO)              | 4.5 <sup>(1)</sup>         | 20 <sup>(2)</sup>   | V    |

| VL                     | Negative supply voltage (VL vs. GNDISO)              | GNDISO - 10 <sup>(3)</sup> | GNDISO              | V    |

| VHL                    | Differential supply voltage (VH vs. VL)              |                            | 36                  | V    |

| VDD                    | Integrated 3.3 V voltage regulator input voltage vs. | 4.5                        | 5.5 <sup>(4)</sup>  | V    |

| VDD                    | GND                                                  | 3                          | 3.6 <sup>(5)</sup>  | V    |

| V <sub>LOGIC</sub>     | Logic pins voltage vs. GND                           |                            | VDD + 0.3           | V    |

| V <sub>IORM</sub>      | Maximum working voltage across isolation             |                            | 1500                | ٧    |

| V <sub>collector</sub> | Maximum COLLECTOR-GNDISO voltage                     |                            | 1200 <sup>(6)</sup> | ٧    |

- 1. When UVLO is enabled this value is  $VH_{on\ max}$ .

- 2. This value is limited by maximum gate-source voltage of Q1.

- 3. When UVLO is enabled this value is  $VL_{on\_max}$ .

- 4. When JP6 = OPEN (VDD is not connected to VREG pin, refer to STGAP1S DS).

- 5. When JP6 = CLOSED (VDD is connected to VREG pin, refer to STGAP1S DS).

- 6. This value is limited by the voltage rating of Q1 and D5.

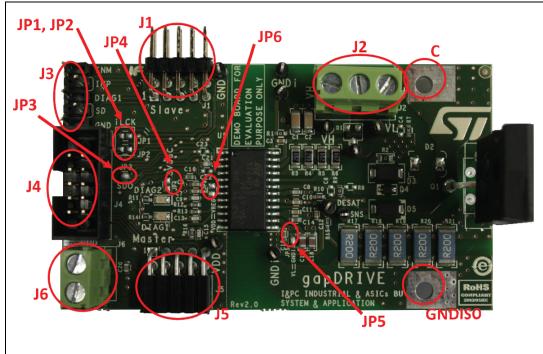

**Table 2. Connector descriptions**

| Name    | Туре                      | Function                                                                                                                                     |

|---------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| J1      | Board extension connector | Used to connect an optional slave EVALSTGAP1S board.                                                                                         |

| J2      | Power supply connector    | Used to feed supply voltage VH and optional negative supply voltage VL to the gate driving side.                                             |

| J3      | Control signals connector | Used for control (logic inputs and fault signals interfacing).                                                                               |

| J4      | Control signals connector | Used for the STGAP1S SPI and diagnostic interfacing. Connector is suitable for interfacing to the STEVAL-PCC009V2 universal interface board. |

| J5      | Board extension connector | Used to connect the master EVALSTGAP1S board in 2-board configuration.                                                                       |

| J6      | Power supply connector    | Used to feed supply voltage VDD to the logic control side.                                                                                   |

| C plate | Load connection           | A plate hole for the load current input path (IGBT collector).                                                                               |

| E plate | Load connection           | A plate hole for the load current output path (IGBT emitter).                                                                                |

In applications requiring galvanic isolation, VH and VL must be generated by an isolated power supply. If a power supply with suitable isolation is not available the gate driver's supply voltages can be provided through a battery. In case the evaluation of driver's performance does not require galvanic isolation, any power supply with suitable functional isolation may be used.

Figure 2. Jumper and connector locations - top side

**Table 3. Jumper descriptions**

| Name     | Type                  | Function                                                                      |

|----------|-----------------------|-------------------------------------------------------------------------------|

| JP1, JP2 | Configuration jumpers | IN- and IN+ sharing in 2-board configuration.                                 |

| JP3      | Configuration jumper  | For SPI daisy chaining in 2-board configuration.                              |

| JP4      | Configuration jumper  | To feed the STGAP1S with VDD voltage coming from the $\mu C$ board.           |

| JP5      | Configuration jumper  | To connect VL and GNDISO if an optional negative power supply VL is not used. |

| JP6      | Configuration jumper  | To connect VDD and Vreg when working with VDD = 3.3 V.                        |

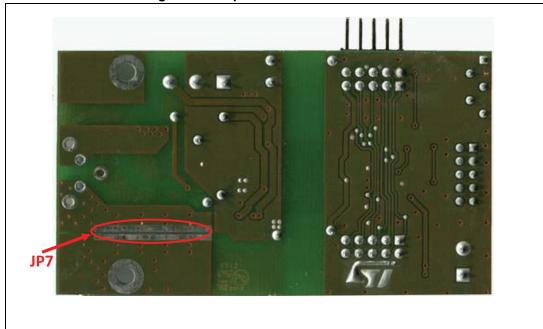

| JP7      | Configuration jumper  | To bypass shunt resistors when SENSE is not used.                             |

Table 4. Jumper configurations for VDD power supply<sup>(1)</sup>

| Operating voltage | Supply voltage source           | Jumper configurations        |

|-------------------|---------------------------------|------------------------------|

| VDD = 5 V         | External power supply (from J6) | JP4 = OPEN<br>JP6 = OPEN     |

| VDD = 3.3 V       | External power supply (from J6) | JP4 = OPEN<br>JP6 = CLOSED   |

| VDD = 3.3 V       | μC supply voltage<br>(from J4)  | JP4 = CLOSED<br>JP6 = CLOSED |

<sup>1.</sup> Input signals logic levels shall be coherent with VDD voltage (3.3\5 V).

Table 5. Jumper configurations for VL power supply

| Operating voltage | Supply voltage source      | Jumper configurations |

|-------------------|----------------------------|-----------------------|

| -10 V ≤ VL < 0 V  | External power supply (J2) | JP5 = OPEN            |

| VL not used       | VL = GNDISO                | JP5 = CLOSED          |

Table 6. Jumper configurations for SPI and input signals settings (single EVALSTGAP1S)

| Name | Function                                               | Jumper configurations |

|------|--------------------------------------------------------|-----------------------|

| JP1  | IN+ connection to the optional slave EVALSTGAP1S       | DON'T CARE            |

| JP2  | IN-/DIAG2 connection to the optional slave EVALSTGAP1S | DON'T CARE            |

| JP3  | Connects the SDO to the μC                             | CLOSED                |

Table 7. Jumper configurations for SENSE

| SENSE function | Jumper configurations       |

|----------------|-----------------------------|

| Used           | JP7 = OPEN                  |

| Not used       | JP7 = CLOSED <sup>(1)</sup> |

<sup>1.</sup> This configuration is preferred (but not mandatory) to avoid dissipating power on shunt resistors.

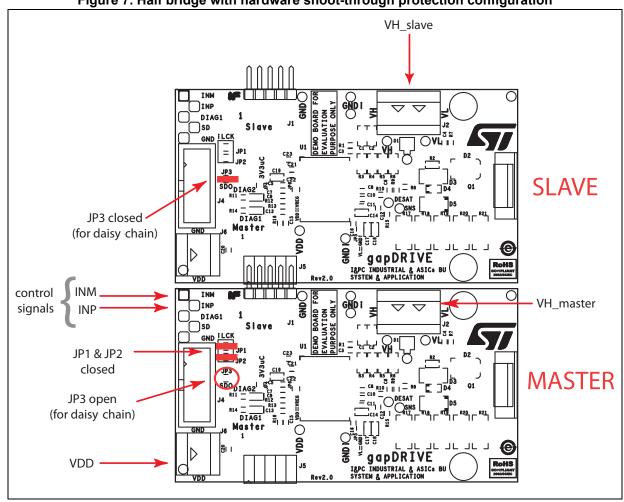

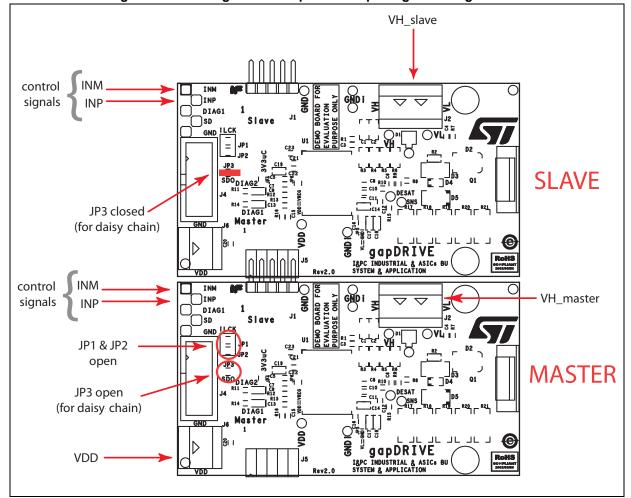

#### 2 Connection of two EVALSTGAP1S boards

It is possible to connect two EVALSTGAP1S boards through connectors J1 and J5: the lower board (master) shall be connected to the  $\mu$ C and the other one (slave) is configured through the daisy chain connection of the SPI bus.

JP3 slave

JP1, JP2 master

μC connection

J6 master

JP3 master

Figure 4. Relevant jumper and connector locations for 2-board configuration

Connecting two EVALSTGAP1S boards allows implementing independent, half bridge, or interleaved configuration of power switches  $Q1_m$  and  $Q1_s$ .

The logic side power supply VDD shall be fed to the J6 of the master board, that will also supply the slave board through J1 - J5 connectors. The jumper JP4 and JP6 of each board shall be properly set (see *Table 4*). A setting of the JP4<sub>slave</sub> is not relevant.

Positive VH and optional negative VL power supplies for each board shall be independently provided by different sources to connectors  $J2_{master}$  and  $J2_{slave}$  unless an interleaved operation is required, in which case VH, GNDISO and VL nets of each board shall be externally connected. The jumper JP5 of each board shall be properly configured (see *Table 5*).

Table 8. Jumper configurations for SPI settings using two EVALSTGAP1S boards

| Name                  | Function                      | Jumper configurations |

|-----------------------|-------------------------------|-----------------------|

| JP3 <sub>master</sub> | SPI daisy chain configuration | OPEN                  |

| JP3 <sub>slave</sub>  | SPI daisy chain configuration | CLOSED                |

Lines SD and DIAG1 of both STGAP1S drivers are shared, whereas it is possible to independently control IN+ and IN-/DIAG2 pins of each driver through appropriate lines of the  $\rm J3_{master}$  and  $\rm J3_{slave}$ .

If the STGAP1S devices are used in single input configuration both IN-/DIAG2 lines are independently present on the  $J4_{\mbox{\scriptsize master}}$  for interfacing with the  $\mu\mbox{\scriptsize C}$  and diagnostic purposes.

If the two boards are used in half bridge configuration (GNDISO  $_{\rm slave}$  and  $\rm C_{\rm master}$  plate holes shall therefore be connected) it is possible to achieve cross conduction prevention by driving both drivers with only two µC lines as shown in Figure 5.

lın+ gapDRIVE HS -אוב HIN μC LIN gapDRIVE LS

Figure 5. Half bridge configuration with hardware shoot-through protection

In order to use this configuration the STGAP1S shall be used as 2-input device and the JP1 and JP2 jumpers shall be properly set (see Table 9).

Gate driving configuration Source of IN+ and IN- control signals **Jumper configurations** JP1<sub>master</sub> = DON'T CARE Single driver (Figure 6) J3 JP2<sub>master</sub> = DON'T CARE Half bridge with hardware JP1<sub>master</sub> = CLOSED shoot-through protection J3<sub>master</sub> JP2<sub>master</sub> = CLOSED (Figure 7) JP1<sub>master</sub> = OPEN Half bridge with independent J3<sub>master</sub> for master board J3<sub>slave</sub> for slave board input signals (Figure 8) JP2<sub>master</sub> = OPEN

Table 9. Jumper configurations for input signal settings

VHcontrol INM end ! INP signals INP DIAG1 SD GND JP1 & JP2 J<u>P</u>3 don't care SDO DIAGE JP3 close 9 **e** gapDRIVE VDD ISPC INDUSTRIAL & ASIC: BU

Figure 6. Single driver configuration

Figure 7. Half bridge with hardware shoot-through protection configuration

577

Figure 8. Half bridge with independent input signal configurations

## 3 Getting started

### 3.1 Using EVALSTGAP1S in standalone mode

The STGAP1S device can work also without SPI programming using the device default values.

#### 3.1.1 Check list

- EVALSTGAP1S board

- Two power supplies (VDD and VH supply voltage)

Power supply for negative gate driving voltage VL is optional

- PWM function generator

#### 3.1.2 EVALSTGAP1S board setup example

- 1. VDD = 3.3 V or 5 V from external power supply (J6 connector)

- 2. VH from external power supply (J2 connector)

- 3. VL = GNDISO (JP5 closed)

- 4. PWM input signals can be applied to J3 connector (IN-, IN+)

If you have only one PWM signal available:

- To have gate output in phase with input command: PWM on IN+ and IN- = GND

- To have gate output out of phase with input command: PWM on IN- and IN+ = VDD

#### 3.1.3 EVALSTGAP1S board in standalone mode

- Connect the power supply to the EVALSTGAP1S VDD (J6 connector) and turn it on.

The DIAG1 LED (DL2) on the EVALSTGAP1S is turned on.

The status of the DIAG2 depends on the voltage level forced on the IN- pin.

- 2. Connect the power supply to the EVALSTGAP1S VH (J2 connector) and turn it on.

- 3. Set the SD pin low for at least 105  $\mu$ s to clear the fault (J3 connector).

- 4. Set the SD pin to the 'High' logic level (which depends on VDD value): the DIAG1 LED (DL2) is switched off.

- 5. The device outputs will now follow the input signals coming from IN+ and IN-.

UM1839 Getting started

#### 3.1.4 EVALSTGAP1S default parameters

- IN-/DIAG2 configured as input

- Active Miller clamp enabled

- Desaturation detection enabled:  $V_{DESATth} = 7 \text{ V}$  and  $I_{DESAT} = 250 \mu\text{A}$

- VDD OVLO function enabled

- Thermal shutdown protection enabled

- The DIAG1 pin reports the following faults event:

- DESAT events

- VDD supply failures

- Missing VH

- Thermal shutdown

- Register error R and L

- All others features are disabled

# 3.2 Using EVALSTGAP1S with STEVAL-PCC009V2 and STGAP1S evaluation software

Using the EVALSTGAP1S board in connection with the 'STGAP1S evaluation software' and the STEVAL-PCC009V2 interface board it is possible to evaluate the device functionalities and driving two EVALSTGAP1S boards implementing independent, half bridge, or interleaved configuration of power switches.

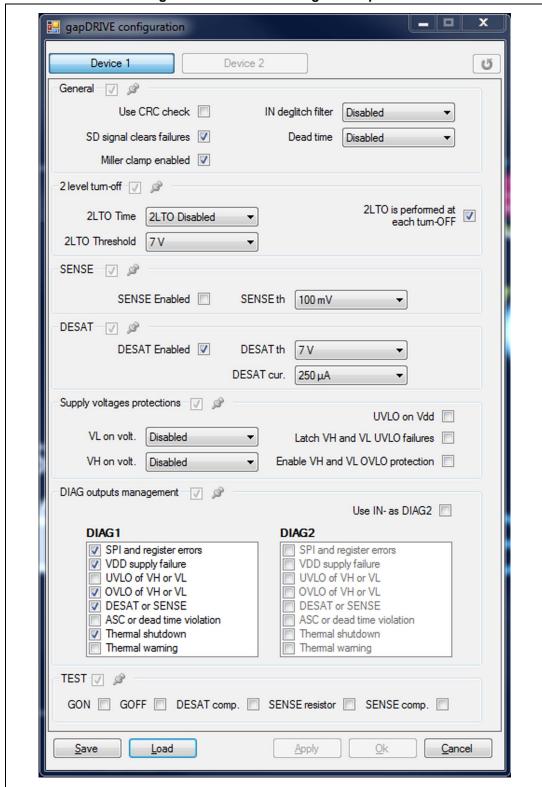

The software allows saving the device parameters configuration in a dedicated file that can be reloaded whenever it is necessary, for example after the board power-on. The 'Save' and 'Load' buttons on the bottom-left side of the STGAP1S configuration panel (*Figure 10*) have these functions.

#### 3.2.1 Check list

- Microsoft® Windows® 7 or Windows® XP PC with a free USB port

- EVALSTGAP1S board

- STEVAL-PCC009V2 interface board

- gapDRIVE™ evaluation software (the right version for your OS)

- Power supply

- PWM function generator

- 10-pin flat cable and USB MiniUSB cable

#### 3.2.2 Single EVALSTGAP1S board setup example

- 1. VDD = 3.3 V from the STEVAL-PCC009V2: closing JP4 and JP6

- 2. VH from external power supply (J2 connector)

- 3. VL = GNDISO (JP5 closed)

- 4. PWM input signals can be applied to the J3 connector (IN-, IN+)

If you have only one PWM signal available:

To have gate output in phase with input command: PWM on IN+ and IN- = GND

To have gate output out of phase with input command: PWM on IN- and IN+ = VDD

#### 3.2.3 Connection to STEVAL-PCC009V2 interface board

The EVALSTGAP1S shall be connected to the interface board and the following steps performed:

- Connect the interface board to the PC through the USB cable: the red LED (POWER -D2) turns on

- 2. Connect the interface board 10-pin connector to the EVALSTGAP1S J4 connector through the 10-pin flat cable

- The DIAG1 red LED (DL2) on the EVALSTGAP1S turns-on

- 3. Connect the power supply to VH of the EVALSTGAP1S (J2 connector) and turn it on

- 4. Start the EVALSTGAP1S evaluation software

- 5. Click the icon 'Connect' on the top left side of the GUI window to establish a connection between the EVALSTGAP1S and interface boards (see *Figure 9*)

- The DIAG1 LED (DL2) on the EVALSTGAP1S is switched off

- 6. Press the 'Refresh' button and verify all fault lights are off. If OK jump to the next point, otherwise two options are available to clear the faults and make the device operative:

- a) Perform a double transition on SD (high => low => high) clicking on the SD button

- b) Perform a status reset clicking on the 'Reset' button and after set the SD button to 'High'

- 7. Set the SD button to 'High'

- 8. Connect IN- to GND and applying the PWM on IN+, the device outputs will follow the input signal

In order to read the device status, use the 'Refresh' button to update the status indicators according to driver's status registers.

To customize the device parameters and functions open the 'STGAP1S configuration' panel pushing the relative toolbar icon (refer to *Figure 9*).

UM1839 Getting started

\_ □ 🖳 gapDRIVE Evaluation Software SPI freq BR\_1MHz → Chain Dual 0 gapDRIVE configuration ─ "connect" icon Device 1 status CRC error SPI error OVLO VH OVLO VL OVLO Vdd DESAT T Warning Reg err L ASC SD Low DIAG1 DIAG2 Refresh Reset Device 2 status DIAG2 OVLO VH OVLO VL OVLO Vdd DESAT T Warning SPI error Reg err L ASC ✓ Auto-refresh 200 Refresh Reset SW Version 1.3.5431.19010 FW Version UNK

Figure 9. STGAP1S evaluation software screenshot

In the new window shown in *Figure 10*, it is possible to enable or disable the device functionalities and set the device parameters.

Figure 10. STGAP1S configuration panel

Note:

The CRC error light will blink if the CRC check is not used ('Use CRC check' not ticked in the gapDRIVE™ configuration panel) as in the default settings.

UM1839 Getting started

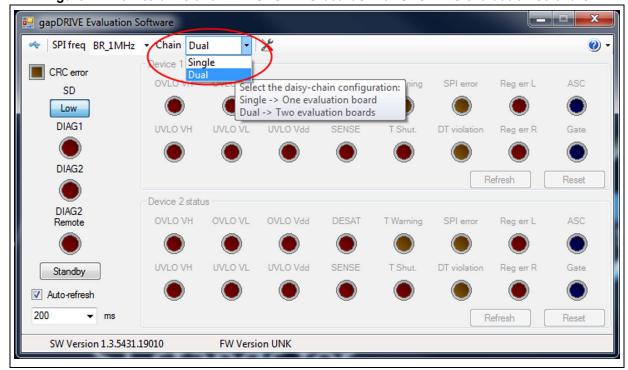

#### 3.2.4 Using two EVALSTGAP1S boards in daisy chain configuration

If you want to drive two EVALSTGAP1S boards refer to dedicated Section 2: Connection of two EVALSTGAP1S boards on page 6 for the board's connection and jumper's settings, then follow the steps of Section 3.2.3: Connection to STEVAL-PCC009V2 interface board up to point 5.

It is possible to set the driven device number using the drop down list in the software main panel.

Figure 11. How to drive two EVALSTGAP1S boards with STGAP1S evaluation software

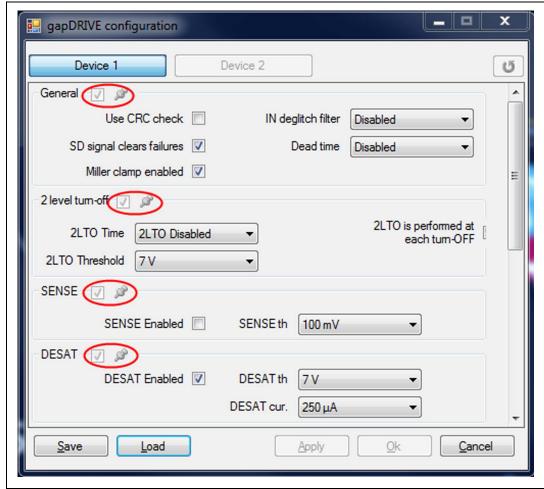

When the 'Dual' option is selected the devices parameters can be set independently selecting the 'Device 1' or 'Device 2' in the STGAP1S configuration panel. Otherwise it is possible to set some parameter values on both devices ticking one or more 'push-pin' boxes (refer to *Figure 12*).

Figure 12. How to set the same parameters in both devices

UM1839 Revision history

# 4 Revision history

Table 10. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 19-Nov-2014 | 1        | Initial release. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2014 STMicroelectronics - All rights reserved

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP130-1.8-EVALZ ADP130-1.8-EVALZ ADP1712-3.3-EVALZ ADP1714-3.3-EVALZ ADP1715-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5-EVALZ ADP1752-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3-EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ ADP2106-1.8-EVALZ ADP2147CB-110EVALZ AS3606-DB BQ24010EVM BQ24075TEVM BQ24155EVM BQ24157EVM-697 BQ24160EVM-742 BQ24296MEVM-655 BQ25010EVM BQ3055EVM NCV891330PD50GEVB ISLUSBI2CKIT1Z LM2744EVAL LM2854EVAL LM3658SD-AEV/NOPB LM3658SDEV/NOPB LM4510SDEV/NOPB LM5033SD-EVAL LP38512TS-1.8EV