# 1 x 45 W class D digital input automotive power amplifier with I<sub>Load</sub> current monitoring, wide voltage operation range for car audio and telematic

Datasheet - production data

#### **Features**

- AEC-Q100 qualified

- Integrated 108 dB D/A conversion

- I<sup>2</sup>S and TDM digital input (4/8/16CH TDM)

- Input sampling frequency: 44.1 kHz, 48 kHz, 96 kHz, 192 kHz

- Full I<sup>2</sup>C bus driving (3.3/1.8 V)

- · CISPR 25 Class V (Fourth edition)

- · Very low quiescent current

- Output lowpass filter included in the feedback allowing outstanding audio performances

- Wide operating supply range from 3.3 to 18 V, suitable for car radio, telematics and e-call

- MOSFET power outputs allowing high output power capability

- $-1 \times 25 \text{ W} / 4 \Omega @ 14.4 \text{ V}, 1 \text{ kHz THD} = 1\%$

- 1 x 30 W /4 Ω @ 14.4 V, 1 kHz THD = 10%

- 2 Ω loads driving

- Power limiting function (configurable through I<sup>2</sup>C)

- I<sup>2</sup>C bus diagnostics:

- Short to V<sub>CC</sub>/GND

- Short load and open load detection (also in play mode)

- Four thermal warnings

- DC offset detector (also in play) and 'hot spot' detection

- Clipping detector

- Integrated thermal protection

- Legacy mode ('no l<sup>2</sup>C' mode), 4 configurable settings

- Short circuit and ESD integrated protections

- Package: PowerSSO-36 exposed pad up

### **Description**

The FDA903U is a single bridge class D amplifier, designed in the most advanced BCD technology, intended for any automotive audio application (car radio, telematics and e-call, noise and tone generators, etc).

The FDA903U integrates a high performance D/A converter together with powerful MOSFET outputs in class D, so it is very compact and powerful, moreover it reaches outstanding efficiency performances (90%).

It has a very wide operating range: it can be operated both with standard car battery levels (5.5-18 V operating, compatible to load dump pulse) and with external step-down generated voltages or emergency battery (since it is compatible to minimum 3.3 V operative).

The feedback loop includes the output L-C lowpass filter, allowing superior frequency response linearity and lower distortion.

FDA903U is configurable through I<sup>2</sup>C bus interface and integrates a complete diagnostics array specially intended for automotive applications including innovative open load and DC offset detection in play mode.

Thanks to the solutions implemented to solve the EMI problems, the device is intended to be used in the standard single DIN car-radio box together with the tuner.

Moreover FDA903U features a configurable power limiting function, and can be optionally operated under no I<sup>2</sup>C mode ('legacy mode').

Table 1. Device summary

| Order code  | Package     | Packing     |

|-------------|-------------|-------------|

| FDA903U-KBT | PowerSSO-36 | Tape & reel |

| FDA903U-KBX | (Slug-up)   | Tube        |

Contents FDA903U

# **Contents**

| 1 | Bloc  | k diagram                                        | 8 |

|---|-------|--------------------------------------------------|---|

| 2 | Pins  | description                                      | 9 |

| 3 | Арр   | lication diagram                                 | 1 |

| 4 | Elec  | trical specifications1                           | 2 |

|   | 4.1   | Absolute maximum ratings                         | 2 |

|   | 4.2   | Thermal data                                     | 2 |

|   | 4.3   | Electrical characteristics                       | 2 |

|   | 4.4   | Typical curves of the main electrical parameters | 5 |

| 5 | Gen   | eral information                                 | 2 |

|   | 5.1   | LC filter design                                 | 2 |

|   | 5.2   | Load possibilities                               | 2 |

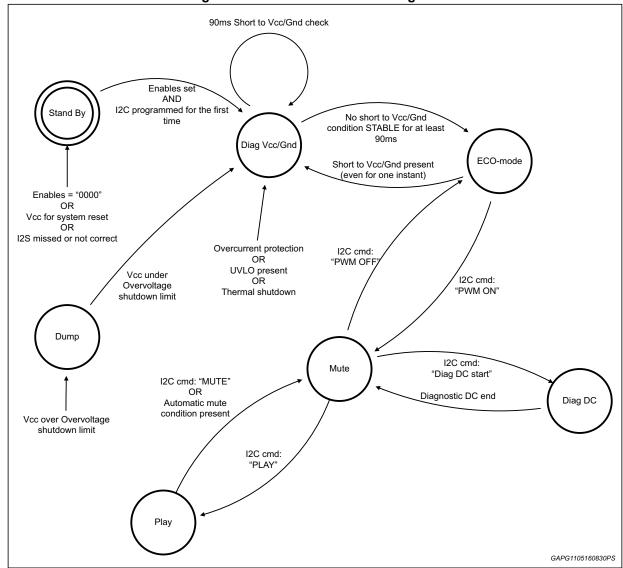

| 6 | Finit | te state machine                                 | 3 |

|   | 6.1   | Device state and address selection               | 4 |

|   | 6.2   | Standby state                                    | 5 |

|   | 6.3   | Diagnostic Vcc-Gnd state                         | 5 |

|   | 6.4   | ECO-mode state                                   | 5 |

|   | 6.5   | MUTE-PLAY and diagnostic states                  | 6 |

|   | 6.6   | Operation compatibility vs battery               | 7 |

| 7 | Muti  | ng function architecture                         | 8 |

|   | 7.1   | Command dependence                               | 8 |

|   | 7.2   | Analog-Mute                                      | 9 |

|   | 7.3   | Digital-Mute                                     | 9 |

|   | 7.4   | Mixed mute advantages                            | 0 |

| 8 | Hard  | dware mute pin                                   | 2 |

| 9 | Pow   | er limiter function                              | 3 |

|   | 9.1   | Power limiter control                            | 4 |

| Diagr               | nostic                                                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.1                | DC diagnostic                                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.1.1 Diagnostic control                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.1.2 Relation with short circuit protection activation                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.1.3 Load range                                                                      | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.2                | Short to Vcc / GND diagnostic                                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.3                | Diagnostic time-line diagrams                                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.4                | Open load in play detector                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.4.1 Open load in play detector operation overview                                   | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.4.2 Processing bandwidth range                                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.4.3 Audio signal evaluation                                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.4.4 Impedance threshold                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | 10.4.5 I <sup>2</sup> C control and timing                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.5                | Input offset detector                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.6                | Output voltage offset detector4                                                        | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.7                | Output current offset detector                                                         | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.7.1 Output current offset detector operation principle                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.7.2 Result communication and I <sup>2</sup> C control                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | 10.7.3 Hot spot detection                                                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.8                | PWM pulse skipping detector                                                            | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.9                | Thermal protection                                                                     | <b>l</b> 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.10               | Watch-dog4                                                                             | <b>‡</b> 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.11               | Error frame check                                                                      | <b>ļ</b> 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Addit               | ional features                                                                         | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11.1                | AM operation mode4                                                                     | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11.2                | Noise gating 4                                                                         | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11.3                | Dither PWM                                                                             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11.4                | Real time load current monitoring5                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 11.4.1 Result communication and I <sup>2</sup> C control                               | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 11.4.2 Current sensing limitations                                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| l <sup>2</sup> S bu | us interface5                                                                          | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

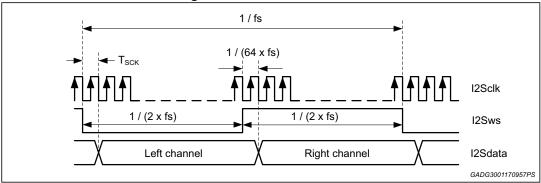

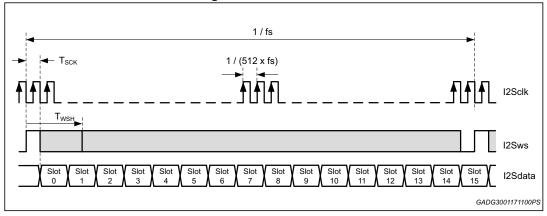

| 12.1                | I <sup>2</sup> S standard mode description                                             | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

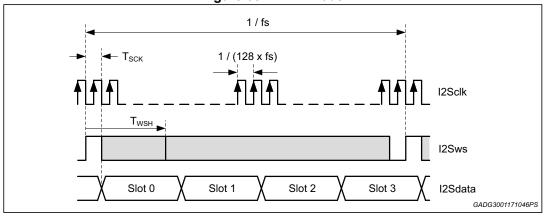

| 12.2                | TDM 4CH mode description                                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 10.1  10.2 10.3 10.4  10.5 10.6 10.7  10.8 10.9 10.10 10.11  Addit 11.1 11.2 11.3 11.4 | 10.1.1       Diagnostic control         10.1.2       Relation with short circuit protection activation         10.1.3       Load range         10.2       Short to Vec / GND diagnostic         10.3       Diagnostic time-line diagrams         10.4       Open load in play detector         10.4.1       Open load in play detector operation overview         10.4.2       Processing bandwidth range         10.4.3       Audio signal evaluation         10.4.4       Impedance threshold         10.4.5       I <sup>2</sup> C control and timing         10.5       Input offset detector         10.6       Output voltage offset detector         10.7       Output current offset detector operation principle         10.7.1       Output current offset detector operation principle         10.7.2       Result communication and I <sup>2</sup> C control         10.7.3       Hot spot detection         10.8       PWM pulse skipping detector         10.9       Thermal protection         10.10       Watch-dog         10.11       Error frame check         Additional features       4         11.1       AM operation mode         11.2       Noise gating         11.4.1       Result communication and I <sup>2</sup> |

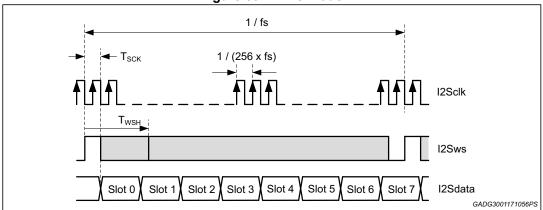

|    | 12.3                | TDM 8CH mode description                                   | . 54 |

|----|---------------------|------------------------------------------------------------|------|

|    | 12.4                | TDM 16CH mode description                                  | . 55 |

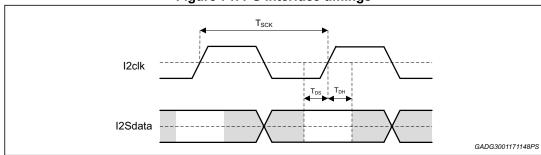

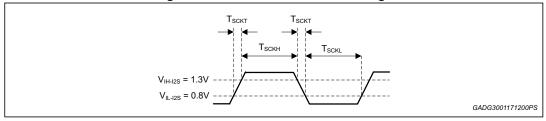

|    | 12.5                | Timing requirements                                        | . 56 |

|    | 12.6                | Group delay                                                | . 57 |

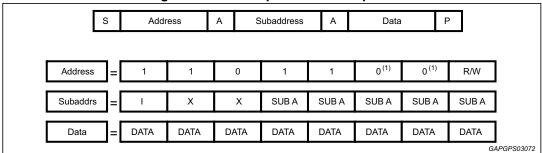

| 13 | I <sup>2</sup> C b  | us interface                                               | . 58 |

|    | 13.1                | Writing procedure                                          | . 59 |

|    | 13.2                | Reading procedure                                          | . 59 |

|    | 13.3                | Data validity                                              | . 60 |

|    | 13.4                | Start and stop conditions                                  | . 60 |

|    | 13.5                | Byte format                                                | . 60 |

|    | 13.6                | Acknowledge                                                | . 60 |

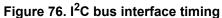

|    | 13.7                | I <sup>2</sup> C timing                                    | . 61 |

|    | 13.8                | I <sup>2</sup> S, I <sup>2</sup> C and Enable relationship | . 62 |

| 14 | I <sup>2</sup> C re | egister                                                    | . 63 |

|    | 14.1                | Instruction bytes- "I00xxxxx"                              | . 63 |

|    | 14.2                | Data bytes - "I01xxxxx"                                    | . 72 |

| 15 | Pack                | age information                                            | . 76 |

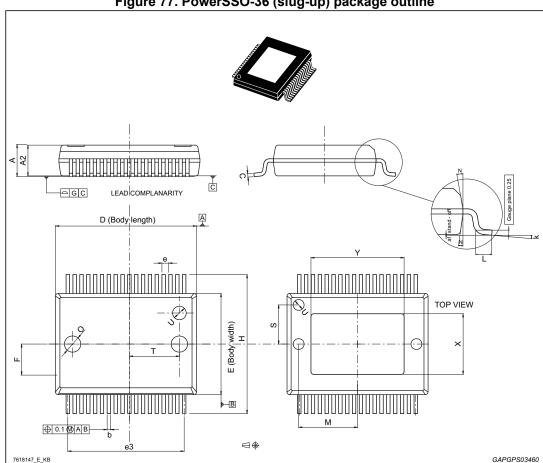

|    | 15.1                | PowerSSO-36 (slug-up) package information                  | . 76 |

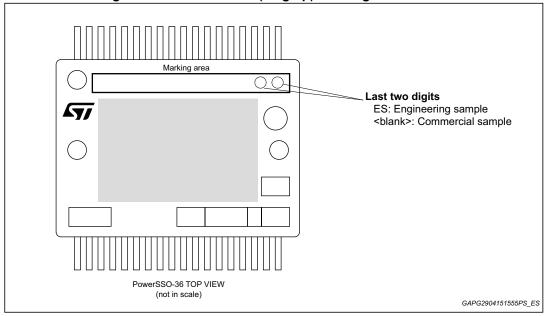

|    | 15.2                | PowerSSO-36 (slug up) marking information                  | . 78 |

| 16 | Revis               | sion history                                               | . 79 |

|    |                     |                                                            |      |

FDA903U List of tables

# List of tables

| Table 1.  | Device summary                                               | . 1 |

|-----------|--------------------------------------------------------------|-----|

| Table 2.  | Pins list function                                           |     |

| Table 3.  | Absolute maximum ratings                                     | 12  |

| Table 4.  | Thermal data                                                 | 12  |

| Table 5.  | Electrical characteristics                                   | 12  |

| Table 6.  | Operation mode                                               | 24  |

| Table 7.  | Command dependence                                           | 28  |

| Table 8.  | Power limiter function                                       |     |

| Table 9.  | Open load in play detector impedance and validity thresholds | 41  |

| Table 10. | I <sup>2</sup> S Interface timings                           |     |

| Table 11. | Group delay dependency from input sampling frequency         |     |

| Table 12. | I <sup>2</sup> C bus interface timing                        |     |

| Table 13. | IB0-ADDR: "I0000000"                                         | 63  |

| Table 14. | IB1-ADDR: "I0000001"                                         |     |

| Table 15. | IB2-ADDR: "I0000010"                                         |     |

| Table 16. | IB3-ADDR: "I0000011"                                         |     |

| Table 17. | IB4-ADDR: "I0000100" - CDDiag pin configuration              |     |

| Table 18. | IB5-ADDR: "I0000101" - CDDiag pin configuration              |     |

| Table 19. | IB6-ADDR: "I0000110"                                         |     |

| Table 20. | IB7-ADDR: "I0000111"                                         |     |

| Table 21. | IB8-ADDR: "I0001000" - CHANNEL CONTROLS                      | 69  |

| Table 22. | IB9-ADDR: "I0001001"                                         | 69  |

| Table 23. | IB10-ADDR: "I0001010"                                        | 70  |

| Table 24. | IB11-ADDR: "I0001011"                                        |     |

| Table 25. | IB12-ADDR: "I0001100"                                        |     |

| Table 26. | IB13-ADDR: "I0001101"                                        |     |

| Table 27. | IB14-ADDR: "I0001110"                                        |     |

| Table 28. | DB0-ADDR: "I0100000"                                         |     |

| Table 29. | DB1-ADDR: "I0100001"                                         |     |

| Table 30. | DB2-ADDR:"I0100010"                                          |     |

| Table 31. | DB3-ADDR: "I0100011" DC Diagnostic Error code                |     |

| Table 32. | DB4-ADDR:"I0100100" - Current Sensing data (10-8)            |     |

| Table 33. | DB5-ADDR:"I0100101" - Current Sensing data (7-0)             |     |

| Table 34. | DB6-ADDR:"I0100110"                                          |     |

| Table 35. | PowerSSO-36 (slug-up) package mechanical data                | 77  |

| Table 36. | Document revision history.                                   | 79  |

5/80

List of figures FDA903U

# List of figures

| Figure 1.  | Block diagram                                                                                                               | 8  |

|------------|-----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Pins connection diagram                                                                                                     |    |

| Figure 3.  | Application diagram                                                                                                         |    |

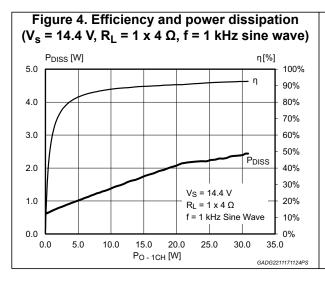

| Figure 4.  | Efficiency and power dissipation ( $V_s = 14.4 \text{ V}$ , $R_L = 1 \text{ x } 4 \Omega$ , $f = 1 \text{ kHz sine wave}$ ) | 15 |

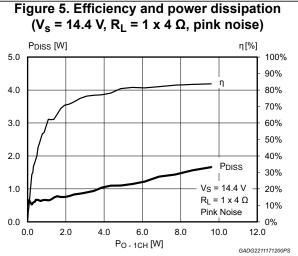

| Figure 5.  | Efficiency and power dissipation ( $V_s = 14.4 \text{ V}$ , $R_l = 1 \text{ x } 4 \Omega$ , pink noise)                     |    |

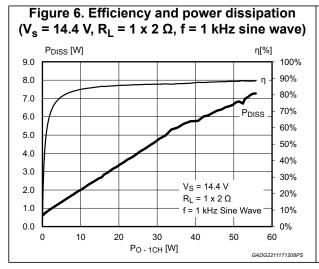

| Figure 6.  | Efficiency and power dissipation ( $V_s = 14.4 \text{ V}$ , $R_L = 1 \text{ x } 2 \Omega$ , $f = 1 \text{ kHz sine wave}$ ) |    |

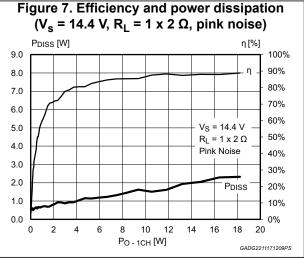

| Figure 7.  | Efficiency and power dissipation ( $V_s = 14.4 \text{ V}$ , $R_l = 1 \text{ x } 2 \Omega$ , pink noise)                     |    |

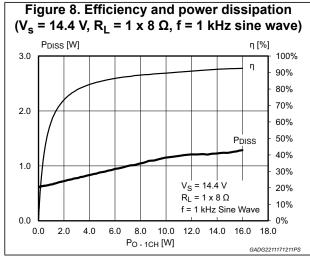

| Figure 8.  | Efficiency and power dissipation ( $V_s = 14.4 \text{ V}$ , $R_L = 1 \times 8 \Omega$ , $f = 1 \text{ kHz sine wave}$ )     |    |

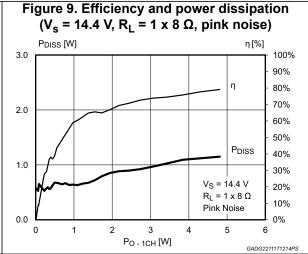

| Figure 9.  | Efficiency and power dissipation ( $V_s = 14.4 \text{ V}$ , $R_l = 1 \times 8 \Omega$ , pink noise)                         |    |

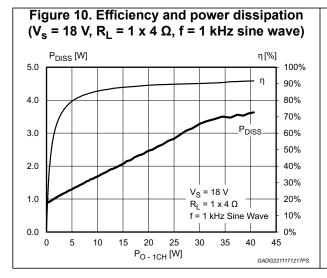

| Figure 10. | Efficiency and power dissipation ( $V_s = 18 \text{ V}$ , $R_L = 1 \text{ x } 4 \Omega$ , $f = 1 \text{ kHz sine wave}$ )   |    |

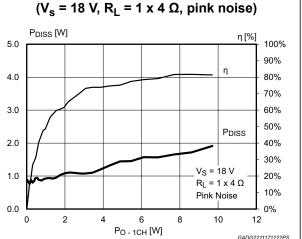

| Figure 11. | Efficiency and power dissipation ( $V_s = 18 \text{ V}$ , $R_L = 1 \text{ x } 4 \Omega$ , pink noise)                       |    |

| Figure 12. | Efficiency and power dissipation ( $V_s = 16 \text{ V}$ , $R_L = 1 \text{ x } 2 \Omega$ , $f = 1 \text{ kHz sine wave}$ )   |    |

| Figure 13. | Efficiency and power dissipation ( $V_s = 16 \text{ V}$ , $R_L = 1 \text{ x } 2 \Omega$ , pink noise)                       |    |

| Figure 14. | Efficiency and power dissipation ( $V_s = 18 \text{ V}$ , $R_L = 1 \text{ x } 8 \Omega$ , $f = 1 \text{ kHz sine wave}$ )   |    |

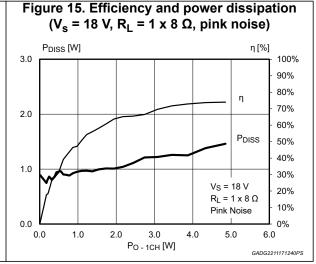

| Figure 15. | Efficiency and power dissipation ( $V_s = 18 \text{ V}$ , $R_L = 1 \times 8 \Omega$ , pink noise)                           |    |

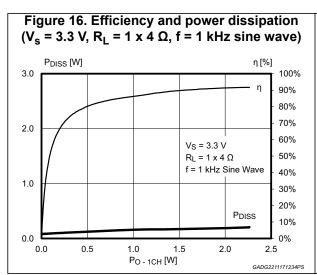

| Figure 16. | Efficiency and power dissipation ( $V_s = 3.3 \text{ V}$ , $R_L = 1 \times 4 \Omega$ , $f = 1 \text{ kHz}$ sine wave)       |    |

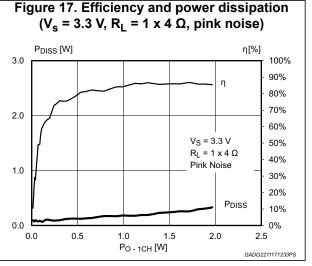

| Figure 17. | Efficiency and power dissipation ( $V_s = 3.3 \text{ V}$ , $R_L = 1 \text{ x 4 } \Omega$ , pink noise)                      |    |

| Figure 18. | Efficiency and power dissipation ( $V_s = 3.3 \text{ V}$ , $R_L = 1 \times 2 \Omega$ , $f = 1 \text{ kHz sine wave}$ )      |    |

| Figure 19. | Efficiency and power dissipation ( $V_s = 3.3 \text{ V}$ , $R_L = 1 \text{ x } 2 \Omega$ , pink noise)                      |    |

| Figure 20. | Efficiency and power dissipation ( $V_s = 3.3 \text{ V}$ , $R_L = 1 \times 8 \Omega$ , $f = 1 \text{ kHz sine wave}$ )      |    |

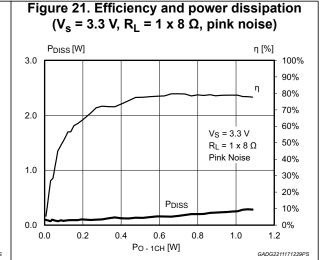

| Figure 21. | Efficiency and power dissipation ( $V_s = 3.3 \text{ V}$ , $R_l = 1 \times 8 \Omega$ , pink noise)                          |    |

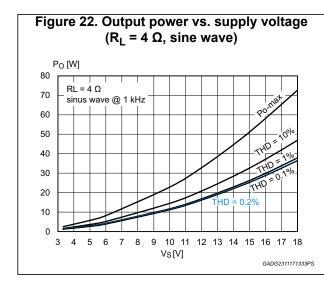

| Figure 22. | Output power vs. supply voltage ( $R_{I} = 4 \Omega$ , sine wave)                                                           |    |

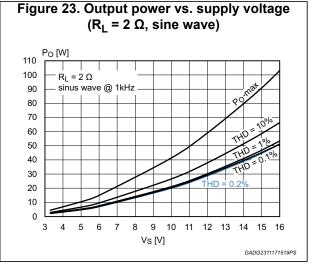

| Figure 23. | Output power vs. supply voltage ( $R_{I} = 2 \Omega$ , sine wave)                                                           |    |

| Figure 24. | Output power vs. supply voltage ( $R_{\rm I} = 8 \Omega$ , sine wave)                                                       |    |

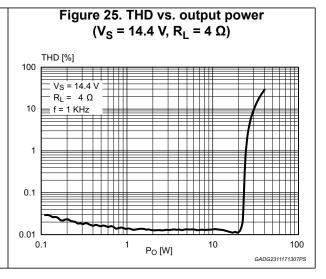

| Figure 25. | THD vs. output power ( $V_S = 14.4 \text{ V}$ , $R_L = 4 \Omega$ )                                                          |    |

| Figure 26. | THD vs. output power ( $V_S = 14.4 \text{ V}, R_I = 2 \Omega$ )                                                             |    |

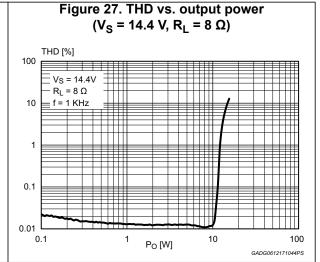

| Figure 27. | THD vs. output power ( $V_S = 14.4 \text{ V}, R_I = 8 \Omega$ )                                                             | 19 |

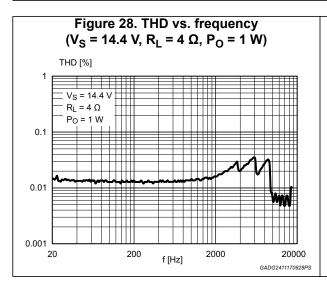

| Figure 28. | THD vs. frequency ( $V_S = 14.4 \text{ V}$ , $R_L = 4 \Omega$ , $P_O = 1 \text{ W}$ )                                       | 19 |

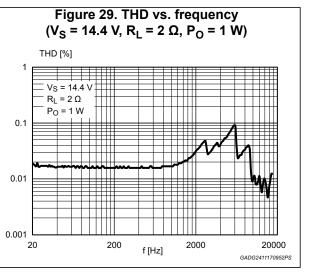

| Figure 29. | THD vs. frequency ( $V_S = 14.4 \text{ V}$ , $R_L = 2 \Omega$ , $P_O = 1 \text{ W}$ )                                       |    |

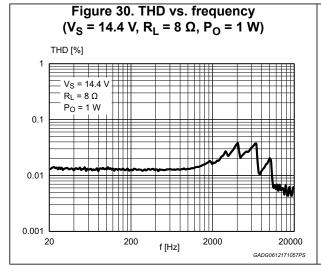

| Figure 30. | THD vs. frequency ( $V_S = 14.4 \text{ V}$ , $R_L = 8 \Omega$ , $P_O = 1 \text{ W}$ )                                       | 20 |

| Figure 31. | Frequency response (1 W, $R_L = 4 \Omega$ , $f = 1 \text{ kHz}$ )                                                           |    |

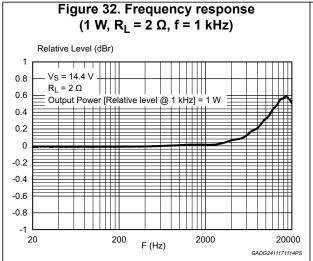

| Figure 32. | Frequency response (1 W, $R_L = 2 \Omega$ , f = 1 kHz)                                                                      | 20 |

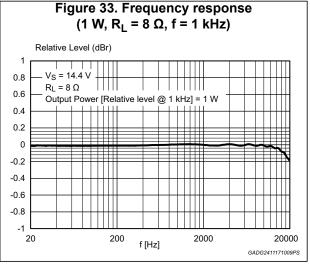

| Figure 33. | Frequency response (1 W, $R_L = 8 \Omega$ , f = 1 kHz)                                                                      | 20 |

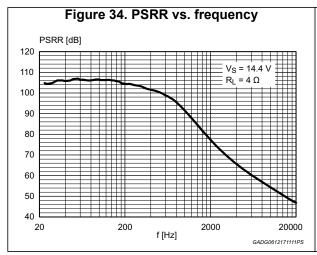

| Figure 34. | PSRR vs. frequency                                                                                                          |    |

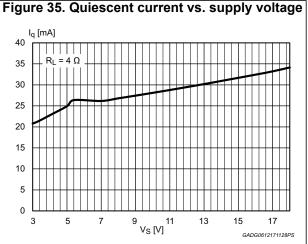

| Figure 35. | Quiescent current vs. supply voltage                                                                                        |    |

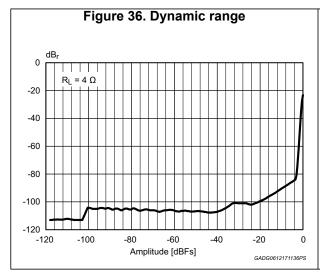

| Figure 36. | Dynamic range                                                                                                               | 21 |

| Figure 37. | FFT - Output spectrum (-60 dBFS input signal)                                                                               |    |

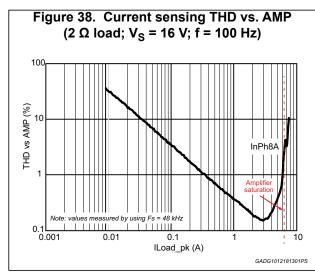

| Figure 38. | Current sensing THD vs. AMP (2 $\Omega$ load; V <sub>S</sub> = 16 V; f = 100 Hz)                                            | 21 |

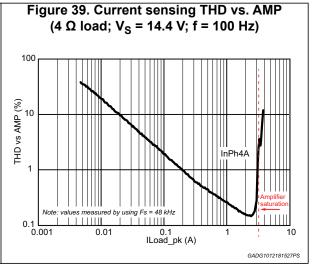

| Figure 39. | Current sensing THD vs. AMP (4 $\Omega$ load; $V_S$ = 14.4 V; f = 100 Hz)                                                   | 21 |

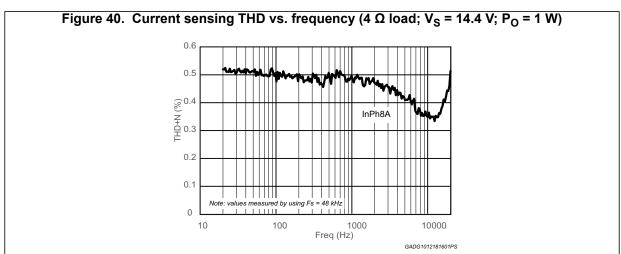

| Figure 40. | Current sensing THD vs. frequency (4 $\Omega$ load; $V_S$ = 14.4 V; $P_O$ = 1 W)                                            | 21 |

| Figure 41. | Finite state machine diagram                                                                                                | 23 |

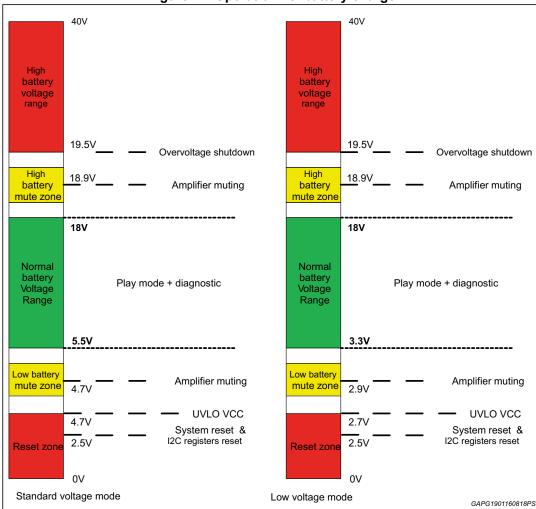

| Figure 42. | Operation vs. battery charge                                                                                                | 27 |

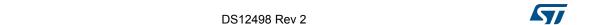

| Figure 43. | Analog-Mute diagram                                                                                                         | 29 |

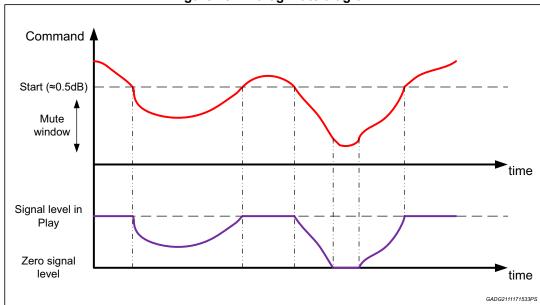

| Figure 44. | Digital-Mute diagram                                                                                                        | 30 |

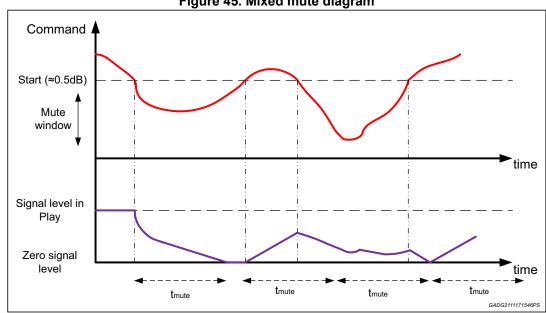

| Figure 45. | Mixed mute diagram                                                                                                          |    |

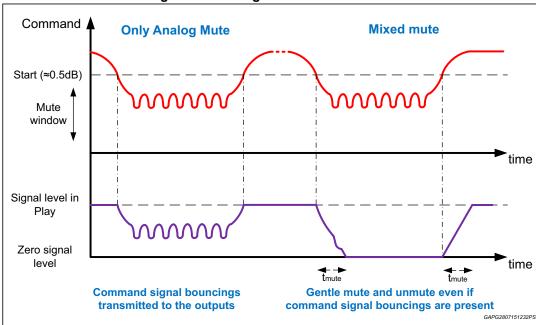

| Figure 46. | Analog-Mute vs. Mixed-Mute                                                                                                  | 31 |

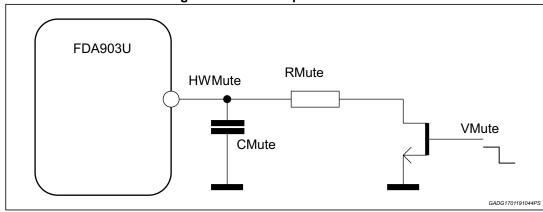

| Figure 47. | HWMute pin schematic                                                                                                        |    |

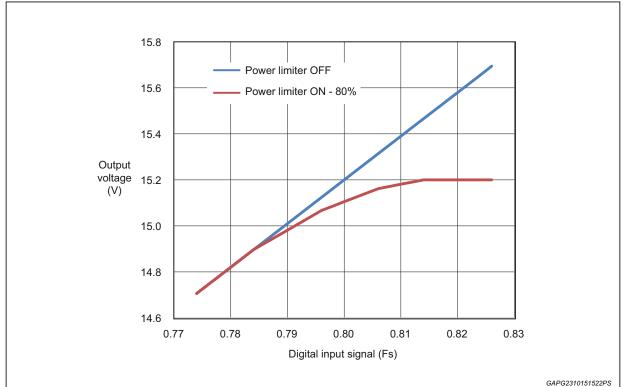

| Figure 48  | Response obtained with a limitation corresponding to 80% of the full-scale                                                  | 34 |

FDA903U List of figures

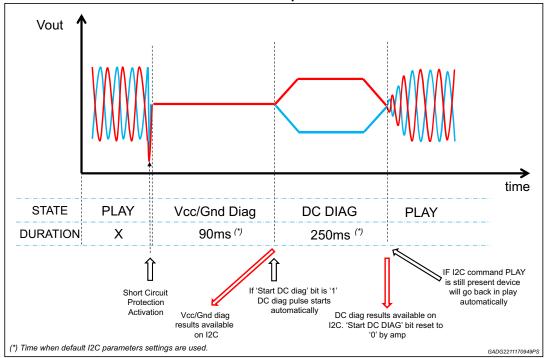

| Figure 49. | Load range detection configured properly setting IB5 d7-d6                                   | 36 |

|------------|----------------------------------------------------------------------------------------------|----|

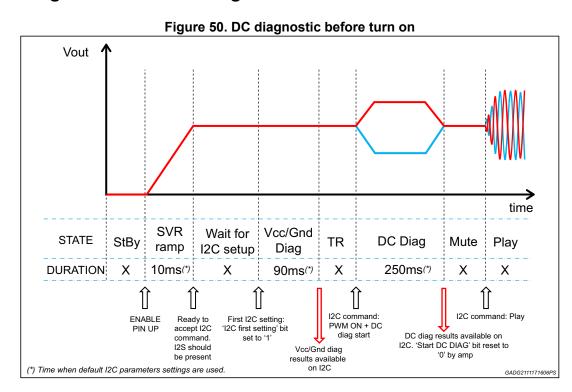

| Figure 50. | DC diagnostic before turn on                                                                 | 37 |

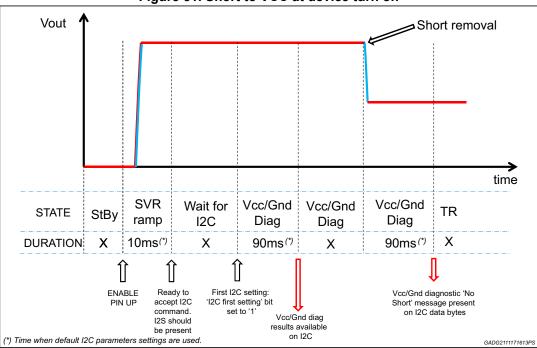

| Figure 51. | Short to VCC at device turn on                                                               | 38 |

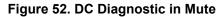

| Figure 52. | DC Diagnostic in Mute                                                                        | 38 |

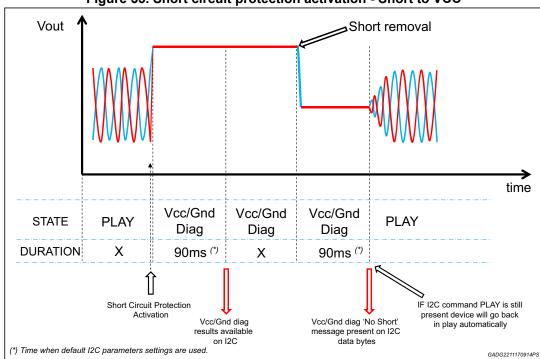

| Figure 53. | Short circuit protection activation - Short to VCC                                           | 39 |

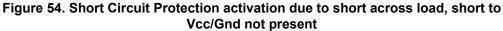

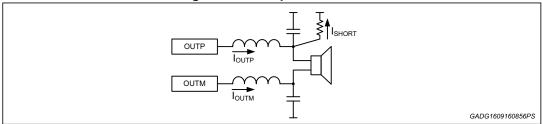

| Figure 54. | Short Circuit Protection activation due to short across load, short to Vcc/Gnd not present 3 | 39 |

| Figure 55. | Open load in play detector guaranteed thresholds with standard gain setting                  | 41 |

| Figure 56. | Open load in play detector guaranteed thresholds with low gain setting                       | 41 |

| Figure 57. | Open load in play detector timing                                                            | 42 |

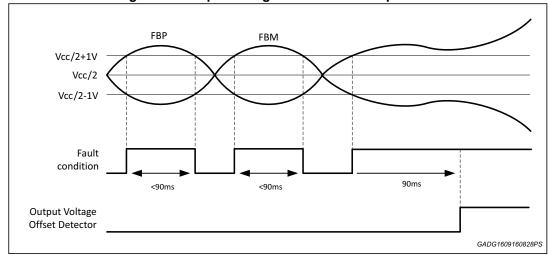

| Figure 58. | Output voltage offset detector operation                                                     | 43 |

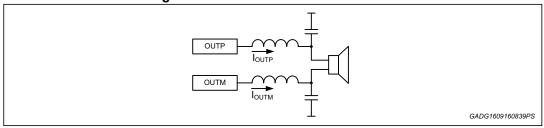

| Figure 59. | Current offset measurement                                                                   | 44 |

| Figure 60. | Hot spot detection                                                                           | 45 |

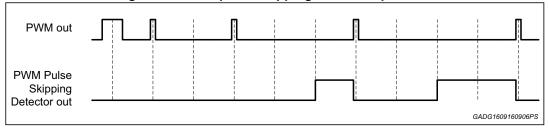

| Figure 61. | PWM pulse skipping detector operation                                                        | 45 |

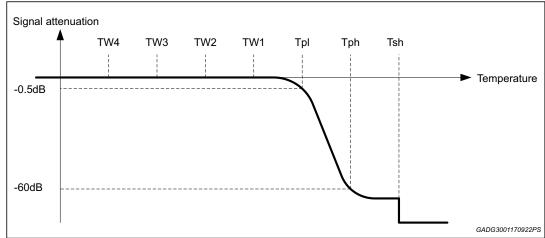

| Figure 62. | Thermal attenuation curve                                                                    | 46 |

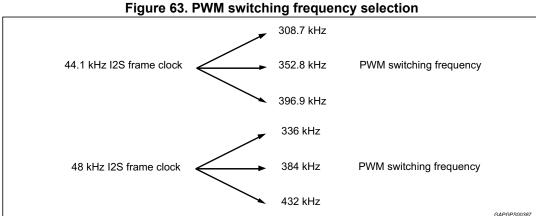

| Figure 63. | PWM switching frequency selection                                                            | 48 |

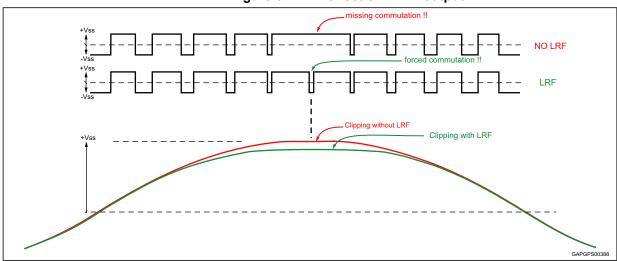

| Figure 64. | LRF effect on PWM output                                                                     | 48 |

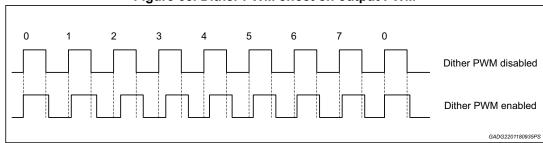

| Figure 65. | Dither PWM effect on output PWM                                                              | 49 |

| Figure 66. | Current sensing path                                                                         | 50 |

| Figure 67. | I <sup>2</sup> S standard mode                                                               | 53 |

| Figure 68. | TDM4 mode                                                                                    | 53 |

| Figure 69. | TDM8 mode                                                                                    | 54 |

| Figure 70. | TDM16 mode                                                                                   | 55 |

| Figure 71. | I <sup>2</sup> S Interface timings                                                           | 56 |

| Figure 72. | I <sup>2</sup> S clock transition timings                                                    | 56 |

| Figure 73. | I <sup>2</sup> C bus protocol description                                                    | 58 |

| Figure 74. | Reading procedure                                                                            |    |

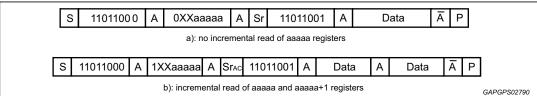

| Figure 75. | Without/with auto-increment reading procedure                                                | 30 |

| Figure 76. | I <sup>2</sup> C bus interface timing                                                        |    |

| Figure 77. | PowerSSO-36 (slug-up) package outline                                                        | 76 |

| Figure 78. | PowerSSO-36 (slug up) marking information                                                    | 78 |

DS12498 Rev 2 7/80

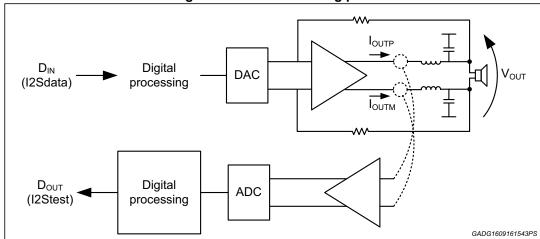

Block diagram FDA903U

# 1 Block diagram

D1V8SVR Enable 1 Enable 2 Enable 3 Enable 4 A5VSVR AVdd 12Cdata VCCP VCCM PLL I2C interface I2Sclk 23 Interpolator PWM 32/33 OUTP 4/5 OUTM Current I2S Transresistence Power Amplifier Scrambler Generator interface Noise Array Shaper 6 FBM 30 HWMute 15 CDDiag 14 NC 36 GNDP 2 GNDM 29 SVR GAPG1105160712PS

Figure 1. Block diagram

FDA903U Pins description

# 2 Pins description

36 GNDP | TAB 35 2 GNDM VCCP 34 3 VCCM NC [ OUTP [ 33 4 OUTM OUTP [ 32 5 OUTM FBP [ 31 FBM 7 HWMute [ 30 NC SVR [ 29 8 DGnd Slug - up 9 28 DVdd AGSVR [ A5VSVR 27 10 Enable1 11 Enable2 AVdd [ 26 AGnd | 25 12 Enable3 I2Sws 24 13 Enable4 I2Sclk [ 23 14 NC 22 15 I2Sdata CDDiag I2Stest [ 21 16 NC I2Cclk 20 17 D1V8SVR I2Cdata 19 18 DGSVR GADG1403180903PS

Figure 2. Pins connection diagram

**Table 2. Pins list function**

| Pin # | Pin name | Function                                    |

|-------|----------|---------------------------------------------|

| 1     | TAB      | Device slug connection                      |

| 2     | GNDM     | Channel half bridge minus, Power Ground     |

| 3     | VCCM     | Channel half bridge minus, Power Supply     |

| 4     | OUTM     | Channel half bridge minus, Output           |

| 5     | OUTM     | Channel half bridge minus, Output           |

| 6     | FBM      | Channel half bridge minus, Feedback         |

| 7     | NC       | Not connected                               |

| 8     | DGnd     | Digital ground                              |

| 9     | DVdd     | Digital supply                              |

| 10    | Enable1  | Enable 1                                    |

| 11    | Enable2  | Enable 2                                    |

| 12    | Enable3  | Enable 3                                    |

| 13    | Enable4  | Enable 4                                    |

| 14    | NC       | Not connected                               |

| 15    | CDDiag   | Clipping detector and diagnostic output pin |

Pins description FDA903U

Table 2. Pins list function (continued)

| Pin # | Pin name | Function                                                   |  |

|-------|----------|------------------------------------------------------------|--|

| 16    | NC       | Not connected                                              |  |

| 17    | D1V8SVR  | ositive digital supply V(SVR)+0.9V (Internally generated)  |  |

| 18    | DGSVR    | Negative digital supply V(SVR)-0.9V (Internally generated) |  |

| 19    | I2Cdata  | I2C Data                                                   |  |

| 20    | I2Cclk   | I2C Clock                                                  |  |

| 21    | I2Stest  | test pin, left open                                        |  |

| 22    | I2Sdata  | I2S/TDM data                                               |  |

| 23    | I2Sclk   | I2S/TDM Clock input                                        |  |

| 24    | I2Sws    | 2S/TDM Sync input /Word Select input                       |  |

| 25    | AGnd     | Analog ground                                              |  |

| 26    | AVdd     | Analog supply                                              |  |

| 27    | A5VSVR   | Positive Analog Supply V(SVR)+2.5V (Internally generated)  |  |

| 28    | AGSVR    | Negative Analog Supply V(SVR)-2.5V (Internally generated)  |  |

| 29    | SVR      | Supply Voltage Ripple Rejection Capacitor                  |  |

| 30    | HWMute   | Hardware mute pin                                          |  |

| 31    | FBP      | Channel half bridge plus, Feedback                         |  |

| 32    | OUTP     | Channel half bridge plus, Output                           |  |

| 33    | OUTP     | Channel half bridge plus, Output                           |  |

| 34    | NC       | Not connected                                              |  |

| 35    | VCCP     | Channel half bridge plus, Power Supply                     |  |

| 36    | GNDP     | Channel half bridge plus, Power Ground                     |  |

# 3 Application diagram

<u>36</u> ⊳ GNDP I2SWS 31 I2SCLK FBP L1 10uH 33 I2SDATA OUTP 32 I2STEST OUTP VCCP 35 VCC I2CCLK VCCM 3 VCC I2CDATA OUTM C19 + C15 JuFT ENABLE 1 OUTM 1000uF L2 10uH ENABLE 2 FBM GNDM ENABLE 3 ENABLE 4 FDA903U HWMUTE D1V8SVR DGSVR CD/DIAG 15 CDDIAG SVR AGSVR C11 C10 DVDD OOO A5VSVR 현원니 88 GADG1403181504P3

Figure 3. Application diagram

# 4 Electrical specifications

### 4.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Table 6. Abbotate maximum ratings                                                                                                   |                                                        |                    |      |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|--|--|--|

| Symbol                                                                                                                              | Parameter                                              | Value              | Unit |  |  |  |

| V IV V A D I                                                                                                                        | DC supply voltage                                      | -0.3 to 28         | V    |  |  |  |

| V <sub>CC</sub> [V <sub>CCP</sub> ,V <sub>CCM</sub> , A <sub>VDD</sub> , D <sub>VDD</sub> ]                                         | Transient supply voltage for t = 100 ms <sup>(1)</sup> | -0.3 to 40         | V    |  |  |  |

| GND <sub>max</sub> [D <sub>GND</sub> , A <sub>GND</sub> , GNDP, GNDM]                                                               | Ground pin voltage difference                          | -0.3 to 0.3        | V    |  |  |  |

| I <sup>2</sup> C <sub>data,</sub> I <sup>2</sup> C <sub>clk</sub>                                                                   | I <sup>2</sup> C bus pins voltage                      | -0.3 to 5.5        | V    |  |  |  |

| I <sup>2</sup> S <sub>test,</sub> I <sup>2</sup> S <sub>data,</sub> I <sup>2</sup> S <sub>clk,</sub> I <sup>2</sup> S <sub>ws</sub> | I <sup>2</sup> S bus pins voltage                      | -0.3 to 5.5        | V    |  |  |  |

| Enable <sub>1,2,3,4</sub>                                                                                                           | Enables                                                | -0.3 to 5.5        | V    |  |  |  |

| HWMute                                                                                                                              | Hardware mute                                          | -0.3 to 7          | V    |  |  |  |

| CDDiag                                                                                                                              | Clip detection                                         | -0.3 to 5.5        | V    |  |  |  |

| I <sub>o</sub>                                                                                                                      | Output current (repetitive f > 10 Hz)                  | Internally limited | Α    |  |  |  |

| T <sub>amb</sub>                                                                                                                    | Ambient operating temperature                          | -40 to 125         | °C   |  |  |  |

| T <sub>stg</sub> , T <sub>j</sub>                                                                                                   | Storage and junction temperature                       | -55 to 150         | °C   |  |  |  |

| ESDHBM                                                                                                                              | ESD protection HBM                                     | 2000               | V    |  |  |  |

| ESDCDM                                                                                                                              | ESD protection CDM                                     | 500                | V    |  |  |  |

<sup>1.</sup>  $V_{CC}$  = 35 V for t < 400 ms as per ISO16750-2 load dump with centralized load dump suppression.

#### 4.2 Thermal data

Table 4. Thermal data

| Symbol                 | Symbol Parameter                                           |  | Max | Unit |

|------------------------|------------------------------------------------------------|--|-----|------|

| R <sub>th j-case</sub> | R <sub>th j-case</sub> Thermal resistance junction-to-case |  | 5.5 | °C/W |

#### 4.3 Electrical characteristics

$V_{cc}$  = 14.4 V;  $R_L$  = 4  $\Omega$ ; f = 1 kHz;  $T_{amb}$  = 25 °C;  $I^2C$  defaults, unless otherwise specified. LC filter: L = 10  $\mu$ H, C = 3.3  $\mu$ F. PWM in In-phase modulation, feedback connected after the filter.

**Table 5. Electrical characteristics**

| Symbol          | Parameter            | Test condition                        |     | Тур | Max | Unit |

|-----------------|----------------------|---------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> | Supply voltage range | $R_L = 4 \Omega$                      | 3.3 | -   | 18  | V    |

|                 |                      | R <sub>L</sub> = 2 Ω                  | 3.3 | -   | 16  |      |

| lvcc            | Quiescent current    | Device in Standby                     | -   | 1   | 5   | μA   |

|                 |                      | Device on (MUTE state) <sup>(1)</sup> | -   | 35  | -   | mA   |

|                 |                      | ECO MODE                              | -   | 22  | -   | mA   |

12/80 DS12498 Rev 2

Table 5. Electrical characteristics (continued)

| Symbol              | Parameter                                        | 5. Electrical characteristics (continued<br>Test condition | Min  | Тур      | Max  | Unit |

|---------------------|--------------------------------------------------|------------------------------------------------------------|------|----------|------|------|

| V <sub>os</sub>     | Offset voltage                                   | Mute & Play                                                | -10  | -        | +10  | mV   |

| D <sub>VDD</sub>    | Digital supply voltage range                     | -                                                          | 3.3  | -        | 18   | V    |

| A <sub>VDD</sub>    | Analog supply voltage range                      | -                                                          | 3.3  | -        | 18   | V    |

|                     | Overcurrent protection <sup>(2)</sup>            | IB11 D5-4 = 00                                             | 9.5  | 11       | 12.5 | Α    |

|                     |                                                  | IB11 D5-4 = 01                                             | 6.7  | 8        | 9.3  | Α    |

| l <sub>op</sub>     |                                                  | IB11 D5-4 = 10                                             | 5    | 6        | 7    | Α    |