# HVLED001A

Datasheet - production data

## Offline controller for LED lighting with constant voltage primarysensing and high power factor

## **Features**

- Quasi resonant (QR) topology

- Optimized output voltage accuracy at any load (PSR mode)

- Improved transient response and startup time

- Direct optocoupler connection for current loop regulation with feedback disconnection detection

- 800 V high voltage startup

- High power factor and low THD over wide range of input voltage and load variations

- High efficiency and output stability over wide voltage and current range

- Low startup and quiescent current

- Programmable minimum off-time

- Integrated input voltage detection for high power factor capability and protection triggering

- Latch-free device guaranteed by smart autoreload timer (ART)

- 0-10 and PWM dimming compatible

- Remote control pin

## Applications

- Single stage LED drivers with high power factor up to 75 W

- Two stages LED drivers up to 150 W

### Description

The HVLED001A is an enhanced peak current mode controller capable of controlling high power factor (HPF) flyback or buck-boost topologies in LED drivers that have an output power of up to 150 W. Other topologies, such as buck, boost and SEPIC, can also be implemented.

ST's innovative high voltage technology allows direct connection of the HVLED001A device to the input voltage to start up the device and to monitor the input voltage, without the need for external components.

The device embeds advanced features to control either the output voltage or the output current precisely and reliably using a reduced number of mainly passive components. Startup and light load conditions are managed by dedicated operating schemes to improve the quality of the regulation of the output variable in the final application. Abnormal conditions such as open circuit, output short-circuit, input overvoltage/ undervoltage and circuit failures like open loop and overcurrent of the main switch are effectively controlled.

A smart auto-recover timer (ART) function is builtin to guarantee automatic application recovery, without loss of reliability.

| Table | 1. | Device | summary |

|-------|----|--------|---------|

|-------|----|--------|---------|

| Order code  | Package | Packaging     |  |  |

|-------------|---------|---------------|--|--|

| HVLED001A   | SSO10   | Tube          |  |  |

| HVLED001ATR | 33010   | Tape and reel |  |  |

September 2017

DocID029000 Rev 3

This is information on a product in full production.

1/30

# Contents

| 1 | Bloc | k diagra  | am                              |

|---|------|-----------|---------------------------------|

| 2 | Турі | cal appl  | ication - HPF flyback 5         |

| 3 | Pins | settings  |                                 |

| 4 | Elec | trical da | ata                             |

|   | 4.1  | Absolu    | te maximum ratings              |

|   | 4.2  | Therm     | al data                         |

| 5 | Elec | trical ch | naracteristics                  |

| 6 | Турі | cal elec  | trical characteristic 14        |

| 7 | App  | lication  | information                     |

|   | 7.1  | Operat    | ting modes                      |

|   |      | 7.1.1     | Startup mode                    |

|   |      | 7.1.2     | Active mode                     |

|   |      | 7.1.3     | Stop mode                       |

|   |      | 7.1.4     | Low consumption mode            |

|   |      | 7.1.5     | Soft-start                      |

|   | 7.2  | Contro    | l loop                          |

|   |      | 7.2.1     | Current sense input             |

|   |      | 7.2.2     | Feedback input                  |

|   |      | 7.2.3     | Zero current detection          |

|   |      | 7.2.4     | Primary side regulation feature |

|   |      | 7.2.5     | Burst mode operation            |

|   |      | 7.2.6     | Gate driver                     |

|   | 7.3  | IC sup    | ply management                  |

|   |      | 7.3.1     | VCC supply management23         |

|   |      | 7.3.2     | High voltage startup            |

|   | 7.4  | Auto-re   | estart timer (ART)              |

|   | 7.5   | Protecti | ons                                  | 25 |

|---|-------|----------|--------------------------------------|----|

|   |       | 7.5.1    | Overcurrent protection (OCP)         | 25 |

|   |       | 7.5.2    | Input overvoltage protection (I-OVP) | 25 |

|   |       | 7.5.3    | Brownout protection (BO)             | 25 |

|   |       | 7.5.4    | Optocoupler failure protection (OFP) | 25 |

|   |       | 7.5.5    | Output overvoltage protection (oOVP) | 25 |

|   | 7.6   | Disable  | and monitor feature                  | 26 |

| 8 | Packa | age info | rmation                              | 27 |

|   | 8.1   | SSO10    | package information                  | 27 |

| 9 | Revis | ion hist | ory                                  | 29 |

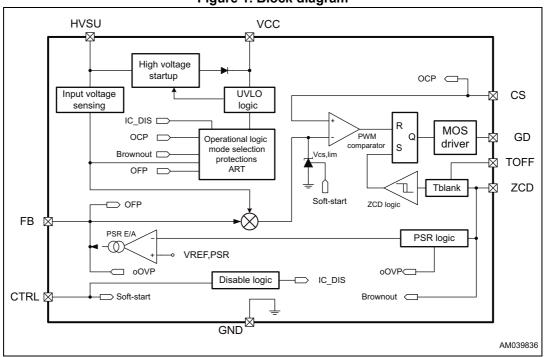

# 1 Block diagram

Figure 1. Block diagram

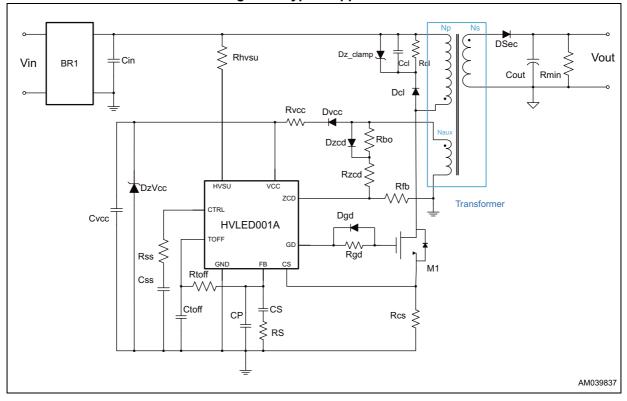

# 2 Typical application - HPF flyback

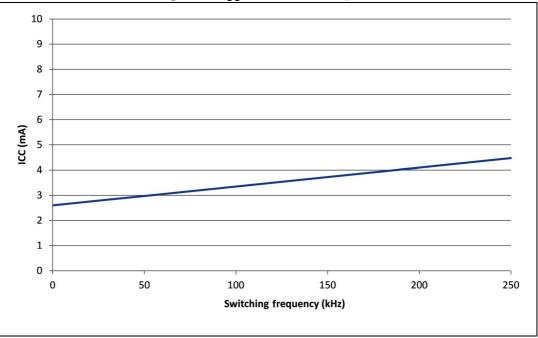

Figure 2. Typical application

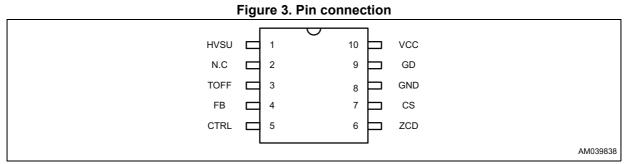

# 3 Pin settings

#### Table 2. Pin description

| Symbol | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HVSU   | 1   | High voltage startup and input voltage detection.<br>The pin, able to withstand 800 V, is intended to be tied to the input voltage using a low value resistor (1 k $\Omega$ typ.). It embeds the internal startup unit that charges the capacitor connected between the V <sub>CC</sub> pin and GND pin during the startup and low consumption.<br>During the operational mode, the voltage at this pin is used to both - measure the input voltage and detect input overvoltages. |

| N.C.   | 2   | Not connected pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TOFF   | 3   | A blanking time for zero voltage detection can be set applying a voltage to this pin. A minimum blanking time is obtained leaving the pin unconnected.                                                                                                                                                                                                                                                                                                                             |

| FB     | 4   | Input for loop regulation.<br>The pin is intended to be directly driven by the phototransistor (emitter-grounded) of an optocoupler<br>and/or to be connected to the compensation network related to the output voltage primary side<br>regulation loop.<br>An upper threshold VOFP detects a failure of the optocoupler.<br>The burst mode is also related to the voltage applied to this pin.                                                                                    |

| CTRL   | 5   | This pin is used to disable the IC and generate the soft-start ramp.<br>External active circuitry can be used to turn-off the application.                                                                                                                                                                                                                                                                                                                                         |

| ZCD    | 6   | Multiple function pin able to detect the zero current instant, to sense the output voltage for the primary side regulation and the input voltage for brownout detection. A negative-going edge triggers the MOSFET's turn-on, while an internal starter unit is active to generate the triggering signal when not externally available (e.g.: startup).                                                                                                                            |

| CS     | 7   | Input to the current sense comparator for the power regulation. A second level overcurrent (OCP) threshold detects abnormal currents (e.g.: due to transformer's saturation) and, on this occurrence, activates the second level overcurrent protection procedure.                                                                                                                                                                                                                 |

| GND    | 8   | Reference pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Symbol | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GD     | 9   | Gate driver output. The output stage is able to drive the power MOSFET's and IGBT's gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VCC    | 10  | Supply voltage of the IC.<br>Internal UVLO logic prevents the operation at voltages that are insufficient for the efficient gate driving or signal processing. Both a bulk capacitor (typically around 10 $\mu$ F) and a high frequency filter capacitor (100 nF ceramic, mounted as close as possible to the device) are connected between this pin and GND. An internal clamp structure prevents accidental low energy spikes damaging the device. An external clamping device should be used to avoid the voltage applied to the VCC pin to overcome the AMR. |

### Table 2. Pin description (continued)

## 4 Electrical data

## 4.1 Absolute maximum ratings

| Symbol    | Pin  | Parameter                     | Test condition                                            | Min.  | Max.            | Unit |

|-----------|------|-------------------------------|-----------------------------------------------------------|-------|-----------------|------|

| VHVSU,bd  | HVSU | HVSU breakdown voltage        | IHVSU < 100 $\mu$ A, V <sub>CC</sub> = 15 V <sub>DC</sub> | 800   | -               | V    |

| VHVSU,neg | HVSU | HVSU negative voltage         | IHVSU source < 2 mA                                       | - 0.3 | -               | V    |

| VGD       | GD   | Maximum swing voltage         | -                                                         | - 0.3 | V <sub>CC</sub> | V    |

| VCS       | CS   | Current sense applied voltage | -                                                         | - 0.3 | 7               | V    |

| VZCD      | ZCD  | ZCD pin voltage               | -                                                         | -     | 7               | V    |

| VZGD      | 200  |                               | Negative, Isource < 1 mA                                  | - 0.3 | -               | V    |

| VFB       | FB   | FB voltage                    | -                                                         | - 0.3 | 3.6             | V    |

| VCTRL     | CTRL | CTRL voltage                  | Stop mode                                                 | - 0.3 | V <sub>CC</sub> | V    |

| ICTRL     | CTRL | CTRL injected current         | -                                                         | -     | 1               | mA   |

| VCC,MAX   | VCC  | IC supply voltage             | -                                                         | -     | 18              | V    |

| VTOFF     | TOFF | Maximum applied voltage       | -                                                         | - 0.3 | 7               | V    |

#### Table 3. Absolute maximum ratings

Note: Where not otherwise indicated the AMR values are intended to be applied when  $V_{CC} > V_{CC,on}$ . When  $V_{CC} < V_{CC,on}$  the minimum between the indicated value and  $V_{CC} + 0.3$  V has to be considered.

## 4.2 Thermal data

#### Table 4. Thermal data

| Symbol            | Parameter                              | Value      | Unit |

|-------------------|----------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient | 120        | °C/W |

| TJ                | Junction temperature operating range   | -40 to 125 | °C   |

| T <sub>stg</sub>  | Storage temperature range              | -55 to 150 | °C   |

| Symbol          | Parameter                       | Min.               | Max.    | Unit | Remarks                                                |

|-----------------|---------------------------------|--------------------|---------|------|--------------------------------------------------------|

| V <sub>CC</sub> | V <sub>CC</sub> supply voltage  | V <sub>CC,su</sub> | 16.5    | V    | -                                                      |

| VHV,op          | HVSU voltage                    | 0                  | 480     | V    | Linearity not guaranteed between 480 V<br>and VHVSU,bd |

| VFB             | FB pin regulation voltage range | 1.085              | 2.8     | V    | -                                                      |

| VCS,op          | CS pin operative condition      | 0                  | VCS,lim | V    | -                                                      |

| VZCD            | ZCD pin operative voltage       | Self limited       | 3.3     | V    | -                                                      |

| IZCD_sink       | ZCD pin operative current       | IBO                | 650     | μA   | -                                                      |

| VCTRL           | CTRL pin operative voltage      | VCTRL,dis          | Vadis   | V    | -                                                      |

| VTOFF           | TOFF pin operative voltage      | 0                  | 3.3     | V    | -                                                      |

### Table 5. Recommended operating conditions

# 5 Electrical characteristics

$T_{j}$  = -40 °C to 125 °C, 25 °C production tested,  $V_{CC}$  = 15 V, unless otherwise specified.

| Symbol        | Pin     | Parameter                            | Test condition                                               | Min. | Тур. | Max. | Unit |

|---------------|---------|--------------------------------------|--------------------------------------------------------------|------|------|------|------|

| Supply volta  | ge      | •                                    | •                                                            |      |      |      |      |

| Vcc,on        | VCC     | Turn-on threshold                    | (1)                                                          | 11.8 | 13   | 14.2 | V    |

|               | VCC     | Low consumption mode                 | Low consumption mode <sup>(1)</sup>                          | 8.8  | 9.2  | 9.7  | V    |

| Vcc,su        | VCC     | activation                           | Startup                                                      | 2.2  | 3    | 3.8  | V    |

| Vcc,shd       | VCC     | V <sub>CC</sub> for IC reset         | Low consumption <sup>(1)</sup>                               | 7.8  | 8.5  | 9.2  | V    |

| Supply curre  | nt      |                                      |                                                              |      |      |      |      |

| Istart-up     | VCC     | Startup current                      | Startup, Vcc < Vcc,on                                        | -    | 125  | 250  | μA   |

| 100           | NOC     | Operating supply                     | No switching <sup>(2)</sup>                                  | -    | -    | 3.15 | mA   |

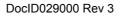

| ICC           | VCC     | current                              | See Figure 4 on page 14                                      |      |      | •    |      |

| lq            | VCC     | Quiescent current                    | Low consumption mode,<br>CTRL < VCTRL,dis                    | -    | 330  | 480  | μA   |

| High-voltage  | startup | generator                            |                                                              |      |      |      |      |

| VHV           | HVSU    | Breakdown voltage                    | IHV < 100 μA                                                 | 800  | -    | -    | V    |

| VHVstart      | HVSU    | Start voltage                        | IVcc < 100 μA                                                | 40   | 46   | 55   | V    |

| lcharge,su    | VCC     | Initial charging current             | VHVSU > VHvstart, Vcc < 2 V                                  | 0.25 | 0.43 | 0.8  | mA   |

| Icharge       | VCC     | V <sub>CC</sub> charge current       | VHVSU > VHvstart,<br>Startup, V <sub>CC</sub> < Vcc,on       | 2    | 3.4  | 5    | mA   |

|               |         |                                      | VHVSU > VHvstart, Vcc < 2 V                                  | 0.3  | 0.65 |      |      |

| ihv, on       | HVSU    | ON-state current                     | VHVSU > VHvstart, startup,<br>Vcc < Vcc,on                   | 2.3  | 4    | 6    | mA   |

| IHV, OFF      | HVSU    | OFF-state leakage<br>current         | VHVSU = 400 V, active mode                                   | -    | 18   | 30   | μA   |

| Input voltage | sensin  | g                                    |                                                              |      |      |      |      |

| Vsurge        | HVSU    | Surge protection threshold           | -                                                            | 500  | 570  | 620  | V    |

| Tsurge        | HVSU    | Max. stop state duration after surge | VHVSU > Vsurge <sup>(3)</sup>                                | 7    | 10   | 15   | ms   |

| Feedback in   | out     |                                      |                                                              |      |      |      |      |

| VFB,ref       | FB      | FB reference voltage                 | Active mode <sup>(4)</sup> , <sup>(5)</sup> , <sup>(6)</sup> | -    | 1    | -    | V    |

| kp            | FB      | Multiplier gain                      | Active mode, VFB = 2.8 V,<br>VHVSU = 300 $V^{(6)}$           | 0.35 | 0.4  | 0.46 | -    |

| IFBsrc        | FB      | FB pin pull-up current               | Active mode, VZCD,off = 2.0 V,<br>VFB = 1.65 V               | 0.67 | 1    | 1.35 | mA   |

| Table | 6. | Electrical | characteristics |

|-------|----|------------|-----------------|

|-------|----|------------|-----------------|

|              |           |                                                   | ical characteristics (continued)                                               |      |         |      |      |

|--------------|-----------|---------------------------------------------------|--------------------------------------------------------------------------------|------|---------|------|------|

| Symbol       | Pin       | Parameter                                         | Test condition                                                                 | Min. | Тур.    | Max. | Unit |

| IFBsnk       | FB        | FB pull-down current                              | Active mode, VZCD,off = 3.2 V,<br>VFB = 1.65 V                                 | 1.3  | 2       | 2.7  | mA   |

| VBm          | FB        | Burst mode threshold                              | Active mode <sup>(5)</sup>                                                     | 0.97 | 1.054   | 1.11 | V    |

| Tbm          | FB        | Burst mode repetition rate                        | VFB = 0.8 V <sup>(3)</sup> , VTOFF = 2.5 V                                     | 0.8  | 1.04    | 1.4  | ms   |

| VOFP         | FB        | Optocoupler failure<br>protection threshold       | Active mode <sup>(5)</sup>                                                     | 2.75 | 2.95    | 3.4  | V    |

| TOFP         | FB        | Max. active mode<br>duration after FB<br>clamping | VFB > VFB,max <sup>(3)</sup>                                                   | 70   | 100     | 130  | ms   |

| PSR function |           |                                                   |                                                                                |      |         |      |      |

|              | <b>FD</b> |                                                   | Tamb = 25 °C <sup>(7)</sup>                                                    | 2.55 | 2.6     | 2.65 | V    |

| VREF,PSR     | FB        | PSR loop reference                                | Over all temperature range <sup>(4)</sup> , <sup>(7)</sup>                     | 2.5  | 2.6     | 2.7  | V    |

| gm           | FB        | Transconductance                                  | ΔIFB = ± 10 μA,<br>VFB = 1.65 V                                                | 1.3  | 2.3     | 3.2  | mS   |

| Current sens | e input   | (8)                                               |                                                                                |      |         |      |      |

| VCS,lim      | CS        | Current sense<br>reference clamp                  | VHVSU = DC voltage,<br>VFB = 3.3 V,<br>1.9 V < VCTRL < 2.4 V                   | 700  | 750     | 810  | mV   |

| VCS,min      | CS        | Current sense minimum<br>level                    | -                                                                              | 30   | 55      | 80   | mV   |

| ICS          | CS        | Current sense pin bias current                    | VCS = 500 mV <sup>(4)</sup>                                                    | -    | 2.5     | 5    | μA   |

| TLEB         | CS        | Leading edge blanking                             | -                                                                              | 140  | 340     | 470  | ns   |

| VOCP         | CS        | Saturation protection threshold                   | During Ton                                                                     | 1    | 1.1     | 1.2  | V    |

| TOCP         | CS        | Max. stop state duration after OCP                | tpulse = 1 $\mu$ s, amplitude 2 V <sup>(3)</sup>                               | 0.72 | 1.04    | 1.41 | ms   |

|              | CS        | VCS during SS                                     | VCTRL = 0.7 V                                                                  | 280  | 348     | 450  | mV   |

| VCS_SS       | 03        |                                                   | VCTRL = Vctrl,bias                                                             | -    | VCS,lim | -    | mV   |

| ZCD input    |           |                                                   |                                                                                |      |         |      |      |

| VZCD,arm     | ZCD       | ZCD arming threshold                              | After Tblank,min <sup>(7)</sup>                                                | 0.42 | 0.5     | 0.6  | V    |

| VZCD,trig    | ZCD       | ZCD triggering<br>threshold                       | Negative going edge <sup>(7)</sup>                                             | 0.24 | 0.3     | 0.38 | V    |

| TBLANK,min   | ZCD       | ZCD min. blanking time                            | From MOS turn off                                                              | 2    | 3.2     | 4.6  | μs   |

| TBLANK,var   | ZCD       | ZCD programmable<br>blanking time                 | VTOFF = 0 V <sup>(9)</sup> , from 1 <sup>st</sup> ZCD trig<br>after TBLANK,min | 120  | 200     | 290  | μs   |

| VZCD,cl_l    | ZCD       | ZCD negative clamping voltage                     | IZCD src = 1 mA                                                                | -230 | -100    | -    | mV   |

Table 6. Electrical characteristics (continued)

| Symbol          | Pin  | Parameter                                                             | Test condition                                  | Min. | Тур. | Max. | Unit |

|-----------------|------|-----------------------------------------------------------------------|-------------------------------------------------|------|------|------|------|

| IZCDb           | ZCD  | ZCD pin biasing current                                               | VZCD = 0.1 to 2.6 V <sup>(4)</sup>              | -    | -    | 1    | μA   |

| IBO             | ZCD  | Brownout detection level                                              | Sourcing during on time                         | 65   | 105  | 140  | μA   |

| ТВО             | ZCD  | Brownout detection time                                               | IZCD < IBO <sup>(3)</sup>                       | 70   | 100  | 130  | ms   |

| Timing          |      |                                                                       |                                                 |      |      |      |      |

| Trec            | -    | Recovery time after<br>opto failure, analogue<br>disable or brownout  | (3)                                             | 1.7  | 2.5  | 3.2  | s    |

| Gate driver     |      |                                                                       |                                                 |      |      |      |      |

| VGDH            | GD   | Output high voltage                                                   | IGD,source = 5 mA                               | 14.5 | -    | -    | V    |

| VGDL            | GD   | Output low voltage                                                    | IGD,sink = 5 mA                                 | -    | -    | 0.1  | V    |

| Isource         | GD   | Output source peak current                                            | VGD = 7.5 V <sup>(4)</sup>                      | 0.3  | -    | -    | А    |

| lsink           | GD   | Output sink peak<br>current                                           | VGD = 7.5 V <sup>(4)</sup>                      | 0.6  | -    | -    | А    |

| Tf              | GD   | Fall time                                                             | CGD = 1 nF, from 13.5 V to 1.5 V                | -    | 6    | -    | ns   |

| Tr              | GD   | Rise time                                                             | CGD = 1 nF, from 1.5 V to 13.5 V                | -    | 35   | -    | ns   |

| VGD,shd         | GD   | Maximum voltage<br>during shut-down                                   | V <sub>CC</sub> < Vcc,shd , IGD = 2 mA          | 0.2  | 1    | 1.5  | V    |

| CTRL input      |      |                                                                       |                                                 |      |      |      |      |

| VCTRL,dis       | CTRL | Disabling threshold                                                   | Negative going edge <sup>(7)</sup>              | 0.4  | 0.5  | 0.6  | V    |

| Vadis           | CTRL | Timed disabling threshold                                             | (7)                                             | 2.4  | 2.6  | 2.85 | V    |

| TADIS           | CTRL | Max. operating interval<br>after analog disable<br>feature triggering | VCTRL > Vadis <sup>(3)</sup>                    | 70   | 100  | 130  | ms   |

| Vctrl,bias CTRL | стрі | IRL CTRL biasing voltage                                              | Tamb = 25 °C <sup>(10)</sup>                    | 1.84 | 2.05 | 2.26 | V    |

|                 |      |                                                                       | Over whole temp. range                          | 1.75 | -    | 2.35 | -    |

| lctrl,bias      | CTRL | CTRL biasing current                                                  | VCTRL = 0 V                                     | 5    | 10   | 15   | μA   |

| Rctrl           | CTRL | Internal parallel resistor                                            | (11)                                            | -    | 205  | -    | kΩ   |

| Vctrl,pd        | CTRL | Pin voltage during low<br>consumption (power<br>good)                 | Low consumption, ICTRL = 0.2 mA                 | -    | -    | 0.2  | v    |

| Veoss           | CTRL | End of soft-start level                                               | $^{(10)}$ Pulse duration greater than 5 $\mu$ s | 1.7  | 1.8  | 1.95 | V    |

Table 6. Electrical characteristics (continued)

| Symbol      | Pin                  | Parameter                    | Test condition | Min. | Тур. | Max. | Unit |

|-------------|----------------------|------------------------------|----------------|------|------|------|------|

| TOFF charac | TOFF characteristics |                              |                |      |      |      |      |

| VTOFF,fix   | TOFF                 | Minimum fixed TBLANK voltage | (4)            | -    | 2    | -    | V    |

| koff        | TOFF                 | TOFF characteristic slope    | (4)            | -    | 100  | -    | µs/V |

| ITOFFpu     | TOFF                 | Pull-up current              | -              | 6    | 12   | 18   | μA   |

| VTOFF,bias  | TOFF                 | Internal bias voltage        | (4)            | -    | 2.4  | -    | V    |

Table 6. Electrical characteristics (continued)

1. Parameters in tracking group 1.

2. Calculated during testing procedure as difference between measured  $I_{\mbox{\scriptsize CC}}$  and FB source current.

3. Parameter calculated.

4. Parameters not tested in production.

5. Parameters in tracking group 2.

6. The Kp parameter includes the overall tolerances of the multiplier block defined as per note<sup>(8)</sup>.

7. Parameters in tracking group 3.

- 8.  $VCS = kp \cdot \frac{VHVSU}{VHVSU,pk} (VFB VFB, ref) OR VCS, min , VHVSU, pk indicates the maximum value of VHVSU.$

- 9. TBLANK.var = koff  $\cdot$  (VTOFF, fix VTOFF)

10. Parameters in tracking group 4.

11. VCTRL,bias/ICTRL,bias.

# **6** Typical electrical characteristic

#### Figure 4. V<sub>CC</sub> current consumption

## 7 Application information

## 7.1 Operating modes

The HVLED001A QR flyback controller is able to operate either as a single stage high power factor (HPF) flyback controller or as a DC/DC flyback controller in dual-stage topologies.

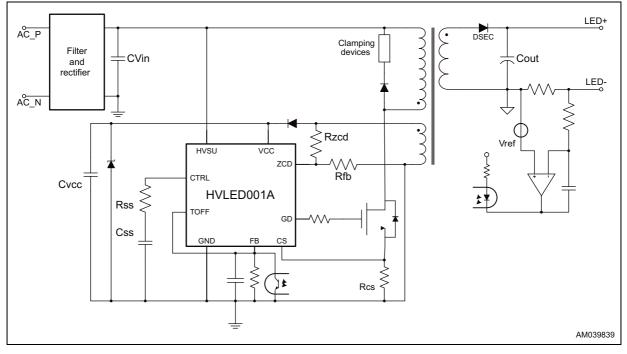

Application schematics of the two main topologies are reported in *Figure 5* and *Figure 6*.

Figure 5. High power factor flyback - constant output current

#### Figure 6. High power factor flyback – primary side regulated constant output voltage

The HVLED001A has four main operating modes: the startup mode, active mode, stop mode and low consumption mode.

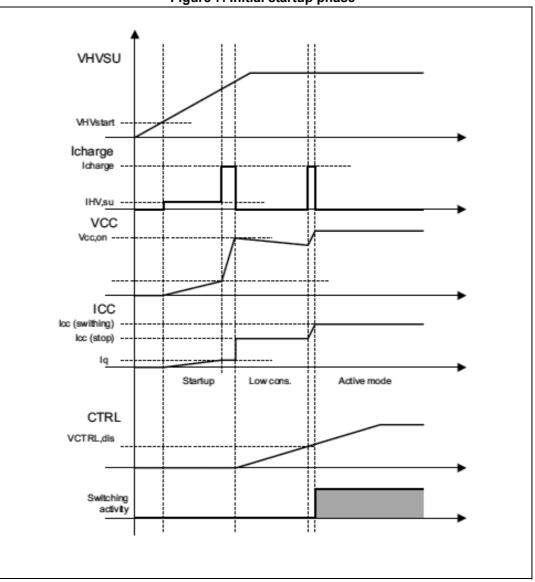

### 7.1.1 Startup mode

This state is entered to begin the switching activity (during application's turn-on or exiting from the low consumption state). The HVSU is involved into the mechanism of VCC charging; all other peripherals, except the UVLO and logic supply, are turned off to minimize the startup time.

During this state the CTRL pin is internally pulled to ground.

Figure 7. Initial startup phase

### 7.1.2 Active mode

It is the normal operational mode. During this state the external MOSFET is driven accordingly to signals coming from the application in order to regulate the desired output parameter in the closed loop (peak current control method).

The active mode is exited when abnormal conditions are present or  $V_{CC}$  drops below the Vcc,su threshold. The HVSU is inactive during the active mode.

#### 7.1.3 Stop mode

This state is intended to stop the switching activity without turning off the entire function set, to quickly restart when abnormal or disabling conditions end. During this state the power consumption is not minimized and the soft-start procedure is not enabled.

#### 7.1.4 Low consumption mode

This state is intended to stop the switching activity reducing the power consumption to a minimum level. The soft-start procedure is set to be performed when abnormal or disabling condition is removed.

During this state the VCC is kept between VCC, su and VCC, on by the high voltage startup unit (HVSU) delivering Icharge to the output capacitor.

# Note: IMPORTANT: The HVSU charges the VCC so any other external voltage (including auxiliary winding) must be decoupled using a diode (e.g.: 1N4148).

#### 7.1.5 Soft-start

The soft-start phase is entered after the startup and every time the IC exits from the low consumption mode. This phase lasts until the voltage at the CTRL pin reaches the "end of soft-start" level (Veoss).

The current sense maximum limit is derived from this voltage, therefore the charging time of a capacitor placed between the CTRL pin and GND defines the soft-start time.

During this phase some protections [optocoupler failure protection (OFP), brownout (BO) and analog disable (AN\_DIS)] are ignored.

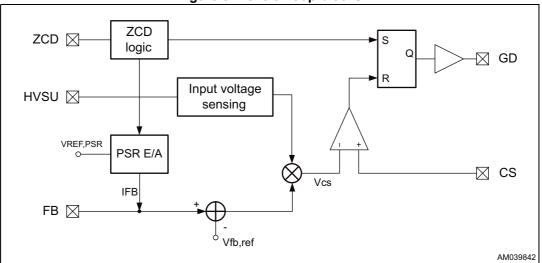

## 7.2 Control loop

The control loop is based on the current mode quasi resonant flyback control scheme and is therefore performed by turning off the MOSFET when the peak of its source current reaches the threshold set by the control loop, and by turning on the MOSFET in correspondence of the resonant valley following the demagnetization of the transformer or inductor.

A detail of the block involved into this scheme is shown in *Figure 8*.

Figure 8. Control loop blocks

#### 7.2.1 Current sense input

The peak of the primary current is read across a shunt resistor placed between the MOSFET's source and compared with a threshold equal to:

#### **Equation 1**

$$V_{CS} = k_p \cdot \frac{V_{HVSU}}{V_{HVSU,pk}} \cdot \left(V_{FB} - V_{FB,ref}\right)$$

Where the term  $V_{HVSU,pk}$  is the maximum value of the HVSU voltage within around 20 ms and is used to compensate the dependency on the input voltage of the open loop gain transfer function. The gain  $k_p$  collects all the proportional terms between the HVSU voltage and CS threshold.

A leading edge blanking time (LEB) is applied after the MOSFET's turn-on.

The  $V_{CS}$  signal is upper limited to a value that depends on the CTRL voltage and is lower limited to 55 mV.

A second level OCP threshold is present to temporarily stop the switching activity in case of inductor saturation.

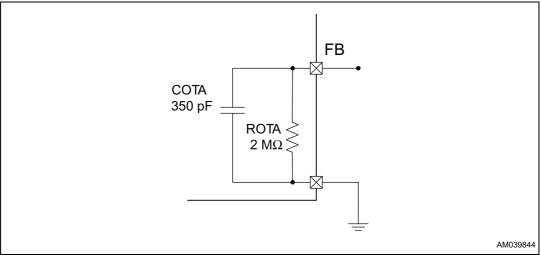

### 7.2.2 Feedback input

The FB pin is intended to be connected to the compensation network for the primary side control (PSR) loop of the output voltage (see Section 7.2.4) as well as to be connected directly to the collector of the optocoupler that provides the galvanic insulation to the secondary side regulation control loop.

In case of constant output voltage applications, the PSR loop can be used to regulate the output voltage saving the secondary side error amplifier.

The FB voltage is also used as an input parameter for the burst mode operation described in *Section 7.2.5*.

The pin embeds a protection to prevent from the operation with a failed optocoupler.

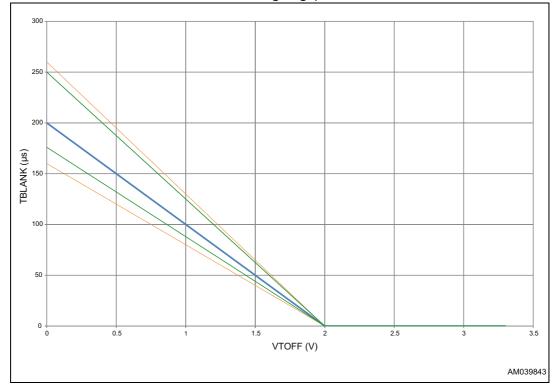

### 7.2.3 Zero current detection

The zero level detection is performed by a trigger logic that, once armed (if a ZCD voltage is higher than VZCD, arm after Tblank, min starting from GD turn-off instant), is sensitive to falling edges. The advanced ZCD logic is able to discriminate between the normal operation, output short-circuit or startup condition.

An internal blanking time prevents any triggering signal to activate the MOSFETs at the very beginning of the off-time, where spurious resonances could be present. As a result, the first falling edge occurring after the blanking time turns on the MOSFET.

To ensure a proper operation, the transformer has to be designed to guarantee that the inductor's demagnetization time is longer than TBLANK (at VTOFF > VTOFF,fix) when the  $V_{CS}$  value (*Equation 1*) is higher than 0.7 V (typ.).

The TOFF pin is intended to select the blanking time duration. If the pin is left unconnected a fixed blanking time is provided.

The TBLANK value depends on the TOFF voltage (Figure 9).

An internal starter provides the triggering signal whenever a valid arming signal is not detected.

The ZCD pin embeds a negative clamp to limit the negative-going current.

Figure 9. Tblank time vs. TBLANK voltage (typical, measured starting form first ZCD falling edge)

### 7.2.4 Primary side regulation feature

The ZCD pin is also used as input of the PSR error amplifier (E/A). The reference voltage of this loop is internally fixed to VREF,PSR and applied to the non-inverting input of the E/A. The output of such error amplifier is connected to the FB pin where the relevant compensation network has to be connected.

In a flyback or buck-boost topology the output voltage can be read from the primary side using an auxiliary winding of the power magnetic: in this case the output voltage is obtained using *Equation 2*:

#### **Equation 2**

$$Vout = VREF, PSR \cdot \frac{N_{SEC}}{N_{AUX}} \cdot \left(1 + \frac{Rzcd}{Rfb}\right)$$

The internal small signal model of the PSR E/A is obtained by considering the voltage gain ( $G_V$  = 73 dB) and the gain bandwidth product (GBWP = 1 MHz) and is illustrated in *Figure 10*:

Figure 10. PSR E/A small signal model

### 7.2.5 Burst mode operation

As soon as the FB pin drops below Vbm the burst mode operating mode is entered. The switching activity is temporarily interrupted until the FB voltage returns above the Vbm value. An internal hysteresis improves the noise rejection of this feature. The FB biasing current follows the same rules as in the normal operation; therefore the burst mode operation is either defined by a secondary side error amplifier when an optocoupler is used or by the internal error amplifier if the PSR operation is on.

During the burst mode, the output voltage value is refreshed every millisecond by means of the generation of four switching pulses separated by the ZCD voltage's falling edge. The TBLANK,min interval is also present between each pulse.

A minimum power delivery is associated with the burst mode. A small preloading device (resistor or clamping Zener) should be placed on the output port to prevent the output voltage runaway when no load is connected to the output port.

DocID029000 Rev 3

#### 7.2.6 Gate driver

The output stage, connected to VCC potential and capable of the 300 mA source and 600 mA sink current, is suitable to drive high current MOSFETs. The resulting managed power can be greater than 150 W.

### 7.3 IC supply management

The IC's voltage supply is managed by the UVLO circuitry together with the high voltage startup unit and reference generators. These logics define also supply currents during different operating conditions.

### 7.3.1 VCC supply management

The IC is designed to operate with a range of supply voltage to ensure optimum gate driving. An active limiting device is embedded to prevent low energy fluctuations to bring the VCC voltage above the technological constraints.

Both the active mode and the low consumption mode exhibit very low supply currents in order to meet the energy saving regulation.

The VCC pin can be driven independently from the HVSU pin's connection, for example when auxiliary supply voltage is present. In this case the HVSU pin will be used solely to monitor input voltage.

A bulk capacitor, having a capacitance of around 10  $\mu$ F, followed by a ceramic capacitor, having a typical capacitance of 100 nF and connected very tight to the V<sub>CC</sub> pin, are necessary to properly sustain the V<sub>CC</sub> voltage during all operating phases.

#### 7.3.2 High voltage startup

The high voltage startup (HVSU) circuitry is primarily intended to provide the startup current to the VCC pin and maintain the IC responsive during low consumption modes.

This structure is able to sustain at least 800 V to avoid any damage in case of a surge or burst on the stage's input.

The overall structure is off until input voltage reaches the VHVSU, start threshold, after that it sources a minimum current (Icharge,su) to charge the VCC pin up to the Vcc,su threshold. This condition prevents the IC from severe damages in case of the short-circuit on the V<sub>CC</sub> pin.

At this  $V_{CC}$  voltage a higher current (Icharge) is provided to the VCC to reach the VCC, on threshold. At this occurrence the active mode is invoked and the HVSU is turned off.

During other active mode's phases and the stop mode the HVSU is off.

If the low consumption mode is entered, the HVSU unit is turned on.

Table 7 summarizes the HVSU behavior in all IC conditions.

Table 7. HVSU operating modes

| Operating condition (see Figure 7)                             | VCC range              | OFF | lcharge,su | lcharge |

|----------------------------------------------------------------|------------------------|-----|------------|---------|

| All states if VIN < VHVSU,ON                                   | -                      | Х   | -          | -       |

| Startup (logic startup)                                        | 0 V Vcc,su             | -   | Х          | -       |

| Startup (IC startup)                                           | Vcc,su Vcc,on          | -   | -          | Х       |

| Active mode                                                    | Vcc,su VCC,MAX         | Х   | -          | -       |

| Stop mode                                                      | Vcc,su VCC,MAX         | Х   | -          | -       |

| Low consumption mode                                           | Vcc,su Vcc,on (rising) | -   | -          | Х       |

| Low consumption mode<br>(after the end of entering conditions) | Vcc,su Vcc,on          | -   | -          | х       |

## 7.4 Auto-restart timer (ART)

The auto-restart timer unit is responsible for the generation of the protection intervals and of the restart times after the low consumption mode. A summary of all possible combinations of times is described in *Section 7.5*.

### 7.5 Protections

A comprehensive set of protections is embedded to ensure a high level of reliability of the final application using a limited number of components.

#### 7.5.1 Overcurrent protection (OCP)

To prevent any damage to active components in case of inductor's saturation the MOSFET is immediately turned off by fast OCP protection. At this occurrence the IC temporarily enters the stop state for a time equal to TOCP.

#### 7.5.2 Input overvoltage protection (I-OVP)

Disturbances of the input voltage like surges or bursts may increase the voltage applied to the transformer primary side. Worst, an excessive input voltage could be applied to the application. These occurrences may result into MOSFET's damages during the off state when the drain voltage rises to Vin plus reflected voltage, eventually above the maximum absolute rating of the MOSFET itself.

An input voltage higher than VSurge, measured by HVSU structure, immediately stops the IC. If the extra voltage diminishes before Tsurge the device restarts immediately without activating the startup procedure, otherwise the low consumption mode is entered until the input voltage returns below the safety threshold. An internal hysteresis improves the noise rejection of this feature. In the latter case the ART activates the startup procedure.

### 7.5.3 Brownout protection (BO)

The current sourced by the ZCD pin's negative clamp during the on time is compared to a minimum value to determine whether the input voltage is lower than the input range specification (brownout protection). If a value lower than IBO for a time longer than TBO, managed by the ART, is detected the IC is stopped for Trec and then restarted.

When the protection is triggered, the ART performs the autoreloading procedure after Trec. The brownout protection is active during the active mode, but blanked during the soft-start.

### 7.5.4 Optocoupler failure protection (OFP)

This protection detects either the absence of the optocoupler control (no pull-down) or the overload condition for more than a time equal to TOFP and switches off the application putting the device in the low consumption mode. This prevents the output power from a rising above excessive values due to the loss of control.

The ART manages the TOFP interval and performs the auto-reloading procedure after Trec. The OFP is active during the active mode, but blanked during the soft-start.

### 7.5.5 Output overvoltage protection (oOVP)

In case of the ZCD sampled voltage is well above the VREF,PSR voltage (around 3 V) OTA provides an extra sink current (2 mA typ.) to the FB pin to speed up the energy transfer reduction and limiting the output voltage overshooting.

## 7.6 Disable and monitor feature

Several disabling means are available to externally disable the IC:

- 1. **Driving the CTRL pin low (CTRL\_DIS):** this occurrence immediately puts the device in the low consumption mode; when the CTRL pin is left free, the internal biasing mean pulls up the voltage above the threshold entering the soft-start procedure.

- 2. **Driving the CTRL pin high (AN\_DIS):** a CTRL voltage higher than the threshold for a time longer than Tdis causes the device to enter the low consumption mode. The ART timer performs an auto recover procedure after Trec.

Anytime the HVLED001A device enters low consumption an internal pull-down discharges the soft-start capacitor and resets the soft-start time.

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK is an ST trademark.

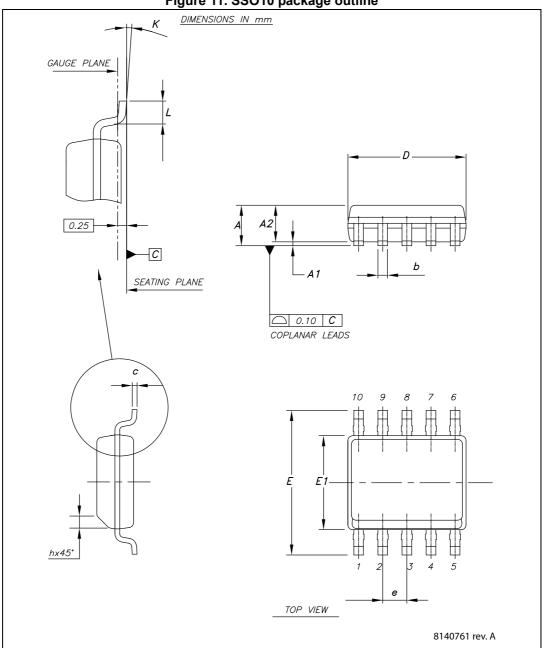

## 8.1 SSO10 package information

#### Figure 11. SSO10 package outline

| Table 8. SSOTU package mechanical data |                 |      |      |  |  |

|----------------------------------------|-----------------|------|------|--|--|

| Symbol                                 | Dimensions (mm) |      |      |  |  |

| Symbol                                 | Min.            | Тур. | Max. |  |  |

| А                                      | -               | -    | 1.75 |  |  |

| A1                                     | 0.10            | -    | 0.25 |  |  |

| A2                                     | 1.25            | -    | -    |  |  |

| b                                      | 0.31            | -    | 0.51 |  |  |

| С                                      | 0.17            | -    | 0.25 |  |  |

| D                                      | 4.80            | 4.90 | 5    |  |  |

| E                                      | 5.80            | 6    | 6.20 |  |  |

| E1                                     | 3.80            | 3.90 | 4    |  |  |

| е                                      | -               | 1    | -    |  |  |

| h                                      | 0.25            | -    | 0.50 |  |  |

| L                                      | 0.40            | -    | 0.90 |  |  |

| К                                      | 0°              | -    | 8°   |  |  |

Table 8. SSO10 package mechanical data

# 9 Revision history

| Date Revision |   | Changes                                                                                                                                                                                                                                                                                      |  |  |

|---------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 24-Mar-2016   | 1 | Initial release.                                                                                                                                                                                                                                                                             |  |  |

| 26-May-2016   | 2 | Updated document status to Datasheet - production data on page 1.                                                                                                                                                                                                                            |  |  |

| 14-Sep-2017   | 3 | <ul> <li>Updated <i>Table 5 on page 9</i> (updated Parameter of VHV,op symbol).</li> <li>Updated <i>Section 5 on page 10</i> (updated T<sub>j</sub> and values of VCS,lim and TBLANK,min symbols in <i>Table 6 on page 10</i>).</li> <li>Minor modifications throughout document.</li> </ul> |  |  |

#### Table 9. Document revision history

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID029000 Rev 3

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LED Lighting Drivers category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below :

LV5235V-MPB-H MB39C602PNF-G-JNEFE1 MIC2871YMK-T5 AL1676-10BS7-13 AL1676-20AS7-13 AP5726WUG-7 ICL8201 IS31BL3228B-UTLS2-TR IS31BL3506B-TTLS2-TR AL3157F-7 AP5725FDCG-7 LV52204MTTBG AP5725WUG-7 STP4CMPQTR NCL30086BDR2G CAT4004BHU2-GT3 LV52207AXA-VH AP1694AS-13 TLE4242EJ KTD2027EWE-TR AS3688 IS31LT3172-GRLS4-TR TLD2311EL KTD2694EDQ-TR KTZ8864EJAA-TR IS32LT3174-GRLA3-TR MP2488DN-LF-Z NLM0010XTSA1 AL1676-20BS7-13 ZXLD1370QESTTC MPQ7220GF-AEC1-P MPQ7220GR-AEC1-P MPQ4425BGJ-AEC1-P MPQ7220GF-AEC1-Z MPQ4425BGJ-AEC1-Z IS31FL3737B-QFLS4-TR IS31FL3239-QFLS4-TR KTD2058EUAC-TR KTD2037EWE-TR DI05662ST6 KTD2026BEWE-TR MAX20052CATC/V+ MAX25606AUP/V+ BD6586MUV-E2 BD9206EFV-E2 LYT4227E LYT6079C-TL MP3394SGF-P MP4689AGN-P MPQ4425AGQB-AEC1-Z