High efficiency, high-side switch with extended diagnostics and smart driving for capacitive loads

#### **Features**

- 8V to 60V operating supply voltage range

- Smart driving of capacitive load

- · Under-voltage lock-out

- V<sub>CC</sub> over-voltage protection

- Fast demagnetization of inductive loads

- · Overload and over-temperature protection

- · Case over-temperature protection

- · Overload event diagnostic pin

- Over-temperature event diagnostic pin

- Ground disconnection protection

- Designed to meet IEC 61000-4-2, IEC 61000-4-4, IEC 61000-4-5

- Package PowerSSO-24

### **Applications**

- · Programmable logic control

- Vending machines

- Industrial PC peripheral input/output

- Numerical control machines

- · General high-side switch applications

#### Product status link

IPS1025H IPS1025H-32

#### Product label

#### **Description**

The IPS1025H and IPS1025H-32 are single high-side switch ICs able to drive capacitive, resistive or inductive loads with one side connected to ground.

The very low  $R_{DS-ON}$  ( $\leq 25m\Omega$  up to  $T_J$  = 125°C) makes the IC suitable for the applications with up to 2.4A/ 5.6A steady state operating current.

The output channel is protected against junction over-temperature events by a junction temperature sensor, and a further temperature sensor is included to monitor case temperature, so the overheated output channel can only be turned back ON when the case temperature returns below the reset temperature.

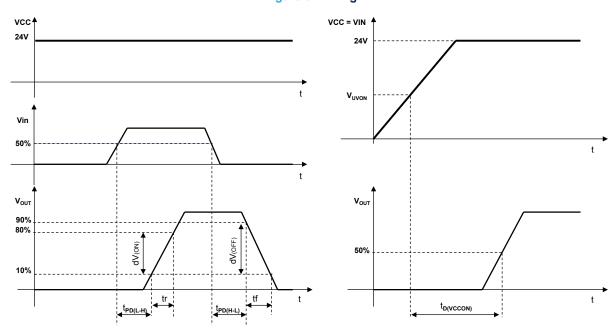

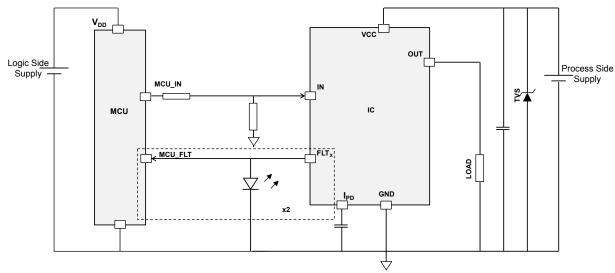

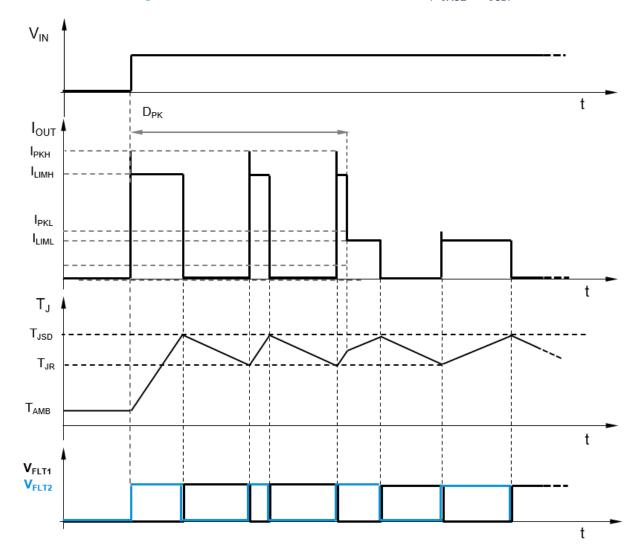

The embedded overload protection circuit monitors the output current and, on triggering of the activation threshold ( $I_{PK}$ ), starts modulating the impedance of the output switch to limit the output current to  $I_{LIM}$ , for both IC and load protection.

The IC offers two different sets of activation threshold and limitation levels ( $I_{PKH}$ ,  $I_{LIMH}$  and  $I_{PKL}$ ,  $I_{LIML}$ ) for smart driving of capacitive loads (such as bulb lamps) and loads with initial peak current requirements.

The IC diagnostics is based on FLT<sub>1</sub> and FLT<sub>2</sub> pins (both current source); activated by respective overload or overtemperature events on the output channel.

# 1 Block diagram

$\mathbf{V}_{\mathsf{CC}}$ **UNDERVOLTAGE** LOCKOUT  $V_{\text{cc}}$  CLAMP FLT<sub>X</sub> **X2 OUTPUT CLAMP** CONTROL IN **LOGIC CURRENT LIMITATION** OUT **JUNCTION TEMP** I<sub>PD</sub> **DETECTION**  $R_{PD}$ **CASE TEMP DETECTION** GND

Figure 1. IPS1025H, IPS1025H-32 block diagram

DS13780 - Rev 1 page 2/28

## 2 Pin connection

VCC 1 24 GND NC 2 IN 23 NC 3 22 I<sub>PD</sub> FLT<sub>2</sub> 4 21 FLT<sub>1</sub> OUT 5 20 OUT OUT 6 19 OUT  $V_{CC}$ OUT 7 18 OUT OUT 8 17 OUT 16 OUT OUT 9 OUT 10 15 OUT OUT 11 14 OUT OUT 12 13 OUT

Figure 2. Pin connections (top through view)

Table 1. Pin descriptions

| Pin no.        | Pin name | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, exposed pad | VCC      | Supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2,3            | N.C.     | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4              | FLT2     | Overload event diagnostic pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5 to 20        | OUT      | Power stage output channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21             | FLT1     | Over-temperature event diagnostic pin.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 22             | IPD      | Initial current duration / level selector. Connect to GND by a capacitor to set duration of $I_{PKH}$ (see Section 7.3 and Table 9). Connect to IN pin by a 220 k $\Omega$ resistor to disable initial $I_{PKH}$ threshold (the over-current limit is only $I_{PKL}$ ). Connect to GND by a 10 k $\Omega$ resistor to disable $I_{PKL}$ (the over-current threshold is only $I_{PKH}$ ). Note: Leaving $I_{PD}$ floating is equivalent to a 1 $\mu$ s duration for $I_{PKH}$ . |

| 23             | IN       | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24             | GND      | Device ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

DS13780 - Rev 1 page 3/28

# 3 Absolute maximum ratings

Absolute maximum ratings are the values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referenced to GND.

Table 2. Absolute maximum ratings

| Symbol             | Parameter                                                                                                 | Value                   | Unit |

|--------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|------|

| V <sub>CC</sub>    | Supply Voltage                                                                                            | -0.3 to 65              | V    |

| Icc                | Maximum DC reverse current (from GND to V <sub>CC</sub> )                                                 | -250                    | mA   |

| I <sub>OUT</sub>   | Output stage current                                                                                      | Internally limited      | А    |

| -l <sub>OUT</sub>  | Reverse current (from single OUT pin to V <sub>CC</sub> )                                                 | 5                       | А    |

| V <sub>IN</sub>    | IN pin voltage                                                                                            | -0.3 to V <sub>CC</sub> | V    |

| I <sub>IN</sub>    | IN pin current                                                                                            | -10/+10                 | mA   |

| V <sub>PD</sub>    | I <sub>PD</sub> pin voltage                                                                               | -0.3 to 5.5             | V    |

| I <sub>PD</sub>    | I <sub>PD</sub> pin current                                                                               | -1/+10                  | mA   |

| V <sub>FAULT</sub> | FLT pins voltage                                                                                          | -0.3 to 5.5             | V    |

| I <sub>FAULT</sub> | FLT pins current                                                                                          | -1 <sup>(1)</sup> /+10  | mA   |

| E <sub>AS</sub>    | Single pulse avalanche energy (T <sub>AMB</sub> = 125 °C, V <sub>CC</sub> = 24 V, I <sub>OUT</sub> = 2 A) | 14                      | J    |

| P <sub>TOT</sub>   | Power Dissipation at T <sub>C</sub> = 25 °C                                                               | Internally limited      | W    |

| T <sub>STG</sub>   | Storage Temperature Range -55 to 150                                                                      |                         | °C   |

| TJ                 | Junction Operating Temperature Internally limited                                                         |                         | °C   |

| T <sub>C</sub>     | Case Operating Temperature                                                                                | -40 to 150              | °C   |

<sup>1.</sup> intended as worst case when IC is in normal operation (no fault)

DS13780 - Rev 1 page 4/28

## 4 Thermal data

Table 3. Thermal data

| Symbol                  | Parameter                                    | Value | Unit |

|-------------------------|----------------------------------------------|-------|------|

| R <sub>th(JC)</sub> (1) | Thermal resistance junction-case per channel | 0.7   | °C/W |

| R <sub>th(JA)</sub> (2) | Thermal resistance junction-ambient          | 22    | °C/W |

<sup>1.</sup> Rth between the die and the bottom case surface measured by cold plate as per JESD51.

DS13780 - Rev 1 page 5/28

<sup>2.</sup> JESD51-7.

## 5 Electrical characteristics

(8 V < V<sub>CC</sub> < 60 V; -40 °C < T<sub>J</sub> < 125 °C, unless otherwise specified)

Table 4. Supply

| Symbol             | Parameter                   | Test Conditions                                    | Min. | Тур. | Max.  | Unit |

|--------------------|-----------------------------|----------------------------------------------------|------|------|-------|------|

| $V_{UVON}$         | Under-voltage ON threshold  | -                                                  | 6.9  | -    | 8     | V    |

| V <sub>UVOFF</sub> | Under-voltage OFF threshold | -                                                  | 6.5  | -    | 7.8   | V    |

| V <sub>UVH</sub>   | Under-voltage hysteresis    | -                                                  | 0.15 | 0.5  | -     | V    |

|                    | Supply current in OFF state | V <sub>CC</sub> = 24 V, IN = GND, OUT = open load; | 0.28 | -    | 0.64  | mA   |

| I <sub>SOFF</sub>  |                             | V <sub>CC</sub> = 36 V, IN = GND, OUT = open load; | 0.28 | -    | 0.64  | mA   |

|                    |                             | V <sub>CC</sub> = 60 V, IN = GND, OUT = open load; | 0.29 | -    | 0.685 | mA   |

|                    |                             | V <sub>CC</sub> = 24 V, IN = 5 V, OUT = open load; | 1.05 | -    | 2.25  | mA   |

| I <sub>SON</sub>   | Supply current in ON state  | V <sub>CC</sub> = 36 V, IN = 5 V, OUT = open load; | 1.15 | -    | 2.35  | mA   |

|                    |                             | V <sub>CC</sub> = 60 V, IN = 5 V, OUT = open load; | 1.35 | -    | 2.55  | mA   |

Table 5. Output stage

| Symbol                | Parameter                | Test Conditions                                                               | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| Procu                 | On state registeres      | $V_{CC} = 24 \text{ V}, R_{LOAD} = 12 \Omega,$ @ $T_J = 25  ^{\circ}\text{C}$ | -    | 12   | 16   | mΩ   |

| R <sub>DSON</sub>     | On-state resistance      | $V_{CC} = 24 \text{ V}, R_{LOAD} = 12 \Omega,$ @ $T_J = 125 ^{\circ}\text{C}$ | -    | -    | 30   | mΩ   |

| V <sub>OUT(OFF)</sub> | OFF state output voltage | V <sub>IN</sub> = 0 V and I <sub>OUT</sub> = 0 A                              | -    | -    | 2    | V    |

| I <sub>OUT(OFF)</sub> | OFF state output current | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = 0 V                                 | -    | -    | 10   | μA   |

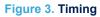

### Table 6. Switching

(V<sub>CC</sub> = 24 V; -40 °C < T<sub>J</sub> < 125 °C, R<sub>LOAD</sub> = 12  $\Omega$ , input rise time < 0.1  $\mu$ s)

| Symbol               | Parameter                                     | Test Conditions                            | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------------|--------------------------------------------|------|------|------|------|

| t <sub>r</sub>       | Rise time                                     |                                            | -    | 30   | 60   | μs   |

| t <sub>f</sub>       | Fall time                                     |                                            | -    | 25   | 60   | μs   |

| t <sub>PD(L-H)</sub> | Propagation delay time IN to OUT, low to high |                                            | -    | 13   | 25   | μs   |

| t <sub>PD(H-L)</sub> | Propagation delay time IN to OUT, high to low |                                            | -    | 60   | 100  | μs   |

| td(Vccon)            | Propagation delay time IN to OUT at power-on  | $V_{IN} = V_{CC}$ and rising from 0 to 24V | 150  | 500  | 1600 | μs   |

DS13780 - Rev 1 page 6/28

Table 7. Input pin (IN)

| Symbol               | Parameter                    | Test Condition                           | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------|------------------------------------------|------|------|------|------|

| V <sub>IL</sub>      | Input pin low level voltage  | -                                        | -    | -    | 0.8  | V    |

| V <sub>IH</sub>      | Input pin high level voltage | -                                        | 2.2  | -    | -    | V    |

| V <sub>I(HYST)</sub> | Input pin hysteresis voltage | -                                        | 0.15 | 0.4  | -    | V    |

| 1                    | Input pin current            | V <sub>IN</sub> = V <sub>CC</sub> = 36 V | -    | -    | 200  |      |

| IIN                  |                              | V <sub>IN</sub> = V <sub>CC</sub> = 60V  | -    | -    | 600  | μA   |

Table 8. Diagnostic pins (FLT<sub>1</sub>, FLT<sub>2</sub>)

| Symbol             | Parameter                                          | Test Condition                                     | Min. | Тур. | Max. | Unit                                  |

|--------------------|----------------------------------------------------|----------------------------------------------------|------|------|------|---------------------------------------|

| IH <sub>FLT</sub>  | Diagnostic pins source current in fault condition. | V <sub>FLT</sub> = 1 V<br>(fault condition active) | -2.5 | -    | -4.0 | mA                                    |

| ITFLT              | Diagnostic pins source current in fault condition. | $V_{FLT} = 5 V$ (fault condition active)           | -0.4 | -    | -1.0 | ША                                    |

| IL <sub>FLT</sub>  | Diagnostic pins leakage current                    | Normal operation V <sub>CC</sub> = 60 V            | 0    | -    | -25  | μА                                    |

| BT <sub>FLT</sub>  | Diagnostic pins blanking time                      | -                                                  | 60   | -    | 400  | μs                                    |

| VCL <sub>FLT</sub> | Diagnostic pins clamp voltage                      | I <sub>FLT</sub> = +1 mA                           | 6    | 6.8  | 8    | V                                     |

| VOLFLI             |                                                    | I <sub>FLT</sub> = -1 mA                           | -    | -    | 0.7  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

DS13780 - Rev 1 page 7/28

Table 9. Protections and diagnostics

| Symbol                | Parameter                                                   | Test C                                                        | ondition                    | Min.      | Тур.                                 | Max.  | Uni    |

|-----------------------|-------------------------------------------------------------|---------------------------------------------------------------|-----------------------------|-----------|--------------------------------------|-------|--------|

| Overload              | I with Dual Threshold Protection: I <sub>PD</sub> pin to G  | ND by C <sub>PD</sub> (47                                     | 70 pF ≤ C <sub>PD</sub> ≤ 4 | 70 nF); s | see Section 7.3                      | 3.1   |        |

|                       |                                                             |                                                               | IPS1025H                    |           | 15.4                                 |       |        |

| I <sub>PKH</sub>      | Initial over-current activation threshold                   | V <sub>CC</sub> = 24 V                                        | IPS1025H-32                 | _         | 25.1                                 | -     | A      |

|                       |                                                             | V 04 V                                                        | IPS1025H                    | 6.25      | 9.0                                  | 11.75 |        |

| I <sub>LIMH</sub>     | Initial over-current limitation level                       | V <sub>CC</sub> = 24 V                                        | IPS1025H-32                 | 12.5      | 17.9                                 | 23.2  | A      |

| D <sub>PK</sub>       | Time limit of Initial over-current                          | V <sub>CC</sub>                                               | = 24 V                      | -         | 215*C <sub>PD</sub> [nF]             | -     | μs     |

| 1                     | Chandy state over company activistics through ald           | \/ = 24\/                                                     | IPS1025H                    |           | 8.0                                  | 11.4  |        |

| I <sub>PKL</sub>      | Steady state over-current activation threshold              | V <sub>CC</sub> = 24 V                                        | IPS1025H-32                 | -         | 13.1                                 | -     | A      |

| l                     | Stoady state over current limitation level                  | V <sub>CC</sub> = 24 V                                        | IPS1025H                    | 2.5       | 3.5                                  | 4.5   | A      |

| I <sub>LIML</sub>     | Steady state over-current limitation level                  | VCC - 24 V                                                    | IPS1025H-32                 | 5.7       | 8.0                                  | 10.4  |        |

| I <sub>HYS</sub>      | Steady state output Current limitation hysteresis           | Vac                                                           | = 24 V                      | -         | 0.3                                  | -     | А      |

| I <sub>LIML-OFF</sub> | Steady state over-current limitation deactivation threshold |                                                               | - 24 V                      | -         | I <sub>LIML</sub> - I <sub>HYS</sub> | -     | А      |

| Overload              | I with Single Level (Lowest) Protection: I <sub>PD</sub> pi | n connected t                                                 | to IN by 10 kΩ r            | esistor;  | see Section 7.                       | .3.2  |        |

|                       |                                                             |                                                               | IPS1025H                    |           | 6.5                                  |       |        |

| I <sub>PKL</sub>      | Steady state over-current activation threshold              | V <sub>CC</sub> = 24 V                                        | IPS1025H-32                 | -         | 13.1                                 | -     | A      |

| l                     | Steady state over-current limitation level                  | V <sub>CC</sub> = 24 V                                        | IPS1025H                    | 2.5       | 3.5                                  | 4.5   | A      |

| I <sub>LIML</sub>     | Steady state over-current illilitation level                |                                                               | IPS1025H-32                 | 5.7       | 8.0                                  | 10.4  |        |

| I <sub>HYS</sub>      | Steady state output Current limitation hysteresis           | V <sub>CC</sub> = 24 V                                        |                             | -         | 0.3                                  | -     | А      |

| I <sub>LIML-OFF</sub> | Steady state over-current limitation deactivation threshold |                                                               |                             | -         | I <sub>LIML</sub> -I <sub>HYS</sub>  | -     | А      |

| Overload              | with Single Level (Highest) Protection: I <sub>PD</sub> p   | in connected                                                  | to GND by 10 k              | Ω resist  | or; see Section                      | 7.3.3 |        |

|                       |                                                             | V - 24 V                                                      | IPS1025H                    |           | 14.4                                 |       |        |

| I <sub>PKH</sub>      | Initial over-current activation threshold                   | V <sub>CC</sub> = 24 V                                        | IPS1025H-32                 | -         | 25.1                                 | -     | A      |

| l                     | Initial over-current limitation level                       | V <sub>CC</sub> = 24 V                                        | IPS1025H                    | 6.4       | 9.0                                  | 11.6  | _      |

| I <sub>LIMH</sub>     | miliai over-current iimitation level                        | vCC- 24 v                                                     | IPS1025H-32                 | 12.5      | 17.9                                 | 23.2  | A      |

| Over-tem              | perature protections                                        |                                                               |                             |           |                                      |       |        |

| T <sub>JSD</sub>      | Junction temperature shutdown                               |                                                               | -                           | 150       | 170                                  | 190   | °C     |

| $T_{JR}$              | Junction temperature reset                                  |                                                               | -                           | -         | 150                                  | -     | °C     |

| T <sub>JHYS</sub>     | Junction temperature hysteresis                             |                                                               | -                           | -         | 20                                   | -     | °C     |

| T <sub>CSD</sub>      | Case temperature shutdown                                   |                                                               | -                           | -         | 130                                  | -     | °C     |

| T <sub>CR</sub>       | Case temperature reset                                      | -                                                             |                             | -         | 110                                  | -     | °C     |

| T <sub>CHYS</sub>     | Case temperature hysteresis                                 | -                                                             |                             | -         | 20                                   | -     | °C     |

| Ground o              | disconnection/Wire break                                    | 1                                                             |                             | l         |                                      |       | 1      |

| I <sub>LGND</sub>     | GND disconnection output current                            | $V_{INX} = V_{CC} = 24 \text{ V},$<br>$V_{OUT} = 0 \text{ V}$ |                             | -         | -                                    | 0.5   | m      |

| Vac over              | -voltage                                                    | 1001 - 0 4                                                    |                             |           |                                      |       |        |

| V <sub>CC</sub> over  | _                                                           |                                                               |                             |           |                                      |       |        |

| $V_{CLAMP}$           | V <sub>CC</sub> Clamp Voltage                               | I <sub>CC</sub> ≤ 10 mA                                       |                             | 65.5      | 70.0                                 | 73.5  | \<br>\ |

DS13780 - Rev 1 page 8/28

| Symbol             | Parameter                   | Test Condition                         | Min.   | Тур.     | Max.   | Unit |

|--------------------|-----------------------------|----------------------------------------|--------|----------|--------|------|

| Demagne            | etization of inductive load |                                        |        |          |        |      |

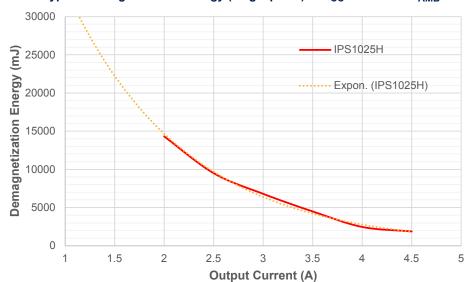

| V <sub>DEMAG</sub> | Demagnetization Voltage     | I <sub>OUT</sub> = 0.5 A, Load ≥ 10 mH | Vcc-76 | Vcc-72.5 | Vcc-68 | V    |

Figure 4. High (left) and Low (right)  $I_{LOAD}$  control activation thresholds ( $I_{PK}$ ) and limitation levels ( $I_{LIM}$ )

DS13780 - Rev 1 page 9/28

# 6 Output Logic

Table 10. Output stage truth table

(L = pin voltage Low, H = pin voltage High, X = not determined)

| , , , , , , , , , , , , , , , , , , , , | IN | OUT              | FLT              |

|-----------------------------------------|----|------------------|------------------|

| Normal Operation                        | L  | L                | L                |

|                                         | H  | H                | L                |

| Overload                                | L  | L                | L                |

|                                         | H  | X <sup>(1)</sup> | H                |

| Junction over-temperature               | L  | L                | L                |

|                                         | H  | L                | H                |

| Case over-temperature                   | L  | L                | L                |

|                                         | H  | L <sup>(2)</sup> | L <sup>(2)</sup> |

| UVLO                                    | L  | L                | X                |

|                                         | H  | L                | X                |

- 1. Pin voltage =  $I_{OUT} * R_{LOAD}$

- 2. Channels with  $T_J > T_{JSD}$  are forced off and the related FLT are activated

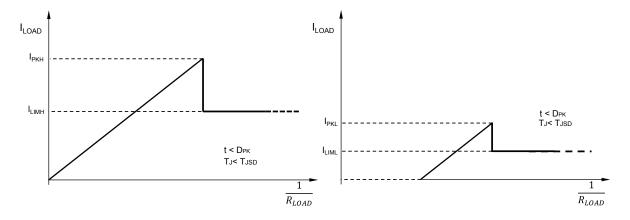

OPTO BARRIER

Vodic Side Supply

MCU\_FLTx

Vod MCU\_FLTx

Vod MCU\_FLTx

N MCU\_FLTx

Vod MCU\_FLTx

Vod

Figure 5. Typical application diagram with opto-couplers

DS13780 - Rev 1 page 10/28

Figure 6. Typical application diagram without opto-couplers

DS13780 - Rev 1 page 11/28

### 7 Protections and diagnostic

The IC integrates several protections to help the design of robust applications.

### 7.1 Under-voltage lock-out

The IC is turned off if the voltage on  $V_{CC}$  pin falls below the turn-off threshold ( $V_{UVOFF}$ ). Normal operation restarts after  $V_{CC}$  exceeds the turn-on threshold ( $V_{UVON}$ ). Turn-on and turn-off thresholds are defined in Table 4.

### 7.2 Over-temperature

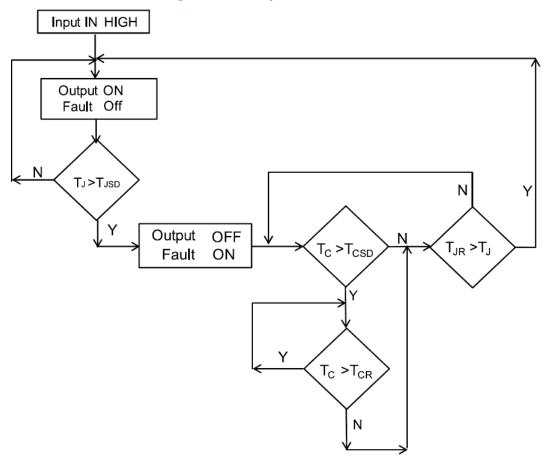

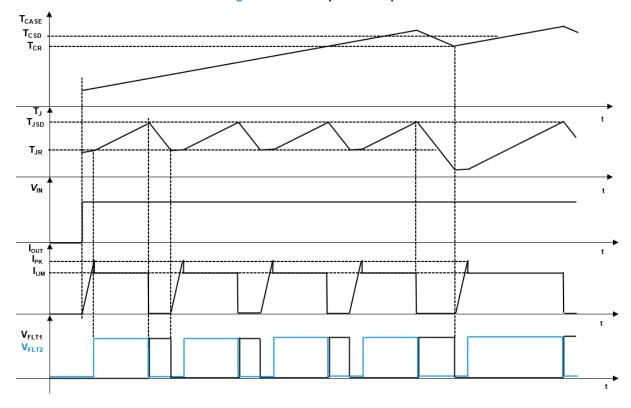

The device is protected against overheating in case of overload conditions. During the driving period (when the MCU is forcing the IN pin high), if the output is overloaded, the device suffers two different thermal stresses: one related to the junction temperature of each output channel, and the other related to the whole case temperature. The two thermal faults (Thermal Junction and Thermal Case) have different trigger thresholds:  $T_{JSD}$  and  $T_{CSD}$ , respectively.

Usually, in thermal stress conditions due to overload, the junction thermal shutdown is the first protection that is activated: the output channel (OUT) is turned off when its junction temperature  $(T_J)$  is higher than the activation threshold  $(T_{JSD})$  and turned back on when it falls below the reset threshold  $(T_{JR})$ . This behavior continues while overload on the output persists. When the thermal protection is active, the FLT<sub>1</sub> (current source) becomes active accordingly.

If the thermal protection is active and the temperature of the case  $(T_C)$  increases over the case protection threshold  $(T_{CSD})$ , then the thermal case protection is activated and the output is switched off until the junction temperature and case temperature fall below their respective reset thresholds  $(T_{CR})$  and  $T_{JR}$ . The FLT<sub>1</sub> pin is active even when thermal case events occur.

Figure 7 shows the thermal protection behavior, while Figure 8 and Section 7.2 show typical temperature trends and output vs. input state.

DS13780 - Rev 1 page 12/28

Figure 7. Thermal protection flowchart

DS13780 - Rev 1 page 13/28

#### 7.3 Overload

The IC integrates an overload protection circuit consisting of an output current sensing section and an output current limitation section.

When the output channel is ON, the sensing circuitry monitors the current supplied to the load: if the activation threshold ( $I_{PK}$ ) is triggered, then the current limitation control circuitry is activated to limit output current to the current limitation level ( $I_{LIM}$ ) and  $FLT_2$  pin is activated until the overload condition is removed.

See the following sections for details and Table 9 for specific activation thresholds and limitation levels. Note that while the output channel operates below its activation threshold, the power dissipation can be calculated by  $R_{ON} * I_{OUT}^2$ , but when the current limitation circuit is activated, power dissipation increases and can be calculated by  $V_{DS} * I_{OUT}$ , where  $V_{DS}$  is the voltage drop between the OUT and  $V_{CC}$  pins of the IC. In order to protect the IC against thermal stress, the over-temperature protection is always active and retains the highest priority.

#### 7.3.1 Overload protection with dual threshold

This case is activated when the pin  $I_{PD}$  is connected to GND by a capacitor ( $C_{PD}$ ) and the IC works with two activation thresholds  $I_{PKH}$  and  $I_{PKL}$ .

The  $I_{PKH}$  is active only in the limited time frame between the L-H transition of the IN signal and the  $D_{PK}$  delay defined by the following design rule:

$$D_{PK}[\mu s] = 215 \times CPD[nF]$$

The above design rule is valid in the range 470 pF  $\leq$  C<sub>PD</sub>  $\leq$  470 nF (see Table 9).

If the I<sub>PKH</sub> is triggered within the D<sub>PK</sub> time frame, then the output current is limited to I<sub>LIMH</sub>.

After D<sub>PK</sub> has elapsed, the IC operates with I<sub>PKL</sub> activation threshold and I<sub>LIML</sub> limitation level, respectively.

DS13780 - Rev 1 page 14/28

Figure 9. Short-circuit behavior with dual threshold ( $T_{CASE} < T_{CSD}$ )

#### 7.3.2 Overload protection with single (low) threshold

The user can set the activation threshold to  $I_{PKL}$  and the limitation level to  $I_{LIML}$  by connecting the  $I_{PD}$  pin to the IN pin with a 220 K $\Omega$  resistor.

This condition is equivalent to setting  $D_{PK} = 0 \mu s$ .

Note: Leaving I<sub>PD</sub> floating is equivalent to having an initial peak duration of 1 μs.

#### 7.3.3 Overload protection with single (high) threshold

The user can set the activation threshold to  $I_{PKH}$  and the limitation level to  $I_{LIMH}$  by connecting the  $I_{PD}$  pin to GND with a 10 K $\Omega$  resistor.

### 7.4 V<sub>CC</sub> disconnection protection

$V_{CC}$  disconnection involves the disconnection of the module from the supply line. When this condition is detected, the output channel can be driven normally until the voltage on  $V_{CC}$  pin remains higher than the UVLO threshold.

In case of inductive load, if the  $V_{CC}$  is disconnected while the channel is active, the energy stored in the inductance is discharged through the power switch thanks to the integrated demagnetization circuit.

DS13780 - Rev 1 page 15/28

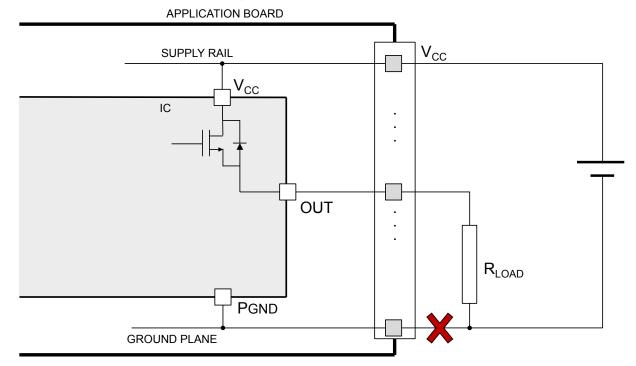

### 7.5 GND disconnection protection

GND disconnection is the disconnection of the module from the reference line. When this condition occurs, the output channel is turned off regardless of the input status.

When this event occurs, the IC continues working normally until the voltage between  $V_{CC}$  and GND pins of the IC results  $\geq V_{UVOFF}$ . The voltage on the GND pin of the IC rises up to the supply rail voltage level. In case of a GND disconnection event, a current ( $I_{LGND}$ ) flows through OUT pin.

For an inductive load, if the GND is disconnected while the output channel is active, the current flows through the power, which is activated by an active clamp as if the input had been deactivated.

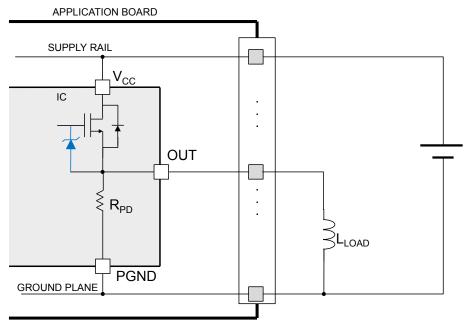

Figure 10. Ground disconnection

DS13780 - Rev 1 page 16/28

## 8 Active clamp

Active clamp is also known as Fast Demagnetization of inductive loads or Fast Current Decay. When a high-side driver turns off an inductance, an under-voltage on output is detected.

The OUT pin is pulled-down to  $V_{CC}$ - $V_{DEMAG}$ . The conduction state is modulated by an internal circuitry in order to keep the OUT pin voltage at  $\sim V_{DEMAG}$  until the load energy has been dissipated. The energy is dissipated in both IC internal switch and load resistance.

Figure 11. Active clamp equivalent principle schematic

DS13780 - Rev 1 page 17/28

## 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

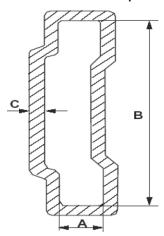

### 9.1 Package mechanical data

D DI MAB b

Figure 13. PowerSSO-24 package dimensions [mm]

Table 11. PowerSSO-24 mechanical data

| Dim.   | [mm]  |      |       |  |  |  |

|--------|-------|------|-------|--|--|--|

| Dilli. | Min.  | Тур. | Max.  |  |  |  |

| A      | 2.15  | -    | 2.47  |  |  |  |

| A2     | 2.15  | -    | 2.40  |  |  |  |

| a1     | 0     | -    | 0.075 |  |  |  |

| b      | 0.33  | -    | 0.51  |  |  |  |

| С      | 0.23  | -    | 0.32  |  |  |  |

| D      | 10.10 | -    | 10.50 |  |  |  |

| E      | 7.4   | -    | 7.6   |  |  |  |

DS13780 - Rev 1 page 18/28

| Dim. |      | [mm] |        |

|------|------|------|--------|

|      | Min. | Тур. | Max.   |

| е    | -    | 0.8  | -      |

| e3   | -    | 8.8  | -      |

| G    | -    | -    | 0.1    |

| G1   | -    | -    | 0.06   |

| Н    | 10.1 |      | 10.5   |

| h    | -    | -    | 0.4    |

| L    | 0.55 | -    | 0.85   |

| N    | -    | -    | 10 deg |

| X    | 4.1  | -    | 4.7    |

| Υ    | 6.5  | -    | 7.1    |

Figure 14. PowerSSO-24 suggested footprint [mm]

STMicroelectronics is not responsible for PCB-related issues. The footprint shown in the above figure is a suggestion which may differ from the customer PCB supplier design rules.

DS13780 - Rev 1 page 19/28

# 10 PowerSSO-24 packing information

Figure 15. PowerSSO-24 tube shipment (no suffix)

Table 12. PowerSSO-24 tube shipment information

All dimensions are in mm

| Description        | Value |

|--------------------|-------|

| Base quantity      | 49    |

| Bulk quantity      | 1225  |

| Tube length (±0.5) | 532   |

| Α                  | 3.5   |

| В                  | 13.8  |

| C (±0.1)           | 0.6   |

DS13780 - Rev 1 page 20/28

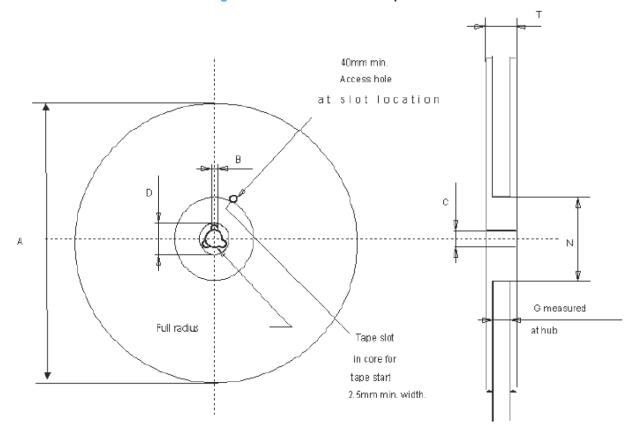

Figure 16. PowerSSO-24 reel shipment

Table 13. PowerSSO-24 reel information

| ΑII | dime | nsions | are | in | mm |

|-----|------|--------|-----|----|----|

| Description   | Value |

|---------------|-------|

| Base quantity | 1000  |

| Bulk quantity | 1000  |

| A (max.)      | 330   |

| B (min.)      | 1.5   |

| C (±0.2)      | 13    |

| F             | 20.2  |

| G (2 ±0)      | 24.4  |

| N (min.)      | 100   |

| T (max.)      | 30.4  |

DS13780 - Rev 1 page 21/28

Р1 TOP COVER TAPE P User Direction of Feed End Start Тор No components Components No components cover 500mm min tape Empty components pockets 500mm min saled with cover tape. User direction of feed 0 0 Ь

Figure 17. PowerSSO-24 tape drawings

Table 14. PowerSSO-24 tape dimension

User Direction of Feed

All dimensions are in mm

| Description       | Symbol     | Value |

|-------------------|------------|-------|

| Tape width        | W          | 24    |

| Tape hole spacing | P0 (± 0.1) | 4     |

| Component spacing | Р          | 12    |

| Hole diameter     | D (± 0.05) | 1.55  |

| Hole diameter     | D1 (min.)  | 1.5   |

| Hole position     | F (± 0.1)  | 11.5  |

| Compartment depth | K (max.)   | 2.85  |

| Hole spacing      | P1 (± 0.1) | 2     |

Note: According to the Electronic Industries Association (EIA) standard 481 rev. A, Feb 1986.

DS13780 - Rev 1 page 22/28

# 11 Ordering information

**Table 15. Ordering information**

| Part number   | Package     | Packaging     |

|---------------|-------------|---------------|

| IPS1025H      | PowerSSO-24 | Tube          |

| IPS1025HTR    | PowerSSO-24 | Tape and reel |

| IPS1025H-32   | PowerSSO-24 | Tube          |

| IPS1025HTR-32 | PowerSSO-24 | Tape and reel |

DS13780 - Rev 1 page 23/28

# **Revision history**

Table 16. Document revision history

| Date        | Version | Changes         |

|-------------|---------|-----------------|

| 15-Nov-2021 | 1       | Initial release |

DS13780 - Rev 1 page 24/28

## **Contents**

| 1   | Bloc  | k diagr                   | am                                               | 2  |  |  |  |

|-----|-------|---------------------------|--------------------------------------------------|----|--|--|--|

| 2   | Pin ( | connec                    | tion                                             | 3  |  |  |  |

| 3   | Abs   | Absolute maximum ratings4 |                                                  |    |  |  |  |

| 4   | The   | Thermal data5             |                                                  |    |  |  |  |

| 5   | Elec  | trical cl                 | haracteristics                                   | 6  |  |  |  |

| 6   | Outp  | out Log                   | ic                                               | 10 |  |  |  |

| 7   | Prot  | ections                   | and diagnostic                                   | 12 |  |  |  |

|     | 7.1   | Under-                    | -voltage lock-out                                |    |  |  |  |

|     | 7.2   | Over-t                    | emperature                                       |    |  |  |  |

|     | 7.3   | Overlo                    | pad                                              | 14 |  |  |  |

|     |       | 7.3.1                     | Overload protection with dual threshold          | 14 |  |  |  |

|     |       | 7.3.2                     | Overload protection with single (low) threshold  | 15 |  |  |  |

|     |       | 7.3.3                     | Overload protection with single (high) threshold | 15 |  |  |  |

|     | 7.4   | V <sub>CC</sub> di        | isconnection protection                          | 15 |  |  |  |

|     | 7.5   | GND o                     | disconnection protection                         | 16 |  |  |  |

| 8   | Acti  | ve clam                   | np                                               | 17 |  |  |  |

| 9   | Pacl  | kage inf                  | formation                                        | 18 |  |  |  |

|     | 9.1   | Packa                     | ge mechanical data                               |    |  |  |  |

| 10  | Pow   | erSSO-                    | -24 packing information                          | 20 |  |  |  |

| 11  | Orde  | ering in                  | formation                                        |    |  |  |  |

| Rev | ision | history                   | ,                                                | 24 |  |  |  |

# **List of figures**

| Figure 1.  | IPS1025H, IPS1025H-32 block diagram                                                                                                      | . 2 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin connections (top through view)                                                                                                       | . 3 |

| Figure 3.  | Timing                                                                                                                                   | . 7 |

| Figure 4.  | High (left) and Low (right) I <sub>LOAD</sub> control activation thresholds (I <sub>PK</sub> ) and limitation levels (I <sub>LIM</sub> ) | . 9 |

| Figure 5.  | Typical application diagram with opto-couplers                                                                                           | 10  |

| Figure 6.  | Typical application diagram without opto-couplers                                                                                        | 11  |

| Figure 7.  | Thermal protection flowchart                                                                                                             | 13  |

| Figure 8.  | Thermal protection plot                                                                                                                  | 13  |

| Figure 9.  | Short-circuit behavior with dual threshold (T <sub>CASE</sub> < T <sub>CSD</sub> )                                                       | 15  |

| Figure 10. | Ground disconnection                                                                                                                     | 16  |

| Figure 11. | Active clamp equivalent principle schematic                                                                                              | 17  |

| Figure 12. | Typical demagnetization energy (single pulse) at V <sub>CC</sub> = 24 V and T <sub>AMB</sub> = 125 °C                                    | 17  |

| Figure 13. | PowerSSO-24 package dimensions [mm]                                                                                                      | 18  |

| Figure 14. | PowerSSO-24 suggested footprint [mm]                                                                                                     | 19  |

| Figure 15. | PowerSSO-24 tube shipment (no suffix)                                                                                                    | 20  |

| Figure 16. | PowerSSO-24 reel shipment                                                                                                                | 21  |

| Figure 17. | PowerSSO-24 tape drawings                                                                                                                | 22  |

|            |                                                                                                                                          |     |

DS13780 - Rev 1 page 26/28

## **List of tables**

| Table 1.  | Pin descriptions                                       | . 3 |

|-----------|--------------------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings                               | . 4 |

| Table 3.  | Thermal data                                           | . 5 |

| Table 4.  | Supply                                                 |     |

| Table 5.  | Output stage                                           | . 6 |

| Table 6.  | Switching                                              | . 6 |

| Table 7.  | Input pin (IN)                                         | . 7 |

| Table 8.  | Diagnostic pins (FLT <sub>1</sub> , FLT <sub>2</sub> ) | . 7 |

| Table 9.  | Protections and diagnostics                            | . 8 |

| Table 10. | Output stage truth table                               | 10  |

| Table 11. | PowerSSO-24 mechanical data                            | 18  |

| Table 12. | PowerSSO-24 tube shipment information                  | 20  |

| Table 13. | PowerSSO-24 reel information                           | 21  |

| Table 14. | PowerSSO-24 tape dimension                             | 22  |

| Table 15. | Ordering information                                   | 23  |

| Table 16. | Document revision history                              | 24  |

|           |                                                        |     |

DS13780 - Rev 1 page 27/28

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS13780 - Rev 1 page 28/28

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

TCK111G,LF(S FPF1018 DS1222 TCK2065G,LF SZNCP3712ASNT3G MIC2033-05BYMT-T5 MIC2033-12AYMT-T5 MIC2033-05BYM6-T5 SLG5NT1437VTR SZNCP3712ASNT1G NCV330MUTBG DML1008LDS-7 KTS1670EDA-TR KTS1640QGDV-TR KTS1641QGDV-TR NCV459MNWTBG FPF2260ATMX U6513A MIC2012YM-TR NCP45780IMN24RTWG MAX14919ATP+ MC33882PEP TPS2104DBVR MIC2098-1YMT-TR MIC94062YMT TR MP6231DN-LF MIC2075-2YM MIC94068YML-TR SIP32461DB-T2-GE1 NCP335FCT2G TCK105G,LF(S AP2191DWG-7 AP2151DSG-13 MIC94094YC6-TR MIC94064YC6-TR MIC2505-1YM MIC94305YMT-TR MIC94085YFT-TR MIC94081YFT-TR MIC94042YFL-TR MIC94041YFL-TR MIC2005-1.2YM6-TR TPS2032QDRQ1 SIP32510DT-T1-GE3 NCP333FCT2G BTS3050TFATMA1 NCP331SNT1G TPS2092DR TPS2063DR TPS2042P