### High voltage high and low-side 2 A gate driver

Datasheet - production data

#### **Features**

- Transient withstand voltage 600 V

- dV/dt immunity ± 50 V/ns in full temperature range

- Driver current capability:

- 2 A source typ. at 25 °C

- 2.5 A sink typ. at 25 °C

- Short propagation delay: 85 ns

- Switching times 25 ns rise/fall with 1 nF load

- Integrated bootstrap diode

- Single input and shutdown pin

- Adjustable deadtime

- 3.3 V, 5 V TTL/CMOS inputs with hysteresis

- UVLO on both high-side and low-side sections

- · Compact and simplified layout

- · Bill of material reduction

- Flexible, easy and fast design

### **Applications**

- Motor driver for home appliances, factory automation, industrial drives and fans

- HID ballasts

- Induction heating

- Welding

- Industrial inverters

- UPS

- · Power supply units

- DC-DC converters

#### **Description**

The L6494 is a high-voltage device manufactured with the BCD6 "offline" technology. It is a single chip half-bridge gate driver for N-channel power MOSFETs or IGBTs.

The high-side (floating) section is designed to stand a DC voltage rail up to 500 V, with 600 V transient withstand voltage. The logic inputs are CMOS/TTL compatible down to 3.3 V for easy interfacing control units such as microcontrollers or DSP.

The device is a single input gate driver with programmable deadtime, and also features an active-low shutdown pin.

Both device outputs can sink 2.5 A and source 2 A, making the L6494 particularly suited for medium and high capacity power MOSFETs\IGBTs.

The independent UVLO protection circuits present on both the lower and upper driving sections prevent the power switches from being operated in low efficiency or dangerous conditions.

The integrated bootstrap diode as well as all of the integrated features of this driver make the application PCB design simpler and more compact, and help reducing the overall bill of material. Contents L6494

## **Contents**

| 1  | Block diagram                            | 3 |

|----|------------------------------------------|---|

| 2  | Pin description and connection diagram   | 4 |

| 3  | Electrical data                          | 5 |

|    | 3.1 Absolute maximum ratings             | 5 |

|    | 3.2 Thermal data                         |   |

|    | 3.3 Recommended operating conditions     | 6 |

| 4  | Electrical characteristics               | 7 |

| 5  | Truth table                              | 1 |

| 6  | Typical application diagram 1            | 2 |

| 7  | Bootstrap driver                         | 3 |

|    | C <sub>BOOT</sub> selection and charging | 3 |

| В  | Package information                      | 5 |

|    | 8.1 SO-14 package information            | 5 |

| 9  | Ordering information1                    | 7 |

| 10 | Revision history 1                       | 7 |

L6494 Block diagram

# 1 Block diagram

BOOTSTRAP DIODE BOOT VCC U٧ UV DETECTION DETECTION HVG LEVEL SHIFTER LOGIC HVG DRIVER  $\overline{\mathrm{SD}}$ FLOATING STRUCTURE OUT IN VCC P LVG DRIVER LVG DT PGND DEADTIME SGND AM040065

Figure 1. Block diagram SO-14

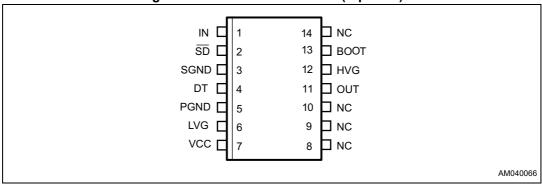

## 2 Pin description and connection diagram

Figure 2. Pin connection SO-14 (top view)

Table 1. Pin description

| Pin no.      | Pin name           | Туре | Function                                                                              |  |

|--------------|--------------------|------|---------------------------------------------------------------------------------------|--|

| 1            | IN                 | 1    | Output drivers logic input (is in phase with HVG and in opposition of phase with LVG) |  |

| 2            | SD                 | -    | Shutdown logic input (active-low)                                                     |  |

| 4            | DT                 | I    | Deadtime setting                                                                      |  |

| 6            | LVG <sup>(1)</sup> | 0    | Low-side driver output                                                                |  |

| 7            | VCC                | Р    | Low-side section supply voltage                                                       |  |

| 11           | OUT                | Р    | High-side (floating) section common voltage                                           |  |

| 12           | HVG <sup>(1)</sup> | 0    | High-side driver output                                                               |  |

| 13           | BOOT               | Р    | High-side (bootstrapped) section supply voltage                                       |  |

| 3            | SGND               | Р    | Signal ground                                                                         |  |

| 5            | PGND               | Р    | Power ground                                                                          |  |

| 8, 9, 10, 14 | NC                 | -    | Not connected                                                                         |  |

The circuit guarantees less than 1 V on the LVG and HVG pins (at I<sub>sink</sub> = 10 mA), with V<sub>CC</sub> > 3 V. This

allows omitting the "bleeder" resistor connected between the gate and the source of the external MOSFET

normally used to hold the pin low.

L6494 Electrical data

## 3 Electrical data

### 3.1 Absolute maximum ratings

Table 2. Absolute maximum ratings<sup>(1)</sup>

| Cymhal                | Parameter                                                    | Va                     | lue                     | Unit |  |

|-----------------------|--------------------------------------------------------------|------------------------|-------------------------|------|--|

| Symbol                | Parameter                                                    | Min. Max.              |                         | Oint |  |

| V <sub>CC</sub>       | Supply voltage                                               | -0.3                   | 21                      | V    |  |

| V <sub>PGND</sub>     | Low-side driver ground                                       | V <sub>CC</sub> - 21   | V <sub>CC</sub> + 0.3   | V    |  |

| V <sub>OUT</sub>      | Output voltage                                               | V <sub>BOOT</sub> - 21 | V <sub>BOOT</sub> + 0.3 | V    |  |

| V                     | Boot DC voltage                                              | -0.3                   | 500                     | V    |  |

| V <sub>BOOT</sub>     | Boot transient withstand voltage (T <sub>pulse</sub> < 1 ms) | -                      | 620                     | V    |  |

| V <sub>hvg</sub>      | High-side gate output voltage                                | V <sub>OUT</sub> - 0.3 | V <sub>BOOT</sub> + 0.3 | V    |  |

| V <sub>Ivg</sub>      | Low-side gate output voltage                                 | PGND - 0.3             | V <sub>CC</sub> + 0.3   | V    |  |

| V <sub>i</sub>        | Logic input pins voltage                                     | -0.3                   | 15                      | V    |  |

| dV <sub>OUT</sub> /dt | Allowed output slew rate                                     | -                      | 50                      | V/ns |  |

| P <sub>TOT</sub>      | Total power dissipation (T <sub>A</sub> = 25 °C) SO-14       | -                      | 1                       | W    |  |

| T <sub>J</sub>        | Junction temperature                                         | -                      | 150                     | °C   |  |

| T <sub>stg</sub>      | Storage temperature                                          | -50                    | 150                     | °C   |  |

| ESD                   | Human body model                                             | 2                      | kV                      | -    |  |

<sup>1.</sup> Each voltage referred to SGND unless otherwise specified.

#### 3.2 Thermal data

Table 3. Thermal data

| Symbol              | mbol Parameter                         |       | Value | Unit |

|---------------------|----------------------------------------|-------|-------|------|

| R <sub>th(JA)</sub> | Thermal resistance junction to ambient | SO-14 | 120   | °C/W |

Electrical data L6494

## 3.3 Recommended operating conditions

Table 4. Recommended operating conditions

| Symbol                         | Pin Parameter                        |                                 | Test condition                      | Min. | Max. | Unit |

|--------------------------------|--------------------------------------|---------------------------------|-------------------------------------|------|------|------|

| $V_{CC}$                       | VCC                                  | Supply voltage                  | -                                   | 10   | 20   | V    |

| V <sub>PS</sub> <sup>(1)</sup> | SGND - PGND                          | Low-side driver ground          | -                                   | -5   | +5   | ٧    |

| V <sub>BO</sub> <sup>(2)</sup> | BOOT - OUT                           | Floating supply voltage         | -                                   | 9.3  | 20   | ٧    |

|                                | OUT DC voltage                       | -                               | - 9 <sup>(3)</sup>                  | 480  | V    |      |

| V <sub>OUT</sub>               | OUT                                  | OUT transient withstand voltage | T <sub>pulse</sub> < 1 ms           | -    | 600  | ٧    |

| f <sub>SW</sub>                | -                                    | Maximum switching frequency     | HVG, LVG load C <sub>L</sub> = 1 nF | ı    | 800  | kHz  |

| $T_J$                          | -                                    | Junction temperature            | -                                   | -40  | 125  | °C   |

| T <sub>A</sub>                 | - Ambient temperature <sup>(4)</sup> |                                 | -                                   | -40  | 125  | °C   |

<sup>1.</sup>  $V_{PS} = V_{PGND} - SGND$ .

<sup>2.</sup>  $V_{BO} = V_{BOOT} - V_{OUT}$ .

<sup>3.</sup> LVG off.  $V_{CC}$  = 12.5 V. Logic is operational if  $V_{BOOT}$  > 5 V.

<sup>4.</sup> Maximum ambient temperature is actually limited by  $T_{\rm J}$ .

## 4 Electrical characteristics

Table 5. Electrical characteristics ( $V_{CC}$  = 15 V;  $T_J$  = +25 °C; PGND = SGND)

| Symbol                | Pin                     | Parameter Parameter                            | Test condition                                      | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------------|------------------------------------------------|-----------------------------------------------------|------|------|------|------|

| Low-side s            | Low-side section supply |                                                |                                                     |      |      |      |      |

| V <sub>CC_hys</sub>   |                         | V <sub>CC</sub> UV hysteresis                  | -                                                   | 0.5  | 0.6  | 0.72 | V    |

| V <sub>CC_thON</sub>  |                         | V <sub>CC</sub> UV turn ON threshold           | -                                                   | 8.7  | 9.3  | 9.8  | V    |

| V <sub>CC_thOFF</sub> | VCC vs.                 | V <sub>CC</sub> UV turn OFF threshold          | -                                                   | 8.2  | 8.7  | 9.2  | V    |

| I <sub>QCCU</sub>     | SGND                    | Undervoltage quiescent supply current          | $V_{CC} = \overline{SD} = 7 \text{ V}$<br>IN = SGND | -    | 135  | 200  | μА   |

| I <sub>QCC</sub>      |                         | Quiescent current                              | $V_{CC}$ = 15 V<br>$\overline{SD}$ = 5 V; IN = SGND | -    | 490  | 700  | μА   |

| High-side f           | loating sec             | tion supply <sup>(1)</sup>                     |                                                     |      |      |      |      |

| V <sub>BO_hys</sub>   |                         | V <sub>BO</sub> UV hysteresis                  | -                                                   | 0.48 | 0.6  | 0.7  | V    |

| V <sub>BO_thON</sub>  |                         | V <sub>BO</sub> UV turn ON threshold           | -                                                   | 8.0  | 8.6  | 9.1  | V    |

| V <sub>BO_thOFF</sub> |                         | V <sub>BO</sub> UV turn OFF threshold          | -                                                   | 7.5  | 8.0  | 8.5  | V    |

| I <sub>QBOU</sub>     | BOOT vs.<br>OUT         | Undervoltage V <sub>BO</sub> quiescent current | $V_{BO} = \overline{SD} = 7 \text{ V}$<br>IN = SGND | -    | 20   | 30   | μА   |

| I <sub>QBO</sub>      | 001                     | V <sub>BO</sub> quiescent current              | VBO = 15 V<br>SD = IN = 5 V                         | -    | 90   | 120  | μА   |

| I <sub>LK</sub>       |                         | High-voltage leakage current                   | $V_{hvg} = V_{out} = V_{boot} = 600 V$              | -    | -    | 8    | μА   |

| R <sub>DS(on)</sub>   |                         | Bootstrap diode on-resistance <sup>(2)</sup>   | -                                                   | -    | 175  | -    | Ω    |

| Output driv           | ing buffers             |                                                | •                                                   |      |      |      |      |

| I <sub>SO</sub>       |                         | High/low-side source short-circuit current     | LVG/HVG ON<br>T <sub>J</sub> = 25 °C                | 1.6  | 2    | -    | Α    |

|                       | IVC HVC                 | Current                                        | Full temperature range <sup>(3)</sup>               | 1.25 | -    | -    | Α    |

| I <sub>SI</sub>       | LVG, HVG                | High/low-side sink short-circuit               | LVG/HVG ON<br>T <sub>J</sub> = 25 °C                | 2    | 2.5  | -    | Α    |

| O.                    |                         | current                                        | Full temperature range <sup>(3)</sup>               | 1.55 | -    | -    | Α    |

| Logic inputs          |                         |                                                |                                                     |      |      |      |      |

| V <sub>il</sub>       | IN, SD vs.              | Low level logic threshold voltage              | -                                                   | 0.95 | -    | 1.45 | V    |

| V <sub>ih</sub>       | SGND                    | High level logic threshold voltage             | -                                                   | 2    | -    | 2.5  | V    |

| I <sub>INh</sub>      | IN vs.                  | IN logic "1" input bias current                | IN = 15 V                                           | 120  | 200  | 260  | μА   |

| I <sub>INI</sub>      | SGND                    | IN logic "0" input bias current                | IN = 0 V                                            | -    | -    | 1    | μА   |

| I <sub>SDh</sub>      | SD vs.                  | SD logic "1" input bias current                | SD = 15 V                                           | -    | -    | 1    | μА   |

| I <sub>SDI</sub>      | SGND                    | SD logic "0" input bias current                | <u>SD</u> = 0 V                                     | 14   | 17   | 23   | μА   |

Electrical characteristics L6494

Table 5. Electrical characteristics ( $V_{CC}$  = 15 V;  $T_J$  = +25 °C; PGND = SGND) (continued)

| Symbol             | Pin                                     | Parameter                                            | Test condition                                                                                               | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|

| R <sub>PU_SD</sub> | SD vs.<br>SGND                          | SD pull-up resistor                                  | -                                                                                                            | 185  | 250  | 310  | kΩ   |

| R <sub>PD_IN</sub> | IN vs.<br>SGND                          | IN pull-down resistor                                | -                                                                                                            | 58   | 75   | 125  | kΩ   |

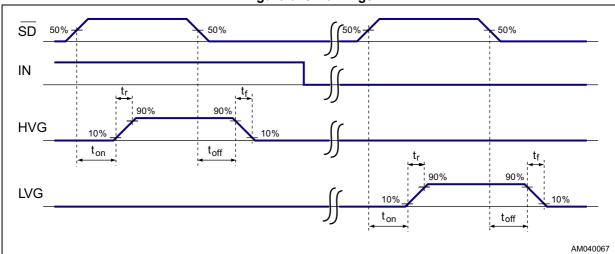

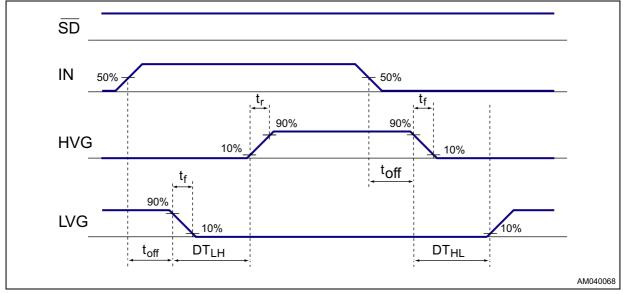

| Dynamic c          | haracteristi                            | cs (see Figure 3 and Figure 4)                       |                                                                                                              |      |      |      |      |

| t <sub>on</sub>    | SD vs.<br>LVG/HVG                       | High/low-side driver turn-on propagation delay       |                                                                                                              | -    | 85   | 120  | ns   |

| t <sub>off</sub>   | SD vs.<br>LVG/HVG;<br>IN vs.<br>LVG/HVG | High/low-side driver turn-off propagation delay      | $V_{OUT} = 0 \text{ V; } V_{BOOT} = V_{CC};$<br>$C_{L} = 1 \text{ nF; } V_{i} = 0 \text{ to } 3.3 \text{ V}$ | -    | 85   | 120  | ns   |

| MT                 | -                                       | Delay matching, HS and LS turn-on/off <sup>(4)</sup> | -                                                                                                            | -    | -    | 30   | ns   |

| t <sub>r</sub>     | LVG, HVG                                | Rise time                                            | C <sub>L</sub> = 1 nF                                                                                        | -    | 25   | -    | ns   |

| t <sub>f</sub>     | LVG, HVG                                | Fall time                                            | C <sub>L</sub> = 1 nF                                                                                        | -    | 25   | -    | ns   |

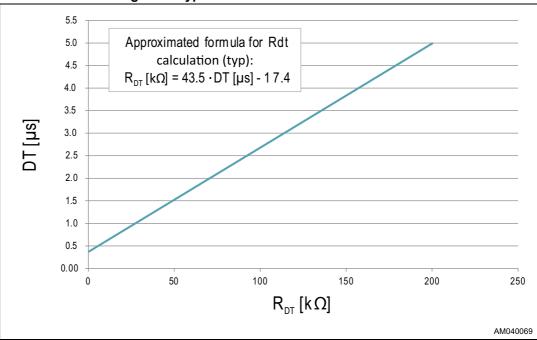

|                    |                                         |                                                      | $R_{DT} = 0 \Omega$ , $C_L = 1 nF$ ,                                                                         | 0.26 | 0.40 | 0.54 | μS   |

| DT                 | -                                       | Deadtime setting range <sup>(5)</sup>                | $R_{DT}$ = 100 k $\Omega$ , $C_L$ = 1 nF, $C_{DT}$ = 100 nF                                                  | 2.10 | 2.70 | 3.30 | μS   |

|                    |                                         |                                                      | $R_{DT}$ = 200 k $\Omega$ , $C_L$ = 1 nF, $C_{DT}$ = 100 nF                                                  | 4.00 | 5.00 | 6.00 | μS   |

|                    |                                         |                                                      | $R_{DT} = 0 \Omega$ , $C_L = 1 nF$ ,                                                                         | -    | -    | 85   | ns   |

| MDT                | -                                       | Matching deadtime <sup>(5)</sup>                     | $R_{DT}$ = 100 k $\Omega$ , $C_L$ = 1 nF, $C_{DT}$ = 100 nF                                                  | -    | -    | 350  | ns   |

|                    |                                         |                                                      | $R_{DT}$ = 200 k $\Omega$ , $C_L$ = 1 nF, $C_{DT}$ = 100 nF                                                  | -    | -    | 700  | ns   |

<sup>1.</sup>  $V_{BO} = V_{BOOT} - V_{OUT}$

$\mathsf{R}_{\mathsf{DSON}} = \left[ \left( \mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{BOOT1}} \right) - \left( \mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{BOOT2}} \right) \right] / \left[ \mathsf{I}_{1} \left( \mathsf{V}_{\mathsf{CC}}, \mathsf{V}_{\mathsf{BOOT1}} \right) - \mathsf{I}_{2} \left( \mathsf{V}_{\mathsf{CC}}, \mathsf{V}_{\mathsf{BOOT2}} \right) \right]$

where  $I_1$  is the BOOT pin current when  $V_{BOOT} = V_{BOOT1}$ ,  $I_2$  when  $V_{BOOT} = V_{BOOT2}$ .

- 3. Characterized, not tested in production.

- 4.  $MT = max. (|t_{on} (LVG) t_{off} (LVG)|, |t_{on} (HVG) t_{off} (HVG)|, |t_{off} (LVG) t_{on} (HVG)|, |t_{off} (HVG) t_{on} (LVG)|).$

- 5. MDT =  $|DT_{LH} DT_{HL}|$  see *Figure 4*.

<sup>2.</sup>  $R_{DSON}$  is tested in the following way:

Figure 3. SD timings

Figure 4. IN timings and deadtime

Electrical characteristics L6494

Figure 5. Typical deadtime vs. DT resistor value

L6494 Truth table

## 5 Truth table

Table 6. Truth table

| Inp   | out              | Out | put |

|-------|------------------|-----|-----|

| SD IN |                  | LVG | HVG |

| L     | X <sup>(1)</sup> | L   | L   |

| Н     | L                | Н   | L   |

| Н     | Н                | L   | Н   |

<sup>1.</sup> X = don't care.

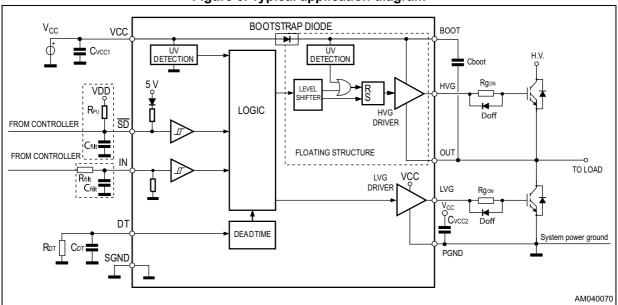

## 6 Typical application diagram

Figure 6. Typical application diagram

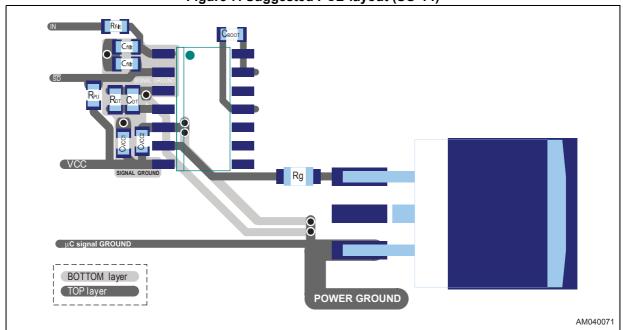

Figure 7. Suggested PCB layout (SO-14)

57

L6494 Bootstrap driver

#### 7 Bootstrap driver

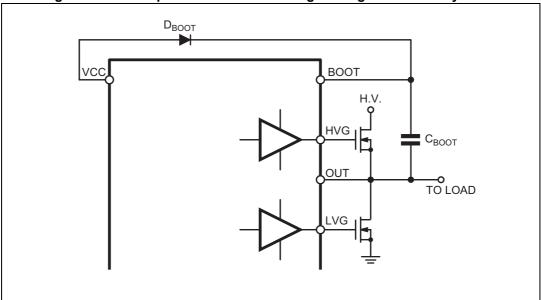

A bootstrap circuitry is needed to supply the high voltage section. This function is usually accomplished by a high voltage fast recovery diode (*Figure 8*). In the L6494 an integrated structure replaces the external diode.

### **C**BOOT selection and charging

To choose the proper  $C_{BOOT}$  value the external MOS can be seen as an equivalent capacitor. This capacitor  $C_{EXT}$  is related to the MOS total gate charge:

#### **Equation 1**

$$C_{EXT} = \frac{Q_{gate}}{V_{gate}}$$

The ratio between the capacitors  $C_{\text{EXT}}$  and  $C_{\text{BOOT}}$  is proportional to the cyclical voltage loss. It has to be:

#### **Equation 2**

$$C_{BOOT} >>> C_{EXT}$$

if  $Q_{qate}$  is 30 nC and  $V_{qate}$  is 10 V,  $C_{EXT}$  is 3 nF. With  $C_{BOOT}$  = 100 nF the drop is 300 mV.

If HVG has to be supplied for a long time, the  $C_{BOOT}$  selection has also to take into account the leakage and quiescent losses.

HVG steady-state consumption is lower than 120  $\mu$ A, so if HVG T<sub>ON</sub> is 5 ms, C<sub>BOOT</sub> has to supply 0.6  $\mu$ C. This charge on a 1  $\mu$ F capacitor means a voltage drop of 0.6 V.

The internal bootstrap driver gives a great advantage: the external fast recovery diode can be avoided (it usually has great leakage current).

This structure can work only if  $V_{OUT}$  is close to SGND (or lower) and in the meanwhile the LVG is on. The charging time ( $T_{charge}$ ) of the  $C_{BOOT}$  is the time in which both conditions are fulfilled and it has to be long enough to charge the capacitor.

The bootstrap driver introduces a voltage drop due to the DMOS  $R_{DS(on)}$  (typical value: 175  $\Omega$ ). At low frequency this drop can be neglected. Anyway, the rise of frequency has to take into account.

The following equation is useful to compute the drop on the bootstrap DMOS:

#### **Equation 3**

$$V_{drop} = I_{charge}R_{DS(on)} \rightarrow V_{drop} = \frac{Q_{gate}}{T_{charge}}R_{DS(on)}$$

where  $Q_{gate}$  is the gate charge of the external power MOS,  $R_{DS(on)}$  is the on resistance of the bootstrap DMOS and  $T_{charge}$  is the charging time of the bootstrap capacitor.

Bootstrap driver L6494

For example: using a power MOS with a total gate charge of 30 nC the drop on the bootstrap DMOS is about 1 V, if the  $T_{charge}$  is 5  $\mu s$ . In fact:

#### **Equation 4**

$$V_{drop} = \frac{30nC}{5\mu s} \cdot 175\Omega \sim 1V$$

$V_{drop}$  has to be taken into account when the voltage drop on  $C_{BOOT}$  is calculated: if this drop is too high, or the circuit topology doesn't allow a sufficient charging time, an external diode can be used.

Figure 8. Bootstrap driver with external high voltage fast recovery diode

14/18 DocID030317 Rev 2

L6494 Package information

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

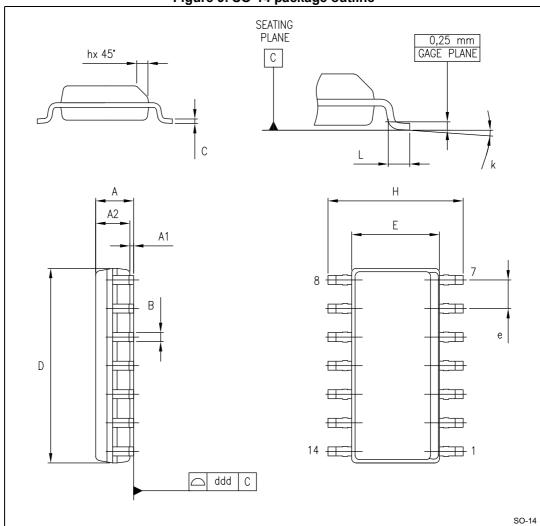

### 8.1 SO-14 package information

Figure 9. SO-14 package outline

Package information L6494

Table 7. SO-14 package mechanical data

| Symbol |      | Dimensions (mm) |      |  |  |  |

|--------|------|-----------------|------|--|--|--|

| Symbol | Min. | Тур.            | Max. |  |  |  |

| Α      | 1.35 | -               | 1.75 |  |  |  |

| A1     | 0.10 | -               | 0.25 |  |  |  |

| A2     | 1.10 | -               | 1.65 |  |  |  |

| В      | 0.33 | -               | 0.51 |  |  |  |

| С      | 0.19 | -               | 0.25 |  |  |  |

| D      | 8.55 | -               | 8.75 |  |  |  |

| E      | 3.80 | -               | 4.00 |  |  |  |

| е      | -    | 1.27            | -    |  |  |  |

| Н      | 5.80 | -               | 6.20 |  |  |  |

| h      | 0    | -               | -    |  |  |  |

| 25     | -    | 0.50            | -    |  |  |  |

| L      | 0.40 | -               | 1.27 |  |  |  |

| k      | 0    | -               | 8    |  |  |  |

| ddd    | -    | -               | 0.10 |  |  |  |

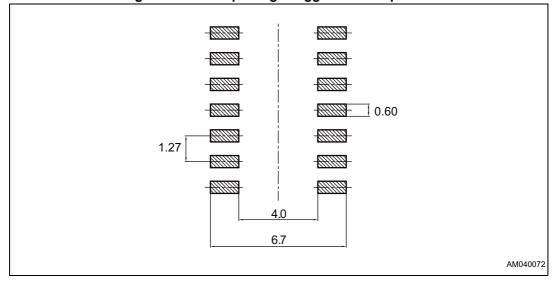

Figure 10. SO-14 package suggested land pattern

# 9 Ordering information

**Table 8. Device summary**

| Order code | Package | Packaging     |

|------------|---------|---------------|

| L6494LD    | SO-14   | Tube          |

| L6494LDTR  | SO-14   | Tape and reel |

# 10 Revision history

**Table 9. Document revision history**

| Date        | Revision | Changes                                                                          |

|-------------|----------|----------------------------------------------------------------------------------|

| 08-Feb-2017 | 1        | Initial release.                                                                 |

| 14-Nov-2017 | 2        | Updated Section: Description on page 1, Table 4 on page 6 and Table 5 on page 7. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

00053P0231 56956 57.404.7355.5 LT4936 57.904.0755.0 5882900001 00600P0005 00-9050-LRPP 00-9090-RDPP 5951900000 011003W-10/32-15 0131700000 00-2240 LTP70N06 LVP640 5J0-1000LG-SIL LY1D-2-5S-AC120 LY2-US-AC240 LY3-UA-DC24

00576P0020 00600P0010 LZN4-UA-DC12 LZNQ2M-US-DC5 LZNQ2-US-DC12 LZP40N10 00-8196-RDPP 00-8274-RDPP 00-8275RDNP 00-8722-RDPP 00-8728-WHPP 00-8869-RDPP 00-9051-RDPP 00-9091-LRPP 00-9291-RDPP 0207100000 0207400000 01312

0134220000 60713816 M15730061 61161-90 61278-0020 6131-204-23149P 6131-205-17149P 6131-209-15149P 6131-218-17149P 6131220-21149P 6131-260-2358P 6131-265-11149P CS1HCPU63