## 1.5 A low-dropout linear regulator with programmable soft-start

#### **Features**

- AEC-Q100 qualified

- · Dual supply pins

- V<sub>IN</sub>: 0.8 V to 5.5 V

- V<sub>BIAS</sub>: 2.7 V to 5.5 V

- V<sub>OUT</sub> range: 0.8 V to 3.6 V

- Ultra low-dropout: 65 mV typ. (125 mV max.) at 1.5 A

- High V<sub>OUT</sub> accuracy

- 0.5% typ. at T<sub>amb</sub>

- 2% max.

- · Power Good function

- · Programmable soft-start

- · Thermal shutdown

- · Current limitation circuit

- Adjustable output voltage

- Stable with low ESR output capacitor (> 2.2 μF)

- DFN10 (3x3) mm package with wettable flanks

- Operating temperature range: 40 °C + 125 °C

### **Maturity status link**

LD59150

### **Applications**

- Automotive and industrial post regulation

- · Generic POL

- Automotive and industrial ASICs and FPGA supply

- · Telecom infrastructure

- · A.D.A.S. (advanced driver-assistance systems)

### **Description**

The LD59150 is a 1.5 A LDO regulator, designed to be used in several environments.

Two versions, Industrial and AEC-Q100 are available.

NMOS topology allows  $R_{DS(on)}$  of the pass-element to be reduced, which results in a very small dropout voltage even with a very low input supply voltage.

Output voltage can be adjusted from 0.8 to 3.6 V, by an external resistor divider.

The programmable soft-start circuit offers the possibility to control the inrush current at start-up providing a monotonic supply voltage to the load.

The LD59150 has enable pin to turn on/off (EN) the regulator and Power Good to monitor the regulated output voltage (PG).

The combination of both can be used to set a desired power sequence in case of multiple regulated rails.

The LD59150 embeds protection functions, such as: current limit and thermal shutdown.

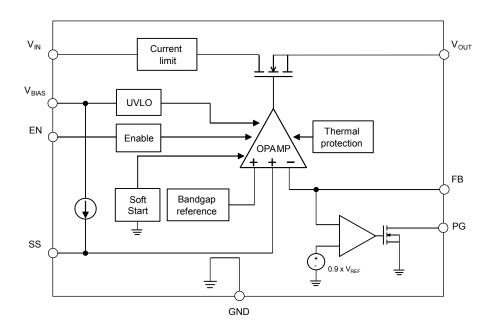

# 1 Diagram

Figure 1. Block diagram

DS12455 - Rev 5 page 2/22

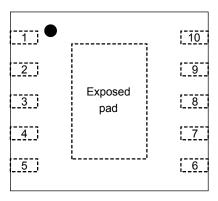

# 2 Pin configuration

Figure 2. Pin connection (top view)

DFN10 - 3 x 3

Table 1. Pin description

| Pin n°      | Symbol            | Function                      |  |

|-------------|-------------------|-------------------------------|--|

| 1, 2        | V <sub>IN</sub>   | Input pin                     |  |

| 3           | PG                | Power Good                    |  |

| 4           | V <sub>BIAS</sub> | Bias supply pin               |  |

|             |                   | Enable pin logic input:       |  |

| 5           | EN                | low = shutdown, high = active |  |

|             |                   | Do not leave floating         |  |

| 6           | GND               | Ground                        |  |

| 7           | SS                | Soft-start                    |  |

| 8           | FB                | Feedback pin                  |  |

| 9, 10       | V <sub>OUT</sub>  | Regulated output              |  |

| Exposed pad | Exposed pad       | Must be connected to GND      |  |

DS12455 - Rev 5 page 3/22

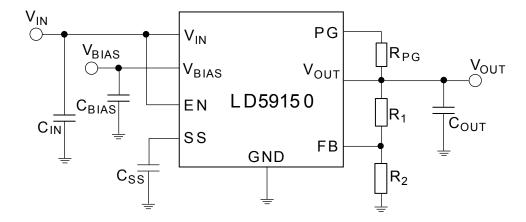

# 3 Typical application

Figure 3. Typical application circuit

DS12455 - Rev 5 page 4/22

## 4 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol            | Parameter                            | Value                          | Unit |

|-------------------|--------------------------------------|--------------------------------|------|

| V <sub>IN</sub>   | Input voltage pin                    | -0.3 to 6                      | V    |

| V <sub>BIAS</sub> | Bias supply pin                      | - 0.3 to 6                     | V    |

| V <sub>OUT</sub>  | DC output voltage                    | -0.3 to V <sub>IN</sub> + 0.3  | V    |

| V <sub>EN</sub>   | Enable input voltage                 | -0.3 to 6                      | V    |

| V <sub>ADJ</sub>  | Adjustable pin voltage               | -0.3 to 6                      | V    |

| V <sub>SS</sub>   | Soft-start pin                       | -0.3 to 6                      | V    |

| V <sub>PG</sub>   | Power Good pin                       | -0.3 to 6                      | V    |

| l <sub>OUT</sub>  | Output current                       | Internally limited             | mA   |

| P <sub>DIS</sub>  | Maximum power dissipation            | Refer to Table 3. Thermal data | W    |

| I <sub>PG</sub>   | Power Good sink current              | 0 to 1.5                       | mA   |

| T <sub>ST</sub>   | Storage temperature range            | -55 to 150                     | °C   |

| TJ                | Operating junction temperature range | -40 to 150                     | °C   |

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All values are referred to GND.

Table 3. Thermal data

| Symbol            | Parameter                           | Value | Unit |

|-------------------|-------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 47.5  | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case    | 8     | °C/W |

Note:

Thermal resistance refers to 4 layer JEDEC PCB (2S2P) test board with thermal vias.

Table 4. ESD data

| Symbol | Parameter            | DFN10 3 x 3 | Unit |

|--------|----------------------|-------------|------|

| HBM    | Human body model     | ± 2000      | V    |

| CDM    | Charged device model | ± 750       | V    |

DS12455 - Rev 5 page 5/22

## **5** Electrical characteristics

$T_J$  = - 40 °C to + 125 °C, typical values refer to  $T_J$  = + 25 °C,  $V_{IN}$  =  $V_{OUT}$  + 0.3 V,  $V_{EN}$  = 1.1 V,  $V_{BIAS}$  = 5 V,  $I_{OUT}$  = 50 mA,  $C_{IN}$  =  $C_{OUT}$  = 10  $\mu$ F,  $C_{BIAS}$  = 0.1  $\mu$ F,  $C_{SS}$  = 1 nF unless otherwise specified.

Table 5. Electrical characteristics

| Symbol                         | Parameter                                                                                                                      | Test conditions                                                                                     | Min.                                    | Тур.                | Max.  | Unit              |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------|-------|-------------------|

| V <sub>IN</sub>                | Operating input voltage                                                                                                        |                                                                                                     | V <sub>OUT</sub> +<br>V <sub>drop</sub> |                     | 5.5   | V                 |

| V <sub>BIAS</sub>              | Bias pin voltage                                                                                                               |                                                                                                     | 2.7                                     |                     | 5.5   | V                 |

| $V_{REF}$                      | Reference voltage                                                                                                              | T = + 25 °C                                                                                         | 0.796                                   | 0.8                 | 0.804 | V                 |

|                                | Range                                                                                                                          | V <sub>IN</sub> = 5.5 V, I <sub>OUT</sub> = 1.5 A                                                   | V <sub>REF</sub>                        |                     | 3.6   | V                 |

| V                              | Accuracy                                                                                                                       | 50 mA < I <sub>OUT</sub> < 1.5 A 2.97 V < V <sub>BIAS</sub> < 5.5 V                                 | -2                                      | ± 0.5               | +2    | %                 |

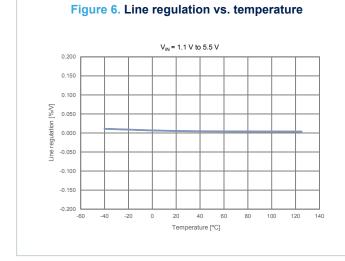

| V <sub>OUT</sub>               | Line regulation                                                                                                                | V <sub>OUT(nom)</sub> + 0.3 V < V <sub>IN</sub> < 5.5 V                                             |                                         | 0.01                |       | %/V               |

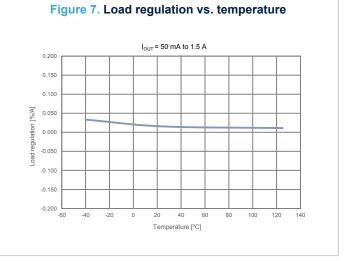

|                                | Load regulation                                                                                                                | 50 mA < I <sub>OUT</sub> < 1.5 A                                                                    |                                         | 0.02                |       | %/A               |

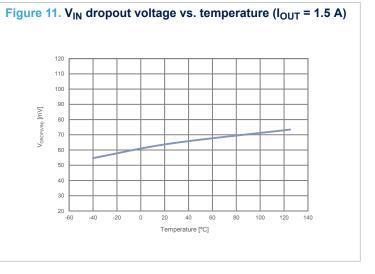

| V (1)                          | V <sub>IN</sub> dropout voltage                                                                                                | I <sub>OUT</sub> = 1.5 A, V <sub>BIAS</sub> - V <sub>OUT</sub> > 3.25 V                             |                                         | 65                  | 125   | mV                |

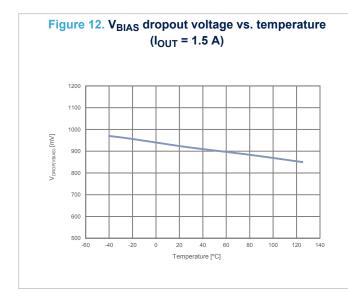

| V <sub>drop</sub> (1)          | V <sub>BIAS</sub> dropout voltage                                                                                              | I <sub>OUT</sub> = 1.5 A V <sub>IN</sub> = V <sub>BIAS</sub>                                        |                                         | 0.92                | 1.1   | V                 |

| I <sub>cl</sub> <sup>(2)</sup> | Current limit                                                                                                                  | V <sub>OUT</sub> = 80% x V <sub>OUT(nom)</sub>                                                      | 2.0                                     | 3                   | 5.5   | Α                 |

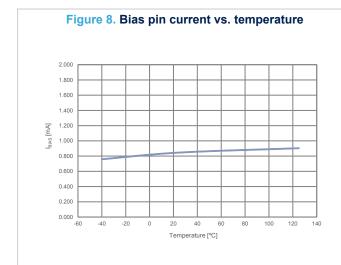

| I <sub>BIAS</sub>              | Bias pin current                                                                                                               |                                                                                                     |                                         | 0.88                | 1.5   | mA                |

| I <sub>SHDN</sub>              | Shutdown supply current                                                                                                        | V <sub>EN</sub> < 0.4 V (measured through GND)                                                      |                                         | 1                   | 50    | μA                |

| I <sub>FB</sub>                | Feedback pin current                                                                                                           |                                                                                                     | -1                                      | 0.001               | +1    | μA                |

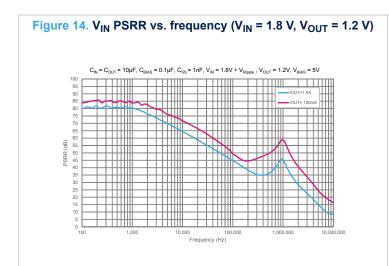

|                                | Power supply rejection (V <sub>IN</sub> to V <sub>OUT</sub> )  Power supply rejection (V <sub>BIAS</sub> to V <sub>OUT</sub> ) | f = 1 kHz, I <sub>OUT</sub> = 1.5 A V <sub>IN</sub> = 1.8 V,<br>V <sub>OUT</sub> = 1.5 V            |                                         | 70                  |       | - dB              |

| DODD                           |                                                                                                                                | $f = 300 \text{ kHz}, I_{OUT} = 1.5 \text{ A V}_{IN} = 1.8 \text{ V},$<br>$V_{OUT} = 1.5 \text{ V}$ |                                         | 30                  |       |                   |

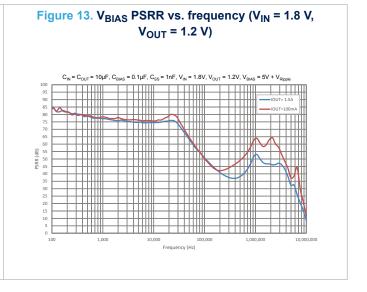

| PSRR                           |                                                                                                                                | $f = 1 \text{ kHz}, I_{OUT} = 1.5 \text{ A V}_{IN} = 1.8 \text{ V},$<br>$V_{OUT} = 1.5 \text{ V}$   |                                         | 75                  |       | 40                |

|                                |                                                                                                                                | $f = 300 \text{ kHz}, I_{OUT} = 1.5 \text{ A V}_{IN} = 1.8 \text{ V},$<br>$V_{OUT} = 1.5 \text{ V}$ |                                         | 40                  |       | - dB              |

| Noise                          | Output noise voltage                                                                                                           | $f$ = 100 Hz to 100 kHz, $I_{OUT}$ = 1.5 A, $C_{SS}$ = 1 nF                                         |                                         | 25xV <sub>OUT</sub> |       | μV <sub>RMS</sub> |

| I <sub>SS</sub>                | Soft-start charging current                                                                                                    | V <sub>SS</sub> = 0.4 V                                                                             |                                         | 0.44                |       | μA                |

| T <sub>str</sub>               | Min. start-up time                                                                                                             | I <sub>OUT</sub> = 1 A, C <sub>SS</sub> = floating                                                  |                                         | 100                 |       | μs                |

| V <sub>EN-H</sub>              | Enable input high                                                                                                              |                                                                                                     | 1.1                                     |                     | 5.5   | V                 |

| V <sub>EN-L</sub>              | Enable input low                                                                                                               |                                                                                                     | 0                                       |                     | 0.4   | V                 |

| V <sub>EN-Hyst</sub>           | Enable hysteresis                                                                                                              |                                                                                                     |                                         | 50                  |       | mV                |

| T <sub>DG</sub>                | Enable deglitch time                                                                                                           |                                                                                                     |                                         | 20                  |       | μs                |

| I <sub>EN</sub>                | Enable pin current                                                                                                             | V <sub>EN</sub> = 5 V                                                                               |                                         | 0.1                 | 1     | μA                |

| V <sub>IT</sub>                | Power Good threshold                                                                                                           | V <sub>OUT</sub> decreasing                                                                         | 85                                      | 90                  | 94    | %V <sub>OUT</sub> |

| V <sub>HYS</sub>               | Power Good hysteresis                                                                                                          |                                                                                                     |                                         | 3                   |       | %V <sub>OUT</sub> |

DS12455 - Rev 5 page 6/22

| Symbol                                       | Parameter                  | Test conditions                                              | Min. | Тур. | Max. | Unit |

|----------------------------------------------|----------------------------|--------------------------------------------------------------|------|------|------|------|

| V <sub>PG-L</sub>                            | Power Good low voltage     |                                                              |      |      | 0.3  | V    |

| I <sub>LK</sub>                              | Power Good leakage         | V <sub>PG</sub> = 5.25 V, V <sub>OUT</sub> > V <sub>IT</sub> |      | 0.1  | 1    | μA   |

| T <sub>SD</sub> Thermal shutdown temperature | High temperature threshold |                                                              | 165  |      | °C   |      |

|                                              | temperature                | Thermal hysteresis                                           |      | 20   |      |      |

<sup>1.</sup> Dropout is defined as the voltage drop when  $V_{\mbox{\scriptsize OUT}}$  is 3% below nominal voltage.

DS12455 - Rev 5 page 7/22

<sup>2.</sup> Maximum value is guaranteed by design and not tested in production.

## 6 Application information

### 6.1 Output voltage setting

The output voltage can be set from 0.8 V ( $V_{REF}$ ) up to the input voltage minus the voltage drop across the pass transistor (dropout voltage), by connecting a resistor divider between the feedback (FB) pin and the output, thus allowing a remote voltage sensing.

With reference to the typical circuit shown in Figure 3, the resistor divider can be designed by the following equation:

$$V_{OUT} = V_{REF} (1 + R_1/R_2)$$

, with  $V_{REF} = 0.8 \text{ V typ.}$

It is recommended to use resistors with values in the range from 5 k $\Omega$  to 100 k $\Omega$ . Lower values can also be suitable, but current consumption increases.

The following table shows some examples of  $R_1$ ,  $R_2$  choices, among standard 1% resistors, to obtain the most common output voltages.

| V <sub>out</sub>       | R <sub>1</sub> | R <sub>2</sub> |

|------------------------|----------------|----------------|

| 0.8 (V <sub>FB</sub> ) | Short          | Open           |

| 0.9                    | 0.619          | 4.99           |

| 1                      | 1.13           | 4.53           |

| 1.05                   | 1.37           | 4.42           |

| 1.1                    | 1.87           | 4.99           |

| 1.2                    | 2.49           | 4.99           |

| 1.5                    | 4.12           | 4.75           |

| 1.8                    | 3.57           | 2.87           |

| 2.5                    | 3.57           | 1.69           |

| 3.3                    | 3.57           | 1.15           |

Table 6. Resistor divider settings for common output voltages

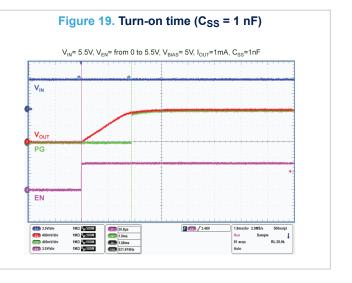

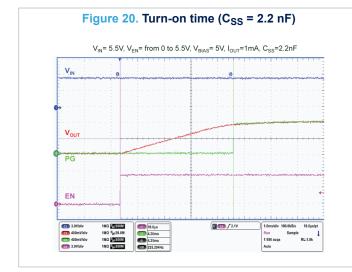

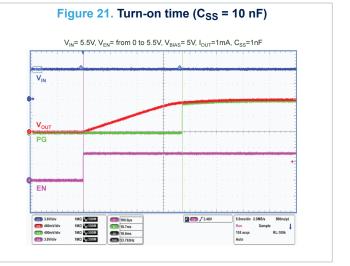

### 6.2 Soft-start time programming

The LD59150 provides a monotonic soft-start feature, which is useful in those applications requiring controlled power-up sequences and low inrush current during the turn-on phase.

The soft-start time, defined as the duration of output voltage ramp, from enable pin assertion to Power Good flag releasing, can be adjusted by the user through an external capacitor (C<sub>SS</sub>).

$C_{SS}$  capacitor is charged with a constant current ( $I_{SS}$ ) and its voltage compared to the internal voltage reference, therefore the soft-start time can be calculated as follows:

$$t_{SS} = (V_{REF} \times C_{SS}) / I_{SS}$$

(1)

with  $V_{REF}$  = 0.8 V typ.,  $I_{SS}$  = 0.44  $\mu A$  typ.

To achieve a good quality, low leakage ceramic capacitors are recommended for C<sub>SS</sub>.

#### 6.3 Power Good

Power Good function provides a flag showing that the output voltage is in the correct range. Power Good signal is available on the PG open-drain pin.

A partition of the output voltage (via the output resistor divider), is sensed on the feedback pin.

When the output voltage surpasses  $V_{IT}$  +  $V_{HYS}$ , Power Good pin is set to high impedance. When  $V_{OUT}$  falls below  $V_{IT}$ , the Power Good pin is pulled low.

If the device is disabled (EN pin low), the PG signal is set to low state.

DS12455 - Rev 5 page 8/22

Power Good function requires an external pull-up resistor, which may be connected to any potential lower than 5.5 V. PG pin typical current capability is up to 1 mA, so it is advisable to choose a pull-up resistor in the range from 10 k $\Omega$  to 1 M $\Omega$ . If Power Good function is not used, PG pin has to remain floating.

#### 6.4 Protection features

#### **Current limit**

The LD59150 embeds a constant-current limit circuit, which acts in case of overload or short-circuit on the output, clamping the load current to a safe value (typ. 3 A).

Normal operation is restored if the overload disappears, but prolonged operation in current limit may lead to high power dissipation inside the LDO and therefore to thermal shutdown.

#### Thermal potection

An internal thermal feedback loop disables the output voltage if the die temperature reaches approximately 165 °C. This feature protects the device from an excessive temperature that could lead to a permanent damage of the LDO.

Once the thermal protection is triggered and the device is shut down, normal operation is automatically recovered if the die temperature falls below 145  $^{\circ}$ C (thermal protection hysteresis of 20  $^{\circ}$ C typically).

Current and thermal limit protections are designed to protect the LDO from an excessive power dissipation and not intended to replace a proper thermal and electrical design of the application. Continuous operation above the maximum ratings may lead to permanent damage of the device.

### 6.5 Power dissipation

An accurate PCB design is recommended, to ensure that the device internal junction temperature is kept below 150 °C, in all the operating conditions. The thermal energy generated by the device flows from the die surface to the PCB copper area through the package leads.

The PCB copper area acts as a heat sink. The footprint copper pads should be as wide as possible to spread and dissipate the heat to the surrounding environment. Thermal micro-vias to the inner or backside copper layers improve the overall thermal performance of the device.

The power dissipation of the LDO depends on the input voltage, output voltage and output current and is given by:

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT}$$

(2)

The junction temperature of the device is:

$$T_{J\_MAX} = T_A + R_{thJA} \times P_D \tag{3}$$

where:  $T_{J\_MAX}$  is the maximum allowable junction temperature of the die, 150 °C;  $T_A$  is the ambient temperature;  $R_{thJA}$  is the thermal resistance junction-to-ambient.

With the above equation it is possible to calculate the maximum allowable power dissipation, therefore the maximum load current for a certain voltage drop. Appropriate de-rating of the operating conditions should be applied accordingly.

DS12455 - Rev 5 page 9/22

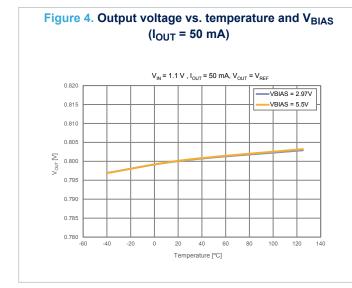

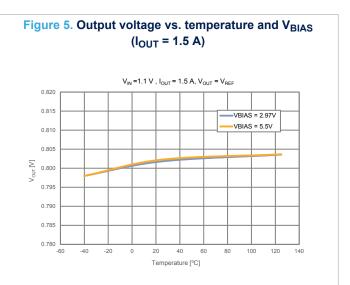

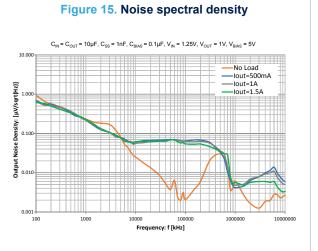

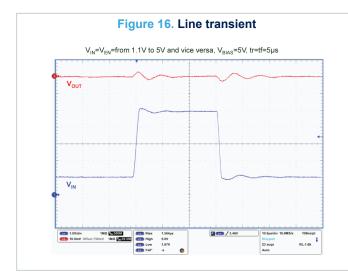

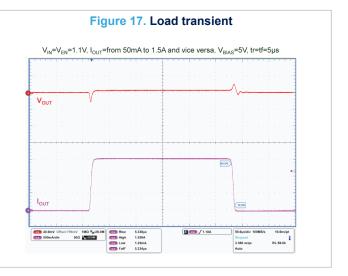

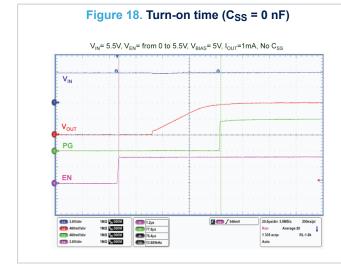

# 7 Typical performance characteristics

$T_J$  = 25 °C,  $V_{IN}$  =  $V_{OUT}$  + 0.3 V,  $V_{BIAS}$  = 5 V,  $V_{OUT}$  =  $V_{REF},$   $V_{EN}$  = 1.1 V,  $I_{OUT}$  = 50 mA,  $C_{IN}$  =  $C_{OUT}$  = 10  $\mu F$ ,  $C_{BIAS}$  = 0.1  $\mu F$ ,  $C_{SS}$  = 1 nF unless otherwise specified.

DS12455 - Rev 5 page 10/22

9. Soft-start charging current vs. temperature

0.800

0.700

0.600

0.500

0.300

0.200

0.100

0.000

0.60

0.40

0.20

0.200

0.100

Temperature [°C]

Figure 10. Current limit vs. temperature

DS12455 - Rev 5 page 11/22

DS12455 - Rev 5 page 12/22

DS12455 - Rev 5 page 13/22

#### **Package information** 8

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

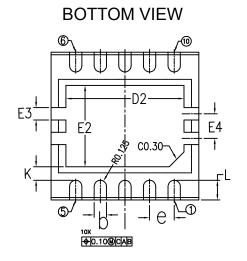

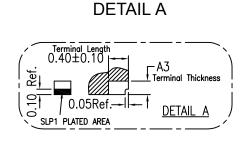

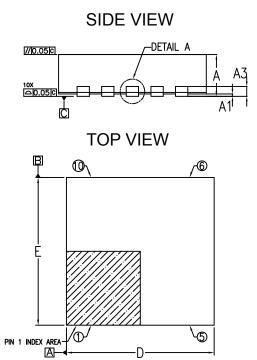

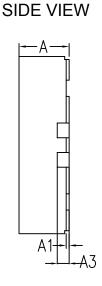

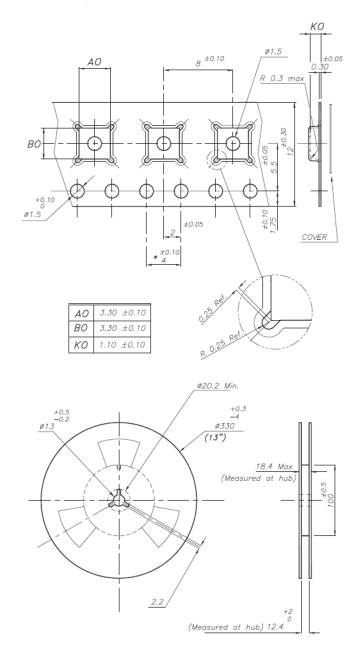

#### DFN10 (3x3 mm) package information 8.1

Figure 22. DFN10 (3x3 mm) package outline

-D

DS12455 - Rev 5 page 14/22

Table 7. DFN10 (3x3 mm) mechanical data

| Dim  | mm   |            |      |  |  |

|------|------|------------|------|--|--|

| Dim. | Min. | Тур.       | Max. |  |  |

| А    | 0.80 | 0.85       | 0.90 |  |  |

| A1   | 0.00 |            | 0.05 |  |  |

| A3   |      | 0.203 Ref. |      |  |  |

| b    | 0.20 | 0.25       | 0.30 |  |  |

| D    | 2.95 | 3.00       | 3.05 |  |  |

| D2   | 2.30 | 2.40       | 2.50 |  |  |

| е    |      | 0.50 BSC   |      |  |  |

| E    | 2.95 | 3.00       | 3.05 |  |  |

| E2   | 1.55 | 1.65       | 1.75 |  |  |

| E3   |      | 0.25 Ref.  |      |  |  |

| E4   |      | 0.50 Ref.  |      |  |  |

| L    | 0.30 | 0.40       | 0.50 |  |  |

| K    |      | 0.275 Ref. |      |  |  |

| N    |      | 10         |      |  |  |

| aaa  | 0.15 |            |      |  |  |

| bbb  | 0.10 |            |      |  |  |

| ccc  | 0.10 |            |      |  |  |

| ddd  | 0.05 |            |      |  |  |

| eee  | 0.08 |            |      |  |  |

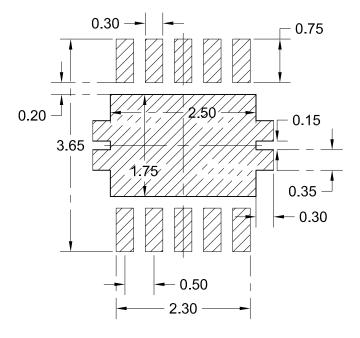

Figure 23. DFN10 (3x3 mm) recommended footprint

DS12455 - Rev 5 page 15/22

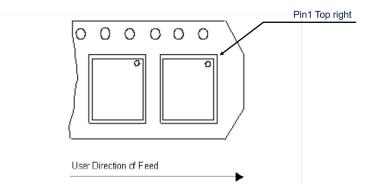

Figure 24. DFN10 (3x3 mm) tape and reel

Figure 25. DFN10 (3x3 mm) reel oriented

DS12455 - Rev 5 page 16/22

# 9 Ordering information

Table 8. Order codes

| Order code |             | Marking | Output voltage |

|------------|-------------|---------|----------------|

| Automotive | LD59150PURY | 595A    | Adjustable     |

| Industrial | LD59150PUR  | 5951    | Aujustable     |

DS12455 - Rev 5 page 17/22

## **Revision history**

Table 9. Document revision history

| Date        | Revision | Changes                                                                                                              |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------|

| 06-Mar-2018 | 1        | Initial release.                                                                                                     |

| 15-May-2018 | 2        | Updated marking in the device summary on the cover page.                                                             |

| 22-Jun-2018 | 3        | Added footnote I <sub>CL</sub> in Table 5. Electrical characteristics.  Minor text change in Section 6.3 Power Good. |

| 16-Apr-2020 | 4        | Updated the cover page and minor text changes.                                                                       |

| 11-Nov-2020 | 5        | Added new LD59150PUR order code in Section 9 Ordering information and new Figure 25. DFN10 (3x3 mm) reel oriented.   |

DS12455 - Rev 5 page 18/22

## **Contents**

| 1   | Diag            | yram                               | 2  |  |  |  |

|-----|-----------------|------------------------------------|----|--|--|--|

| 2   |                 | configuration                      |    |  |  |  |

| 3   |                 | cal application                    |    |  |  |  |

| 4   | Maximum ratings |                                    |    |  |  |  |

| 5   |                 | trical characteristics             |    |  |  |  |

| 6   | Арр             | lication information               | 8  |  |  |  |

|     | 6.1             | Output voltage setting             | 8  |  |  |  |

|     | 6.2             | Soft-start time programming        | 8  |  |  |  |

|     | 6.3             | Power Good                         | 8  |  |  |  |

|     | 6.4             | Protection features                | 9  |  |  |  |

|     | 6.5             | Power dissipation                  | 9  |  |  |  |

| 7   | Турі            | cal performance characteristics    | 10 |  |  |  |

| 8   | Pac             | kage information                   | 14 |  |  |  |

|     | 8.1             | DFN10 (3x3 mm) package information | 14 |  |  |  |

| 9   | Ord             | ering information                  | 17 |  |  |  |

| Rev | ision           | history                            | 18 |  |  |  |

## **List of tables**

| Table 1. | Pin description                                      | 3  |

|----------|------------------------------------------------------|----|

| Table 2. | Absolute maximum ratings                             | 5  |

| Table 3. | Thermal data                                         | 5  |

| Table 4. | ESD data                                             | 5  |

| Table 5. | Electrical characteristics                           | 6  |

| Table 6. | Resistor divider settings for common output voltages | 8  |

| Table 7. | DFN10 (3x3 mm) mechanical data                       | 15 |

|          | Order codes                                          |    |

| Table 9. | Document revision history                            | 18 |

# **List of figures**

| Figure 1.  | Block diagram                                                                            | 2    |

|------------|------------------------------------------------------------------------------------------|------|

| Figure 2.  | Pin connection (top view)                                                                | 3    |

| Figure 3.  | Typical application circuit                                                              | . 4  |

| Figure 4.  | Output voltage vs. temperature and V <sub>BIAS</sub> (I <sub>OUT</sub> = 50 mA)          | . 10 |

| Figure 5.  | Output voltage vs. temperature and V <sub>BIAS</sub> (I <sub>OUT</sub> = 1.5 A)          | . 10 |

| Figure 6.  | Line regulation vs. temperature                                                          | . 10 |

| Figure 7.  | Load regulation vs. temperature                                                          | . 10 |

| Figure 8.  | Bias pin current vs. temperature                                                         | . 11 |

| Figure 9.  | Soft-start charging current vs. temperature                                              | . 11 |

| Figure 10. | Current limit vs. temperature                                                            | . 11 |

| Figure 11. | V <sub>IN</sub> dropout voltage vs. temperature (I <sub>OUT</sub> = 1.5 A)               | . 11 |

| Figure 12. | V <sub>BIAS</sub> dropout voltage vs. temperature (I <sub>OUT</sub> = 1.5 A)             | . 11 |

| Figure 13. | V <sub>BIAS</sub> PSRR vs. frequency (V <sub>IN</sub> = 1.8 V, V <sub>OUT</sub> = 1.2 V) | . 11 |

| Figure 14. | V <sub>IN</sub> PSRR vs. frequency (V <sub>IN</sub> = 1.8 V, V <sub>OUT</sub> = 1.2 V)   | . 12 |

| Figure 15. | Noise spectral density                                                                   | . 12 |

| Figure 16. | Line transient                                                                           | . 12 |

| Figure 17. | Load transient                                                                           | . 12 |

| Figure 18. | Turn-on time ( $C_{SS} = 0 \text{ nF}$ )                                                 | . 12 |

| Figure 19. | Turn-on time (C <sub>SS</sub> = 1 nF)                                                    | . 12 |

| Figure 20. | Turn-on time ( $C_{SS} = 2.2 \text{ nF}$ )                                               | . 13 |

| Figure 21. | Turn-on time (C <sub>SS</sub> = 10 nF)                                                   | . 13 |

| Figure 22. | DFN10 (3x3 mm) package outline                                                           | . 14 |

| Figure 23. | DFN10 (3x3 mm) recommended footprint                                                     | . 15 |

| Figure 24. | DFN10 (3x3 mm) tape and reel                                                             | . 16 |

| Figure 25. | DFN10 (3x3 mm) reel oriented                                                             | . 16 |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics - All rights reserved

DS12455 - Rev 5 page 22/22

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

AP7363-SP-13 L79M05TL-E PT7M8202B12TA5EX TCR3DF185,LM(CT TCR3DF24,LM(CT TCR3DF285,LM(CT TCR3DF31,LM(CT TCR3DF31,LM(CT TCR3DF45,LM(CT MP2013GQ-33-Z 059985X NCP4687DH15T1G 701326R TCR2EN28,LF(S NCV8170AXV250T2G TCR3DF27,LM(CT TCR3DF19,LM(CT TCR3DF125,LM(CT TCR2EN18,LF(S AP2112R5A-3.3TRG1 AP7315-25W5-7 IFX30081LDVGRNXUMA1 NCV47411PAAJR2G AP2113KTR-G1 AP2111H-1.2TRG1 ZLDO1117QK50TC AZ1117IH-1.8TRG1 AZ1117ID-ADJTRG1 TCR3DG12,LF MIC5514-3.3YMT-T5 MIC5512-1.2YMT-T5 MIC5317-2.8YM5-T5 SCD7912BTG NCP154MX180270TAG SCD33269T-5.0G NCV8170BMX330TCG NCV8170AMX120TCG NCP706ABMX300TAG NCP153MX330180TCG NCP114BMX075TCG MC33269T-3.5G CAT6243-ADJCMT5T TCR3DG33,LF AP2127N-1.0TRG1 TCR4DG35,LF LT1117CST-3.3 LT1117CST-5 TAR5S15U(TE85L,F) TAR5S18U(TE85L,F) TCR3UG19A,LF TCR4DG105,LF