## LNBP20 / LNBP1X series

## LNBP supply and control voltage regulator (parallel interface)

#### **Feature summary**

- Complete interface for two LNBs remote supply and control

- LNB selection and stand-by function

- Built-in tone oscillator factory trimmed at 22KHz

- Fast oscillator start-up facilitates DiSEqC<sup>TM</sup> encoding

- Two supply inputs for lowest dissipation

- Bypass function for slave operation

- LNB short circuit protection and diagnostic

- Auxiliary modulation input extends flexibility

- Cable length compensation

- Internal over temperature protection

- Backward current protection

#### **Description**

Intended for analog and digital satellite receivers, the LNBP is a monolithic linear voltage regulator, assembled in PowerSO-20 and PowerSO-10, specifically designed to provide the powering voltages and the interfacing signals to the LNB downconverter situated in the antenna

via the coaxial cable. Since most satellite receivers have two antenna ports, the output voltage of the regulator is available at one of two logic-selectable output pins (LNBA, LNBB). When the IC is powered and put in Stand-by (EN pin LOW), both regulator outputs are disabled to allow the antenna downconverters to be supplied/controlled by others satellite receivers sharing the same coaxial lines. In this occurrence the device will limit at 3 mA (max) the backward current that could flow from LNBA and LNBB output pins to GND. (See continuous description).

#### **Order codes**

| Part number | Pac         | ckage       |

|-------------|-------------|-------------|

| Part number | PowerSO-20  | PowerSO-10  |

| LNBP10      |             | LNBP10SP-TR |

| LNBP11      |             | LNBP11SP-TR |

| LNBP12      |             | LNBP12SP-TR |

| LNBP13      |             | LNBP13SP-TR |

| LNBP14      |             | LNBP14SP-TR |

| LNBP15      |             | LNBP15SP-TR |

| LNBP16      |             | LNBP16SP-TR |

| LNBP20      | LNBP20PD-TR |             |

# **Contents**

| 1 | Description (continued)        | . 3 |

|---|--------------------------------|-----|

| 2 | Pin configuration              | . 4 |

| 3 | Maximum ratings                | . 6 |

| 4 | Diagram                        | . 7 |

| 5 | Electrical characteristics     | . 8 |

| 6 | Typical characteristics        | 10  |

| 7 | Typical application schematics | 14  |

| 8 | Package mechanical data        | 18  |

| 9 | Revision history               | 23  |

## 1 Description (continued)

For slave operation in single dish, dual receiver systems, the bypass function is implemented by an electronic switch between the Master Input pin (MI) and the LNBA pin, thus leaving all LNB powering and control functions to the Master Receiver. This electronic switch is closed when the device is powered and EN pin is LOW.

The regulator outputs can be logic controlled to be 13 or 18 V (typ.) by mean of the VSEL pin for remote controlling of LNBs. Additionally, it is possible to increment by 1V (typ.) the selected voltage value to compensate the excess voltage drop along the coaxial cable (LLC pin HIGH).

In order to reduce the power dissipation of the device when the lowest output voltage is selected, the regulator has two Supply Input pins  $V_{CC1}$  and  $V_{CC2}$ . They must be powered respectively at 16V (min) and 23V (min), and an internal switch automatically will select the suitable supply pin according to the selected output voltage. If adequate heatsink is provided and higher power losses are acceptable, both supply pins can be powered by the same 23V source without affecting any other circuit performance.

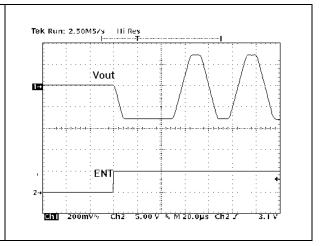

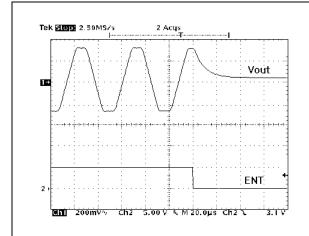

The ENT (Tone Enable) pin activates the internal oscillator so that the DC output is modulated by a  $\pm 0.3$  V, 22KHz (typ.) square wave. This internal oscillator is factory trimmed within a tolerance of  $\pm 2$ KHz, thus no further adjustments neither external components are required.

A burst coding of the 22KHz tone can be accomplished thanks to the fast response of the ENT input and the prompt oscillator start-up. This helps designers who want to implement the DiSEgC<sup>TM</sup> protocols <sup>(a)</sup>.

In order to improve design flexibility and to allow implementation of newcoming LNB remote control standards, an analogic modulation input pin is available (EXTM). An appropriate DC blocking capacitor must be used to couple the modulating signal source to the EXTM pin. When external modulation is not used, the relevant pin can be left open.

Two pins are dedicated to the overcurrent protection/monitoring: CEXT and OLF. The overcurrent protection circuit works dynamically: as soon as an overload is detected in either LNB output, the output is shut-down for a time  $t_{\rm off}$  determined by the capacitor connected between CEXT and GND. Simultaneously the OLF pin, that is an open collector diagnostic output flag, from HIGH IMPEDANCE state goes LOW.

After the time has elapsed, the output is resumed for a time  $t_{on}=1/15t_{off}$  (typ.) and OLF goes in HIGH IMPEDANCE. If the overload is still present, the protection circuit will cycle again through  $t_{off}$  and ton until the overload is removed. Typical  $t_{on}+t_{off}$  value is 1200ms when a 4.7µF external capacitor is used.

This dynamic operation can greatly reduce the power dissipation in short circuit condition, still ensuring excellent power-on start up even with highly capacitive loads on LNB outputs.

The device is packaged in PowerSO-20 for surface mounting. When a limited functionality in a smaller package matches design needs, a range of cost-effective PowerSO-10 solutions is also offered. All versions have built-in thermal protection against overheating damage.

57

External components are needed to comply to level 2.x and above (bidirectional) DiSEqC<sup>TM</sup> bus hardware requirements. DiSEqC<sup>TM</sup> is a trademark or EUTELSAT.

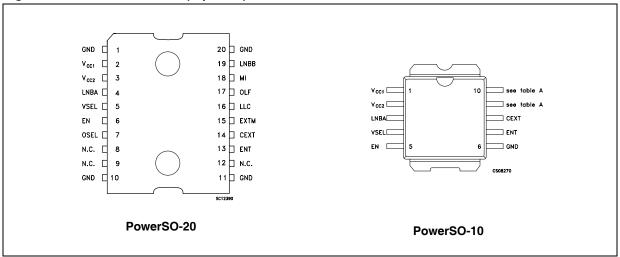

# 2 Pin configuration

Figure 1. Pin connections (top view)

Table 1. Pin Description

| CVMPOL           | NAME                                              | FUNCTION                                                                                                                                      | PIN NUMBER vs SALES TYPE (LNBP) |      |      |      |      |      |      |      |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|------|------|------|------|

| SYMBOL           | NAME                                              | FUNCTION                                                                                                                                      | 20PD                            | 10SP | 11SP | 12SP | 13SP | 14SP | 15SP | 16SP |

| V <sub>CC1</sub> | Supply input<br>1                                 | 15V to 25V supply. It is automatically selected when V <sub>OUT</sub> = 13 or 14V                                                             | 2                               | 1    | 1    | 1    |      | 1    | 1    | 1    |

| V <sub>CC2</sub> | Supply input<br>2                                 | 22V to 25V supply. It is<br>automatically selected<br>when V <sub>OUT</sub> = 18 or 19V                                                       | 3                               | 2    | 2    | 2    | 2    | 2    | 2    | 2    |

| LNBA             | Output port                                       | See truth table voltage<br>and port selection. In<br>stand-by mode this port<br>is powered by the MI pin<br>via the internal bypass<br>switch | 4                               | 3    | 3    | 3    | 3    | 3    | 3    | 3    |

| V <sub>SEL</sub> | Output<br>voltage<br>selection:13<br>or 18V (typ) | Logic control input: see truth table                                                                                                          | 5                               | 4    | 4    | 4    | 4    | 4    | 4    | 4    |

| EN               | Port enable                                       | Logic control input: see truth table                                                                                                          | 6                               | 5    | 5    | 5    | 5    | 5    | 5    | 5    |

| OSEL             | Port selection                                    | Logic control input: see truth table                                                                                                          | 7                               | 9    | NA   | NA   | NA   | NA   | NA   | NA   |

| GND              | Ground                                            | Circuit ground. It is internally connected to the die frame                                                                                   | 1<br>10<br>11<br>20             | 6    | 6    | 6    | 6    | 6    | 6    | 6    |

Table 1. Pin Description

| SYMBOL  | NAME                          | FUNCTION                                                                                                                   |      | PIN I | NUMBE | R vs S | ALES T | YPE (LI | NBP) |      |

|---------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|-------|-------|--------|--------|---------|------|------|

| STIMBOL | NAME                          | FUNCTION                                                                                                                   | 20PD | 10SP  | 11SP  | 12SP   | 13SP   | 14SP    | 15SP | 16SP |

| ENT     | 22KHz tone<br>enable          | Logic control input: see truth table                                                                                       | 13   | 7     | 7     | 7      | 7      | 7       | 7    | 7    |

| CEXT    | External capacitor            | Timing capacitor used by<br>the dynamic overload<br>protection. Typical<br>application is 4.7μF for a<br>1200ms cycle      | 14   | 8     | 8     | 8      | 8      | 8       | 8    | 8    |

| EXTM    | External<br>modulator         | External modulation input. Needs DC decoupling to the AC source. if not used, can be left open.                            | 15   | NA    | NA    | NA     | 9      | NA      | 9    | 9    |

| LLC     | Line length compens. (1V typ) | Logic control input: see truth table                                                                                       | 16   | NA    | NA    | 9      | NA     | 9       | NA   | 10   |

| OLF     | Over load<br>flag             | Logic output (open<br>collector). Normally in<br>HIGH IMPEDANCE,<br>goes LOW when current<br>or thermal overload<br>occurs | 17   | NA    | 9     | NA     | NA     | 10      | 10   | NA   |

| MI      | Master input                  | In stand-by mode, the voltage on MI is routed to LNBA pin. Can be left open if bypass function is not needed               | 18   | NA    | 10    | 10     | 10     | NA      | NA   | NA   |

| LNBB    | Output port                   | See truth tables for voltage and port selection                                                                            | 19   | 10    | NA    | NA     | NA     | NA      | NA   | NA   |

Note: The limited pin availability of the PowerSO-10 package leads to drop some functions.

# 3 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol           | Parameter                                                   | Value              | Unit |

|------------------|-------------------------------------------------------------|--------------------|------|

| VI               | DC Input voltage (V <sub>CC1</sub> , V <sub>CC2</sub> , MI) | 28                 | V    |

| Vo               | Output voltage                                              | -0.3 to 28         | V    |

| Io               | Output current (LNBA, LNBB)                                 | Internally Limited | mA   |

| VI               | Logic input voltage (ENT, EN OSEL, VSEL, LLC)               | -0.5 to 7          | V    |

| I <sub>SW</sub>  | Bypass switch current                                       | 900                | mA   |

| P <sub>D</sub>   | Power dissipation at T <sub>case</sub> < 85°C               | 14                 | W    |

| T <sub>stg</sub> | Storage temperature range                                   | -40 to +150        | °C   |

| T <sub>op</sub>  | Operating junction temperature range                        | -40 to +125        | °C   |

Note:

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied

Table 3. Thermal data

| Symbol            | Parameter                        | PowerSO-20 | PowerSO-10 | Unit |

|-------------------|----------------------------------|------------|------------|------|

| R <sub>thJC</sub> | Thermal resistance junction-case | 2          | 2          | °C/W |

Table 4.

Logic Controls Truth Table

| CONTROL I/O | PIN NAME | L                                      | Н                                    |

|-------------|----------|----------------------------------------|--------------------------------------|

| OUT         | OLF      | $I_{OUT} > I_{OMAX}$ or $T_j > 150$ °C | I <sub>OUT</sub> < I <sub>OMAX</sub> |

| IN          | ENT      | 22KHz tone OFF                         | 22KHz tone ON                        |

| IN          | EN       | See Table Below                        | See Table Below                      |

| IN          | OSEL     | See Table Below                        | See Table Below                      |

| IN          | VSEL     | See Table Below                        | See Table Below                      |

| IN          | LLC      | See Table Below                        | See Table Below                      |

| EN | OSEL | VSEL | LLCO | V <sub>LNBA</sub>             | V <sub>LNBB</sub> |

|----|------|------|------|-------------------------------|-------------------|

| L  | Х    | Х    | Х    | V <sub>MI</sub> - 0.4V (typ.) | Disabled          |

| Н  | L    | L    | L    | 13V (typ.)                    | Disabled          |

| Н  | L    | Н    | L    | 18V (typ.)                    | Disabled          |

| Н  | L    | L    | Н    | 14V (typ.)                    | Disabled          |

| Н  | L    | Н    | Н    | 19V (typ.)                    | Disabled          |

| Н  | Н    | L    | L    | Disabled                      | 13V (typ.)        |

| Н  | Н    | Н    | L    | Disabled                      | 18V (typ.)        |

| Н  | Н    | L    | Н    | Disabled                      | 14V (typ.)        |

| Н  | Н    | Н    | Н    | Disabled                      | 19V (typ.)        |

Note: All logic input pins have internal pull-down resistor (typ. = 250KW)

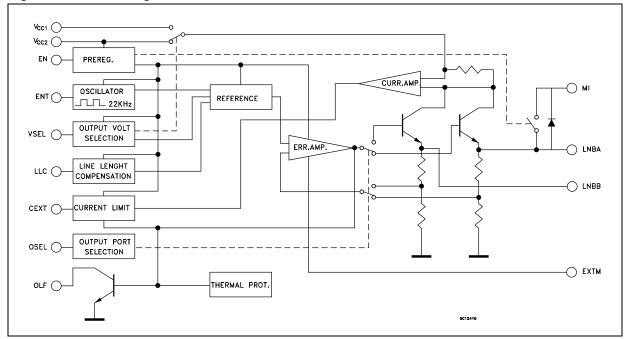

# 4 Diagram

Figure 2. Block diagram

## 5 Electrical characteristics

Table 5. Electrical characteristics for LNBP Series ( $T_J = 0$  to 85°C,  $C_I = 0.22 \mu F$ ,  $C_O = 0.1 \mu F$ , EN=H, ENT=L, LLC=L,  $V_{IN1}$ =16V,  $V_{IN2}$ =23V  $I_{OUT}$ =50mA, unless otherwise specified.)

| Symbol                          | Parameter                                   | Test conditions                                                                                      | Min. | Тур.                 | Max. | Unit             |

|---------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------|------|----------------------|------|------------------|

| \ <u>/</u>                      | V Complements                               | I <sub>O</sub> = 500 mA, ENT=H, VSEL=L, LLC=L                                                        | 15   |                      | 25   | V                |

| $V_{IN1}$                       | V <sub>CC1</sub> Supply voltage             | I <sub>O</sub> = 500 mA, ENT=H, VSEL=L, LLC=H                                                        | 16   |                      | 25   | V                |

|                                 | V Complements                               | I <sub>O</sub> = 500 mA, ENT=H, VSEL=L, LLC=L                                                        | 22   |                      | 25   | V                |

| $V_{IN2}$                       | V <sub>CC2</sub> Supply voltage             | I <sub>O</sub> = 500 mA, VSEL=L, LLC=H                                                               | 23   |                      | 25   | V                |

|                                 | Output valtage                              | I <sub>O</sub> = 500 mA, VSEL=H, LLC=L                                                               | 17.3 | 18                   | 18.7 | V                |

| V <sub>O1</sub>                 | Output voltage                              | I <sub>O</sub> = 500 mA, VSEL=H, LLC=H                                                               |      | 19                   |      | ٧                |

| \/                              | Output voltage                              | I <sub>O</sub> = 500 mA, VSEL=L, LLC=L                                                               | 12.5 | 13                   | 13.5 | V                |

| $V_{O2}$                        | Output voltage                              | I <sub>O</sub> = 500 mA, VSEL=L, LLC=H                                                               |      | 14                   |      | V                |

| 41/                             | Line regulation                             | V <sub>IN1</sub> =15 to 18V, V <sub>OUT</sub> =13V                                                   |      | 4                    | 40   | mV               |

| $\Delta V_{O}$                  | Line regulation                             | V <sub>IN2</sub> =22 to 25V, V <sub>OUT</sub> =18V                                                   |      | 4                    | 40   | mV               |

| $\Delta V_{O}$                  | Load regulation                             | V <sub>IN1</sub> =V <sub>IN2</sub> =22V, V <sub>OUT</sub> =13 or 18V<br>I <sub>O</sub> = 50 to 500mA |      | 80                   | 180  | mV               |

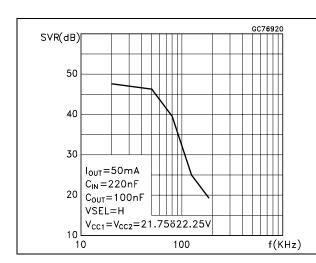

| SVR                             | Supply voltage rejection                    | $V_{IN1} = V_{IN2} = 23 \pm 0.5 V_{ac}, f_{ac} = 120 \text{ Hz},$                                    |      | 45                   |      | dB               |

| I <sub>MAX</sub>                | Output current limiting                     |                                                                                                      | 500  | 650                  | 800  | mA               |

| t <sub>OFF</sub>                | Dynamic overload protection OFF time        | Output Shorted, C <sub>EXT</sub> = 4.7μF                                                             |      | 1100                 |      | ms               |

| t <sub>ON</sub>                 | Dynamic overload protection ON time         | Output Shorted, C <sub>EXT</sub> = 4.7μF                                                             |      | t <sub>OFF</sub> /15 |      | ms               |

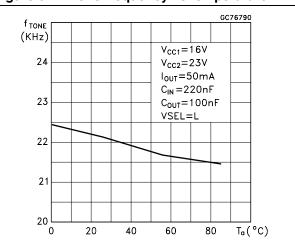

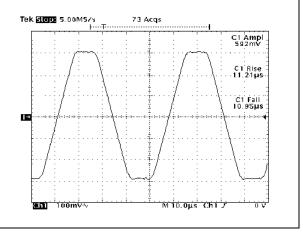

| f <sub>TONE</sub>               | Tone frequency                              | ENT=H                                                                                                | 20   | 22                   | 24   | KHz              |

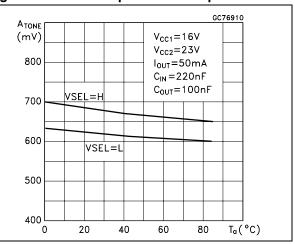

| A <sub>TONE</sub>               | Tone amplitude                              | ENT=H                                                                                                | 0.55 | 0.72                 | 0.9  | $V_{PP}$         |

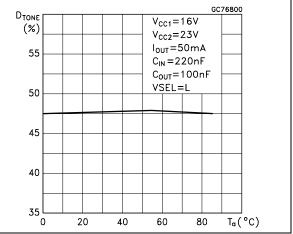

| D <sub>TONE</sub>               | Tone duty cycle                             | ENT=H                                                                                                | 40   | 50                   | 60   | %                |

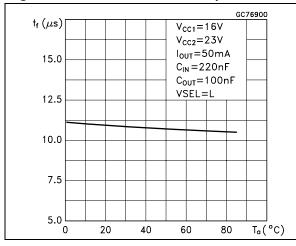

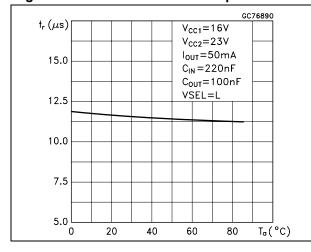

| t <sub>r</sub> , t <sub>f</sub> | Tone rise and fall time                     | ENT=H                                                                                                | 5    | 10                   | 15   | μs               |

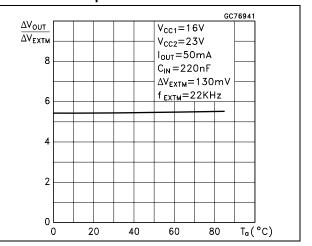

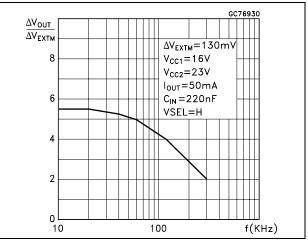

| G <sub>EXTM</sub>               | External modulation gain                    | $\Delta V_{OUT}/\Delta V_{EXTM}$ , f = 10Hz to 40KHz                                                 |      | 5                    |      |                  |

| V <sub>EXTM</sub>               | External modulation input voltage           | AC Coupling                                                                                          |      |                      | 400  | mV <sub>PP</sub> |

| Z <sub>EXTM</sub>               | External modulation impedance               | f = 10Hz to 40KHz                                                                                    |      | 400                  |      | Ω                |

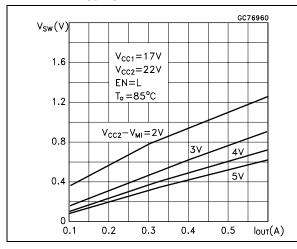

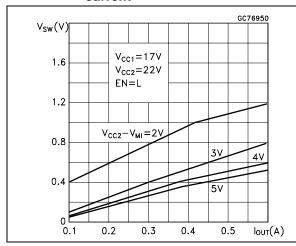

| V <sub>SW</sub>                 | Bypass switch voltage drop (MI to LNBA)     | EN=L, I <sub>SW</sub> =300mA, V <sub>CC2</sub> -V <sub>MI</sub> =4V                                  |      | 0.35                 | 0.6  | V                |

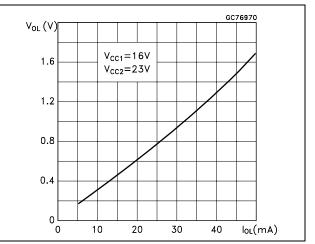

| V <sub>OL</sub>                 | Overload flag pin logic<br>LOW              | I <sub>OL</sub> =8mA                                                                                 |      | 0.28                 | 0.5  | V                |

| I <sub>OZ</sub>                 | Overload flag pin OFF state leakage current | V <sub>OH</sub> = 6V                                                                                 |      |                      | 10   | μΑ               |

| $V_{IL}$                        | Control input pin logic<br>LOW              |                                                                                                      |      |                      | 0.8  | V                |

| Symbol            | Parameter                       | Test conditions                                                            | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| V <sub>IH</sub>   | Control input pin logic<br>HIGH |                                                                            | 2.5  |      |      | ٧    |

| I <sub>IH</sub>   | Control pins input current      | V <sub>IH</sub> = 5V                                                       |      | 20   |      | μΑ   |

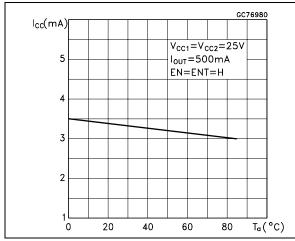

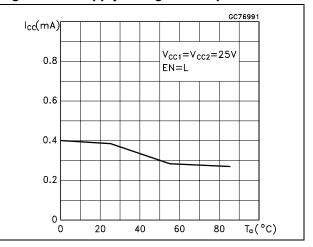

| 1                 | Supply current                  | Output Disabled (EN=L)                                                     |      | 0.3  | 1    | mA   |

| Icc               | Зирріу сипені                   | ENT=H, I <sub>OUT</sub> =500mA                                             |      | 3.1  | 6    | mA   |

| I <sub>OBK</sub>  | Output backward current         | EN=L, $V_{LNBA} = V_{LNBB} = 18V$<br>$V_{IN1} = V_{IN2} = 22V$ or floating |      | 0.2  | 3    | mA   |

| T <sub>SHDN</sub> | Temperature shutdown threshold  |                                                                            |      | 150  |      | °C   |

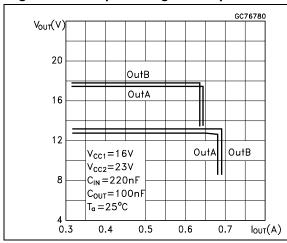

## **6** Typical characteristics

(unless otherwise specified  $T_J = 25^{\circ}C$ )

Figure 3. Output voltage vs output current

Figure 4. Tone duty cycle vs temperature

Figure 5. Tone fall time vs temperature

Figure 6. Tone frequency vs temperature

Figure 7. Tone rise time vs temperature

Figure 8. Tone amplitude vs temperature

5/

Figure 9. S.V.R. vs Frequency

Figure 10. External modulation vs temperature

Figure 11. Bypass switch drop vs output current

Figure 12. LNBA External modulation gain vs frequency

Figure 13. Bypass switch drop vs output current

Figure 14. Overload flag pin logic low vs flag current

Figure 15. Supply voltage vs temperature

Figure 16. Supply voltage vs temperature

Figure 17. Dynamic overload protection (I<sub>SC</sub> vs time)

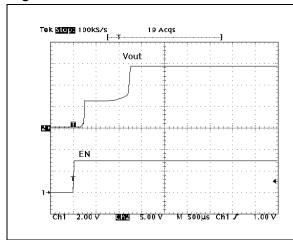

Figure 18. Tone enable

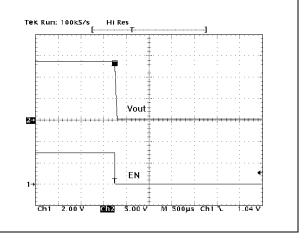

Figure 19. Tone disable

Figure 20. 22KHz Tone

Figure 21. Enable time

Figure 22. Disable time

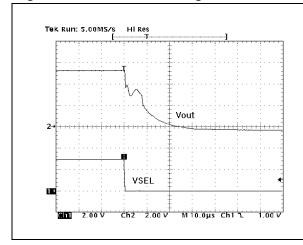

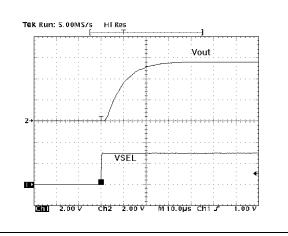

Figure 23. 18V to 13V Change

Figure 24. 18V to 13V Change

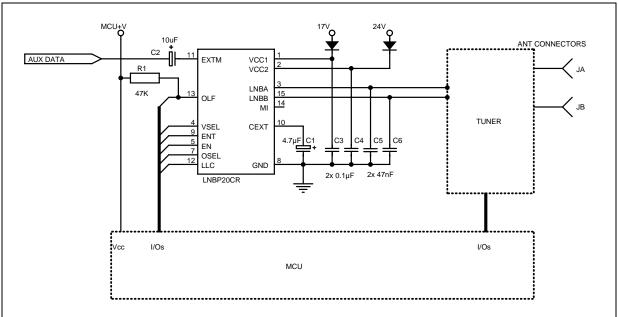

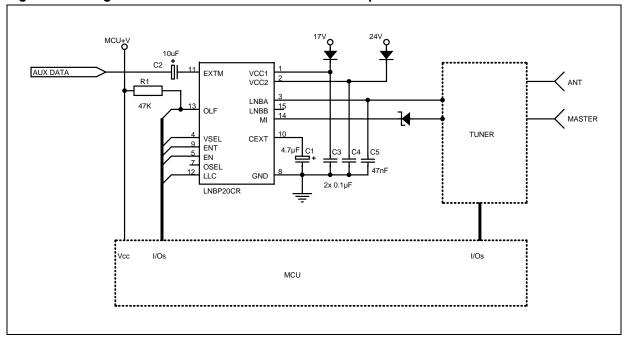

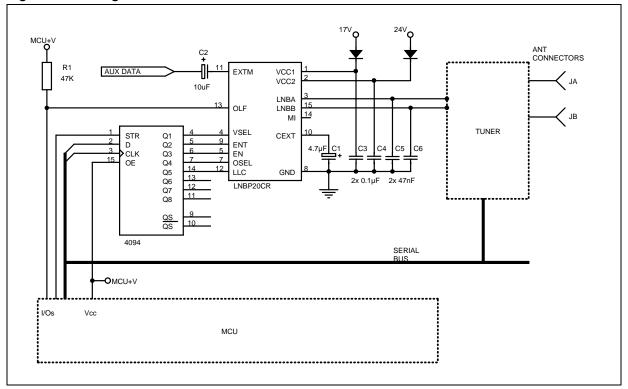

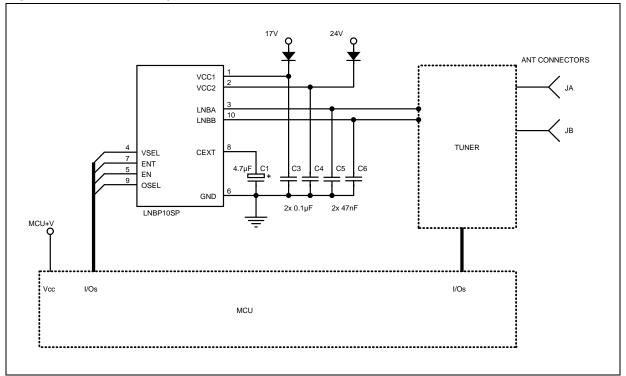

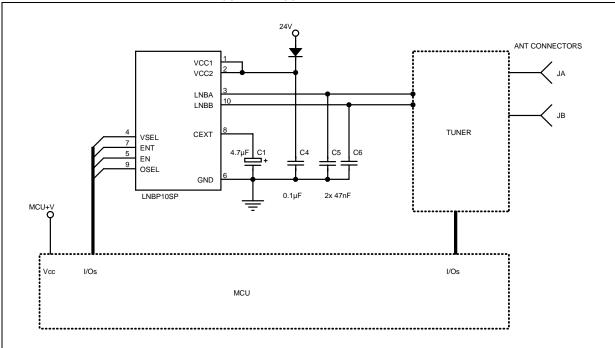

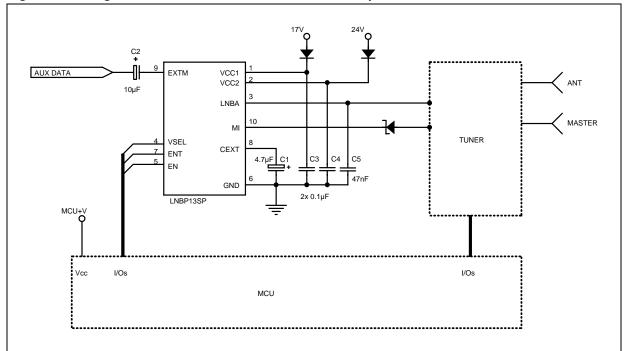

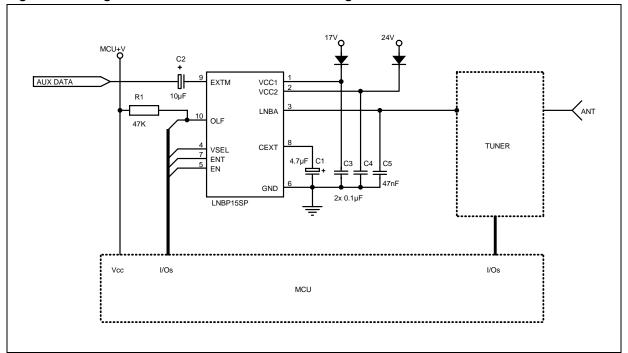

# 7 Typical application schematics

Figure 25. Two antenna ports receiver

Figure 26. Single antenna receiver with master receiver port

Figure 27. Using serial bus to save MPU I/os

Figure 28. Two antenna ports receiver - low cost solution

Figure 29. Connecting together  $V_{CC1}$  and  $V_{CC2}$

Figure 30. Single antenna receiver with master receiver port - low cost solution

Figure 31. Single antenna receiver with overload diagnostic

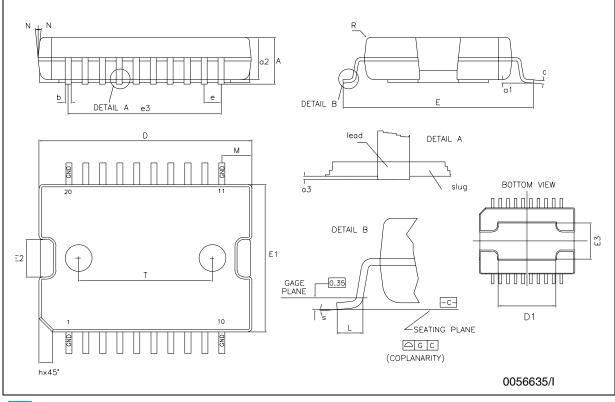

# 8 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

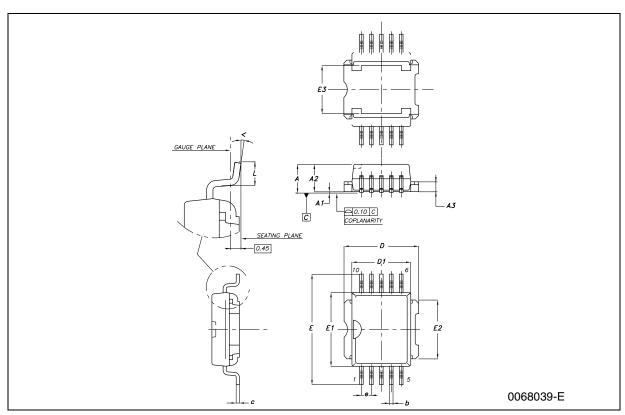

#### **PowerSO-20 MECHANICAL DATA**

| DIM    |       | mm.   |       |        | inch   |        |

|--------|-------|-------|-------|--------|--------|--------|

| DIM.   | MIN.  | TYP   | MAX.  | MIN.   | TYP.   | MAX.   |

| Α      |       |       | 3.60  |        |        | 0.1417 |

| a1     | 0.10  |       | 0.30  | 0.0039 |        | 0.0118 |

| a2     |       |       | 3.30  |        |        | 0.1299 |

| аЗ     | 0     |       | 0.10  | 0      |        | 0.0039 |

| b      | 0.40  |       | 0.53  | 0.0157 |        | 0.0209 |

| С      | 0.23  |       | 0.32  | 0.0090 |        | 0.0013 |

| D (1)  | 15.80 |       | 16.00 | 0.6220 |        | 0.630  |

| E      | 13.90 |       | 14.50 | 0.5472 |        | 0.5710 |

| е      |       | 1.27  |       |        | 0.0500 |        |

| e3     |       | 11.43 |       |        | 0.4500 |        |

| E1 (1) | 10.90 |       | 11.10 | 0.4291 |        | 0.4370 |

| E2     |       |       | 2.90  |        |        | 0.1141 |

| E3     | 5.8   |       | 6.2   | 0.2283 |        | 0.2441 |

| G      | 0     |       | 0.10  | 0.0000 |        | 0.0039 |

| Н      | 15.5  |       | 15.9  | 0.6102 |        | 0.6260 |

| h      |       |       | 1.10  |        |        | 0.0433 |

| L      | 0.80  |       | 1.10  | 0.0314 |        | 0.0433 |

| N      |       |       | 10°   |        |        | 10°    |

| S      | 0°    |       | 8°    | 0°     |        | 8°     |

| Т      |       | 10.0  |       |        | 0.3937 |        |

(1) "D and E1" do not include mold flash or protusions - Mold flash or protusions shall not exceed 0.15mm (0.006")

5/

#### **PowerSO-10 MECHANICAL DATA**

| DIM. |       | mm.  |       |       | inch  |       |  |  |

|------|-------|------|-------|-------|-------|-------|--|--|

| DIW. | MIN.  | TYP  | MAX.  | MIN.  | TYP.  | MAX.  |  |  |

| Α    |       |      | 3.70  |       |       | 0.146 |  |  |

| A1   |       |      | 0.10  |       |       | 0.004 |  |  |

| A2   | 3.40  |      | 3.60  | 0.134 |       | 0.142 |  |  |

| A3   | 1.25  |      | 1.35  | 0.049 |       | 0.053 |  |  |

| b    | 0.40  |      | 0.53  | 0.016 |       | 0.021 |  |  |

| С    | 0.35  |      | 0.55  | 0.014 |       | 0.022 |  |  |

| D    | 9.40  |      | 9.60  | 0.370 |       | 0.378 |  |  |

| D1   | 7.40  |      | 7.60  | 0.291 |       | 0.299 |  |  |

| E    | 13.80 |      | 14.40 | 0.543 |       | 0.567 |  |  |

| E1   | 9.30  |      | 9.50  | 0.366 |       | 0.374 |  |  |

| E2   | 7.20  |      | 7.60  | 0.283 |       | 0.299 |  |  |

| E3   | 5.90  |      | 6.10  | 0.232 |       | 0.240 |  |  |

| е    |       | 1.27 |       |       | 0.050 |       |  |  |

| L    | 0.95  |      | 1.65  | 0.037 |       | 0.065 |  |  |

| α    | 0°    |      | 8°    | 0°    |       | 8°    |  |  |

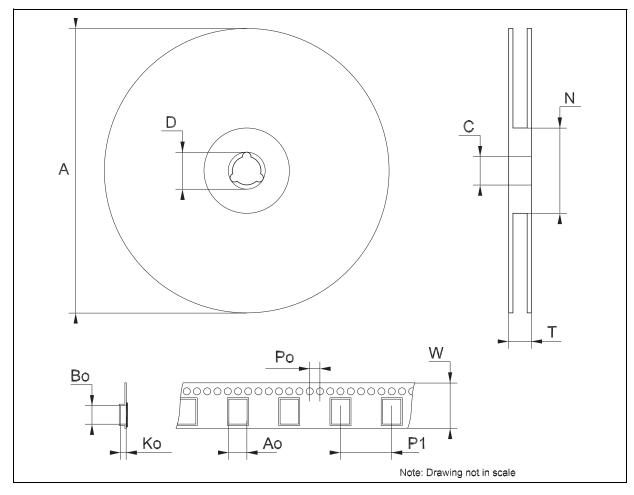

Tape & Reel PowerSO-20 MECHANICAL DATA

| DIM. | mm.  |     |      | inch  |      |        |

|------|------|-----|------|-------|------|--------|

|      | MIN. | TYP | MAX. | MIN.  | TYP. | MAX.   |

| А    |      |     | 330  |       |      | 12.992 |

| С    | 12.8 |     | 13.2 | 0.504 |      | 0.519  |

| D    | 20.2 |     |      | 0.795 |      |        |

| N    | 60   |     |      | 2.362 |      |        |

| Т    |      |     | 30.4 |       |      | 1.197  |

| Ao   | 15.1 |     | 15.3 | 0.594 |      | 0.602  |

| Во   | 16.5 |     | 16.7 | 0.650 |      | 0.658  |

| Ко   | 3.8  |     | 4.0  | 0.149 |      | 0.157  |

| Po   | 3.9  |     | 4.1  | 0.153 |      | 0.161  |

| Р    | 23.9 |     | 24.1 | 0.941 |      | 0.949  |

| W    | 23.7 |     | 24.3 | 0.933 |      | 0.957  |

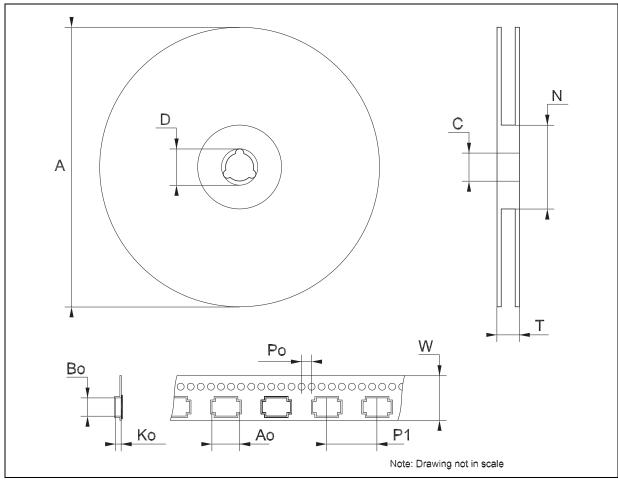

| Tape & Reel PowerSC | 10 MECHANICAL DATA |

|---------------------|--------------------|

|---------------------|--------------------|

| DIM. | mm.  |     |      | inch  |      |        |

|------|------|-----|------|-------|------|--------|

|      | MIN. | TYP | MAX. | MIN.  | TYP. | MAX.   |

| А    |      |     | 330  |       |      | 12.992 |

| С    | 12.8 |     | 13.2 | 0.504 |      | 0.519  |

| D    | 20.2 |     |      | 0.795 |      |        |

| N    | 60   |     |      | 2.362 |      |        |

| Т    |      |     | 30.4 |       |      | 1.197  |

| Ao   | 14.9 |     | 15.1 | 0.587 |      | 0.594  |

| Во   | 9.9  |     | 10.1 | 0.390 |      | 0.398  |

| Ko   | 4.15 |     | 4.35 | 0.163 |      | 0.171  |

| Po   | 3.9  |     | 4.1  | 0.153 |      | 0.161  |

| Р    | 23.9 |     | 24.1 | 0.941 |      | 0.949  |

| W    | 23.7 |     | 24.3 | 0.933 |      | 0.957  |

LNBP20 / LNBP1X series Revision history

# 9 Revision history

Table 6. Revision history

| Date        | Revision | Changes                                                               |

|-------------|----------|-----------------------------------------------------------------------|

| 08-Jun-2004 | 7        | Typing Error V <sub>O1</sub> and V <sub>O2</sub> on Table 6 - Page 6. |

| 21-Dec-2004 | 8        | Table 2 has been updated on GND row.                                  |

| 07-Sep-2006 | 9        | Add value V <sub>O</sub> on table 2 and new template.                 |

| 03-May-2007 | 10       | Order codes has been updated.                                         |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Linear Voltage Regulators category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

LV56831P-E LV5684PVD-XH MAX202ECWE-LF MCDTSA6-2R L4953G L7815ACV-DG PQ3DZ53U LV56801P-E

TCR3DF13,LM(CT TCR3DF39,LM(CT TLE42794G L78L05CZ/1SX L78LR05DL-MA-E L78MR05-E 033150D 033151B 090756R

636416C NCV78M15BDTG 702482B 714954EB TLE42794GM TLE42994GM ZMR500QFTA BA033LBSG2-TR

NCV78M05ABDTRKG NCV78M08BDTRKG NCP7808TG NCV571SN12T1G LV5680P-E CAJ24C256YI-GT3 L78M15CV-DG L9474N

TLS202B1MBV33HTSA1 L79M05T-E NCP571SN09T1G MAX15006AASA/V+ MIC5283-5.0YML-T5 L4969URTR-E L78LR05D-MA-E

NCV7808BDTRKG L9466N NCP7805ETG SC7812CTG NCV7809BTG NCV571SN09T1G NCV317MBTG MC78M15CDTT5G

MC78M12CDTT5G L9468N