# High power density 600V Half bridge driver with two enhancement mode GaN

**Product status link**

MASTERGAN1

Product label

#### **Features**

- 600 V system-in-package integrating half-bridge gate driver and high-voltage power GaN transistors:

- QFN 9 x 9 x 1 mm package

- R<sub>DS(ON)</sub> = 150 m $\Omega$

- $I_{DS(MAX)} = 10 A$

- · Reverse current capability

- · Zero reverse recovery loss

- · UVLO protection on low-side and high-side

- · Internal bootstrap diode

- Interlocking function

- · Dedicated pin for shutdown functionality

- Accurate internal timing match

- 3.3 V to 15 V compatible inputs with hysteresis and pull-down

- Overtemperature protection

- · Bill of material reduction

- · Very compact and simplified layout

- · Flexible, easy and fast design.

#### **Application**

- · Switch-mode power supplies

- · Chargers and adapters

- High-voltage PFC, DC-DC and DC-AC Converters

- UPS Systems

- Solar Power

#### Description

The MASTERGAN1 is an advanced power system-in-package integrating a gate driver and two enhancement mode GaN transistors in half-bridge configuration.

The integrated power GaNs have  $R_{DS(ON)}$  of 150 m $\Omega$  and 650 V drain-source breakdown voltage, while the high side of the embedded gate driver can be easily supplied by the integrated bootstrap diode.

The MASTERGAN1 features UVLO protection on both the lower and upper driving sections, preventing the power switches from operating in low efficiency or dangerous conditions, and the interlocking function avoids cross-conduction conditions.

The input pins extended range allows easy interfacing with microcontrollers, DSP units or Hall effect sensors.

The MASTERGAN1 operates in the industrial temperature range, -40°C to 125°C.

The device is available in a compact 9x9 mm QFN package.

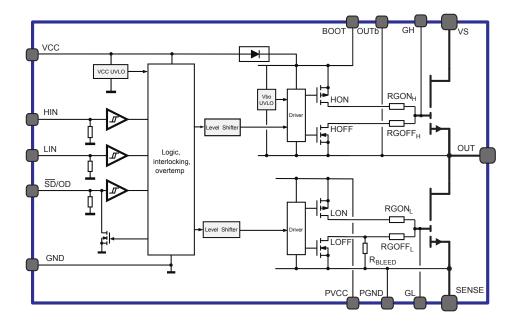

## 1 Block diagram

Figure 1. Block diagram

DS13417 - Rev 3 page 2/27

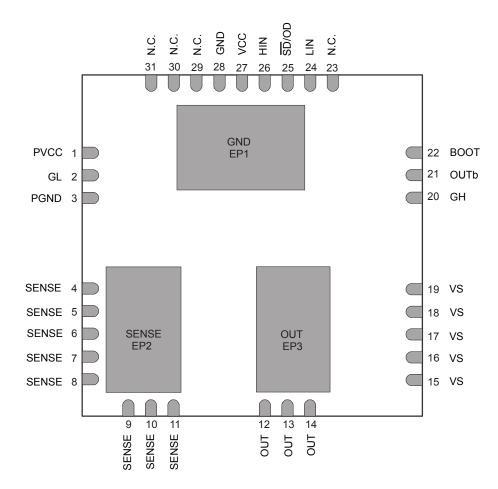

### 2 Pin description and connection diagram

Figure 2. Pin connection (top view)

#### 2.1 Pin list

Table 1. Pin description

| Pin Number                       | Pin Name | Туре         | Function                                                                                                            |

|----------------------------------|----------|--------------|---------------------------------------------------------------------------------------------------------------------|

| 15, 16, 17, 18, 19               | VS       | Power Supply | High voltage supply (high-side GaN Drain)                                                                           |

| 12, 13, 14, EP3                  | OUT      | Power Output | Half-bridge output                                                                                                  |

| 4, 5, 6, 7, 8, 9, 10,<br>11, EP2 | SENSE    | Power Supply | Half-bridge sense (low-side GaN Source)                                                                             |

| 22                               | воот     | Power Supply | Gate driver high-side supply voltage                                                                                |

| 21                               | OUTb     | Power Supply | Gate driver high-side reference voltage, used only for Bootstrap capacitor connection. Internally connected to OUT. |

| 27                               | VCC      | Power Supply | Logic supply voltage                                                                                                |

DS13417 - Rev 3 page 3/27

| Pin Number     | Pin Name | Туре               | Function                                                              |

|----------------|----------|--------------------|-----------------------------------------------------------------------|

| 1              | PVCC     | Power Supply       | Gate driver low-side supply voltage                                   |

| 28, EP1        | GND      | Power Supply       | Logic ground                                                          |

| 3              | PGND     | Power Supply       | Gate driver low-side driver reference. Internally connected to SENSE. |

| 26             | HIN      | Logic Input        | High-Side driver logic input                                          |

| 24             | LIN      | Logic Input        | Low-Side driver logic input                                           |

| 25             | SD/OD    | Logic Input-Output | Driver Shutdown input and Over-Temperature                            |

| 2              | GL       | Output             | Low-Side GaN gate.                                                    |

| 20             | GH       | Output             | High-Side GaN gate.                                                   |

| 23, 29, 30, 31 | N.C.     | Not Connected      | Leave floating                                                        |

DS13417 - Rev 3 page 4/27

#### 3 Electrical Data

#### 3.1 Absolute maximum ratings

Table 2. Absolute maximum ratings (each voltage referred to GND unless otherwise specified)

| Symbol            | Parameter                                                                 | Test Condition                                                                 | Value        | Unit |

|-------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------|------|

| V <sub>DS</sub>   | GaN Drain-to-Source Voltage                                               | T <sub>J</sub> = 25 °C                                                         | 620          | V    |

| VCC               | Logic supply voltage                                                      |                                                                                | -0.3 to 11   | V    |

| PVCC-PGND         | Low-side driver supply voltage (1)                                        |                                                                                | -0.3 to 7    | V    |

| VCC-PGND          | Logic supply vs. Low-side driver ground                                   |                                                                                | -0.3 to 18.3 | V    |

| PVCC              | Low-side driver supply vs. logic ground                                   |                                                                                | -0.3 to 18.3 | V    |

| PGND              | Low-side driver ground vs. logic ground                                   |                                                                                | -7.3 to 11.3 | V    |

| $V_{BO}$          | BOOT to OUTb voltage (2)                                                  |                                                                                | -0.3 to 7    | V    |

| BOOT              | Bootstrap voltage                                                         |                                                                                | -0.3 to 620  | V    |

| CGL, CGH          | Maximum external capacitance between GL and PGND and between GH and OUTb  | F <sub>sw</sub> = 2 MHz <sup>(3)</sup>                                         | 680          | pF   |

| RGL, RGH          | Minimum external pull-down resistance between GL and PGND and GH and OUTb |                                                                                | 6.8          | kΩ   |

|                   |                                                                           | DC @ T <sub>CB</sub> = 25°C <sup>(4)</sup> , <sup>(5)</sup>                    | 9.7          | Α    |

| $I_D$             | Drain current (per GaN transistor)                                        | DC @ T <sub>CB</sub> = 100°C <sup>(4)</sup> ), <sup>(5)</sup>                  | 6.4          | Α    |

|                   |                                                                           | Peak @ T <sub>CB</sub> = 25°C <sup>(4)</sup> , <sup>(5)</sup> , <sup>(6)</sup> | 17           | Α    |

| S <sub>Rout</sub> | Half-bridge outputs slew rate (10% - 90%)                                 |                                                                                | 100          | V/ns |

| V <sub>i</sub>    | Logic inputs voltage range                                                |                                                                                | -0.3 to 21   | V    |

| T <sub>J</sub>    | Junction temperature                                                      |                                                                                | -40 to 150   | °C   |

| T <sub>s</sub>    | Storage temperature                                                       |                                                                                | -40 to 150   | °C   |

- 1. PGND internally connected to SENSE.

- 2. OUTb internally connected to OUT.

- 3.  $CGx < 0.08/(Pvcc^2Fsw)-(330^*10^{-12})$ .

- 4. T<sub>CB</sub> is temperature of case exposed pad.

- 5. Range estimated by characterization, not tested in production.

- 6. Value specified by design factor, pulse duration limited to 50 µs and junction temperature.

DS13417 - Rev 3 page 5/27

#### 3.2 Recommended operating conditions

Table 3. Recommended operating conditions (Each voltage referred to GND unless otherwise specified)

| Symbol              | Parameter                                                          | Note             | Min  | Max | Unit |

|---------------------|--------------------------------------------------------------------|------------------|------|-----|------|

| VS                  | High voltage bus                                                   |                  | 0    | 520 | V    |

| VCC                 | Supply voltage                                                     |                  | 4.75 | 9.5 | V    |

| PVCC-PGND           | DVCC to DCND low side cumply(1)                                    |                  | 4.75 | 6.5 | V    |

| PVCC-PGND           | PVCC to PGND low side supply <sup>(1)</sup>                        | Best performance | 5    | 6.5 | V    |

| PVCC                | Low-side driver supply                                             |                  | 3    | 8.5 | V    |

| VCC-PVCC            | VCC to PVCC pin voltage                                            |                  | -3   | 3   | V    |

| PGND                | Low-side driver ground <sup>(1)</sup>                              |                  | -2   | 2   | V    |

| DT                  | Suggested minimum deadtime                                         |                  | 5    |     | ns   |

| T <sub>IN_MIN</sub> | Minimum duration of input pulse to obtain undistorted output pulse |                  | 120  |     | ns   |

| V                   | DOOT to OLITh win valle and (2)                                    |                  | 4.4  | 6.5 | V    |

| $V_{BO}$            | BOOT to OUTb pin voltage <sup>(2)</sup>                            | Best performance | 5    | 6.5 | V    |

| BOOT                | BOOT to GND voltage                                                |                  | 0(3) | 530 | V    |

| Vi                  | Logic inputs voltage range                                         |                  | 0    | 20  | V    |

| T <sub>J</sub>      | Junction temperature                                               |                  | -40  | 125 | °C   |

<sup>1.</sup> PGND internally connected to SENSE.

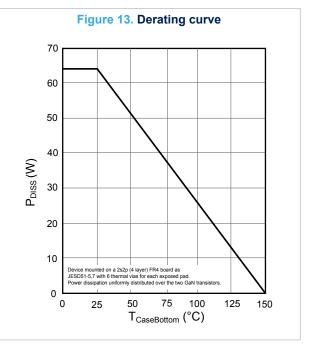

#### 3.3 Thermal data

Table 4. Thermal data

| Symbol                | Parameter                                                               | Value | Unit |

|-----------------------|-------------------------------------------------------------------------|-------|------|

| R <sub>th(J-CB)</sub> | Thermal resistance junction to each GaN transistor exposed pad, typical | 1.9   | °C/W |

| R <sub>th(J-A)</sub>  | Thermal resistance junction-to-ambient <sup>(1)</sup>                   | 17.5  | °C/W |

<sup>1.</sup> The junction to ambient thermal resistance is obtained simulating the device mounted on a 2s2p (4 layer) FR4 board as JESD51-5,7 with 6 thermal vias for each exposed pad. Power dissipation uniformly distributed over the two GaN transistors.

DS13417 - Rev 3 page 6/27

<sup>2.</sup> OUTb internally connected to OUT.

<sup>3. 5</sup> V is recommended during high-hide turn-on.

### 4 Electrical characteristics

#### 4.1 Driver

Table 5. Driver electrical characteristics : VCC = PVCC = 6 V; SENSE = GND;  $T_J$  = 25°C, unless otherwise specified (Each voltage referred to GND unless otherwise specified.)

| Symbol               |                     | Parameter                                                            | Test condition                                                                                               | Min | Тур | Max  | Unit |

|----------------------|---------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Logic sec            | tion supply         | '                                                                    |                                                                                                              | _   |     |      |      |

| VCC <sub>thON</sub>  |                     | VCC UV turn ON threshold <sup>(1)</sup>                              |                                                                                                              | 4.2 | 4.5 | 4.75 | V    |

| VCC <sub>thOFF</sub> |                     | VCC UV turn OFF threshold <sup>(1)</sup>                             |                                                                                                              | 3.9 | 4.2 | 4.5  | V    |

| VCC <sub>hys</sub>   |                     | VCC UV hysteresis <sup>(1)</sup>                                     |                                                                                                              | 0.2 | 0.3 | 0.45 | V    |

| I <sub>QVCCU</sub>   |                     | VCC undervoltage quiescent supply current                            | VCC = PVCC = 3.8 V                                                                                           |     | 320 | 410  | μА   |

| I <sub>QVCC</sub>    | VCC vs. GND         | VCC quiescent supply current                                         | SD/OD = LIN = 5 V;<br>HIN = 0 V;<br>BOOT = 7 V                                                               |     | 680 | 900  | μΑ   |

| I <sub>svcc</sub>    |                     | VCC switching supply current                                         | $\overline{SD}/OD = 5 \text{ V};$ $V_{BO} = 6.5 \text{ V};$ $VS = 0 \text{ V};$ $F_{SW} = 500 \text{ kHz}$   |     | 0.8 |      | mA   |

| Low-side             | driver section supp | ly                                                                   |                                                                                                              |     |     |      |      |

| I <sub>QPVCC</sub>   |                     | PVCC quiescent supply current                                        | SD/OD = LIN = 5 V                                                                                            |     | 150 |      | μA   |

| I <sub>SPVCC</sub>   | PVCC vs. PGND       | PVCC switching supply current                                        | VS = 0 V<br>F <sub>SW</sub> = 500 kHz                                                                        |     | 1.4 |      | mA   |

| R <sub>BLEED</sub>   | GL vs. PGND         | Low side gate bleeder                                                | PVCC = PGND                                                                                                  | 75  | 100 | 125  | kΩ   |

| RONL                 |                     | Low side turn on resistor                                            | I(GL) = 1 mA (source)                                                                                        |     | 50  |      | Ω    |

| ROFFL                |                     | Low side turn off resistor                                           | I(GL) = 1 mA (sink)                                                                                          |     | 2   |      | Ω    |

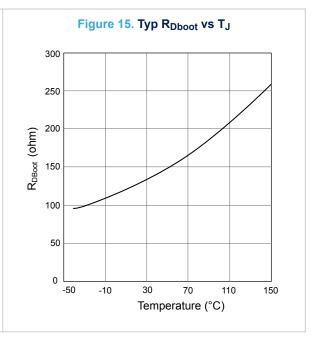

| High-side            | floating section su | oply                                                                 |                                                                                                              |     |     |      |      |

| V <sub>BOthON</sub>  |                     | V <sub>BO</sub> UV turn ON threshold <sup>(2)</sup>                  |                                                                                                              | 3.6 | 4.0 | 4.4  | V    |

| V <sub>BOthOFF</sub> |                     | V <sub>BO</sub> UV turn OFF threshold <sup>(2)</sup>                 |                                                                                                              | 3.4 | 3.7 | 4.0  | V    |

| V <sub>BOhys</sub>   |                     | V <sub>BO</sub> UV hysteresis <sup>(2)</sup>                         |                                                                                                              | 0.1 | 0.3 | 0.5  | V    |

| I <sub>QBOU</sub>    | BOOT vs. OUTb       | V <sub>BO</sub> undervoltage quiescent supply current <sup>(2)</sup> | V <sub>BO</sub> = 3.4 V                                                                                      |     | 140 | 200  | μA   |

| I <sub>QBO</sub>     |                     | V <sub>BO</sub> quiescent supply current <sup>(2)</sup>              | $V_{BO} = 6 \text{ V}$ ; LIN = GND;<br>$\overline{SD}/OD = \text{HIN} = 5 \text{ V}$ ;                       |     | 217 |      | μA   |

| I <sub>SBO</sub>     | воот                | BOOT switching supply current                                        | $V_{BO} = 6 \text{ V};$<br>$\overline{SD}/OD = 5 \text{ V};$<br>$VS = 0 \text{ V}; F_{SW} = 500 \text{ kHz}$ |     | 2   |      | mA   |

| I <sub>LK</sub>      | BOOT vs. SGND       | High voltage leakage current                                         | BOOT = OUT = 600 V                                                                                           |     |     | 11   | μA   |

| R <sub>DBoot</sub>   | VCC vs. BOOT        | Bootstrap diode on resistance <sup>(3)</sup>                         | SD/OD = LIN = 5 V;<br>HIN = GND = PGND                                                                       |     | 140 | 175  | Ω    |

DS13417 - Rev 3 page 7/27

| Symbol             |                    | Parameter                          | Test condition                                                    | Min | Тур  | Max  | Unit |

|--------------------|--------------------|------------------------------------|-------------------------------------------------------------------|-----|------|------|------|

|                    |                    |                                    | VCC – BOOT = 0.5 V                                                |     |      |      |      |

| RON <sub>H</sub>   |                    | High side turn on resistor         | I(GH) = 1 mA (source)                                             |     | 50   |      | Ω    |

| ROFF <sub>H</sub>  |                    | High side turn off resistor        | I(GH) = 1 mA (sink)                                               |     | 2    |      | Ω    |

| Logic inpu         | ıts                |                                    | '                                                                 |     |      |      |      |

| V                  |                    | Lavidaval lavia threadadh valtara  | T <sub>J</sub> = 25°C                                             | 1.1 | 1.31 | 1.45 | V    |

| V <sub>il</sub>    |                    | Low level logic threshold voltage  | Full Temperature range <sup>(4)</sup>                             | 0.8 |      |      | V    |

|                    | LIN, HIN, SD/OD    | High level logic threshold         | T <sub>J</sub> = 25°C                                             | 2   | 2.17 | 2.5  | .,   |

| $V_{ih}$           |                    | voltage                            | Full Temperature range <sup>(4)</sup>                             |     |      | 2.7  | V    |

| V <sub>ihys</sub>  |                    | Logic input threshold hysteresis   |                                                                   | 0.7 | 0.96 | 1.2  | V    |

| I <sub>INh</sub>   |                    | Logic '1' input bias current       | LIN, HIN = 5 V                                                    | 23  | 33   | 55   | μA   |

| I <sub>INI</sub>   | LIN, HIN           | Logic '0' input bias current       | LIN, HIN = GND                                                    |     |      | 1    | μA   |

| R <sub>PD_IN</sub> |                    | Input pull-down resistor           | LIN, HIN = 5 V                                                    | 90  | 150  | 220  | kΩ   |

| I <sub>SDh</sub>   | SD/OD              | Logic "1" input bias current       | <u>SD</u> /OD = 5 V                                               | 11  | 15   | 20   | μA   |

| I <sub>SDI</sub>   | SD/OD              | Logic "0" input bias current       | <u>SD</u> /OD = 0 V                                               |     |      | 1    | μA   |

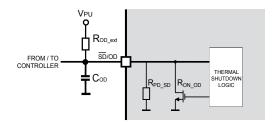

| R <sub>PD_SD</sub> | SD/OD              | Pull-down resistor                 | SD/OD = 5 V<br>OpenDrain OFF                                      | 250 | 330  | 450  | kΩ   |

| V <sub>TSD</sub>   | SD/OD              | Thermal shutdown unlatch threshold | T <sub>J</sub> = 25°C <sup>(5)</sup>                              | 0.5 | 0.75 | 1    | V    |

| R <sub>ON_OD</sub> | SD/OD              | Open drain ON resistance           | T <sub>J</sub> = 25°C;<br>I <sub>OD</sub> = 400 mV <sup>(5)</sup> | 8   | 10   | 18   | Ω    |

| I <sub>OL_OD</sub> | SD/OD              | Open Drain low level sink current  | $T_J = 25^{\circ}C;$<br>$V_{OD} = 400 \text{ mV}^{(5)}$           | 22  | 40   | 50   | mA   |

| Over temp          | erature protection |                                    |                                                                   |     |      |      |      |

| T <sub>TSD</sub>   |                    | Shutdown temperature               | (4)                                                               |     | 175  |      | °C   |

| T <sub>HYS</sub>   |                    | Temperature hysteresis             | (4)                                                               |     | 20   |      | °C   |

|                    |                    |                                    |                                                                   |     |      |      |      |

- 1. VCC UVLO is referred to VCC GND.

- 2.  $V_{BO} = V_{BOOT} V_{OUT}$ .

- 3.  $R_{BD(on)}$  is tested in the following way:

$R_{BD(on)} = \left[ (VCC - V_{BOOTa}) - (VCC - V_{BOOTb}) \right] / \left[ I_a - I_b \right]$

Where:  $I_a$  is BOOT pin current when  $V_{BOOT} = V_{BOOTa}$ ;  $I_b$  is BOOT pin current when  $V_{BOOT} = V_{BOOTb}$

- 4. Range estimated by characterization, not tested in production.

- 5. Tested on wafer.

#### 4.2 **GaN** power transistor

Table 6. GaN power transistor electrical characteristics ( $V_{GS} = 6 \text{ V}$ ;  $T_J = 25^{\circ}\text{C}$ , unless otherwise specified.)

| Symbol              | Parameter                      | Test condition                                   | Min | Тур | Max | Unit |

|---------------------|--------------------------------|--------------------------------------------------|-----|-----|-----|------|

| GaN on/off states   |                                |                                                  |     |     |     |      |

| V <sub>(BR)DS</sub> | Drain-source breakdown voltage | $I_{DSS} < 18 \ \mu A^{(1)}$<br>$V_{GS} = 0 \ V$ | 650 |     |     | V    |

DS13417 - Rev 3 page 8/27

| Symbol              | Parameter                                        | Test condition                                          |                                              | Min | Тур | Max | Unit |

|---------------------|--------------------------------------------------|---------------------------------------------------------|----------------------------------------------|-----|-----|-----|------|

|                     |                                                  | V <sub>DS</sub> = 600 V                                 |                                              |     | 0.7 |     |      |

| DSS                 | I <sub>DSS</sub> Zero gate voltage drain current |                                                         | V <sub>GS</sub> = 0 V                        |     | 0.7 |     | μΑ   |

| V <sub>GS(th)</sub> | Gate threshold voltage                           | V <sub>DS</sub> = V <sub>GS, ID</sub>                   | $V_{DS} = V_{GS, ID} = 2.5 \text{ mA}^{(1)}$ |     | 1.7 |     | V    |

| I <sub>GS</sub>     | Gate to source voltage                           | V <sub>DS</sub> = 0 V <sup>(2)</sup>                    |                                              |     | 57  |     | μA   |

| D                   | Chatia dualin accurac au usalatan ac             | L = 2 2 A                                               | T <sub>J</sub> = 25°C                        |     | 150 | 220 | 0    |

| R <sub>DS(on)</sub> | Static drain-source on-resistance                | $I_D = 3.2 \text{ A}$ $T_J = 125^{\circ}\text{C}^{(2)}$ |                                              |     | 330 |     | mΩ   |

<sup>1.</sup> Tested on wafer.

DS13417 - Rev 3 page 9/27

<sup>2.</sup> Value estimated by characterization, not tested in production.

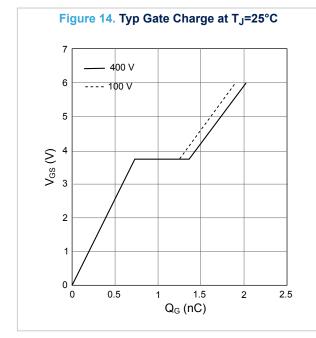

#### 5 Device characterization values

The information in Table 7 and Table 8 represents typical values based on characterization and simulation results and are not subject to the production test.

Table 7. GaN power transistor characterization values

| Symbol             | Parameter                                                  | Test condition                                   | Min | Тур | Max | Unit |

|--------------------|------------------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|

|                    |                                                            | V <sub>GS</sub> = 6 V,                           |     |     |     |      |

| $Q_G$              | Total gate charge                                          | T <sub>J</sub> = 25°C                            |     | 2   |     | nC   |

|                    |                                                            | V <sub>DS</sub> = 0 to 400 V                     |     |     |     |      |

| Q <sub>OSS</sub>   | Output charge                                              | V0V                                              |     | 20  |     | nC   |

| E <sub>OSS</sub>   | Output capacitance stored energy                           | $V_{GS} = 0 \text{ V},$ $V_{DS} = 400 \text{ V}$ |     | 2.7 |     | μJ   |

| C <sub>OSS</sub>   | Output capacitance                                         | , ADS +400 A                                     |     | 20  |     | pF   |

| C <sub>O(ER)</sub> | Effective output capacitance energy related <sup>(1)</sup> | V <sub>GS</sub> = 0 V,                           |     | 31  |     | pF   |

| C <sub>O(TR)</sub> | Effective output capacitance time related <sup>(2)</sup>   | V <sub>DS</sub> = 0 to 400 V                     |     | 50  |     | pF   |

| Q <sub>RR</sub>    | Reverse recovery charge                                    |                                                  |     | 0   |     | nC   |

| I <sub>RRM</sub>   | Reverse recovery current                                   |                                                  |     | 0   |     | Α    |

C<sub>O(ER)</sub> is the fixed capacitance that would give the same stored energy as C<sub>OSS</sub> while V<sub>DS</sub> is rising from 0 V to the stated V<sub>DS</sub>

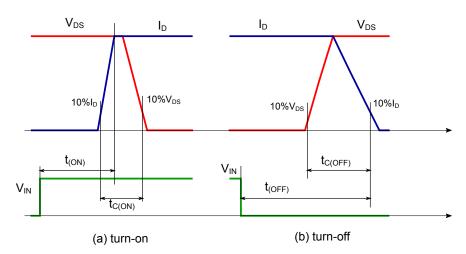

Table 8. Inductive load switching characteristics

| Symbol                             | Parameter                                   | Test condition                         | Min | Тур  | Max | Unit |

|------------------------------------|---------------------------------------------|----------------------------------------|-----|------|-----|------|

| t <sub>(on)</sub> <sup>(1)</sup>   | Turn-on time                                |                                        |     | 70   |     | ns   |

| t <sub>C(on)</sub> <sup>(2)</sup>  | Crossover time (on)                         |                                        |     | 15   |     | ns   |

| t(off) <sup>(1)</sup>              | Turn-off time                               | VS = 400 V,                            |     | 70   |     | ns   |

| t <sub>C(off)</sub> <sup>(2)</sup> | Crossover time (off)                        | $V_{GS} = 6 V$                         |     | 15   |     | ns   |

| t <sub>SD</sub>                    | Shutdown to high/low-side propagation delay | I <sub>D</sub> = 3.2 A<br>See Figure 3 |     | 70   |     | ns   |

| E <sub>on</sub>                    | Turn-on switching losses                    |                                        |     | 12.5 |     | μJ   |

| E <sub>off</sub>                   | Turn-off switching losses                   |                                        |     | 2.5  |     | μJ   |

<sup>1.</sup>  $t_{(on)}$  and  $t_{(off)}$  include the propagation delay time of the internal driver

DS13417 - Rev 3 page 10/27

<sup>2.</sup>  $C_{O(TR)}$  is the fixed capacitance that would give the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 V to the stated  $V_{DS}$

<sup>2.</sup>  $t_{C(on)}$  and  $t_{C(off)}$  are the switching times of GaN transistor itself under the internally given gate driving conditions

Figure 3. Switching time definition

DS13417 - Rev 3 page 11/27

DS13417 - Rev 3 page 12/27

DS13417 - Rev 3 page 13/27

DS13417 - Rev 3 page 14/27

#### 6 Functional description

#### 6.1 Logic inputs

The MASTERGAN1 features a half-bridge gate driver with three logic inputs to control the internal high-side and low-side GaN transistors.

The devices are controlled through the following logic inputs:

- SD/OD: Shutdown input, active low;

- LIN: low-side driver inputs, active high;

- HIN: high-side driver inputs, active high.

| In    | Input pins GaN transistors status |                  |     | stors status |

|-------|-----------------------------------|------------------|-----|--------------|

| SD/OD | LIN                               | HIN              | LS  | HS           |

| L     | X <sup>(1)</sup>                  | X <sup>(1)</sup> | OFF | OFF          |

| Н     | L                                 | L                | OFF | OFF          |

| Н     | L                                 | Н                | OFF | ON           |

| Н     | Н                                 | L                | ON  | OFF          |

| Н     | H <sup>(2)</sup>                  | H <sup>(2)</sup> | OFF | OFF          |

Table 9. Inputs truth table (applicable when device is not in UVLO)

- 1. X: Don't care

- 2. Interlocking

The logic inputs have internal pull-down resistors. The purpose of these resistors is to set a proper logic level in case, for example, there is an interruption in the logic lines or the controller outputs are in tri-state conditions.

If logic inputs are left floating, the gate driver outputs are set to low level and the correspondent GaN transistors are turned off.

The internal logic is able to transfer the control signal pulse longer than  $T_{IN\_MIN}$  = 120 ns and introduces a very short propagation delay to output.

#### 6.2 Bootstrap structure

A bootstrap circuitry is typically used to supply the high-voltage section. MASTERGAN1 integrates this structure, realized by a patented integrated high-voltage DMOS, to reduce the external components.

The Boostrap integrated circuit is connected to VCC pin and is driven synchronously with the low-side driver.

The use of an external bootstrap diode in parallel to the integrated structure is possible, in particular if the operating frequency is approximately higher than 500 kHz.

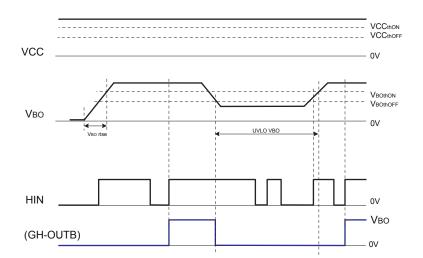

#### 6.3 VCC supply pins and UVLO function

The VCC pin supplies current to the logic circuit, level-shifters in the low-side section and the integrated bootstrap diode.

The PVCC pin supplies low-side output buffer. During output commutations the average current used to provide gate charge to the high-side and low-side GaN transistors flows through this pin.

The PVCC pin can be connected either to the same supply voltage of the VCC pin or to a separated voltage source. In case the same voltage source is used, it is suggested to connect VCC and PVCC pins by means of a small decoupling resistance. The use of dedicated bypass ceramic capacitors located as close as possible to each supply pin is highly recommended.

DS13417 - Rev 3 page 15/27

The MASTERGAN1 VCC supply voltage is continuously monitored by an under-voltage lockout (UVLO) circuitry that turns both the high-side and low-side GaN transistors off when the supply voltage goes below the  $V_{CC\_thOFF}$  threshold. The UVLO circuitry turns on the GaN, according to LIN and HIN status, as soon as the supply voltage goes above the  $V_{CCthON}$  voltage. A  $V_{CChys}$  hysteresis is provided for noise rejection purpose.

Figure 16. VCC UVLO and Low Side

#### 6.4 V<sub>BO</sub> UVLO protection

Dedicated undervoltage protection is available on the bootstrap section between BOOT and OUTb supply pins. In order to avoid intermittent operation, a hysteresis sets the turn-off threshold with respect to the turn-on threshold. When  $V_{BO}$  voltage goes below  $V_{BOthOFF}$  threshold the high-side GaN transistor is switched off. When  $V_{BO}$  voltage reaches  $V_{BOthON}$  threshold the device returns to normal operation and the output remains off until the detection of the HIN pin's rising edge, that activates the high side transistor's turn-on.

Figure 17. V<sub>BO</sub> UVLO and High Side

DS13417 - Rev 3 page 16/27

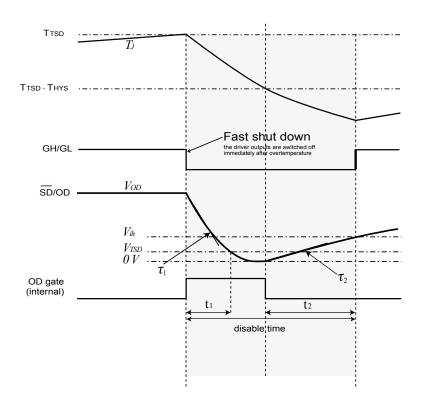

#### 6.5 Thermal shutdown

The integrated gate driver has a thermal shutdown protection.

When junction temperature reaches the  $T_{TSD}$  temperature threshold, the device turns off both GaN transistors leaving the half-bridge in 3-state and signaling the state forcing  $\overline{SD}/OD$  pin low.  $\overline{SD}/OD$  pin is released when junction temperature is below  $T_{TSD}$ - $T_{HYS}$  and  $\overline{SD}/OD$  is below  $V_{TSD}$ .

GaN are driven again according to inputs when SD/OD rises above Vih.

The thermal smart shutdown system gives the possibility to increase the time constant of the external RC network (that determines the disable time after the overtemperature event) up to very large values without delaying the protection.

Figure 18. Thermal shutdown timing waveform

DS13417 - Rev 3 page 17/27

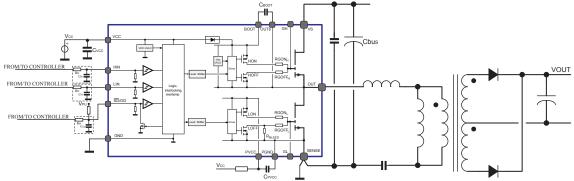

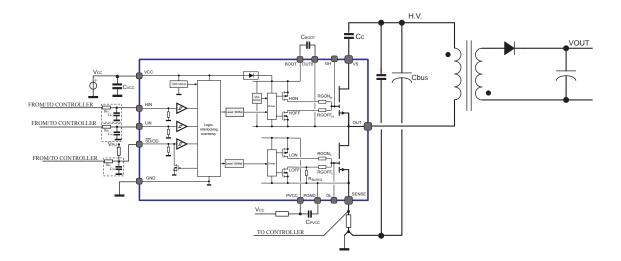

### **Typical application diagrams**

Figure 19. Typical application diagram – Resonant LLC converter

Figure 20. Typical application diagram – Active clamp flyback

DS13417 - Rev 3 page 18/27

### 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

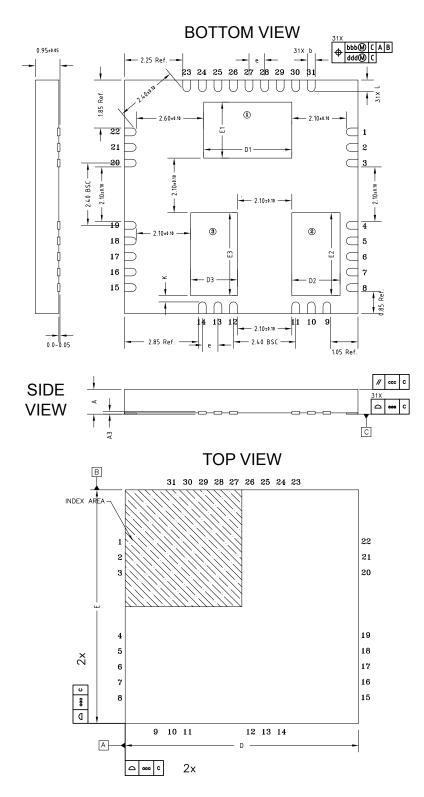

#### 8.1 QFN 9 x 9 x 1 mm, 31 leads, pitch 0.6 mm package information

Table 10. QFN 9 x 9 x 1 mm package dimensions

| Symbol | Dimensions (mm) |      |      |  |

|--------|-----------------|------|------|--|

|        | Min.            | Тур. | Max. |  |

| A      | 0.90            | 0.95 | 1.00 |  |

| A3     |                 | 0.10 |      |  |

| b      | 0.25            | 0.30 | 0.35 |  |

| D      | 8.96            | 9.00 | 9.04 |  |

| Е      | 8.96            | 9.00 | 9.04 |  |

| D1     | 3.30            | 3.40 | 3.50 |  |

| E1     | 2.06            | 2.16 | 2.26 |  |

| D2     | 1.76            | 1.86 | 1.96 |  |

| E2     | 3.10            | 3.20 | 3.30 |  |

| D3     | 1.70            | 1.80 | 1.90 |  |

| E3     | 3.10            | 3.20 | 3.30 |  |

| е      |                 | 0.60 |      |  |

| К      |                 | 0.24 |      |  |

| L      | 0.35            | 0.45 | 0.55 |  |

| N      |                 | 31   |      |  |

| aaa    |                 | 0.10 |      |  |

| bbb    |                 | 0.10 |      |  |

| ccc    | 0.10            |      |      |  |

| ddd    | 0.05            |      |      |  |

| eee    | 0.08            |      |      |  |

Note:

- 1. Dimensioning and tolerances conform to ASME Y14.5-2009.

- 2. All dimensions are in millimeters.

- 3. N total number of terminals.

- 4. Dimensions do not include mold protrusion, not to exceed 0.15 mm.

- 5. Package outline exclusive of metal burr dimensions.

DS13417 - Rev 3 page 19/27

Figure 21. QFN 9 x 9 x 1 mm package dimensions

DS13417 - Rev 3 page 20/27

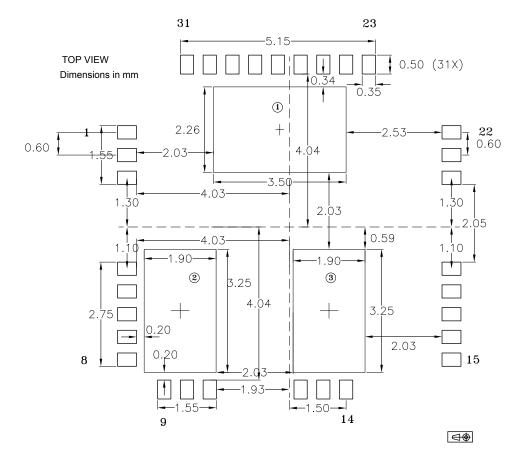

### 9 Suggested footprint

The MASTERGAN1 footprint for the PCB layout is usually defined based on several design factors such as assembly plant technology capabilities and board component density. For easy device usage and evaluation, ST provides the following footprint design, which is suitable for the largest variety of PCBs.

The following footprint indicates the copper area which should be free from the solder mask, while the copper area shall extend beyond the indicated areas especially for EP2 and EP3. To aid thermal dissipation, it is recommended to add thermal vias under these EPADs to transfer and dissipate device heat to the other PCB copper layers. A PCB layout example is available with the MASTERGAN1 evaluation board.

Figure 22. Suggested footprint (top view drawing)

DS13417 - Rev 3 page 21/27

### 10 Ordering information

Table 11. Order codes

| Order code   | Package          | Package Marking | Packaging     |

|--------------|------------------|-----------------|---------------|

| MASTERGAN1   | QFN 9 x 9 x 1 mm | MASTERGAN1      | Tray          |

| MASTERGAN1TR | QFN 9 x 9 x 1 mm | MASTERGAN1      | Tape and Reel |

DS13417 - Rev 3 page 22/27

### **Revision history**

**Table 12. Document revision history**

| Date        | Version | Changes                                                                                                                                                            |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Jul-2020 | 1       | Initial release.                                                                                                                                                   |

| 10-Aug-2020 | 2       | Changed R <sub>DS(on)</sub> unit in Table 6                                                                                                                        |

| 21-Oct-2020 | 3       | Changed Figure 1, Figure 2, Figure 13, Figure 19 and Figure 20; added test conditions of some parameters in Table 2 and Table 5; updated text in Section Features. |

DS13417 - Rev 3 page 23/27

### **Contents**

| 1                 | Bloc   | k diagram                                                    | 2    |

|-------------------|--------|--------------------------------------------------------------|------|

| 2                 | Pin c  | lescription and connection diagram                           | 3    |

|                   | 2.1    | Pin list                                                     | 3    |

| 3 Electrical Data |        | rical Data                                                   | 5    |

|                   | 3.1    | Absolute maximum ratings                                     | 5    |

|                   | 3.2    | Recommended operating conditions                             | 6    |

|                   | 3.3    | Thermal data                                                 | 6    |

| 4                 | Elect  | trical characteristics                                       | 7    |

|                   | 4.1    | Driver                                                       | 7    |

|                   | 4.2    | GaN power transistor                                         | 8    |

| 5                 | Devi   | ce characterization values                                   | .10  |

| 6                 | Fund   | tional description                                           | .15  |

|                   | 6.1    | Logic inputs                                                 | . 15 |

|                   | 6.2    | Bootstrap structure                                          | . 15 |

|                   | 6.3    | VCC supply pins and UVLO function                            | . 15 |

|                   | 6.4    | V <sub>BO</sub> UVLO protection                              | . 16 |

|                   | 6.5    | Thermal shutdown                                             | . 17 |

| 7                 | Typic  | cal application diagrams                                     | .18  |

| 8                 | Pack   | age information                                              | .19  |

|                   | 8.1    | QFN 9 x 9 x 1 mm, 31 leads, pitch 0.6 mm package information | . 19 |

| 9                 | Sugg   | gested footprint                                             | .21  |

| 10                | Orde   | ring information                                             | .22  |

| Rev               | ision  | history                                                      | .23  |

| Con               | tents  |                                                              | .24  |

| List              | of tab | oles                                                         | .25  |

| List              | of fig | ures                                                         | .26  |

### **List of tables**

| Table 1.  | Pin description                                                                                                             | . 3 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings (each voltage referred to GND unless otherwise specified)                                          | . 5 |

| Table 3.  | Recommended operating conditions (Each voltage referred to GND unless otherwise specified)                                  | . 6 |

| Table 4.  | Thermal data                                                                                                                | . 6 |

| Table 5.  | Driver electrical characteristics: VCC = PVCC = 6 V; SENSE = GND; T <sub>J</sub> = 25°C, unless otherwise specified (Each   | h   |

|           | voltage referred to GND unless otherwise specified.)                                                                        | . 7 |

| Table 6.  | GaN power transistor electrical characteristics (V <sub>GS</sub> = 6 V; T <sub>J</sub> = 25°C, unless otherwise specified.) | . 8 |

| Table 7.  | GaN power transistor characterization values                                                                                | 10  |

| Table 8.  | Inductive load switching characteristics                                                                                    | 10  |

| Table 9.  | Inputs truth table (applicable when device is not in UVLO)                                                                  | 15  |

| Table 10. | QFN 9 x 9 x 1 mm package dimensions                                                                                         | 19  |

| Table 11. | Order codes                                                                                                                 | 22  |

| Table 12. | Document revision history                                                                                                   | 23  |

DS13417 - Rev 3 page 25/27

### **List of figures**

| Figure 1.  | Block diagram                                                       | . 2 |

|------------|---------------------------------------------------------------------|-----|

| Figure 2.  | Pin connection (top view)                                           | . 3 |

| Figure 3.  | Switching time definition                                           | 11  |

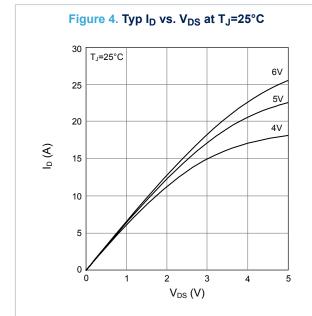

| Figure 4.  | Typ $I_D$ vs. $V_{DS}$ at $T_J$ =25°C                               | 11  |

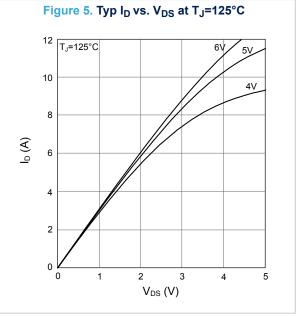

| Figure 5.  | Typ $I_D$ vs. $V_{DS}$ at $T_J$ =125°C                              | 11  |

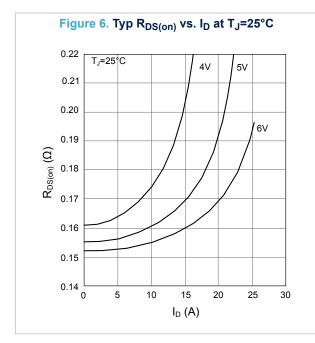

| Figure 6.  | Typ R <sub>DS(on)</sub> vs. I <sub>D</sub> at T <sub>J</sub> =25°C  | 12  |

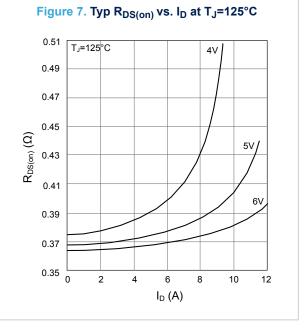

| Figure 7.  | Typ R <sub>DS(on)</sub> vs. I <sub>D</sub> at T <sub>J</sub> =125°C | 12  |

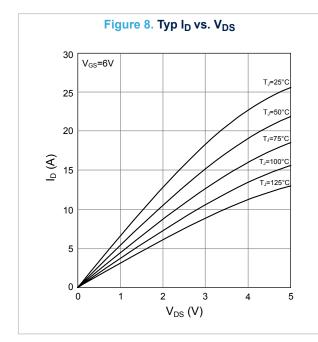

| Figure 8.  | Typ $I_D$ vs. $V_{DS}$                                              | 12  |

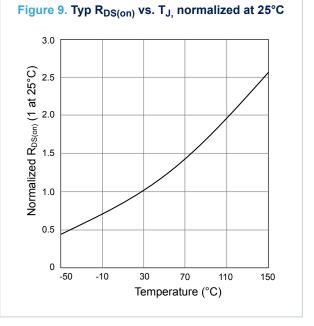

| Figure 9.  | Typ R <sub>DS(on)</sub> vs. T <sub>J,</sub> normalized at 25°C      | 12  |

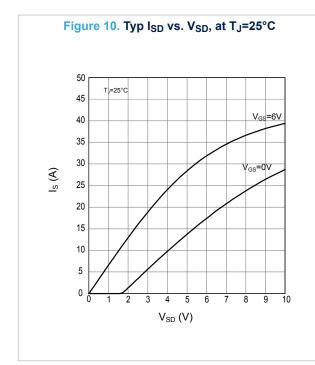

| Figure 10. | Typ I <sub>SD</sub> vs. V <sub>SD</sub> , at T <sub>J</sub> =25°C   | 13  |

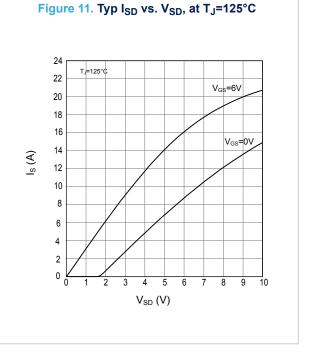

| Figure 11. | Typ I <sub>SD</sub> vs. V <sub>SD</sub> , at T <sub>J</sub> =125°C  | 13  |

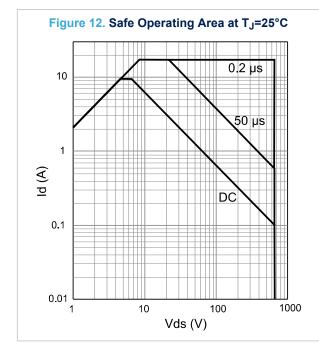

| Figure 12. | Safe Operating Area at T <sub>J</sub> =25°C                         | 13  |

| Figure 13. | Derating curve                                                      | 13  |

| Figure 14. | Typ Gate Charge at T <sub>J</sub> =25°C                             | 14  |

| Figure 15. | Typ R <sub>Dboot</sub> vs T <sub>J</sub>                            | 14  |

| Figure 16. | VCC UVLO and Low Side                                               | 16  |

| Figure 17. | V <sub>BO</sub> UVLO and High Side                                  | 16  |

| Figure 18. | Thermal shutdown timing waveform                                    |     |

| Figure 19. | Typical application diagram – Resonant LLC converter                |     |

| Figure 20. | Typical application diagram – Active clamp flyback                  |     |

| Figure 21. | QFN 9 x 9 x 1 mm package dimensions                                 |     |

| Figure 22. | Suggested footprint (top view drawing)                              | 21  |

DS13417 - Rev 3 page 26/27

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics - All rights reserved

DS13417 - Rev 3 page 27/27

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

00053P0231 56956 57.404.7355.5 LT4936 57.904.0755.0 5882900001 00600P0005 00-9050-LRPP 00-9090-RDPP 5951900000 011003W-10/32-15 0131700000 00-2240 LTP70N06 LVP640 5J0-1000LG-SIL LY1D-2-5S-AC120 LY2-US-AC240 LY3-UA-DC24

00576P0020 00600P0010 LZN4-UA-DC12 LZNQ2M-US-DC5 LZNQ2-US-DC12 LZP40N10 00-8196-RDPP 00-8274-RDPP 00-8275RDNP 00-8722-RDPP 00-8728-WHPP 00-8869-RDPP 00-9051-RDPP 00-9091-LRPP 00-9291-RDPP 0207100000 0207400000 01312

0134220000 60713816 M15730061 61161-90 61278-0020 6131-204-23149P 6131-205-17149P 6131-209-15149P 6131-218-17149P 6131220-21149P 6131-260-2358P 6131-265-11149P CS1HCPU63