# PM6652

Datasheet – production data

### Single-phase controller for Intel<sup>®</sup> MVP 6.5 render voltage regulator, CPU and VR11 CPU

### Features

- 4.5 V to 36 V input voltage range

- 0.3 V to 1.5 V output voltage range

- IMVP6.5 GPU/CPU and VR11 CPU mode selection

- Very fast load transient response using constant-on-time loop control

- Remote voltage sensing

- Programmable droop function

- 7-bit dynamic voltage positioning (VID)

- Programmable PWM frequency

- Lossless current sense with inductor DCR

- Accurate inductor current sense with R<sub>SENSE</sub>

- Negative current limit

- Boot diode embedded

- Latched OVP, UVP and overtemperature

- Pulse-skipping when suspend state is selected

- Output voltage ripple compensation

- Soft-start and soft-end

- Power good available

- Current monitor (IMON)

- Thermal throttling

### Applications

- Intel mobile graphic core IMVP6.5

- Intel mobile CPU IMVP6.5

- Intel ATOM<sup>®</sup> VR11 based devices

- Notebook, netbook and nettop computers

- Handheld devices and PDAs

#### Table 1.Device summary

| Order codes | Package                              | Packaging     |

|-------------|--------------------------------------|---------------|

| PM6652      | VFQFPN-32 5 x 5 mm (exposed pad)     | Tray          |

| PM6652TR    | vr Qr Fiv-52 5 x 5 min (exposed pad) | Tape and reel |

March 2012

Doc ID 16867 Rev 5

### Description

The PM6652 is a single-phase, step-down SMPS controller with high precision 7-bit DAC. It has been designed to supply the CPU and the graphics core (render engine) of the Intel<sup>®</sup> mobile platform, according to Intel MVP6.5 specifications.

The PM6652 can also be configured to supply the 7-bit family, VR11 compliant, ATOM  $^{\textcircled{R}}$  processors.

The controller, based on constant on-time (COT) architecture, allows real-time dynamic switching of the core operating voltages and frequencies, working in both performance and suspend render states.

An embedded integrator control loop compensates the DC voltage error due to the output ripple.

The high efficiency at light load, achieved with pulse-skipping working mode, and the extremely low shutdown and quiescent adsorbed current, make the PM6652 the ideal choice in battery powered devices.

This is information on a product in full production.

### Contents

| 1        | Туріс    | application circuit6                    |  |  |  |  |

|----------|----------|-----------------------------------------|--|--|--|--|

| 2        | Pin s    | ettings                                 |  |  |  |  |

|          | 2.1      | Connections                             |  |  |  |  |

|          | 2.2      | Pin description                         |  |  |  |  |

| 3        | Elect    | rical data                              |  |  |  |  |

|          | 3.1      | Maximum rating                          |  |  |  |  |

|          | 3.2      | Thermal data                            |  |  |  |  |

|          | 3.3      | Recommended operating conditions        |  |  |  |  |

| 4        |          | rical characteristics                   |  |  |  |  |

| 5        | Volta    | ge identification (VID) 15              |  |  |  |  |

| 6        | Туріс    | al operating characteristics            |  |  |  |  |

| 7        | Block    | c diagram                               |  |  |  |  |

| 8        | Devic    | e description                           |  |  |  |  |

|          | 8.1      | Constant on-time PWM control 24         |  |  |  |  |

|          | .0.      | 8.1.1 Constant on-time PWM architecture |  |  |  |  |

|          | <u>S</u> | 8.1.2 Output ripple compensation        |  |  |  |  |

| ~~°      | 8.2      | Mode selection                          |  |  |  |  |

| <u>}</u> | 8.3      | Pulse-skip working mode                 |  |  |  |  |

|          | 8.4      | Differential remote sensing             |  |  |  |  |

|          | 8.5      | Droop function                          |  |  |  |  |

|          | 8.6      | Voltage dynamic (VID) transitions       |  |  |  |  |

|          | 8.7      | Current sensing                         |  |  |  |  |

|          | 8.8      | Soft-start and soft-end 32              |  |  |  |  |

|          | 8.9      | Internal MOS drivers                    |  |  |  |  |

|          | 8.10     | Monitoring and protection               |  |  |  |  |

|          |          | 8.10.1 Power good                       |  |  |  |  |

|             |      | 8.10.2    | Current monitor (IMON)                               | 34   |

|-------------|------|-----------|------------------------------------------------------|------|

|             |      | 8.10.3    | Thermal throttling                                   | 36   |

|             |      | 8.10.4    | Overvoltage protection                               | 37   |

|             |      | 8.10.5    | Undervoltage protection                              | 37   |

|             |      | 8.10.6    | Overcurrent protection                               | 38   |

|             |      | 8.10.7    | SVCC undervoltage protection                         | 39   |

|             |      | 8.10.8    | Thermal protection                                   | 39   |

|             | 8.11 | System    | accuracy                                             | . 40 |

|             |      | 8.11.1    | VCORE accuracy                                       | 40   |

|             |      | 8.11.2    | Current reporting (IMON) accuracy                    | . 41 |

| 9           | Appl | ication   | ideas                                                | . 43 |

|             | 9.1  | Load tr   | ansient response improvement with feedback capacitor | . 43 |

|             | 9.2  | Voltage   | e regulation without droop                           | . 45 |

| 10          | Layo | out guide | elines                                               | . 48 |

| 11          | Pack | age me    | chanical data                                        | . 49 |

| 12          | Revi | sion his  | tory                                                 | . 51 |

| 12<br>00501 | ete  | Pro       | AUCIN                                                |      |

| 0v          |      |           |                                                      |      |

# List of figures

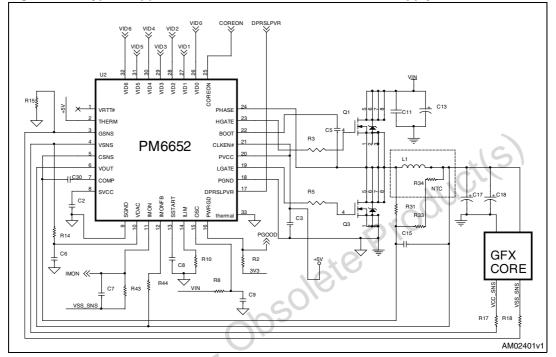

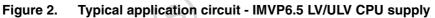

| Figure 1.  | Typical application circuit - IMVP6.5 render core supply         | 6    |

|------------|------------------------------------------------------------------|------|

| Figure 2.  | Typical application circuit - IMVP6.5 LV/ULV CPU supply          | 6    |

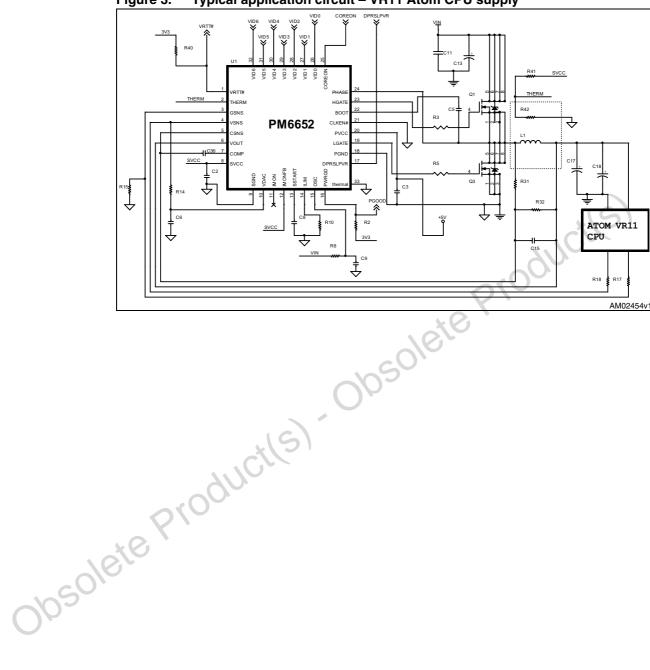

| Figure 3.  | Typical application circuit – VR11 Atom CPU supply               | 7    |

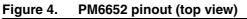

| Figure 4.  | PM6652 pinout (top view)                                         |      |

| Figure 5.  | Pin functions                                                    | 8    |

| Figure 6.  | VCORE turn-on and PGOOD rising - no load                         | . 19 |

| Figure 7.  | VCORE turn-on - CPU IMVP6.5 mode                                 | . 19 |

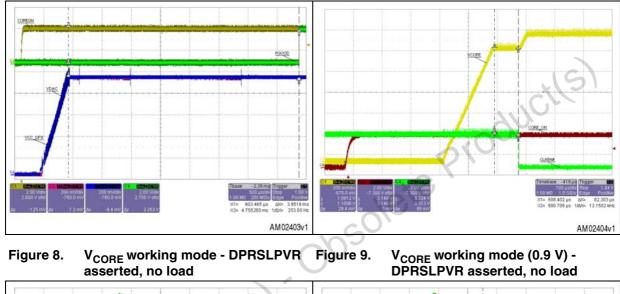

| Figure 8.  | VCORE working mode - DPRSLPVR asserted, no load                  | . 19 |

| Figure 9.  | VCORE working mode (0.9 V) - DPRSLPVR asserted, no load          | . 19 |

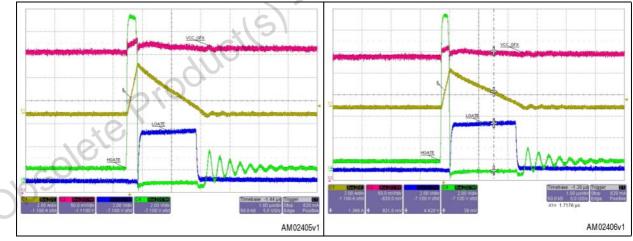

| Figure 10. | VCORE working mode (0.4 V) - DPRSLPVR asserted, no load          | . 20 |

| Figure 11. | VCORE working mode - DPRSLPVR not asserted, no load              | . 20 |

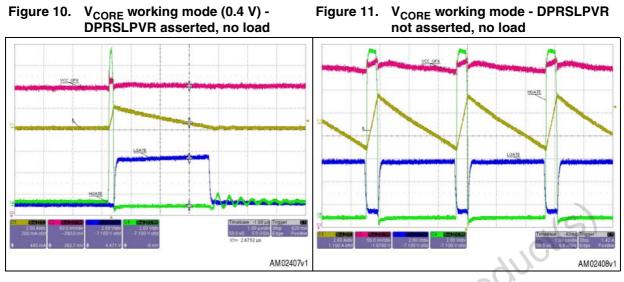

| Figure 12. | VCORE working mode - DPRSLPVR not asserted, 10 A load            | . 20 |

| Figure 13. | VCORE working mode (0.9 V) - DPRSLPVR not asserted, no load      | . 20 |

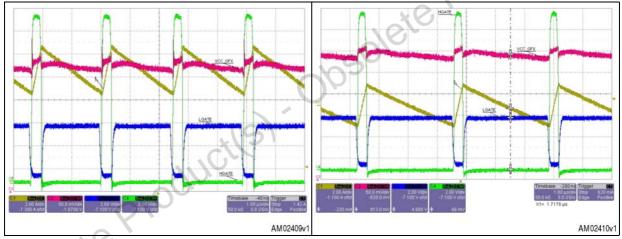

| Figure 14. | VCORE working mode (0.4 V) - DPRSLPVR not asserted, no load.     | . 20 |

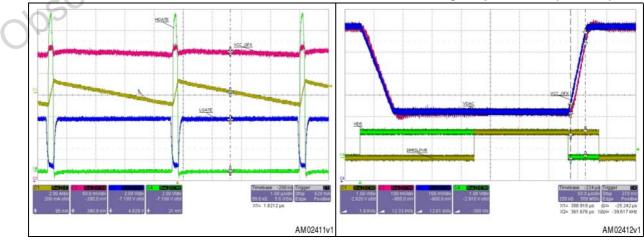

| Figure 15. | VID5 transition - entering and exiting suspend state (fast exit) |      |

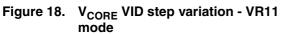

| Figure 16. | VID5 transition - entering and exiting suspend state (slow exit) | . 21 |

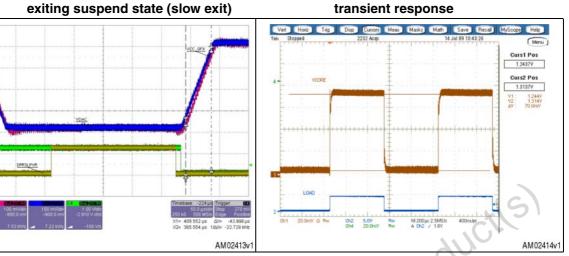

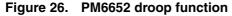

| Figure 17. | Droop function - 5 A to 15 A transient response.                 | . 21 |

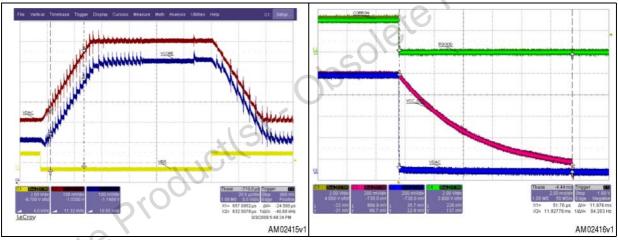

| Figure 18. | VCORE VID step variation - VR11 mode                             | . 21 |

| Figure 19. | VCORE soft-end - COREON pin de-assertion and PGOOD transition.   |      |

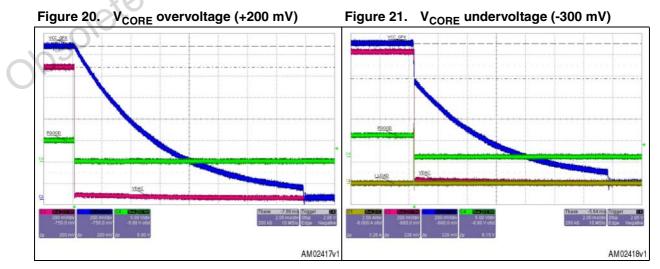

| Figure 20. | VCORE overvoltage (+200 mV)                                      |      |

| Figure 21. | VCORE undervoltage (-300 mV)                                     |      |

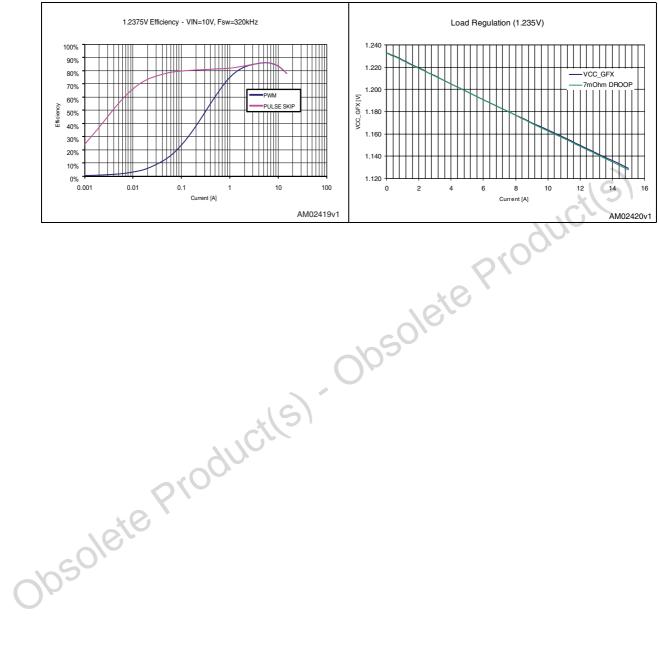

| Figure 22. | VCORE efficiency (DPRSLPVR high and low)                         |      |

| Figure 23. | VCORE load regulation - droop function                           |      |

| Figure 24. | Simplified block diagram.                                        | . 23 |

| Figure 25. | PM6652 integrator                                                | . 27 |

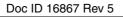

| Figure 26. | PM6652 droop function                                            |      |

| Figure 27. | GFX supply - VID step, skip mode                                 |      |

| Figure 28. | CPU IMVP6.5 - VID step, skip mode                                |      |

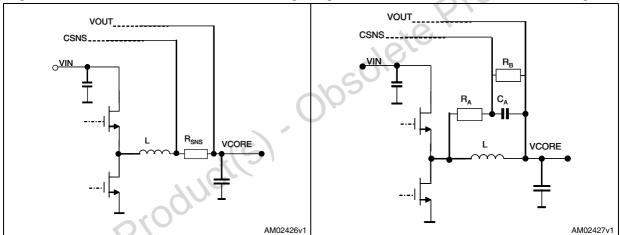

| Figure 29. | Precision resistor current sensing.                              |      |

| Figure 30. | Inductor's DCR current sensing                                   |      |

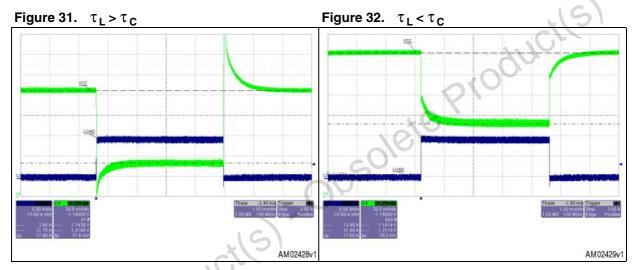

| Figure 31. | τL>τC                                                            |      |

| Figure 32. | τL < τC                                                          | . 31 |

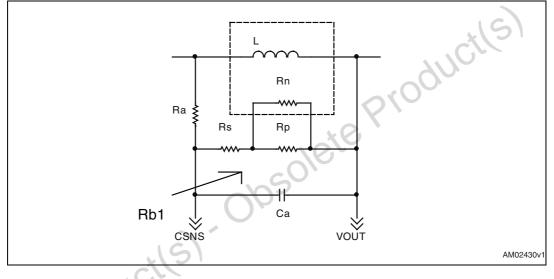

| Figure 33. | Thermal compensation network                                     | . 32 |

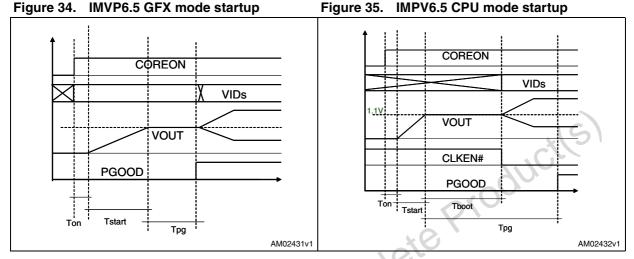

| Figure 34. | IMVP6.5 GFX mode startup                                         |      |

| Figure 35. | IMPV6.5 CPU mode startup                                         | . 33 |

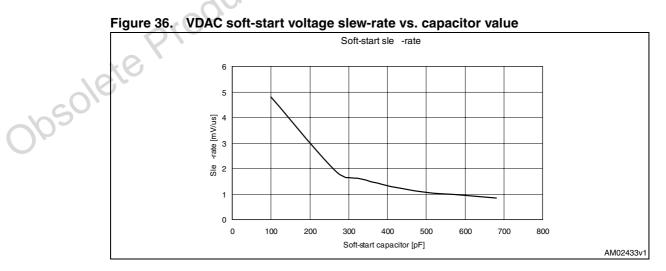

| Figure 36. | VDAC soft-start voltage slew-rate vs. capacitor value            |      |

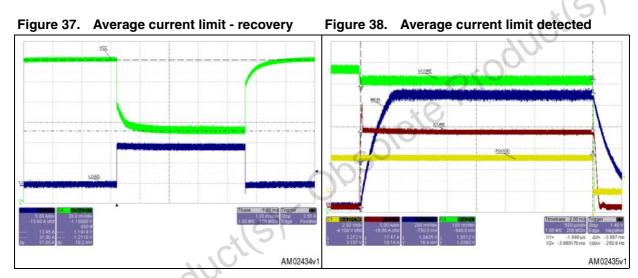

| Figure 37. | Average current limit - recovery                                 |      |

| Figure 38. | Average current limit detected                                   | . 35 |

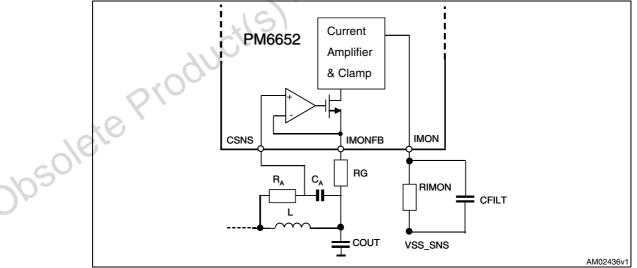

| Figure 39. | Current monitor with external components                         | . 36 |

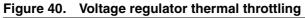

| Figure 40. | Voltage regulator thermal throttling.                            |      |

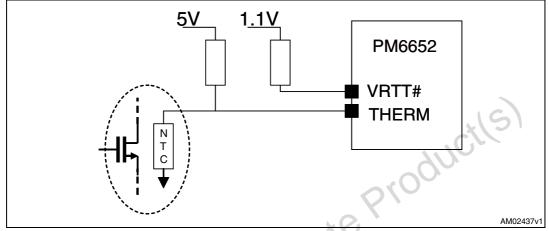

| Figure 41. | Valley current limit circuitry                                   |      |

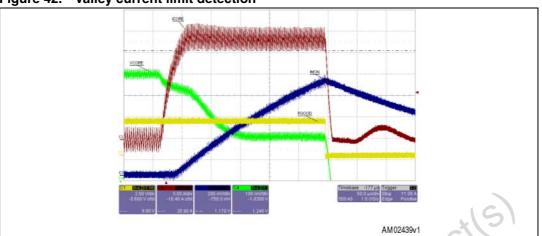

| Figure 42. | Valley current limit detection                                   |      |

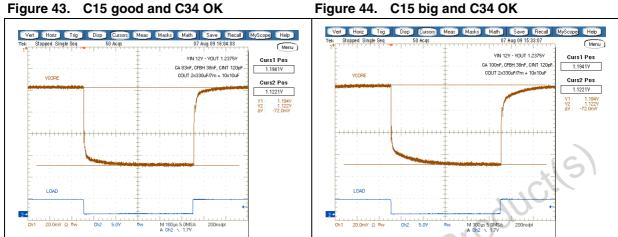

| Figure 43. | C15 good and C34 OK                                              | . 44 |

| Figure 44. | C15 big and C34 OK                                               |      |

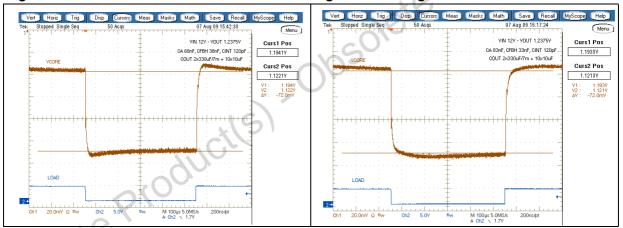

| Figure 45. | C15 small and C34 OK                                             |      |

| Figure 46. | C15 good and C34 small                                           |      |

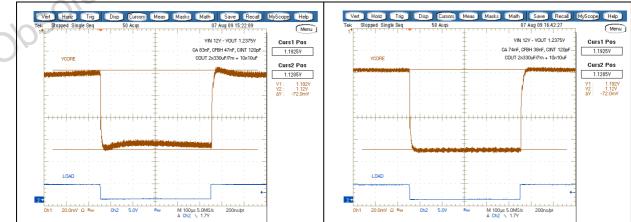

| Figure 47. | C15 good and C34 big                                             |      |

| Figure 48. | C15 OK and C34 OK                                                |      |

| Figure 49. | No load line output reference schematic             | 45 |

|------------|-----------------------------------------------------|----|

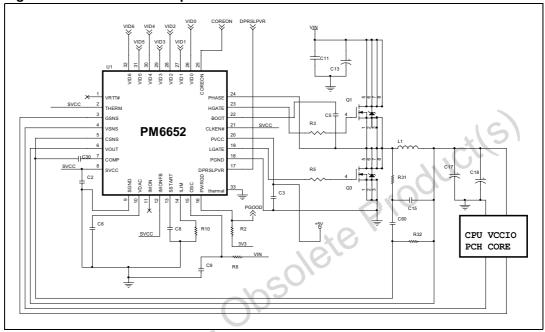

| Figure 50. | Load line disabled – VCCIO supply example           | 46 |

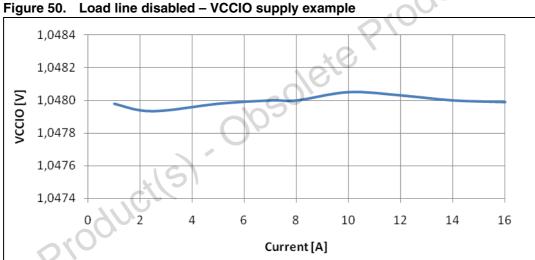

| Figure 51. | VCCIO output voltage ripple (1 A)                   | 47 |

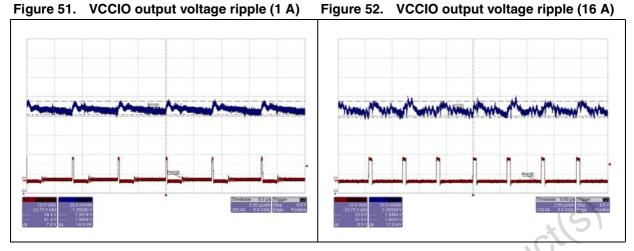

| Figure 52. | VCCIO output voltage ripple (16 A)                  | 47 |

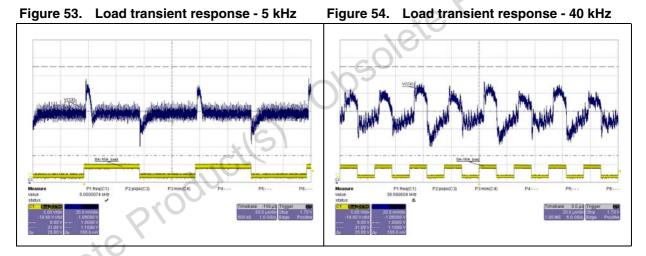

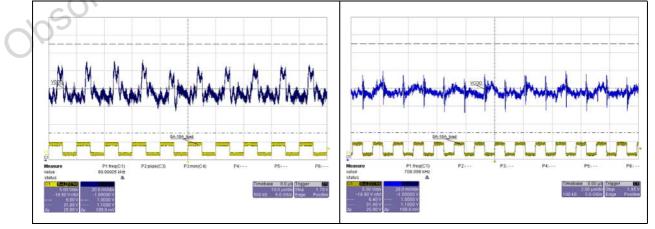

| Figure 53. | Load transient response - 5 kHz.                    | 47 |

| Figure 54. | Load transient response - 40 kHz.                   | 47 |

| Figure 55. | Load transient response - 100 kHz.                  | 47 |

| Figure 56. | Load transient response - 300 kHz.                  | 47 |

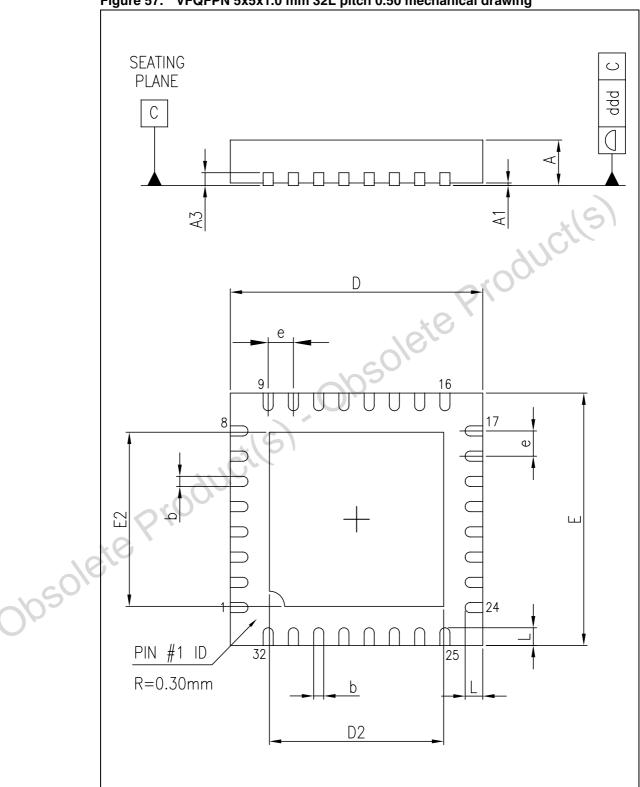

| Figure 57. | VFQFPN 5x5x1.0 mm 32L pitch 0.50 mechanical drawing | 50 |

obsolete Product(s) - Obsolete Product(s)

### List of tables

| ר<br>ר<br>ר | Table 1.<br>Table 2.<br>Table 3   | Device summary.                                                                     | 1<br>1<br>1 |

|-------------|-----------------------------------|-------------------------------------------------------------------------------------|-------------|

| ר<br>ר<br>ר | Table 4.<br>Table 5.              | Recommended operating conditions       1         Electrical characteristics       1 | 2<br>3      |

| ך<br>ך<br>ר | Table 6.<br>Table 7.              | VID for INTEL MVP 6.5 GFX core and CPU operation mode                               | 6<br>8      |

| י<br>ך<br>ר | Table 8.<br>Fable 9.<br>Fable 10. | VFQFPN 5x5x1.0 mm 32L pitch 0.50 mechanical data                                    | 0           |

|             |                                   |                                                                                     | -           |

|             |                                   | dul                                                                                 |             |

|             |                                   | Plo                                                                                 |             |

|             |                                   | dete                                                                                |             |

|             |                                   | Obsor                                                                               |             |

|             |                                   |                                                                                     |             |

|             |                                   | ct(S)                                                                               |             |

|             |                                   | due                                                                                 |             |

|             |                                   | PIO                                                                                 |             |

|             | 26                                | ste                                                                                 |             |

| 0           | 05 <sup>0</sup>                   |                                                                                     |             |

| U           | ~                                 |                                                                                     |             |

|             |                                   |                                                                                     |             |

|             |                                   |                                                                                     |             |

57

1

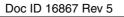

## Typical application circuit

Figure 1. Typical application circuit - IMVP6.5 render core supply

Figure 3. Typical application circuit – VR11 Atom CPU supply

### 2 Pin settings

### 2.1 Connections

## 2.2 Pin description

.(

|                                                                                        | Figure 5. Pin functions |                                                                                                        |                                                                                                                                                                                                                                           |  |  |

|----------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                        | Pin n°                  | Name                                                                                                   | Description                                                                                                                                                                                                                               |  |  |

| 20                                                                                     | 1                       | VRTT#                                                                                                  | Thermal throttling indicator, open drain output.                                                                                                                                                                                          |  |  |

| 0050°                                                                                  | 2                       | THERM                                                                                                  | Thermal throttling input. Connect to the central tap of NTC-based divider for MOS or inductor thermal monitoring.                                                                                                                         |  |  |

| 0.                                                                                     | 3                       | GSNS                                                                                                   | Output voltage ground remote sensing.                                                                                                                                                                                                     |  |  |

|                                                                                        | 4                       | VSNS                                                                                                   | Output voltage remote sensing.                                                                                                                                                                                                            |  |  |

|                                                                                        | 5                       | CSNS                                                                                                   | Current sensing input for droop function and IMON reporting. It represents the positive input of the differential current comparator. Connect to the inductor, for DCR sensing, or to a dedicated resistor for precision current sensing. |  |  |

| 6 VOUT Output voltage feedback. It also represents the negative in current comparator. |                         | Output voltage feedback. It also represents the negative input of the differential current comparator. |                                                                                                                                                                                                                                           |  |  |

|                                                                                        | 7                       | 7 COMP DC output voltage error compensation pin.                                                       |                                                                                                                                                                                                                                           |  |  |

|                                                                                        | 8                       | SVCC                                                                                                   | +5 V analog and digital supply.                                                                                                                                                                                                           |  |  |

|                                                                                        | 9                       | SGND                                                                                                   | Analog and digital ground.                                                                                                                                                                                                                |  |  |

| Pin n°                                                                            | Name     | Description                                                                                                                                                     |

|-----------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                                                                                | VDAC     | Internal DAC reference output. Bypass to GND with a 10 nF capacitor.                                                                                            |

| 11                                                                                | IMON     | Current monitor output. Bypass to remote ground through R-C network.                                                                                            |

| 12                                                                                | IMONFB   | Current monitor gain setting pin. Connect to $V_{OUT}$ through a resistor in the range 0.47 k $\Omega$ to 7 k $\Omega.$                                         |

| 13                                                                                | SSTART   | Soft-start programming pin and mode of operation selection input.                                                                                               |

| 14                                                                                | ILIM     | Current limit input. Connect ILIM to GND with a resistor to set the current limit threshold.                                                                    |

| 15                                                                                | OSC      | Frequency selection pin. Connect this pin to the input power supply rail through a resistor.                                                                    |

| 16                                                                                | PWRGD    | Power good signal (open drain output). High when VCC_GFX output voltage is within +200 mV/-300 mV of the programmed $V_{DAC}$ value.                            |

| 17                                                                                | DPRSLPVR | Render suspend state enter and render suspend exit mode control input.<br>Pulse-skipping or forced PWM working mode selection for IMVP6.5 CPU and<br>VR11 mode. |

| 18     PGND     Power ground.       19     LGATE     Low-side gate driver output. |          | Power ground.                                                                                                                                                   |

|                                                                                   |          | Low-side gate driver output.                                                                                                                                    |

| 20                                                                                | PVCC     | +5 V supply for internal driver supply.                                                                                                                         |

| 21                                                                                | CLKEN#   | CLOCK ENABLE open drain output (active low) and mode of operation selection pin.                                                                                |

| 22                                                                                | BOOT     | Bootstrap capacitor connection. Input for the supply voltage of the high-side gate driver.                                                                      |

| 23                                                                                | HGATE    | High-side gate driver output.                                                                                                                                   |

| 24                                                                                | PHASE    | Switch node connection and return path for the high-side gate driver.                                                                                           |

| 25                                                                                | COREON   | Switching regulator ON/OFF control input.                                                                                                                       |

| 26                                                                                | VID0     |                                                                                                                                                                 |

| 27                                                                                | VID1     |                                                                                                                                                                 |

| 28                                                                                | VID2     | VIDs bits of the controller voltage programming DAC input. They allow                                                                                           |

| 29                                                                                | VID3     | programming of the no load output voltage, depending on the selected mode<br>of operation. VID0 is the LSB and VID6 the MSB. Connect VIDx to a voltage          |

| 30                                                                                | VID4     | <0.33 V to program a '0'; connect VIDx to a voltage >0.77 V to program a '1'.                                                                                   |

| 31                                                                                | VID5     |                                                                                                                                                                 |

| 32                                                                                | VID6     |                                                                                                                                                                 |

| 33                                                                                | EP       | Exposed pad. Connect to SGND.                                                                                                                                   |

Figure 5. Pin functions (continued)

### 3 Electrical data

### 3.1 Maximum rating <sup>(a)</sup>

#### Table 2. Absolute maximum ratings

| Symbol             | Parameter                                                                                                                                             | Value                          | Unit        |   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|---|

| V <sub>PVCC</sub>  | PVCC to PGND                                                                                                                                          |                                | -0.3 to 6   | V |

| V <sub>SVCC</sub>  | SVCC to SGND                                                                                                                                          |                                | -0.3 to 6   | V |

|                    | SGND to PGND                                                                                                                                          |                                | -0.3 to 0.3 | V |

| V <sub>BOOT</sub>  | BOOT to PHASE                                                                                                                                         |                                | -0.3 to 6   | V |

| V <sub>HGATE</sub> | HGATE to PHASE                                                                                                                                        | -0.3 to V <sub>BOOT</sub> +0.3 | V           |   |

| $V_{PHASE}$        | PHASE to PGND                                                                                                                                         | -0.3 to 37                     | V           |   |

| V <sub>LGATE</sub> | LGATE to PGND                                                                                                                                         | -0.3 to V <sub>PVCC</sub> +0.3 | V           |   |

|                    | VRTT#, THERM, GSNS, VSNS, CSNS, VOUT, C<br>VDAC, IMON, IMONFB, ILIM, OSC, PWRGD,<br>DPRSLPVR, SSTART, CLKEN#, COREON, VID<br>SGND                     | -0.3 to V <sub>SVCC</sub> +0.3 | v           |   |

|                    | Maximum withstanding voltage range test<br>condition: CDF-AEC-Q100-002- "human body<br>model" acceptance criteria: "NormalAll the<br>pinsPerformance" |                                | ±1250       | v |

## 3.2 Thermal data

#### Table 3. Thermal data

|       | Symbol            | Parameter                                       | Value      | Unit |

|-------|-------------------|-------------------------------------------------|------------|------|

| 16    | R <sub>thJA</sub> | Thermal resistance between junction and ambient | 35         | °C/W |

| 06501 | TJ                | Junction operating temperature range            | -40 to 125 |      |

|       | T <sub>A</sub>    | Operating ambient temperature range             | -40 to 85  | °C   |

|       | T <sub>STG</sub>  | Storage temperature range                       | -50 to 150 |      |

a. Free air operating conditions unless otherwise specified. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

### **3.3** Recommended operating conditions

|        | Oramika I         | Demenden            | Value |      |      | 11   |

|--------|-------------------|---------------------|-------|------|------|------|

|        | Symbol            | Parameter           | Min.  | Тур. | Max. | Unit |

|        | V <sub>IN</sub>   | Input voltage range | 4.5   | -    | 36   | V    |

|        | V <sub>PVCC</sub> | PVCC voltage range  | 4.5   | -    | 5.5  | V    |

| obsole | tepre             | PVCC voltage range  | 3 Pr  | od1  |      |      |

#### Table 4. Recommended operating conditions

## 4 Electrical characteristics

$T_J$  = 25 °C,  $V_{IN}$  = +12 V, PVCC = +5 V if not otherwise specified.

| Table 5. | Electrical | characteristics |

|----------|------------|-----------------|

|----------|------------|-----------------|

| Symbol                                                  | Parameter                                          | Test cond                                                                   | ition            | Min.  | Тур.  | Max. | Unit  |

|---------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------|------------------|-------|-------|------|-------|

| Supply section                                          |                                                    |                                                                             |                  |       |       |      |       |

| ISVCC,QUIESCENT                                         | IC supply current                                  | COREON=5 V, DPRS forced above the regul                                     |                  |       |       | 850  | μA    |

| I <sub>SVCC,SHDN</sub>                                  | Operating current in<br>shutdown                   | COREON=SGND, T <sub>A</sub> =                                               | =25 °C           |       |       | 10   | μΑ    |

|                                                         | SVCC undervoltage lockout upper threshold          | Rising edge, controller<br>this level                                       | r disabled below |       | 4.3   | 4.5  | V     |

| V <sub>SVCC</sub> UVLO                                  | SVCC undervoltage<br>lockout lower threshold       | Falling edge, controller enabled above this level                           |                  |       | 3.9   |      | v     |

|                                                         | UVLO hysteresis                                    |                                                                             | ×C `             |       | 400   |      | mV    |

| On-time                                                 | ·                                                  |                                                                             | 161              |       |       |      |       |

|                                                         |                                                    | 5                                                                           | OSC=250 mV       | 820   | 920   | 1020 |       |

| T <sub>on</sub>                                         | On-time duration                                   | V <sub>CORE</sub> =1.5 V                                                    | OSC=500 mV       | 410   | 470   | 530  | ns    |

|                                                         |                                                    |                                                                             | OSC=1 V          | 210   | 248   | 280  |       |

| Off-time                                                |                                                    | 51                                                                          |                  |       |       |      |       |

| T <sub>OFFMIN</sub>                                     | Minimum off-time                                   |                                                                             |                  |       | 250   | 400  | ns    |

| Integrator                                              | du                                                 |                                                                             |                  |       |       |      |       |

| V <sub>COMP</sub>                                       | Overvoltage clamp                                  | V <sub>OVCLAMP</sub> =V <sub>COMP</sub> -V <sub>C</sub>                     | SNS              |       | 80    |      | mV    |

| .0                                                      | Undervoltage clamp                                 | V <sub>UVCLAMP</sub> =V <sub>COMP</sub> -V <sub>C</sub>                     | SNS              |       | -140  |      | mV    |

| 1010                                                    | Integrator offset                                  |                                                                             |                  | -2.5  |       | 2.5  | mV    |

| Voltages and DAC                                        |                                                    |                                                                             |                  |       |       |      |       |

| 0                                                       | Internal DAC reference                             | DAC codes from 0.812                                                        | 25 V to 1.5000 V | -0.7% |       | 0.7% |       |

| V <sub>DAC</sub>                                        | voltage accuracy                                   | DAC codes from 0.300                                                        | 00 V to 0.8000 V | -10   |       | 10   | mV    |

| V <sub>DAC</sub> output voltage<br>slew rate after VIDs |                                                    | GFX mode selected, a asserted, positive V <sub>DA</sub> VR11 mode selected. |                  | 10    | 12.5  |      | mV/µs |

| slew-rate                                               | variation.                                         | GFX mode selected, a de-assert, or CPU mo                                   |                  | 5     | 6.25  |      | mV/µs |

| I <sub>leak</sub> VCC_GFXC                              | V <sub>CORE</sub> voltage sense<br>leakage current |                                                                             |                  |       |       | 1    | μA    |

| VBOOT                                                   | Boot-up voltage                                    | CPU or VR11 mode se                                                         | elected          |       | 1.100 |      | V     |

|                                                         | •                                                  | •                                                                           |                  |       | •     |      |       |

| Symbol                 | Parameter                               | Test condition                                                                           | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| Current sensing        |                                         |                                                                                          |      |      |      |      |

| I <sub>CSNS</sub>      | Input leakage current                   |                                                                                          |      |      | 1    | μA   |

|                        | Current limit<br>comparator offset      | V <sub>OFFS</sub> =V <sub>PGND</sub> -V <sub>PHASE</sub>                                 | -4   |      | 4    | mV   |

| I <sub>LIM</sub>       | ILIM bias current                       |                                                                                          | 4.5  | 5    | 5.5  | μA   |

|                        | Zero-crossing<br>comparator offset      |                                                                                          | -3.5 |      | 3.5  | mV   |

| High-side and low      | v-side gate drivers                     |                                                                                          |      |      |      |      |

|                        | HGATE driver ON-                        | HGATE high state (pull-up)                                                               |      | 2.0  | 3    | Ω    |

|                        | resistance                              | HGATE low state (pull-down)                                                              | ,    | 1.6  | 2.7  | Ω    |

|                        | LGATE driver ON-                        | LGATE high state (pull-up)                                                               |      |      | 1.7  | Ω    |

|                        | resistance                              | LGATE low state (pull-down)                                                              | 2    | 0.6  | 1    | Ω    |

| UVP/OVP protecti       | ons, PWRGD and CLKE                     | N# signals                                                                               |      |      |      |      |

| OVP <sub>FIXED</sub>   | Fixed overvoltage threshold             | colet                                                                                    |      | 1.55 |      | V    |

| OVPLATCHED             | Overvoltage threshold                   | Referred to V <sub>DAC</sub> value                                                       |      | 200  |      | mV   |

| UVP <sub>LATCHED</sub> | Undervoltage threshold                  | Referred to V <sub>DAC</sub> value                                                       |      | -300 |      | mV   |

| PWRGD                  | Upper threshold                         | Referred to V <sub>DAC</sub> value                                                       |      | 200  |      | mV   |

| 1 WIIGD                | Lower threshold                         | Helened to VDAC value                                                                    |      | -300 |      | IIIV |

| I <sub>PWRGD</sub>     | PWRGD leakage current                   | PWRGD forced to 3.3 V                                                                    |      |      | 1    | μA   |

| V <sub>PWRGD</sub>     | Output low voltage                      | Isink=4 mA                                                                               |      | 250  | 350  | mV   |

| CLKEN#                 | Output low voltage                      | Isink=4 mA                                                                               |      | 250  | 350  | mV   |

| lete                   | CLKEN# leakage current                  | CLKEN# forced to 3.3 V; SSTART=5 V                                                       |      |      | 1    | μA   |

| Current monitor s      | section                                 |                                                                                          |      |      |      |      |

| Q                      |                                         | $V_{CSNS} - V_{OUT} = 60 mV;$<br>RIMONFB=1.8 kΩ R <sub>IMON</sub> =10 kΩ                 | 970  | 1000 | 1030 |      |

|                        | Current monitor output                  | V <sub>CSNS</sub> – V <sub>OUT</sub> = 30 mV;<br>RIMONFB=1.8 kΩ R <sub>IMON</sub> =10 kΩ | 474  | 500  | 526  | mV   |

| IMON                   |                                         | V <sub>CSNS</sub> – V <sub>OUT</sub> = 15 mV;<br>RIMONFB=1.8 kΩ R <sub>IMON</sub> =10 kΩ | 226  | 250  | 274  |      |

|                        | Current monitor clamp, referred to GSNS | 8 kΩ <r<sub>IMON&lt;16 kΩ<br/>GSNS-AGND&lt;20 mV</r<sub>                                 |      |      | 1.15 | v    |

|                        | Current monitor input offset            | I <sub>IMON</sub> = 0 μA                                                                 | 0    |      | 1.0  | mV   |

Table 5. Electrical characteristics (continued)

| Symbol                | Parameter                          | Test condition                   | Min.  | Тур. | Max.  | Unit  |

|-----------------------|------------------------------------|----------------------------------|-------|------|-------|-------|

| Soft-start section    |                                    |                                  |       |      |       |       |

|                       | Default soft-start slew rate       | SSTART pin connected to AVCC     | 5     | 6.25 |       | mV/µs |

| Soft-end section      |                                    |                                  |       |      |       |       |

|                       | VCC_GFX discharge resistance       |                                  |       | 7    |       | Ω     |

| Thermal throttling    | management                         |                                  |       |      |       |       |

| THERM                 | Thermal detection trip threshold   | Measured with respect to SGND    |       | 1.0  | * 6   | v     |

|                       | Threshold hysteresis               |                                  |       | 200  |       | mV    |

| VRTT#                 | Output ON-resistance               | THERM tied to SGND               |       | 7    |       | Ω     |

| I <sub>VRTT#</sub>    | VRTT# leakage current              | VRTT# forced to 3.3 V; THERM=5 V | 0     |      | 1     | μA    |

| Power manageme        | ent                                | * 21                             |       |      |       |       |

| COREON                | SW regulator enable turn-on level  | colett                           | 0.800 |      |       | v     |

| COREON                | SW regulator enable turn-off level | 0,02                             |       |      | 0.346 | V     |

| V                     | Render suspend pin                 | Render suspend (low)             |       |      | 0.346 | v     |

| V <sub>DPRSLPVR</sub> | thresholds                         | Render performance (high)        | 0.731 |      |       | v     |

| VID <sub>IH</sub>     | VID high threshold                 |                                  | 0.731 |      |       | V     |

| VID <sub>IL</sub>     | VID low threshold                  |                                  |       |      | 0.346 | V     |

| I <sub>VID</sub>      | VID pull-up current                |                                  |       |      | 1     | μA    |

| Thermal shutdow       | n                                  |                                  |       |      |       |       |

| T <sub>SHDN</sub>     | Shutdown temperature               |                                  |       | 150  |       | °C    |

### Table 5. Electrical characteristics (continued)

1. Guaranteed by design. Not production tested.

# 5 Voltage identification (VID)

| Table | 0.   |      |      |      |      | <u> </u> | core and |      | opera |      | nouc |      |      |      |        |

|-------|------|------|------|------|------|----------|----------|------|-------|------|------|------|------|------|--------|

| VID6  | VID5 | VID4 | VID3 | VID2 | VID1 | VID0     | VCORE    | VID6 | VID5  | VID4 | VID3 | VID2 | VID1 | VID0 | VCORE  |

| 0     | 0    | 0    | 0    | 0    | 0    | 0        | 1.5000   | 1    | 0     | 0    | 0    | 0    | 0    | 0    | 0.7000 |

| 0     | 0    | 0    | 0    | 0    | 0    | 1        | 1.4875   | 1    | 0     | 0    | 0    | 0    | 0    | 1    | 0.6875 |

| 0     | 0    | 0    | 0    | 0    | 1    | 0        | 1.4750   | 1    | 0     | 0    | 0    | 0    | 1    | 0    | 0.6750 |

| 0     | 0    | 0    | 0    | 0    | 1    | 1        | 1.4625   | 1    | 0     | 0    | 0    | 0    | 1    | 1    | 0.6625 |

| 0     | 0    | 0    | 0    | 1    | 0    | 0        | 1.4500   | 1    | 0     | 0    | 0    | 1    | 0    | 0    | 0.6500 |

| 0     | 0    | 0    | 0    | 1    | 0    | 1        | 1.4375   | 1    | 0     | 0    | 0    | 1    | 0    | 1    | 0.6375 |

| 0     | 0    | 0    | 0    | 1    | 1    | 0        | 1.4250   | 1    | 0     | 0    | 0    | 1    | J    | 0    | 0.6250 |

| 0     | 0    | 0    | 0    | 1    | 1    | 1        | 1.4125   | 1    | 0     | 0    | 0    | 10   | Y    | 1    | 0.6125 |

| 0     | 0    | 0    | 1    | 0    | 0    | 0        | 1.4000   | 1    | 0     | 0    | 1    | 0    | 0    | 0    | 0.6000 |

| 0     | 0    | 0    | 1    | 0    | 0    | 1        | 1.3875   | 1    | 0     | 0    | 2    | 0    | 0    | 1    | 0.5875 |

| 0     | 0    | 0    | 1    | 0    | 1    | 0        | 1.3750   | 1    | 0     | 0    | 1    | 0    | 1    | 0    | 0.5750 |

| 0     | 0    | 0    | 1    | 0    | 1    | 1        | 1.3625   | -    | 0     | 0    | 1    | 0    | 1    | 1    | 0.5625 |

| 0     | 0    | 0    | 1    | 1    | 0    | 0        | 1.3500   |      | 0     | 0    | 1    | 1    | 0    | 0    | 0.5500 |

| 0     | 0    | 0    | 1    | 1    | 0    | 1        | 1.3375   | 1    | 0     | 0    | 1    | 1    | 0    | 1    | 0.5375 |

| 0     | 0    | 0    | 1    | 1    | 1    | 0        | 1.3250   | 1    | 0     | 0    | 1    | 1    | 1    | 0    | 0.5250 |

| 0     | 0    | 0    | 1    | 1    | 1    |          | 1.3125   | 1    | 0     | 0    | 1    | 1    | 1    | 1    | 0.5125 |

| 0     | 0    | 1    | 0    | 0    | 0    | 0        | 1.3000   | 1    | 0     | 1    | 0    | 0    | 0    | 0    | 0.5000 |

| 0     | 0    | 1    | 0    | 0    | 0    | 1        | 1.2875   | 1    | 0     | 1    | 0    | 0    | 0    | 1    | 0.4875 |

| 0     | 0    | -    | 0    | 0    | 1    | 0        | 1.2750   | 1    | 0     | 1    | 0    | 0    | 1    | 0    | 0.4750 |

| 0     | 0    | Y    | 0    | 0    | 1    | 1        | 1.2625   | 1    | 0     | 1    | 0    | 0    | 1    | 1    | 0.4625 |

| 0     | 0    |      | 0    | 1    | 0    | 0        | 1.2500   | 1    | 0     | 1    | 0    | 1    | 0    | 0    | 0.4500 |

| 0     | 0    | 1    | 0    | 1    | 0    | 1        | 1.2375   | 1    | 0     | 1    | 0    | 1    | 0    | 1    | 0.4375 |

| 0     | 0    | 1    | 0    | 1    | 1    | 0        | 1.2250   | 1    | 0     | 1    | 0    | 1    | 1    | 0    | 0.4250 |

| 0     | 0    | 1    | 0    | 1    | 1    | 1        | 1.2125   | 1    | 0     | 1    | 0    | 1    | 1    | 1    | 0.4125 |

| 0     | 0    | 1    | 1    | 0    | 0    | 0        | 1.2000   | 1    | 0     | 1    | 1    | 0    | 0    | 0    | 0.4000 |

| 0     | 0    | 1    | 1    | 0    | 0    | 1        | 1.1875   | 1    | 0     | 1    | 1    | 0    | 0    | 1    | 0.3875 |

| 0     | 0    | 1    | 1    | 0    | 1    | 0        | 1.1750   | 1    | 0     | 1    | 1    | 0    | 1    | 0    | 0.3750 |

| 0     | 0    | 1    | 1    | 0    | 1    | 1        | 1.1625   | 1    | 0     | 1    | 1    | 0    | 1    | 1    | 0.3625 |

| 0     | 0    | 1    | 1    | 1    | 0    | 0        | 1.1500   | 1    | 0     | 1    | 1    | 1    | 0    | 0    | 0.3500 |

| 0     | 0    | 1    | 1    | 1    | 0    | 1        | 1.1375   | 1    | 0     | 1    | 1    | 1    | 0    | 1    | 0.3375 |

| 0     | 0    | 1    | 1    | 1    | 1    | 0        | 1.1250   | 1    | 0     | 1    | 1    | 1    | 1    | 0    | 0.3250 |

| 0     | 0    | 1    | 1    | 1    | 1    | 1        | 1.1125   | 1    | 0     | 1    | 1    | 1    | 1    | 1    | 0.3125 |

#### Table 6. VID for INTEL MVP 6.5 GFX core and CPU operation mode

| Table | 6.   | VID 1 | for IN | TEL N | IVP 6. | 5 GF) | Core and | CPU  | opera | tion n | node | (cont | inued | l)   |        |

|-------|------|-------|--------|-------|--------|-------|----------|------|-------|--------|------|-------|-------|------|--------|

| VID6  | VID5 | VID4  | VID3   | VID2  | VID1   | VID0  | VCORE    | VID6 | VID5  | VID4   | VID3 | VID2  | VID1  | VID0 | VCORE  |

| 0     | 1    | 0     | 0      | 0     | 0      | 0     | 1.1000   | 1    | 1     | 0      | 0    | 0     | 0     | 0    | 0.3000 |

| 0     | 1    | 0     | 0      | 0     | 0      | 1     | 1.0875   | 1    | 1     | 0      | 0    | 0     | 0     | 1    | 0.2875 |

| 0     | 1    | 0     | 0      | 0     | 1      | 0     | 1.0750   | 1    | 1     | 0      | 0    | 0     | 1     | 0    | 0.2750 |

| 0     | 1    | 0     | 0      | 0     | 1      | 1     | 1.0625   | 1    | 1     | 0      | 0    | 0     | 1     | 1    | 0.2625 |

| 0     | 1    | 0     | 0      | 1     | 0      | 0     | 1.0500   | 1    | 1     | 0      | 0    | 1     | 0     | 0    | 0.2500 |

| 0     | 1    | 0     | 0      | 1     | 0      | 1     | 1.0375   | 1    | 1     | 0      | 0    | 1     | 0     | 1    | 0.2375 |

| 0     | 1    | 0     | 0      | 1     | 1      | 0     | 1.0250   | 1    | 1     | 0      | 0    | 1     | 1     | 0    | 0.2250 |

| 0     | 1    | 0     | 0      | 1     | 1      | 1     | 1.0125   | 1    | 1     | 0      | 0    | 1     | 1     | 1    | 0.2125 |

| 0     | 1    | 0     | 1      | 0     | 0      | 0     | 1.0000   | 1    | 1     | 0      | 1    | 0     | 0     | 0    | 0.2000 |

| 0     | 1    | 0     | 1      | 0     | 0      | 1     | 0.9875   | 1    | 1     | 0      | 1    | 0     | 0     | Y    | 0.1875 |

| 0     | 1    | 0     | 1      | 0     | 1      | 0     | 0.9750   | 1    | 1     | 0      | 1    | 0     | Ţ     | 0    | 0.1750 |

| 0     | 1    | 0     | 1      | 0     | 1      | 1     | 0.9625   | 1    | 1     | 0      | 1    | 0     | 1     | 1    | 0.1625 |

| 0     | 1    | 0     | 1      | 1     | 0      | 0     | 0.9500   | 1    | 1     | 0      | S'   | 1     | 0     | 0    | 0.1500 |

| 0     | 1    | 0     | 1      | 1     | 0      | 1     | 0.9375   | 1    | 1     | 0      | 1    | 1     | 0     | 1    | 0.1375 |

| 0     | 1    | 0     | 1      | 1     | 1      | 0     | 0.9250   | 1    | 2     | 0      | 1    | 1     | 1     | 0    | 0.1250 |

| 0     | 1    | 0     | 1      | 1     | 1      | 1     | 0.9125   | 2    | 1     | 0      | 1    | 1     | 1     | 1    | 0.1125 |

| 0     | 1    | 1     | 0      | 0     | 0      | 0     | 0.9000   | 1    | 1     | 1      | 0    | 0     | 0     | 0    | 0.1000 |

| 0     | 1    | 1     | 0      | 0     | 0      | 1     | 0.8875   | 1    | 1     | 1      | 0    | 0     | 0     | 1    | 0.0875 |

| 0     | 1    | 1     | 0      | 0     | 1      | 0     | 0.8750   | 1    | 1     | 1      | 0    | 0     | 1     | 0    | 0.0750 |

| 0     | 1    | 1     | 0      | 0     | 1      | 1     | 0.8625   | 1    | 1     | 1      | 0    | 0     | 1     | 1    | 0.0625 |

| 0     | 1    | 1     | 0      | 1     | 0      | 0     | 0.8500   | 1    | 1     | 1      | 0    | 1     | 0     | 0    | 0.0500 |

| 0     | 1    | 1     | 0      | 1     | 0      | 1     | 0.8375   | 1    | 1     | 1      | 0    | 1     | 0     | 1    | 0.0375 |

| 0     | 1    | x1C   | 0      | 1     | 1      | 0     | 0.8250   | 1    | 1     | 1      | 0    | 1     | 1     | 0    | 0.0250 |

| 0     | 1    | 01    | 0      | 1     | 1      | 1     | 0.8125   | 1    | 1     | 1      | 0    | 1     | 1     | 1    | 0.0125 |

| 0     | Ч    | 1     | 1      | 0     | 0      | 0     | 0.8000   | 1    | 1     | 1      | 1    | 0     | 0     | 0    | 0.0000 |

| 0     | 1    | 1     | 1      | 0     | 0      | 1     | 0.7875   | 1    | 1     | 1      | 1    | 0     | 0     | 1    | 0.0000 |

| 0     | 1    | 1     | 1      | 0     | 1      | 0     | 0.7750   | 1    | 1     | 1      | 1    | 0     | 1     | 0    | 0.0000 |

| 0     | 1    | 1     | 1      | 0     | 1      | 1     | 0.7625   | 1    | 1     | 1      | 1    | 0     | 1     | 1    | 0.0000 |

| 0     | 1    | 1     | 1      | 1     | 0      | 0     | 0.7500   | 1    | 1     | 1      | 1    | 1     | 0     | 0    | 0.0000 |

| 0     | 1    | 1     | 1      | 1     | 0      | 1     | 0.7375   | 1    | 1     | 1      | 1    | 1     | 0     | 1    | 0.0000 |

| 0     | 1    | 1     | 1      | 1     | 1      | 0     | 0.7250   | 1    | 1     | 1      | 1    | 1     | 1     | 0    | 0.0000 |

| 0     | 1    | 1     | 1      | 1     | 1      | 1     | 0.7125   | 1    | 1     | 1      | 1    | 1     | 1     | 1    | OFF    |

Table 6.

VID for INTEL MVP 6.5 GFX core and CPU operation mode (continued)

| Table | ••   |            | -90 .a | •    | Jano | ,    |        |      | 6961 | allen |        |      |      |      |        |

|-------|------|------------|--------|------|------|------|--------|------|------|-------|--------|------|------|------|--------|

| VID6  | VID5 | VID4       | VID3   | VID2 | VID1 | VID0 | VCORE  | VID6 | VID5 | VID4  | VID3   | VID2 | VID1 | VID0 | VCORE  |

| 0     | 0    | 0          | 0      | 0    | 0    | 0    | 1.5000 | 1    | 0    | 0     | 0      | 0    | 0    | 0    | 0.8125 |

| 0     | 0    | 0          | 0      | 0    | 0    | 1    | 1.5000 | 1    | 0    | 0     | 0      | 0    | 0    | 1    | 0.8000 |

| 0     | 0    | 0          | 0      | 0    | 1    | 0    | 1.5000 | 1    | 0    | 0     | 0      | 0    | 1    | 0    | 0.7875 |

| 0     | 0    | 0          | 0      | 0    | 1    | 1    | 1.5000 | 1    | 0    | 0     | 0      | 0    | 1    | 1    | 0.7750 |

| 0     | 0    | 0          | 0      | 1    | 0    | 0    | 1.5000 | 1    | 0    | 0     | 0      | 1    | 0    | 0    | 0.7625 |

| 0     | 0    | 0          | 0      | 1    | 0    | 1    | 1.5000 | 1    | 0    | 0     | 0      | 1    | 0    | 1    | 0.7500 |

| 0     | 0    | 0          | 0      | 1    | 1    | 0    | 1.5000 | 1    | 0    | 0     | 0      | 1    | 1    | 0    | 0.7375 |

| 0     | 0    | 0          | 0      | 1    | 1    | 1    | 1.5000 | 1    | 0    | 0     | 0      | 1    | 1    | 1    | 0.7250 |

| 0     | 0    | 0          | 1      | 0    | 0    | 0    | 1.5000 | 1    | 0    | 0     | 1      | 0    | 0    | 0    | 0.7125 |

| 0     | 0    | 0          | 1      | 0    | 0    | 1    | 1.5000 | 1    | 0    | 0     | 1      | 0    | 0    | 1    | 0.7000 |

| 0     | 0    | 0          | 1      | 0    | 1    | 0    | 1.4875 | 1    | 0    | 0     | 1      | 0    | 1    | 0    | 0.6875 |

| 0     | 0    | 0          | 1      | 0    | 1    | 1    | 1.4750 | 1    | 0    | 0     | $\sim$ | 0    | 1    | 1    | 0.6750 |

| 0     | 0    | 0          | 1      | 1    | 0    | 0    | 1.4625 | 1    | 0    | 0     |        | 1    | 0    | 0    | 0.6625 |

| 0     | 0    | 0          | 1      | 1    | 0    | 1    | 1.4500 | 1    | 0    | 0     | 1      | 1    | 0    | 1    | 0.6500 |

| 0     | 0    | 0          | 1      | 1    | 1    | 0    | 1.4375 | 1    | 0    | 0     | 1      | 1    | 1    | 0    | 0.6375 |

| 0     | 0    | 0          | 1      | 1    | 1    | 1    | 1.4250 | 1    | 0    | 0     | 1      | 1    | 1    | 1    | 0.6250 |

| 0     | 0    | 1          | 0      | 0    | 0    | 0    | 1.4125 | 1    | 0    | 1     | 0      | 0    | 0    | 0    | 0.6125 |

| 0     | 0    | 1          | 0      | 0    | 0    | 1    | 1.4000 | 1    | 0    | 1     | 0      | 0    | 0    | 1    | 0.6000 |

| 0     | 0    | 1          | 0      | 0    | 1    | 0    | 1.3875 | 1    | 0    | 1     | 0      | 0    | 1    | 0    | 0.5875 |

| 0     | 0    | 1          | 0      | 0    |      | 1    | 1.3750 | 1    | 0    | 1     | 0      | 0    | 1    | 1    | 0.5750 |

| 0     | 0    | 1          | 0      | T    | 0    | 0    | 1.3625 | 1    | 0    | 1     | 0      | 1    | 0    | 0    | 0.5625 |

| 0     | 0    | <b>1</b> 0 | 0      | 1    | 0    | 1    | 1.3500 | 1    | 0    | 1     | 0      | 1    | 0    | 1    | 0.5500 |

| 0     | 0    | 1          | 0      | 1    | 1    | 0    | 1.3375 | 1    | 0    | 1     | 0      | 1    | 1    | 0    | 0.5375 |

| 0     | 0    | 1          | 0      | 1    | 1    | 1    | 1.3250 | 1    | 0    | 1     | 0      | 1    | 1    | 1    | 0.5250 |

| 0     | 0    | 1          | 1      | 0    | 0    | 0    | 1.3125 | 1    | 0    | 1     | 1      | 0    | 0    | 0    | 0.5125 |

| 0     | 0    | 1          | 1      | 0    | 0    | 1    | 1.3000 | 1    | 0    | 1     | 1      | 0    | 0    | 1    | 0.5000 |

| 0     | 0    | 1          | 1      | 0    | 1    | 0    | 1.2875 | 1    | 0    | 1     | 1      | 0    | 1    | 0    | 0.4875 |

| 0     | 0    | 1          | 1      | 0    | 1    | 1    | 1.2750 | 1    | 0    | 1     | 1      | 0    | 1    | 1    | 0.4750 |

| 0     | 0    | 1          | 1      | 1    | 0    | 0    | 1.2625 | 1    | 0    | 1     | 1      | 1    | 0    | 0    | 0.4625 |

| 0     | 0    | 1          | 1      | 1    | 0    | 1    | 1.2500 | 1    | 0    | 1     | 1      | 1    | 0    | 1    | 0.4500 |

| 0     | 0    | 1          | 1      | 1    | 1    | 0    | 1.2375 | 1    | 0    | 1     | 1      | 1    | 1    | 0    | 0.4375 |

| 0     | 0    | 1          | 1      | 1    | 1    | 1    | 1.2250 | 1    | 0    | 1     | 1      | 1    | 1    | 1    | 0.4250 |

| 0     | 1    | 0          | 0      | 0    | 0    | 0    | 1.2125 | 1    | 1    | 0     | 0      | 0    | 0    | 0    | 0.4125 |

| 0     | 1    | 0          | 0      | 0    | 0    | 1    | 1.2000 | 1    | 1    | 0     | 0      | 0    | 0    | 1    | 0.4000 |

Table 7.

Voltage identification (VID) for INTEL VR11 operation mode

| Table | 7.   | Volta | ige id | entifie | cation     | ı (VID) | for INTEL | VR11 | oper   | ation | mode | e (cor | ntinue | d)   |        |

|-------|------|-------|--------|---------|------------|---------|-----------|------|--------|-------|------|--------|--------|------|--------|

| VID6  | VID5 | VID4  | VID3   | VID2    | VID1       | VID0    | VCORE     | VID6 | VID5   | VID4  | VID3 | VID2   | VID1   | VID0 | VCORE  |

| 0     | 1    | 0     | 0      | 0       | 1          | 0       | 1.1875    | 1    | 1      | 0     | 0    | 0      | 1      | 0    | 0.3875 |

| 0     | 1    | 0     | 0      | 0       | 1          | 1       | 1.1750    | 1    | 1      | 0     | 0    | 0      | 1      | 1    | 0.3750 |

| 0     | 1    | 0     | 0      | 1       | 0          | 0       | 1.1625    | 1    | 1      | 0     | 0    | 1      | 0      | 0    | 0.3625 |

| 0     | 1    | 0     | 0      | 1       | 0          | 1       | 1.1500    | 1    | 1      | 0     | 0    | 1      | 0      | 1    | 0.3500 |

| 0     | 1    | 0     | 0      | 1       | 1          | 0       | 1.1375    | 1    | 1      | 0     | 0    | 1      | 1      | 0    | 0.3375 |

| 0     | 1    | 0     | 0      | 1       | 1          | 1       | 1.1250    | 1    | 1      | 0     | 0    | 1      | 1      | 1    | 0.3250 |

| 0     | 1    | 0     | 1      | 0       | 0          | 0       | 1.1125    | 1    | 1      | 0     | 1    | 0      | 0      | 0    | 0.3125 |

| 0     | 1    | 0     | 1      | 0       | 0          | 1       | 1.1000    | 1    | 1      | 0     | 1    | 0      | 0      | 1    | 0.3000 |

| 0     | 1    | 0     | 1      | 0       | 1          | 0       | 1.0875    | 1    | 1      | 0     | 1    | 0      | 1      | 0    | 0.2875 |

| 0     | 1    | 0     | 1      | 0       | 1          | 1       | 1.0750    | 1    | 1      | 0     | 1    | 0      | Ţ      | Y    | 0.2750 |

| 0     | 1    | 0     | 1      | 1       | 0          | 0       | 1.0625    | 1    | 1      | 0     | 1    | 10     | 0      | 0    | 0.2625 |

| 0     | 1    | 0     | 1      | 1       | 0          | 1       | 1.0500    | 1    | 1      | 0     | 1    |        | 0      | 1    | 0.2500 |

| 0     | 1    | 0     | 1      | 1       | 1          | 0       | 1.0375    | 1    | 1      | 0     | 2    | 1      | 1      | 0    | 0.2375 |

| 0     | 1    | 0     | 1      | 1       | 1          | 1       | 1.0250    | 1    | 1      | 0     | 1    | 1      | 1      | 1    | 0.2250 |

| 0     | 1    | 1     | 0      | 0       | 0          | 0       | 1.0125    | 1    | P<br>P | 1     | 0    | 0      | 0      | 0    | 0.2125 |

| 0     | 1    | 1     | 0      | 0       | 0          | 1       | 1.0000    | P    | 1      | 1     | 0    | 0      | 0      | 1    | 0.2000 |

| 0     | 1    | 1     | 0      | 0       | 1          | 0       | 0.9875    | 1    | 1      | 1     | 0    | 0      | 1      | 0    | 0.1875 |

| 0     | 1    | 1     | 0      | 0       | 1          | 1       | 0.9750    | 1    | 1      | 1     | 0    | 0      | 1      | 1    | 0.1750 |

| 0     | 1    | 1     | 0      | 1       | 0          | 0       | 0.9625    | 1    | 1      | 1     | 0    | 1      | 0      | 0    | 0.1625 |

| 0     | 1    | 1     | 0      | 1       | 0          | 1       | 0.9500    | 1    | 1      | 1     | 0    | 1      | 0      | 1    | 0.1500 |

| 0     | 1    | 1     | 0      |         | <b>J</b> 1 | 0       | 0.9375    | 1    | 1      | 1     | 0    | 1      | 1      | 0    | 0.1375 |

| 0     | 1    | 1     | 0      | 1       | 1          | 1       | 0.9250    | 1    | 1      | 1     | 0    | 1      | 1      | 1    | 0.1250 |

| 0     | 1    | ×10   | 1      | 0       | 0          | 0       | 0.9125    | 1    | 1      | 1     | 1    | 0      | 0      | 0    | 0.1125 |

| 0     |      | 01    | 1      | 0       | 0          | 1       | 0.9000    | 1    | 1      | 1     | 1    | 0      | 0      | 1    | 0.1000 |

| 0     | H.   | 1     | 1      | 0       | 1          | 0       | 0.8875    | 1    | 1      | 1     | 1    | 0      | 1      | 0    | 0.0875 |

| 0     | 1    | 1     | 1      | 0       | 1          | 1       | 0.8750    | 1    | 1      | 1     | 1    | 0      | 1      | 1    | 0.0750 |

| 0     | 1    | 1     | 1      | 1       | 0          | 0       | 0.8625    | 1    | 1      | 1     | 1    | 1      | 0      | 0    | 0.0625 |

| 0     | 1    | 1     | 1      | 1       | 0          | 1       | 0.8500    | 1    | 1      | 1     | 1    | 1      | 0      | 1    | 0.0500 |

| 0     | 1    | 1     | 1      | 1       | 1          | 0       | 0.8375    | 1    | 1      | 1     | 1    | 1      | 1      | 0    | 0.0375 |

| 0     | 1    | 1     | 1      | 1       | 1          | 1       | 0.8250    | 1    | 1      | 1     | 1    | 1      | 1      | 1    | OFF    |

Table 7.

Voltage identification (VID) for INTEL VR11 operation mode (continued)

### **6** Typical operating characteristics

Measurement setup:  $V_{IN}$  = 10 V,  $F_{SW}$  = 320 kHz,  $V_{CORE}$  = 1.2375 V, DPRSLPVR = 0 V if not otherwise specified.

Figure 6. V<sub>CORE</sub> turn-on and PGOOD rising - Figure 7. V<sub>CORE</sub> turn-on - CPU IMVP6.5 mode no load

Figure 12. V<sub>CORE</sub> working mode - DPRSLPVR Figure 13. V<sub>CORE</sub> working mode (0.9 V) -not asserted, 10 A load DPRSLPVR not asserted, no load

Figure 14. V<sub>CORE</sub> working mode (0.4 V) -DPRSLPVR not asserted, no load

Figure 15. VID5 transition - entering and exiting suspend state (fast exit)

Figure 16. VID5 transition - entering and exiting suspend state (slow exit)

22/53

Figure 19. V<sub>CORE</sub> soft-end - COREON pin deassertion and PGOOD transition

Figure 17. Droop function - 5 A to 15 A

Doc ID 16867 Rev 5

# Figure 22. V<sub>CORE</sub> efficiency (DPRSLPVR high Figure 23. and low)

# re 23. V<sub>CORE</sub> load regulation - droop function

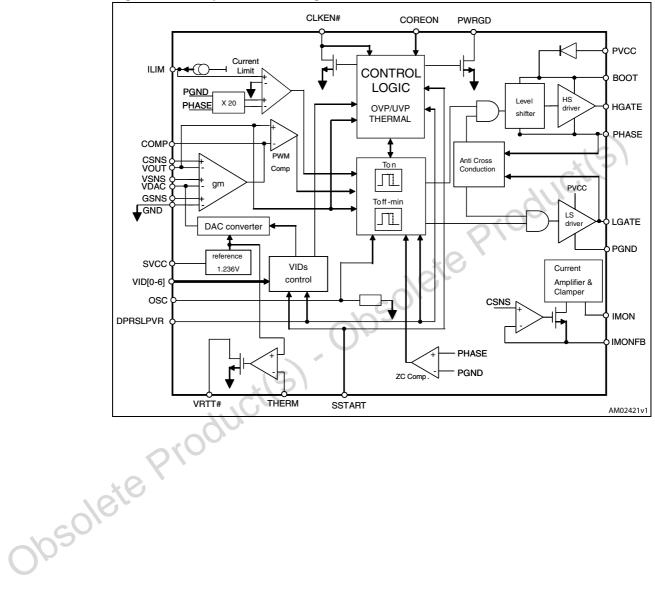

## 7 Block diagram

#### Figure 24. Simplified block diagram

### 8 Device description

The PM6652 is a single-phase, step-down controller which can be easily configured to regulate power to IMPV6.5 and VR11 devices, as listed below:

- The graphics (Render) core of the Intel<sup>®</sup> mobile Arrandale processor used on the Calpella platform

- The low voltage and ultra low voltage mobile CPU, used on the Calpella platform

- The VR11 compliant CPU, like Intel<sup>®</sup> ATOM 200/300 and Pineview-D CPU.

The supply mode and platform compliance are selected by acting on two multi-function pins (refer to *Section 8.2: Mode selection* for details), before the device turn-on.

The PM6652 is based on constant on-time control architecture. This type of control offers a very fast load transient response with a minimum external component count. A typical application circuit is shown in *Figure 1*. The controller includes a 7-bit digital-to-analog converter (DAC) that provides a reference voltage according to the VID pin settings (see *Table 6* and *Table 7*). The PM6652 also allows the adjusting of an active load line (or droop) control, proportional to the inductor DCR or dedicated precision resistor, according to IMVP6.5 specifications.

The switching frequency can be programmed in the range 200 kHz up to 600 kHz with an external resistor connected to the input voltage (see *Section 8.1: Constant on-time PWM control* for details).

In order to maximize the efficiency at very light load, a pulse-skipping control algorithm is performed. The PM6652 is also fully compliant with the fast and slow render suspend state exit mode, as required by IMVP 6.5 spec. for render core supply (see *Section 8.6: Voltage dynamic (VID) transitions* for details).

The device provides protection for overvoltage, undervoltage, overcurrent and overtemperature as well as power good (PWRGD), current monitor (IMON) and thermal throttling (VRTT#) signals for monitoring purposes. The clock enable output signal (CLKEN#), for appropriate platform power-up, is available in CPU supply mode only.

### 3.1 Constant on-time PWM control

The PM6652 controller uses a pseudo-fixed frequency, constant on-time (COT) controller as the core of the switching section. The COT controller uses a relatively simple algorithm, exploiting the ripple voltage due to inductor resistance DCR (or due to a sense resistor  $R_{SNS}$ ) to trigger the fixed on-time one-shot generator.

Nearly constant switching frequency is achieved by the system loop in steady-state operating conditions, therefore avoiding the need for a clock generator. A slight switching frequency variation towards the load is the consequence of the switching regulator power losses, which implies the off-time duration decrease.

The on-time one-shot duration is directly proportional to the output voltage, sensed at the VOUT pin, and inversely proportional to the input voltage, sensed at the VOSC pin, as follows:

$$T_{ON} = K_{OSC} \frac{V_{OUT}}{V_{OSC}} + \tau$$

where  $K_{OSC}$  is a constant value (140 ns typ.) and  $\tau$  is the internal propagation delay (40 ns typ.).

This leads to a nearly constant switching frequency, regardless of input and output voltages.

When the output voltage goes lower than the internal programmed voltage (see Section 8.5: *Droop function* for details), the on-time one-shot generator directly drives the high-side MOSFET for a fixed on-time, allowing the inductor current to increase; after the on-time, an off-time phase, in which the low-side MOSFET is turned on, follows.

If the DPRSLPVR control pin is set low, the low-side MOSFET is turned off only when the output voltage becomes lower than the programmed value again, and a new cycle begins. In this working mode the switching frequency is almost load independent, as shown below. Refer to Section 8.4: Differential remote sensing section for details about the light load, highefficiency algorithm.

V<sub>OUT</sub>

The duty cycle of the buck converter, in steady-state conditions, is given by:

#### Equation 2

The switching frequency is therefore calculated as:

**Equation 3**

ion 3

$$f_{SW} = \frac{D}{T_{ON}} = \frac{\frac{V_{OUT}}{V_{IN}}}{K_{OSC}\frac{V_{OUT}}{V_{OSC}} + \tau} \cong \alpha_{OSC} \cdot \frac{1}{K_{OSC}}$$

where:

Equation 4

$$\alpha_{OSC} = \frac{V_{OSC}}{V_{IN}} = \frac{R_{INT}}{R_{INT} + R_{OSC}}$$

can be set by varying the external resistor R<sub>OSC</sub>, placed between the VIN and VOSC pin.  $R_{INT}$  is the integrated switching frequency programming resistor (typ. 17 k $\Omega$ ).

The resulting switching frequency is theoretically independent from battery and output voltage; actually the conduction losses due to MOSFET ON-resistance, inductor DCR and PCB traces can slightly influence the programmed value.

#### PM6652

#### 8.1.1 Constant on-time PWM architecture

*Figure 24* shows the simplified block diagram of a constant on-time controller. A minimum off-time constraint (250 ns typ.) is introduced to allow inductor valley current sensing on the synchronous switch. A minimum on-time (70 ns) is also introduced to assure the startup switching sequence.

The PM6652 has a one-shot generator that turns on the high-side MOSFET when the following conditions are satisfied simultaneously:

- The PWM comparator is high

- The synchronous rectifier current is below the current limit threshold

- The minimum off-time has timed out.

Once the on-time has timed out, the high-side switch is turned off, while the synchronous switch is turned on, according to the anti-cross conduction circuitry management.

When the negative input voltage at the PWM comparator reaches the valley limit (determined by the output voltage), the low-side MOSFET is turned off according to the anticross conduction logic once again, and a new cycle begins.

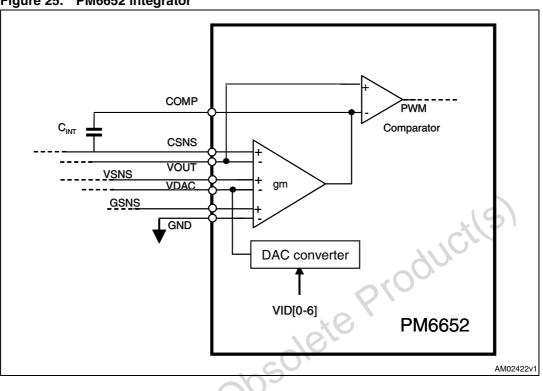

#### 8.1.2 Output ripple compensation

In a classic constant on-time control, the system regulates the valley value of the output voltage and not the average value. In this condition, the half of the output voltage ripple is the equivalent DC static error.

To compensate this error, an integrator network has been introduced in the control loop, by connecting the CSNS pin to the COMP pin through a capacitor  $C_{INT}$  as shown in *Figure 25*. The ripple is generated by the output capacitor ESR and by the voltage drop on the sense resistor  $R_{SENSE}$  (inductor's DCR or dedicated sense resistor). Assuming that  $R_{OUT}$  is the cumulative output capacitors' ESR,  $C_{OUT}$  is the cumulative output capacitance and  $G_M$  is an internal parameter (Gm = 50 µs typ.), the loop stability requires that the  $C_{INT}$  value is:

Equation 5

$C_{INT} \geq g_M \cdot C_{OUT} \cdot R_{OUT}$

The integrator amplifier generates a current, proportional to the DC input error, which sets the output voltage in order to compensate the total static error. In this way the DC output voltage value is independent of the output ripple, ensuring a very good line and load regulation.

In addition, C<sub>INT</sub> provides an AC path for the R<sub>SENSE</sub> voltage ripple. In steady-state condition, the voltage at COMP pin is the sum of the output voltage and the output ripple.

#### Figure 25. PM6652 integrator

### 8.2 Mode selection

The PM6652 has two multifunction pins which allow the selection of the supply mode of operation. There are three different modes, as shown in *Table 8*.

| Table 8. | PM6652 | mode of | operation | selection |

|----------|--------|---------|-----------|-----------|

|----------|--------|---------|-----------|-----------|

$\lambda$

|       | Feature                  | Mode o                                                                     | f operation               |                            |

|-------|--------------------------|----------------------------------------------------------------------------|---------------------------|----------------------------|

|       | eature                   | GFX render IMVP6.5                                                         | CPU core IMVP6.5          | CPU core VR11              |

| colle | VDAC Table               | Table 6                                                                    | Table 6                   | Table 7 on page 18         |

| 05    | VOUT minimum             | 5 mV/µs, DPRSLPVR=LOW                                                      |                           |                            |

| 06    | voltage slew-rate        | 10 mV/ìs, when DPRSLPVR=HIGH (render suspend fast exit mode)               | 5 mV/μs                   | 10 mVµs                    |

|       | VBOOT voltage            | Not required. See <i>Section 8.8: Soft-start and soft-end</i> for details. | 1.1 V                     | 1.1 V                      |

|       | CLKEN#                   | Not used. connect to 5 V.                                                  | Output required           | Not used. connect to SGND. |

|       | Soft-start slew-<br>rate | Programmable by ext. cap.                                                  | Fixed, 5 mV/µs<br>minimum | Programmable by ext. cap.  |

### 8.3 Pulse-skip working mode

The PM6652 can obtain very high efficiency at light load if the low-side MOSFET is turned off when the inductor current becomes equal to zero. This feature is performed by the zerocrossing comparator (see the internal block diagram, *Figure 24*). In CPU and VR11 mode this feature is activated by asserting the DPRSLPVR pin. In GFX render mode the DPRSLPVR assertion implies also that the V<sub>DAC</sub> minimum slew-rate is 10 mV/µs, for increasing the programmed output voltage, as required by IMPV6.5 specifications for render suspend fast exit mode (refer to *Section 8.6: Voltage dynamic (VID) transitions* for details).

### 8.4 Differential remote sensing

The PM6652 performs a differential remote sensing, between the VSNS and GSNS pins. The error between the sensed output voltage and the programmed one (VSNS - VDAC) and between the remote ground and local one (GSNS - GND) are the other two inputs of the integrator, as shown in *Figure 25*. The differential remote sense must be directly connected to the mobile processor differential feedback pins; only two catch resistors (100  $\Omega$ ) are allowed to avoid any VR output voltage runaway, due to a lack of negative feedback when the processor is not mounted.

### 8.5 Droop function

In order to reduce the output capacitance amount, the PM6652 performs a load dependent behavior. The voltage sensed between pins CSNS and  $V_{OUT}$  is proportional to the load current:

**Equation 6**

$$C_{SNS} - V_{OUT} = R_{SNS} \cdot I_{LOAD}$$

Given the network shown in *Figure 25*, the resulting regulated output voltage is:

#### **Equation 7**

$$V_{\text{CORE}_SS} - V_{\text{GND}_SS} = V_{\text{DAC}} - \left(1 + \frac{R_2}{R_1}\right) \cdot R_{\text{SNS}} \cdot I_{\text{LOAD}}$$

From the previous equation the equivalent droop resistance performed by the switching regulator is:

#### **Equation 8**