# 3 A monolithic step-down current source with synchronous rectification

Datasheet - production data

## **Features**

- 3.0 V to 18 V operating input voltage range

- 850 kHz fixed switching frequency

- 100 mV typ. current sense voltage drop

- 6 μA standby current in inhibit mode

- ± 7% output current accuracy

- Synchronous rectification

- 95 m $\Omega$  HS / 69 m $\Omega$  LS typical R<sub>DS(on)</sub>

- · Peak current mode architecture

- Embedded compensation network

- Internal current limiting

- Ceramic output capacitor compliant

- Thermal shutdown

## **Applications**

- · Battery charger

- Signage

- · Emergency lighting

- High brightness LED driving

- General lighting

## **Description**

The ST1CC40 device is an 850 kHz fixed switching frequency monolithic step-down DC-DC converter designed to operate as precise constant current source with an adjustable current capability up to 3 A DC. The regulated output current is set connecting a sensing resistor to the feedback pin. The embedded synchronous rectification and the 100 mV typical R<sub>SENSE</sub> voltage drop enhance the efficiency performance. The size of the overall application is minimized thanks to the high switching frequency and ceramic output capacitor compatibility. The device is fully protected against thermal overheating, overcurrent and output short-circuit. Inhibit mode minimizes the current consumption in standby. The ST1CC40 is available in VFQFPN8 4 mm x 4 mm 8-lead, and standard SO8 package.

Contents ST1CC40

## **Contents**

| 1 | Pin s | settings                                                | 6  |

|---|-------|---------------------------------------------------------|----|

|   | 1.1   | Pin connection                                          | 6  |

|   | 1.2   | Pin description                                         | 6  |

| 2 | Max   | mum ratings                                             | 7  |

| 3 | Ther  | mal data                                                | 7  |

| 4 | Elec  | trical characteristics                                  | 8  |

| 5 | Fund  | tional description                                      | 9  |

|   | 5.1   | Power supply and voltage reference                      | 10 |

|   | 5.2   | Voltage monitor                                         | 10 |

|   | 5.3   | Soft-start                                              | 10 |

|   | 5.4   | Error amplifier                                         | 10 |

|   | 5.5   | Inhibit                                                 | 11 |

|   | 5.6   | Thermal shutdown                                        | 11 |

| 6 | Арр   | ication notes 1                                         | 12 |

|   | 6.1   | Closing the loop                                        | 12 |

|   | 6.2   | G <sub>CO</sub> (s) control to output transfer function | 12 |

|   | 6.3   | Error amplifier compensation network                    | 13 |

|   | 6.4   | LED small signal model                                  | 15 |

|   | 6.5   | Total loop gain                                         | 16 |

|   |       | Example                                                 | 16 |

|   | 6.6   | eDesignSuite software                                   | 18 |

| 7 | Арр   | ication information                                     | 20 |

|   | 7.1   | Component selection                                     | 20 |

|   |       | 7.1.1 Sensing resistor                                  | 20 |

|   |       | 7.1.2 Inductor and output capacitor selection           | 20 |

|   |       | 7.1.3 Input capacitor                                   | 22 |

|   | 7.2   | Layout considerations                                   | 23 |

| ST1CC40 |      | Contents                 |

|---------|------|--------------------------|

|         | 7.3  | Thermal considerations   |

|         | 7.4  | Short-circuit protection |

|         | 7.5  | Application circuit      |

| 8       | Турі | cal characteristics      |

| 9       | Pacl | kage information         |

| 10      | Orde | ering information        |

| 11      | Rev  | sion history             |

List of tables ST1CC40

# List of tables

| Table 1.  | Pin description                                   | . 6 |

|-----------|---------------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings                          | . 7 |

| Table 3.  | Thermal data                                      | . 7 |

| Table 4.  | Electrical characteristics                        | . 8 |

| Table 5.  | Uncompensated error amplifier characteristics     | 11  |

| Table 6.  | Inductor selection                                | 22  |

| Table 7.  | List of ceramic capacitors for the ST1CC40        | 23  |

| Table 8.  | Component list                                    | 29  |

| Table 9.  | VFQFPN8 (4 x 4 x 1.08 mm) package mechanical data | 34  |

| Table 10. | SO8-BW package mechanical data                    | 35  |

| Table 11. | Ordering information                              | 36  |

| Table 12. | Document revision history                         | 37  |

ST1CC40 List of figures

# **List of figures**

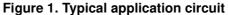

| Figure I.  | Typical application circuit                        | . ! |

|------------|----------------------------------------------------|-----|

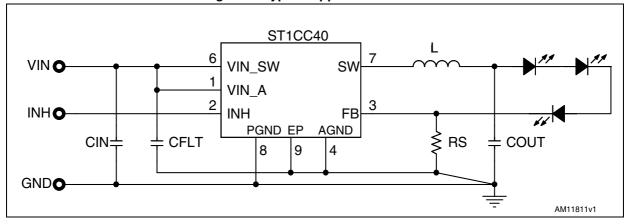

| Figure 2.  | Pin connection (top view)                          | . 6 |

| Figure 3.  | ST1CC40 block diagram                              | . 9 |

| Figure 4.  | Internal circuit                                   | 10  |

| Figure 5.  | Block diagram of the loop                          | 12  |

| Figure 6.  | Transconductance embedded error amplifier          | 14  |

| Figure 7.  | Equivalent series resistor                         | 15  |

| Figure 8.  | Load equivalent circuit                            | 16  |

| Figure 9.  | Module plot                                        | 17  |

| Figure 10. | Phase plot                                         | 18  |

| Figure 11. | eDesignSuite screenshot                            | 19  |

| Figure 12. | Equivalent circuit                                 | 20  |

| Figure 13. | Layout example                                     | 24  |

| Figure 14. | Switching losses                                   |     |

| Figure 15. | Constant current protection triggering hiccup mode | 28  |

| Figure 16. | Demonstration board application circuit            |     |

| Figure 17. | PCB layout (component side) VFQFPN8 package        |     |

| Figure 18. | PCB layout (bottom side) VFQFPN8 package           |     |

| Figure 19. | PCB layout (component side) SO8 package            |     |

| Figure 20. | PCB layout (bottom side) SO8 package               |     |

| Figure 21. | Soft-start                                         |     |

| Figure 22. | Inhibit operation                                  |     |

| Figure 23. | Thermal shutdown protection                        |     |

| Figure 24. | Hiccup current protection                          | 32  |

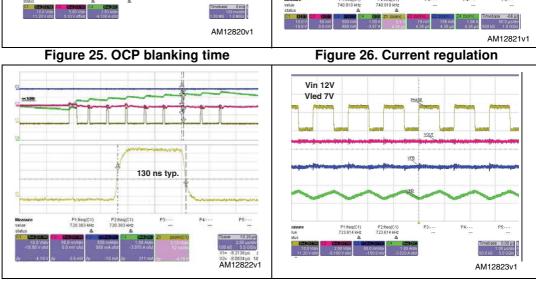

| Figure 25. | OCP blanking time                                  |     |

| Figure 26. | Current regulation                                 |     |

| Figure 27. | VFQFPN8 (4 x 4 x 1.08 mm) package outline          | 33  |

| Figure 28. | SO8-BW package outline                             | 34  |

Pin settings ST1CC40

# 1 Pin settings

## 1.1 Pin connection

Figure 2. Pin connection (top view)

# 1.2 Pin description

Table 1. Pin description

| No.     |        | Toma              | Description                                                                                                                                                                                    |  |

|---------|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VFQFPN8 | S08-BW | Туре              | Description                                                                                                                                                                                    |  |

| 1       | 3      | VIN <sub>A</sub>  | Analog circuitry power supply connection                                                                                                                                                       |  |

| 2       | 4      | INH               | Inhibit input pin. Low signal level disables the device. An external 100 k pulldown resistor is suggested to ensure device disabled when the pin is left floating. Connect to VIN if not used. |  |

| 3       | 5      | FB                | Feedback input. Connect a proper sensing resistor to set the LED current                                                                                                                       |  |

| 4       | 6      | AGND              | Analog circuitry ground connection                                                                                                                                                             |  |

| 5       | -      | NC                | Not connected                                                                                                                                                                                  |  |

| 6       | 8      | V <sub>INSW</sub> | Power input voltage                                                                                                                                                                            |  |

| 7       | 1      | SW                | Regulator switching pin                                                                                                                                                                        |  |

| 8       | 2      | PGND              | Power ground                                                                                                                                                                                   |  |

| -       | 7      | GND               | Connect to AGND                                                                                                                                                                                |  |

ST1CC40 Maximum ratings

# 2 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol            | Parameter                                   | Value                    | Unit |

|-------------------|---------------------------------------------|--------------------------|------|

| V <sub>INSW</sub> | Power input voltage                         | -0.3 to 20               |      |

| V <sub>INA</sub>  | Input voltage                               | -0.3 to 20               |      |

| V <sub>INH</sub>  | Inhibit voltage                             | -0.3 to V <sub>INA</sub> | V    |

| V <sub>SW</sub>   | Output switching voltage                    | -1 to V <sub>IN</sub>    | ]    |

| V <sub>PG</sub>   | Power Good                                  | -0.3 to V <sub>IN</sub>  |      |

| V <sub>FB</sub>   | Feedback voltage                            | -0.3 to 2.5              |      |

| I <sub>FB</sub>   | FB current                                  | -1 to +1                 | mA   |

| P <sub>TOT</sub>  | Power dissipation at T <sub>A</sub> < 60 °C | 2                        | W    |

| T <sub>OP</sub>   | Operating junction temperature range        | -40 to 150               | °C   |

| T <sub>stg</sub>  | Storage temperature range                   | -55 to 150               | °C   |

## 3 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                      |                | Value | Unit |

|-------------------|--------------------------------|----------------|-------|------|

| D                 | Maximum thermal resistance     | stance VFQFPN8 | 40    | °C/W |

| R <sub>thJA</sub> | unction-ambient <sup>(1)</sup> | SO8-BW         | 65    |      |

<sup>1.</sup> Package mounted on demonstration board.

Electrical characteristics ST1CC40

## 4 Electrical characteristics

$T_{J} = 25~^{\circ}C,~V_{CC} = 12~V,$  unless otherwise specified.

**Table 4. Electrical characteristics**

| Cumbal               | Parameter                        | To ak a so diki so s                    | Value |      |      | Unit |

|----------------------|----------------------------------|-----------------------------------------|-------|------|------|------|

| Symbol               |                                  | Test conditions                         | Min.  | Тур. | Max. | Unit |

|                      | Operating input voltage range    | See <sup>(1)</sup>                      | 3     |      | 18   |      |

| $V_{IN}$             | Device ON level                  |                                         | 2.6   | 2.75 | 2.9  | ٧    |

|                      | Device OFF level                 |                                         | 2.4   | 2.55 | 2.7  |      |

| V                    | Foodback valtage                 | T <sub>J</sub> = 25 °C                  | 90    | 97   | 104  | \/   |

| $V_{FB}$             | Feedback voltage                 | T <sub>J</sub> = 125 °C                 | 90    | 100  | 110  | mV   |

| I <sub>FB</sub>      | V <sub>FB</sub> pin bias current |                                         |       |      | 600  | nA   |

| R <sub>DSON</sub> -P | High-side switch on-resistance   | I <sub>SW</sub> = 750 mA                |       | 95   |      | mΩ   |

| R <sub>DSON</sub> -N | Low-side switch on-resistance    | I <sub>SW</sub> = 750 mA                |       | 69   |      | mΩ   |

| I <sub>LIM</sub>     | Maximum limiting current         | See <sup>(2)</sup>                      |       | 5    |      | Α    |

| Oscillator           |                                  | •                                       |       |      | •    |      |

| F <sub>SW</sub>      | Switching frequency              |                                         | 0.7   | 0.85 | 1    | MHz  |

| D                    | Duty cycle                       | See <sup>(2)</sup>                      | 0     |      | 100  | %    |

| DC charac            | cteristics                       | •                                       |       |      | •    |      |

| Iq                   | Quiescent current                | Duty cycle = 0 V <sub>fb</sub> > 100 mV |       | 1.5  | 2.5  | mA   |

|                      |                                  | OFF                                     |       | 2.4  | 4.5  | - μΑ |

| I <sub>QST-BY</sub>  | Total standby quiescent current  | See <sup>(1)</sup>                      |       |      | 6    |      |

| Inhibit              |                                  | •                                       | •     |      | •    | ,    |

| .,                   |                                  | Device ON level                         | 1.2   |      |      | .,   |

| $V_{INH}$            | INH threshold voltage            | Device OFF level                        |       |      | 0.4  | V    |

| I <sub>INH</sub>     | INH current                      |                                         |       | 2    |      | μΑ   |

| Soft-start           |                                  |                                         |       | •    |      | ,    |

| T <sub>SS</sub>      | Soft-start duration              |                                         |       | 1    |      | ms   |

| Protection           | 1                                | •                                       | •     | •    | •    | •    |

| _                    | Thermal shutdown                 |                                         |       | 150  |      |      |

| T <sub>SHDN</sub>    | Hystereris                       |                                         |       | 15   |      | °C   |

|                      |                                  |                                         |       |      |      |      |

Specifications referred to T<sub>J</sub> from -40 to +125 °C. Specifications in the -40 to +125 °C temperature range are assured by design, characterization and statistical correlation.

<sup>2.</sup> Guaranteed by design.

## 5 Functional description

The ST1CC40 device is based on a "peak current mode" architecture with fixed frequency control. As a consequence, the intersection between the error amplifier output and the sensed inductor current generates the control signal to drive the power switch.

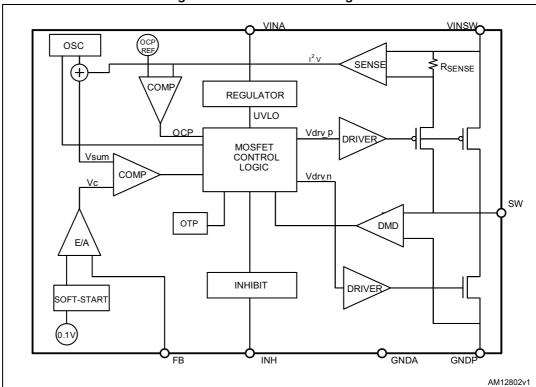

The main internal blocks shown in the block diagram in *Figure 3* are:

- High-side and low-side embedded power element for synchronous rectification

- A fully integrated sawtooth oscillator with a typical frequency of 850 kHz

- A transconductance error amplifier

- A high-side current sense amplifier to track the inductor current

- A pulse width modulator (PWM) comparator and the circuitry necessary to drive the internal power element

- The soft-start circuitry to decrease the inrush current at power-up

- The current limitation circuit based on the pulse-by-pulse current protection with frequency divider

- The inhibit circuitry

- The thermal protection function circuitry

Figure 3. ST1CC40 block diagram

## 5.1 Power supply and voltage reference

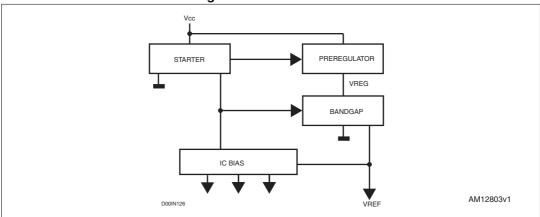

The internal regulator circuit consists of a startup circuit, an internal voltage pre-regulator, the BandGap voltage reference and the bias block that provides current to all the blocks. The starter supplies the startup current to the entire device when the input voltage goes high and the device is enabled (INHIBIT pin connected to  $V_{\rm IN}$ ). The pre-regulator block supplies the bandgap cell with a pre-regulated voltage that has a very low supply voltage noise sensitivity.

## 5.2 Voltage monitor

An internal block continuously senses the  $V_{cc}$ ,  $V_{ref}$  and  $V_{bg}$ . If the monitored voltages are good, the regulator begins operating. There is also a hysteresis on the  $V_{CC}$  (UVLO).

Figure 4. Internal circuit

## 5.3 Soft-start

The startup phase is implemented ramping the reference of the embedded error amplifier in 1 msec typ. time. It minimizes the inrush current and decreases the stress of the power components at power-up.

During normal operation a new soft-start cycle takes place in case of:

- Thermal shutdown event

- UVLO event.

## 5.4 Error amplifier

The voltage error amplifier is the core of the loop regulation. It is a transconductance operational amplifier whose non-inverting input is connected to the internal voltage reference (100 mV), while the inverting input (FB) is connected to the output current sensing resistor.

The error amplifier is internally compensated to minimize the size of the final application.

Table 5. Uncompensated error amplifier characteristics

| Description        | Value  |

|--------------------|--------|

| Transconductance   | 250 μS |

| Low frequency gain | 96 dB  |

| C <sub>C</sub>     | 195 pF |

| R <sub>C</sub>     | 70 ΚΩ  |

The error amplifier output is compared with the inductor current sense information to perform PWM control.

## 5.5 Inhibit

The inhibit block disables most of the circuitry when the INH input signal is low. The current drawn from the input voltage is  $6 \mu A$  typical in inhibit mode.

## 5.6 Thermal shutdown

The shutdown block generates a signal that disables the power stage if the temperature of the chip goes higher than a fixed internal threshold (150  $\pm$  10 °C typical). The sensing element of the chip is close to the PDMOS area, ensuring fast and accurate temperature detection. A 15 °C typical hysteresis prevents the device from turning ON and OFF continuously during the protection operation.

**Application notes** ST1CC40

#### **Application notes** 6

#### Closing the loop 6.1

VIΝ PWM control Gco(s) Current sense HS switch LC filter LS switch error FΒ amplifier V<sub>CONTROI</sub> **PWM**  $V_{REF}$ comparator compensation network AM12804v1

Figure 5. Block diagram of the loop

#### 6.2 G<sub>CO</sub>(s) control to output transfer function

The accurate control to output transfer function for a buck peak current mode converter can be written as:

## **Equation 1**

$$G_{CO}(s) \, = \, \frac{R_0}{R_i} \cdot \frac{1}{1 + \frac{R_0 \cdot T_{SW}}{L} \cdot [m_C \cdot (1-D) - 0.5]} \cdot \frac{\left(1 + \frac{s}{\omega_z}\right)}{\left(1 + \frac{s}{\omega_p}\right)} \cdot F_H(s)$$

where  $\boldsymbol{R}_0$  represents the load resistance,  $\boldsymbol{R}_i$  the equivalent sensing resistor of the current sense circuitry,  $\omega_{\text{p}}$  the single pole introduced by the LC filter and  $\omega_{\text{z}}$  the zero given by the ESR of the output capacitor.

F<sub>H</sub>(s) accounts for the sampling effect performed by the PWM comparator on the output of the error amplifier that introduces a double pole at one half of the switching frequency.

DocID18279 Rev 7 12/38

ST1CC40 Application notes

**Equation 2**

$$\omega_{Z} = \frac{1}{ESR \cdot C_{OUT}}$$

**Equation 3**

$$\omega_{P} \, = \, \frac{1}{R_{LOAD} \cdot C_{OUT}} + \frac{m_{C} \cdot (1-D) - 0.5}{L \cdot C_{OUT} \cdot f_{SW}}$$

where:

**Equation 4**

$$\begin{cases} m_{C} = 1 + \frac{S_{e}}{S_{n}} \\ S_{e} = V_{pp} \cdot f_{SW} \\ S_{n} = \frac{V_{IN} - V_{OUT}}{L} \cdot R_{i} \end{cases}$$

$S_n$  represents the slope of the sensed inductor current,  $S_e$  the slope of the external ramp ( $V_{PP}$  peak-to-peak amplitude) that implements the slope compensation to avoid subharmonic oscillations at duty cycle over 50%.

The sampling effect contribution  $F_H(s)$  is:

**Equation 5**

$$F_{H}(s) = \frac{1}{1 + \frac{s}{\omega_{n} \cdot Q_{p}} + \frac{s^{2}}{\omega_{n}^{2}}}$$

where:

**Equation 6**

$$\omega_n = \pi \cdot f_{SW}$$

and

**Equation 7**

$$Q_{P} = \frac{1}{\pi \cdot [m_{C} \cdot (1 - D) - 0.5]}$$

## 6.3 Error amplifier compensation network

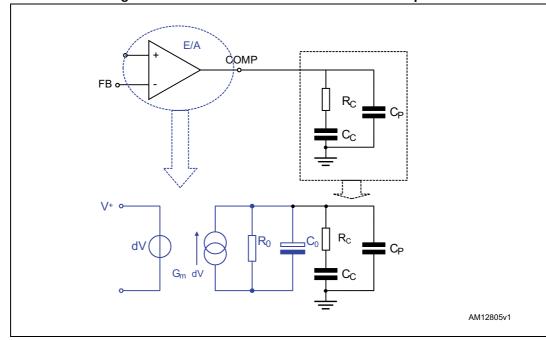

The ST1CC40 device embeds the error amplifier (see *Figure 6*) and a pre-defined compensation network which is effective in stabilizing the system in most of the application conditions.

Application notes ST1CC40

Figure 6. Transconductance embedded error amplifier

$R_C$  and  $C_C$  introduce a pole and a zero in the open loop gain.  $C_P$  does not significantly affect system stability but it is useful to reduce the noise at the output of the error amplifier.

The transfer function of the error amplifier and its compensation network is:

## **Equation 8**

$$A_0(s) = \frac{A_{V0} \cdot (1 + s \cdot R_c \cdot C_c)}{s^2 \cdot R_0 \cdot (C_0 + C_p) \cdot R_c \cdot C_c + s \cdot (R_0 \cdot C_c + R_0 \cdot (C_0 + C_p) + R_c \cdot C_c) + 1}$$

where  $A_{vo} = G_m \cdot R_o$ .

The poles of this transfer function are (if  $C_c >> C_0 + C_P$ ):

## **Equation 9**

$$f_{PLF} = \frac{1}{2 \cdot \pi \cdot R_0 \cdot C_c}$$

## **Equation 10**

$$f_{P HF} = \frac{1}{2 \cdot \pi \cdot R_c \cdot (C_0 + C_p)}$$

whereas the zero is defined as:

## **Equation 11**

$$F_Z = \frac{1}{2 \cdot \pi \cdot R_c \cdot C_c}$$

57/

ST1CC40 **Application notes**

> The embedded compensation network is  $R_C$  = 70 K,  $C_C$  = 195 pF while  $C_P$  and  $C_O$  can be considered as negligible. The error amplifier output resistance is 240 M $\Omega$  so the relevant singularities are:

## **Equation 12**

$$f_Z = 11, 6 \text{ kHz}$$

$f_{PLF} = 3, 4 \text{ Hz}$

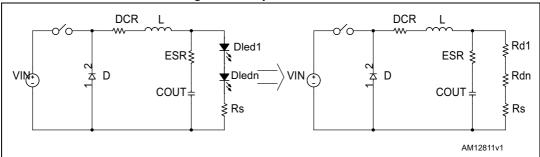

#### 6.4 LED small signal model

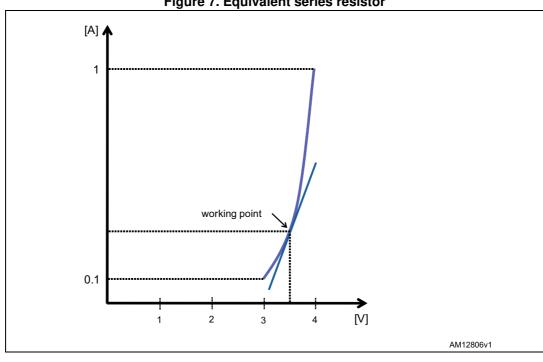

Once the system reaches the working condition the LEDs composing the row are biased and their equivalent circuit can be considered as a resistor for frequencies << 1 MHz.

The LED manufacturer typically provides the equivalent dynamic resistance of the LED biased at different DC current. This parameter is required to study the behavior of the system in the small signal analysis.

For instance, the equivalent dynamic resistance of Luxeon III Star from Lumiled measured with a different biasing current level is reported below:

$$r_{LED}$$

$$\begin{cases} 1.3\Omega & I_{LED} = 350 \text{mA} \\ 0.9\Omega & I_{LED} = 700 \text{mA} \end{cases}$$

In case the LED datasheet doesn't report the equivalent resistor value, it can be simply derived as the tangent to the diode I-V characteristic in the present working point (see Figure 7).

Figure 7. Equivalent series resistor

Application notes ST1CC40

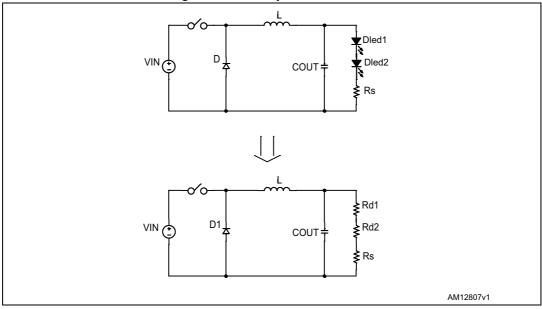

Figure 8 shows the equivalent circuit of the LED constant current generator.

Figure 8. Load equivalent circuit

As a consequence, the LED equivalent circuit gives the  $\alpha_{\text{LED}}(s)$  term correlating the output voltage with the high impedance FB input:

## **Equation 13**

$$\alpha_{\text{LED}}(n_{\text{LED}}) = \frac{R_{\text{SENSE}}}{n_{\text{LED}} \cdot r_{\text{LED}} + R_{\text{SENSE}}}$$

## 6.5 Total loop gain

In summary, the open loop gain can be expressed as:

## **Equation 14**

$$G(s) \, = \, G_{CO}(s) \cdot A_0(s) \cdot \alpha_{LED}(n_{LED})$$

## **Example**

Design specifications:

$$V_{IN} = 12 \text{ V}, V_{FW \text{ LED}} = 3.5 \text{ V}, n_{LED} = 2, r_{LED} = 1.1 \Omega, I_{LED} = 700 \text{ mA}, I_{LED \text{ RIPPLE}} = 2\%$$

The inductor and capacitor value are dimensioned in order to meet the  $I_{LED\ RIPPLE}$  specifications (see Section 7.1.2 for output capacitor and inductor selection guidelines):

$$L = 10 \mu H$$

,  $C_{OUT} = 2.2 \mu F$  MLCC (negligible ESR)

577

ST1CC40 Application notes

Accordingly, with Section 7.1.1 the sensing resistor value is:

## **Equation 15**

$$R_S = \frac{100 \text{ mV}}{700 \text{ mA}} \cong 140 \text{ m}\Omega$$

## **Equation 16**

$$\alpha_{\text{LED}}(n_{\text{LED}}) = \frac{R_{\text{SENSE}}}{n_{\text{LED}} \cdot r_{\text{LED}} + R_{\text{SENSE}}} = \frac{140 \text{ m}\Omega}{2 \cdot 1.1\Omega + 140 \text{ m}\Omega} = 0.06$$

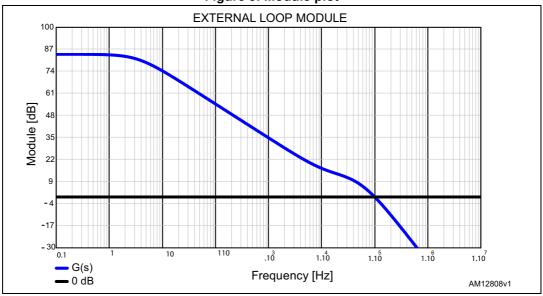

The gain and phase margin Bode diagrams are plotted respectively in *Figure 9* and *Figure 10*.

Application notes ST1CC40

EXTERNAL LOOP GAIN PHASE 180 157.5 135 112.5 Phase 90 67.5 45 22.5 100 1.10 1.18 110 1.10 1.10 — G(s) AM12809v1 Frequency [Hz]

Figure 10. Phase plot

The cutoff frequency and the phase margin are:

## **Equation 17**

$$f_C = 100 \text{ kHz}$$

pm = 47°

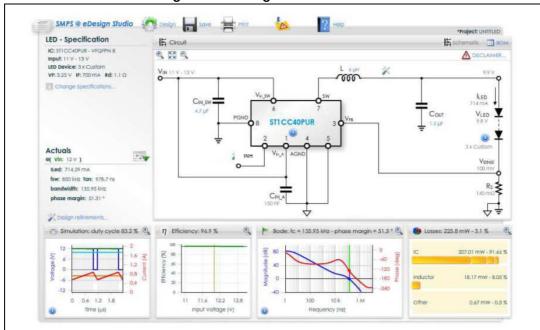

## 6.6 eDesignSuite software

The ST1CC40 device is supported by the eDesign software which can be seen online on the STMicroelectronics  $^{\circledR}$  home page (www.st.com).

ST1CC40 Application notes

Figure 11. eDesignSuite screenshot

The software easily supports the component sizing according to the technical information given in this datasheet (see *Section 6*).

The final user is requested to fill in the requested information such as the input voltage range, the selected LED parameters and the number of LEDs composing the row.

The software calculates external components according to the internal database. It is also possible to define new components and ask the software to have them used.

Bode plots, estimated efficiency and thermal performance are provided.

Finally, the user can save the design and print all the information including the bill of material of the board.

#### **Application information** 7

#### 7.1 Component selection

#### 7.1.1 Sensing resistor

In closed loop operation the ST1CC40 feedback pin voltage is 100 mV so the sensing resistor calculation is expressed as:

## **Equation 18**

$$R_S = \frac{100 \text{ mV}}{I_{LED}}$$

Since the main loop (see Section 6.1) regulates the sensing resistor voltage drop, the average current is regulated into the LEDs. The integration period is at minimum 5 \* T<sub>SW</sub> since the system bandwidth can be dimensioned up to F<sub>SW</sub>/5 at maximum.

The system performs the output current regulation over a period which is at least five times longer than the switching frequency. The output current regulation neglects the ripple current contribution and its reliance on external parameters like input voltage and output voltage variations (line transient and LED forward voltage spread). This performance can not be achieved with simpler regulation loops like a hysteretic control.

For the same reason the switching frequency is constant over the application conditions, that helps to tune the EMI filtering and to guarantee the maximum LED current ripple specifications in the application range. This performance cannot be achieved using constant on/off-time architecture.

#### 7.1.2 Inductor and output capacitor selection

The output capacitor filters the inductor current ripple that, given the application conditions, depends on the inductor value. As a consequence, the LED current ripple, that is the main specification for a switching current source, depends on the inductor and output capacitor selection.

Figure 12. Equivalent circuit

DocID18279 Rev 7 20/38

The LED ripple current can be calculated as the inductor ripple current ratio flowing into the output impedance using the Laplace transform (see *Figure 11*):

### **Equation 19**

$$\Delta I_{RIPPLE}(s) = \frac{\frac{8}{\pi^2} \cdot \Delta I_L \cdot (1 + s \cdot ESR \cdot C_{OUT})}{1 + s \cdot (R_S + ESR + n_{LED} \cdot R_{LED}) \cdot C_{OUT}}$$

where the term  $8/\pi^2$  represents the main harmonic of the inductor current ripple (which has a triangular shape) and  $\Delta I_L$  is the inductor current ripple.

## **Equation 20**

$$\Delta I_L = \frac{V_{OUT}}{L} \cdot T_{OFF} = \frac{n_{LED} \cdot V_{FW\_LED} + 100mV}{L} \cdot T_{OFF}$$

so L value can be calculated as:

### **Equation 21**

$$L \ = \ \frac{n_{\text{LED}} \cdot V_{\text{FW\_LED}} + 100 \text{mV}}{\Delta I_{\text{L}}} \cdot T_{\text{OFF}} \ = \ \frac{n_{\text{LED}} \cdot V_{\text{FW\_LED}} + 100 \text{mV}}{\Delta I_{\text{L}}} \cdot \left(1 - \frac{n_{\text{LED}} \cdot V_{\text{FW\_LED}} + 100 \text{mV}}{V_{\text{IN}}}\right)$$

where  $T_{\mbox{\scriptsize OFF}}$  is the off-time of the embedded high switch, given by 1-D.

As a consequence, the lower the inductor value (so the higher the current ripple), the higher the  $C_{\text{OUT}}$  value would be to meet the specifications.

A general rule to dimension L value is:

### **Equation 22**

$$\frac{\Delta I_L}{I_{LED}} \le 0.5$$

Finally the required output capacitor value can be calculated equalizing the LED current ripple specification with the module of the Fourier transformer (see  $Equation\ 19$ ) calculated at  $F_{SW}$  frequency.

## **Equation 23**

$$|\Delta I_{\text{RIPPLE}}(s=j\cdot\omega)| = \Delta I_{\text{RIPPLE SPEC}}$$

Example (see Section : Example):

$$V_{IN}$$

= 12 V,  $I_{LED}$  = 700 mA,  $\Delta_{ILED}/I_{LED}$  = 2%,  $V_{FW}$   $_{LED}$  = 3.5 V,  $n_{LED}$  = 2

The output capacitor value must be dimensioned according to Equation 23.

Finally, given the selected inductor value, a 2.2 µF ceramic capacitor value keeps the LED current ripple ratio lower than 2% of the nominal current. An output ceramic capacitor type (negligible ESR) is suggested to minimize the ripple contribution given a fixed capacitor value.

**Table 6. Inductor selection**

| Manufacturer      | Series      | Inductor value (μH) | Saturation current (A) |

|-------------------|-------------|---------------------|------------------------|

| Würth Elektronik  | WE-HCI 7040 | 1 to 4.7            | 20 to 7                |

| Wultif Liektionik | WE-HCI 7050 | 4.9 to 10           | 20 to 4.0              |

| Coilcraft         | XPL 7030    | 2.2 to 10           | 29 to 7.2              |

## 7.1.3 Input capacitor

The input capacitor must be able to support the maximum input operating voltage and the maximum RMS input current.

Since step-down converters draw current from the input in pulses, the input current is squared and the height of each pulse is equal to the output current. The input capacitor must absorb all this switching current, whose RMS value can be up to the load current divided by two (worst case, with duty cycle of 50%). For this reason, the quality of these capacitors must be very high to minimize the power dissipation generated by the internal ESR, thereby improving system reliability and efficiency. The critical parameter is usually the RMS current rating, which must be higher than the RMS current flowing through the capacitor. The maximum RMS input current (flowing through the input capacitor) is:

## **Equation 24**

$$I_{RMS} = I_O \cdot \sqrt{D - \frac{2 \cdot D^2}{\eta} + \frac{D^2}{\eta^2}}$$

where  $\eta$  is the expected system efficiency, D is the duty cycle and  $I_O$  is the output DC current. Considering  $\eta=1$ , this function reaches its maximum value at D = 0.5 and the equivalent RMS current is equal to  $I_O$  divided by 2. The maximum and minimum duty cycles are:

### **Equation 25**

$$D_{MAX} = \frac{V_{OUT} + V_{F}}{V_{INMIN} - V_{SW}}$$

and

## **Equation 26**

$$D_{MIN} = \frac{V_{OUT} + V_{F}}{V_{INMAX} - V_{SW}}$$

where  $V_F$  is the freewheeling diode forward voltage and  $V_{SW}$  the voltage drop across the internal PDMOS. Considering the range  $D_{MIN}$  to  $D_{MAX}$ , it is possible to determine the max.  $I_{RMS}$  going through the input capacitor. Capacitors that can be considered are:

## Electrolytic capacitors:

These are widely used due to their low price and their availability in a wide range of RMS current ratings.

The only drawback is that, considering ripple current rating requirements, they are physically larger than other capacitors.

### Ceramic capacitors:

If available for the required value and voltage rating, these capacitors usually have a higher RMS current rating for a given physical dimension (due to very low ESR).

The drawback is the considerably high cost.

Tantalum capacitors:

Small tantalum capacitors with very low ESR are becoming more available. However, they can occasionally burn if subjected to very high current during charge.

Therefore, it is recommended to avoid this type of capacitor for the input filter of the device as they may be stressed by a high surge current when connected to the power supply.

Table 7. List of ceramic capacitors for the ST1CC40

| Manufacturer | Series              | Capacitor value (μF) | Rated voltage (V) |

|--------------|---------------------|----------------------|-------------------|

| TAIYO YUDEN  | UMK325BJ106MM-T     | 10                   | 50                |

| MURATA       | GRM42-2 X7R 475K 50 | 4.7                  | 50                |

In case the selected capacitor is ceramic (so neglecting the ESR contribution), the input voltage ripple can be calculated as:

### **Equation 27**

$$V_{\text{IN PP}} \, = \, \frac{I_{\text{O}}}{C_{\text{IN}} \cdot f_{\text{SW}}} \cdot \left[ \left( 1 - \frac{D}{\eta} \right) \cdot D + \frac{D}{\eta} \cdot (1 - D) \right]$$

## 7.2 Layout considerations

The layout of switching DC-DC converters is very important to minimize noise and interference. Power-generating portions of the layout are the main cause of noise and so high switching current loop areas should be kept as small as possible and lead lengths as short as possible.

High impedance paths (in particular the feedback connections) are susceptible to interference, so they should be as far as possible from the high current paths. A layout example is provided in *Figure 13*.

The input and output loops are minimized to avoid radiation and high frequency resonance problems. The feedback pin to the sensing resistor path must be designed as short as possible to avoid pick-up noise. Another important issue is the ground plane of the board. Since the package has an exposed pad, it is very important to connect it to an extended ground plane in order to reduce the thermal resistance junction-to-ambient.

The input capacitor, connected to VINSW, must be placed as close as possible to the device, to avoid spikes on VINSW due to the stray inductance and the pulsed input current. In order to prevent dynamic unbalance between VINSW and VINA, the trace connecting the VINA pin to the input must be derived from VINSW and designs local ceramic bypass capacitor (1  $\mu$ F) as close as possible to the VINA pin.

To increase the design noise immunity, different signal and power ground should be implemented in the layout (see *Section 7.5: Application circuit*). The signal ground serves the small signal components, the device analog ground pin, the exposed pad and a small filtering capacitor connected to the  $V_{INA}$  pin. The power ground serves the device ground pin and the input filter. The different grounds are connected underneath the output capacitor. Neglecting the current ripple contribution, the current flowing through this component is constant during the switching activity and so this is the cleanest ground point of the buck application circuit.

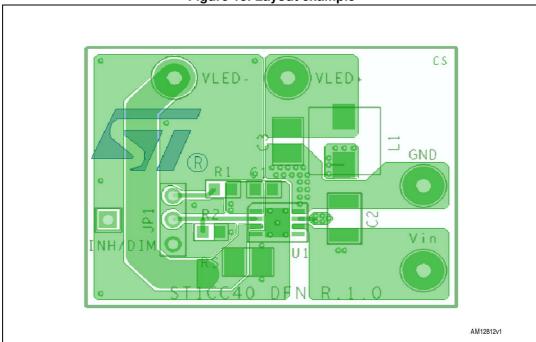

Figure 13. Layout example

## 7.3 Thermal considerations

The dissipated power of the device is tied to three different sources:

Conduction losses due to the R<sub>DS(on)</sub>, which are equal to:

### **Equation 28**

$$\begin{aligned} &P_{ON} = R_{RDSON\_HS} \cdot \left(I_{OUT}\right)^2 \cdot D \\ &P_{OFF} = R_{RDSON\_LS} \cdot \left(I_{OUT}\right)^2 \cdot (1 - D) \end{aligned}$$

where D is the duty cycle of the application. Note that the duty cycle is theoretically given by the ratio between  $V_{OUT}$  ( $n_{LED} * V_{LED} + 100$  mV) and  $V_{IN}$ , but in practice it is substantially higher than this value to compensate for the losses in the overall application. For this reason, the conduction losses related to the  $R_{DS(on)}$  increase compared to an ideal case.

577

• Switching losses due to turning ON and OFF. These are derived using Equation 29:

## **Equation 29**

$$\mathsf{P}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \frac{(\mathsf{T}_{\mathsf{RISE}} + \mathsf{T}_{\mathsf{FALL}})}{2} \cdot \mathsf{F}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \mathsf{T}_{\mathsf{SW\_EQ}} \cdot \mathsf{F}_{\mathsf{SW}}$$

where  $T_{RISE}$  and  $T_{FALL}$  represent the switching times of the power element that causes the switching losses when driving an inductive load (see *Figure 14*).  $T_{SW}$  is the equivalent switching time.

Figure 14. Switching losses

Quiescent current losses.

## **Equation 30**

$$P_Q = V_{IN} \cdot I_Q$$

Example (see Section : Example):

$$V_{IN} = 12 \ V, \ V_{FW\_LED} = 3.5 \ V, \ n_{LED} = 2, \ I_{LED} = 700 \ mA$$

The typical output voltage is:

## **Equation 31**

$$V_{OUT} = n_{LED} \cdot V_{FW\_LED} + V_{FB} = 7.1V$$

$R_{DSON~HS}$  has a typical value of 95 m $\Omega$  and  $R_{DS(on)~LS}$  is 69 m $\Omega$  at 25 °C.

For the calculation we can estimate  $R_{DS(on)\_HS}$  = 140 m $\Omega$  and  $R_{DS(on)\_LS}$  = 100 m $\Omega$  as a consequence of  $T_J$  increase during the operation.

$T_{SW\ EQ}$  is approximately 12 ns.

$I_Q$  has a typical value of 1.5 mA at  $V_{IN}$  = 12 V.

The overall losses are:

## **Equation 32**

$$\mathsf{P}_{\mathsf{TOT}} = \mathsf{R}_{\mathsf{DS}(\mathsf{on}) \; \mathsf{HS}} \cdot \left(\mathsf{I}_{\mathsf{OUT}}\right)^2 \cdot \mathsf{D} + \mathsf{R}_{\mathsf{DS}(\mathsf{on}) \; \mathsf{LS}} \cdot \left(\mathsf{I}_{\mathsf{OUT}}\right)^2 \cdot (1-\mathsf{D}) + \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \mathsf{f}_{\mathsf{SW}} \cdot \mathsf{T}_{\mathsf{SW}} + \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{QU}} + \mathsf{V}_{\mathsf{QU}} +$$

## **Equation 33**

$$P_{TOT} = 0.14 \cdot 0.7^2 \cdot 0.6 + 0.1 \cdot 0.7^2 \cdot 0.4 + 12 \cdot 0.7 \cdot 12 \cdot 10^{-9} \cdot 850 \cdot 10^3 + 12 \cdot 1.5 \cdot 10^{-3} \cong 205 \text{mW}$$

The junction temperature of the device is:

## **Equation 34**

$$T_J = T_A + Rth_{J-A} \cdot P_{TOT}$$

where  $T_A$  is the ambient temperature and  $Rth_{J-A}$  is the thermal resistance junction-to-ambient. The junction-to-ambient ( $Rth_{J-A}$ ) thermal resistance of the device assembled in HSO8 package and mounted on the board is about 40 °C/W.

Assuming the ambient temperature is around 40 °C, the estimated junction temperature is:

### **Equation 35**

$$T_{.1} = 60 + 0.205 \cdot 40 \cong 68^{\circ}C$$

## 7.4 Short-circuit protection

In overcurrent protection mode, when the peak current reaches the current limit threshold, the device disables the power element and it is able to reduce the conduction time down to the minimum value (approximately 100 nsec typ.) to keep the inductor current limited. This is the pulse-by-pulse current limitation to implement the constant current protection feature.

In overcurrent condition, the duty cycle is strongly reduced and, in most applications, this is enough to limit the switch current to the current threshold.

The inductor current ripple during ON and OFF phases can be written as:

ON phase

## **Equation 36**

$$\Delta I_{L \; TON} = \frac{V_{IN} - V_{OUT} - (DCR_L + R_{DS(on) \; HS}) \cdot I}{L} (T_{ON})$$

OFF phase

## **Equation 37**

$$\Delta I_{L \, TON} = \frac{-(V_{OUT} + (DCR_L + R_{DS(on) \, LS}) \cdot I)}{I} (T_{OFF})$$

where DCR<sub>L</sub> is the series resistance of the inductor.

The pulse-by-pulse current limitation is effective in implementing constant current protection when:

### **Equation 38**

$$|\Delta I_{L TON}| = |\Delta I_{L TOFF}|$$

From Equation 36 and Equation 37 we can gather that the implementation of the constant current protection becomes more critical the lower the  $V_{OUT}$  is and the higher  $V_{IN}$  is.

In fact, in short-circuit condition the voltage applied to the inductor during the off-time becomes equal to the voltage drop across parasitic components (typically the DCR of the inductor and the  $R_{DS(on)}$  of the low-side switch) since  $V_{OUT}$  is negligible, while during  $T_{ON}$  the voltage applied at the inductor is maximized and it is approximately equal to  $V_{IN}$ .

In general, the worst case scenario is heavy short-circuit at the output with maximum input voltage. *Equation 36* and *Equation 37* in overcurrent conditions can be simplified to:

### **Equation 39**

$$\Delta I_{L TON} = \frac{V_{IN} - (DCR_L + R_{DS(on) HS}) \cdot I}{L} (T_{ON MIN}) \cong \frac{V_{IN}}{L} (90 ns)$$

considering T<sub>ON</sub> that has already been reduced to its minimum.

### **Equation 40**

$$\Delta I_{L\;TOFF}\;=\;\frac{-(DCR_L+R_{DS(on)\;LS})\cdot I}{L}(T_{SW}-90ns)\cong\frac{-(DCR_L+R_{DS(on)\;LS})\cdot I}{L}(1.18\mu s)$$

where  $T_{SW} = 1 / F_{SW}$  and considering the nominal  $F_{SW}$ .

At higher input voltage,  $\Delta I_{L\ TON}$  may be higher than  $\Delta I_{L\ TOFF}$  and so the inductor current may escalate. As a consequence, the system typically meets *Equation 38* at a current level higher than the nominal value thanks to the increased voltage drop across stray components. In most of the application conditions the pulse-by-pulse current limitation is effective to limit the inductor current. Whenever the current escalates, a second level current protection called "Hiccup mode" is enabled. Hiccup protection offers an additional protection against heavy short-circuit condition at very high input voltage even considering the spread of the minimum conduction time of the power element. If the hiccup current level (6.2 A typ.) is triggered, the switching activity is prevented for 12 cycles.

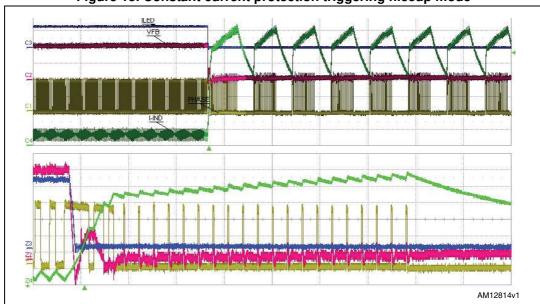

*Figure 15* shows the operation of the constant current protection when a short-circuit is applied at the output at the maximum input voltage.

Figure 15. Constant current protection triggering hiccup mode

## 7.5 Application circuit

ST1CC40

VIN 0

6

VIN\_SW

SW

7

L1

VIN\_A

INH

FB

PGND EP AGND

PGND EP AGND

R1

R1

VIN\_A

RS

C3

2.2 μ, 25 V

GND O

GND O

ST1CC40

VIN\_SW

SW

7

L1

O VLED+

SRS

C3

2.2 μ, 25 V

Signal GND

Power GND

E

Figure 16. Demonstration board application circuit

577

Table 8. Component list

| Reference | Part number        | Description                                                                                                       | Manufacturer |

|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------|--------------|

| C1        |                    | 1 μF 25 V<br>(size 0805)                                                                                          |              |

| C2        | GRM31CR61E106KA12L | 10 μF 25 V<br>(size 1206)                                                                                         | Murata       |

| C3        | GRM21BR71E225KA73L | 2.2 μF 25 V<br>(size 0805)                                                                                        | Murata       |

| R1        |                    | 4.7 KΩ 5%<br>(size 0603)                                                                                          |              |

| R2        |                    | Not mounted                                                                                                       |              |

| Rs        | ERJ14BSFR15U       | 0.15 Ω 1%<br>(size 1206)                                                                                          | Panasonic    |

| L1        | XAL6060-223ME      | 22 μH<br>I <sub>SAT</sub> = 5.6 A (30% drop) I <sub>RMS</sub> = 6.9 A (40 °C rise)<br>(size 6.36 x 6.56 x 6.1 mm) | Coilcraft    |

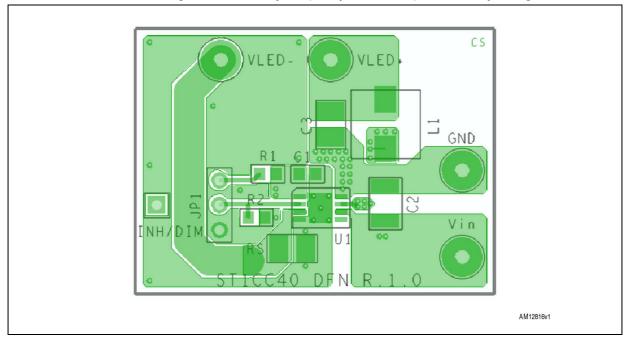

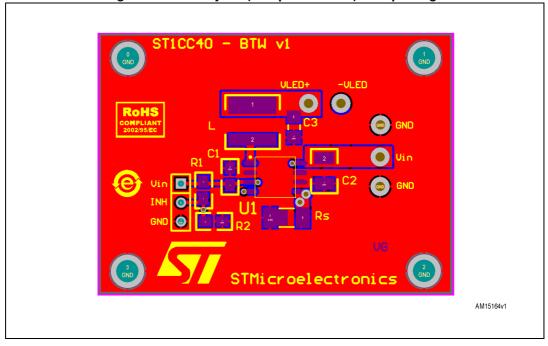

Figure 17. PCB layout (component side) VFQFPN8 package

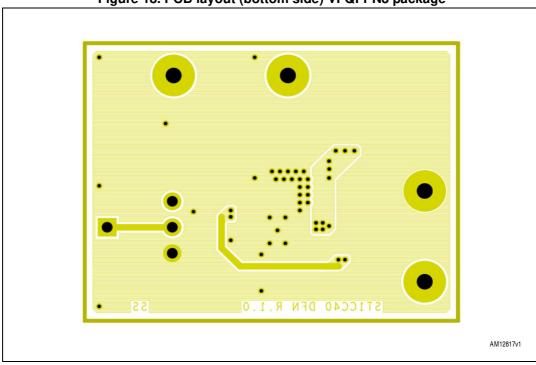

Figure 18. PCB layout (bottom side) VFQFPN8 package

Figure 19. PCB layout (component side) SO8 package

It is strongly recommended that the input capacitors are to be put as close as possible to the relative pins, see C1 and C2.

30/38 DocID18279 Rev 7

STICC40 - BTW VI

CONDLIANT

MOTORISE

STMICTOELECTRONICS

AM15185/1

Figure 20. PCB layout (bottom side) SO8 package

# 8 Typical characteristics

Figure 21. Soft-start

Figure 22. Inhibit operation

Figure 22. Inhibit operation

Figure 22. Inhibit operation

Figure 23. Inhibit operation

AMABERT 72324Hz 72324Hz

Figure 23. Thermal shutdown protection

Figure 24. Hiccup current protection

Figure 24. Hiccup current protection

32/38 DocID18279 Rev 7

ST1CC40 Package information

# 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Figure 27. VFQFPN8 (4 x 4 x 1.08 mm) package outline

Package information ST1CC40

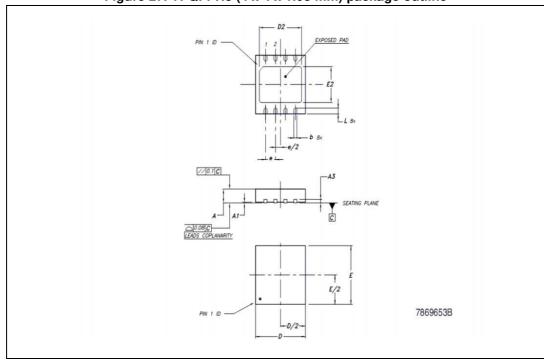

Figure 28. SO8-BW package outline

Table 9. VFQFPN8 (4 x 4 x 1.08 mm) package mechanical data

| Symbol | Dimensions (mm) |      |      |

|--------|-----------------|------|------|

|        | Min.            | Тур. | Max. |

| Α      | 0.80            | 0.90 | 1.00 |

| A1     |                 | 0.02 | 0.05 |

| A3     |                 | 0.20 |      |

| b      | 0.23            | 0.30 | 0.38 |

| D      | 3.90            | 4.00 | 4.10 |

| D2     | 2.82            | 3.00 | 3.23 |

| E      | 3.90            | 4.00 | 4.10 |

| E2     | 2.05            | 2.20 | 2.30 |

| е      |                 | 0.80 |      |

| L      | 0.40            | 0.50 | 0.60 |

Table 10. SO8-BW package mechanical data

| Symbol           | Dimensions (mm) |                      |      |

|------------------|-----------------|----------------------|------|

|                  | Min.            | Тур.                 | Max. |

| А                | 135             |                      | 1.75 |

| A1               | 0.10            |                      | 0.25 |

| A2               | 1.10            |                      | 1.65 |

| В                | 0.33            |                      | 0.51 |

| С                | 0.19            |                      | 0.25 |

| D <sup>(1)</sup> | 4.80            |                      | 5.00 |

| E                | 3.80            |                      | 4.00 |

| е                |                 | 1.27                 |      |

| Н                | 5.80            |                      | 6.20 |

| h                | 0.25            |                      | 0.50 |

| L                | 0.40            |                      | 1.27 |

| k                |                 | 0° (min.), 8° (max.) |      |

| ddd              |                 |                      | 0.10 |

Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shouldn't exceed 0.15 mm (.006 inch) in total (both sides).

Ordering information ST1CC40

# 10 Ordering information

**Table 11. Ordering information**

| Order code | Package          | Packaging     |

|------------|------------------|---------------|

| ST1CC40PUR | VFQFPN8 4 x 4 8L | Tape and reel |

| ST1CC40DR  | SO8-BW           | Tape and reel |

ST1CC40 Revision history

# 11 Revision history

**Table 12. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04-Mar-2011 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                       |

| 21-Jun-2011 | 2        | Updated coverpage                                                                                                                                                                                                                                                                                                                                                                                      |

| 18-Oct-2012 | 3        | Pin 2 operation has been updated: Figure 1 and Table 1 have been updated accordingly. Figure 19 and Figure 20 have been added. Minor text changes to improve the readability. Status promoted from preliminary to production data.                                                                                                                                                                     |

| 04-Mar-2013 | 4        | Updated Table 9: VFQFPN8 (4 x 4 x 1.08 mm) package mechanical data and Section 7.1.2: Inductor and output capacitor selection.  Minor text changes to improve the readability.                                                                                                                                                                                                                         |

| 18-Jun-2013 | 5        | Unified package names in the whole document.  Updated Table 2 (changed "operating junction temperature range" from -40 to 125 °C to -40 to 150 °C).  Updated Table 4 (updated data of IQST-BY symbol).  Updated Section 7.2 (replaced VCC by VINA).  Updated Section 9 (reversed order of Figure 27 and Table 9, Figure 28 and Table 10, minor modifications).  Minor corrections throughout document. |

| 28-Aug-2019 | 6        | Updated Section 5.1: Power supply and voltage reference and Figure 16: Demonstration board application circuit.  Added sentence in Section 7.2: Layout considerations.                                                                                                                                                                                                                                 |

| 05-Aug-2021 | 7        | eDesign Studio has been changed into eDesignSuite.                                                                                                                                                                                                                                                                                                                                                     |

### **IMPORTANT NOTICE – PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to <a href="www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LED Lighting Drivers category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

LV5235V-MPB-H MB39C602PNF-G-JNEFE1 MIC2871YMK-T5 AL1676-10BS7-13 AL1676-20AS7-13 AP5726WUG-7 ICL8201

IS31BL3228B-UTLS2-TR IS31BL3506B-TTLS2-TR AL3157F-7 LV52204MTTBG AP5725WUG-7 STP4CMPQTR NCL30086BDR2G

CAT4004BHU2-GT3 LV52207AXA-VH AP1694AS-13 TLE4242EJ AS3688 IS31LT3172-GRLS4-TR TLD2311EL KTD2694EDQ-TR

KTZ8864EJAA-TR IS32LT3174-GRLA3-TR MP2488DN-LF-Z NLM0010XTSA1 AL1676-20BS7-13 ZXLD1370QESTTC MPQ7220GF-AEC1-P MPQ7220GR-AEC1-P MPQ4425BGJ-AEC1-P MPQ7220GF-AEC1-Z MPQ7220GR-AEC1-Z MPQ4425BGJ-AEC1-Z

IS31FL3737B-QFLS4-TR IS31FL3239-QFLS4-TR KTD2058EUAC-TR KTD2037EWE-TR DIO5662ST6 IS31BL3508A-TTLS2-TR

KTD2026BEWE-TR MAX20052CATC/V+ MAX25606AUP/V+ BD6586MUV-E2 BD9206EFV-E2 LYT4227E LYT6079C-TL

MP3394SGF-P MP4689AGN-P MPQ4425AGQB-AEC1-Z