# STLVDS3486

## High speed differential line drivers

### Feature summary

- meets or exceeds the requirements of ansi TIA/EIA-644 standard

- Operates with a single 3.3V supply

- Designed for signaling rate up to 400Mbps

- Differential input thresholds ±100mV max

- Typical propagation delay time of 2.5ns

- Power dissipation 60mW typical per receiver at 200MHz

- Low voltage TTL (LVTTL) logic output levels

- Pin compatible with the MC3486 and SN65LVD3486

- Open circuit fail safe

- ESD protection: 7KV receiver pins 3KV all pins vs gnd

## Description

The STLVDS3486, is a differential line receiver that implements the electrical characteristics of low voltage differential signaling (LVC.3). This signaling technique lowers the outcut voltage levels of 5V differential stands of levels (such as TIA/EIA-422B) to reduce the power, increase the switching speeds and allow operations with a 3.3V supply rail. This differential receiver provides a valid logical or circut state with a 3.3V supply rail.

It also provides a valid logical putput state with a ±100mV differential input volvage within the input common mode voltage lange. The input common mode voltage allows 1V of ground potential difference between two LVDS nodes.

The interded application of this device and signaling technique is both point-to-point and rected op data transmission over controlled impedance media approximately  $100\Omega$ . The transmission media may be printed circuit board traces, backplanes or cables. The ultimate rate and distance of data transfer depend upon the attenuation characteristics of the media and noise coupling to the environment.

The STLVDS3486 version is characterized for operation from -40°C to  $85^{\circ}$ C.

### Order code

| Part number   | Temperature<br>Range | Package               | Comments            |

|---------------|----------------------|-----------------------|---------------------|

| STLVDS3486BTR | -40 to 85 °C         | TSSOP16 (Tape & Reel) | 2500 parts per reel |

| April 2006    |                      | Rev. 4                | 1/15                |

## Contents

| 1   | Pin configuration                                                                                                                                                                                                                                             |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | Logic diagram                                                                                                                                                                                                                                                 |

| 3   | Maximum ratings 5                                                                                                                                                                                                                                             |

| 4   | Electrical characteristics6                                                                                                                                                                                                                                   |

| 5   | Test circuit                                                                                                                                                                                                                                                  |

| 6   | Typical performance characteristics                                                                                                                                                                                                                           |

| 7   | Package mechanical data 12                                                                                                                                                                                                                                    |

| 8   | Revision history                                                                                                                                                                                                                                              |

| 005 | Logic diagram       4         Maximum ratings       5         Electrical characteristics       6         Test circuit       8         Typical performance characteristics       11         Package mechanical data       12         Revision history       15 |

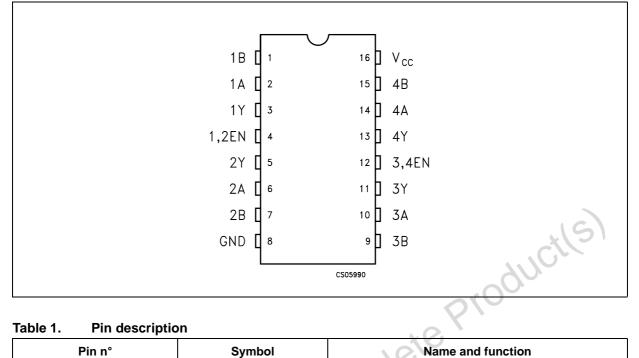

#### **Pin configuration** 1

| Figure 1 | Ι. | Pin | connections |

|----------|----|-----|-------------|

|----------|----|-----|-------------|

#### **Pin description** Table 1.

| Table 1. Pin descriptio | n               |                          |

|-------------------------|-----------------|--------------------------|

| Pin n°                  | Symbol          | Name and function        |

| 2, 6, 10, 14            | 1A to 4A        | Receiver inputs          |

| 1, 7, 9, 15             | 1B to 4B        | Negated receiver inputs  |

| 3, 5, 11, 13            | 1Y to 4Y        | Receiver outputs         |

| 4                       | 1EN, 2EN        | Receivers 1 and 2 enable |

| 12                      | 3EN, 4EN        | Receivers 3 and 4 enable |

| 8                       | GND             | Ground                   |

| 16                      | V <sub>cc</sub> | Supply voltage           |

|                         |                 |                          |

#### Table 2. Truth table

| Differential input               | Enables | Output |

|----------------------------------|---------|--------|

| A, B                             | EN      | Y      |

| $V_{ID} \ge 100 \text{mV}$       | Н       | Н      |

| -100mV < V <sub>ID</sub> < 100mV | Н       | ?      |

| $V_{ID} \le -100 mV$             | Н       | L      |

| Х                                | L       | Z      |

| OPEN                             | Н       | Н      |

L=Low level, H=High Level, X=Don't care, Z= High Impedance

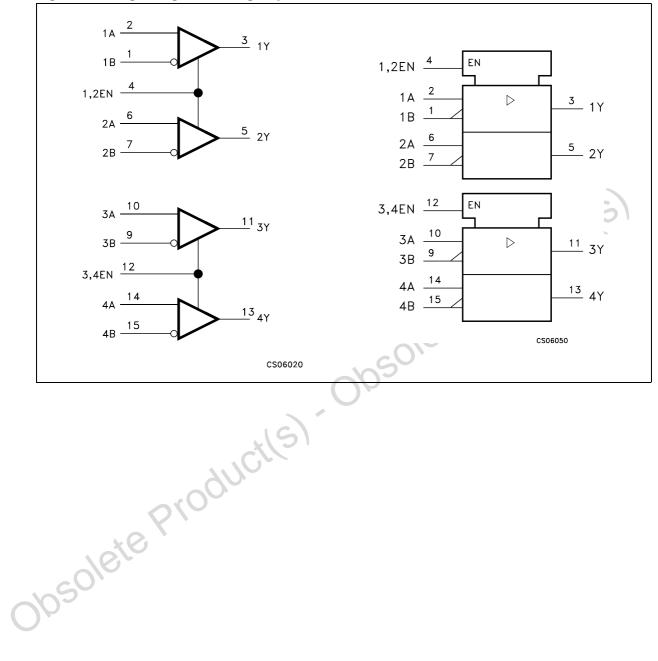

# 2 Logic diagram

Figure 2. Logic diagram and logic symbol

#### **Maximum ratings** 3

| Symbol           | Paramete                         | Value                                                                               | Unit        |      |                         |  |   |

|------------------|----------------------------------|-------------------------------------------------------------------------------------|-------------|------|-------------------------|--|---|

| V <sub>CC</sub>  | Supply voltage (Note 1)          | Supply voltage (Note 1)         Input voltage         Input voltage (A or B inputs) |             |      | Supply voltage (Note 1) |  | V |

| VI               | Input voltage                    |                                                                                     |             |      |                         |  |   |

| VI               | Input voltage (A or B inputs)    |                                                                                     |             |      |                         |  |   |

| ESD              | Human bady model                 | Pins receivers                                                                      | 7           | — кv |                         |  |   |

| 230              | Human body model All pins vs gnd |                                                                                     | 3           |      |                         |  |   |

| T <sub>stg</sub> | Storage temperature range        |                                                                                     | -65 to +150 | °C   |                         |  |   |

#### Table 3. Absolute maximum ratings

Note: Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

All voltages except differential I/O bus voltage, are with respect to the network ground Note: 1 terminal. arndi

| Symbol                                            | Parameter                               | Min.                | Тур. | Max.                    | Unit |

|---------------------------------------------------|-----------------------------------------|---------------------|------|-------------------------|------|

| V <sub>CC</sub>                                   | Supply voltage                          | 3.0                 | 3.3  | 3.6                     | V    |

| V <sub>IH</sub> HIGH Level input voltage (enable) |                                         | 2.0                 |      |                         | V    |

| V <sub>IL</sub>                                   | LOW Level input voltage (enable)        | 5                   |      | 0.8                     | V    |

| V <sub>ID</sub>                                   | Magnitude of differential input voltage | 0.1                 |      | 0.6                     | V    |

| V <sub>IC</sub>                                   |                                         | 0.5 V <sub>ID</sub> |      | 2.4-0.5 V <sub>ID</sub> | V    |

|                                                   | Common mode input voltage               |                     |      | V <sub>CC</sub> - 0.8   |      |

| TJ                                                | Operating temperature range             | -40                 |      | 85                      | °C   |

| osolf                                             | ste Proole                              |                     |      |                         |      |

#### Table 4. **Recommended operating conditions**

# 4 Electrical characteristics

#### Table 5. Electrical characteristics

<sup>(</sup>Over recommended operating conditions unless otherwise noted. All typical values are at  $T_A$  = 25°C, and  $V_{CC}$  = 3.3V).

| Symbol              | Parameter                                                  | Test conditions               | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------------------|-------------------------------|------|------|------|------|

| V <sub>ITH+</sub>   | Positive Going Differential Input Voltage<br>Threshold     |                               |      |      | 100  | mV   |

| V <sub>ITH-</sub>   | Negative Going Differential Input<br>Voltage Threshold     |                               | -100 |      |      | mV   |

| M                   | High Level Output Voltage                                  | I <sub>OH</sub> = -8mA        | 2.4  |      |      | V    |

| V <sub>OH</sub>     | light Level Output voltage                                 | I <sub>OH</sub> = -4mA        | 2.8  |      |      | v    |

| V <sub>OL</sub>     | Low Level Output Voltage                                   | I <sub>OH</sub> = 8mA         |      |      | 0.4  | V    |

|                     | Supply Current                                             | Enabled, No Load              |      | 10   | 18   | mA   |

| I <sub>CC</sub>     | Supply Current                                             | Disabled                      |      | 0.25 | 0.5  | mA   |

| 1                   | Input Current (A or P inpute)                              | $V_{I} = 0V$                  | -2   | -10  | -20  |      |

| l,                  | Input Current (A or B inputs)                              | V <sub>1</sub> = 2.4V -1.2 -3 |      | -3   |      | μA   |

| I <sub>I(OFF)</sub> | Power off Input Current (A or B inputs)                    | $V_{CC} = 0, V_{I} = 3.6V$    |      | 10   | 20   | μA   |

| IIH                 | High Level Input Current (EN, G, $\overline{G}$ or Inputs) | V <sub>IH</sub> = 2V          |      |      | 10   | μΑ   |

| Ι <sub>ΙL</sub>     | Low Level Input Current (EN, G, $\overline{G}$ or Inputs)  | V <sub>IL</sub> = 0.8V        |      |      | 10   | μΑ   |

| I <sub>OZ</sub>     | High Impedance Output Current                              | $V_0 = 0 \text{ or } V_{CC}$  |      |      | ± 10 | μA   |

$V_{IL} = V_{0}$

57

### Table 6.Switching characteristics

(Over recommended operating conditions unless otherwise noted. All typical values are at  $T_A = 25$  °C, and  $V_{CC} = 3.3$ V).

| Symbol              | Parameter                                                      | Test conditions               | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------------------|-------------------------------|------|------|------|------|

| t <sub>PLH</sub>    | Propagation Delay Time, Low to<br>High Output                  |                               | 1.5  | 2.5  | 3.3  | ns   |

| t <sub>PHL</sub>    | Propagation Delay Time, High to Low Output                     |                               | 1.5  | 2.5  | 3.3  | ns   |

| t <sub>r</sub>      | Differential Output Signal Rise<br>Time                        |                               |      | 0.4  |      | ns   |

| t <sub>f</sub>      | Differential Output Signal Fall<br>Time                        | C <sub>L</sub> = 10pF, Fig. 1 |      | 0.4  |      | ns   |

| t <sub>sk(O)</sub>  | Channel to Channel Output Skew (note1)                         |                               |      | 0.1  | 0.3  | ns   |

| t <sub>sk(P)</sub>  | Pulse Skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) (note2)    |                               |      | 0.2  | 0.4  | ns   |

| t <sub>sk(PP)</sub> | Part to Part Skew (note3)                                      |                               |      |      | 1    | ns   |

| t <sub>PZH</sub>    | Propagation Delay Time, High<br>Impedance to High Level Output |                               |      | 3    | 12   | ns   |

| t <sub>PZL</sub>    | Propagation Delay Time, High<br>Impedance to Low Level Output  | Fig. 2                        | 05   | 5    | 12   | ns   |

| t <sub>PHZ</sub>    | Propagation Delay Time, High<br>Level to High Impedance Output |                               |      | 5    | 12   | ns   |

| t <sub>PLZ</sub>    | Propagation Delay Time, Low<br>Level to High Impedance Output  | soleto                        |      | 5    | 12   | ns   |

Note: 1  $t_{sk(O)}$  is the maximum delay time difference between the propagation delay of one channel and that of the others on the same chip with any event on the inputs.

- 2  $t_{sk(P)}$  is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

- 3 t<sub>sk(PP)</sub> is the differential channel-to-channel skew of any event between devices. This specification applies to devices at the same V<sub>CC</sub>, and within 5°C of each other within the operating temperature range.

Jbsolete

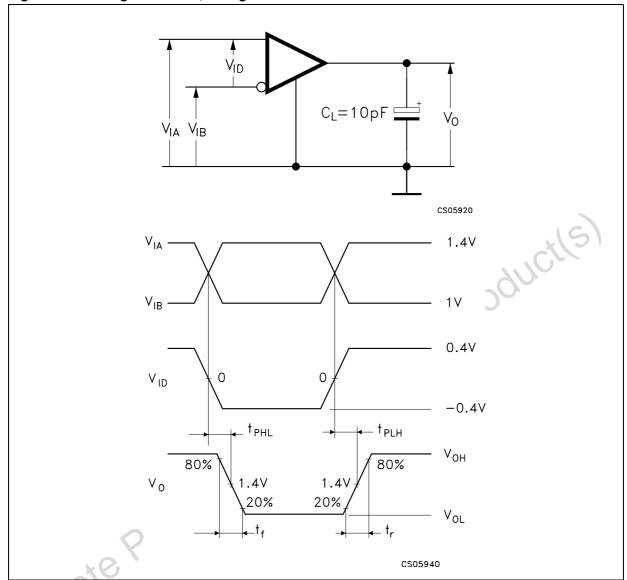

## 5 Test circuit

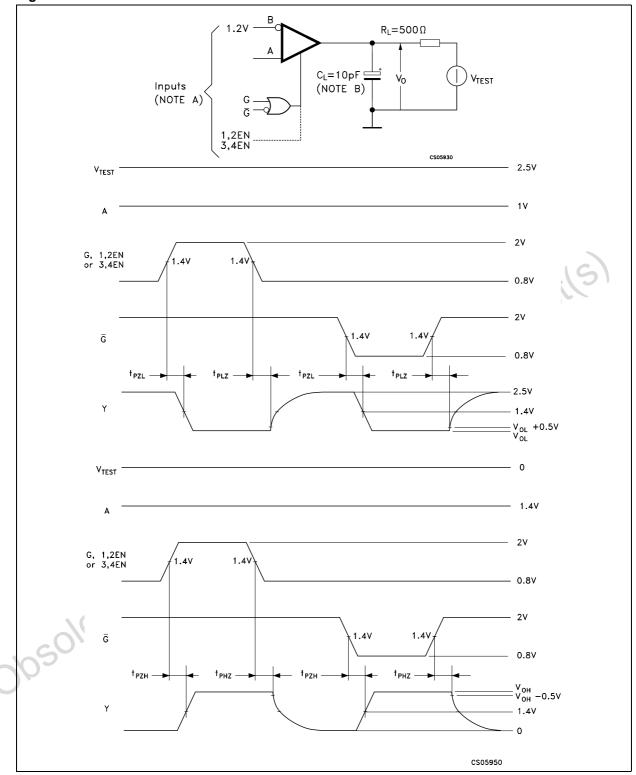

### Figure 3. Timing test circuit, timing and waveforms

Note A: All input pulse are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$ ns, pulse repetition rate (PRR) = 50Mpps, pulse width = 10 ± 0.2ns. Note B:  $C_L$  includes instrumentation and fixture capacitance within 6mm of the D.U.T.

Figure 4. Enable and disable time test circuit and waveform

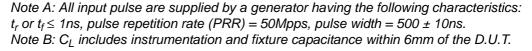

# **6** Typical performance characteristics

(unless otherwise specified at  $T_J = 25^{\circ}C$ )

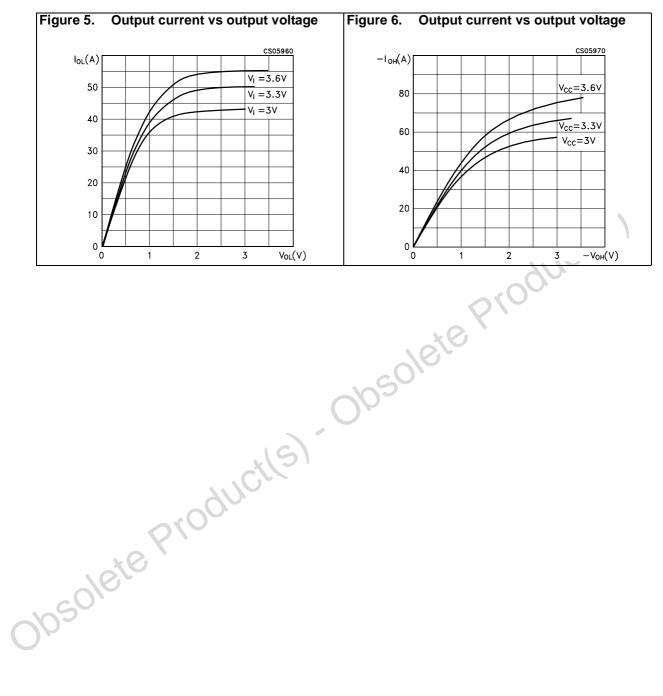

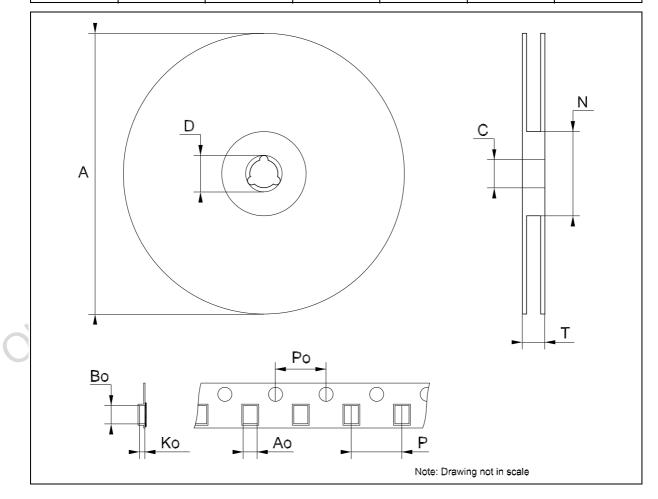

## 7 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

obsolete Product(s)- Obsolete Product(s)

57

| DIM  |      | mm.      |      |       | inch       |        |  |  |

|------|------|----------|------|-------|------------|--------|--|--|

| DIM. | MIN. | ТҮР      | MAX. | MIN.  | TYP.       | MAX.   |  |  |

| A    |      |          | 1.2  |       |            | 0.047  |  |  |

| A1   | 0.05 |          | 0.15 | 0.002 | 0.004      | 0.006  |  |  |

| A2   | 0.8  | 1        | 1.05 | 0.031 | 0.039      | 0.041  |  |  |

| b    | 0.19 |          | 0.30 | 0.007 |            | 0.012  |  |  |

| С    | 0.09 |          | 0.20 | 0.004 |            | 0.0079 |  |  |

| D    | 4.9  | 5        | 5.1  | 0.193 | 0.197      | 0.201  |  |  |

| E    | 6.2  | 6.4      | 6.6  | 0.244 | 0.252      | 0.260  |  |  |

| E1   | 4.3  | 4.4      | 4.48 | 0.169 | 0.173      | 0.176  |  |  |

| е    |      | 0.65 BSC |      |       | 0.0256 BSC |        |  |  |

| к    | 0°   |          | 8°   | 0°    |            | 8°     |  |  |

| L    | 0.45 | 0.60     | 0.75 | 0.018 | 0.024      | 0.030  |  |  |

| Tape & Reel TSSOP16 MECHANICAL DATA |      |     |      |       |      |        |  |  |  |

|-------------------------------------|------|-----|------|-------|------|--------|--|--|--|

| DIM.                                |      | mm. |      |       | inch |        |  |  |  |

| DIWI.                               | MIN. | ТҮР | MAX. | MIN.  | TYP. | MAX.   |  |  |  |

| A                                   |      |     | 330  |       |      | 12.992 |  |  |  |

| С                                   | 12.8 |     | 13.2 | 0.504 |      | 0.519  |  |  |  |

| D                                   | 20.2 |     |      | 0.795 |      |        |  |  |  |

| Ν                                   | 60   |     |      | 2.362 |      |        |  |  |  |

| Т                                   |      |     | 22.4 |       |      | 0.882  |  |  |  |

| Ao                                  | 6.7  |     | 6.9  | 0.264 |      | 0.272  |  |  |  |

| Во                                  | 5.3  |     | 5.5  | 0.209 |      | 0.217  |  |  |  |

| Ко                                  | 1.6  |     | 1.8  | 0.063 |      | 0.071  |  |  |  |

| Po                                  | 3.9  |     | 4.1  | 0.153 |      | 0.161  |  |  |  |

| Р                                   | 7.9  |     | 8.1  | 0.311 |      | 0.319  |  |  |  |

# 8 Revision history

### Table 7. Revision history

| Date        | Revision | Changes                                        |

|-------------|----------|------------------------------------------------|

| 06-Apr-2006 | 4        | Order codes has been updated and new template. |

Obsolete Product(s) - Obsolete Product(s)

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZE REPRESENTATIVE OF ST, ST PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS, WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2006 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Buffers & Line Drivers category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below :

5962-9217601MSA 634810D HEF4043BP NL17SG125DFT2G NL17SZ126P5T5G NLU1GT126CMUTCG NLU3G16AMX1TCG NLV27WZ125USG CY2CP1504ZXC CY2DP1510AXC MC74HCT365ADTR2G BCM6306KMLG 54FCT240CTDB Le87401NQC Le87402MQC 028192B 042140C 051117G 070519XB 065312DB 091056E 098456D NL17SG07DFT2G NL17SG17DFT2G NL17SG34DFT2G NL17SZ07P5T5G NL17SZ125P5T5G NLU1GT126AMUTCG NLV27WZ16DFT2G NLV74LCX244DTR2G 5962-8982101PA 5962-9052201PA 74LVC07ADR2G MC74VHC1G125DFT1G NL17SH17P5T5G NL17SZ125CMUTCG NLV17SZ07DFT2G NLV37WZ17USG NLVHCT244ADTR2G NC7WZ17FHX 74HCT126T14-13 NL17SH125P5T5G NLV14049UBDTR2G NLV37WZ07USG 74VHC541FT(BE) SNJ54LVTH244AW 74LVC1G17FW4-7 74LVC1G126FZ4-7 BCM6302KMLG 74LVC1G07FZ4-7