# STMPE1208S

# S-Touch<sup>™</sup> 12-channel capacitive touchkey controller

## Features

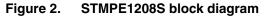

- 12 touchkey capacitive sensor inputs

- 12-bit general purpose input/output (GPIO)

- Operating voltage 3.0 5.5 V

- 98 µA in active mode, 60 µA in idle mode

- Dual interrupt output pin

- I<sup>2</sup>C interface (up to 400 kHz)

- 7 kV HBM ESD protection

- Idle and sleep mode for low power operation

- Advanced data filtering (AFS)

- Environment tracking calibration (ETC)

- Individually adjustable touch variance (TVR) setting for all channels

- Adjustable environmental variance (EVR) for optimal calibration

## Applications

- Notebook computers

- Monitors

- Set-top boxes

- Televisions

- Portable media players and game consoles

- Mobile and smart phones

- Home entertainment systems

- Domestic appliances

## Description

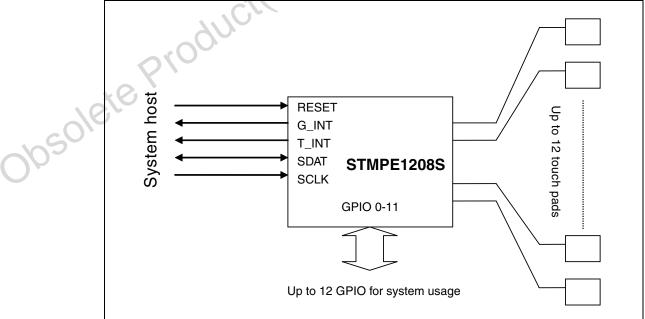

The STMPE1208S is a 12-channel GPIO capacitive touchkey sensor able to interface a main digital ASIC via the two-line bidirectional bus (I<sup>2</sup>C). It senses changes in capacitance using a fully digital architecture, giving fast and accurate results at very low power consumption. Automatic impedance calibration ensures that changes in environment will never affect the correct operation of the capacitive touchkeys.

### Table 1. Device summary

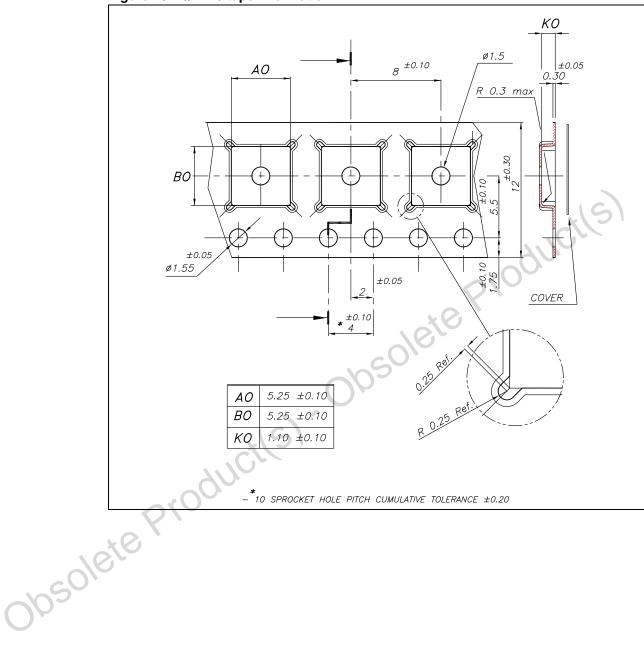

| Order code    | Package | Packing       |

|---------------|---------|---------------|

| STMPE1208SQTR | QFN40   | Tape and reel |

# Contents

| 1     | Pin c                       | onfiguration and function           | . 6 |

|-------|-----------------------------|-------------------------------------|-----|

|       | 1.1                         | Power management                    | . 9 |

| 2     | Cloc                        | c setting                           | 10  |

| 3     | I2C ir                      | nterface                            | 11  |

|       | 3.1                         | Start condition                     |     |

|       | 3.2                         | Stop condition                      |     |

|       | 3.3                         | Acknowledge bit (ACK)               | 11  |

|       | 3.4                         | Data Input                          | 12  |

|       | 3.5                         | Slave device address                | 12  |

|       | 3.6                         | Memory addressing                   | 12  |

| 4     |                             | er schemes                          |     |

| 5     | Сара                        | citive sensors                      | 15  |

|       | 5.1                         | Capacitive sensing                  | 15  |

|       | 5.2                         | Capacitance compensation            | 16  |

|       | 5.3                         | Setting of TVR and EVR              | 16  |

|       |                             | 5.3.1 3-stage data filtering system | 17  |

|       |                             | 5.3.2 Noise filtering               | 18  |

| 10    | 20                          | 5.3.3 BEEP output                   |     |

| bsole |                             | 5.3.4 Interrupt system              | 19  |

| 6     |                             | ster map and function description   | 20  |

| 7     | Com                         | mand registers                      | 36  |

| 8     | Maxi                        | mum rating                          | 39  |

|       | 8.1                         | Recommended operating conditions    |     |

| 9     | Electrical specifications 4 |                                     |     |

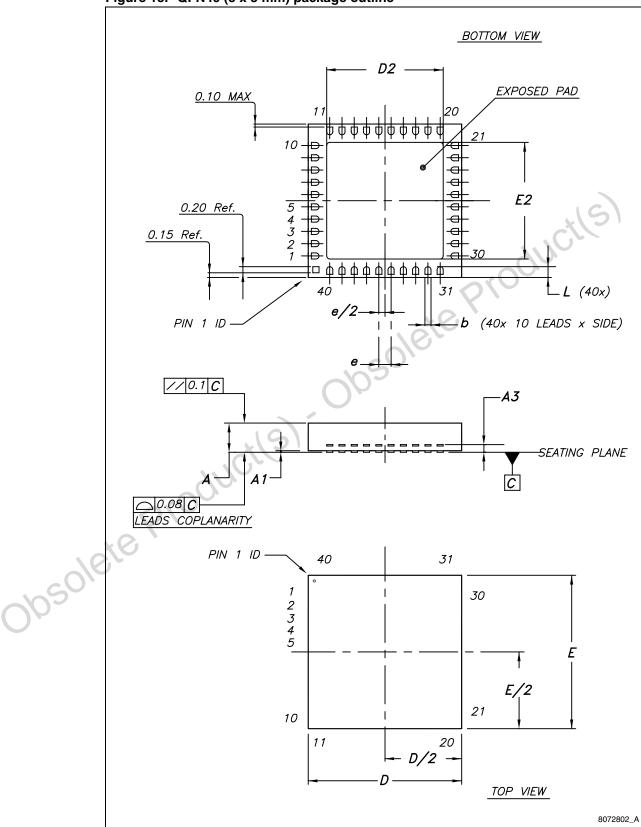

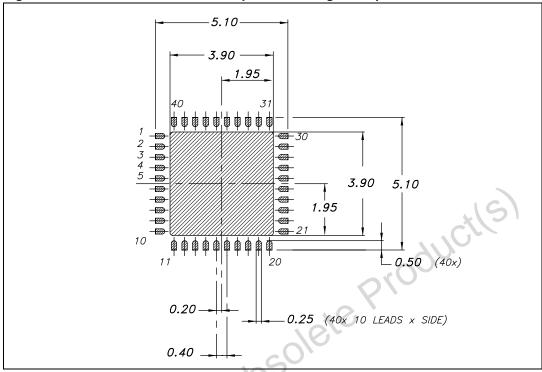

| 10    | Pack                        | age mechanical data                 | 41  |

| 2/47  |                             | Doc ID 14438 Rev 5                  | 7/  |

| 11 | <b>Revision history</b> | · | 46 |

|----|-------------------------|---|----|

|----|-------------------------|---|----|

obsolete Product(s). Obsolete Product(s)

57

# List of tables

| Table 1.<br>Table 2.<br>Table 3.<br>Table 4.<br>Table 5.<br>Table 6.<br>Table 7.<br>Table 8.<br>Table 9.<br>Table 10.<br>Table 11.<br>Table 12.<br>Table 13. | Device summary1Pin assignments and description6Clocking system10I2C addresses11Operation modes12Calibration action under different scenarios17Register summary map table20Command registers36Absolute maximum ratings39Recommended operating conditions39DC electrical characteristics (-40 - 85 °C unless otherwise stated)40QFN40 (5 x 5 mm) mechanical data41Document revision history46                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                              | Device summary       1         Pin assignments and description       6         Clocking system       10         12C addresses       11         Operation modes       12         Calibration action under different scenarios       17         Register summary map table       20         Command registers       36         Absolute maximum ratings       39         Recommended operating conditions       39         DC electrical characteristics (-40 - 85 °C unless otherwise stated)       40         QFN40 (5 x 5 mm) mechanical data       41         Document revision history       46 |

| 0,0501                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# List of figures

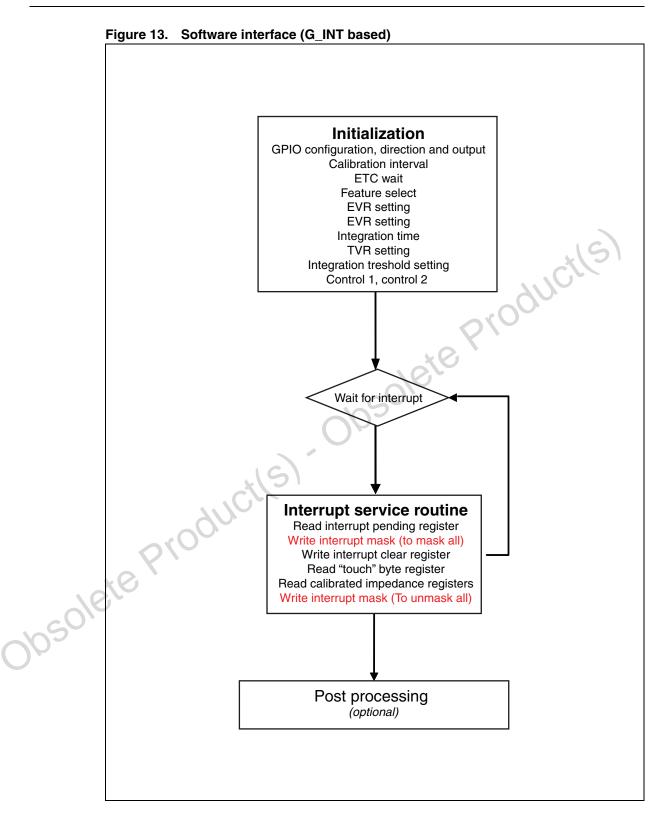

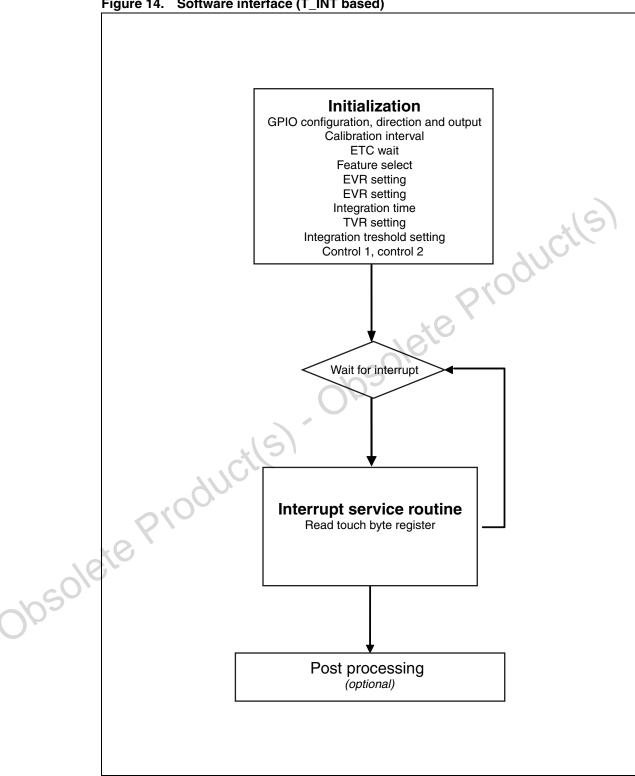

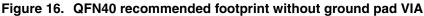

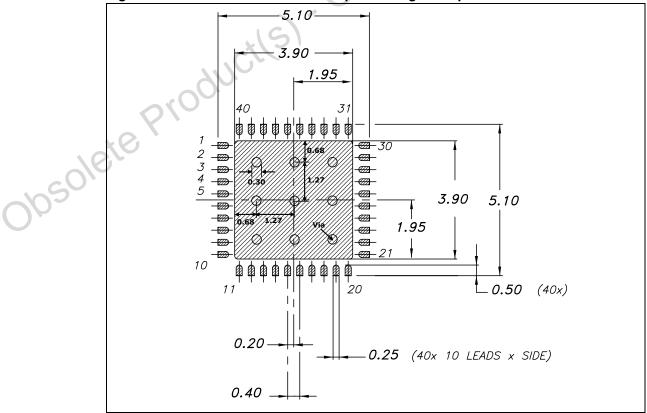

| Figure 1.<br>Figure 2.<br>Figure 3.<br>Figure 3.<br>Figure 5.<br>Figure 6.<br>Figure 7.<br>Figure 8.<br>Figure 9.<br>Figure 10.<br>Figure 11.<br>Figure 12.<br>Figure 13.<br>Figure 14.<br>Figure 15.<br>Figure 16.<br>Figure 18.<br>Figure 19. | 3-stage data filtering system       18         Interrupt system       19         Software interface (G_INT based)       31         Software interface (T_INT based)       32         QFN40 (5 x 5 mm) package outline       34         QFN40 recommended footprint without ground pad VIA       44         QFN40 recommended footprint with ground pad VIA       44         QFN40 tape information       44 | 8893445568978233 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Obsol                                                                                                                                                                                                                                           | ette                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

#### Pin configuration and function 1

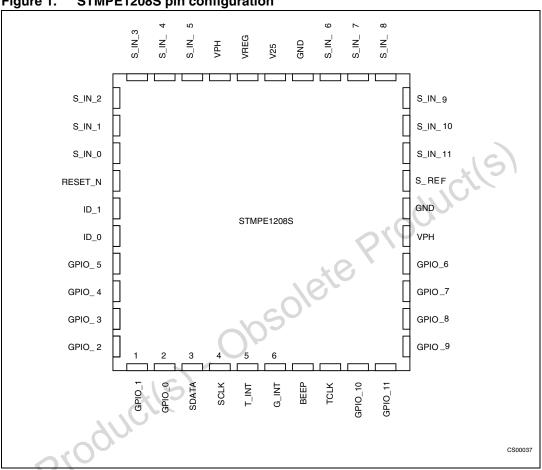

#### Figure 1. STMPE1208S pin configuration

Table 2. Pin assignments and description

| Table 2. Pl | n assignments and description                                                                                   |                                                                                                                                                                                                                                                                                                     |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin number  |                                                                                                                 | Description                                                                                                                                                                                                                                                                                         |  |  |

| 1           | GPIO_1                                                                                                          | General purpose I/O                                                                                                                                                                                                                                                                                 |  |  |

| 2           | GPIO_0                                                                                                          | General purpose I/O                                                                                                                                                                                                                                                                                 |  |  |

| 3           | SDATA                                                                                                           | I <sup>2</sup> C data                                                                                                                                                                                                                                                                               |  |  |

| 4           | SCLK                                                                                                            | I <sup>2</sup> C clock                                                                                                                                                                                                                                                                              |  |  |

| 5           | T_INT                                                                                                           | Touch interrupt                                                                                                                                                                                                                                                                                     |  |  |

| 6           | G_INT                                                                                                           | General interrupt                                                                                                                                                                                                                                                                                   |  |  |

| 7           | BEEP                                                                                                            | Beep output                                                                                                                                                                                                                                                                                         |  |  |

| 8           | TCLK                                                                                                            | Test pin (to be grounded)                                                                                                                                                                                                                                                                           |  |  |

| 9           | GPIO_11                                                                                                         | General purpose I/O                                                                                                                                                                                                                                                                                 |  |  |

| 10          | GPIO_10                                                                                                         | General purpose I/O                                                                                                                                                                                                                                                                                 |  |  |

| 11          | GPIO_9                                                                                                          | General purpose I/O                                                                                                                                                                                                                                                                                 |  |  |

|             | Pin number         1         2         3         4         5         6         7         8         9         10 | Pin number         Pin name           1         GPIO_1           2         GPIO_0           3         SDATA           4         SCLK           5         T_INT           6         G_INT           7         BEEP           8         TCLK           9         GPIO_11           10         GPIO_10 |  |  |

Doc ID 14438 Rev 5

|                        | Pin number | Pin name | Description                                                                                                                                    |  |

|------------------------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        | 12         | GPIO_8   | General purpose I/O                                                                                                                            |  |

|                        | 13         | GPIO_7   | General purpose I/O                                                                                                                            |  |

|                        | 14         | GPIO_6   | General purpose I/O                                                                                                                            |  |

|                        | 15         | VPH      | 3 –5.5 V power supply (regulator input)<br>Supply to this pin is also used for powering the GPIO                                               |  |

|                        | 16         | GND      | Ground                                                                                                                                         |  |

|                        | 17         | S_REF    | Touch sensing reference.                                                                                                                       |  |

|                        | 18         | S_IN_11  | Capacitance sensing input 11                                                                                                                   |  |

|                        | 19         | S_IN_10  | Capacitance sensing input 10                                                                                                                   |  |

|                        | 20         | S_IN_9   | Capacitance sensing input 9                                                                                                                    |  |

|                        | 21         | S_IN_8   | Capacitance sensing input 8                                                                                                                    |  |

|                        | 22         | S_IN_7   | Capacitance sensing input 7                                                                                                                    |  |

|                        | 23         | S_IN_6   | Capacitance sensing input 6                                                                                                                    |  |

|                        | 24         | GND      | Ground                                                                                                                                         |  |

|                        | 25         | V25      | 2.5 V supply                                                                                                                                   |  |

|                        | 26         | VREG     | Internal regulator output                                                                                                                      |  |

|                        | 27         | VPH      | 3-5.5 V power supply (regulator input)                                                                                                         |  |

|                        | 28         | S_IN_5   | Capacitance sensing input 5                                                                                                                    |  |

|                        | 29         | S_IN_4   | Capacitance sensing input 4                                                                                                                    |  |

|                        | 30         | S_IN_3   | Capacitance sensing input 3                                                                                                                    |  |

|                        | 31         | S_IN_2   | Capacitance sensing input 2                                                                                                                    |  |

|                        | 32         | S_IN_1   | Capacitance sensing input 1                                                                                                                    |  |

|                        | 33         | S_IN_0   | Capacitance sensing input 0                                                                                                                    |  |

| sole                   | 34         | RESET_IN | Active low reset pin.<br>This pin should be held 'low' for 10 mS from power stable<br>state. Recommended: 47 K resistor with 0.47 µF capacitor |  |

| $\mathbf{O}\mathbf{V}$ | 35         | ID_1     | I <sup>2</sup> C address                                                                                                                       |  |

|                        | 36         | ID_0     | I <sup>2</sup> C address                                                                                                                       |  |

|                        | 37         | GPIO_5   | General purpose I/O                                                                                                                            |  |

|                        | 38         | GPIO_4   | General purpose I/O                                                                                                                            |  |

|                        | 39         | GPIO_3   | General purpose I/O                                                                                                                            |  |

|                        | 40         | GPIO_2   | General purpose I/O                                                                                                                            |  |

Table 2.

Pin assignments and description (continued)

## 1.1 Power management

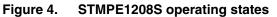

The STMPE1208S operates in 3 states.

On reset, the STMPE1208S enters the active state immediately.

Upon a fixed period of inactivity, the device enters into the IDLE state. Any touch activity in IDLE state would cause the device to go back to active state.

In IDLE state, the calibration will not run. If the calibration is required at all time, set F2A bit to '1'.

If no touch activity is expected, the host may set the device into SLEEP state to save power.

# 2 Clock setting

The STMPE1208S uses a flexible clocking system that allows the user to adjust the clock speed for optimization of power consumption.

| OSC     | PDIV      | Clock   | NDIV  | Active       | ldle    |

|---------|-----------|---------|-------|--------------|---------|

| 050     |           |         |       | Sensor clock |         |

|         | 00        | 1.6 MHz | 0     | 20 kHz       | 100 Hz  |

| U       | 00        |         | 1     | 10 kHz       | 50 Hz   |

|         | 01        | 800 kHz | 0     | 10 kHz       | 50 Hz   |

| -       | 000 KI 12 | 1       | 5 kHz | 25 Hz        |         |

| 1.6 MHz | 10        | 400 kHz | 0     | 5 kHz        | 25 Hz   |

| 10      | 10        |         | 1     | 2.5 kHz      | 12.5 Hz |

|         | 44        | 200 kHz | 0     | 2.5 kHz      | 12.5 Hz |

|         | 11 200    |         | 1     | 1.25 kHz     | 6.25 Hz |

Table 3.Clocking system

The clock frequency must be set to value higher than the expected I<sup>2</sup>C frequency.

#### I<sup>2</sup>C interface 3

The features that are supported by the I<sup>2</sup>C interface are the following ones:

- I<sup>2</sup>C slave device

- Compliant to Philips I<sup>2</sup>C specification version 2.1

- Supports standard (up to 100 kbps) and fast (up to 400 kbps) modes.

- 7-bit and 10-bit device addressing modes

- General call

- Start/restart/stop

The address is selected by the state of 2 pins. The state of the pins is read upon reset and then the pins can be configured for normal operation. The pins have a pull-up or down to set the address. The I<sup>2</sup>C interface module allows the connected host system to access the registers in the STMPE1208S.

I<sup>2</sup>C addresses Table 4.

| Table 4. I <sup>2</sup> C addresses |      |               |               |      |  |  |

|-------------------------------------|------|---------------|---------------|------|--|--|

| ID_1                                |      | 7-bit address | 7-bit address |      |  |  |

| ו_טו                                | ID_0 |               | Write         | Read |  |  |

| 0                                   | 0    | 0x58          | 0xB0          | 0xB1 |  |  |

| 0                                   | 1    | 0x59          | 0xB2          | 0xB3 |  |  |

| 1                                   | 0    | 0x5A          | 0xB4          | 0xB5 |  |  |

| 1                                   | 16   | 0x5B          | 0xB6          | 0xB7 |  |  |

#### 3.1 Start condition

A start condition is identified by a falling edge of SDATA while SCLK is stable at high state. A start condition must precede any data/command transfer. The device continuously monitors for a start condition and will not respond to any transaction unless one is encountered.

## Stop condition

A stop condition is identified by a rising edge of SDATA while SCLK is stable at high state. A stop condition terminates communication between the slave device and bus master. A read command that is followed by NoAck can be followed by a stop condition to force the slave device into idle mode. When the slave device is in idle mode, it is ready to receive the next I2C transaction. A Stop condition at the end of a write command stops the write

## operation to registers.

#### 3.3 Acknowledge bit (ACK)

The acknowledge bit is used to indicate a successful byte transfer. The bus transmitter releases the SDATA after sending eight bits of data. During the ninth bit, the receiver pulls

the SDATA low to acknowledge the receipt of the eight bits of data. The receiver may leave the SDATA in high state if it would to not acknowledge the receipt of the data.

## 3.4 Data Input

The device samples the data input on SDATA on the rising edge of the SCLK. The SDATA signal must be stable during the rising edge of SCLK and the SDATA signal must change only when SCLK is driven low.

## 3.5 Slave device address

The slave device address is a 7 or 10-bit address, where the least significant 3-bit are programmable. These 3-bit values will be loaded in once upon reset and after that these 3 pins no longer be needed with the exception during general call. Up to 4 STMPE1208S devices can be connected on a single  $I^2C$  bus.

## 3.6 Memory addressing

For the bus master to communicate to the slave device, the bus master must initiate a start condition and followed by the slave device address. Accompanying the slave device address, there is a read/bit (R/). The bit is set to 1 for read and 0 for write operation.

If a match occurs on the slave device address, the corresponding device gives an acknowledgement on the SDA during the 9th bit time. If there is no match, it deselects itself from the bus by not responding to the transaction.

|        | Mode  | Byte | Programming sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | P100  | 0    | Start, device address, $R/\overline{W} = 0$ , register address to be read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |       |      | Restart, device address, $R/\overline{W} = 1$ , data read, stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Obsole | Read  | ≥1   | If no stop is issued, the data read can be continuously performed. If<br>the register address falls within the range that allows an address auto-<br>increment, then the register address auto-increments internally after<br>every byte of data being read. For those register addresses that fall<br>within a non-incremental address range, the address will be kept static<br>throughout the entire write operations. Refer to the memory map table<br>for the address ranges that are auto and non-increment. An example<br>of such a non-increment address is FIFO |

|        |       | ≥1   | Start, device address, $R/\overline{W} = 0$ , register address to be written, data write, stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | Write |      | If no stop is issued, the data write can be continuously performed. If<br>the register address falls within the range that allows address auto-<br>increment, then the register address auto-increments internally after<br>every byte of data being written in. For those register addresses that<br>fall within a non-incremental address range, the address will be kept<br>static throughout the entire write operations. Refer to the memory map<br>table for the address ranges that are auto and non-increment.                                                   |

Table 5. Operation modes

Figure 5. Read and write modes (random and sequential)

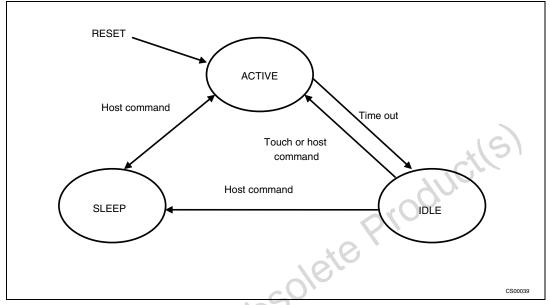

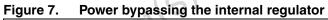

## 4 Power schemes

The STMPE1208S can be powered by a 2.5 V supply directly, or 3.0 - 5.5 V supply through the internal voltage regulator.

Figure 6. Power using the internal regulator

1. REG\_DISABLE bit in CTRL\_2 register = 0

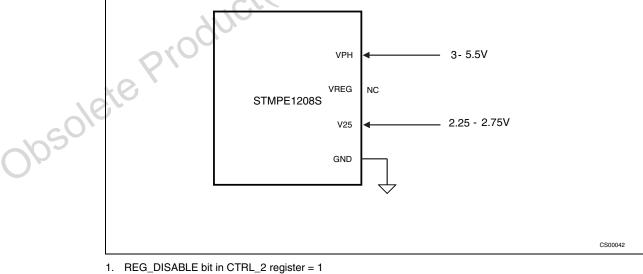

## 5 Capacitive sensors

The STMPE1208S capacitive sensor is based on fully digital, impedance change detection engine that is capable of detecting very small change in capacitance.

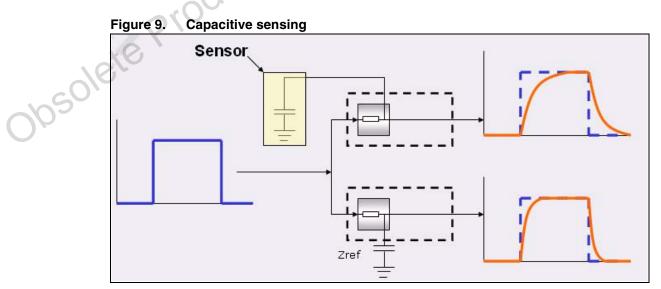

## 5.1 Capacitive sensing

The STMPE1208S senses a human touch by the additional capacitance introduced to the pad (with respect to ground). This capacitance causes a delay in a clock signal on the sensing pad, and the delay in the sensing pad is compared with a reference clock and the difference is a direct representation of the additional capacitance introduced by the proximity/touch of finger.

## 5.2 Capacitance compensation

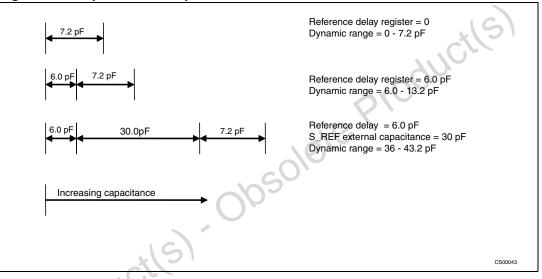

The STMPE1208S is capable to measuring up to 7.2 pF in capacitance difference between the reference point (Zref) and the individual channels. In the case where the PCB connection between the sensor pads and the device is too long, the "reference delay" register is able to shift the reference by up to 6.0 pF, allowing the touch channels to measure added capacitance 7.2 pF with offset of 6.0 pF, as shown in following diagram.

In case this is still not enough to compensate for the capacitance on sensor lines (due to very long sensor trace), an external capacitor of up to 30 pF can be connected at the A\_Ref pin. This allows to further shift up the dynamic range of the capacitance measurement.

Figure 10. Capacitance compensation

The sensed capacitance is accessible to host through the "IMPEDANCE" registers.

## 5.3 Setting of TVR and EVR

The STMPE1208S uses 2 main parameters to control the sensitivity and calibration of the capacitive sensing system. TVR (touch variance) is a channel-specific value, that specifies the number of steps the sensed capacitance must be above the internal reference, to be considered a touch. Generally, this should be set as 4 - 10, but it must be bigger than EVR.

The EVR (environment variance) is a shared value that is applied to all the channels. This specifies the maximum change in capacitance that can be considered due to the shifting of the environmental factor. Generally, this should be set to 1-5, but it must be less than TVR.

### **Environment tracking calibration**

On power up, a calibration is executed. The initial calibration takes about 150 clock cycles of sensor clock for completion. Using 5 kHz sensor clock, this would be 30 mS.

However, if any of the sensors are touched during powering up, calibration is delayed, until all sensors are untouched. In this case, the time taken for calibration, from the time when all sensors are untouched is:

2 \* calibration interval + 150 \* sensor clock period

Doc ID 14438 Rev 5

The STMPE1208S maintains 2 parameters for each touch channels: TVR and calibrated impedance. calibrated impedance is an internal reference of which, if the currently measured impedance exceeds the calibrated impedance by a magnitude of TVR, it is considered a touch.

If the impedance is more than the calibrated impedance, but the magnitude does not exceed calibrated impedance by TVR, it is not considered a TOUCH. In this case, 2 scenarios are possible:

- 1. Environmental changes has caused the impedance to increase

- 2. Finger is near the sensing pad, but not near enough

In case 1, the change in impedance is expected to be small, as environmental changes are normally gradual. A value "EVR" is maintained to specify the maximum impedance change that is still considered an environmental change.

| Scenario                                                                                      | Touch sensing and calibration action     |

|-----------------------------------------------------------------------------------------------|------------------------------------------|

| IMP>CALIBRATED IMP + TVR                                                                      | Touch,<br>no calibration                 |

| IMP>CALIBRATED IMP + EVR                                                                      | No touch,<br>no calibration              |

| IMP <calibrated +="" imp="" td="" tvr<=""><td>No touch,</td></calibrated>                     | No touch,                                |

| IMP <calibrated +="" evr<="" imp="" td=""><td>new Calibrated IMP = previous</td></calibrated> | new Calibrated IMP = previous            |

| IMP>CALIBRATED IMP                                                                            | Calibrated IMP + change in IMP           |

| IMP <calibrated imp<="" td=""><td>No touch,<br/>new alibrated IMP = new IMP</td></calibrated> | No touch,<br>new alibrated IMP = new IMP |

Table 6.

Calibration action under different scenarios

ETC WAIT register state a period of time of which, all touch inputs must remain "no touch" for the next calibration to be carried out.

CAL INTERVAL states the period of time between successive calibrations when there are prolonged no touch condition.

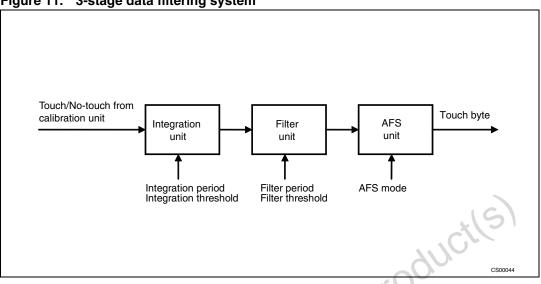

## 5.3.1 3-stage data filtering system

The output from the calibration unit is an instantaneous "touch" or "no touch" status. This output is directed to the filtering stage where the 2 stage noise filtering and 1 stage data filtering is applied to the touch status.

Figure 11. 3-stage data filtering system

### Integration and filtering unit

Touch is sampled across a programmable period of time. The output of the integration stage would be a "strength" (in strength register) that indicates the number of times a "touch" is seen, across the integration period. The "strength" is then compared with the value in "strength threshold" register. If strength exceeds the strength threshold, this is considered a valid touch.

If required, a 2<sup>nd</sup> stage filtering feature controlled by filter period and filter threshold registers.

In data filtering stage, 3 modes of operation are supported:

AFS Mode 1: Only the touch channel with highest strength is taken

AFS Mode 2: All touch channels with strength > strength threshold is taken

AFS Mode 3: The 2 touch channels with the highest strength are selected.

These modes are selected using the feature selector register.

The final, filtered data is accessible through the touch byte register.

#### 5.3.2 Noise filtering

When the STMPE1208S is operating in the vicinity of highly emissive circuits (DC-DC converter, PWM controller/drive etc), the sensor inputs will be affected by high-frequency noise. In this situation, the 2-stage time-integrating function could be used to distinguish between real touch, or emission-related false touch.

#### 5.3.3 **BEEP** output

STMPE1208S is able to drive an external piezo buzzer directly with the built-in beep generator. The beep output can be programmed to varies from 1.5 kHz to 400 kHz, with period of 100 µS to 2.5 S.

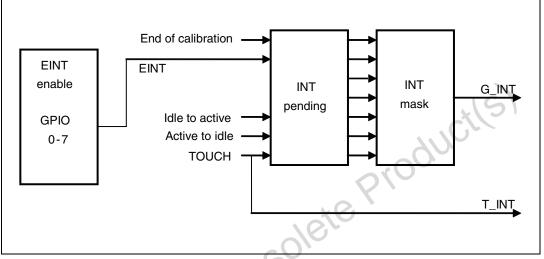

## 5.3.4 Interrupt system

2 interrupt pins are available in STMPE1208S for different application needs.

- G\_INT asserts when there are any unmasked interrupt events

- T\_INT asserts when there are any touch events

### Figure 12. Interrupt system

- 1. G\_INT is cleared by writing to the INT CLEAR register

- 2. T\_INT is cleared by reading the Touch Byte register

# 6 Register map and function description

This section lists and describes the registers of the STMPE1208S device, starting with a register map and then detailed descriptions of register types.

|     | Address    | Module register   | Туре | Reset value | Description                                                            |

|-----|------------|-------------------|------|-------------|------------------------------------------------------------------------|

|     | 0x00       | FEATURE_SEL       | R/W  | 0x04        | Feature selection                                                      |

|     | 0x01 –0x0C | TVR 0 –11         | R/W  | 0x08        | TVR (touch variance) setting of each capacitive channel                |

|     | 0x0D       | EVR               | R/W  | 0x04        | EVR (enviromental variance) setting of all 12 channels                 |

|     | 0x0E       | ETC_WAIT          | R/W  | 0x27        | Wait time for calibration                                              |

|     | 0x0F       | REF_DELAY         | R/W  | 0x00        | Value of reference delay chain                                         |

|     | 0x10-0x1B  | STRENGTH_THRES    | R/W  | 0x01        | Setting of strength threshold for each channel                         |

|     | 0x1C       | INTEGRATION_ TIME | R/W  | 0x0F        | Integration time for AFS mode                                          |

|     | 0x1D       | IDLE_TIME         | R/W  | 0x0F        | Period to enter IDLE mode after non-activity                           |

|     | 0x1E       | GPIO_REG_L        | R/W  | 0x00        | Output state of I/O if configured as GPIO                              |

|     | 0x1F       | GPIO_REG_H        | R/W  | 0x00        | Output state of I/O if configured as GPIO                              |

|     | 0x20       | GPIO_CFG_L        | R/W  | 0x00        | To configure I/O as GPIO or direct capacitive measurement output       |

|     | 0x21       | GPIO_CFG_H        | R/W  | 0x00        | To configure I/O as GPIO or<br>direct capacitive measurement<br>output |

| 16  | 0x22       | GPIO_DIR_L        | R/W  | 0x00        | Direction of GPIO                                                      |

| )   | 0x23       | GPIO_DIR_H        | R/W  | 0x00        | Direction of GPIO                                                      |

| 9/6 | 0x24       | CTRL_1            | R/W  | 0x00        | Functional control of capacitive sensing                               |

|     | 0x25       | CTRL_2            | R/W  | 0x00        | Functional control of capacitive sensing                               |

|     | 0x26       | INT_MASK          | R/W  | 0x00        | Mask for GINT interrupt sources                                        |

|     | 0x27       | INT_CLR           | R/W  | 0x00        | Writing this register clears the INT pending register                  |

|     | 0x28       | BEEP_PER          | R/W  | 0x00        | Set the period of beep output                                          |

|     | 0x29       | BEEP_FREQ         | R/W  | 0x00        | Set the frequency of beep output                                       |

### Table 7. Register summary map table

| Table 7.             | Register summary ma | p table (col | ntinuea)    |                                                              |  |

|----------------------|---------------------|--------------|-------------|--------------------------------------------------------------|--|

| Address              | Module register     | Туре         | Reset value | Description                                                  |  |

| 0x2A                 | CAL_INTERVAL        | R/W          | 0x30        | Set the interval between calibrations                        |  |

| 0x2B                 | EXT_INT_EN          | R/W          | 0x00        | Enable for GPIO interrupt                                    |  |

| 0x2C                 | EXT_INT_POL         | R/W          | 0x00        | Polarity of GPIO interrupt                                   |  |

| 0x2D                 | FILTER_PERIOD       | R/W          | 0x00        | Set the period for filter feature                            |  |

| 0x2E                 | FILTER_TRES         | R/W          | 0x00        | Set the threshold of filter feature                          |  |

| 0x50 –0x5B           | STRENGHT            | R            | 0x00        | Strength recorded during each integration period in AFS mode |  |

| 0x5C0x67             | CAL_IMP             | R            | 0x00        | Reference impedance of each channel after ETC calibration    |  |

| 0x68 –0x73           | IMP                 | R            | 0x00        | Measured impedance of each channel                           |  |

| 0x74                 | STA                 | R            | 0x00        | Power management mode                                        |  |

| 0x75                 | TOUCH_BYTE_L        | R            | 0x00        | Touch sensing data output                                    |  |

| 0x76                 | TOUCH_BYTE_H        | R            | 0x00        | Touch sensing data output                                    |  |

| 0x77                 | INT_PENDING         | RS           | 0x00        | Status of GINT interrupt sources                             |  |

| 0x78                 | GPIO_IN_L           | R            | 0x00        | GPIO input states can be read here                           |  |

| 0x79                 | GPIO_IN_H           | R            | 0x00        | GPIO input states can be read here                           |  |

| 0xF8                 | CLK_SRC_INTERN      | W            | _           |                                                              |  |

| 0xF9                 | CLK_SRC_EXT         | W            | _           |                                                              |  |

| 0xFA                 | BIAS_OFF            | W            | _           |                                                              |  |

| 0xFB                 | BIAS_ON             | W            | _           |                                                              |  |

| 0xFB<br>0xFC<br>0xFD | WAKEUP_SLEEP        | W            | _           |                                                              |  |

| 0xFD                 | ENTER_SLEEP         | W            | _           |                                                              |  |

| 0xFE                 | COLD_RST            | W            | _           |                                                              |  |

| 0xFF                 | WARM_RST            | W            | _           |                                                              |  |

Table 7.

Register summary map table (continued)

| FEATURE     | SE    | L                                   |           |              |                                        | Feature sele   | ection register      |

|-------------|-------|-------------------------------------|-----------|--------------|----------------------------------------|----------------|----------------------|

| 7           | 6     | 5                                   | 4         | 3            | 2                                      | 1              | 0                    |

|             |       | RESERVED                            |           | AFS3         | AFS2                                   | AFS1           | FILTER_EN            |

| Address:    |       | 0x00                                |           |              |                                        |                |                      |

| Туре:       |       | R/W                                 |           |              |                                        |                |                      |

| Reset:      |       | 0x04                                |           |              |                                        |                |                      |

| Description |       | The feature sele<br>RESERVED        | ction reg | ister is use | d to select the A                      | FS mode and fi | lter enable          |

|             | [3]   | AFS3: write '1' to                  | enable AF | S mode 3 (tv | wo strongest keys                      | only)          |                      |

|             | [2]   | AFS2: write '1' to                  | enable AF | S mode 2 (a  | II keys above three                    | shold)         | .15)                 |

|             | [1]   | AFS1: write '1' to                  | enable AF | S mode 1 (o  | ne strongest key o                     | only)          | CL                   |

|             | [0]   | FILTER_EN: write                    |           |              |                                        | - 21           | 70                   |

|             |       |                                     |           |              | AFS3 could be set<br>n would be unpred |                | e time. If more than |

| TVR         |       |                                     |           |              | Touc                                   | h variance     | register [0-11]      |

| 7           | 6     | 5                                   | 4         | 3            | 2                                      | 1              | 0                    |

| -           |       |                                     |           | T            | VR [6:0]                               |                |                      |

| Address:    |       | 0x01 - 0x0C                         |           |              | V-                                     |                |                      |

| Туре:       |       | R/W                                 | ic        |              |                                        |                |                      |

| Reset:      |       | 0x08                                | -112      |              |                                        |                |                      |

| Description | :     | Setting the TVR                     | betweer   | n 0 - 99     |                                        |                |                      |

|             |       | A high TVR valu<br>to ambient noise |           |              | •                                      |                | sing its tolerance   |

|             | × 0   | Each step of TV                     | R is equi | valent to a  | capacitance of 6                       | 0 fF           |                      |

| 10          |       | Recommended                         | value to  | TVR is 4-8.  |                                        |                |                      |

| - GO'       | [7]   | Reserved                            |           |              |                                        |                |                      |

| NO -        | [6:0] | TVR [6:0]                           |           |              |                                        |                |                      |

|             |       |                                     |           |              |                                        |                |                      |

| EVR         |       |                       |                        |                 |                                  | Envi                                | romental va                      | ariance register                               |

|-------------|-------|-----------------------|------------------------|-----------------|----------------------------------|-------------------------------------|----------------------------------|------------------------------------------------|

| 7           | 6     |                       | 5                      | 4               | 3                                | 2                                   | 1                                | 0                                              |

| -           |       |                       |                        |                 | EV                               | r [6:0]                             |                                  |                                                |

| Address:    |       | 0x0D                  |                        |                 |                                  |                                     |                                  |                                                |

| Туре:       |       | R/W                   |                        |                 |                                  |                                     |                                  |                                                |

| Reset:      |       | 0x04                  |                        |                 |                                  |                                     |                                  |                                                |

| Description | :     | capacit               |                        | 60 fF. Red      |                                  |                                     | step of EVR is<br>is 2-6 (EVR mi | s equivalent to a<br>ust always be             |

|             | [7]   | Reserve               | ed                     |                 |                                  |                                     |                                  |                                                |

|             | [6:0] | EVR [6:               | 0]                     |                 |                                  |                                     |                                  | (5)                                            |

| ETC_WAI     | г     |                       |                        |                 | Envir                            | omental tra                         | cking calib                      | ration wait time                               |

| 7           | 6     |                       | 5                      | 4               | 3                                | 2                                   |                                  | 0                                              |

|             |       |                       |                        |                 | ETC_WAIT [7                      | :0]                                 |                                  |                                                |

| Address:    |       | 0x0E                  |                        |                 |                                  | (cit                                | 0                                |                                                |

| Туре:       |       | R/W                   |                        |                 |                                  | colo                                |                                  |                                                |

| Reset:      |       | 0x27                  |                        |                 |                                  | 5                                   |                                  |                                                |

| Description |       | status.               | ETC wait<br>ersist for | t time = E      | TC_wait[7:0                      | 0] *64 *clock p                     |                                  | turning to no-touch<br>buch" condition<br>out. |

| REFEREN     | ICE_I | DELAY                 | 00                     |                 |                                  |                                     | F                                | Reference delay                                |

| 7           | 6     | 61.                   | 5                      | 4               | 3                                | 2                                   | 1                                | 0                                              |

| RESERVED    | ×C    |                       |                        |                 | REFERE                           | ENCE_DELAY                          |                                  |                                                |

| Address:    |       | 0x0F                  |                        |                 |                                  |                                     |                                  |                                                |

| Type:       |       | R/W                   |                        |                 |                                  |                                     |                                  |                                                |

| Reset:      |       | 0x00                  |                        |                 |                                  |                                     |                                  |                                                |

| Description |       |                       | f 60 pF. V             | -               | -                                | e = 0-128. Each<br>d after this val |                                  | nts capacitance                                |

|             | [6:0] | Valid rar<br>Each ste | • •                    | 7<br>ents capac | sitance value<br>r this value is | •                                   |                                  |                                                |

#### STRENGTH\_THRES Strength threshold 6 0 7 5 4 3 2 1 STRENGTH\_THRESHOLD Address: 0x10 - 0x1B R/W Type: **Reset:** 0x01 **Description:** Setting threshold to be used in AFS mode to determin a valid touch. [7:0] Strength\_threshold Integration time register INTEGRATION\_TIME 0 6 2 7 5 4 3 INTEGRATION\_TIME oleteP Address: 0x1C R/W Type: **Reset:** 0x0F **Description:** Integration time in AFS mode. [7:0] Integration\_time: Total period of integration = sensor clock period \* integration time [7:0] IDLE\_TIME Idle time register 6 3 2 1 0 IDLE\_TIME Address: 0x1D R/W Type: 0x0F **Reset: Description:** The device enters in idle state if there is not touch detected for a period equal to idle time [7:0] \* 5000 \* clock\_sensor\_period. [7:0] IDLE\_TIME

| GPIO_ST    | A_L  |              |                |             |                                                     | GPIO st | ate register L |

|------------|------|--------------|----------------|-------------|-----------------------------------------------------|---------|----------------|

| 7          | 6    | 5            | 4              | 3           | 2                                                   | 1       | 0              |

| IO-7       | IO-6 | IO-5         | IO-4           | IO-3        | IO-2                                                | IO-1    | IO-0           |

| Address:   | 0×   | :1E          |                |             |                                                     |         |                |

| Туре:      | R/   | W            |                |             |                                                     |         |                |

| Reset:     | 0×   | :00          |                |             |                                                     |         |                |

| Descriptio | re   | gister), the | oits in this r | egister wou | GPIO_CFG regis<br>Ild determine the<br>GPIOs 0 - 7. |         |                |

| GPIO ST    | АН   |              |                |             |                                                     | GPIO st | ate register H |

| GPIO_STA_    | н       |            |               |             |                                                     | GPIO sta | ite register H |

|--------------|---------|------------|---------------|-------------|-----------------------------------------------------|----------|----------------|

| 7            | 6       | 5          | 4             | 3           | 2                                                   | 1        | C o            |

|              | RESERVE | D          |               | IO-11       | IO-10                                               | IO-9     | IO-8           |

| Address:     | 0x1F    |            |               |             |                                                     | 0100     |                |

| Туре:        | R/W     |            |               |             | ~0                                                  |          |                |

| Reset:       | 0x00    |            |               |             | 1erc                                                |          |                |

| Description: | registe | er), the b | its in this r | egister wou | GPIO_CFG regis<br>Id determine the<br>GPIOs 8 - 11. |          |                |

|              |         |            |               | -           | G                                                   |          | tion register  |

| GPIO_C               | FG_L                                                                            |                         | 15   |      | GPIO configuration registe |                                  |              |  |

|----------------------|---------------------------------------------------------------------------------|-------------------------|------|------|----------------------------|----------------------------------|--------------|--|

| 7                    | 6                                                                               | 5                       | 4    | 3    | 2                          | 1                                | 0            |  |

| IO-7                 | IO-6                                                                            | IO-5                    | 10-4 | IO-3 | IO-2                       | IO-1                             | IO-0         |  |

| Address:             | 0:                                                                              | (20 00)                 |      |      |                            |                                  |              |  |

| _                    |                                                                                 |                         |      |      |                            |                                  |              |  |

| Туре:                | R                                                                               | W                       |      |      |                            |                                  |              |  |

| Type:<br>Reset:      |                                                                                 | (VV<br>(00              |      |      |                            |                                  |              |  |

| Reset:               | 0)<br>0)<br>0)<br>0)                                                            | (00                     |      |      | register sets the          | e corresponding                  | DIO as GPIO. |  |

|                      | 0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0 | k00<br>/riting '1' in t |      |      | -                          | e corresponding<br>PIO configura |              |  |

| Reset:<br>Descriptio | 0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0:<br>0 | k00<br>/riting '1' in t |      |      | -                          |                                  |              |  |

| Address:     | 0.721                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------|

| Туре:        | R/W                                                                                                               |

| Reset:       | 0x00                                                                                                              |

| Description: | Writing '1' in this GPIO configuration register sets the corresponding DIO as GPIO.<br>Applicable for GPIOs 8-11. |

| GPIO_DIR_                                        | L                                                                                                                                                                                                      |                                                                                                                                                                                                                                                               |                                                                                                                               |                                                                                  |                                        | GPIO dire  | ction regist  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|------------|---------------|

| 7                                                | 6                                                                                                                                                                                                      | 5                                                                                                                                                                                                                                                             | 4                                                                                                                             | 3                                                                                | 2                                      | 1          | 0             |

| IO-7                                             | IO-6                                                                                                                                                                                                   | IO-5                                                                                                                                                                                                                                                          | IO-4                                                                                                                          | IO-3                                                                             | IO-2                                   | IO-1       | IO-0          |

| Address:                                         | 0                                                                                                                                                                                                      | x22                                                                                                                                                                                                                                                           |                                                                                                                               |                                                                                  |                                        |            |               |

| Гуре:                                            | F                                                                                                                                                                                                      | /W                                                                                                                                                                                                                                                            |                                                                                                                               |                                                                                  |                                        |            |               |

| Reset:                                           | 0                                                                                                                                                                                                      | x00                                                                                                                                                                                                                                                           |                                                                                                                               |                                                                                  |                                        |            |               |

| Description:                                     |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                               |                                                                                                                               |                                                                                  | rresponding GPIC<br>) as output. Appli |            |               |

| GPIO_DIR_                                        | H                                                                                                                                                                                                      |                                                                                                                                                                                                                                                               |                                                                                                                               |                                                                                  |                                        | GPIO dire  | ction regist  |

| 7                                                | 6                                                                                                                                                                                                      | 5                                                                                                                                                                                                                                                             | 4                                                                                                                             | 3                                                                                | 2                                      | 1          | S             |

|                                                  | RE                                                                                                                                                                                                     | SERVED                                                                                                                                                                                                                                                        |                                                                                                                               | IO-11                                                                            | IO-10                                  | IO-9       | IO-8          |

| Address:                                         | 0                                                                                                                                                                                                      | x23                                                                                                                                                                                                                                                           |                                                                                                                               |                                                                                  |                                        | 0          | <b>.</b>      |

| Гуре:                                            | F                                                                                                                                                                                                      | /W                                                                                                                                                                                                                                                            |                                                                                                                               |                                                                                  |                                        | 010        |               |

| Reset:                                           | 0                                                                                                                                                                                                      | x00                                                                                                                                                                                                                                                           |                                                                                                                               |                                                                                  | × C,                                   |            |               |

| Description:                                     |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                               |                                                                                                                               |                                                                                  | responding GPIC<br>as output. Appli    |            |               |

|                                                  |                                                                                                                                                                                                        | U                                                                                                                                                                                                                                                             | •                                                                                                                             | •                                                                                |                                        |            |               |

| CTRL_1                                           |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                               |                                                                                                                               | OX                                                                               | ) _                                    | Con        | trol registe  |

| CTRL_1                                           | 6                                                                                                                                                                                                      | 5                                                                                                                                                                                                                                                             | 4                                                                                                                             | 3                                                                                | 2                                      | Con        | trol registe  |

|                                                  | 6<br>F2A                                                                                                                                                                                               |                                                                                                                                                                                                                                                               | 4                                                                                                                             | 3<br>NDIV                                                                        | 2<br>HDC_U                             |            | trol register |