# STPMS1

# Dual-channel 1-bit, 2 MHz, 1<sup>st</sup> order sigma-delta modulator with embedded PGA

#### **Features**

- V<sub>CC</sub> supply range: 3.2 V 5.5 V

- Two 1<sup>st</sup> order sigma-delta modulators

- Programmable chopper-stabilized low noise and low offset amplifier

- Supports 50-60 Hz AC watt meters

- Internal low-drop regulator at 3 V (typ.)

- Precision voltage reference: 1.23 V and 30 ppm/°C (typ.)

### **Applications**

- Power metering

- Motor control

- Industrial process control

- Weight scale

- Pressure transducers

### **Description**

The STPMS1, also called a smart-sensor device, is an ASSP designed for effective measurement in power line systems utilizing the Rogowski coil, current transformer, or shunt principle. It is used in combination with the STPMC1 programmable poly-phase energy calculator IC, as a building block for single-phase or poly-phase energy meters. The STPMS1 is a mixed signal IC consisting of an analog and a digital section. The analog section consists of a pre-amplifier and two  $1^{\rm st}$  order  $\Sigma\Delta$  modulator blocks, band-gap voltage reference, a low-drop voltage regulator, and DC buffers, while the digital section consists of a clock generator and output multiplexer. This device is designed for use in medium resolution

Table 1. Device summary

| Order code | Package          | Packaging           |

|------------|------------------|---------------------|

| STPMS1BPQR | QFN16 (3 x 3 mm) | 2500 parts per reel |

measurement applications when single or double inputs must be monitored at the same time.

Contents STPMS1

# **Contents**

| 1  | Sche  | ematic diagram                             | 3 |

|----|-------|--------------------------------------------|---|

| 2  | Pin o | configuration                              | 4 |

| 3  | Elec  | trical characteristics                     | 5 |

| 4  | Gen   | eral operating conditions                  | 6 |

| 5  | App   | lication                                   | 9 |

| 6  | Term  | ninology                                   | 2 |

|    | 6.1   | Conventions                                | 2 |

|    | 6.2   | Notation 1                                 | 2 |

| 7  | Турі  | cal performance characteristics            | 3 |

| 8  | The   | ory of operation1                          | 5 |

|    | 8.1   | General operation description 1            | 5 |

|    | 8.2   | Function description of the analog part 1  | 5 |

|    | 8.3   | Functional description of the digital part | 7 |

| 9  | Pack  | age mechanical data1                       | 8 |

| 10 | Povi  | eion history                               | 2 |

STPMS1 Schematic diagram

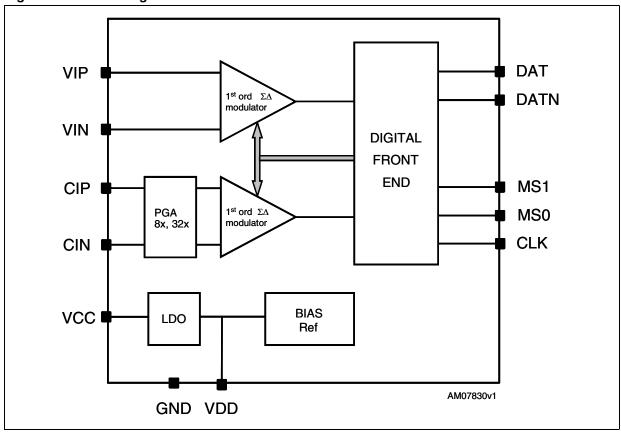

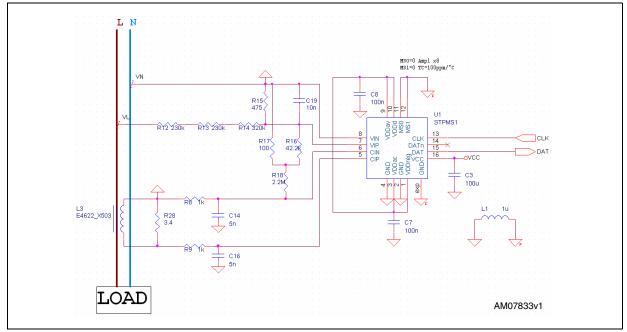

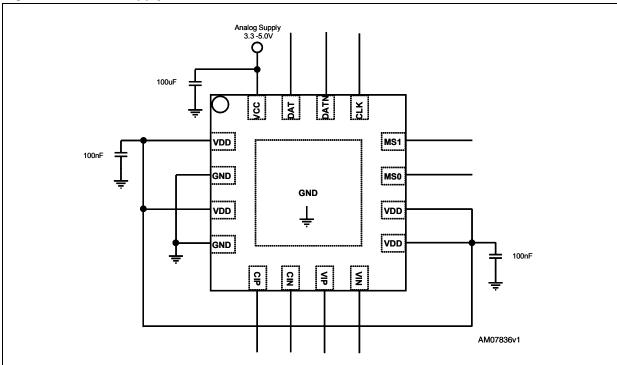

# 1 Schematic diagram

Figure 1. Block diagram

Pin configuration STPMS1

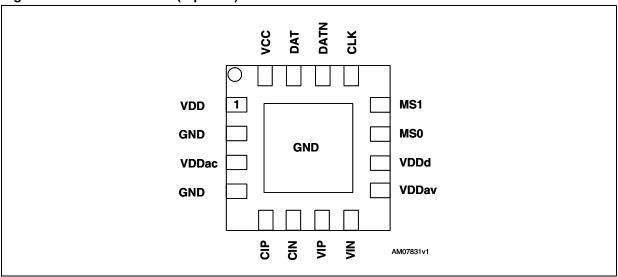

# 2 Pin configuration

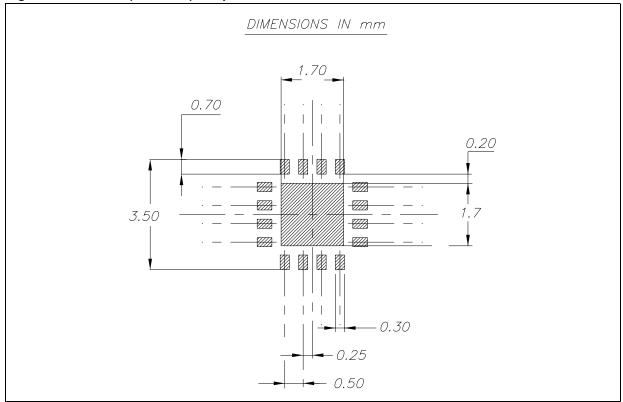

Figure 2. Pin connection (top view)

Table 2. Pin description

| Table 2. Pin description |                                                                                              |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| Symbol                   | Description                                                                                  |  |  |  |

| VDD                      | + 3.0 V output of LDO                                                                        |  |  |  |

| GND                      | Ground level for signals and pin protection                                                  |  |  |  |

| VDDac                    | Current channel modulator supply input                                                       |  |  |  |

| GND                      | Ground level for signals and pin protection                                                  |  |  |  |

| CIP                      | Current channel +                                                                            |  |  |  |

| CIN                      | Current channel -                                                                            |  |  |  |

| VIP                      | Voltage channel +                                                                            |  |  |  |

| VIN                      | Voltage channel -                                                                            |  |  |  |

| VDDav                    | Voltage channel modulator supply input                                                       |  |  |  |

| VDDd                     | Digital front-end supply input                                                               |  |  |  |

| MS0                      | Input for configurator 0                                                                     |  |  |  |

| MS1                      | Input for configurator 1                                                                     |  |  |  |

| CLK                      | Input for external measurement clock                                                         |  |  |  |

| DAT                      | Output of multiplexed $\Sigma\Delta$ signal                                                  |  |  |  |

| DATn                     | Output of multiplexed $\Sigma\Delta$ signal negated                                          |  |  |  |

| VCC                      | Unregulated supply voltage                                                                   |  |  |  |

| GND                      | Ground level for signals and pin protection                                                  |  |  |  |

|                          | Symbol  VDD  GND  VDDac  GND  CIP  CIN  VIP  VIN  VDDav  VDDa  MS0  MS1  CLK  DAT  DATn  VCC |  |  |  |

# 3 Electrical characteristics

Table 3. Absolute maximum ratings

| Symbol           | Parameter                                                | Value                        | Unit |

|------------------|----------------------------------------------------------|------------------------------|------|

| VCC              | DC input voltage                                         | -0.3 to 6                    | V    |

| I <sub>PIN</sub> | Current on any pin (sink/source)                         | ±150                         | mA   |

| V <sub>ID</sub>  | Input voltage at digital pins (MS0, MS1, CLK, DAT, DATN) | -0.3 to V <sub>CC</sub> +0.3 | V    |

| V <sub>IA</sub>  | Input voltage at analog pins (VIP, VIN, CIP, CIN)        | -0.7 to 0.7                  | V    |

| ESD              | Human body model (all pins)                              | ±3.5                         | kV   |

| T <sub>OP</sub>  | Operating ambient temperature                            | -40 to 85                    | °C   |

| T <sub>J</sub>   | Junction temperature                                     | -40 to 150                   | °C   |

| T <sub>STG</sub> | Storage temperature range                                | -55 to 150                   | °C   |

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 4. Thermal data

| Symbol     | Parameter                           | Value                | Unit |

|------------|-------------------------------------|----------------------|------|

| $R_{thJA}$ | Thermal resistance junction-ambient | 38.10 <sup>(1)</sup> | °C/W |

<sup>1.</sup> This value refers to a single-layer PCB, JEDEC standard test board.

# 4 General operating conditions

$V_{CC}$  = 5 V,  $T_A$  = 25 °C, 2.2  $\mu F$  between  $V_{DD}$  and GND, 100 nF between  $V_{CC}$  and GND,  $f_{CLK}$  = 2.048 MHz unless otherwise specified.

Table 5. General operating conditions

| Symbol             | Parameter                                    | Test conditions                                              |       | Тур.  | Max.  | Unit  |  |

|--------------------|----------------------------------------------|--------------------------------------------------------------|-------|-------|-------|-------|--|

| General            | section                                      |                                                              |       |       |       |       |  |

| V <sub>CC</sub>    | Operating supply voltage                     |                                                              | 3.165 |       | 5.5   | V     |  |

| Icc                | Quiescent current                            | 1.049 MHz; $V_{CC}$ =3.165 V; $C_L$ =100 nF, no loads        |       | 2.5   |       | mA    |  |

| V <sub>POR</sub>   | Power on reset on V <sub>CC</sub>            |                                                              |       | 2.5   |       | V     |  |

| $V_{DD}$           | Regulated supply voltage                     | 1.049 MHz; $V_{CC}$ =3.2 V; $C_L$ =100 nF, no loads          | 2.85  | 3.00  | 3.15  | V     |  |

| I <sub>LATCH</sub> | Current injection latch-up immunity          |                                                              |       |       | 300   | mA    |  |

| f <sub>CLK</sub>   | Nominal frequencies                          |                                                              | 1.0   |       | 2.458 | MHz   |  |

| DC meas            | urement accuracy                             |                                                              |       |       |       |       |  |

|                    | Resolution                                   |                                                              | 11    |       | 16    | bit   |  |

| INII               | Integral per linearity                       | Result referred to a 13-bit resolution of CIP-CIN channel    |       | 0.35  |       | LCD   |  |

| INL                | Integral non-linearity                       | Result referred to a 9-bit resolution of VIP-VIN channel     |       | 0.5   |       | - LSB |  |

| DNII               | Differential linearity                       | Result referred to a 13-bit resolution of CIP-CIN channel    |       | 0.2   |       | LCD   |  |

| DNL                | Differential linearity                       | Result referred to a 9-bit resolution of VIP-VIN channel     |       | 0.4   |       | LSB   |  |

|                    | Officet arrow                                | Result referred to a 13-bit resolution of CIP-CIN channel    |       | 0.15  |       | LCD   |  |

|                    | Offset error                                 | Result referred to a 9-bit resolution of VIP-VIN channel     |       | 0.05  |       | LSB   |  |

|                    | Coin away                                    | Result referred to a 13-bit resolution of CIP-CIN channel    |       | 0.05  |       | LSB/  |  |

|                    | Gain error                                   | Result referred to a 9-bit resolution of VIP-<br>VIN channel |       | 0.001 |       | μV    |  |

| NF                 | Noise floor                                  | CIP-CIN channel, Gain 8x                                     |       | 115   |       | dB    |  |

| PSRR <sub>DC</sub> | Voltage signal: 200 mV <sub>rms</sub> /50 Hz |                                                              |       | 0.2   | %     |       |  |

Table 5. General operating conditions (continued)

| Symbol             | Parameter                       | Test conditions                                                                                                                                                                                                                               | Min.                    | Тур.                | Max.            | Unit |

|--------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------|-----------------|------|

| AC meas            | urement accuracy                |                                                                                                                                                                                                                                               |                         |                     |                 |      |

| SNR                | Signal to noise ratio           | CIP-CIN channel – Vin=±120 mV @ 55 Hz<br>Gain 8x                                                                                                                                                                                              |                         | 65                  |                 | dB   |

|                    |                                 | VIP-VIN channel – Vin=±230 mV @ 55 Hz                                                                                                                                                                                                         |                         | 50                  |                 |      |

| SINAD              | Signal to noise ratio +         | CIP-CIN channel – Vin=±120 mV @ 55 Hz<br>Gain 8x                                                                                                                                                                                              |                         | 65                  |                 | dB   |

|                    | distortion                      | VIP-VIN channel – Vin=±230 mV @ 55 Hz                                                                                                                                                                                                         |                         | 50                  |                 |      |

| THD                | Total harmonic distortion       | CIP-CIN channel – Vin=±120 mV @ 55 Hz<br>Gain 8x                                                                                                                                                                                              |                         | -80                 |                 | dB   |

|                    |                                 | VIP-VIN channel – Vin=±230 mV @ 55 Hz                                                                                                                                                                                                         |                         | -70                 |                 |      |

| SFDR               | Spurious free dynamic           | CIP-CIN channel – Vin=±120 mV @ 55 Hz<br>Gain 8x                                                                                                                                                                                              |                         | 80                  |                 | dB   |

|                    | range                           | VIP-VIN channel – Vin=±230 mV @ 55 Hz                                                                                                                                                                                                         |                         | 50                  |                 |      |

| PSRR <sub>AC</sub> | Power supply AC rejection       | Voltage signal: 200 mV <sub>rms</sub> /50 Hz<br>Current signal: 10 mV <sub>rms</sub> /50 Hz<br>f <sub>CLK</sub> = 2.048 MHz<br>V <sub>CC</sub> =3.3 V+0.2 V <sub>rms</sub> 1 @100 Hz<br>V <sub>CC</sub> =5.0 V+0.2 V <sub>rms</sub> 1 @100 Hz |                         |                     | 0.1             | %    |

| Analog ir          | nputs (CIP, CIN, VIP, VIN)      |                                                                                                                                                                                                                                               | 1                       | •                   | •               |      |

|                    |                                 | VIP-VIN channel                                                                                                                                                                                                                               | -0.3                    |                     | +0.3            | V    |

| $V_{MAX}$          | Maximum input signal levels     | CIP-CIN channel<br>Gain 8X<br>Gain 32X                                                                                                                                                                                                        | -0.15<br>-0.035         |                     | +0.15<br>+0.035 | V    |

| f <sub>SPL</sub>   | A/D sampling frequency          |                                                                                                                                                                                                                                               |                         | f <sub>CLK</sub> /2 |                 | Hz   |

| V <sub>off</sub>   | Amplifier offset                |                                                                                                                                                                                                                                               |                         |                     | ±20             | mV   |

| Z <sub>IP</sub>    | VIP, VIN impedance              | Over the total operating voltage range                                                                                                                                                                                                        | 200                     |                     | 400             | kΩ   |

| Z <sub>IN</sub>    | CIP, CIN impedance              | Over the total operating voltage range                                                                                                                                                                                                        |                         | 240                 |                 | kΩ   |

| G <sub>ERR</sub>   | Current channel gain error      |                                                                                                                                                                                                                                               |                         | ±10                 |                 | %    |

| I <sub>ILV</sub>   | Voltage channel leakage current | V <sub>CC</sub> = 5.3 V, f <sub>CLK</sub> = 1.049 MHz                                                                                                                                                                                         | -1                      |                     | 1               |      |

|                    | Current channel leakage         |                                                                                                                                                                                                                                               | -1                      |                     | 1               | μΑ   |

| I <sub>ILI</sub>   | current                         | Input enabled                                                                                                                                                                                                                                 | -10                     |                     | 10              |      |

| Digital I/0        | O (CLK, DAT, DATn, MS0,         | MS1)                                                                                                                                                                                                                                          |                         |                     |                 |      |

| V <sub>IH</sub>    | Input high voltage              |                                                                                                                                                                                                                                               | 0.75<br>V <sub>CC</sub> |                     | 5.3             | ٧    |

| V <sub>IL</sub>    | Input low voltage               |                                                                                                                                                                                                                                               | -0.3                    |                     | 0.25V<br>CC     | ٧    |

Table 5.

General operating conditions (continued)

| Symbol           | Parameter               | Test conditions                                                      | Min.                     | Тур. | Max.  | Unit       |

|------------------|-------------------------|----------------------------------------------------------------------|--------------------------|------|-------|------------|

| V <sub>OH</sub>  | Output high voltage     | I <sub>O</sub> =-1 mA, C <sub>L</sub> =50 pF, V <sub>CC</sub> =3.2 V | V <sub>CC</sub> -<br>0.4 |      |       | V          |

| V <sub>OL</sub>  | Output low voltage      | I <sub>O</sub> =+1 mA, C <sub>L</sub> =50 pF, V <sub>CC</sub> =3.2 V |                          |      | 0.4   | V          |

| I <sub>UP</sub>  | Pull up current         |                                                                      |                          | 15   |       | μΑ         |

| t <sub>TR</sub>  | Transition time         | C <sub>LOAD</sub> =50 pF                                             |                          | 10   |       | ns         |

| t <sub>L</sub>   | Latency                 | From 50 % of CLK to 50 % to DAT                                      |                          | 40   |       | ns         |

| Clock inp        | out                     |                                                                      |                          |      |       |            |

| f.               | Nominal frequencies     | Low precision                                                        | 1.0                      |      | 1.228 | MHz        |

| f <sub>CLK</sub> | Nominal frequencies     | High precision                                                       | 2.0                      |      | 2.458 | MHz        |

| On chip r        | eference voltage        |                                                                      |                          |      |       |            |

| V <sub>REF</sub> | Reference voltage       |                                                                      | 1.21                     | 1.23 | 1.25  | V          |

| T <sub>C</sub>   | Temperature coefficient | After calibration                                                    |                          | 30   | 50    | ppm/<br>°C |

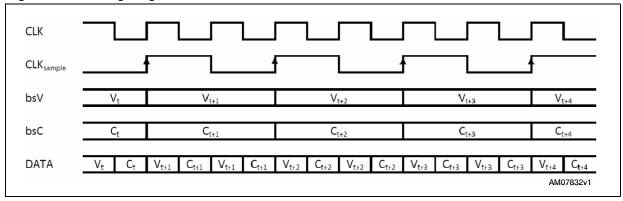

Figure 3. Timing diagram

CLK - clock signal on CLK pin

$\mathsf{CLK}_\mathsf{sample}$  - sigma-delta sample frequency

bsV - sigma-delta bitstream of voltage signal

bsC - sigma-delta bitstream of current signal

DATA - multiplexed data of voltage and current signal on DAT pin

STPMS1 Application

### 5 Application

The choice of external components in the transduction section of the application is a crucial point in the application design, affecting the precision and the resolution of the whole system.

Among the several considerations, a compromise must be found between the following needs:

- 1. Maximize the signal to noise ratio in the voltage and current channel

- 2. Choose the current to voltage conversion ratio Ks and the voltage divider ratio in a way that calibration can be achieved (see also the AN2299; *Fast digital calibration procedure for STPM01 based energy meters*, application note)

- 3. Choose Ks to take advantage of the whole current dynamic range according to desired maximum current and resolution.

To maximize the signal to noise ratio of the current channel the voltage divider resistors ratio should be as close as possible to that shown in *Table 6*.

Figure 4 below shows a reference schematic for an application with the following properties:

- P = 64000 imp/kWh

- INOM = 5 A

- IMAX = 60 A

Typical values for the current sensors sensitivity are indicated in *Table 6*.

Application STPMS1

Table 6. Suggested external components in metering applications

| Function               | Component     | Description                             | Value  | Tole | erance    | Unit |

|------------------------|---------------|-----------------------------------------|--------|------|-----------|------|

| Calculator             |               | STPMC1                                  |        |      |           |      |

| Line voltage           | Resistor      | R to R ratio V <sub>RMS</sub> =230 V    | 1:1650 | ±1 % | 50 ppm/°C | V/V  |

| interface              | divider       | R to R ratio V <sub>RMS</sub> =110 V    | 1:830  |      |           |      |

|                        | Rogowski coil | Current to voltage ratio K <sub>S</sub> | 0.15   | ±5 % | 50 ppm/°C | mV/A |

| Line current interface | СТ            |                                         | 1.7    | ±5 % |           |      |

|                        | Shunt         |                                         | 0.43   | ±5 % |           |      |

Note: The above listed components refer to typical metering applications. However, STPMS1 operation is not limited to the choice of these external components.

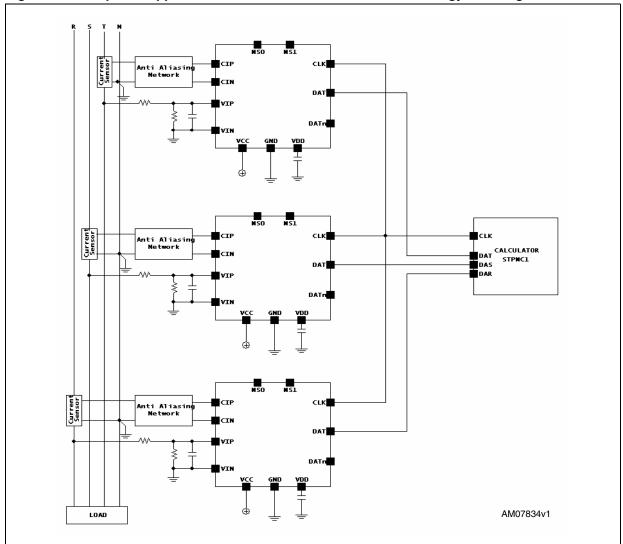

Figure 5. Simplified application schematics for STPMC1 based energy metering

STPMS1 Application

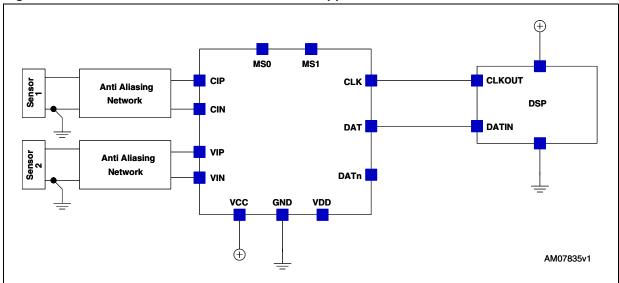

Figure 6. Connection schematic for DSP based applications

Terminology STPMS1

# 6 Terminology

#### 6.1 Conventions

The lowest analog and digital power supply voltage is named GND which represents the system Ground. All voltage specifications for digital input/output pins are referred to GND.

Positive currents flow into a pin. Sinking current means that the current is flowing into the pin and then it is positive. Sourcing current means that the current is flowing out of the pin and then it is negative.

Timing specifications of a signal treated by a digital control part are relative to CLK. This signal is provided from the STPMC1 calculator IC of 1.024 MHz or of 2.048 MHz nominal frequency.

A positive logic convention is used in all equations.

#### 6.2 Notation

Current and voltage signals are represented as u and i.

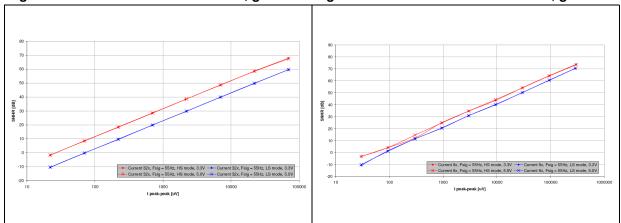

# 7 Typical performance characteristics

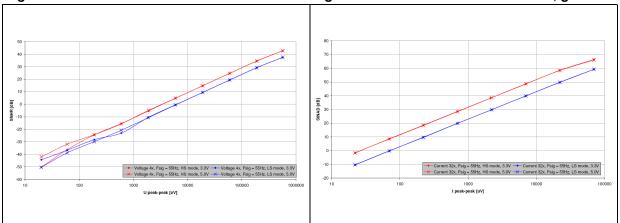

Figure 7. SNRH of CIP-CIN channel, gain 32x Figure 8. SNHR of CIP-CIN channel, gain 8x

Figure 9. SNHR of VIP-VIN channel

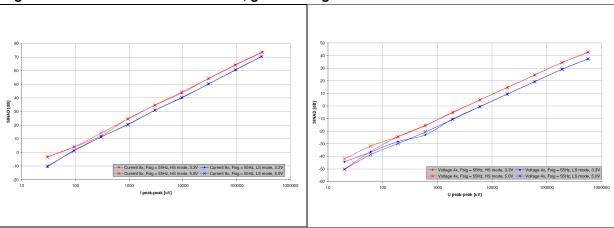

Figure 10. SINAD of CIP-CIN channel, gain 32x

Figure 11. SINAD of CIP-CIN channel, gain 8x Figure 12. SINAD of VIP-VIN channel

577

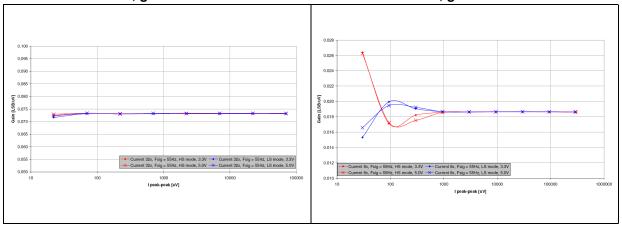

Figure 13. Relative gain error of CIP-CIN channel, gain 32x

Figure 14. Relative gain error of CIP-CIN channel, gain 8x

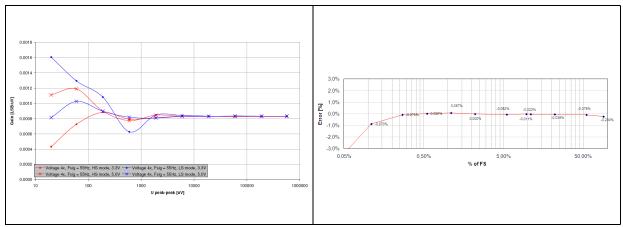

Figure 15. Relative gain error of VIP-VIN channel

Figure 16. Accuracy over dynamic range

14/23 Doc ID 16524 Rev 2

STPMS1 Theory of operation

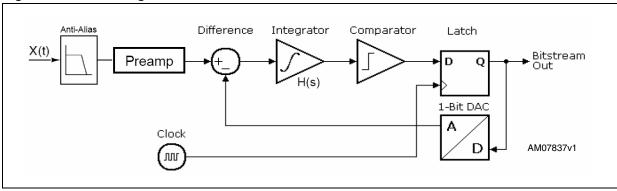

### 8 Theory of operation

#### 8.1 General operation description

The STPMS1 performs first-order analog modulation of signals which have frequencies varying from DC to 2 kHz on two independent channels in parallel. There is a current channel for measuring line current and a voltage channel for measuring line voltage. The outputs of the converters provide two streams of digital ones and zeros which are therefore multiplexed in time to reduce the number of external connections.

The sampling and the data multiplexing are driven by an external clock signal, as it is used to strobe the analog inputs. The combination of one or more STPMS1s and an STPMC1 (which implements the digital filtering) constitutes a conversion system for energy metering applications.

The STPMS1 can also be used along with a DSP programmed to demultiplex the output bitstream and to implement the digital filtering as a medium resolution ADC system.

When used in energy metering applications, the voltage channel is connected externally and differentially to a line voltage divider which provides an analog signal proportional to the voltage u. The current channel is connected to a Rogowski coil, or to a current transformer (CT) or a shunt, which are used to interface the line current. The Rogowski coil provides an analog signal proportional to di/dt, while the shunt or CT provides an analog signal proportional to the current i. A CT differs from a shunt in sensitivity and phase error. There should be an anti-aliasing LP filter inserted between the sensors and the inputs of both channels of the STPMS1.

Internally, the differential voltage input related to the voltage channel is connected directly to the A/D converter, which implies an amplification of x4. On the other side, the differential voltage input related to the current channel is connected first to a configurable x2 or x8 preamplifier and the output of this pre-amplifier to the similar A/D converter (x4 gain), which implies selectable pre-amplification of x8 or x32 and uses the same reference voltage.

A pair of digital inputs (MS0 and MS1) is used to configure the device.

### 8.2 Function description of the analog part

The supply pins for the analog part are  $V_{CC}$ ,  $V_{DD}$ ,  $V_{DDac}$ ,  $V_{DDav}$ ,  $V_{DDd}$ , and GND.

The GND pin also represents a reference point. The  $V_{DD}$  is an analog I/O pin of an internal +3.0 V low-drop voltage regulator, the  $V_{DDac}$  and  $V_{CCav}$  are the modulators supply inputs, while the  $V_{DDd}$  is the digital front-end supply input. A 100 nF capacitor should be connected between  $V_{DDxx}$  and GND. The input of the mentioned regulator is  $V_{CC}$  which powers also a band-gap, and bias generators.

The analog part consists of several modules:

- Band-gap reference and bias generators

- +3 V low-drop regulator

- two DC buffer amplifiers

- two ΣΔ AD converters

- control signal module

Theory of operation STPMS1

The band-gap voltage reference is used as the reference level source for the low-drop module and for the AD converters. This module produces several bias currents and voltages for all other analog modules.

The low-drop regulator generates the +3.0 V power supply level. This level is used to power the DC buffers, pre-amplifier, and AD converter pair in the analog part of the device and whole digital part. It is brought out as  $V_{DD}$  for external connections. As part of low-drop, there is a power on reset (POR) detection circuit, which blocks all functions of the STPMS1 by asserting the reset condition whenever a  $V_{CC}$  supply level is less than +2.5 V.

Figure 17. Power supply external connection scheme

In order to enable proper operation of the switched capacitor (SC) section of AD converters, two DC buffers are added to the device. One is buffering the voltage reference level and the other is buffering the level of value equal to (VDD-VSS)/2.

The AD converter block is further split into a voltage and current channel. Each channel consists of a differential pre-amplifier, SC integrator, comparator, amplifier bias block, and all necessary switches. The voltage channel SC integrator has a gain of 2 and there is no pre-amplifier block. The current channel SC integrator has a gain of 2 or 8, which can be selected by MS0 input, and has a pre-amplifier with a gain of 4.

The amplitude of the input signal to the AD converter block must be kept less than 0.45  $V_{\text{ref}}$

The output of each channel is input to the digital module as  $\Sigma\Delta$  stream.

For the operation of the analog part, a set of five clock signals is provided from the digital module. These signals derive from the CLK signal. Two of them are used to run the conversion, the next one is used as the chopper signal for the voltage channel and the last two are used as chopper signals for the current channel. All these signals are connected to the control signal module, which consists of standard digital cells powered from an analog supply. It produces all the necessary signals and switch controls of the AD converters.

STPMS1 Theory of operation

Figure 18. Block diagram of the modulator

### 8.3 Functional description of the digital part

A digital part is made up of:

- clock generator

- mode decoder

- time multiplex

The clock generator produces all five clocks for the analog module.

The mode decoder generates signals for controlling the temperature coefficient of the onchip band-gap voltage reference and the amplification factor of the current channel, clock prescaler, and voltage channel enable.

Table 7. Modes of operation

| MS0 | Mode | Description |

|-----|------|-------------|

| 0   | 0    | ampl = 8    |

| 1   | 1    | ampl = 32   |

Table 8. Changing of band-gap voltage reference

| MS1  | Mode | Description     |  |

|------|------|-----------------|--|

| 0    | 0    | TC = 100 ppm/°C |  |

| CLK  | 1    | TC = 170 ppm/°C |  |

| NCLK | 2    | TC = 125 ppm/°C |  |

| 1    | 3    | TC = 190 ppm/°C |  |

The multiplex combines both  $\Sigma\Delta$  input signals for the analog module into one signal DAT which drives differential outputs DAT and DATn according to:

DAT= if CLK then bsV or else bsC

DATN = NOT(DAT).

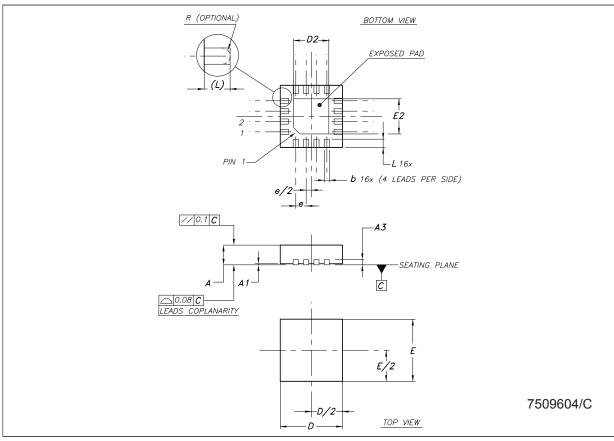

# 9 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at <a href="www.st.com">www.st.com</a>. ECOPACK is an ST registered trademark.

18/23 Doc ID 16524 Rev 2

# QFN16 (3 x 3 mm.) mechanical data

| Dim.   | mm.  |      |      | inch. |       |       |

|--------|------|------|------|-------|-------|-------|

| Dilli. | Min. | Тур. | Max. | Min.  | Тур.  | Max.  |

| А      | 0.80 | 0.90 | 1.00 | 0.031 | 0.035 | 0.039 |

| A1     | 0    |      | 0.05 |       |       | 0.002 |

| А3     |      | 0.20 |      |       | 0.008 |       |

| b      | 0.18 |      | 0.30 | 0.007 |       | 0.012 |

| D      | 2.90 | 3.00 | 3.10 | 0.114 | 0.118 | 0.122 |

| D2     | 1.50 |      | 1.80 | 0.059 |       | 0.071 |

| E      |      | 3.00 |      |       | 0.118 |       |

| E2     | 2.90 | 3.00 | 3.10 | 0.114 | 0.118 | 0.122 |

| е      |      | 0.50 |      |       | 0.020 |       |

| L      | 0.30 |      | 0.50 | 0.012 |       | 0.020 |

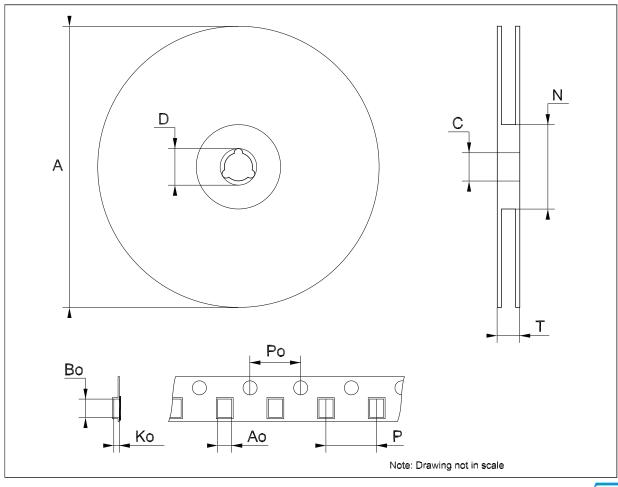

# Tape & reel QFNxx/DFNxx (3 x 3 mm.) mechanical data

| Dim. | mm.  |      |      | inch. |       |       |

|------|------|------|------|-------|-------|-------|

|      | Min. | Тур. | Max. | Min.  | Тур.  | Max.  |

| Α    |      |      | 180  |       |       | 7.087 |

| С    | 12.8 |      | 13.2 | 0.504 |       | 0.519 |

| D    | 20.2 |      |      | 0.795 |       |       |

| N    | 60   |      |      | 2.362 |       |       |

| Т    |      |      | 14.4 |       |       | 0.567 |

| Ao   |      | 3.3  |      |       | 0.130 |       |

| Во   |      | 3.3  |      |       | 0.130 |       |

| Ko   |      | 1.1  |      |       | 0.043 |       |

| Ро   |      | 4    |      |       | 0.157 |       |

| Р    |      | 8    |      |       | 0.315 |       |

Figure 19. QFN16 (3 x 3 mm) footprint recommended data

Revision history STPMS1

# 10 Revision history

Table 9. Document revision history

| Date        | Revision | Changes                                        |  |

|-------------|----------|------------------------------------------------|--|

| 23-Oct-2009 | 1        | Initial release.                               |  |

| 07-Oct-2010 | 2        | Data brief header removed from the cover page. |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Current & Power Monitors & Regulators category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

NCP347MTAHTBG NCS37000MNG NCP4353BSNT1G MAX4845DEYT+T ZXCT1080QE5TA NCP4353ASNT1G UC3838ADW

NCP361SNT1G ZXCT1023DFGTA ADM1294-1AARUZ-RL7 LT3092ETS8#TRPBF LTC4151IMS-1#PBF LM334S8#PBF INA203AIDR

ADM1294-1AACPZ ADM1294-1BACPZ ADL5315ACPZ-R7 ADL5317ACPZ-REEL7 ADM1041ARQZ ADM1192-1ARMZ-R7

ADM1293-1BARUZ ADM1294-1AARUZ LT3092EST#TRPBF LTC1921CMS8#PBF LTC1921IS8#PBF LTC1392CS8#PBF

LTC1921CS8#PBF LTC2921CGN#PBF LTC2947IUHF-65#PBF ZXCT1009FTA DM7332G-00364-B1 CS5460A-BSZ CS5463-ISZR

ZXCT1107QSA-7 AP4341SNTR-G1 LT2940IDD#PBF ZXCT1110W5-7 ZXCT1083E5TA ZXCT1021E5TA ZXCT1022E5TA

ZXCT1041E5TA ZXCT1051E5TA ZXCT1080E5TA ZXCT1107SA-7 INA285AQDGKRQ1 INA286AQDGKRQ1 IR3725MTRPBF

ISL28023FR12Z-T7A ISL28025FI12Z-T7A IXCY10M45S