## Qi-compliant dual mode wireless power receiver for up to 15W applications

# Features

- Up to 15 W output power

- Up to 5W output power in Tx mode

- Qi 1.3 inductive wireless standard communication protocol compliant

- High efficiency (98% typical) synchronous rectifier operating up to 800 kHz

- Low drop-out linear regulator with output current limit and input voltage control loop

- Adaptive Rectifier Configuration (ARC) Mode for enhanced spatial freedom

- 4 V to 12 V programmable output voltage

- Above 85% overall system efficiency

- 32-bit, 64 MHz ARM Cortex M0+ core with 32kB RRAM,16 kB SRAM,64kB ROM

- 10-bit A/D Converter

- · Configurable GPIOs

- I2C Slave interface

- Multi-level ASK modulator. Enhanced FSK demodulator.

- Output Over-Voltage clamping protection

- Accurate voltage/current measurement for Foreign Object Detection (FOD)

- · On-chip thermal management and protections

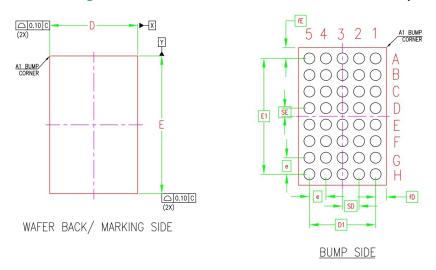

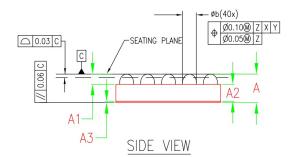

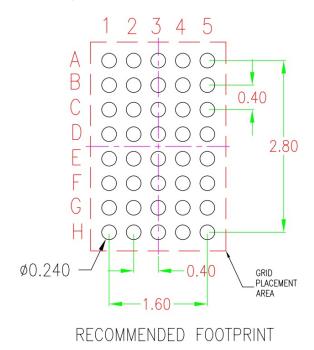

- Flip chip 40 bumps (2.12mm x 3.32mm)

#### Product status link

STWLC38

| Product summary |               |  |  |  |  |

|-----------------|---------------|--|--|--|--|

| Order code      | STWLC38JRM    |  |  |  |  |

| Package         | WLCSP40       |  |  |  |  |

| Packing         | Tape and Reel |  |  |  |  |

## **Applications**

- Smartphones

- Wearable/Hearables TWS

- Asset tracking devices

- · Medical and healthcare equipment

#### **Description**

The STWLC38 is an integrated Wireless Power Receiver suitable for wearable/ hearable and smart phone applications and can supply up to 15 W of output power. The chip has been designed to support Qi 1.3 specifications for inductive communication protocol, 5W Baseline Power Profile and 15W Extended Power Profile.

STWLC38 shows excellent efficiency performance thanks to the integrated low-loss synchronous rectifier and the low drop-out linear regulator: both elements are dynamically managed by the digital core to minimize the overall power dissipation over a wide range of output load conditions.

Through the  $I^2C$  interface the user can access and modify different configuration parameters, tailoring the operation of the device to the needs of custom applications. The configuration parameters can be saved in the embedded Resistive RAM (RRAM) and automatically retrieved at power-up.

STWLC38 is also capable of operating in Tx mode to transmit power to charge other devices. The device can provide power up to 5W Output power in this mode.

The STWLC38 is housed in a Chip-Scale Package to fit real-estate sensitive solutions in wearable devices.

#### 1 Introduction

STWLC38 is a Wireless Power Receiver that rectifies the AC voltage developed across the receiving coil and provides a regulated DC voltage at the output.

The 32-bit core MCU is the supervisor of the whole device and manages all the functional blocks to

- establish and maintain communication with the transmitter,

- ensure adherence to Qi standard specifications (wherever required).

- optimize the efficiency by properly adjusting the operating point

- guarantee reliability by monitoring and protecting both the load and the device itself.

In order to execute the above mentioned (and many others) tasks, the MCU core relies on a resident firmware stored in ROM. In addition, some configuration parameters (e.g. output voltage, FOD tuning parameters, etc.) can be saved in the internal few times programmable Resistive RAM (RRAM) and retrieved at power-up, allowing the STWLC38 to operate as a fully autonomous stand-alone chip.

For applications in which the host system directly monitors or controls the power transfer, the I2C interface provides access to the internal registers of the STWLC38.

The device is also equipped with three programmable general-purpose I/O pins (GPIOs) to implement specific functions (e.g. driving status LEDs, enabling the output on request, informing the host system about faulty conditions, etc.).

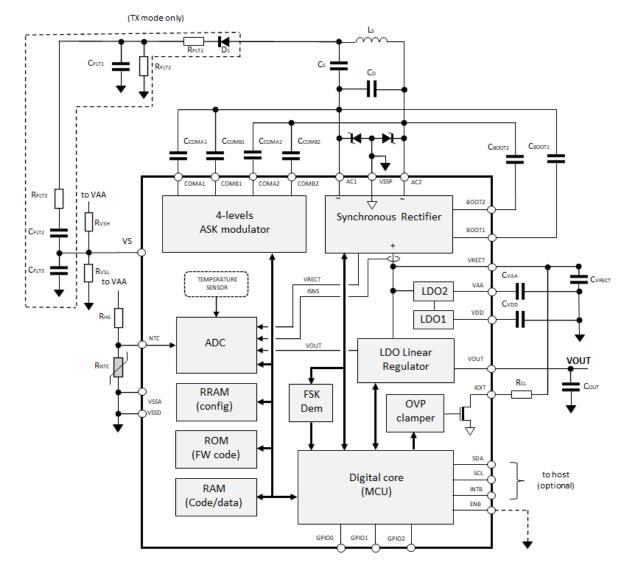

Figure below shows the block diagram of the device with simplified interconnections among the functional blocks. The synchronous rectifier converts the AC voltage from the receiving coil into a DC voltage at the VRECT pin. The four switches of the rectifier (that is basically an H-bridge) are controlled by the digital core in order to minimize both conduction and switching losses as a function of the output voltage and current, both monitored by two channels of the ADC. Two bootstrap capacitors are externally connected to the BOOT1-BOOT2 pins to correctly drive the high-side switches of the rectifier.

The output of the rectifier, filtered by an external capacitor, is also the input rail for the main LDO linear regulator and for the auxiliary linear regulators in charge of deriving the 1.1 V and 2.5 V supply voltages.

The digital core has full control of the main LDO linear regulator in order to manage the output voltage, the output current and the drop-out voltage.

Of course the minimization of the drop-out voltage requires a closed loop regulation of the voltage at the VRECT pin, i.e. a feedback information that is sent to the transmitter (via ASK modulation) which, in turn, adjusts the delivered power by acting on the supply voltage, the switching frequency or the switching duty-cycle (or a combination of the three) of its own power stage, depending on the adopted technique.

This regulation loop involving the transmitter is an essential part of the wireless power transmission and is extensively described in Qi specifications.

STWLC38 is also capable to function as a transmitter to provide power up to 5W.

DS14078 - Rev 1 page 2/63

# 2 Block diagram

(TX mode only) to VAA 4-levels Synchronous Rectifier ASK modulator VS TEMPERATURE SENSOR LDO2 ISNS LDO1 ADC LDO Linear Regulator RRAM FSK OVP (config) Dem clamper ROM (FW code) SCL to host Digital core (optional) RAM INTB ) (MCU) (Code/data) ENB

Figure 1. Simplified block diagram

DS14078 - Rev 1 page 3/63

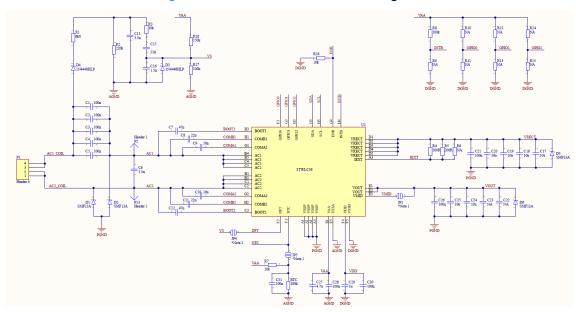

# 3 Device pin out

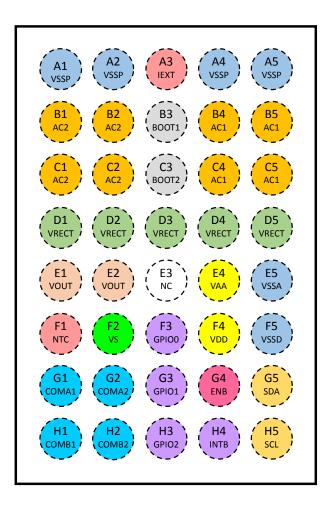

Figure 2. Pin assignment (through top view)

Table 1. Pin description

| Pin name | Pin location   | Pin function                                                                                                                             |  |  |  |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VSSA     | E5             | Analog ground. Power return for the main LDO and the analog circuitry.                                                                   |  |  |  |

| VSSD     | F5             | Digital ground. Reference for digital input and output signals.                                                                          |  |  |  |

| VSSP     | A1, A2, A4, A5 | Power ground. Power return for the synchronous rectifier.                                                                                |  |  |  |

| AC1      | B4, B5, C4, C5 | AC power input: input of the synchronous rectifier. Connect to RX series resonant circuit.                                               |  |  |  |

| AC2      | B1, B2, C1, C2 | AC power input: input of the synchronous rectifier. Connect to RX series resonant circuit.                                               |  |  |  |

| BOOT1    | В3             | Synchronous rectifier bootstrap capacitor connection: a 47 nF (typ.) ceramic capacitor is connected between this pin and AC1.            |  |  |  |

| BOOT2    | C3             | Synchronous rectifier bootstrap capacitor connection: a 47 nF (typ.) ceramic capacities connected between this pin and AC2.              |  |  |  |

| COMA1    | G1             | Modulation switches connection: capacitors between COMA1 and AC1 pin and between COMA2 and AC2 pin are used to implement ASK modulation. |  |  |  |

| COMA2    | G2             |                                                                                                                                          |  |  |  |

DS14078 - Rev 1 page 4/63

| Pin name | Pin location      | Pin function                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| COMB1    | H1                | Auxiliary modulation switches connection: capacitors between COMB1 and AC1 and                                                                                                                                                                                                                                                                                                        |  |  |  |

| COMB2    | H2                | between COMB2 and AC2 are used to implement additional ASK modulation. These pins are optionally used, in conjunction with COMA1 and COMA2 pins, to modify the ASK modulation index in specific operating conditions.                                                                                                                                                                 |  |  |  |

| VRECT    | D1, D2, D3,D4, D5 | Synchronous rectifier output and input for the main LDO linear regulator. A suitable capacitor between these pins and VSSA ensures residual AC ripple filtering and energy storage for proper load-transient response.                                                                                                                                                                |  |  |  |

| VS       | F2                | ASK de-modulation input;                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| NTC      | F1                | Coil temperature-sensing input: this pin is connected to the center tap of a resistor divider having an NTC in the low-side position. If this function is not used, the pin must be pulled-up to VAA through a 10 k $\Omega$ resistor to prevent triggering the coil over-temperature protection. If not used as temperature-sensing pin, it can be used as ADCIN2 sampling input pin |  |  |  |

| VOUT     | E1,E2             | Main LDO linear regulator output voltage. Connect a suitable filtering capacitor between these pins and VSSA to ensure stable operation and proper load tran response in all operating conditions.                                                                                                                                                                                    |  |  |  |

| NC       | E3                | Not connected (To be left floating)                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VDD      | F4                | 1.1 V LDO output and supply rail for the digital core, the ADC, and the analog circuitry. Connect a 1 µF filtering capacitor between this pin and ground.                                                                                                                                                                                                                             |  |  |  |

| VAA      | E4                | $2.5~V~LDO$ output and supply rail for the auxiliary circuitry. Connect a 4.7 $\mu F$ filtering capacitor between this pin and ground.                                                                                                                                                                                                                                                |  |  |  |

| ENB      | G4                | Chip-enable input. If set high, the device is disabled. This pin is eventually used by the host controller to control the power transfer process. Connect to ground if not used.                                                                                                                                                                                                      |  |  |  |

| IEXT     | А3                | Internal pull-down switch for active (dissipative) over-voltage clamper: a resistor with adequate power dissipation capability must be connected between this pin and VRECT to damp excessive voltage developing at the output of the rectifier.                                                                                                                                      |  |  |  |

| SCL      | H5                | I2C bus, clock line input. A pull-up resistor to the supply rail of the host controller is required to ensure correct digital levels.                                                                                                                                                                                                                                                 |  |  |  |

| SDA      | G5                | I2C bus, data line I/O. A pull-up resistor to the supply rail of the host controller is required to ensure correct digital levels.                                                                                                                                                                                                                                                    |  |  |  |

| GPIO0    | F3                |                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| GPIO1    | G3                | Programmable general-purpose I/Os: the function of these pins depends on the configuration of the device.                                                                                                                                                                                                                                                                             |  |  |  |

| GPIO2    | H3                |                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| INTB     | H4                | Interrupt output (active low). Programmable open-drain output used to generate an interrupt on specific events for the host controller.                                                                                                                                                                                                                                               |  |  |  |

DS14078 - Rev 1 page 5/63

## 4 Electrical and thermal specifications

## 4.1 Absolute maximum ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other condition above those indicated in Table 2 is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

Table 2. Absolute maximum ratings

| Parameter              | Pin(s)                                                                                    | Min. | Max. | Unit |

|------------------------|-------------------------------------------------------------------------------------------|------|------|------|

|                        | AC1, AC2, COMA1, COMA2, COMB1 and COMB2 respect to ground (VSSA, VSSD and VSSP pins)      | -0.9 | 20   |      |

|                        | BOOT1 to AC1                                                                              | 0.2  | 0.75 | -    |

|                        | BOOT2 to AC2                                                                              | -0.3 | 2.75 |      |

|                        | BOOT1 and BOOT2 respect to ground (VSSA, VSSD and VSSP pins)                              | -0.3 | 22.5 |      |

| Pin voltage range      | VRECT, VOUT and IEXT respect to ground (VSSA, VSSD and VSSP pins)                         | -0.9 | 20   | V    |

|                        | VDD respect to ground (VSSA, VSSD, and VSSP pins)                                         | -0.3 | 1.21 |      |

|                        | VAA, VS, and NTC respect to ground (VSSA, VSSD, and VSSP pins)                            | -0.3 | 2.75 |      |

|                        | GPIO0, GPIO1, GPIO2, INTB, ENB, SDA and SCL respect to ground (VSSA, VSSD, and VSSP pins) | -0.3 | 3.6  |      |

|                        | Relative voltage between any ground pin (VSSA, VSSD, VSSP)                                | -0.3 | 0.3  |      |

| RMS pin current        | AC1, AC2, VRECT, VOUT                                                                     |      | 2    | A    |

| Rivio pin current      | COMA1, COMA2, COMB1, COMB2, IEXT                                                          |      | 0.5  | A    |

| HBM ESD susceptibility |                                                                                           |      | 2000 |      |

| JEDEC JS001-2012       |                                                                                           |      | 2000 | V    |

| CDM ESD susceptibility | All pins                                                                                  |      | 500  | V    |

| JEDEC JS002-2012       |                                                                                           |      | 300  |      |

| Latch-Up EIA/JESD78E   |                                                                                           | -200 | 200  | mA   |

## 4.2 Thermal characteristics

Table 3. Thermal characteristics

| Symbol                           | Parameter                              | Conditions | Min. | Тур. | Max. | Unit |

|----------------------------------|----------------------------------------|------------|------|------|------|------|

| T <sub>A,OP</sub> <sup>(1)</sup> | Operating ambient temperature          |            | -40  |      | 85   | °C   |

| T <sub>J,OP</sub>                | Operating junction temperature         |            | 0    |      | 125  |      |

| R <sub>OJA</sub> (2)             | Junction to ambient thermal resistance | 2s2p       |      | 48   |      | °C/W |

| T <sub>SHDN</sub>                | Thermal shutdown threshold             |            |      | 125  |      | °C   |

| T <sub>SHDN,HYST</sub>           | Thermal shutdown hysteresis            |            |      | 10   |      |      |

<sup>1.</sup> T<sub>A,OP</sub> -40°C to +85°C, limits over the operating range guaranteed by design and characterization, if not otherwise specified.

DS14078 - Rev 1 page 6/63

<sup>2.</sup> Device mounted on a standard JESD51-5 test board

## 4.3 Electrical characteristics

0 °C <  $T_A$  < 85 °C;  $V_{VRECT}$  = 5 V to 10 V. Typical values are at  $T_J$  = 25 °C, if not otherwise specified.

**Table 4. Electrical characteristics**

| Symbol                  | Parameter                                                            | Test Conditions                                                                                  | Min.  | Тур. | Max.         | Unit |  |

|-------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|------|--------------|------|--|

| Supply section          |                                                                      |                                                                                                  |       |      |              |      |  |

| V                       | VRECT Under-Voltage Lock-Out upper (turn-on) threshold               | VRECT pin voltage, rising edge                                                                   |       | 2.5  |              | V    |  |

| V <sub>VRECT,UVLO</sub> | VRECT Under-Voltage Lock-Out lower (turn-off) threshold              | VRECT pin voltage, falling edge                                                                  |       | 2.3  |              | V    |  |

| V <sub>VRECT,MAX</sub>  | VRECT maximum operating supply voltage                               | Voltage on VRECT pin                                                                             |       |      | HOVP setting | V    |  |

| $I_{VOUT,Q}$            | VOUT current consumption in shut-<br>down mode                       | ENB High for more than 1 ms, supply voltage (5 V) applied to VOUT                                |       | 500  |              | μΑ   |  |

| I <sub>VRECT,OP</sub>   | Operating current consumption (not considering the programmed dummy- | ENB low, supply voltage applied to VRECT                                                         |       | 5    |              | m 1  |  |

| I <sub>VOUT,OP</sub>    | load current)                                                        | ENB low, supply voltage applied to VOUT                                                          |       | 5    |              | mA   |  |

| I.1V supply voltag      | ge LDO linear regulator                                              |                                                                                                  |       |      |              | ,    |  |

|                         | LDO1 output voltage                                                  | I <sub>VDD</sub> = 5 mA                                                                          | 1.05  | 1.10 | 1.15         | V    |  |

| VDD                     | LDO1 under-voltage lock-out upper threshold                          |                                                                                                  | 0.85  | 0.9  | 0.95         | V    |  |

| 2.5V supply voltag      | ge LDO linear regulator                                              |                                                                                                  |       |      |              |      |  |

|                         | LDO2 output voltage                                                  | I <sub>VAA</sub> =10 mA                                                                          | 2.4   | 2.5  | 2.6          | V    |  |

| V AA                    | LDO2 under-voltage lock-out upper threshold                          |                                                                                                  | 2.0   | 2.1  | 2.2          | V    |  |

| I <sub>VAA,EXT</sub>    | Maximum current allowed for external load                            |                                                                                                  |       |      | 20           | mA   |  |

| Synchronous rect        | tifier                                                               |                                                                                                  |       |      |              |      |  |

| R <sub>DSON,ACx</sub>   | Synchronous rectifier switches on-<br>resistance                     | low resistance mode (dynamically selected)                                                       |       | 50   |              | m Ω  |  |

| ASK modulator           |                                                                      |                                                                                                  |       |      |              |      |  |

| R <sub>DSON,COMMx</sub> | COMAx-COMBx modulation switches on-resistance                        | V <sub>VRECT</sub> = 5 V                                                                         |       | 0.5  | 1            | Ω    |  |

| I <sub>COMxx,MAX</sub>  | COMAx-COMBx modulation switches current capability                   | RMS value                                                                                        |       | 0.25 |              | Α    |  |

| Main LDO linear r       | egulator                                                             |                                                                                                  |       |      |              |      |  |

|                         |                                                                      | VOUT_SET=5V                                                                                      |       |      |              |      |  |

|                         |                                                                      | 0x00B2 = 2D<br>I <sub>VOUT</sub> =0.1A                                                           | 4.95  | 5.0  | 5.05         |      |  |

|                         | Output voltage                                                       | VOUT_SET=12V                                                                                     |       |      |              | V    |  |

| V <sub>OUT</sub>        |                                                                      | 0x00B2=49<br>I <sub>VOUT</sub> =0.1A                                                             | 11.95 | 12   | 12.05        | 5    |  |

|                         | VOUT Line regulation                                                 | $I_{VOUT} = 0.1 \text{ A}, V_{OUT} = 5 \text{ V},$<br>$5.1 \text{ V} < V_{VRECT} < 12 \text{ V}$ |       | 30   | 50           | mV   |  |

|                         | VOUT Load regulation                                                 | V <sub>VRECT</sub> = 5.5 V, V <sub>OUT</sub> = 5 V,                                              |       | 50   | 70           | mV   |  |

DS14078 - Rev 1 page 7/63

| Symbol                  | Parameter                                         | Test Conditions                         | Min. | Тур. | Max. | Unit |  |

|-------------------------|---------------------------------------------------|-----------------------------------------|------|------|------|------|--|

| V <sub>OUT_STEP</sub>   | Programmable step size                            |                                         |      | 25   |      | mV   |  |

| V <sub>DROP</sub>       | Linear regulator drop-out voltage                 | I <sub>OUT</sub> = 1 A                  |      | 80   |      | mV   |  |

| I <sub>OUT_CL</sub>     | Linear regulator over current protection          |                                         |      | 1.75 |      | Α    |  |

| Thermal protection      | on (external NTC)                                 |                                         |      |      | ı    |      |  |

| V                       | External over-temperature NTC pin upper threshold |                                         | 0.55 | 0.59 | 0.65 | V    |  |

| V <sub>NTC,OTP</sub>    | External over-temperature NTC pin hysteresis      |                                         | 50   | 125  | 150  | mV   |  |

| I <sub>NTC,BIAS</sub>   | NTC pin bias current                              | V <sub>NTC</sub> = 1.5 V                |      | 1    | 2    | μA   |  |

| Over-Voltage Pro        | tection                                           |                                         |      |      |      |      |  |

| V <sub>VRECT,OVPH</sub> | Hard OVP (AC1-AC2 short to VSSP) upper threshold  | HOVP threshold                          | 12   |      | 18   |      |  |

|                         | Hard-OVP step size                                | HOVP threshold step size                |      | 2.0  |      |      |  |

|                         |                                                   | SOVP threshold                          | 9    |      | 16   |      |  |

| $V_{VRECT,OVPS}$        | Soft OVP (IEXT clamping) upper threshold          | SOVP threshold step size                |      | 0.2  |      | V    |  |

|                         |                                                   | Hysteresis                              |      | 1    |      |      |  |

| $I_{IEXT,MAX}$          | IEXT clamping switch current capability           | Non-repetitive 100 ms rectangular pulse |      |      | 0.3  | А    |  |

| R <sub>IEXT,ON</sub>    | IEXT switch on-resistance                         | I <sub>IEXT</sub> = 250 mA              |      | 1    | 2    | Ω    |  |

| Digital signals         |                                                   |                                         |      |      |      |      |  |

| V <sub>IL</sub>         | Low level input voltage                           |                                         |      |      | 0.54 |      |  |

| V <sub>IH</sub>         | High level input voltage                          |                                         | 1.26 |      |      | V    |  |

| V <sub>OH</sub>         | GPIOx high level output voltage                   | Output high, I <sub>SOURCE</sub> = 2mA  | 1.4  |      |      |      |  |

| I <sub>OH</sub>         | GPIOx pin current capability                      | Output high                             | 3    |      |      | mA   |  |

| V <sub>OL</sub>         | Low level output voltage                          | Output low, I <sub>SINK</sub> =3mA      |      |      | 0.4  | V    |  |

DS14078 - Rev 1 page 8/63

## 4.4 Recommended operating conditions

| Symbol                 | Parameter                                              | Conditions                                         | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------------------------------------|----------------------------------------------------|------|------|------|------|

| DC characteris         | tics                                                   |                                                    |      |      |      |      |

| V <sub>VRECT,OP</sub>  | Operating VRECT supply voltage range                   |                                                    | 4.5  |      | 13   | V    |

| V <sub>VRECT,BPP</sub> | Operating VRECT supply voltage range in BPP mode       | V <sub>VOUT</sub> = 5 V, I <sub>VOUT</sub> = 0.5 A | 5.1  | 5.2  | 8    | V    |

| AC characteris         | tics                                                   |                                                    |      |      |      |      |

| V <sub>ACIN</sub>      | AC peak-to-peak voltage between AC1 and AC2 input pins |                                                    |      |      | 14   | V    |

| I <sub>AC,MAX</sub>    | AC1 and AC2 pins maximum RMS current capability        | Sinusoidal waveform at AC1-AC2                     |      |      | 1.25 | Α    |

| f <sub>AC</sub>        | AC synchronous rectifier input frequency range         | terminals                                          | 100  |      | 800  | kHz  |

## 4.5 Typical characteristics

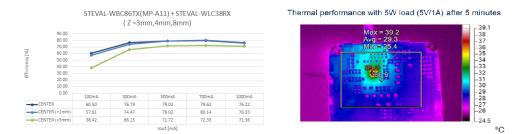

Measurements performed at room temperature (25 $^{\circ}$ C) using evaluation boards STEVAL-WBC86 TX (MP-A11a) and STEVAL-WLC38RX (8uH Coil).

Figure 3. System efficiency and Thermal Performance 5V,1A

#### 4.6 Start up waveforms

This section shows typical waveforms measured on AC1,AC2,VRECT,VOUT pins during receiver power up and ARC mode operation.

Figure 4. STWLC38 Power Up and ARC mode waveforms

DS14078 - Rev 1 page 9/63

## 5 Device description

#### 5.1 Chip-Enable Pin

When Chip-enable pin is set to HIGH, the device is in reset mode. Both rectifier low-side switches are turned-on while high-side switches are turned-off. After releasing the enable pin, STWLC38 can resume normal operational mode.

#### 5.2 Synchronous rectifier

The synchronous rectifier of the STWLC38 is a key block in charge of converting the AC input power from the receiving coil into a DC supply rail for the following linear regulator.

In principle it consists of four N-channel MOSFETs arranged in an H-bridge, conveniently driven by a control block that monitors the voltage at the AC1 and AC2 pins to optimize the commutations and to charge the external bootstrap capacitors for the high-side switches.

Different driving schemes are possible for the switches of the rectifier and the MCU core dynamically selects the optimal one to maximize the overall efficiency as a function of the operating point.

When designing the filtering capacitor at the output of the synchronous rectifier, it must be taken into account that it has to minimize the AC residual ripple and to provide energy storage to sustain load transients, without impacting on the ASK communication with the transmitter.

#### 5.3 ASK and FSK communication

Robust and reliable in-band ASK modulation is critical to the operation of any Qi compliant devices.

STWLC38 has dedicated hardware on top of the firmware algorithm to improve the performance of the in-band communication.

STWLC38 allows for two sets of modulation capacitors, namely COMA1/2 and COMB1/2. These 2 sets of ASK communication capacitors can be used in parallel or individually according to the load condition of the device. This allows for high level of flexibility to cater for a wide range of wireless transmitters.

STWLC38 comes with an advanced FSK demodulation filter which is able to remove any glitches present in the rectifier input.

The filter comes with a programmable masking pulse which is controlled by the firmware. This allows the firmware to adaptively control the filter to cater to different rectifier modes thereby ensuring robust FSK demodulation across the operating range.

#### 5.4 ARC (Adaptive Rectifier Configuration) Mode

ARC (Adaptive Rectifier Configuration) mode improves the ping up and power transfer spatial freedom of the system in both X and Y direction.

Without any change in hardware or optimization of the coil, the ping up distance is enhanced by up to 50% in all directions by enabling ARC mode. This transforms the whole surface of the Tx to a usable area. Further enhancement is possible by customization of the coil.

Coil parameter tolerance requirements are widely relaxed due to ARC mode ping up feature. This is critical to wearables and hearables application where coils are of smaller and thinner dimensions, and it is relatively costlier to keep coil parameters within tight tolerances.

#### 5.5 Protections

#### Over-voltage protection

The STWLC38 integrates different Over-Voltage Protection circuits to protect itself, the load connected to its output rail and the external components from damage due to overheating and/or exceeding AMR condition. Under normal operating conditions the voltage at the output of the synchronous rectifier is slightly higher than the output one thanks to the communication with the transmitter.

DS14078 - Rev 1 page 10/63

A sudden change in the coupling factor between transmitting and receiving coils, for example due to abrupt reciprocal repositioning of the coils, easily leads to unpredictable voltage peaks at the AC input terminals: the TX-RX regulation loop is not fast enough to prevent such an event and additional precautions must be taken.

There are 3 over voltage protections, which are POVP, SOVP and HOVP.

- POVP (Ping Over Voltage Protection)

During power-up when VAA and VDD are lower than UVLO threshold, POVP is triggered when VRECT > 14V, both rectifier low-side switches are turned-on while high-side switches are turned-off. POVP is released when VRECT < 11V.</li>

- SOVP (Soft over voltage protection)

When VRECT > VOUT + SOVP threshold, IEXT switch will be turned-on. SOVP threshold is programmable and can be set by PC GUI tool.

SOVP is released when VRECT < SOVP threshold 1V.</li>

- HOVP (Hard Over voltage Protection)

When VRECT > HOVP threshold, both rectifier low-side switches are turned on while high-side switches are turned-off. HOVP threshold is set by internal register. HOVP is released when VRECT < VOUT + SOVP release threshold, which is SOVP threshold 1V.</li>

#### Over-temperature protection

The STWLC38 is equipped with over-temperature detection circuits based on different sources:

- Internal temperature sensor

- external NTC temperature sensor

- TSHUT (hardware)

Over temperature protection(Software) The signals coming from the internal temperature sensors are conditioned and routed to the ADC. The temperature can be monitored in dedicated register. When the temperature exceeds set threshold level, it can turn off Main Voltage regulator (VOUT), EPT can be sent to TX to stop power transfer.

The external sensor (NTC), typically placed very close to the coil to detect the over temperature of the coil , low-sided NTC of a resistor divider whose center tap is connected to the NTC pin(analog input), while the high-side resistor is connected to the VAA pin.

The temperature threshold is programmable by GUI.

If this function is not used, the pin must be pulled-up to VAA through a 10  $k\Omega$  resistor to prevent triggering the coil over-temperature protection.

TSHUT comparator monitor die temperature and turns off Main voltage regulator (VOUT) when temperature exceed set threshold level. The temperature threshold is programmable by GUI from 105 °C to 135 °C with 10 °C step (10 °C hysteresis).

When TSHUT is triggered both rectifier low-side switches are turned on while high-side switches are turned-off.

#### **Over current Protection**

The current limit is programmable (1.25A, 1.5A, 1.75A, 1.93A), when output current exceed the set current limit, it can turn off Main Voltage regulator (VOUT), EPT can be sent to TX to stop power transfer.

#### 5.6 GPIOx and INTB pins

The GPIO0 through GPIO2 pins are programmable general-purpose I/O pins whose functions can be assigned in NVM memory. These pins can be configured both as inputs and outputs (either push-pull or open-drain) according to the selected function.

The INTB (GPIO3) pin is an interrupt output line that can be associated to any internal interrupt condition and used to inform the host system about specific events. The INTB pin is programmed as open-drain type.

#### 5.7 RRAM (Resistive Random Access Memory)

STWLC38 has a 32kB RRAM which allows for multiple erase/re-write cycles.

This provides flexibility for custom firmware needed for various applications like proprietary protocols or field firmware upgrades.

RRAM also offers design in flexibility during preproduction optimization.

RRAM programming can be done in standalone mode, applying 5V (USB-VBUS 5V) to VOUT pin. Using USB-I2C interface to PC GUI tool.

DS14078 - Rev 1 page 11/63

## 6 TX Mode

STWLC38 can be configured to Tx mode, it is capable of delivering output power up to 5W (coil dependent).

#### **Input Voltage**

The device can support wide range of input voltage of 5V up to 12V.

The power is applied to VOUT pin (VIN), which is the same VOUT pin when in Receiver Mode

#### Tx Inverter

The power transmitter uses a Full Bridge inverter, four N-channel MOSFETs arranged in an H-bridge.

The inverter converts the DC input into AC waveform that drives resonant circuit, which consists of Primary coil plus series capacitor.

The power transmitted to the coil is regulated by varying the switching frequency of the bridge.

A higher the operating frequency (example 200kHZ) for lower transmitted power, while a lower operating frequency (example 110kHZ) for higher transmitted power.

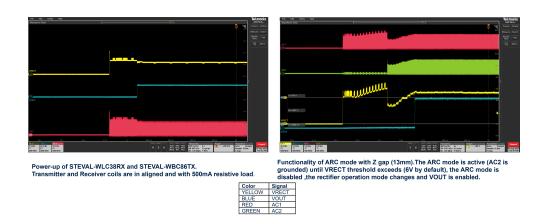

#### **ASK Demodulation**

Using ASK (Amplitude Shift Keying) modulation, the power receiver regularly sends Control error Packets to tune operating point to match Load requirements.

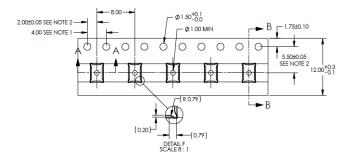

Tx receives this modulated signal from AC1 input, the coil signal is conditioned using discrete filter circuit as shown below and fed into VS pin for demodulation.

Figure 5. ASK Demodulator Circuit

DS14078 - Rev 1 page 12/63

## Wireless power interface

The blocks that refer to the wireless power interface are the synchronous rectifier, the main LDO linear regulator and the ASK modulator, as well as the digital core as supervisor. The power transfer from the transmitter to the receiver is established as a result of a procedure which consists of several distinct stages.

The power transfer begins after the transmitter has properly detected a valid receiver and a specific communication has been established between the two parts.

#### Power transfer phases

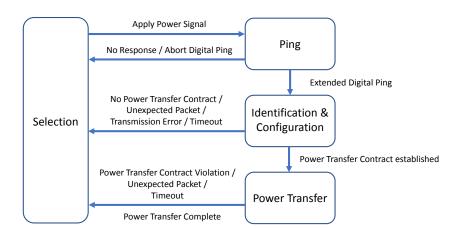

The flow-chart in Figure 6 reports the whole process of power transfer in Baseline Power Profile (BPP up to 1A@5V)

Figure 6. Power transfer phases for Baseline Power Profile

#### BPP power transfer phases

- Digital ping: this phase is an interrogation session based on a more energetic AC burst during which the

potential receiver is expected to reply through amplitude shift-keying (ASK) modulation, the receiver device

sends Signal strength packet.

- Identification & configuration: this phase is aiming to identify the receiver and to gather information about its power transfer capability. The transmitter generates a so-called "Power Transfer Contract" tailoring some parameters that will characterize the following power transfer phase.

- Power transfer: this is the final step, where the transmitter initially increases and subsequently modulates the transmitted power in response to the control (feedback) data from the receiver.

The flow-chart in below shows the whole process leading to a power transfer in Extended Power Profile (EPP) up to 1.25A@12V

Ping Configuration Negotiation Power Transfer

Figure 7. Power transfer phases for Extended Power Profile

#### EPP power transfer phases

Without entering the details of the different phases, the basic sequence of events taking place when a receiver is properly placed on the transmitting coil are summarized as:

DS14078 - Rev 1 page 13/63

- Digital ping: this phase is an interrogation session based on a more energetic AC burst during which the

potential receiver is expected to reply through amplitude shift-keying (ASK) modulation, the receiver device

sends Signal strength packet.

- Identification & configuration: this phase is aiming to identify the receiver and to gather information about its power transfer capability. The transmitter generates a so-called "Power Transfer Contract" tailoring some parameters that will characterize the following power transfer phase.

- Negotiation: in this phase the Power Receiver negotiates with the Power Transmitter to fine tune the Power Transfer Contract.

- Power transfer: this is the final step, where the transmitter initially increases and subsequently modulates the transmitted power in response to the control (feedback) data from the receiver

STWLC38 goes autonomously through Selection, Ping, Identification & Configuration phases, entering Power Transfer phase if no error occurs.

During the Power Transfer phase, the device sends Received-Power and Control-Error packets periodically as feedback information for the transmitter.

If a critical event like over-voltage, over-current or over-temperature occurs, the STWLC38 automatically sends the End-Power-Transfer packet.

When the Power Transfer is up and running, the End-Power-Transfer packet (with any response value) or any custom packet (e.g. Proprietary packet or Charge-Status packet) can be sent to the transmitter simply through commands via I<sup>2</sup>C interface.

Sending a custom packet may result in a reply (either a data packet or a pattern response from the transmitter) or no reply at all: if a response is received, the content is captured and stored in specific I<sup>2</sup>C registers. Important notes:

- Changing the output voltage must respect the overall system design (selected coil, transmitter type, etc.).

- Output load transient response strongly depends on a correct design of the output capacitors. Severe load transients may lead to temporary output voltage collapse due to the overall TX-RX response time.

- A minimal output load significantly helps in increasing the signal-to-noise ratio during digital ping and is

advisable to ensure interoperability with all transmitters. For this purpose, the STWLC38 allows the user

to set a dummy load (reservoir current) which is dynamically managed to fade-out when an output load is

applied

- The initial load at power-up should not exceed 2.5 W, smoothly ramping-up to full power subsequently.

DS14078 - Rev 1 page 14/63

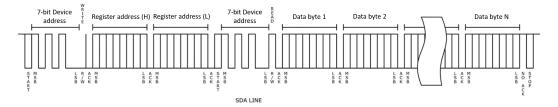

#### 8 I2C interface

The STWLC38 can operate fully independently, i.e. without being interfaced with a host system.

In applications in which the STWLC38 has to be a part of peripherals managed by the host system, the two SDA and SCL pins could be connected to the existing I<sup>2</sup>C bus.

The device works as an I<sup>2</sup>C slave and supports standard (100 kbps) fast (400 kbps) data transfer modes.

The STWLC38 has been assigned 0x61 7-bit hardware address. The pins are up to 3.3 V tolerant and the pull-up resistors should be selected as a trade-off between communication speed (lower resistors lead to faster edges) and data integrity (the input logic levels have to be guaranteed to preserve communication reliability).

When the bus is idle, both SDA and SCL lines are pulled HIGH.

#### **Data Validity**

The data on the SDA line must be stable during the high period of the clock. The high and low states of the SDA line can only change when the SCL clock signal is low.

#### **Start and Stop Conditions**

Both the SDA and the SCL lines remain high when the I<sup>2</sup>C bus is not busy. A START condition is a high-to-low transition of the SDA line when SCL is HIGH, while the STOP condition is a low-to-high transition of the SDA line when SCL is HIGH. A STOP condition must be sent before each START condition.

SCL START condition STOP condition

Figure 8. Start and Stop Condition on the I2C Bus

#### **Byte format**

Every byte transferred over the SDA line must contain 8 bits. Each byte received by the STWLC38 generally is followed by an acknowledge (ACK) bit. The MSB is transferred first. One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high state of each SCL clock pulse.

The device generates the ACK pulse (by pulling-down the SDA line during the acknowledge clock pulse) to confirm the correct device address or received data bytes.

#### Interface protocol

The interface protocol consists of

- Start condition (START)

- 7-bit device address (0x61) + R/W bit (read = 1 / write = 0)

- Register pointer, high-byte

- Register pointer, low-byte

- Data sequence: N x (data byte + ACK)

- Stop condition (STOP)

The register pointer (or address) byte defines the destination register to which the read or write operation applies. When the read or write operation is finished, the register pointer is automatically incremented.

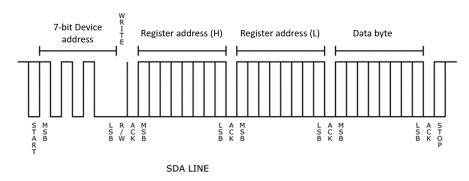

## Writing to a single register

Writing to a single register begins with a START condition followed by device address 0xC2 (7-bit device address plus R/W bit cleared), two bytes of the register pointer and the data byte to be written in the destination register. Each transmitted byte is acknowledged by the STWLC38 through an ACK pulse.

DS14078 - Rev 1 page 15/63

Figure 9. Writing to single register byte

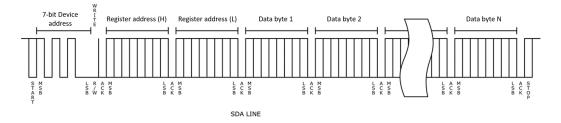

#### Writing to multiple registers (page write)

The STWLC38 supports writing to multiple registers with auto-incremental addressing. When data is written into a register, the register pointer is automatically incremented, therefore transferring data to a set of subsequent registers (also know as page write) is a straightforward operation.

Figure 10. Writing multiple register bytes

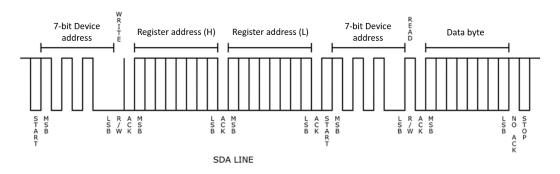

#### Reading from a single register

Reading from a single register begins with a START condition followed by the device address byte 0xC2 (7-bit device address plus R/W bit cleared) and two bytes of register pointer, then a re-START condition is generated and the device address 0xC3 (7-bit device address plus R/W bit asserted) is sent, followed by data reading. ACK pulse is generated by the STWLC38 at the end of each byte, but not for data bytes retrieved from the register. A STOP condition is finally generated to terminate the operation.

Figure 11. Reading single register byte

DS14078 - Rev 1 page 16/63

#### Reading from multiple registers (page reading)

Similarly to multiple (page) writing, reading from subsequent registers relies on an auto-increment of the register: the master can extend data reading to the following registers by generating and an ACK pulse at the end of each byte. Data reading starts immediately and the stream is terminated by a NMAK pulse at the end of the last data byte, followed by a STOP condition.

Figure 12. Reading multiple bytes

DS14078 - Rev 1 page 17/63

## 9 I2C register map

The STWLC38 can be monitored and controlled by accessing the internal registers via I<sup>2</sup>C interface. The following registers map reports the accessible addresses. Addresses not shown in the map and blank bits have to be considered reserved and not altered as well.

These CFG parameters are accessible using the GUI tool, a new memh file needs to be generated after customized changes and to be Programmed in to NVM.

Table 5. Register abbreviations

| Register type | Description                                                 |

|---------------|-------------------------------------------------------------|

| R/W           | can read and write the bits                                 |

| R             | can read only                                               |

| W             | can write only                                              |

| CFG           | For customizing Configuration, accessible through GUI only. |

**Table 6. Chip information**

| Address | Register name            | R/W | Default | Description                  |

|---------|--------------------------|-----|---------|------------------------------|

| 0x0000  | Chip ID [Byte 0]         | R   | 0x26    | Chip ID [70]                 |

| 0x0001  | Chip ID [Byte 1]         | R   | 0x00    | Chip ID [158]                |

| 0x0002  | Chip revision            | R   | 0x03    | Chip revision [70]           |

| 0x0003  | Customer ID              | R   | 0x00    | Customer ID [70]             |

| 0x0004  | ROM ID [Byte 0]          | R   | 0x61    | ROM ID [70]                  |

| 0x0005  | ROM ID[Byte 1]           | R   | 0x00    | ROM ID [158]                 |

| 0x0006  | NVM Patch ID[Byte 0]     | R   | -       | NVM patch ID [70]            |

| 0x0007  | NVM Patch ID[Byte 1]     | R   | -       | NVM patch ID [158]           |

| 0x0008  | RAM patch ID[Byte 0]     | R   | -       | RAM patch ID [70]            |

| 0x0009  | RAM patch ID[Byte 1]     | R   | -       | RAM patch ID [158]           |

| 0x000A  | Configuration ID[Byte 0] | R   | -       | Configuration ID [70]        |

| 0x000B  | Configuration ID[Byte 1] | R   | -       | Configuration ID [158]       |

| 0x000C  | Production ID[Byte 0]    | R   | 0x07    | PE ID [70]                   |

| 0x000D  | Production ID[Byte 1]    | R   | 0x00    | PE ID [158]                  |

|         |                          |     |         | 0x1: Standalone (debug) mode |

| 0x000E  | Operation mode           | R   | 0x02    | 0x2: Qi RX mode              |

|         |                          |     |         | 0x3: Qi TX mode              |

| 0x0010  | Device ID[Bytes 015]     | R   | _       | Device ID Bytes 015          |

| 0x001F  | 201100 12[Bytes 6 1.10]  |     |         | 201100 12 27100 010          |

**Table 7. System information**

| Address | Register name          | R/W | Default | Description                                                 |

|---------|------------------------|-----|---------|-------------------------------------------------------------|

| 0x0020  | System command[Byte 0] | RW  | -       | Bit 0: Switch to TX command Write 1 to switch to Qi TX mode |

DS14078 - Rev 1 page 18/63

| Address | Register name            | R/W | Default | Description                                |

|---------|--------------------------|-----|---------|--------------------------------------------|

| 0x0020  | System command[Byte 0]   | -   | -       | Bit 17 Reserved                            |

|         |                          |     |         | Bit 0: Core hard fault error               |

|         |                          | R   | -       | 0: No hard fault error detected            |

|         |                          |     |         | 1: Hard fault error detected               |

|         |                          |     |         | Bit 1: HW WDT trigger latch                |

|         |                          | R   | -       | 0: HW WDT not triggered                    |

| 0x002C  | System error information |     |         | 1: HW WDT triggered                        |

| 0X002C  | [Byte 0]                 |     |         | Bit 2: NVM IP error                        |

|         |                          | R   | -       | 0: No NVM IP error detected                |

|         |                          |     |         | 1: NVM IP error detected                   |

|         |                          |     |         | Bit 3: Reserved                            |

|         |                          | R   | -       | Bit 4: NVM Boot error                      |

|         |                          |     |         | Bit 57 : Reserved                          |

|         |                          |     |         | Bit [10] NVM PE error                      |

|         |                          |     |         | 0: No error                                |

|         |                          | R   | -       | 1: Section header error                    |

|         |                          |     |         | 2: Section CRC failed                      |

|         |                          |     |         | 3: Reserved                                |

|         |                          |     |         | Bit [32] NVM Configuration error           |

|         |                          |     |         | 0: No error                                |

|         |                          | R   | -       | 1: Section header error                    |

|         |                          |     |         | 2: Section CRC failed                      |

|         |                          |     |         | 3: Reserved                                |

| 0x002D  | System error [Byte 1]    |     |         | Bit [54] NVM Patch error                   |

|         |                          |     |         | 0: No error                                |

|         |                          | R   | -       | 1: Section header error                    |

|         |                          |     |         | 2: Section CRC failed                      |

|         |                          |     |         | 3: Reserved                                |

|         |                          |     |         | Bits [76] NVM Production Information error |

|         |                          |     |         | 0: No error                                |

|         |                          | R   | -       | 1: Section header error                    |

|         |                          |     |         | 2: Section CRC failed                      |

|         |                          |     |         | 3: Reserved                                |

|         |                          | R   |         |                                            |

| 0x002E  | System error[Byte 2]     | R   | -       | Reserved                                   |

| 0x002F  | System error[Byte 3]     | R   | -       | Reserved                                   |

#### **Table 8. Communication**

| Address | Register name            | R/W | Default | Description                                        |

|---------|--------------------------|-----|---------|----------------------------------------------------|

| 0x00D8  | RX DTS SEND LEN Byte 0,1 | RW  | -       | DTS ADS number of data bytes in stream Byte 0 [70] |

| 0x00D9  |                          |     |         | Byte 1 [70]                                        |

| 0x00DA  | RX DTS SEND RQ Byte2     | RW  | _       | Send ADC request Byte 2 Bits [40]                  |

DS14078 - Rev 1 page 19/63

| Address | Register name             | R/W | Default | Description                                                                           |

|---------|---------------------------|-----|---------|---------------------------------------------------------------------------------------|

|         |                           |     |         | Bits[57] Reserved                                                                     |

| 0x00DC  | DV DTS DCV/I EN Duto 0 1  | RW  |         | DTS ADS number of bytes in stream received Byte 0 [70]                                |

| 0x00DD  | RX DTS RCV LEN Byte 0 ,1  | KVV | -       | Byte 1 [70]                                                                           |

| 0,000   | DX00DE DTS RCV RQ[Byte 3] | R   | -       | Received ADC request Bits [40]                                                        |

| UXUUDE  |                           |     |         | Bits[57] Reserved                                                                     |

| 0x0090  | RX SEND DTS               | R   |         | Bit 5 : Start sending DTS transaction , DTS send register specify the data to be send |

| 0x02000 | DTS SEND                  | RW  | -       | Total number of bytes can be sent 128.                                                |

| x27F    | DIS SEND                  |     |         | First 11Bytes shown in GUI                                                            |

| 0x02800 | DTS RECV                  | R   | _       | Total number of bytes can be received 128.                                            |

| x2FF    | DISINECV                  |     | -       | First 11Bytes shown in GUI                                                            |

#### Table 9. Commands

| Address | Register name | R/W | Default | Description                                                              |

|---------|---------------|-----|---------|--------------------------------------------------------------------------|

| 0x0020  | Command       | RW  | -       | SWITCH TO TX Bit 0: Switch to TX command Write 1 to switch to Qi TX mode |

## Table 10. Mode monitor

| Address | Register name          | R/W | Default | Description                                                               |

|---------|------------------------|-----|---------|---------------------------------------------------------------------------|

| 0x0092  | VRECT [Byte 01] R      | В   |         | Rectifier voltage in mV [70]                                              |

| 0x0093  |                        | K   | -       | [158]                                                                     |

| 0x0094  | VOLITIDA (0. 41        | R   |         | Main LDO Voltage output in mV [70]                                        |

| 0x0095  | VOUT[Byte 01]          | K   | -       | Main LDO Voltage output in mV [158]                                       |

| 0x0096  | ICUDID to 0 41         | _   |         | Output current in mA [70]                                                 |

| 0x0097  | ICUR[Byte 01]          | R   | -       | [158]                                                                     |

| 0x0098  | TMEACIDA to 0, 41      | Б   |         | Chip temperature in deg C [70]                                            |

| 0xx099  | TMEAS[Byte 01]         | R   | -       | [158]                                                                     |

| 0x009A  | OD EDEO(D) 4- 0, 41    | R   | -       | Operating frequency in kHz [70]                                           |

| 0x009B  | OP FREQ[Byte 01]       |     |         | [158]                                                                     |

| 0x009C  |                        | R   | -       | NTC temperature measurement [70]                                          |

| 0x009D  | NTC [Byte 01]          |     |         | [158]                                                                     |

| 0x00A4  | RX VOLT DIFF [Byte 01] |     | -       | Control Error: Rx voltage difference target and measured VRECT in mV [70] |

| 0x00A5  |                        |     |         | [158]                                                                     |

| 0x00A6  | DOWED DVID. to 0, 41   | R   |         | RX received power in mW [70]                                              |

| 0x00A7  | POWER RX[Byte 01]      | K   | -       | [158]                                                                     |

| 0x00A8  | SIG STREN[Byte01]      | R   | -       | Signal strength measured in Rx [70]                                       |

| 0x00A9  |                        |     |         | [158]                                                                     |

|         | POWER TX               | CFG |         | Power transferred to RX                                                   |

|         | RX NEG STATE           | CFG |         | Qi Power transfer Indicates BPP or EPP power transfer                     |

DS14078 - Rev 1 page 20/63

| Address | Register name | R/W | Default | Description                              |

|---------|---------------|-----|---------|------------------------------------------|

| 0x012A  | TX DUTY       | R   |         | TX operating duty cycle [70]             |

|         | TX POWER RPP  | CFG |         | Last value sent in Received Power Packet |

|         | TX RECENT CEP | CFG |         | Last CEP value received from RX          |

#### Table 11. GPIO

| Address | Register name | R/W | Default | Description                                     |

|---------|---------------|-----|---------|-------------------------------------------------|

| 0x30    | GPIO0 Func    | RW  | -       | Please refer to GPIO configuration description. |

| 0x31    | GPIO1 Func    | RW  | -       | Please refer to GPIO configuration description. |

| 0x32    | GPIO2 Func    | RW  | -       | Please refer to GPIO configuration description. |

| 0x33    | GPIO3 Func    | RW  |         | Interrupt pin - INTB                            |

#### GPIO configuration - alternate functions

- 0x00: GPIO configured as Input, FLOATING (Default)

- 0x01: GPIO configured as Input , Pull up resistor to internal 1.8V.

- 0x02: GPIO configured as Input ,Pull down resistor to Internal Ground.

- 0x03:GPIO configured as Interrupt pin , Open Drain output.

- 0x04:GPIO configured as Interrupt pin , Push pull output.

- 0x05:Initialization complete, FW ready (Active High).

- 0x06: Input to turn-off Main LDO block (Active High).

- 0x07:Input to Disable ASK communication (Active High).

- 0x0B: Input to Disable RX POWEROUT after Negotiation- Push pull (Active High).

- 0x0C: Input to Disable RX\_POWEROUT after Negotiation- Push pull (Active Low).

- 0x0D:Input to Disable RX\_POWEROUT after Negotiation- Open Drain.

- 0x29: GPIO configured as Output, Open Drain (Active Low).

- 0x2A:GPIO configured as Output , Open Drain (Active High).

- 0x2B: GPIO configured as Output , Push pull (Active Low).

- 0x2C:GPIO configured as Output , Push pull (Active High).

#### Receiver mode (Rx) registers

Table 12. RX interrupts enable

| Address | Register name               | R/W | Default | Description                        |

|---------|-----------------------------|-----|---------|------------------------------------|

|         |                             |     |         | Bit 0:RX OVTP EN                   |

|         |                             | RW  |         | over temperature protection enable |

|         |                             | KVV | -       | 0: disable                         |

|         |                             |     |         | 1: enable                          |

|         |                             | RW  | -       | Bit 1: RX OCP EN                   |

| 0.0000  | RX Interrupt Enable[Byte 0] |     |         | over current protection enable     |

| 0x0080  |                             |     |         | 0: disable                         |

|         |                             |     |         | 1: enable                          |

|         |                             |     |         | Bit 2:RX OVP EN                    |

|         |                             | RW  | -       | over voltage protection enable     |

|         |                             | KVV |         | 0: disable                         |

|         |                             |     |         | 1: enable                          |

DS14078 - Rev 1 page 21/63

| Address | Register name               | R/W  | Default | Description                                               |

|---------|-----------------------------|------|---------|-----------------------------------------------------------|

|         |                             |      |         | Bit 3: RX SYS ERROR EN                                    |

|         |                             | RW   | -       | system error enable                                       |

|         |                             |      |         | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             | RW   | -       | Bit4:Reserved                                             |

|         |                             |      |         | Bit5: RX MSG RCVD EN                                      |

|         |                             |      |         | message received from TX enable                           |

|         |                             | RW   | -       | 0: disable                                                |

| 0x0080  | RX Interrupt Enable[Byte 0] |      |         | 1: enable                                                 |

|         |                             |      |         | Bit6: RX OUTPUT ON EN                                     |

|         |                             |      |         | output on interrupt enable                                |

|         |                             | RW   | -       | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             |      |         | Bit7: RX OUTPUT OFF EN                                    |

|         |                             |      |         | Output off interrupt enable                               |

|         |                             | RW   | -       | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             |      |         | Bit0: RX SENT PACKET EN                                   |

|         |                             |      | -       | Packet sent interrupt enable                              |

|         |                             | RW   |         | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             | RW   | -       | Bit1:RX SENT PKT TO EN                                    |

|         |                             |      |         | Packet sending timeout interrupt enable                   |

|         |                             |      |         | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             | RW   | -       | Bit2:RX SIG STR EN                                        |

|         |                             |      |         | Signal Strength sent interrupt enable                     |

| 0x0081  | RX Interrupt Enable[Byte 1] | KVV  |         | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             |      |         | Bit3:RX VRECT RDY EN                                      |

|         |                             | RW   |         | VRECT ready interrupt enable                              |

|         |                             | KVV  | -       | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             |      |         | Bit4:RX UVLO EN                                           |

|         |                             | RW   |         | under voltage protection interrupt enable                 |

|         |                             | LZVV | _       | 0: disable                                                |

|         |                             |      |         | 1: enable                                                 |

|         |                             |      |         | Bit5,6,7: RESERVED                                        |

|         |                             |      |         | Bit0:RX DTS SEND SUCCESS EN                               |

|         |                             | DIA: |         | DTS sending data stream successfully interrupt enable     |

| 0,0000  | BV Interrupt Enable(Dute 0) | RW   | -       | 0: disable                                                |

| 0x0082  | RX Interrupt Enable[Byte 2] |      |         | 1: enable                                                 |

|         |                             | RW   |         | Bit1: RX DTS SEND TO END EN                               |

|         |                             | Γ₹VV | _       | DTS stopped sending due to timeout error interrupt enable |

DS14078 - Rev 1 page 22/63

| Address | Register name                   | R/W  | Default | Description                                                 |

|---------|---------------------------------|------|---------|-------------------------------------------------------------|

|         |                                 |      |         | 0: disable                                                  |

|         |                                 |      |         | 1: enable                                                   |

|         |                                 |      |         | Bit2: RX DTS SEND RESET END EN                              |

|         |                                 | RW   |         | DTS stopped due to reset interrupt enable                   |

|         |                                 | KVV  | -       | 0: disable                                                  |

|         |                                 |      |         | 1: enable                                                   |

|         |                                 | RW   | -       | Bit3: RESERVED                                              |

|         |                                 |      |         | Bit4:RX DTS RCVD SUCCESS EN                                 |

|         |                                 | RW   |         | DTS received data stream successful interrupt enable        |

| 0x0082  | 082 RX Interrupt Enable[Byte 2] | KVV  | -       | 0: disable                                                  |

| 0X0062  |                                 |      |         | 1: enable                                                   |

|         |                                 |      | -       | Bit 5:RX DTS RCVD TO END EN                                 |

|         |                                 | RW   |         | DTS stopped receiving due to timeout error interrupt enable |

|         |                                 | IXVV |         | 0: disable                                                  |

|         |                                 |      |         | 1: enable                                                   |

|         |                                 |      |         | Bit6:RX DTS RCVD RESET END EN                               |

|         |                                 |      |         | DTS stopped receiving due to reset interrupt enable         |

|         |                                 |      |         | 0: disable                                                  |

|         |                                 |      |         | 1: enable                                                   |

|         |                                 | -    | -       | Bit 7: Reserved                                             |

| 0x0083  | RX Interrupt Enable[Byte 3]     | -    | -       | Reserved                                                    |

**Table 13. RX interrupt Clear**

| Address | Register name              | R/W | Default | Description                       |

|---------|----------------------------|-----|---------|-----------------------------------|

|         |                            |     |         | Bit 0:RX OVTP CLR                 |

|         |                            | R   | -       | Over temperature protection clear |

|         |                            |     |         | 1: clear                          |

|         |                            |     |         | Bit 1:RX OCP CLR                  |

|         |                            | R   | -       | Over current protection clear     |

|         |                            |     |         | 1: clear                          |

|         |                            |     |         | Bit 2:RX OVP CLR                  |

|         | RX interrupt Clear[Byte 0] | R   | -       | Over voltage protection clear     |

| 0x0084  |                            |     |         | 1: clear                          |

| UXUU64  |                            | R   | -       | Bit 3:RX SYS ERROR CLR            |

|         |                            |     |         | system error clear                |

|         |                            |     |         | 1: clear                          |

|         |                            | R   | -       | Bit 4: Reserved                   |

|         |                            |     |         | Bit5:RX MSG RCVD CLR              |

|         |                            | R   | -       | message received from TX clear    |

|         |                            |     |         | 1: clear                          |

|         |                            | R   |         | Bit6:RX OUTPUT ON CLR             |

|         |                            | rX. | _       | Output on interrupt clear         |

DS14078 - Rev 1 page 23/63

| Address | Register name              | R/W | Default | Description                                                |

|---------|----------------------------|-----|---------|------------------------------------------------------------|

|         |                            |     |         | 1: clear                                                   |

|         |                            |     |         | Bit7: RX OUTPUT OFF CLR                                    |