# SK6011 300mA Ultra-Low-Noise LDO for RF and Analog Circuits

#### DESCRIPTION

The SK6011 family of low-dropout (LDO), low-power linear regulators offers very high power supply rejection ratio (PSRR) while maintaining very low quiescent current, suitable for RF applications. The family uses an advanced CMOS process and a PMOSFET pass device to achieve fast start-up, very low noise, excellent transient response, and excellent PSRR performance.

The SK6011 is stable with a 1.0 µF ceramic output capacitor, and uses a precision voltage reference and feedback loop to achieve a worst-case accuracy of 2% over all load, line, process, and temperature variations. It is fully specified from TJ = -40°C to +125°C and is offered in a small UTDFN1×1-4, DFN1×1-4 and SOT23-5 package, which is ideal for small form factor portable equipment such as wireless handsets and PDAs.

#### **FEATURES**

Wide Input Voltage Range: 1.9 V to 5.5 V

Output Voltage: 1.2 V to 4.5 V

Up to 300 mA Load Current

Other Output Voltage Options Available on

Request

Very Low IQ: 14 μA

Low Dropout: 180 mV @ 3.3 V typical

Very High PSRR: 90 dB at 1 kHz

Ultra Low Noise: 10 µVRMS at 3.3 V output

(load = 1 mA)

Excellent Load/Line Transient Response

Line Regulation: 0.02%/V typical

Short-Circuit Current Limit: 80 mA (Current at

short mode) typical

With Auto Discharge

#### **APPLICATIONS**

- **Smart Phones and Cellular Phones**

- **PDAs**

- MP3/MP4 Player

- **Digital Still Cameras**

- Portable Instrument

#### ORDERING INFORMATION

| Ordering Number | Package    | Packing Option       |

|-----------------|------------|----------------------|

| SK6011UD4-XX    | UTDFN1×1-4 | Tape and Reel, 10000 |

| SK6011D4-XX     | DFN1×1-4   | Tape and Reel, 10000 |

| SK6011S5-XX     | SOT23-5    | Tape and Reel, 3000  |

<sup>\*</sup>XX: When expressed as 18, the output voltage is 1.8 V; when expressed as 30 the output voltage is 3.0 V.

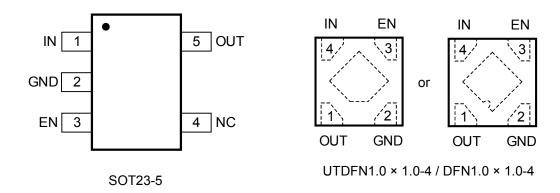

## PIN CONFIGURATION (Top View)

## **PIN DESCRIPTIONS**

|         | Pin                    |        | Description                                                                                             |  |

|---------|------------------------|--------|---------------------------------------------------------------------------------------------------------|--|

| SOT23-5 | UTDFN1×1-4<br>DFN1×1-4 | Symbol |                                                                                                         |  |

| 1       | 4                      | IN     | Supply input pin. Must be closely decoupled to GND with a 1 $\mu\text{F}$ or greater ceramic capacitor. |  |

| 2       | 2                      | GND    | Ground.                                                                                                 |  |

| 3       | 3                      | EN     | Enable control input, active high. Do not leave EN floating.                                            |  |

| 4       |                        | NC     | No Connection.                                                                                          |  |

| 5       | 1                      | OUT    | Output pin. Bypass a 1 $\mu\text{F}$ ceramic capacitor from this pin to ground.                         |  |

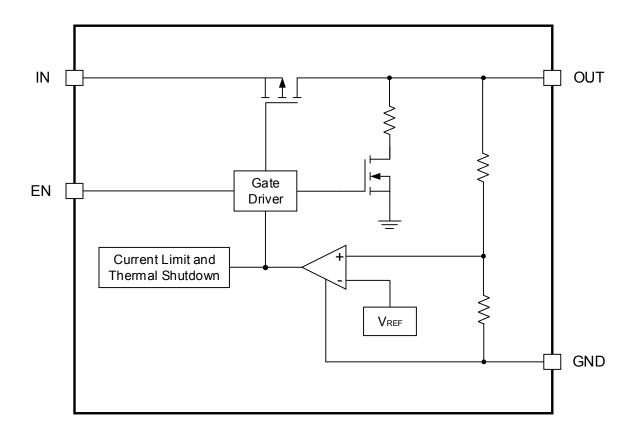

#### **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

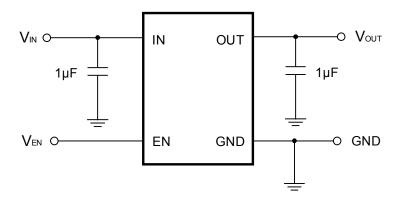

#### **Input Capacitor**

A  $1\,\mu\text{F}$  ceramic capacitor is recommended to connect between IN and GND pins to decouple input power supply glitch and noise. The amount of the capacitance may be increased without limit. This input capacitor must be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both IN and GND. The input capacitor should be at least equal to, or greater than, the output capacitor for good load transient performance.

#### **Output Capacitor**

An output capacitor is required for the stability of the LDO. The recommended output capacitance is from 1  $\mu$ F to 10  $\mu$ F, Equivalent Series Resistance (ESR) is from 5 m $\Omega$  to 500 m $\Omega$ , and temperature characteristics are X7R or X5R. Higher capacitance values help to improve load/line transient response. The output capacitance may be increased to keep low undershoot/overshoot. Place output capacitor as close as possible to OUT and GND pins. With a reasonable PCB layout, the single 1  $\mu$ F ceramic output capacitor can be placed up to 10 cm away from the SK6011 device.

#### **ON/OFF Input Operation**

The SK6011 EN pin is internally held low by a 1 M $\Omega$  resistor to GND. The SK6011 is turned on by setting the EN pin higher than  $V_{IL}$  threshold, and is turned off by pulling it lower than  $V_{IL}$  threshold. If this feature is not used, the EN pin should be tied to IN pin to keep the regulator output on at all time.

#### **High PSRR and Low Noise**

RF circuits such as LNA (low-noise amplifier), up/down-converter, mixer, PLL, VCO, and IF stage, require low noise and high PSRR LDOs. The temperature-compensated crystal oscillator circuit requires very high PSRR at RF power amplifier burst frequency. For instance, minimum 65 dB PSRR at 217 Hz is recommended for the GSM handsets.

In order to provide good audio quality, the audio power supply for hand-free, game, MP3, and multimedia applications in cellular phones, require low-noise and high PSRR at audio frequency range (20 Hz to 20 kHz). The SK6011, with PSRR of 90 dB at 1 kHz, is suitable for most of these applications that require high PSRR and low noise.

#### **Output Automatic Discharge**

The SK6011 output employs an internal 60  $\Omega$  (typical) pulldown resistance to discharge the output when the EN pin is low, and the device is disabled.

#### **Remote Output Capacitor Placement**

The SK6011 requires at least a  $1\,\mu\text{F}$  capacitor at the OUT pin, but there are no strict requirements about the location of the capacitor in regards the OUT pin. In practical designs, the output capacitor may be located up to 10 cm away from the LDO.

#### **Fast Transient Response**

Fast transient response LDOs can also extend battery life. TDMA-based cell phone protocols such as Global System for Mobile Communications (GSM) have a transmit/receive duty factor of only 12.5 percent, enabling power savings by putting much of the baseband circuitry into standby mode in between transmit cycles. In baseband circuits, the load often transitions virtually instantaneously from 100  $\mu$ A to 100 mA. To meet this load requirement, the LDO must react very quickly without a large voltage drop or overshoot -- a requirement that cannot be met with conventional, general-purpose LDOs.

The SK6011's fast transient response from 0 to 300 mA provides stable voltage supply for fast DSP and GSM chipset with fast changing load.

#### **Low Quiescent Current**

Cellular phone baseband internal digital circuits typically operate all the time. That requires LDO stays on at all times. However, in the standby mode, the microprocessor consumes only around 100  $^{\sim}$  300  $\mu$ A. Since the phone stays in standby for the longest percentage of time, using a 14  $\mu$ A quiescent current LDO, instead of 100- $\mu$ A, saves 88  $\mu$ A and can substantially extends the battery standby time.

The SK6011, consuming only 14  $\mu$ A quiescent current, provides great power saving in portable and low power applications.

#### Minimum Operating Input Voltage (VIN)

The SK6011 does not include any dedicated UVLO circuitry. The SK6011 internal circuitry is not fully functional until  $V_{IN}$  is at least 1.8 V. The output voltage is not regulated until  $V_{IN}$  has reached at least the greater of 1.8 V or  $(V_{OUT} + V_{DROP})$ .

#### **Current Limit Protection**

When output current at the OUT pin is higher than current limit threshold or the OUT pin is short-circuit to GND, the current limit protection will be triggered and clamp the output current to approximately 80 mA to prevent overcurrent and to protect the regulator from damage due to overheating.

#### Thermal Overload Protection (TSD)

Thermal shutdown disables the output when the junction temperature rises to approximately 155°C which allows the device to cool. When the junction temperature cools to approximately 140°C, the output circuitry enables. Based on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This thermal cycling limits the dissipation of the regulator and protects it from damage as a result of overheating.

The thermal shutdown circuitry of the SK6011 has been designed to protect against temporary thermal overload conditions. The TSD circuitry was not intended to replace proper heat-sinking. Continuously running the SK6011 device into thermal shutdown may degrade device reliability

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                           | Symbol          | Min              | Max                   | Unit |

|-------------------------------------|-----------------|------------------|-----------------------|------|

| IN Voltage                          | V <sub>IN</sub> | -0.3             | 6.0                   | V    |

| Other Pin Voltage                   |                 | -0.3             | V <sub>IN</sub> + 0.3 | V    |

| Maximum Load Current                |                 | Internal Limited |                       | mA   |

| Operating Junction Temperature      | T <sub>OP</sub> | -40              | +125                  | °C   |

| Storage Temperature                 | $T_{STG}$       | -65              | +150                  | °C   |

| Lead Temperature(Soldering, 10 sec) | T <sub>L</sub>  |                  | 300                   | °C   |

#### NOTE:

Stresses beyond those listed under "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SUNTEK recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

SUNTEK reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. Please contact SUNTEK sales office to get the latest datasheet.

## **ELECTRICAL CHARACTERISTICS**

$T_{\text{A}}$  = +25°C,  $C_{\text{IN}}$  = 1  $\mu\text{F},\,C_{\text{OUT}}$  = 1  $\mu\text{F},\,\text{unless}$  otherwise noted.

| Symbol                 | Parameter                         | Test Conditions                                                           | Min | Тур  | Max | Unit              |

|------------------------|-----------------------------------|---------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>IN</sub>        | Input Voltage Range               |                                                                           | 1.9 |      | 5.5 | ٧                 |

|                        | Output Voltage Tolerance          | V <sub>IN</sub> = 2.8 V to 5.5 V, I <sub>OUT</sub>                        | -2  |      | 2   | %V <sub>OUT</sub> |

| A) /                   | Output voltage Tolerance          | = 1 mA to 300 mA                                                          | -2  |      |     | 70 001            |

| $\Delta V_{OUT}$       | Line Regulation                   | $V_{IN} = 2.8 \text{ V to } 5.5 \text{ V}, I_{OUT} = 1 \text{ mA}$        |     | 0.02 |     | %/V               |

|                        | Load Regulation                   | I <sub>OUT</sub> = 1 mA to 300 mA                                         |     |      | 1   | %                 |

| I <sub>LOAD</sub>      | Maximum Load Current              | V <sub>IN</sub> = V <sub>OUT</sub> + 1 V                                  | 300 |      |     | mA                |

| I <sub>SHDN</sub>      | Input Shutdown Quiescent Current  | V <sub>EN</sub> = 0 V                                                     |     | 0.2  | 1   | μΑ                |

| Ι <sub>Q</sub>         | Input Quiescent Current           | V <sub>IN</sub> > 1.9 V, V <sub>EN</sub> > 1.2 V, I <sub>OUT</sub> = 0 mA |     | 14   | 25  | μΑ                |

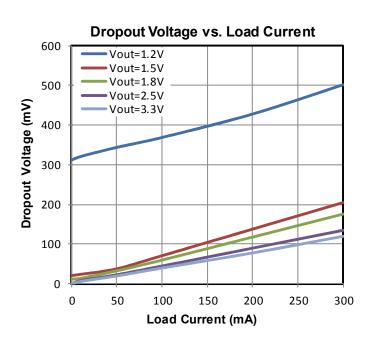

|                        | D (1)                             | I <sub>OUT</sub> = 100 mA                                                 |     | 50   | 100 | mV                |

| $V_{DROP}$             | Dropout Voltage (1)               | I <sub>OUT</sub> = 300 mA                                                 |     | 180  | 300 | mV                |

| I <sub>LMT</sub>       | Output Current Limit              | T <sub>A</sub> = 25°C                                                     | 310 | 500  |     | mA                |

| I <sub>SC</sub>        | Short-Circuit Current Limit       | V <sub>OUT</sub> = 0 V                                                    |     | 80   |     | mA                |

|                        |                                   | f = 100 Hz, I <sub>OUT</sub> = 1 mA                                       |     | 94   |     | dB                |

|                        |                                   | f = 1 kHz, I <sub>OUT</sub> = 1 mA                                        |     | 90   |     | dB                |

|                        |                                   | f = 10 kHz, I <sub>OUT</sub> = 1 mA                                       |     | 84   |     | dB                |

|                        |                                   | f = 100 kHz, I <sub>OUT</sub> = 1 mA                                      |     | 71   |     | dB                |

|                        |                                   | f = 1 MHz, I <sub>OUT</sub> = 1 mA                                        |     | 60   |     | dB                |

| PSRR                   | PSRR Power Supply Rejection Ratio | f = 100 Hz, I <sub>OUT</sub> = 20 mA                                      |     | 84   |     | dB                |

|                        |                                   | f = 1 kHz, I <sub>OUT</sub> = 20 mA                                       |     | 83   |     | dB                |

|                        |                                   | f = 10 kHz, I <sub>OUT</sub> = 20 mA                                      |     | 77   |     | dB                |

|                        |                                   | f = 100 kHz, I <sub>OUT</sub> = 20 mA                                     |     | 60   |     | dB                |

|                        |                                   | f = 1 MHz, I <sub>OUT</sub> = 20 mA                                       |     | 58   |     | dB                |

|                        |                                   | BW = 10 Hz to 100 kHz, I <sub>OUT</sub> = 1 mA                            |     | 10   |     | μV <sub>RMS</sub> |

| $e_N$                  | Output Noise Voltage              | BW = 10 Hz to 100 kHz, I <sub>OUT</sub> = 300 mA                          |     | 6.5  |     | μV <sub>RMS</sub> |

| R <sub>DISCHARGE</sub> | Output Discharge Resistance       | V <sub>EN</sub> < V <sub>IL</sub> (output disable)                        |     | 60   |     | Ω                 |

| V <sub>IL</sub>        | EN Input Logic Low Voltage        | $V_{IN}$ = 1.8 V to 5.5 V, $V_{EN}$ falling until the output is disabled  |     |      | 0.4 | V                 |

| V <sub>IH</sub>        | EN Input Logic High Voltage       | $V_{IN}$ = 1.8 V to 5.5 V, $V_{EN}$ rising until the output is enabled    | 1   |      |     | V                 |

|                        |                                   | V <sub>IN</sub> = 5.5 V ,V <sub>EN</sub> = 0 V                            |     | 0.01 | 1   | μΑ                |

| I <sub>EN</sub>        | EN Input leakage current          | V <sub>IN</sub> = 5.5 V ,V <sub>EN</sub> = 5.5 V                          |     | 5.5  |     | μΑ                |

| T <sub>SHDN</sub>      | Thermal shutdown threshold        | V <sub>IN</sub> = 2.8 V, T <sub>J</sub> rising                            |     | 155  |     | °C                |

| T <sub>HYS</sub>       | Thermal shutdown hysteresis       | V <sub>IN</sub> = 2.8 V, T <sub>J</sub> falling from shutdown             | 1   | 15   |     | °C                |

### NOTE:

(1)  $V_{DROP}$  is measured for devices with  $V_{OUT} \geq 1.5 \ V.$

## **ELECTRICAL CHARACTERISTICS (Continued)**

$T_A$  = +25°C,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F, unless otherwise noted.

| Symbol             | Parameter                    | Test Conditions                                                                                                    | Min | Тур | Max | Unit |

|--------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                    | Line transient               | $V_{IN} = (V_{OUT(NOM)} + 1 V) \text{ to}$<br>$(_{VOUT(NOM)} + 1.6 V) \text{ in } 10 \mu\text{s}$                  |     | 10  |     | mV   |

| ΔV <sub>OUT</sub>  | Line transient               | $V_{IN} = (V_{OUT(NOM)} + 1.6 \text{ V}) \text{ to}$<br>$(V_{OUT(NOM)} + 1 \text{ V}) \text{ in } 10  \mu\text{s}$ |     | 10  |     | mV   |

|                    | Load transient               | I <sub>OUT</sub> = 1 mA to 300 mA in 10 μs                                                                         |     | 20  |     | mV   |

|                    | Load transient               | I <sub>OUT</sub> = 300 mA to 1 mA in 10 μs                                                                         |     | 20  |     | mV   |

| Overshoot          | Overshoot on start-up        | Stated as percentage of V <sub>OUT(NOM)</sub>                                                                      |     |     | 5   | %    |

| T <sub>D(ON)</sub> | Output Turn-on Delay<br>Time | From $V_{EN} > V_{IH}$ to $V_{OUT} = 95\%$ of $V_{OUT(NOM)}$                                                       |     | 150 | 250 | μs   |

## **APPLICATION CIRCUITS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

## **PACKAGE OUTLINE**

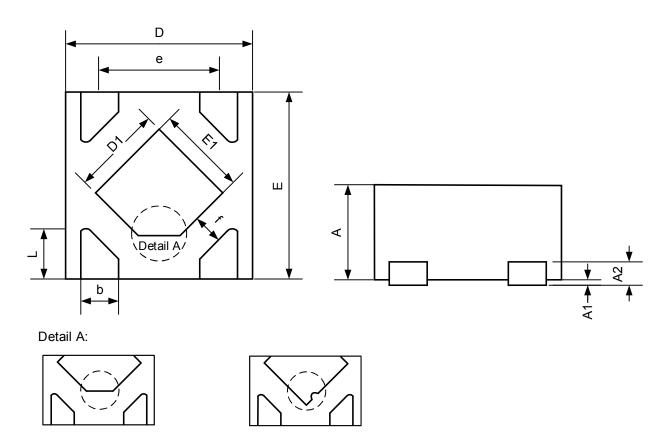

## **UTDFN1.0 × 1.0-4**

Note: Detail A has two kinds of shapes

| Cumbal | Dimensions In Millimeters |          |       |  |

|--------|---------------------------|----------|-------|--|

| Symbol | Min                       | Mod      | Max   |  |

| A      | 0.370                     | 0.400    | 0.430 |  |

| A1     | 0.000                     | 0.020    | 0.050 |  |

| A2     |                           | 0.100REF |       |  |

| D      | 0.950                     | 1.000    | 1.050 |  |

| D1     | 0.430                     | 0.480    | 0.530 |  |

| Е      | 0.950                     | 1.000    | 1.050 |  |

| E1     | 0.430                     | 0.480    | 0.530 |  |

| b      | 0.170                     | 0.220    | 0.270 |  |

| е      | 0.650BSC                  |          |       |  |

| f      | 0.190                     | 0.195    | 0.200 |  |

| L      | 0.200                     | 0.250    | 0.300 |  |

## **PACKAGE OUTLINE**

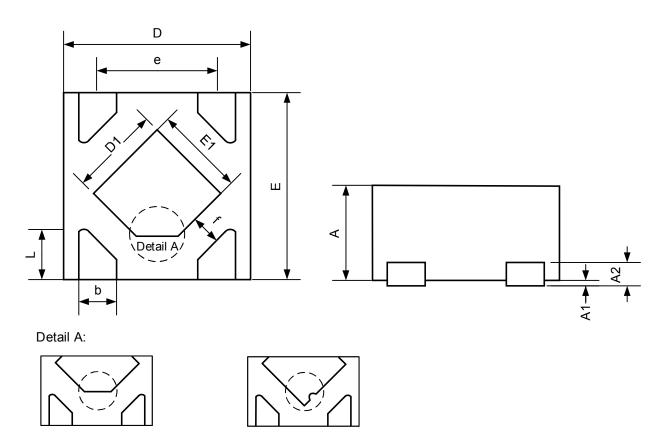

## **DFN1.0 × 1.0-4**

Note: Detail A has two kinds of shapes

| Symbol | Dimensions In Millimeters |          |       |  |

|--------|---------------------------|----------|-------|--|

| Symbol | Min                       | Mod      | Max   |  |

| А      | 0.450                     | 0.500    | 0.550 |  |

| A1     | 0.000                     | 0.025    | 0.050 |  |

| A2     |                           | 0.125REF |       |  |

| D      | 0.950                     | 1.000    | 1.050 |  |

| D1     | 0.380                     | 0.480    | 0.580 |  |

| E      | 0.950                     | 1.000    | 1.050 |  |

| E1     | 0.380                     | 0.480    | 0.580 |  |

| b      | 0.150                     | 0.200    | 0.250 |  |

| е      | 0.650BSC                  |          |       |  |

| f      | 0.190                     | 0.195    | 0.200 |  |

| L      | 0.150                     | 0.250    | 0.350 |  |

## **PACKAGE OUTLINE**

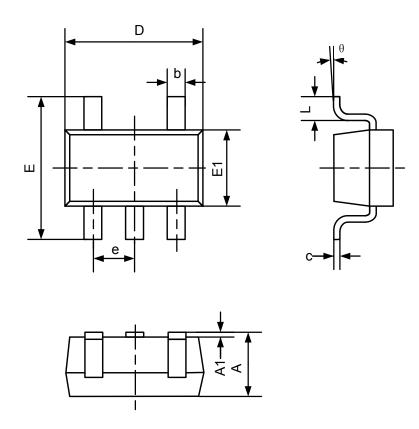

## SOT23-5

| Symbol | Dimensions In Millimeters |       |  |

|--------|---------------------------|-------|--|

| Symbol | Min                       | Max   |  |

| A      | 0.700                     | 1.250 |  |

| A1     | 0.000                     | 0.100 |  |

| b      | 0.300                     | 0.500 |  |

| С      | 0.100                     | 0.200 |  |

| D      | 2.820                     | 3.020 |  |

| E      | 2.650                     | 2.950 |  |

| E1     | 1.500                     | 1.700 |  |

| е      | 0.950BSC                  |       |  |

| L      | 0.300                     | 0.600 |  |

| θ      | 0°                        | 8°    |  |

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Linear Voltage Regulators category:

Click to view products by Suntek manufacturer:

Other Similar products are found below:

LV56831P-E LV5684PVD-XH MCDTSA6-2R L7815ACV-DG PQ3DZ53U LV56801P-E L78L05CZ/1SX L78LR05DL-MA-E 636416C

714954EB ZMR500QFTA LV5680P-E L78M15CV-DG L79M05T-E MIC5283-5.0YML-T5 TLS202A1MBVHTSA1 L78LR05D-MA-E

NCV317MBTG NTE7227 MP2018GZD-33-P MP2018GZD-5-P LV5680NPVC-XH LT1054CN8 MP2018GZD-5-Z MP2018GZD-33-Z

MD57E21WB6 MD57E28WB6 TPMIC5365-3.3YC5 TP6211C33R5G WL2810D33-4/TR WL2815D33-4/TR ZTS6538SE BL9161G33BADRN TP2036-3.3YC5G TP142C33C5 TPS71733DCKR-TP SA21345AFCA AW37030D180DNR MC78L06BP-AP

TA48LS05F(TE85L,F) TA78L12F(TE12L,F) TC47BR5003ECT TCR2LN12,LF(S TCR2LN28,LF(S TCR2LN30,LF(S TCR3DF295,LM(CT TCR3DF40,LM(CT TPS549B22RVFT L78M12ABDT LM7812SX/NOPB