### Single 2-Input Exclusive-OR Gate

#### www.sot23.com.tw

#### **General Descrition**

This single 2-input exclusive-OR gate is designed for 1.65-V to 5.5-V  $V_{\text{CC}}$  operation.

The NC7SZ86 performs the Boolean function Y=A  $\oplus$  B or Y= $\overline{A}B+A\overline{B}$  in positive logic.

A common application is as a true/complement element. If the input is low, the other input is reproduced in true form at the output. If the input is high, the signal on the other input is reproduced inverted at the output.

This device is fully specified for partial-power-down applications using  $l_{\text{off}}$ . The  $l_{\text{off}}$  circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

#### **Features**

- Supports 5V Vcc Operation

- Inputs Accept Voltages to 5.5 V

- Max t<sub>pd</sub> of 4 ns at 3.3 V

- Low Power Consumption, 10µA Max Icc

- ±24mA Output Drive at 3.3V

- Ioff Supports Partial-Power-Down Mode

#### **Applications**

- Wireless Headsets

- Motor Drives and Controls

- TVs

- Set-Top Boxes

- Audio

### Ordering Information

| ORDER NUMBER | PACKAGE DESCRIPTION | PACKAGE OPTION     |

|--------------|---------------------|--------------------|

| NC7SZ86M5X   | SOT23-5             | Tape and Reel,3000 |

| NC7SZ86P5X   | SOT353              | Tape and Reel,3000 |

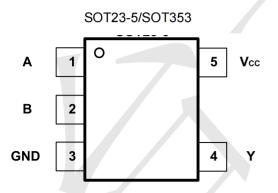

### **Pin Configuration**

### Marking

NC7SZ08M5X Marking:7Z86D NC7SZ08P5X Marking:Z86C

## Single 2-Input Exclusive-OR Gate

www.sot23.com.tw

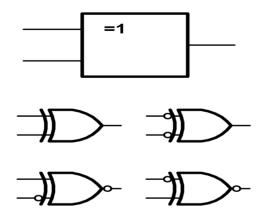

#### **Logic Diagram**

#### **Function Table**

| Inputs |   | Output |  |

|--------|---|--------|--|

| Α      | В | Y      |  |

| L      | L | L      |  |

| L      | Н | Н      |  |

| Н      | L | H      |  |

| Н      | Н | L      |  |

### **Absolute Maximum Ratings**

|                  | Parameter                                | Min                                   | Max.                 | Unit |        |

|------------------|------------------------------------------|---------------------------------------|----------------------|------|--------|

| Vcc              | Supply volt                              | age range                             | -0.5                 | 6.5  | \<br>\ |

| Vı               | Input volta                              | ge range                              | -0.5                 | 6.5  | V      |

| Vo               | Voltage range applied to any output in t | the high-impedance or power-off state | -0.5                 | 6.5  | \ \    |

| Vo               | Voltage range applied to any of          | -0.5                                  | V <sub>CC</sub> +0.5 | V    |        |

| I <sub>IK</sub>  | Input clamp current                      | Input clamp current V <sub>I</sub> <0 |                      |      | mA     |

| I <sub>OK</sub>  | Output clamp current                     | V <sub>0</sub> <0                     |                      | -50  | mA     |

| lo               | Continuous or                            |                                       | ±50                  | mA   |        |

|                  | Continuous current to                    |                                       | ±100                 | mA   |        |

| $T_{J}$          | Junction temperature under bias          |                                       |                      | 150  | ٥̈́    |

| T <sub>stg</sub> | Storage tempe                            | erature range                         | -65                  | 150  | °C     |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability..

<sup>(2)</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

## Single 2-Input Exclusive-OR Gate

www.sot23.com.tw

### **ESD Ratings**

|                                | E                                | VALUE                     | UNIT |   |

|--------------------------------|----------------------------------|---------------------------|------|---|

| V/CCD) Flootrootetis disabassa | Human-body model (HBM)           | 4K                        | V    |   |

| V(ESD)                         | V(ESD)   Electrostatic discharge | Charge device model (CDM) | 2K   | V |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

Over operating free-air temperature range (unless otherwise noted)

| Symbol             | Param                              | Min.                                  | Max.                 | Unit                 |      |  |

|--------------------|------------------------------------|---------------------------------------|----------------------|----------------------|------|--|

| Vcc                | Supply '                           | Voltage                               | 1.65                 | 5.5                  | V    |  |

|                    | V <sub>CC</sub> =1.65V to1.95V     | V <sub>CC</sub> =1.65V to1.95V        | 0.65×V <sub>CC</sub> |                      |      |  |

| V <sub>IH</sub> Hi | Link lavel innut veltage           | V <sub>CC</sub> =2.3V to 2.7V         | 1.7                  |                      |      |  |

|                    | High-level input voltage           | V <sub>CC</sub> =3V to 3.6V           | 2                    |                      | V    |  |

|                    |                                    | V <sub>CC</sub> =4.5V to 5.5V         | 0.7×V <sub>CC</sub>  |                      |      |  |

|                    |                                    | V <sub>CC</sub> =1.65V to1.95V        |                      | 0.35×V <sub>CC</sub> |      |  |

| \                  | Lave lavel inner trueltage         | V <sub>CC</sub> =2.3V to 2.7V         |                      | 0.7                  | ] ,, |  |

| $V_{IL}$           | Low-level input voltage            | V <sub>CC</sub> =3V to 3.6V           |                      | 0.8                  | V    |  |

|                    |                                    | V <sub>CC</sub> =4.5V to 5.5V         |                      | 0.3×V <sub>CC</sub>  | ]    |  |

| Vı                 | Input v                            | oltage                                | 0                    | 5.5                  | V    |  |

| Vo                 | Output                             | voltage                               | 0                    | V <sub>CC</sub>      | V    |  |

|                    |                                    | V <sub>CC</sub> =1.65V                |                      | -4                   |      |  |

|                    |                                    | V <sub>CC</sub> =2.3V                 |                      | -8                   |      |  |

| I <sub>OH</sub>    | High-level output current          | ligh-level output current             |                      | -16                  | m/   |  |

|                    |                                    | V <sub>cc</sub> =3V                   |                      | -24                  | 1    |  |

|                    |                                    | V <sub>CC</sub> =4.5V                 |                      | -32                  | 1    |  |

|                    |                                    | V <sub>CC</sub> =1.65V                |                      | 4                    |      |  |

|                    |                                    | V <sub>CC</sub> =2.3V                 |                      | 8                    | 1    |  |

| I <sub>OL</sub>    | Low-level output current           |                                       |                      | 16                   | m/   |  |

|                    |                                    | V <sub>CC</sub> =3V                   |                      | 24                   | 1    |  |

|                    |                                    | V <sub>CC</sub> =4.5V                 |                      | 32                   |      |  |

|                    |                                    | V <sub>CC</sub> =1.8V±0.15V,2.5V±0.2V |                      | 20                   |      |  |

| Δt/Δν              | Input transition rise or fall rate | V <sub>CC</sub> =3.3V±0.3V            |                      | 10                   | ns/\ |  |

|                    |                                    | V <sub>CC</sub> =5V±0.5V              |                      | 5                    |      |  |

| TA                 | Operating free-                    | Operating free-air temperature        |                      | 125                  | °C   |  |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## Single 2-Input Exclusive-OR Gate

www.sot23.com.tw

#### **Electrical Characteristics**

FULL=-40°C to +125°C, Typical values are at TA = +25°C. (unless otherwise noted)

| Parameters                 | Symbol           | Conditions                                                                      | Vcc           | T <sub>A</sub> | Min.    | Тур. | Max. | Unit |

|----------------------------|------------------|---------------------------------------------------------------------------------|---------------|----------------|---------|------|------|------|

|                            |                  | I <sub>OH</sub> = -100μA                                                        | 1.65V to 5.5V |                | Vcc-0.1 |      |      |      |

|                            |                  | I <sub>OH</sub> = -4mA                                                          | 1.65          |                | 1.2     |      |      |      |

| Lligh lovel output voltage | \ <u>/</u>       | I <sub>OH</sub> = -8mA                                                          | 2.3           |                | 1.9     |      |      |      |

| High-level output voltage  | V <sub>он</sub>  | I <sub>OH</sub> = -16mA                                                         |               | FULL           | 2.4     |      |      | V    |

|                            |                  | I <sub>OH</sub> = -24mA                                                         | 3             |                | 2.3     |      |      |      |

|                            |                  | I <sub>OH</sub> = -32mA                                                         | 4.5           |                | 3.8     |      |      |      |

|                            |                  | I <sub>OL</sub> = 100μA                                                         | 1.65V to 5.5V |                |         |      | 0.1  |      |

|                            |                  | I <sub>OL</sub> = 4mA                                                           | 1.65          |                |         |      | 0.45 |      |

| Laveland autout valtage    | .,               | I <sub>OL</sub> = 8mA                                                           | 2.3           |                |         |      | 0.3  |      |

| Low-level output voltage   | $V_{OL}$         | I <sub>OL</sub> = 16mA                                                          |               | FULL           |         |      | 0.4  | V    |

|                            |                  | I <sub>OL</sub> = 24mA                                                          | 3             |                |         |      | 0.55 |      |

|                            |                  | I <sub>OL</sub> = 32mA 4.5                                                      | 4.5           |                |         |      | 0.55 |      |

| Input leakage current      | l <sub>1</sub>   | A or B input, VI = 5.5V or GND                                                  | 0V to 5.5V    | FULL           |         |      | ±5   | μA   |

|                            | I <sub>off</sub> | $V_1$ or $V_0 = 5.5V$                                                           | 0V            | FULL           |         |      | ±10  | μA   |

| Supply current             | Icc              | V <sub>I</sub> = 5.5 V or GND, I <sub>O</sub> = 0                               | 1.65V to 5.5V | FULL           |         |      | 15   | μA   |

|                            | ΔI <sub>CC</sub> | one input at V <sub>CC</sub> – 0.6 V,<br>other inputs at V <sub>CC</sub> or GND | 3V to 5.5V    | FULL           |         |      | 500  | μА   |

| Input capacitance          | Ci               | V <sub>I</sub> = V <sub>CC</sub> or GND                                         | 3.3V          | FULL           |         | 6    |      | pF   |

|                            |                  |                                                                                 | 1.8V          |                |         | 22   |      |      |

| Power dissipation          | 0                | 6 - 40 MHz                                                                      | 2.5V          | 0500           |         | 22   |      | pF   |

| capacitance                | C <sub>pd</sub>  | f= 10 MHz                                                                       | 3.3V          | <b>25</b> ℃    |         | 22   |      |      |

|                            |                  |                                                                                 | 5V            |                |         | 24   |      |      |

|                            |                  |                                                                                 | 1.8V±0.15V    |                | 2.1     |      | 9.1  |      |

|                            |                  | Any input to Y (output),                                                        | 2.5V±0.2V     | FULL           | 1       |      | 4.5  |      |

| Propagation delay time     |                  | C <sub>L</sub> =15pF                                                            | 3.3V±0.3V     |                | 0.6     |      | 4    |      |

|                            |                  |                                                                                 | 5V±0.5V       |                | 0.8     |      | 3.3  |      |

|                            | t <sub>pd</sub>  |                                                                                 | 1.8V±0.15V    |                | 3.5     |      | 12   | ns   |

|                            |                  | Any input to Y (output),                                                        | 2.5V±0.2V     |                | 1.8     |      | 7    | 1    |

|                            |                  | C <sub>L</sub> =30pF or 50pF                                                    | 3.3V±0.3V     | FULL           | 1.3     |      | 6    |      |

|                            |                  | 5V±0.5V                                                                         |               | 1              |         | 5    |      |      |

**Electrical specifications(continued)**

### Single 2-Input Exclusive-OR Gate

www.sot23.com.tw

#### **Detailed Description**

The NC7SZ86 device performs the Boolean function  $Y=\overline{A}B+A\overline{B}$  in positive logic. This single 2-input exclusive-OR gate is designed for 1.65V to 5.5V V<sub>CC</sub> operation.

A common application is as a true and complement element. If the input is low, the other input is reproduced in true form at the output. If the input is high, the signal on the other input is reproduced inverted at the output.

This device is fully specified for partial-power-down applications using l<sub>off</sub>. The l<sub>off</sub> circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

#### **Function Table**

| Inputs |   | Output |  |  |

|--------|---|--------|--|--|

| Α      | В | Y      |  |  |

| L      | L | L      |  |  |

| L      | Н | Н      |  |  |

| Н      | L | Н      |  |  |

| Н      | Н | L      |  |  |

#### **Application Note**

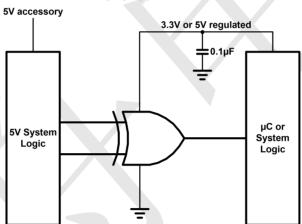

The NC7SZ86 device can accept input voltages up to 5.5 V at any valid Vcc which makes the device suitable for down translation. This feature of the NC7SZ86 makes it ideal for various bus interface applications.

**Typical Application Schematic**

This device uses CMOS technology and has balanced output drive. Take care to avoid bus contention because it can drive currents that would exceed maximum limits. The high drive will also create fast edges into light loads, so routing and load conditions should be considered to prevent ringing.

### Single 2-Input Exclusive-OR Gate

www.sot23.com.tw

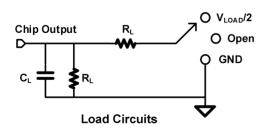

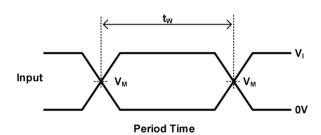

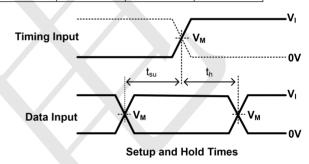

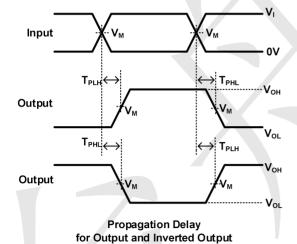

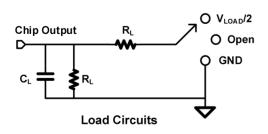

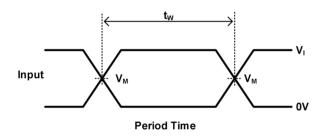

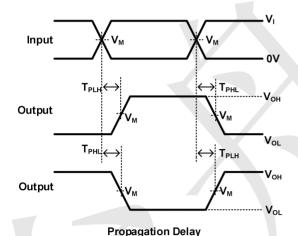

#### **Parameter Measurement Information**

| Test                               | S1    |

|------------------------------------|-------|

| T <sub>PHL</sub> /T <sub>PLH</sub> | OPEN  |

| T <sub>PLZ</sub> /T <sub>PZL</sub> | VLOAD |

| T <sub>PHZ</sub> /T <sub>PZH</sub> | GND   |

| Vcc        | Inp             | uts                            | V <sub>M</sub>     | V <sub>LAOD</sub> | CL   | RL  | VΔ    |

|------------|-----------------|--------------------------------|--------------------|-------------------|------|-----|-------|

| VCC        | Vı              | T <sub>r</sub> /T <sub>f</sub> | VM                 | V LAOD            | OL   | INL | VΔ    |

| 1.8V±0.15V | V <sub>CC</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 2×V <sub>CC</sub> | 15pF | 1ΜΩ | 0.15V |

| 2.5V±0.15V | Vcc             | ≤2ns                           | Vcc/2              | 2×V <sub>CC</sub> | 15pF | 1ΜΩ | 0.15V |

| 3.3V±0.15V | 3V              | ≤2.5ns                         | 1.5V               | 6V                | 15pF | 1ΜΩ | 0.3V  |

| 5V±0.15V   | V <sub>CC</sub> | ≤2.5ns                         | V <sub>CC</sub> /2 | 2×V <sub>CC</sub> | 15pF | 1ΜΩ | 0.3V  |

En Input  $T_{PZH} \longleftrightarrow$ → T<sub>PHZ</sub> Output T<sub>PZL</sub> Output

**Enable and Disable Times** Low-And High-Level Enabling

- Notes: A. C includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ . output is high, except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR 10 MHz, Z = 50.

- D. The outputs are measured one at a time, with one transition per measurement.

- E.  $t_{\text{PLZ}}$  and  $t_{\text{PHZ}}$  are the same as  $t_{\text{dis}}$  .

- G.  $t_{\text{PLH}}$  and  $t_{\text{PHL}}$  are the same as  $t_{\text{pd}}$  .

- H. All parameters and waveforms are not applicable to all device.

### Single 2-Input Exclusive-OR Gate

#### www.sot23.com.tw

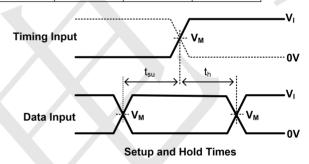

#### Parameter Measurement Information(continued)

| Test                               | S1    |  |

|------------------------------------|-------|--|

| T <sub>PHL</sub> /T <sub>PLH</sub> | OPEN  |  |

| T <sub>PLZ</sub> /T <sub>PZL</sub> | VLOAD |  |

| T <sub>PHZ</sub> /T <sub>PZH</sub> | GND   |  |

| Vcc        | Inputs          |                                | V <sub>M</sub>     | V <sub>LAOD</sub> | CL   | RL   | VΔ    |

|------------|-----------------|--------------------------------|--------------------|-------------------|------|------|-------|

| VCC        | Vı              | T <sub>r</sub> /T <sub>f</sub> | VM                 | V LAOD            | OL   | INL. | VΔ    |

| 1.8V±0.15V | V <sub>CC</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 2×V <sub>CC</sub> | 30pF | 1kΩ  | 0.15V |

| 2.5V±0.15V | Vcc             | ≤2ns                           | Vcc/2              | 2×V <sub>CC</sub> | 30pF | 500Ω | 0.15V |

| 3.3V±0.15V | 3V              | ≤2.5ns                         | 1.5V               | 6V                | 50pF | 500Ω | 0.3V  |

| 5V±0.15V   | V <sub>CC</sub> | ≤2.5ns                         | V <sub>CC</sub> /2 | 2×V <sub>CC</sub> | 50pF | 500Ω | 0.3V  |

Notes: A. C includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

for Output and Inverted Output

C. All input pulses are supplied by generators having the following characteristics: PRR 10 MHz, Z = 50.

Low-And High-Level Enabling

D. The outputs are measured one at a time, with one transition per

**Enable and Disable Times**

E.  $t_{\text{PLZ}}$  and  $t_{\text{PHZ}}$  are the same as  $t_{\text{dis}}$  .

measurement.

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- G.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

- H. All parameters and waveforms are not applicable to all device.

# Single 2-Input Exclusive-OR Gate

www.sot23.com.tw

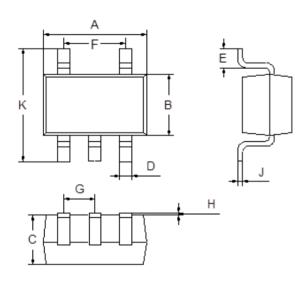

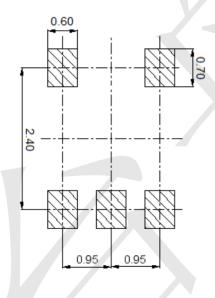

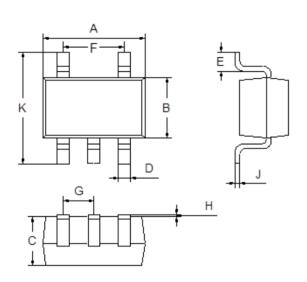

### Package Outline Dimensions (Unit: mm)

SOT23-5

| Dimension | Min. | Max. |

|-----------|------|------|

| Α         | 2.80 | 3.00 |

| В         | 1.50 | 1.70 |

| С         | 1.00 | 1.20 |

| D         | 0.35 | 0.45 |

| Е         | 0.35 | 0.55 |

| F         | 1.80 | 2.00 |

| G         | 0.90 | 1.00 |

| Н         | 0.02 | 0.10 |

| J         | 0.10 | 0.20 |

| K         | 2.60 | 3.00 |

### Mounting Pad Layout (Unit: mm)

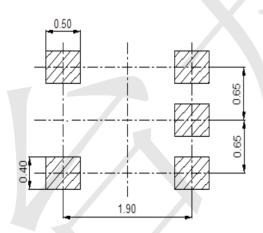

# Single 2-Input Exclusive-OR Gate

www.sot23.com.tw

### Package Outline Dimensions (Unit: mm)

**SOT353**

| Dimension | Min. | Max. |

|-----------|------|------|

| Α         | 2.00 | 2.20 |

| В         | 1.15 | 1.35 |

| С         | 0.85 | 1.05 |

| D         | 0.15 | 0.35 |

| E         | 0.25 | 0.40 |

| F         | 1.20 | 1.40 |

| G         | 0.60 | 0.70 |

| Н         | 0.02 | 0.10 |

| J         | 0.05 | 0.15 |

| K         | 2.20 | 2.40 |

### Mounting Pad Layout (Unit: mm)

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Logic Gates category:

Click to view products by TECH PUBLIC manufacturer:

Other Similar products are found below:

NLV17SG32DFT2G CD4068BE NL17SG86DFT2G NLX1G11AMUTCG NLX1G97MUTCG 74LS38 74LVC1G08Z-7 CD4025BE

NLV17SZ00DFT2G NLV17SZ126DFT2G NLV27WZ17DFT2G NLV74HC02ADR2G 74HC32S14-13 74LS133 74LVC1G32Z-7

74LVC1G86Z-7 NLV74HC14ADR2G NLV74HC20ADR2G NLVVHC1G09DFT1G NLX2G86MUTCG 74LVC2G32RA3-7

74LVC2G00HD4-7 NL17SG02P5T5G 74LVC2G86HK3-7 NLVVHC1G14DFT2G NLX1G99DMUTWG NLVVHC1G00DFT2G

NLV7SZ57DFT2G NLV74VHC04DTR2G NLV27WZ00USG NLU1G86CMUTCG NLU1G08CMUTCG NL17SZ32P5T5G

NL17SZ00P5T5G NL17SH02P5T5G 74AUP2G00RA3-7 NLVVHC1GT00DFT2G NLV74HC02ADTR2G NLX1G332CMUTCG

NLVHCT132ADTR2G NL17SG86P5T5G NL17SZ05P5T5G NLV74VHC00DTR2G NLVVHC1G02DFT1G NLV74HC86ADR2G

74LVC2G86RA3-7 NL17SZ38DBVT1G NLV18SZ00DFT2G NLVVHC1G07DFT1G NLVVHC1G02DFT2G