World Leading FPGA Based Products and Design Services

# **CONTENTS**

| CHAPTER 1    | OVERVIEW                             | 4  |

|--------------|--------------------------------------|----|

| 1.1 GENERAL  | DESCRIPTION                          | 4  |

| 1.2 Key Feat | TURES                                | 5  |

| 1.3 Board O  | OVERVIEW                             | 6  |

| 1.4 Block D  | IAGRAM                               | 7  |

| CHAPTER 2    | USING THE DE4 BOARD                  | 13 |

| 2.1 Configu  | RATION OPTIONS                       | 13 |

| 2.2 SETUP EL | EMENTS                               | 20 |

| 2.3 STATUS E | LEMENTS                              | 21 |

| 2.4 GENERAL  | USER INPUT/OUTPUT                    | 22 |

| 2.5 HIGH-SPE | EED MEZZANINE CARDS                  |    |

| 2.6 GPIO Ex  | PANSION HEADERS                      | 37 |

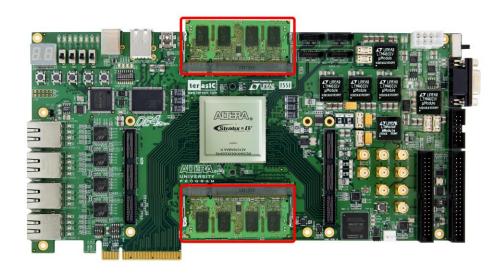

| 2.7 DDR2 SO  | D-DIMM                               | 41 |

| 2.8 USB OTO  | G                                    | 49 |

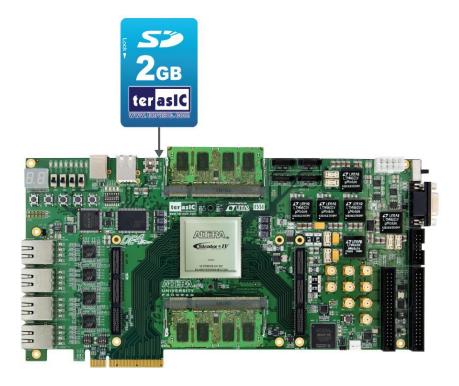

| 2.9 SD CARD  | )                                    | 52 |

| 2.10 CLOCK ( | CIRCUITRY                            | 53 |

| 2.11 PCI EXP | PRESS                                | 57 |

| 2.12 GIGABIT | ETHERNET (GIGE)                      | 60 |

| 2.13 SERIAL  | ATA (SATA)                           | 63 |

| 2.14 RS-232  | SERIAL PORT                          | 66 |

| 2.15 FLASH   | MEMORY                               | 66 |

| 2.16 SSRAM   | MEMORY                               | 68 |

| 2.17 I2C SER | IAL EEPROM                           | 70 |

| 2.18 TEMPER  | ATURE SENSOR                         | 70 |

| 2.19 POWER.  |                                      | 71 |

| CHAPTER 3    | CONTROL PANEL                        | 74 |

| 3.1 CONTROL  | PANEL SETUP                          | 74 |

| 3.2 Control  | LING THE LEDS AND 7-SEGMENT DISPLAYS | 78 |

| 3.3 SWITCH   | /BUTTON                              | 80 |

| 3.4 MEMORY   | CONTROLLER                           | 81 |

| 3.5 USB2.0 C | OTG                                | 84  |

|--------------|------------------------------------|-----|

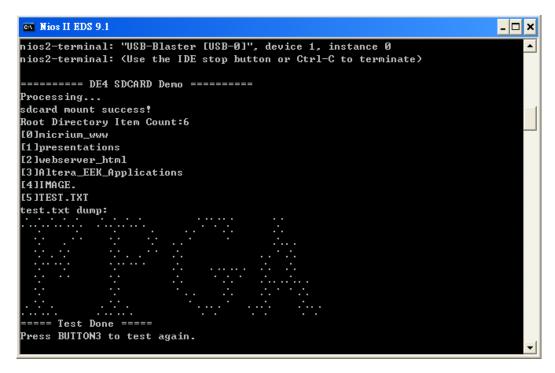

| 3.6 SD CARI  | D                                  | 85  |

| 3.7 TEMPERA  | ATURE MONITOR                      | 86  |

| 3.8 POWER    |                                    | 87  |

| 3.9 PLL      |                                    | 88  |

| 3.10 SATA    |                                    | 89  |

| 3.11 HSMC .  |                                    | 90  |

| 3.12 FAN     |                                    | 91  |

| CHAPTER 4    | DE4 SYSTEM BUILDER                 | 93  |

| 4.1 Introdu  | ICTION                             | 93  |

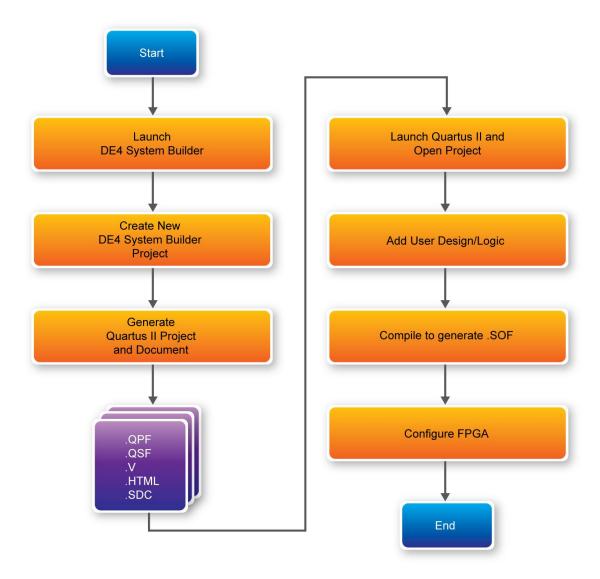

| 4.2 GENERAL  | L DESIGN FLOW                      | 94  |

| 4.3 Using DI | E4 System Builder                  | 95  |

| CHAPTER 5    | EXAMPLES OF ADVANCED DEMONSTRATION | 106 |

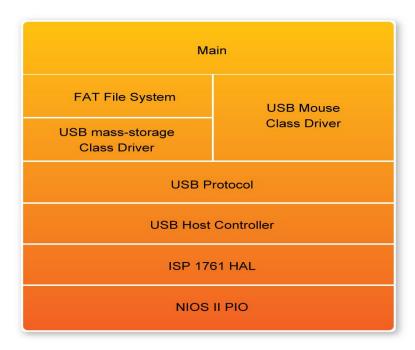

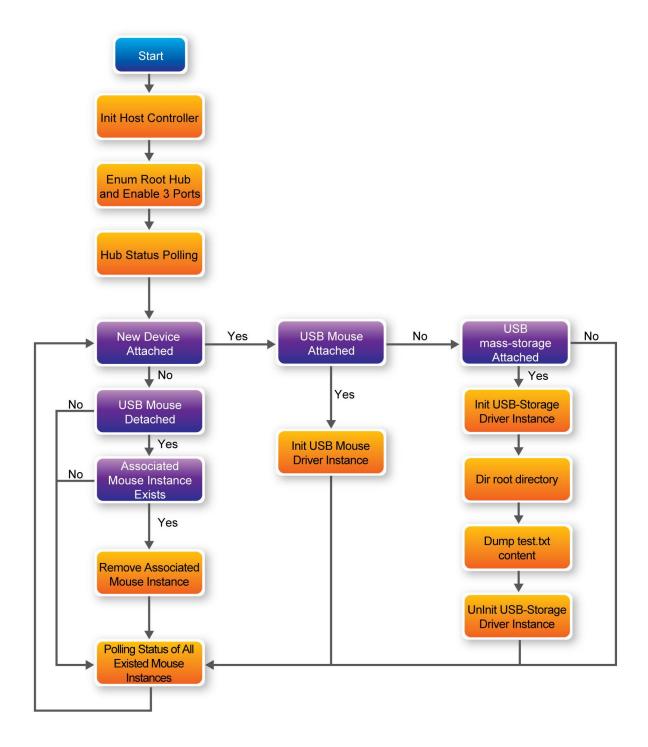

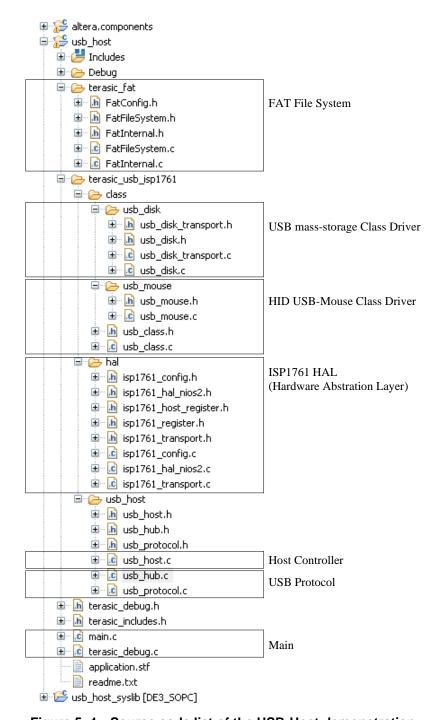

| 5.1 USB Hos  | ST                                 | 106 |

| 5.2 USB DEV  | VICE                               | 115 |

| 5.3 ETHERNE  | ET – SIMPLE SOCKET SERVER          | 119 |

| 5.4 SD CARD  | READER                             | 127 |

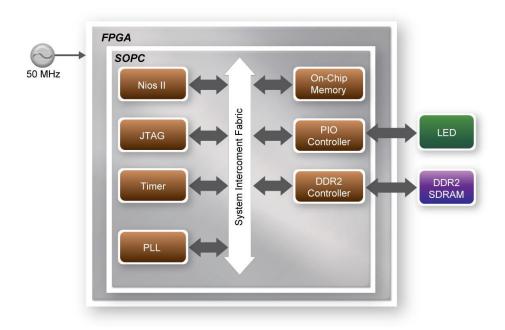

| 5.5 DDR2 SI  | DRAM                               | 131 |

| 5.6 EXTERNA  | AL CLOCK GENERATOR                 | 135 |

| 5.7 POWER M  | ÆASUREMENT                         | 142 |

| 5.8 WEB SER  | VER                                | 146 |

| 5.9 SERIAL A | TA (SATA)                          | 155 |

| 5.10 High-Si | PEED MEZZANINE CARD (HSMC)         | 156 |

| CHAPTER 6    | PCI EXPRESS REFERENCE DESIGN       | 159 |

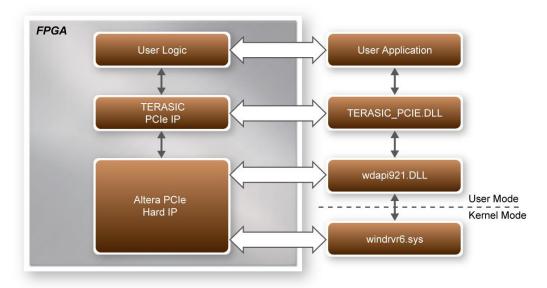

| 6.1 PCI Expr | RESS SYSTEM INFRASTRUCTURE         | 159 |

| 6.2 FPGA PC  | CI EXPRESS SYSTEM DESIGN           | 160 |

| 6.3 PC PCI E | EXPRESS SYSTEM DESIGN              | 164 |

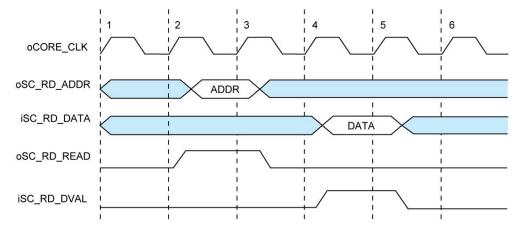

| 6.4 Fundami  | ENTAL COMMUNICATION                | 174 |

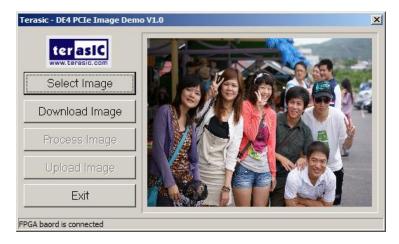

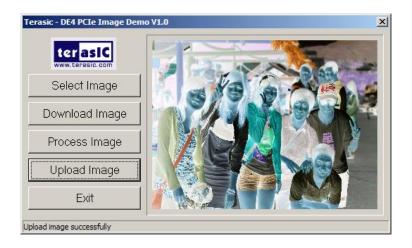

| 6.5 EXAMPLE  | E 2: IMAGE PROCESS APPLICATION     |     |

| ADDITIONAL   | INFORMATION                        | 185 |

# Chapter 1

# Overview

This chapter provides an overview of the DE4 Development Board and details the components and features of the board.

# 1.1 General Description

The DE4 Development Board provides the ideal hardware platform for system designs that demand high-performance, serial connectivity, and advanced memory interfacing. Developed specifically to address the rapidly evolving requirements in many end markets for greater bandwidth, improved jitter performance, and lower power consumption. The DE4 is powered by the Stratix® IV GX device and supported by industry-standard peripherals, connectors and interfaces that offer a rich set of features that is suitable for a wide range of compute-intensive applications.

The advantages of the Stratix® IV GX FPGA platform with integrated transceivers have allowed the DE4 to fully compliant with version 2.0 of the PCI Express standard. This will accelerate mainstream development of PCI Express-based applications enabling customers to deploy designs for a broad range of high-speed connectivity applications. The DE4 coupled with serial ATA (SATA) interfaces, offer a solution for developing storage applications. The DE4 delivers fully tested and supported connectivity targeted reference design that integrates built-in blocks for PCI Express, SATA transceiver verification testing, and Gigabit Ethernet protocol.

The DE4 is supported by multiple reference designs and two High-Speed Mezzanine Card (HSMC) connectors that allow scaling and customization with mezzanine daughter cards. For large-scale ASIC prototype development, it can be established by a cable connecting to multiple DE4/FPGA boards through the HSMC connectors.

It is highly recommended that users read the DE4 Getting Started Guide.pdf before using the DE4

board.

# **1.2 Key Features**

The following hardware is implemented on the DE4 board:

- Featured device

- o Altera Stratix® IV GX FPGA (EP4SGX230C2/EP4SGX530C2)

- Configuration status and set-up elements

- o Built-in USB Blaster circuit for programming

- o Fast passive parallel (FPP) configuration via MAX II CPLD and flash memory

- o Three External Programmable PLL timing chip

- Component and interfaces

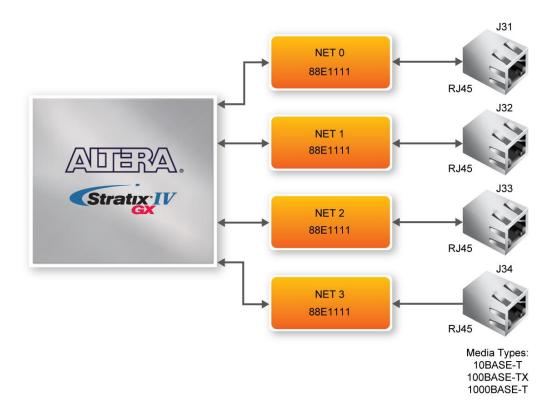

- o Four Gigabit Ethernet (GigE) with RJ-45 connector

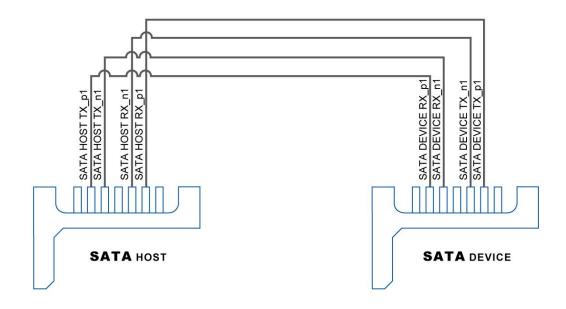

- o Two host and two device Serial ATA (SATA II) ports

- o Two HSMC connectors

- o Two 40-pin expansion headers

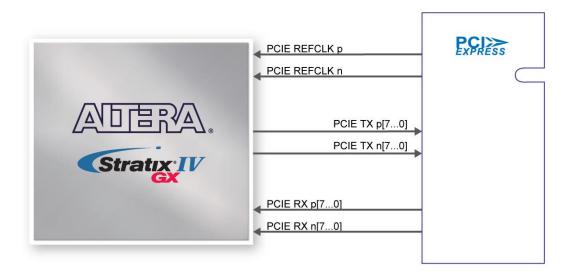

- o PCI Express 2.0 (x8 lane) connector

- Memory

- o DDR2 SO-DIMM socket

- o FLASH

- o SSRAM

- o SD Card socket

- o I2C EEPROM

- General user input/output:

- o 8 LEDs

- o 4 push-buttons and 4 slide switches

- o 8-position DIP switch

- o 2 seven-segment displays

- Clock system

- o On-board clock oscillators: 50MHz and 100MHz

- o SMA connectors for external clock input

- o SMA connectors for clock output

- Other interfaces

- USB 2.0 high-speed host/device OTG

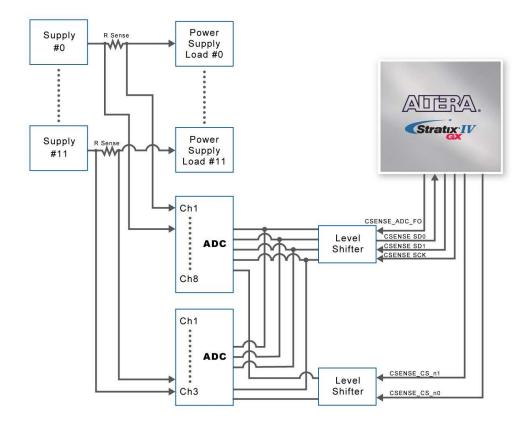

- o Current sensor for FPGA current measurement

- o Temperature sensor

## 1.3 Board Overview

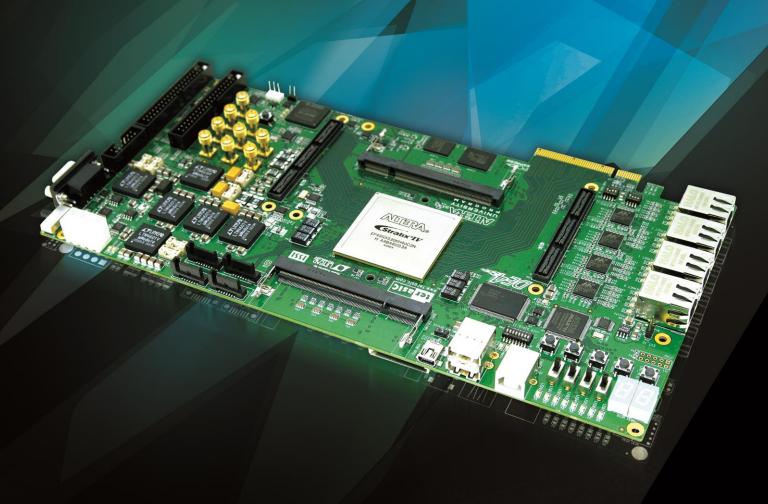

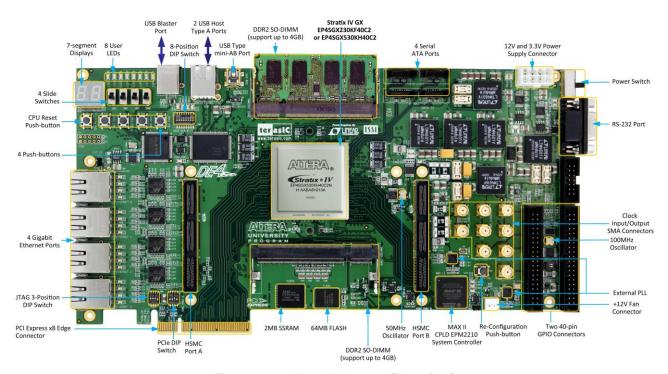

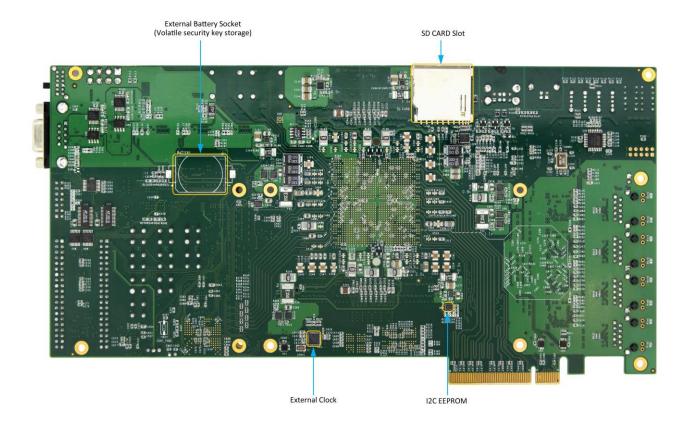

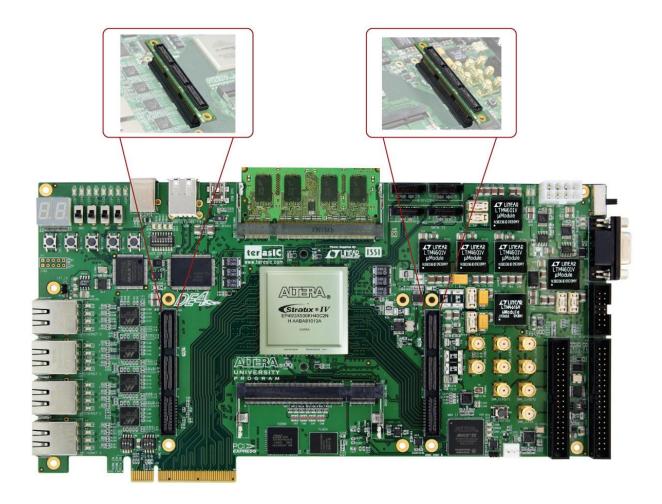

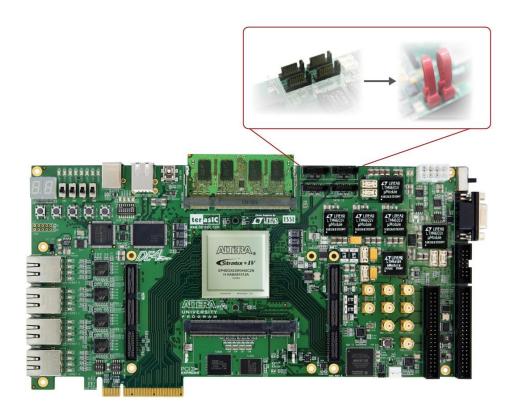

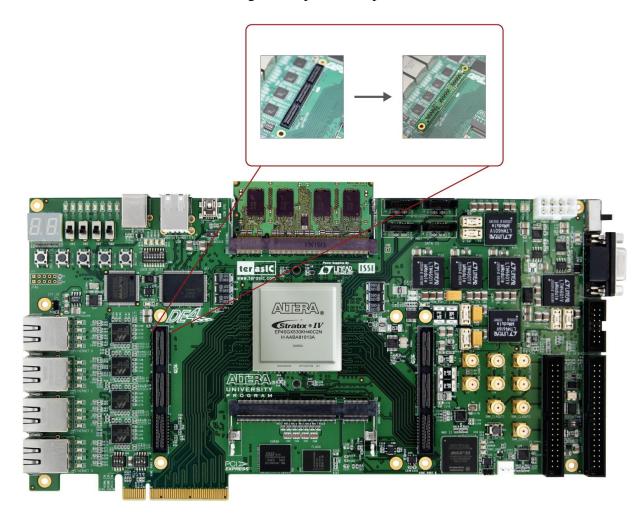

Figure 1–1 and Figure 1–2 is the top and bottom view of the DE4 board. It depicts the layout of the board and indicates the location of the connectors and key components. Users can refer to this figure for relative location when the connectors and key components are introduced in the following chapters.

Figure 1–1 The DE4 board (Top view)

Figure 1–2 The DE4 board (Bottom view)

# **1.4 Block Diagram**

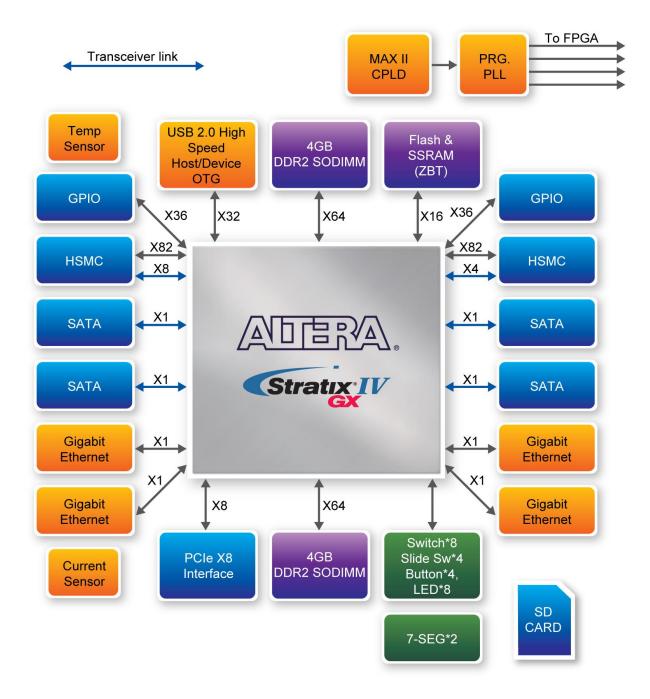

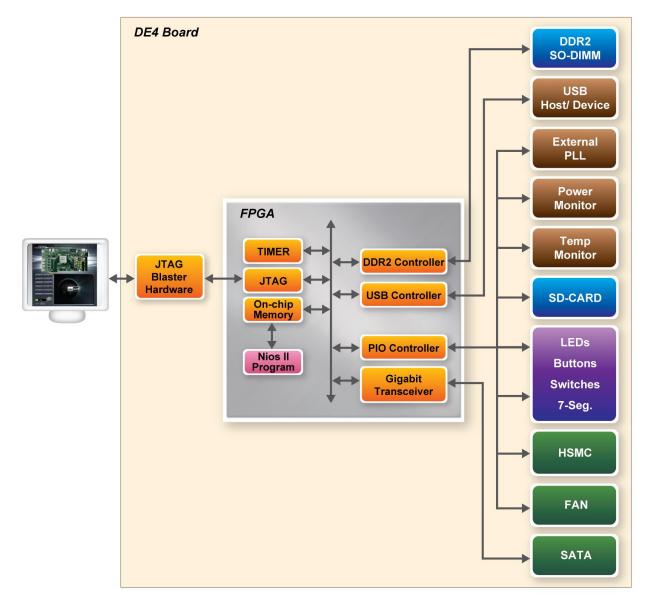

**Figure 1–3** shows the block diagram of the DE4 board. To provide maximum flexibility for the users, all key components are connected with the Stratix IV GX FPGA device. Thus, users can configure the FPGA to implement any system design.

Figure 1-3 Block diagram of the DE4 board

Below is more detailed information regarding the blocks in Figure 1–3.

#### Stratix IV GX FPGA

- EP4SGX230C2

- o 228,000 logic elements (LEs)

- o 17,133 total memory Kbits

- o 1,288 18x18-bit multipliers blocks

- o 2 PCI Express hard IP blocks

- o 744 user I/Os

- o 8 phase locked loops (PLLs)

- EP4SGX530C2

- o 531,200 logic elements (LEs)

- o 27,376K total memory Kbits

- o 1,024 18x18-bit multipliers blocks

- o 4 PCI Express hard IP Blocks

- o 744 user I/Os

- o 8 phase locked loops (PLLs)

## Configuration device and USB Blaster circuit

- MAXII CPLD EPM2210 System Controller and Fast Passive Parallel (FPP) configuration

- On-board USB Blaster for use with the Quartus II Programmer

- Programmable PLL timing chip configured via MAX II CPLD

- Support JTAG mode

## **Memory devices**

- 64MB Flash (32M x16) with a 16-bit data bus

- 2MB SSRAM (1M x 16)

- 2Kb EEPROM

#### Two DDR2 SO-DIMM sockets

- Up to 8GB capacity in total

- Maximum memory clock rate at 400MHz

- Theortical Bandwidth over 102Gbps

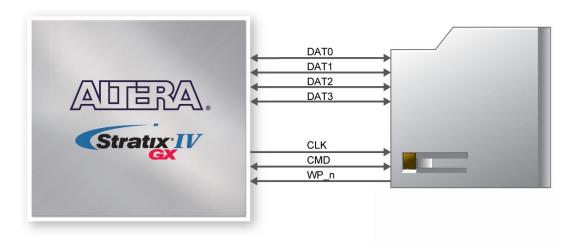

#### **SD** Card socket

Provides SPI and 4-bit SD mode for SD Card access

#### General user I/O

- 8 user controllable LEDs

- 2 seven-segment displays

- 8 user DIP switches

#### **Push-buttons**

- 4 user-defined inputs

- Normally high; generates one active-low pulse when the switch is pressed

#### Slide switches

- 4 slide switches for user-defined inputs

- When a switch is set to the DOWN or UP position, it causes logic 0 or 1, respectively.

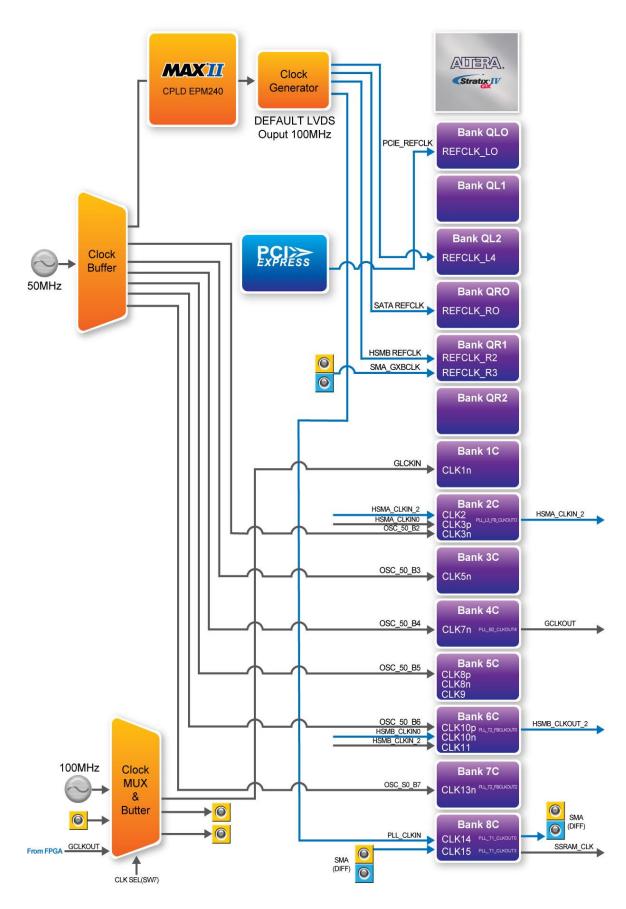

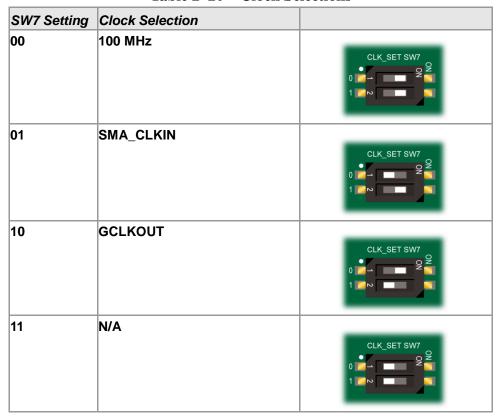

## **On-Board Clocking Circuitry**

- 50MHz/100MHz oscillator

- 2 SMA connector for external transceiver clock input

- 4 SMA connector for LVDS clock input/output

- 2 SMA connectors for clock output

• 1 SMA connector for external clock input

## **Four Serial ATA ports**

• SATA 3.0 standard 6Gbps signaling rate

## **Four Gigabit Ethernet ports**

Integrated 1.25GHz SERDES

## PCI Express x8 edge connector

- Support connection speed of Gen1 at 2.5Gbps/lane to Gen2 at 5.0Gbps/lane

- Connection established with PC motherboard with x8 or x16 PCI Express slot

## Two High Speed Mezzanine Card (HSMC)

- 2 female-HSMC connectors

- Total of 12 pairs CDR-based transceivers at data rate up to 8.5Gbps

- Total 38 LVDS transmitter channels at data rate up to 1.6Gbps, and 36 LVDS receiver channels

- I/O voltage 2.5V

## Two 40-pin expansion headers

- 72 FPGA I/O pins, as well as 4 power and ground lines, are brought out to two 40-pin expansion connectors

- 40-pin header is designed to accept a standard 40-pin ribbon cable used for IDE hard drives

- Compatible with I/O standard 3.3V

## **USB Host/Slave controller**

- Complies fully with Universal Serial Bus Specification Rev. 2.0

- Support data transfer at high-speed, full-speed, and low-speed

- Support both USB host and device

- Three USB ports (one type mini-AB for host/device and two type A for host)

- Support Nios II with the Terasic driver

## **Power**

- Standalone DC inputs 12V and 3.3V

- PCI Express edge connector power

- Optional PCI Express external power source

- On-Board power measurement circuitry

# Chapter 2

# Using the DE4 Board

This chapter gives instructions for using the DE4 board and its components.

It is strongly recommended that users read the *DE4 Getting Started Guide.pdf* before using the DE4 board. The document is located in the *Usermanual* folder on the **DE4 System CD**. The contents of the document include the following:

- Introduction to the DE4 development board

- DE4 development kit contents

- Key features

- Before you begin

- Software Installation

- Development board setup

- Programming the Stratix IV GX device on the DE4 board

- Programming through the Flash memory device

# **2.1 Configuration Options**

## ■ JTAG FPGA Programming over USB-Blaster

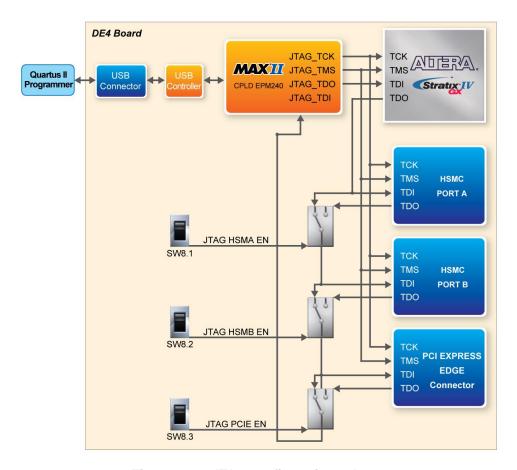

The USB-blaster is implemented on the DE4 board to provide JTAG configuration through onboard USB-to-JTAG configuration logic using a type-B USB connector, a FTDI USB 2.0 Controller, and an Altera MAX II CPLD. Current configuration will be lost when the power is turned off. **Figure 2–1** illustrates the JTAG configuration scheme for the DE4.

To download a configuration bit stream into the Stratix IV GX FPGA, perform the following steps:

- Make sure that power is provided to the DE4 board

- Connect the USB cable supplied directly to the USB Blaster port of the DE4 board

- The FPGA can now be programmed in the Quartus II Programmer by selecting a configuration bit stream file with the .sof filename extension.

Please refer to DE4 Getting Started Guide.pdf for more detailed procedure of FPGA programming.

Figure 2–1 JTAG configuration scheme

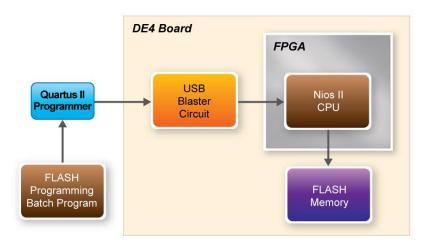

### **■** Flash Programming

The DE4 development board contains a common flash interface (CFI) flash memory to meet the demands for a larger FPGA configuration storage. The parallel flash loader (PFL) feature in MAX II devices provides an efficient method to program CFI flash memory devices through the JTAG

interface and the logic to control configuration from the flash memory device to the Stratix IV GX FPGA. **Figure 2–2** depicts the connection setup between the CFI flash memory, Max II CPLD, and Stratix IV GX.

Please refer to the *DE4 Getting Started Guide.pdf* for the basic programming instruction on parallel flash loader on the CFI flash memory.

Figure 2-2 Flash programming scheme

## **■** Programming Flash Memory using batch file

The DE4 provides a program\_flash batch file (\demonstrations\de4\_<Stratix device>\de4\_board\_update\_portal\demo\_batch\Program\_flash) to limit the steps that are taken when users program the flash memory on the DE4.

Software Requirements:

- Quartus II 9.1 SP2 or later

- Nios II IDE tools 9.1 SP2 or later

Program\_flash folder contents:

- Program\_flash.bat

- Program\_flash.pl

- Program\_flash.sh

• de4\_board\_update\_portal.sof

Before you use the program\_flash.bat batch file to program the flash memory, make sure the DE4 is turned on and USB cable is connected to the USB blaster port (J5). In addition, place the .sof and .elf file (optional) you wish to program/convert in the Program\_flash directory.

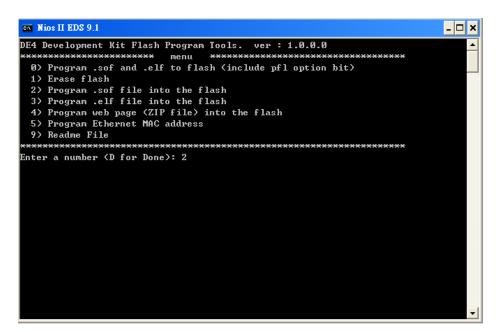

Programming Flash Memory with .sof using Program\_flash.bat

- 1. Launch the program\_flash.bat batch file from the directory (\demonstrations\de4\_<Stratix device>\de4\_board\_update\_portal\demo\_batch\Program\_flash) of the **DE4 system CD-ROM**.

- 2. The flash program tool shows the menu options.

Figure 2-3 Flash program tools

3. Select option 2.

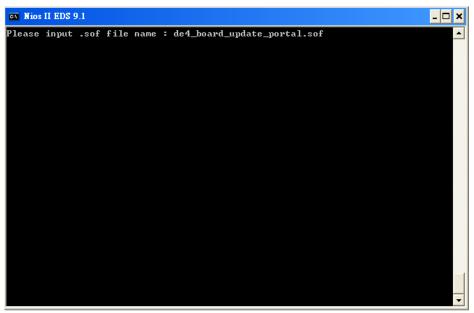

Figure 2–4 Option 2

4. Enter the .sof file name to be programmed onto the flash memory.

Figure 2-5 Enter .sof name to be program

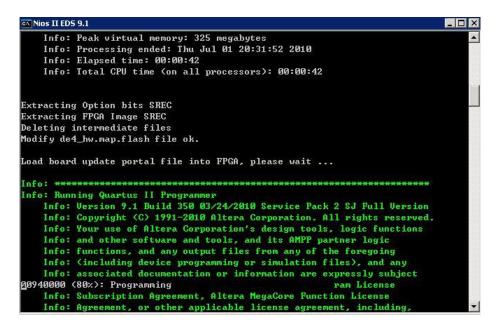

5. The following lines will appear during flash programming: 'Extracting Option bits SREC', 'Extracting FPGA Image SREC', and 'Deleting intermediate files'. If these lines don't appear on the windows command, programming on the flash memory is not successfully setup. Please make sure Quartus II 9.1 SP2 and Nios II 9.1 IDE SP2 or later is used.

Figure 2-6 Loading .sof file to be program

#### 6. Erasing flash.

```

ov Nios II EDS 9.1

_ 🗆 ×

Info: programming logic devices manufactured by Altera and sold by

Info: Altera or its authorized distributors. Please refer to the

Info: applicable agreement for further details.

Info: Processing started: Fri Jun 11 16:50:30 2010

Info: Command: quartus_pgm -c USB-Blaster[USB-01 -m jtag -o p;de4_board_update_p

rtal.sof

Info: Using programming cable "USB-Blaster [USB-0]"

Info: Started Programmer operation at Fri Jun 11 16:50:43 2010

Info: Configuring device index 1

Info: Device 1 contains JTAG ID code 0x024090DD

Info: Configuration succeeded -- 1 device(s) configured

Info: Successfully performed operation(s)

Info: Ended Programmer operation at Fri Jun 11 16:51:05 2010

Info: Quartus II Programmer was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 287 megabytes

Info: Processing ended: Fri Jun 11 16:51:05 2010

Info: Elapsed time: 00:00:35

Info: Total CPU time (on all processors): 00:00:12

Program flash, please wait a few minutes ...

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Resetting and pausing target processor: OK

Checksummed/read 106kB in 4.9s

Q0320000 (26%): Erasing

```

Figure 2-7 Erasing flash

#### 7. Programming flash.

```

_ 🗆 ×

ev Nios II EDS 9.1

Info: Altera or its authorized distributors.

Please refer to the

Info: applicable agreement for further details.

Info: Processing started: Fri Jun 11 16:50:30 2010

nfo: Command: quartus_pgm -c USB-Blaster[USB-0] -m jtag -o p;de4_board_update_p

rtal.sof

Info: Using programming cable "USB-Blaster [USB-01"

Info: Started Programmer operation at Fri Jun 11 16:50:43 2010

Info: Configuring device index 1

Info: Device 1 contains JTAG ID code 0x024090DD

Info: Configuration succeeded -- 1 device(s) configured

nfo: Successfully performed operation(s)

nfo: Ended Programmer operation at Fri Jun 11 16:51:05 2010

Info: Quartus II Programmer was successful. O errors, O warnings

Info: Peak virtual memory: 287 megabytes

Info: Processing ended: Fri Jun 11 16:51:05 2010

Info: Elapsed time: 00:00:35

Info: Total CPU time (on all processors): 00:00:12

Program flash, please wait a few minutes ...

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Resetting and pausing target processor: OK

Checksummed/read 106kB in 4.9s

Erased 11648kB in 86.7s (134.3kB/s)

00440000 (36%): Programming

```

Figure 2–8 Programming flash

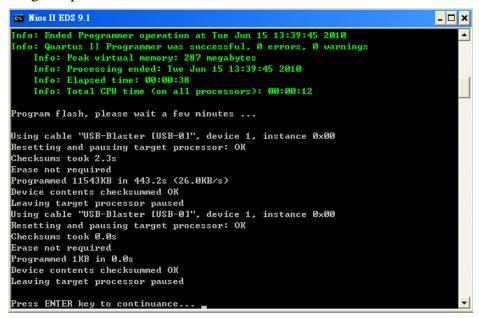

#### 8. Programming complete.

Figure 2-9 Programming flash complete

## 2.2 Setup Elements

#### **■** JTAG Control DIP Switch

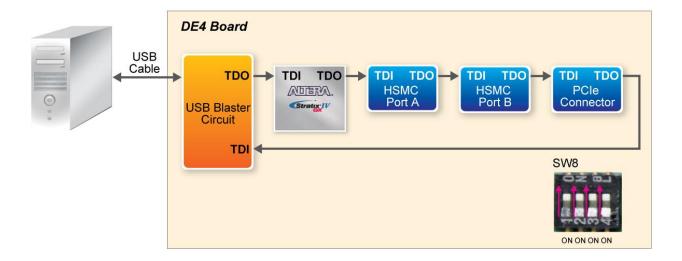

The JTAG control DIP switch is provided to either remove or include devices in the active JTAG chain. The JTAG signals (TDI and TDO) found on the HSMC connectors and PCIe interface can be enabled using a 3-position DIP switch. In the "OFF" position, the TDI and TDO signals are looped, similarly in the "ON" position, the JTAG signals are bypassed. **Table 2–1** lists the position of the DIP switch and their associated interface.

Table 2–1 SW8 JTAG Control DIP Switch

| Board Reference | Signal Name   | Description               | Default |

|-----------------|---------------|---------------------------|---------|

| CIMO 4          | JTAG HSMA EN  | On : Bypass HSMA          | Om      |

| SW8.1           | JIAG_NSWIA_EN | Off: HSMA In-chain        | On      |

| CIMO O          | ITAC LICMD EN | On: Bypass HSMB           | 0.0     |

| SW8.2           | JTAG_HSMB_EN  | Off: HSMB In-chain        | On      |

| CWO 2           | ITAC DOLE EN  | On: Bypass PCI Express    | 0.12    |

| SW8.3           | JTAG_PCIE_EN  | Off: PCI Express In-Chain | On      |

## **■** PCI Express Control DIP switch

The PCI Express Control DIP switch is provided to enable or disable different configurations of the PCIe Connector. Table 2–2 lists the switch controls and description.

Table 2–2 SW9 PCIe Control DIP Switch

| Board Reference | Signal Name      | Description                     | Default |

|-----------------|------------------|---------------------------------|---------|

| CWO 4           | PCIE_PRSNT2n_x1  | On : Enable x1 presence detect  | 0"      |

| SW9.1           | PCIE_PRSN12N_X1  | Off: Disable x1 presence detect | Off     |

| SW9.2           | PCIE PRSNT2n x4  | On : Enable x4 presence detect  | 044     |

| 3W9.Z           | PCIE_PRSN12II_X4 | Off: Disable x4 presence detect | Off     |

| CMO 3           | DOLE DECNITOR VO | On : Enable x8 presence detect  | 0.5     |

| SW9.3           | PCIE_PRSNT2n_x8  | Off: Disable x8 presence detect | On      |

# 2.3 Status Elements

The DE4 development board includes status LEDs. Please refer to Table 2–3 for the status of the LED indicator.

**Table 2–3 LED Indicators**

| Board Reference | LED Name                           | Description                                                                                                                                                                      |

|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D9              | 12-V Power                         | Illuminates when 12-V power is active.                                                                                                                                           |

| D10             | 3.3-V Power                        | Illuminates when 3.3-V power is active.                                                                                                                                          |

| D20             | CONF DONE                          | Illuminates when the FPGA is successfully configured. Driven by the MAX II CPLD EPM2210 System Controller.                                                                       |

| D18             | Loading                            | Illuminates when the MAX II CPLD EPM2210 System Controller is actively configuring the FPGA. Driven by the MAX II CPLD EPM2210 System Controller with the Embedded Blaster CPLD. |

| D19             | Error                              | Illuminates when the MAX II CPLD EPM2210 System Controller fails to configure the FPGA. Driven by the MAX II CPLD EPM2210 System Controller.                                     |

| D12             | USB<br>Blaster Circuit             | Illuminates when USB blaster circuit transmits or receives data.                                                                                                                 |

| D17             | HSMC<br>Port B Present             | Illuminates when the HSMC port B has a board or cable plugged-in such that pin 160 becomes grounded. Driven by the add-in card                                                   |

| D16             | HSMC<br>Port A Present             | Illuminates when the HSMC port A has a board or cable plugged-in such that pin 160 becomes grounded. Driven by the add-in card                                                   |

| RXD1            | UART_RXD/GPIO<br>Expansion 0 IO[7] | Illuminates when RS232 receives data or GPIO Expansion 0 IO[7] is transmits or receives.                                                                                         |

| TXD1            | UART_TXD/GPIO<br>Expansion 1 IO[9] | Illuminates when RS232 transmit data or GPIO Expansion 1 IO[9] is transmits or receives.                                                                                         |

| D15             | USB<br>Jack-Mini-USB-AB<br>Port    | Illuminates when USB Jack-Mini-USB port has a device.                                                                                                                            |

| D14 | USB_TYPE_A port<br>(Top USB)    | Illuminates when the USB_TYPE_A port has a device. |

|-----|---------------------------------|----------------------------------------------------|

| D13 | USB_TYPE_A port<br>(Bottom USB) | Illuminates when the USB_TYPE_A port has a device. |

# 2.4 General User Input/Output

#### **■** Push-buttons

The DE4 board includes six push-buttons that allow you to interact with the Stratix IV GX device. Each push-button provides a high logic level or a low logic level when it is not pressed or pressed, respectively. **Table 2–4** lists the board references, signal names and their corresponding Stratix IV GX device pin numbers.

Table 2–4 Push-button Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal Name | Description                              | I/O<br>Standard | Stratix IV GX Pin Number |

|--------------------|--------------------------|------------------------------------------|-----------------|--------------------------|

| PB1                | BUTTON0                  | High Logic Level when button not pressed | 3.0-V           | PIN_AH5                  |

| PB2                | BUTTON1                  | High Logic Level when button not pressed | 3.0-V           | PIN_AG5                  |

| PB3                | BUTTON2                  | High Logic Level when button not pressed | 3.0-V           | PIN_AG7                  |

| PB4                | BUTTON3                  | High Logic Level when button not pressed | 3.0-V           | PIN_AH8                  |

| PB5                | CPU_RESET_n              | FPGA reset                               | 2.5-V           | PIN_V34                  |

| PB6                | RE_CONFIGn               | Max II EPM2210 System re-configuration   | -               | -                        |

A CPU reset push-button (CPU\_RESET\_n) is an input to the Stratix IV GX device. It is intended to be the master reset signal for FPGA designs loaded into the Stratix IV GX device. The RE\_CONFIGn push-button is used to force a reboot on the MAX II EPM2210 CPLD device.

#### ■ Slide Switches and DIP Switch

There are also four slide switches and one 8-position DIP switch on the DE4 board to provide additional FPGA input control. Each switch is connected directly to a pin of the Stratix IV GX FPGA. When a slide switch is in the DOWN position or the UPPER position, it provides a low

logic level or a high logic level to the FPGA, respectively. For 8-position DIP switch, when a switch is in the DOWN position or the UPPER position, it provides a high logic level or a low logic level to the FPGA. Table 2–5 and Table 2–6 lists the signal names and their corresponding Stratix IV GX device pin numbers for slide switches and DIP switch respectively.

Table 2–5 Slide Switches Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal Name | Description                           | I/O<br>Standard | Stratix IV GX<br>Pin Number |

|--------------------|--------------------------|---------------------------------------|-----------------|-----------------------------|

| SW0                | SLIDE_SW0                | High logic level when SW in the UPPER | 2.5-V           | PIN_J7                      |

| SW1                | SLIDE_SW1                | position                              | 2.5-V           | PIN_K7                      |

| SW2                | SLIDE_SW2                |                                       | 3.0-V           | PIN_AK6                     |

| SW3                | SLIDE_SW3                |                                       | 2.5-V           | PIN_L7                      |

Table 2–6 DIP Switch Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal Name | Description                             | I/O<br>Standard | Stratix IV GX Pin Number |

|--------------------|--------------------------|-----------------------------------------|-----------------|--------------------------|

| SW6                | SW0                      | User-Defined DIP switch connected to    | 3.0-V           | PIN_AB13                 |

| SW6                | SW1                      | FPGA device. When the switch is in the  | 3.0-V           | PIN_AB12                 |

| SW6                | SW2                      | ON position, a logic 0 is selected.     | 3.0-V           | PIN_AB11                 |

| SW6                | SW3                      | Similarly when the switch is in the OFF | 3.0-V           | PIN_AB10                 |

| SW6                | SW4                      | position, a logic 1 is selected.        | 3.0-V           | PIN_AB9                  |

| SW6                | SW5                      |                                         | 3.0-V           | PIN_AC8                  |

| SW6                | SW6                      |                                         | 3.0-V           | PIN_AH6                  |

| SW6                | SW7                      |                                         | 3.0-V           | PIN_AG6                  |

#### **■** LEDs

The DE4 board consists of 8 user-controllable LEDs to allow status and debugging signals to be driven to the LEDs from the designs loaded into the Stratix IV GX device. Each LED is driven directly by the Stratix IV GX FPGA. The LED is turned on or off when the associated pins are driven to a low or high logic level, respectively. A list of the pin names on the FPGA that are connected to the LEDs is given in Table 2–7.

Table 2–7 User LEDs Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal<br>Name | Description                                     | I/O<br>Standard | Stratix IV GX<br>Pin Number |

|--------------------|-----------------------------|-------------------------------------------------|-----------------|-----------------------------|

| D1                 | LED0                        | User-Defined LEDs.                              | 2.5-V           | PIN_V28                     |

| D2                 | LED1                        | Driving a logic 0 on the I/O port turns the LED | 2.5-V           | PIN_W28                     |

| D3                 | LED2                        | ON. Driving a logic 1 on the I/O port turns the | 2.5-V           | PIN_R29                     |

| D4                 | LED3                        | LED OFF.                                        | 2.5-V           | PIN_P29                     |

| D5                 | LED4                        |                                                 | 2.5-V           | PIN_N29                     |

| D6                 | LED5                        |                                                 | 2.5-V           | PIN_M29                     |

| D7                 | LED6                        |                                                 | 2.5-V           | PIN_M30                     |

| D8                 | LED7                        |                                                 | 2.5-V           | PIN_N30                     |

## ■ 7-Segment Displays

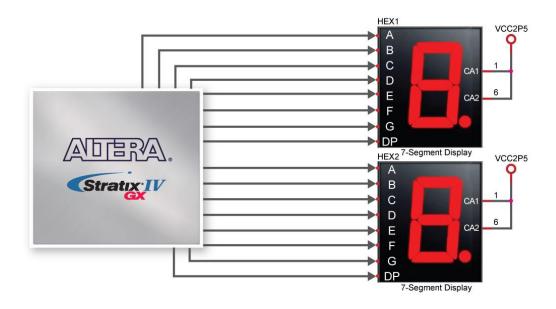

The DE4 board has two 7-segment displays. As indicated in the schematic in **Figure 2–10**, the seven segments are connected to pins of the Stratix IV GX FPGA. Applying a low or high logic level to a segment to light it up or turns it off.

Each segment in a display is identified by an index listed from 0 to 6 with the positions given in **Figure 2–11**. In addition, the decimal point is identified as DP. **Table 2–8** shows the mapping of the FPGA pin assignments to the 7-segment displays.

Figure 2-10 Connection between 7-segment displays and Stratix IV GX FPGA

Figure 2–11 Position and index of each segment in a 7-segment display

Table 2–8 7-Segment Display Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal<br>Name | Description                                           | I/O<br>Standard | Stratix IV GX<br>Pin Number |

|--------------------|-----------------------------|-------------------------------------------------------|-----------------|-----------------------------|

| HEX1               | SEG1_D0                     | User-Defined 7-Segment Display. Driving a logic 0 on  | 2.5-V           | PIN_E31                     |

| HEX1               | SEG1_D1                     | the I/O port turns the 7-segment signal ON. Driving a | 2.5-V           | PIN_F31                     |

| HEX1               | SEG1_D2                     | logic 1 on the I/O port turns the 7-segment signal    | 2.5-V           | PIN_G31                     |

| HEX1               | SEG1_D3                     | OFF.                                                  | 2.5-V           | PIN_C34                     |

| HEX1               | SEG1_D4                     |                                                       | 2.5-V           | PIN_C33                     |

| HEX1               | SEG1_D5                     |                                                       | 2.5-V           | PIN_D33                     |

| HEX1               | SEG1_D6                     |                                                       | 2.5-V           | PIN_D34                     |

25

| HEX1 | SEG1_DP |

|------|---------|

| HEX0 | SEG0_D0 |

| HEX0 | SEG0_D1 |

| HEX0 | SEG0_D2 |

| HEX0 | SEG0_D3 |

| HEX0 | SEG0_D4 |

| HEX0 | SEG0_D5 |

| HEX0 | SEG0_D6 |

| HEX0 | SEG0_DP |

# 2.5 High-Speed Mezzanine Cards

The DE4 development board contains two HSMC interfaces called port A and port B. The HSMC interface provides a mechanism to extend the peripheral-set of an FPGA host board by means of add-on cards, which can address today's high speed signaling requirement as well as low-speed device interface support. The HSMC interfaces support JTAG, clock outputs and inputs, high-speed serial I/O (transceivers), and single-ended or differential signaling.

Both the HSMC interfaces connected to the Stratix IV GX device are female HSMC connectors with each connector having a total of 172pins, including 121 signal pins (120 signal pins +1 PSNTn pin), 39 power pins, and 12 ground pins. The HSMC connector is based on the Samtec 0.5 mm pitch, surface-mount QSH family of high-speed, board-to-board connectors. The Stratix IV GX device provides +12 V DC and +3.3 V DC power to the mezzanine card through the HSMC connector. Table 2–9 indicates the maximum power consumption for both HSMC ports A and B.

Table 2–9 Power Supply of the HSMC

| Supplied Voltage | Max. Current Limit |

|------------------|--------------------|

| 12V              | 3A                 |

| 3.3V             | 3A                 |

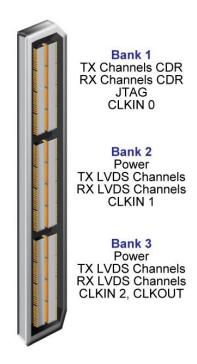

There are three banks in this connector as **Figure 2–12** shows the bank arrangement of signals with respect to the Samtec connector. **Table 2–10** and **Table 2–11** show the mapping of the FPGA pin assignments to the HSMC connectors.

Figure 2-12 HSMC signal and bank diagram

#### **■** I/O Distribution

The two HSMC interfaces combine have a total of 12 pairs CDR-based transceivers operating up to 8.5Gbps, 38 pairs LVDS transmitter channels at data rates up to 1.6Gbps, and 36 pairs LVDS receiver channels. Independently, Port A of the HSMC connector consists of 4 pairs CDR-based transceivers, 19 pairs LVDS transmitter channels, and 18 pairs LVDS receiver channels. While port B of the HSMC connector consists of 8 pairs CDR-based transceivers, 19 pairs LVDS transmitter channels, and 18 pairs LVDS receiver channels. Additionally, both ports A and B of the HSMC interfaces have 5 clock inputs and 4 clock outputs (2 differential clock inputs and outputs).

#### ■ I/O Standards

The HSMC interface has programmable bi-directional I/O pins that can be used as 2.5-V. These pins can also be used as differential I/O standard including LVDS.

## ■ Using THCB-HMF2 adapter card

The purpose of the HSMC Height Extension Male to Female card (THCB-HMF2) included in the

DE4 kit package is to increase the height of the HSMC connector to avoid any obstruction that might take place as a HSMC daughter card is connected. The THCB-HMF2 adapter card can be connected to either ports, A or B of the HSMC connector shown in **Figure 2–13**.

Figure 2-13 Connection setup between THCB-HMF2 adapter card and HSMC

#### **■ JTAG Chain on HSMC**

The JTAG chain on the HSMC can be activated through the 3-position DIP switch (SW8). If there is no connection established on the HSMC connectors, the 3-position DIP switch (SW8) are to set 'On', where the JTAG signals on the HSMC connectors are bypassed illustrated in **Figure 2–14**.

Figure 2–14 JTAG chain for a standalone DE4 board

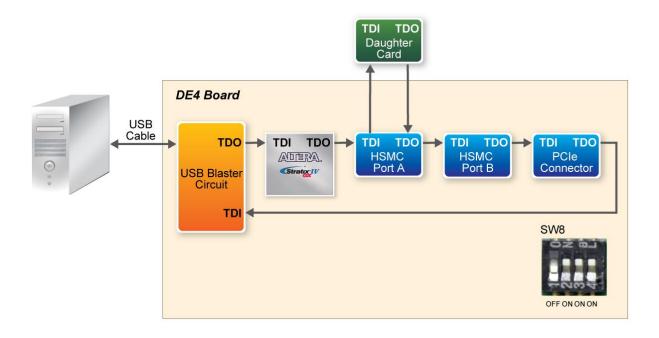

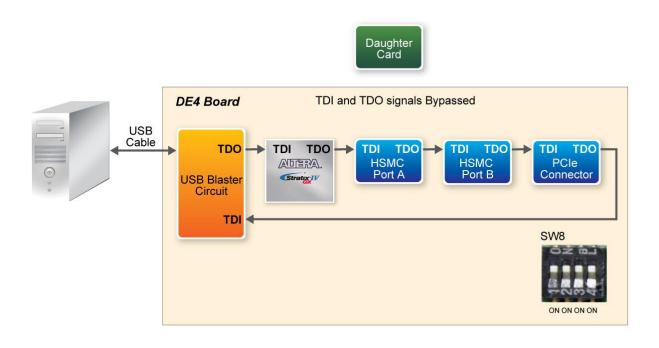

If the HSMC-based daughter card connected to the HSMC connector uses the JTAG interface, the 3-position DIP switch (SW8) is set to 'Off' to which HSMC port is used. In this case, from **Figure 2–15** HSMC port A is used where position 1 of the SW8 is set to 'Off'. Similarly, if the JTAG interface isn't used on the HSMC-based daughter card, position 1 of SW8 is set to 'On' bypassing the JTAG signals as shown in **Figure 2–16**.

Figure 2–15 JTAG chain for a daughter card (uses JTAG) connected to HSMC port A of the DE4

Figure 2-16 JTAG chain for a daughter card (JTAG not used) connected to HSMC port A of the DE4

#### ■ Multi-FPGA high capacity platform through HSMC

The DE4 offers a choice of two Stratix IV GX devices, EP4SGX230 and EPSGX530 which offer logic elements (LEs) up to 228,000 and 531,200, respectively to provide the flexibility for users to select a suitable device in terms of design capacity. In situations where users' design exceeds the capacity of the FPGA, the HSMC interface can be used to connect to other FPGA system boards creating a multi-FPGA scalable system. **Figure 2–17** illustrates a connection setup between two DE4 boards by connecting through port B and Port A of the HSMC connectors using a Samtec high-speed cable. Notice the JTAG switch (SW8) configuration setup where position 2 is set to 'Off' for port B connected on the DE4 and position 1 is set to 'Off' for port A connected on the DE4, allowing JTAG chain to be detected for both DE4 boards.

Figure 2-17 JTAG chain setup between two DE4 boards using HSMC interface

Table 2–10 HSMC Port B Pin Assignments, Schematic Signal Names, and Functions

| HSMC Pin # | Schematic Signal Name | Description           | I/O Standard | Stratix IV GX Pin Number |

|------------|-----------------------|-----------------------|--------------|--------------------------|

| 1          | HSMB_GXB_TX_p7        | Transceiver TX bit 7  | 1.4-V PCML   | PIN_B4                   |

| 2          | HSMB_GXB_RX_p7        | Transceiver RX bit 7  | 1.4-V PCML   | PIN_C2                   |

| 3          | HSMB_GXB_TX_n7        | Transceiver TX bit 7n | 1.4-V PCML   | PIN_B3                   |

| 4          | HSMB_GXB_RX_n7        | Transceiver RX bit 7n | 1.4-V PCML   | PIN_C1                   |

| 5          | HSMB_GXB_TX_p6        | Transceiver TX bit 6  | 1.4-V PCML   | PIN_D4                   |

| 6          | HSMB_GXB_RX_p6        | Transceiver RX bit 6  | 1.4-V PCML   | PIN_E2                   |

| 7          | HSMB_GXB_TX_n6        | Transceiver TX bit 6n | 1.4-V PCML   | PIN_D3                   |

| 8          | HSMB_GXB_RX_n6        | Transceiver RX bit 6n | 1.4-V PCML   | PIN_E1                   |

| 9          | HSMB_GXB_TX_p5        | Transceiver TX bit 5  | 1.4-V PCML   | PIN_K4                   |

| 10         | HSMB_GXB_RX_p5        | Transceiver RX bit 5  | 1.4-V PCML   | PIN_L2                   |

| 11         | HSMB_GXB_TX_n5        | Transceiver RX bit 5n | 1.4-V PCML   | PIN_K3                   |

| 12         | HSMB_GXB_RX_n5        | Transceiver RX bit 5n | 1.4-V PCML   | PIN_L1                   |

| 13         | HSMB_GXB_TX_p4        | Transceiver TX bit 4  | 1.4-V PCML   | PIN_M4                   |

| 14         | HSMB_GXB_RX_p4        | Transceiver RX bit 4  | 1.4-V PCML   | PIN_N2                   |

| 15         | HSMB_GXB_TX_n4        | Transceiver TX bit 4n | 1.4-V PCML   | PIN_M3                   |

| 16         | HSMB_GXB_RX_n4        | Transceiver RX bit 4n | 1.4-V PCML   | PIN_N1                   |

| 17         | HSMB_GXB_TX_p3        | Transceiver TX bit 3  | 1.4-V PCML   | PIN_P4                   |

| 18         | HSMB_GXB_RX_p3        | Transceiver RX bit 3  | 1.4-V PCML   | PIN_R2                   |

| 19         | HSMB_GXB_TX_n3        | Transceiver TX bit 3n | 1.4-V PCML   | PIN_P3                   |

| 20         | HSMB_GXB_RX_n3        | Transceiver RX bit 3n | 1.4-V PCML   | PIN_R1                   |

| 21         | HSMB_GXB_TX_p2        | Transceiver TX bit 2  | 1.4-V PCML   | PIN_T4                   |

| 22         | HSMB_GXB_RX_p2        | Transceiver RX bit 2  | 1.4-V PCML   | PIN_U2                   |

| 23         | HSMB_GXB_TX_n2        | Transceiver TX bit 2n | 1.4-V PCML   | PIN_T3                   |

| 24 | HSMB_GXB_RX_n2 | Transceiver RX bit 2n      | 1.4-V PCML    | PIN_U1  |

|----|----------------|----------------------------|---------------|---------|

| 25 | HSMB_GXB_TX_p1 | Transceiver TX bit 1       | 1.4-V PCML    | PIN_AB4 |

| 26 | HSMB_GXB_RX_p1 | Transceiver RX bit 1       | 1.4-V PCML    | PIN_AC2 |

| 27 | HSMB_GXB_TX_n1 | Transceiver TX bit 1n      | 1.4-V PCML    | PIN_AB3 |

| 28 | HSMB_GXB_RX_n1 | Transceiver RX bit 1n      | 1.4-V PCML    | PIN_AC1 |

| 29 | HSMB_GXB_TX_p0 | Transceiver TX bit 0       | 1.4-V PCML    | PIN_AD4 |

| 30 | HSMB_GXB_RX_p0 | Transceiver RX bit 0       | 1.4-V PCML    | PIN_AE2 |

| 31 | HSMB_GXB_TX_n0 | Transceiver TX bit 0n      | 1.4-V PCML    | PIN_AD3 |

| 32 | HSMB_GXB_RX_n0 | Transceiver RX bit 0n      | 1.4-V PCML    | PIN_AE1 |

| 33 | E_HSMC_SDA     | Management serial data     | 1.8-V(*)      | PIN_M19 |

| 34 | E_HSMC_SCL     | Management serial clock    | 1.8-V(*)      | PIN_L19 |

| 35 | HSMC_TCK       | JTAG clock signal          | 2.5-V         | -       |

| 36 | HSMC_TMS       | JTAG mode select signal    | 2.5-V         | -       |

| 37 | HSMB_TDO       | JTAG data output           | 2.5-V         | -       |

| 38 | HSMC_TDI       | JTAG data input            | 2.5-V         | -       |

| 39 | HSMB_OUT0      | CMOS I/O                   | LVDS or 2.5-V | PIN_L8  |

| 40 | HSMB_CLKIN0    | Dedicated clock input      | LVDS or 2.5-V | PIN_AA5 |

| 41 | HSMB_D0        | LVDS TX or CMOS I/O        | LVDS or 2.5-V | PIN_H10 |

| 42 | HSMB_D1        | LVDS RX or CMOS I/O        | LVDS or 2.5-V | PIN_D6  |

| 43 | HSMB_D2        | LVDS TX or CMOS I/O        | LVDS or 2.5-V | PIN_G10 |

| 44 | HSMB_D3        | LVDS RX or CMOS I/O        | LVDS or 2.5-V | PIN_C6  |

| 47 | HSMB_TX_p0     | LVDS TX bit 0 or CMOS I/O  | LVDS or 2.5-V | PIN_K9  |

| 48 | HSMB_RX_p0     | LVDS RX bit 0 or CMOS I/O  | LVDS or 2.5-V | PIN_D5  |

| 49 | HSMB_TX_n0     | LVDS TX bit 0n or CMOS I/O | LVDS or 2.5-V | PIN_J9  |

| 50 | HSMB_RX_n0     | LVDS RX bit 0n or CMOS I/O | LVDS or 2.5-V | PIN_C5  |

| 53 | HSMB_TX_p1     | LVDS TX bit 1 or CMOS I/O  | LVDS or 2.5-V | PIN_K10 |

| 54 | HSMB_RX_p1     | LVDS RX bit 1 or CMOS I/O  | LVDS or 2.5-V | PIN_D10 |

| 55 | HSMB_TX_n1     | LVDS TX bit 1n or CMOS I/O | LVDS or 2.5-V | PIN_J10 |

| 56 | HSMB_RX_n1     | LVDS RX bit 1n or CMOS I/O | LVDS or 2.5-V | PIN_C10 |

| 59 | HSMB_TX_p2     | LVDS TX bit 2 or CMOS I/O  | LVDS or 2.5-V | PIN_N11 |

| 60 | HSMB_RX_p2     | LVDS RX bit 2 or CMOS I/O  | LVDS or 2.5-V | PIN_D9  |

| 61 | HSMB_TX_n2     | LVDS TX bit 2n or CMOS I/O | LVDS or 2.5-V | PIN_N10 |

| 62 | HSMB_RX_n2     | LVDS RX bit 2n or CMOS I/O | LVDS or 2.5-V | PIN_C9  |

| 65 | HSMB_TX_p3     | LVDS TX bit 3 or CMOS I/O  | LVDS or 2.5-V | PIN_N12 |

| 66 | HSMB_RX_p3     | LVDS RX bit 3 or CMOS I/O  | LVDS or 2.5-V | PIN_D8  |

| 67 | HSMB_TX_n3     | LVDS TX bit 3n or CMOS I/O | LVDS or 2.5-V | PIN_M12 |

| 68 | HSMB_RX_n3     | LVDS RX bit 3n or CMOS I/O | LVDS or 2.5-V | PIN_C8  |

| 71 | HSMB_TX_p4     | LVDS TX bit 4 or CMOS I/O  | LVDS or 2.5-V | PIN_R12 |

| 72 | HSMB_RX_p4     | LVDS RX bit 4 or CMOS I/O  | LVDS or 2.5-V | PIN_D7  |

| 73 | HSMB_TX_n4     | LVDS TX bit 4n or CMOS I/O | LVDS or 2.5-V | PIN_R11 |

| 74 | HSMB_RX_n4     | LVDS RX bit 4n or CMOS I/O | LVDS or 2.5-V | PIN_C7  |

| 77 | HSMB_TX_p5     | LVDS TX bit 5 or CMOS I/O  | LVDS or 2.5-V | PIN_T13 |

| 78 | HSMB_RX_p5     | LVDS RX bit 5 or CMOS I/O  | LVDS or 2.5-V | PIN_F10 |

|     |               |                                                 | 1             | 1       |

|-----|---------------|-------------------------------------------------|---------------|---------|

| 79  | HSMB_TX_n5    | LVDS TX bit 5n or CMOS I/O                      | LVDS or 2.5-V | PIN_T12 |

| 80  | HSMB_RX_n5    | LVDS RX bit 5n or CMOS I/O                      | LVDS or 2.5-V | PIN_E10 |

| 83  | HSMB_TX_p6    | LVDS TX bit 6 or CMOS I/O                       | LVDS or 2.5-V | PIN_R13 |

| 84  | HSMB_RX_p6    | LVDS RX bit 6 or CMOS I/O                       | LVDS or 2.5-V | PIN_G5  |

| 85  | HSMB_TX_n6    | LVDS TX bit 6n or CMOS I/O                      | LVDS or 2.5-V | PIN_P13 |

| 86  | HSMB_RX_n6    | LVDS RX bit 6n or CMOS I/O                      | LVDS or 2.5-V | PIN_F5  |

| 89  | HSMB_TX_p7    | LVDS TX bit 7 or CMOS I/O                       | LVDS or 2.5-V | PIN_H7  |

| 90  | HSMB_RX_p7    | LVDS RX bit 7 or CMOS I/O                       | LVDS or 2.5-V | PIN_G6  |

| 91  | HSMB_TX_n7    | LVDS TX bit 7n or CMOS I/O                      | LVDS or 2.5-V | PIN_G7  |

| 92  | HSMB_RX_n7    | LVDS RX bit 7n or CMOS I/O                      | LVDS or 2.5-V | PIN_F6  |

| 95  | HSMB_OUT_p1   | LVDS TX or CMOS I/O                             | LVDS or 2.5-V | PIN_K8  |

| 96  | HSMB_CLKIN_p1 | LVDS RX or CMOS I/O or differential clock input | LVDS or 2.5-V | PIN_W34 |

| 97  | HSMB_OUT_n1   | LVDS RX or CMOS I/O                             | LVDS or 2.5-V | PIN_J8  |

| 98  | HSMB_CLKIN_n1 | LVDS RX or CMOS I/O or differential clock input | LVDS or 2.5-V | PIN_W35 |

| 101 | HSMB_TX_p8    | LVDS TX bit 8 or CMOS I/O                       | LVDS or 2.5-V | PIN_M10 |

| 102 | HSMB_RX_p8    | LVDS RX bit 8 or CMOS I/O                       | LVDS or 2.5-V | PIN_F7  |

| 103 | HSMB_TX_n8    | LVDS TX bit 8n or CMOS I/O                      | LVDS or 2.5-V | PIN_L10 |

| 104 | HSMB_RX_n8    | LVDS RX bit 8n or CMOS I/O                      | LVDS or 2.5-V | PIN_E7  |

| 107 | HSMB_TX_p9    | LVDS TX bit 9 or CMOS I/O                       | LVDS or 2.5-V | PIN_M8  |

| 108 | HSMB_RX_p9    | LVDS RX bit 9 or CMOS I/O                       | LVDS or 2.5-V | PIN_G8  |

| 109 | HSMB_TX_n9    | LVDS TX bit 9n or CMOS I/O                      | LVDS or 2.5-V | PIN_M7  |

| 110 | HSMB_RX_n9    | LVDS RX bit 9n or CMOS I/O                      | LVDS or 2.5-V | PIN_F8  |

| 113 | HSMB_TX_p10   | LVDS TX bit 10 or CMOS I/O                      | LVDS or 2.5-V | PIN_M11 |

| 114 | HSMB_RX_p10   | LVDS RX bit 10 or CMOS I/O                      | LVDS or 2.5-V | PIN_G9  |

| 115 | HSMB_TX_n10   | LVDS TX bit 10n or CMOS I/O                     | LVDS or 2.5-V | PIN_L11 |

| 116 | HSMB_RX_n10   | LVDS RX bit 10n or CMOS I/O                     | LVDS or 2.5-V | PIN_F9  |

| 119 | HSMB_TX_p11   | LVDS TX bit 11 or CMOS I/O                      | LVDS or 2.5-V | PIN_N9  |

| 120 | HSMB_RX_p11   | LVDS RX bit 11 or CMOS I/O                      | LVDS or 2.5-V | PIN_N6  |

| 121 | HSMB_TX_n11   | LVDS TX bit 11n or CMOS I/O                     | LVDS or 2.5-V | PIN_P8  |

| 122 | HSMB_RX_n11   | LVDS RX bit 11n or CMOS I/O                     | LVDS or 2.5-V | PIN_N5  |

| 125 | HSMB_TX_p12   | LVDS TX bit 12 or CMOS I/O                      | LVDS or 2.5-V | PIN_R9  |

| 126 | HSMB_RX_p12   | LVDS RX bit 12 or CMOS I/O                      | LVDS or 2.5-V | PIN_M6  |

| 127 | HSMB_TX_n12   | LVDS TX bit 12n or CMOS I/O                     | LVDS or 2.5-V | PIN_R8  |

| 128 | HSMB_RX_n12   | LVDS RX bit 12n or CMOS I/O                     | LVDS or 2.5-V | PIN_L5  |

| 131 | HSMB_TX_p13   | LVDS TX bit 13 or CMOS I/O                      | LVDS or 2.5-V | PIN_U10 |

| 132 | HSMB_RX_p13   | LVDS RX bit 13 or CMOS I/O                      | LVDS or 2.5-V | PIN_R6  |

| 133 | HSMB_TX_n13   | LVDS TX bit 13n or CMOS I/O                     | LVDS or 2.5-V | PIN_T9  |

| 134 | HSMB_RX_n13   | LVDS RX bit 13n or CMOS I/O                     | LVDS or 2.5-V | PIN_R5  |

| 137 | HSMB_TX_p14   | LVDS TX bit 14 or CMOS I/O                      | LVDS or 2.5-V | PIN_V10 |

| 138 | HSMB_RX_p14   | LVDS RX bit 14 or CMOS I/O                      | LVDS or 2.5-V | PIN_R7  |

| 139 | HSMB_TX_n14   | LVDS TX bit 14n or CMOS I/O                     | LVDS or 2.5-V | PIN_V9  |

|     |                  |                                 |                | 1         |

|-----|------------------|---------------------------------|----------------|-----------|

| 140 | HSMB_RX_n14      | LVDS RX bit 14n or CMOS I/O     | LVDS or 2.5-V  | PIN_P6    |

| 143 | HSMB_TX_p15      | LVDS TX bit 15 or CMOS I/O      | LVDS or 2.5-V  | PIN_T10   |

| 144 | HSMB_RX_p15      | LVDS RX bit 15 or CMOS I/O      | LVDS or 2.5-V  | PIN_V6    |

| 145 | HSMB_TX_n15      | LVDS TX bit 15n or CMOS I/O     | LVDS or 2.5-V  | PIN_R10   |

| 146 | HSMB_RX_n15      | LVDS RX bit 15n or CMOS I/O     | LVDS or 2.5-V  | PIN_U5    |

| 149 | HSMB_TX_p16      | LVDS TX bit 16 or CMOS I/O      | LVDS or 2.5-V  | PIN_V12   |

| 150 | HSMB_RX_p16      | LVDS RX bit 16 or CMOS I/O      | LVDS or 2.5-V  | PIN_W8    |

| 151 | HSMB_TX_n16      | LVDS TX bit 16n or CMOS I/O     | LVDS or 2.5-V  | PIN_V11   |

| 152 | HSMB_RX_n16      | LVDS RX bit 16n or CMOS I/O     | LVDS or 2.5-V  | PIN_W7    |

| 155 | LICMD CLICOLT =2 | LVDS TX or CMOS I/O or          | LVDS or 2.5-V  | PIN_W12   |

| 133 | HSMB_CLKOUT_p2   | differential clock input/output | LVD3 01 2.3-V  |           |

| 156 | HSMB_CLKIN_p2    | LVDS RX or CMOS I/O or          | LVDS or 2.5-V  | PIN_W6    |

| 150 | HSWIB_CLKIN_P2   | differential clock input        |                |           |

| 157 | HSMB_CLKOUT_n2   | LVDS TX or CMOS I/O or          | LVDS or 2.5-V  | DINI W/44 |

| 101 |                  | differential clock input/output |                | PIN_W11   |

| 158 | HSMB_CLKIN_n2    | LVDS RX or CMOS I/O or          | LVDS or 2.5-V  | PIN_W5    |

|     |                  | differential clock input        | LV D3 01 2.3-V |           |

## Note for Table 2–10:

Table 2–11 HSMC Port A Pin Assignments, Schematic Signal Names, and Functions

| HSMC Pin # | Schematic Signal Name | Description          | I/O Standard | Stratix IV GX Pin Number |

|------------|-----------------------|----------------------|--------------|--------------------------|

| 1          | -                     | -                    | -            | -                        |

| 2          | -                     | -                    | -            | -                        |

| 3          | -                     | -                    | -            | -                        |

| 4          | -                     | -                    | -            | -                        |

| 5          | -                     | -                    | -            | -                        |

| 6          | -                     | -                    | -            | -                        |

| 7          | -                     | -                    | -            | -                        |

| 8          | -                     | -                    | -            | -                        |

| 9          | -                     | -                    | -            | -                        |

| 10         | -                     | -                    | -            | -                        |

| 11         | -                     | -                    | -            | -                        |

| 12         | -                     | -                    | -            | -                        |

| 13         | -                     | -                    | -            | -                        |

| 14         | -                     | -                    | -            | -                        |

| 15         | -                     | -                    | -            | -                        |

| 16         | -                     | -                    | -            | -                        |

| 17         | HSMA_GXB_TX_p3        | Transceiver TX bit 3 | 1.4-V PCML   | PIN_B36                  |

<sup>\*</sup>The signals E\_HSMC\_SDA and E\_HSMC\_SCL are level-shifted from 3.3V (FPGA) to 1.8V (HSMC).

| 18 | HSMA_GXB_RX_p3 | Transceiver RX bit 3       | 1.4-V PCML    | PIN_C38  |

|----|----------------|----------------------------|---------------|----------|

| 19 | HSMA_GXB_TX_n3 | Transceiver TX bit 3n      | 1.4-V PCML    | PIN_B37  |

| 20 | HSMA_GXB_RX_n3 | Transceiver RX bit 3n      | 1.4-V PCML    | PIN_C39  |

| 21 | HSMA_GXB_TX_p2 | Transceiver TX bit 2       | 1.4-V PCML    | PIN_D36  |

| 22 | HSMA_GXB_RX_p2 | Transceiver RX bit 2       | 1.4-V PCML    | PIN_E38  |

| 23 | HSMA_GXB_TX_n2 | Transceiver TX bit 2n      | 1.4-V PCML    | PIN_D37  |

| 24 | HSMA_GXB_RX_n2 | Transceiver RX bit 2n      | 1.4-V PCML    | PIN_E39  |

| 25 | HSMA_GXB_TX_p1 | Transceiver TX bit 1       | 1.4-V PCML    | PIN_K36  |

| 26 | HSMA_GXB_RX_p1 | Transceiver RX bit 1       | 1.4-V PCML    | PIN_L38  |

| 27 | HSMA_GXB_TX_n1 | Transceiver TX bit 1n      | 1.4-V PCML    | PIN_K37  |

| 28 | HSMA_GXB_RX_n1 | Transceiver RX bit 1n      | 1.4-V PCML    | PIN_L39  |

| 29 | HSMA_GXB_TX_p0 | Transceiver TX bit 0       | 1.4-V PCML    | PIN_M36  |

| 30 | HSMA_GXB_RX_p0 | Transceiver RX bit 0       | 1.4-V PCML    | PIN_N38  |

| 31 | HSMA_GXB_TX_n0 | Transceiver TX bit 0n      | 1.4-V PCML    | PIN_M37  |

| 32 | HSMA_GXB_RX_n0 | Transceiver RX bit 0n      | 1.4-V PCML    | PIN_N39  |

| 33 | E_HSMC_SDA     | Management serial data     | 1.8-V(*)      | PIN_M19  |

| 34 | E_HSMC_SCL     | Management serial clock    | 1.8-V(*)      | PIN_L19  |

| 35 | HSMC_TCK       | JTAG clock signal          | 2.5-V         | -        |

| 36 | HSMC_TMS       | JTAG mode select signal    | 2.5-V         | -        |

| 37 | HSMA_TDO       | JTAG data output           | 2.5-V         | -        |

| 38 | HSMA_TDI       | JTAG data input            | 2.5-V         | -        |

| 39 | HSMA_OUT0      | CMOS I/O                   | LVDS or 2.5-V | PIN_AF29 |

| 40 | HSMA_CLKIN0    | Dedicated clock input      | LVDS or 2.5-V | PIN_AC34 |

| 41 | HSMA_D0        | LVDS TX or CMOS I/O        | LVDS or 2.5-V | PIN_AC26 |

| 42 | HSMA_D1        | LVDS RX or CMOS I/O        | LVDS or 2.5-V | PIN_AC31 |

| 43 | HSMA_D2        | LVDS TX or CMOS I/O        | LVDS or 2.5-V | PIN_AD26 |

| 44 | HSMA_D3        | LVDS RX or CMOS I/O        | LVDS or 2.5-V | PIN_AC32 |

| 47 | HSMA_TX_p0     | LVDS TX bit 0 or CMOS I/O  | LVDS or 2.5-V | PIN_AB27 |

| 48 | HSMA_RX_p0     | LVDS RX bit 0 or CMOS I/O  | LVDS or 2.5-V | PIN_AJ32 |

| 49 | HSMA_TX_n0     | LVDS TX bit 0n or CMOS I/O | LVDS or 2.5-V | PIN_AB28 |

| 50 | HSMA_RX_n0     | LVDS RX bit 0n or CMOS I/O | LVDS or 2.5-V | PIN_AK33 |

| 53 | HSMA_TX_p1     | LVDS TX bit 1 or CMOS I/O  | LVDS or 2.5-V | PIN_AB30 |

| 54 | HSMA_RX_p1     | LVDS RX bit 1 or CMOS I/O  | LVDS or 2.5-V | PIN_AH34 |

| 55 | HSMA_TX_n1     | LVDS TX bit 1n or CMOS I/O | LVDS or 2.5-V | PIN_AB31 |

| 56 | HSMA_RX_n1     | LVDS RX bit 1n or CMOS I/O | LVDS or 2.5-V | PIN_AH35 |

| 59 | HSMA_TX_p2     | LVDS TX bit 2 or CMOS I/O  | LVDS or 2.5-V | PIN_AD27 |

| 60 | HSMA_RX_p2     | LVDS RX bit 2 or CMOS I/O  | LVDS or 2.5-V | PIN_AJ34 |

| 61 | HSMA_TX_n2     | LVDS TX bit 2n or CMOS I/O | LVDS or 2.5-V | PIN_AE27 |

| 62 | HSMA_RX_n2     | LVDS RX bit 2n or CMOS I/O | LVDS or 2.5-V | PIN_AJ35 |

| 65 | HSMA_TX_p3     | LVDS TX bit 3 or CMOS I/O  | LVDS or 2.5-V | PIN_AD28 |

| 66 | HSMA_RX_p3     | LVDS RX bit 3 or CMOS I/O  | LVDS or 2.5-V | PIN_AK34 |

| 67 | HSMA_TX_n3     | LVDS TX bit 3n or CMOS I/O | LVDS or 2.5-V | PIN_AD29 |

| 68 | HSMA_RX_n3     | LVDS RX bit 3n or CMOS I/O | LVDS or 2.5-V | PIN_AK35 |

| 71   | HSMA_TX_p4    | LVDS TX bit 4 or CMOS I/O   | LVDS or 2.5-V PIN_AE28 |

|------|---------------|-----------------------------|------------------------|

| 72   | HSMA_RX_p4    | LVDS RX bit 4 or CMOS I/O   | LVDS or 2.5-V PIN_AN30 |

| 73   | HSMA_TX_n4    | LVDS TX bit 4n or CMOS I/O  | LVDS or 2.5-V PIN_AE29 |

| 74   | HSMA_RX_n4    | LVDS RX bit 4n or CMOS I/O  | LVDS or 2.5-V PIN_AP30 |

| 77   | HSMA_TX_p5    | LVDS TX bit 5 or CMOS I/O   | LVDS or 2.5-V PIN_AE26 |

| 78   | HSMA_RX_p5    | LVDS RX bit 5 or CMOS I/O   | LVDS or 2.5-V PIN_AM34 |

| 79   | HSMA_TX_n5    | LVDS TX bit 5n or CMOS I/O  | LVDS or 2.5-V PIN_AF26 |

| 80   | HSMA_RX_n5    | LVDS RX bit 5n or CMOS I/O  | LVDS or 2.5-V PIN_AM35 |

| 83   | HSMA_TX_p6    | LVDS TX bit 6 or CMOS I/O   | LVDS or 2.5-V PIN_AG31 |

| 84   | HSMA_RX_p6    | LVDS RX bit 6 or CMOS I/O   | LVDS or 2.5-V PIN_AM31 |

| 85   | HSMA_TX_n6    | LVDS TX bit 6n or CMOS I/O  | LVDS or 2.5-V PIN_AG32 |

| 86   | HSMA_RX_n6    | LVDS RX bit 6n or CMOS I/O  | LVDS or 2.5-V PIN_AN31 |

| 89   | HSMA_TX_p7    | LVDS TX bit 7 or CMOS I/O   | LVDS or 2.5-V PIN_AG29 |

| 90   | HSMA_RX_p7    | LVDS RX bit 7 or CMOS I/O   | LVDS or 2.5-V PIN_AN33 |

| 91   | HSMA_TX_n7    | LVDS TX bit 7n or CMOS I/O  | LVDS or 2.5-V PIN_AH29 |

| 92   | HSMA_RX_n7    | LVDS RX bit 7n or CMOS I/O  | LVDS or 2.5-V PIN_AP34 |

| 95   | HSMA_OUT_p1   | LVDS TX or CMOS I/O         | LVDS or 2.5-V PIN_AG28 |

|      | -             | LVDS RX or CMOS I/O or      |                        |

| 96   | HSMA_CLKIN_p1 | differential clock input    | LVDS or 2.5-V PIN_AB34 |

| 97   | HSMA_OUT_n1   | LVDS RX or CMOS I/O         | LVDS or 2.5-V PIN_AH28 |

|      |               | LVDS RX or CMOS I/O or      |                        |

| 98   | HSMA_CLKIN_n1 | differential clock input    | LVDS or 2.5-V PIN_AA35 |

| 101  | HSMA_TX_p8    | LVDS TX bit 8 or CMOS I/O   | LVDS or 2.5-V PIN_AC28 |

| 102  | HSMA_RX_p8    | LVDS RX bit 8 or CMOS I/O   | LVDS or 2.5-V PIN_AP32 |

| 103  | HSMA_TX_n8    | LVDS TX bit 8n or CMOS I/O  | LVDS or 2.5-V PIN_AC29 |

| 104  | HSMA_RX_n8    | LVDS RX bit 8n or CMOS I/O  | LVDS or 2.5-V PIN_AR32 |

| 107  | HSMA_TX_p9    | LVDS TX bit 9 or CMOS I/O   | LVDS or 2.5-V PIN_AJ29 |

| 108  | HSMA_RX_p9    | LVDS RX bit 9 or CMOS I/O   | LVDS or 2.5-V PIN_AR31 |

| 109  | HSMA_TX_n9    | LVDS TX bit 9n or CMOS I/O  | LVDS or 2.5-V PIN_AK29 |

| 110  | HSMA_RX_n9    | LVDS RX bit 9n or CMOS I/O  | LVDS or 2.5-V PIN_AT30 |

| 113  | HSMA_TX_p10   | LVDS TX bit 10 or CMOS I/O  | LVDS or 2.5-V PIN_AD30 |

| 114  | HSMA_RX_p10   | LVDS RX bit 10 or CMOS I/O  | LVDS or 2.5-V PIN_AT33 |

| 115  | HSMA_TX_n10   | LVDS TX bit 10n or CMOS I/O | LVDS or 2.5-V PIN_AD31 |

| 116  | HSMA_RX_n10   | LVDS RX bit 10n or CMOS I/O | LVDS or 2.5-V PIN_AU33 |

| 119  | HSMA_TX_p11   | LVDS TX bit 11 or CMOS I/O  | LVDS or 2.5-V PIN_AK32 |

| 120  | HSMA_RX_p11   | LVDS RX bit 11 or CMOS I/O  | LVDS or 2.5-V PIN_AU34 |

| 121  | HSMA_TX_n11   | LVDS TX bit 11n or CMOS I/O | LVDS or 2.5-V PIN_AL32 |

| 122  | HSMA_RX_n11   | LVDS RX bit 11n or CMOS I/O | LVDS or 2.5-V PIN_AV34 |

| 125  | HSMA_TX_p12   | LVDS TX bit 12 or CMOS I/O  | LVDS or 2.5-V PIN_AG27 |

| 126  | HSMA_RX_p12   | LVDS RX bit 12 or CMOS I/O  | LVDS or 2.5-V PIN_AT32 |

| 127  | HSMA_TX_n12   | LVDS TX bit 12 or CMOS I/O  | LVDS or 2.5-V PIN_AH27 |

| 128  | HSMA_RX_n12   | LVDS RX bit 12n or CMOS I/O | LVDS or 2.5-V PIN_AU32 |

| 1120 |               |                             |                        |

| 132 | HSMA_RX_p13         | LVDS RX bit 13 or CMOS I/O      | LVDS or 2.5-V | PIN_AT31   |

|-----|---------------------|---------------------------------|---------------|------------|

| 133 | HSMA_TX_n13         | LVDS TX bit 13n or CMOS I/O     | LVDS or 2.5-V | PIN_AL31   |

| 134 | HSMA_RX_n13         | LVDS RX bit 13n or CMOS I/O     | LVDS or 2.5-V | PIN_AU31   |

| 137 | HSMA_TX_p14         | LVDS TX bit 14 or CMOS I/O      | LVDS or 2.5-V | PIN_AJ31   |

| 138 | HSMA_RX_p14         | LVDS RX bit 14 or CMOS I/O      | LVDS or 2.5-V | PIN_AP35   |

| 139 | HSMA_TX_n14         | LVDS TX bit 14n or CMOS I/O     | LVDS or 2.5-V | PIN_AH30   |

| 140 | HSMA_RX_n14         | LVDS RX bit 14n or CMOS I/O     | LVDS or 2.5-V | PIN_AR35   |

| 143 | HSMA_TX_p15         | LVDS TX bit 15 or CMOS I/O      | LVDS or 2.5-V | PIN_AL29   |

| 144 | HSMA_RX_p15         | LVDS RX bit 15 or CMOS I/O      | LVDS or 2.5-V | PIN_AN32   |

| 145 | HSMA_TX_n15         | LVDS TX bit 15n or CMOS I/O     | LVDS or 2.5-V | PIN_AM29   |

| 146 | HSMA_RX_n15         | LVDS RX bit 15n or CMOS I/O     | LVDS or 2.5-V | PIN_AP33   |

| 149 | HSMA_TX_p16         | LVDS TX bit 16 or CMOS I/O      | LVDS or 2.5-V | PIN_AK30   |

| 150 | HSMA_RX_p16         | LVDS RX bit 16 or CMOS I/O      | LVDS or 2.5-V | PIN_AT34   |

| 151 | HSMA_TX_n16         | LVDS TX bit 16n or CMOS I/O     | LVDS or 2.5-V | PIN_AL30   |

| 152 | HSMA_RX_n16         | LVDS RX bit 16n or CMOS I/O     | LVDS or 2.5-V | PIN_AR34   |

| 155 | HEMA CLIVOUT ma     | LVDS TX or CMOS I/O or          | LVDS or 2.5-V | DIN AC24   |

| 100 | HSMA_CLKOUT_p2      | differential clock input/output | LVD3 01 2.5-V | PIN_AG34   |

| 156 | HSMA_CLKIN_p2       | LVDS RX or CMOS I/O or          | LVDS or 2.5-V | PIN AF34   |

| 130 | nowA_CERIN_pz       | differential clock input        | LVD3 01 2.3-V | FIN_AF34   |

| 157 | HSMA_CLKOUT_n2      | LVDS TX or CMOS I/O or          | LVDS or 2.5-V | PIN_AG35   |

| 131 | I ISIVIA_CERCOT_IIZ | differential clock input/output | LVD3 01 2.3-V | I III_AGSS |

| 158 | HSMA_CLKIN_n2       | LVDS RX or CMOS I/O or          | LVDS or 2.5-V | PIN_AE35   |

| 100 | 110MA_OEIMI4_112    | differential clock input        |               | I III_ALUU |

#### Note for Table 2–11:

# 2.6 GPIO Expansion Headers

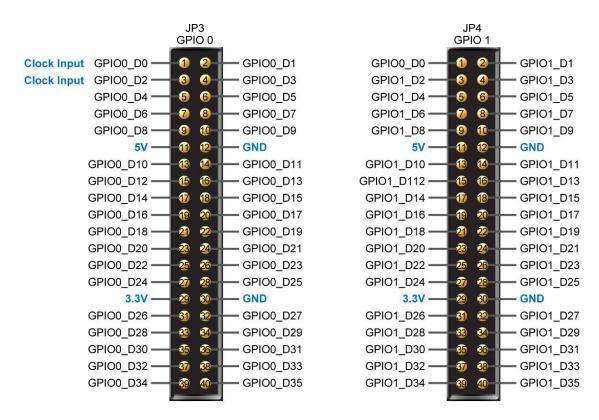

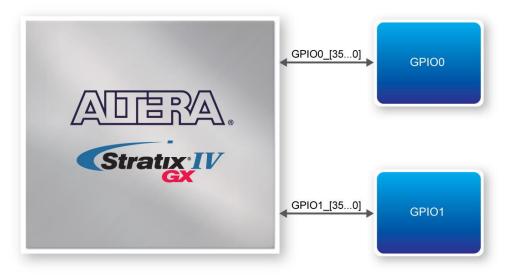

The DE4 Board consists of two 40-pin expansion headers as shown in **Figure 2–18**. Each header has 36 pins connected to the Stratix IV GX FPGA, with the other 4 pins providing DC +5V (VCC5), DC +3.3V (VCC33), and two GND pins. Among these 36 I/O pins for connector JP3, there are 2 pins connected to the differential clock inputs of the FPGA. The I/O pins on the expansion headers have a 3.0-V I/O standard.

<sup>\*</sup>The signals E\_HSMC\_SDA and E\_HSMC\_SCL are level-shifted from 3.3V (FPGA) to 1.8V (HSMC).

Figure 2–18 Pin distribution of the GPIO expansion headers

Finally, **Figure 2–19** shows the connections between the GPIO expansion headers and Stratix IV GX.

Figure 2-19 Connection between the GPIO expansion headers and Stratix IV GX

### ■ External 14-pin Expansion Header

An external 14-pin expansion header (JP6) is provided on the DE4 which offers additional connectivity and I/Os for general purpose applications. The header has 7 pins connected to the Stratix IV GX FPGA, with the other pins providing a DC +3.3V (VCC33) and 6 GND pins. Note the 6 data I/O pins on the 14-pin expansion header share the same bus with the GPIO expansion header (JP3).

The pin assignments are given in Table 2–12, Table 2–13 and Table 2–14.

Table 2–12 GPIO Expansion Header (JP3) Pin Assignments, Schematic Signal Names, and Functions

| Schematic   |                                  |               |                          |

|-------------|----------------------------------|---------------|--------------------------|

| Signal Name | Description                      | I/O Standard  | Stratix IV GX Pin Number |

| GPIO0_D0    | GPIO Expansion 0 IO[0](Clock In) | 3.0-V or LVDS | PIN_AF6                  |

| GPIO0_D1    | GPIO Expansion 0 IO[1]           | 3.0-V         | PIN_AU9                  |

| GPIO0_D2    | GPIO Expansion 0 IO[2](Clock In) | 3.0-V or LVDS | PIN_AE5                  |

| GPIO0_D3    | GPIO Expansion 0 IO[3]           | 3.0-V         | PIN_AR8                  |

| GPIO0_D4    | GPIO Expansion 0 IO[4]           | 3.0-V         | PIN_AN9                  |

| GPIO0_D5    | GPIO Expansion 0 IO[5]           | 3.0-V         | PIN_AP9                  |

| GPIO0_D6    | GPIO Expansion 0 IO[6]           | 3.0-V         | PIN_AV5                  |

| GPIO0_D7    | GPIO Expansion 0 IO[7]           | 3.0-V         | PIN_AW6                  |

| GPIO0_D8    | GPIO Expansion 0 IO[8]           | 3.0-V         | PIN_AV7                  |

| GPIO0_D9    | GPIO Expansion 0 IO[9]           | 3.0-V         | PIN_AW7                  |

| GPIO0_D10   | GPIO Expansion 0 IO[10]          | 3.0-V         | PIN_AT5                  |

| GPIO0_D11   | GPIO Expansion 0 IO[11]          | 3.0-V         | PIN_AT8                  |

| GPIO0_D12   | GPIO Expansion 0 IO[12]          | 3.0-V         | PIN_AP5                  |

| GPIO0_D13   | GPIO Expansion 0 IO[13]          | 3.0-V         | PIN_AP7                  |

| GPIO0_D14   | GPIO Expansion 0 IO[14]          | 3.0-V         | PIN_AN5                  |

| GPIO0_D15   | GPIO Expansion 0 IO[15]          | 3.0-V         | PIN_AN10                 |

| GPIO0_D16   | GPIO Expansion 0 IO[16]          | 3.0-V         | PIN_AM5                  |

| GPIO0_D17   | GPIO Expansion 0 IO[17]          | 3.0-V         | PIN_AM10                 |

| GPIO0_D18   | GPIO Expansion 0 IO[18]          | 3.0-V         | PIN_AL10                 |

| GPIO0_D19   | GPIO Expansion 0 IO[19]          | 3.0-V         | PIN_AM8                  |

| GPIO0_D20   | GPIO Expansion 0 IO[20]          | 3.0-V         | PIN_AL8                  |

| GPIO0_D21   | GPIO Expansion 0 IO[21]          | 3.0-V         | PIN_AK8                  |

| GPIO0_D22   | GPIO Expansion 0 IO[22]          | 3.0-V         | PIN_AJ11                 |

| GPIO0_D23   | GPIO Expansion 0 IO[23]          | 3.0-V         | PIN_AK7                  |

| GPIO0_D24   | GPIO Expansion 0 IO[24]          | 3.0-V         | PIN_AJ5                  |

| GPIO Expansion 0 IO[25] | 3.0-V                                                                                                                                                                                                                   | PIN_AH12                                                                                                                                                                                                                                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO Expansion 0 IO[26] | 3.0-V                                                                                                                                                                                                                   | PIN_AG10                                                                                                                                                                                                                                                                      |

| GPIO Expansion 0 IO[27] | 3.0-V                                                                                                                                                                                                                   | PIN_AG13                                                                                                                                                                                                                                                                      |

| GPIO Expansion 0 IO[28] | 3.0-V                                                                                                                                                                                                                   | PIN_AG9                                                                                                                                                                                                                                                                       |

| GPIO Expansion 0 IO[29] | 3.0-V                                                                                                                                                                                                                   | PIN_AF11                                                                                                                                                                                                                                                                      |

| GPIO Expansion 0 IO[30] | 3.0-V                                                                                                                                                                                                                   | PIN_AT9                                                                                                                                                                                                                                                                       |

| GPIO Expansion 0 IO[31] | 3.0-V                                                                                                                                                                                                                   | PIN_AF10                                                                                                                                                                                                                                                                      |

| GPIO Expansion 0 IO[32] | 3.0-V                                                                                                                                                                                                                   | PIN_AD10                                                                                                                                                                                                                                                                      |

| GPIO Expansion 0 IO[33] | 3.0-V                                                                                                                                                                                                                   | PIN_AD9                                                                                                                                                                                                                                                                       |

| GPIO Expansion 0 IO[34] | 3.0-V                                                                                                                                                                                                                   | PIN_AD12                                                                                                                                                                                                                                                                      |

| GPIO Expansion 0 IO[35] | 3.0-V                                                                                                                                                                                                                   | PIN_AD13                                                                                                                                                                                                                                                                      |

|                         | GPIO Expansion 0 IO[26] GPIO Expansion 0 IO[27] GPIO Expansion 0 IO[28] GPIO Expansion 0 IO[29] GPIO Expansion 0 IO[30] GPIO Expansion 0 IO[31] GPIO Expansion 0 IO[32] GPIO Expansion 0 IO[33] GPIO Expansion 0 IO[34] | GPIO Expansion 0 IO[26] 3.0-V GPIO Expansion 0 IO[27] 3.0-V GPIO Expansion 0 IO[28] 3.0-V GPIO Expansion 0 IO[29] 3.0-V GPIO Expansion 0 IO[30] 3.0-V GPIO Expansion 0 IO[31] 3.0-V GPIO Expansion 0 IO[32] 3.0-V GPIO Expansion 0 IO[33] 3.0-V GPIO Expansion 0 IO[34] 3.0-V |

Table 2–13 GPIO Expansion Header (JP4) Pin Assignments, Schematic Signal Names, and Functions

| 0-4         | 8                       |              |                          |

|-------------|-------------------------|--------------|--------------------------|

| Schematic   | Description             | I/O Standard | Stratix IV GX Pin Number |

| Signal Name |                         |              |                          |

| GPIO1_D0    | GPIO Expansion 1 IO[0]  | 3.0-V        | PIN_AW5                  |

| GPIO1_D1    | GPIO Expansion 1 IO[1]  | 3.0-V        | PIN_AW8                  |

| GPIO1_D2    | GPIO Expansion 1 IO[2]  | 3.0-V        | PIN_AW4                  |

| GPIO1_D3    | GPIO Expansion 1 IO[3]  | 3.0-V        | PIN_AV10                 |

| GPIO1_D4    | GPIO Expansion 1 IO[4]  | 3.0-V        | PIN_AV8                  |

| GPIO1_D5    | GPIO Expansion 1 IO[5]  | 3.0-V        | PIN_AW10                 |

| GPIO1_D6    | GPIO Expansion 1 IO[6]  | 3.0-V        | PIN_AU10                 |

| GPIO1_D7    | GPIO Expansion 1 IO[7]  | 3.0-V        | PIN_AU8                  |

| GPIO1_D8    | GPIO Expansion 1 IO[8]  | 3.0-V        | PIN_AP8                  |

| GPIO1_D9    | GPIO Expansion 1 IO[9]  | 3.0-V        | PIN_AT10                 |

| GPIO1_D10   | GPIO Expansion 1 IO[10] | 3.0-V        | PIN_AU6                  |

| GPIO1_D11   | GPIO Expansion 1 IO[11] | 3.0-V        | PIN_AT6                  |

| GPIO1_D12   | GPIO Expansion 1 IO[12] | 3.0-V        | PIN_AU7                  |

| GPIO1_D13   | GPIO Expansion 1 IO[13] | 3.0-V        | PIN_AR5                  |

| GPIO1_D14   | GPIO Expansion 1 IO[14] | 3.0-V        | PIN_AP6                  |

| GPIO1_D15   | GPIO Expansion 1 IO[15] | 3.0-V        | PIN_AT7                  |

| GPIO1_D16   | GPIO Expansion 1 IO[16] | 3.0-V        | PIN_AN7                  |

| GPIO1_D17   | GPIO Expansion 1 IO[17] | 3.0-V        | PIN_AN6                  |

| GPIO1_D18   | GPIO Expansion 1 IO[18] | 3.0-V        | PIN_AL6                  |

| GPIO1_D19   | GPIO Expansion 1 IO[19] | 3.0-V        | PIN_AM6                  |

| GPIO1_D20   | GPIO Expansion 1 IO[20] | 3.0-V        | PIN_AL5                  |

| GPIO1_D21   | GPIO Expansion 1 IO[21] | 3.0-V        | PIN_AL9                  |

| GPIO1_D22   | GPIO Expansion 1 IO[22] | 3.0-V        | PIN_AK9                  |

| GPIO1_D23   | GPIO Expansion 1 IO[23] | 3.0-V        | PIN_AJ6                  |

| GPIO1_D24   | GPIO Expansion 1 IO[24] | 3.0-V        | PIN_AJ10                 |

| GPIO1_D25   | GPIO Expansion 1 IO[25] | 3.0-V        | PIN_AH11                 |

| GPIO1_D26 | GPIO Expansion 1 IO[26] | 3.0-V | PIN_AH8  |

|-----------|-------------------------|-------|----------|

| GPIO1_D27 | GPIO Expansion 1 IO[27] | 3.0-V | PIN_AH9  |

| GPIO1_D28 | GPIO Expansion 1 IO[28] | 3.0-V | PIN_AG12 |

| GPIO1_D29 | GPIO Expansion 1 IO[29] | 3.0-V | PIN_AH10 |

| GPIO1_D30 | GPIO Expansion 1 IO[30] | 3.0-V | PIN_AF13 |

| GPIO1_D31 | GPIO Expansion 1 IO[31] | 3.0-V | PIN_AE13 |

| GPIO1_D32 | GPIO Expansion 1 IO[32] | 3.0-V | PIN_AE10 |

| GPIO1_D33 | GPIO Expansion 1 IO[33] | 3.0-V | PIN_AP10 |

| GPIO1_D34 | GPIO Expansion 1 IO[34] | 3.0-V | PIN_AE12 |

| GPIO1_D35 | GPIO Expansion 1 IO[35] | 3.0-V | PIN_AE11 |

Table 2–14 External 14-pin Expansion Header (JP6) Pin Assignments, Schematic Signal Names, and Functions

| Schematic<br>Signal Name | Description                      | I/O Standard  | Stratix IV GX Pin Number |

|--------------------------|----------------------------------|---------------|--------------------------|

| GPIO0_D0                 | GPIO Expansion 0 IO[0](Clock In) | 3.0-V or LVDS | PIN_AF6                  |

| GPIO0_D1                 | GPIO Expansion 0 IO[1]           | 3.0-V         | PIN_AU9                  |

| GPIO0_D2                 | GPIO Expansion 0 IO[2](Clock In) | 3.0-V or LVDS | PIN_AE5                  |

| GPIO0_D3                 | GPIO Expansion 0 IO[3]           | 3.0-V         | PIN_AR8                  |

| GPIO0_D4                 | GPIO Expansion 0 IO[4]           | 3.0-V         | PIN_AN9                  |

| GPIO0_D5                 | GPIO Expansion 0 IO[5]           | 3.0-V         | PIN_AP9                  |

| GPIO0_D6                 | GPIO Expansion 0 IO[6]           | 3.0-V         | PIN_AV5                  |

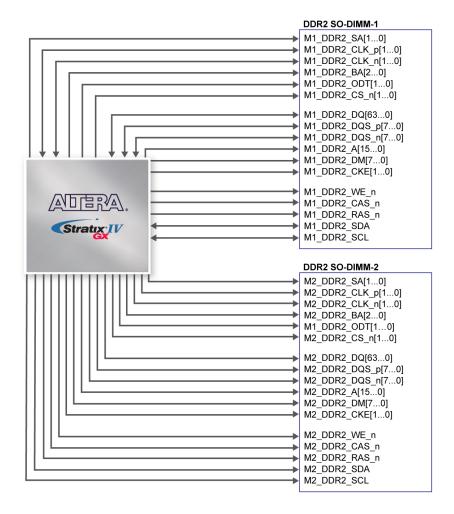

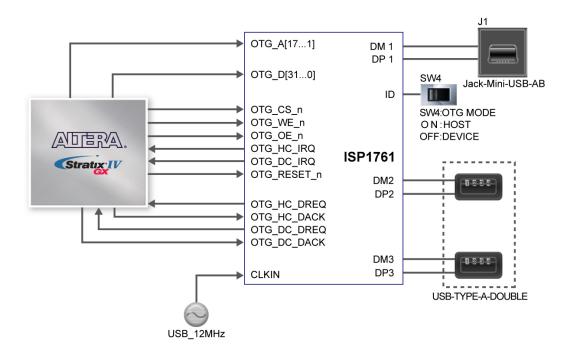

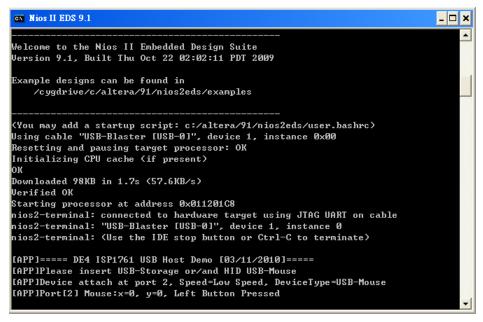

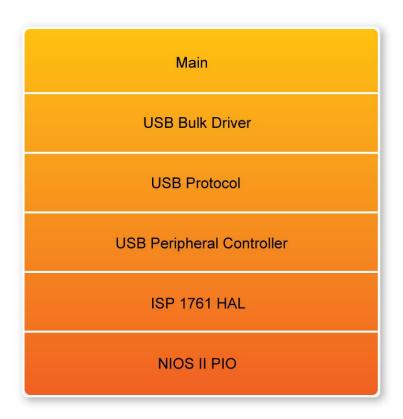

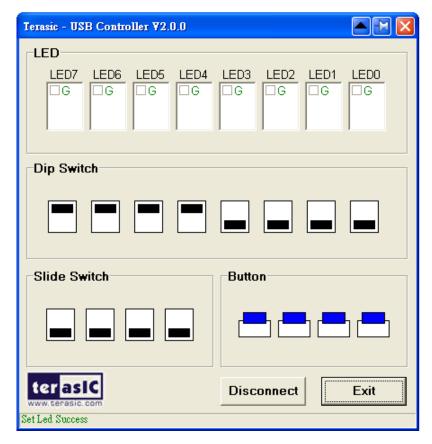

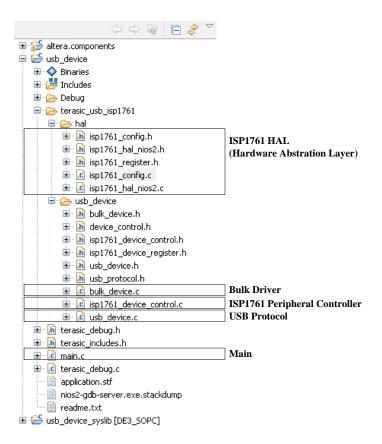

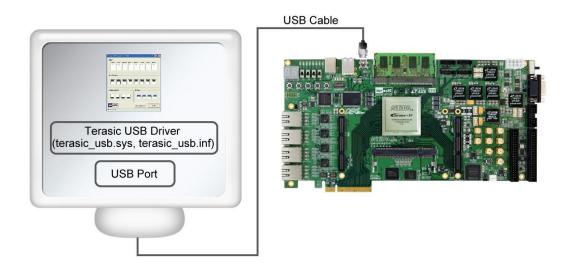

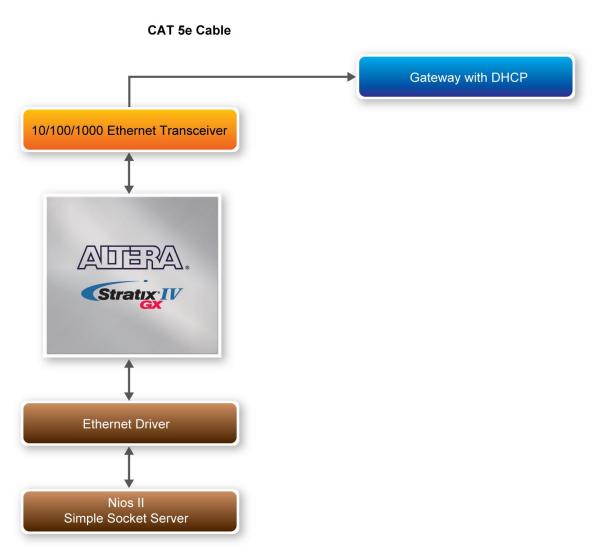

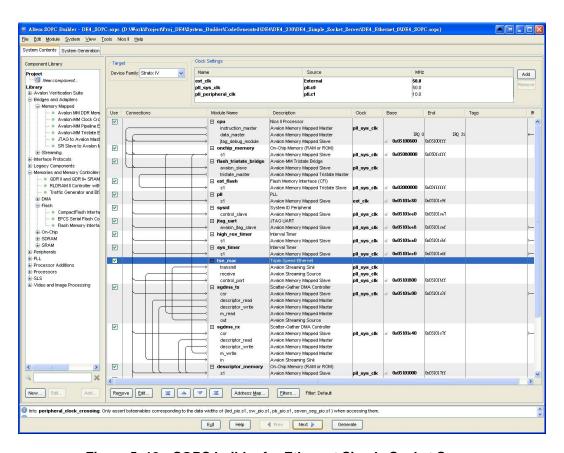

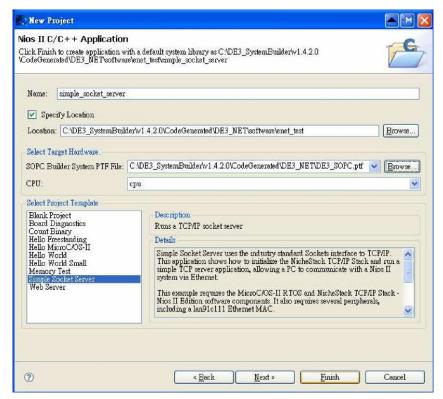

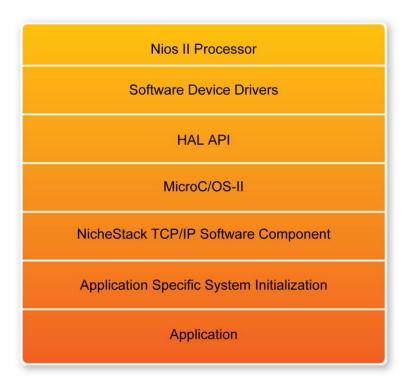

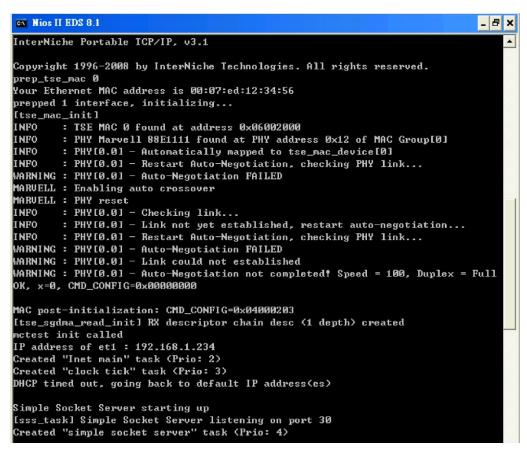

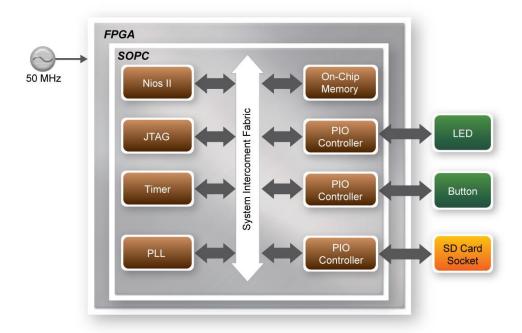

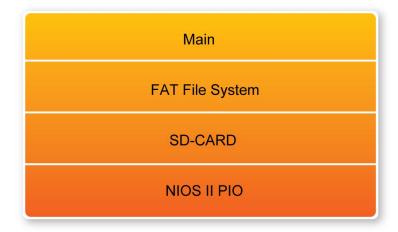

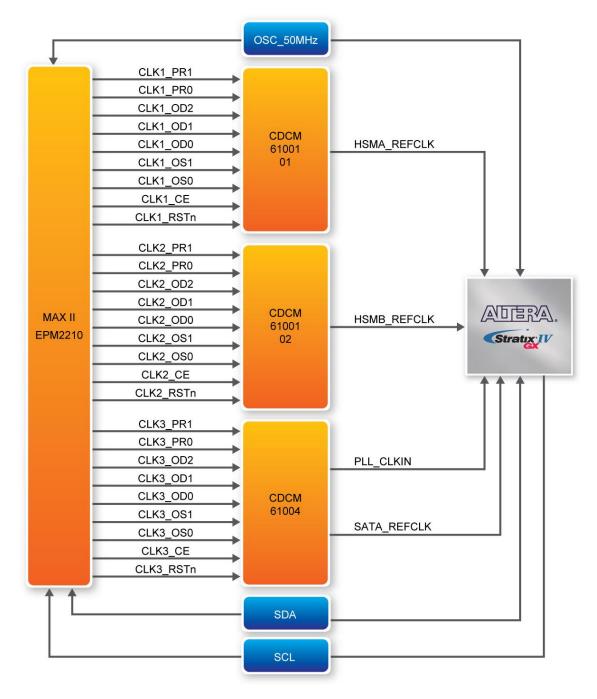

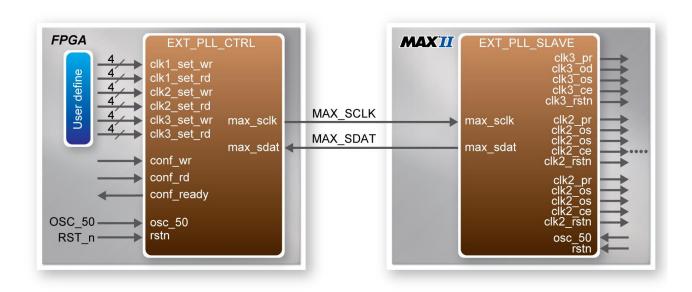

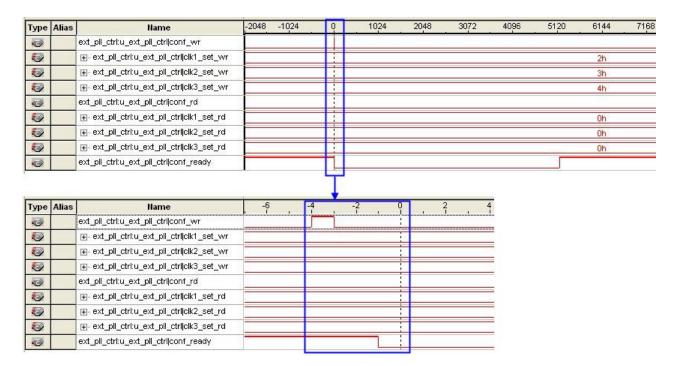

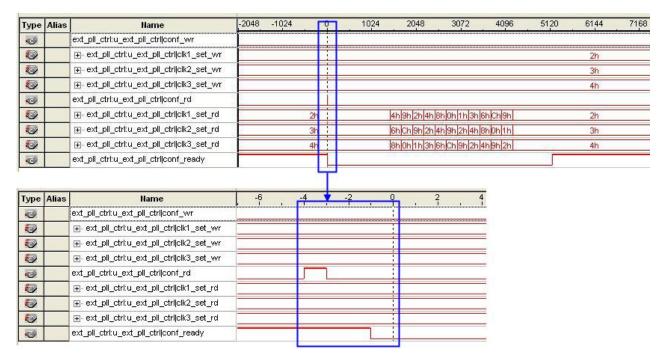

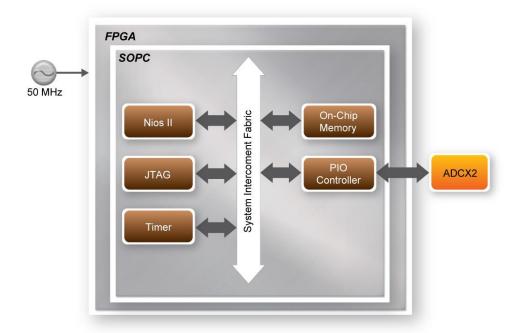

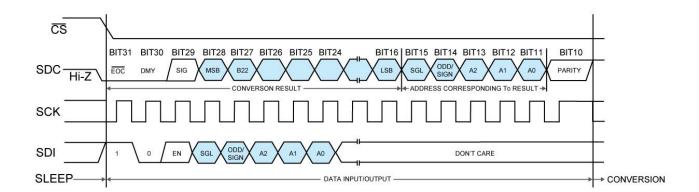

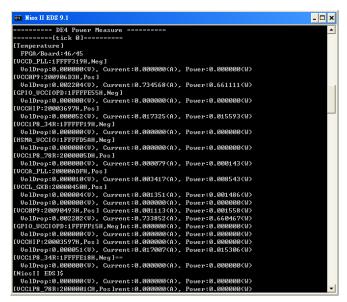

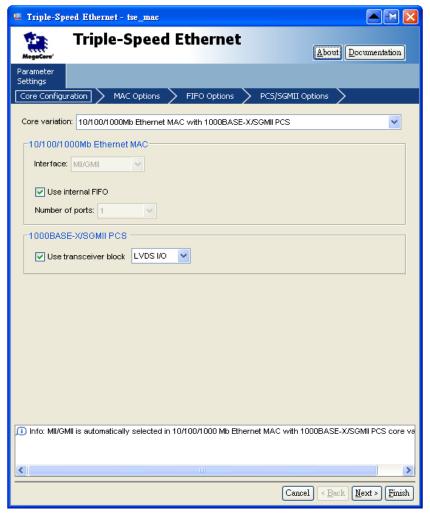

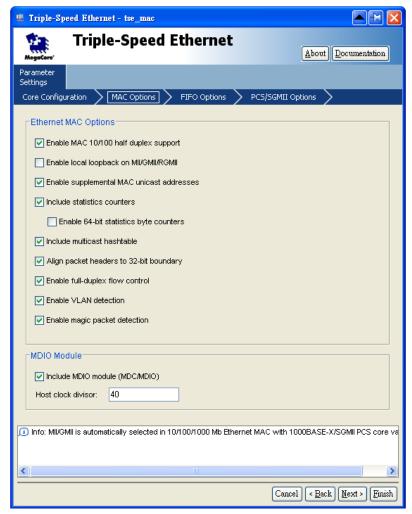

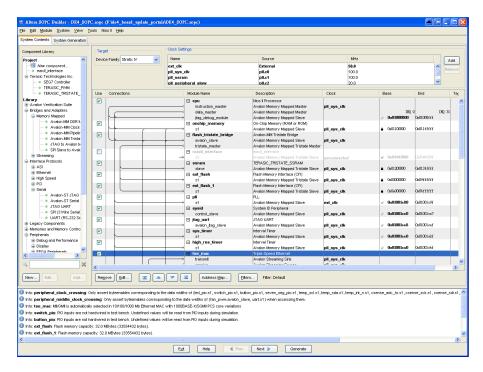

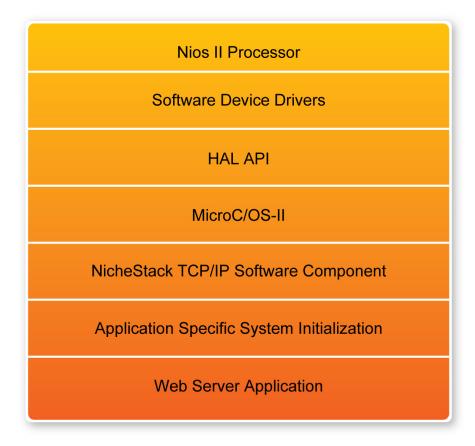

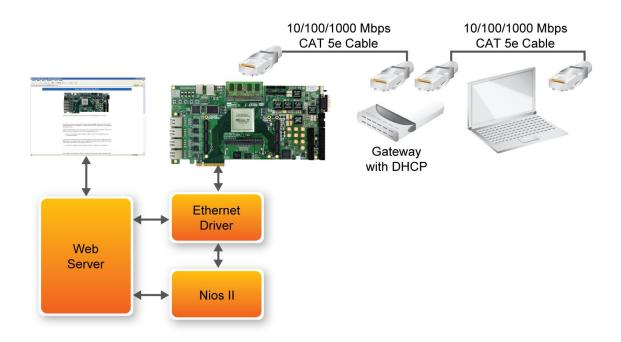

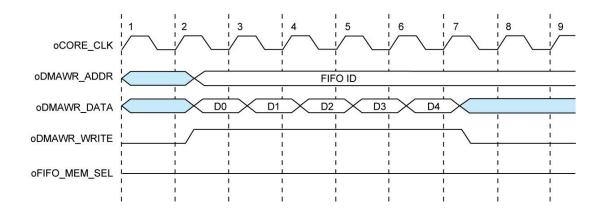

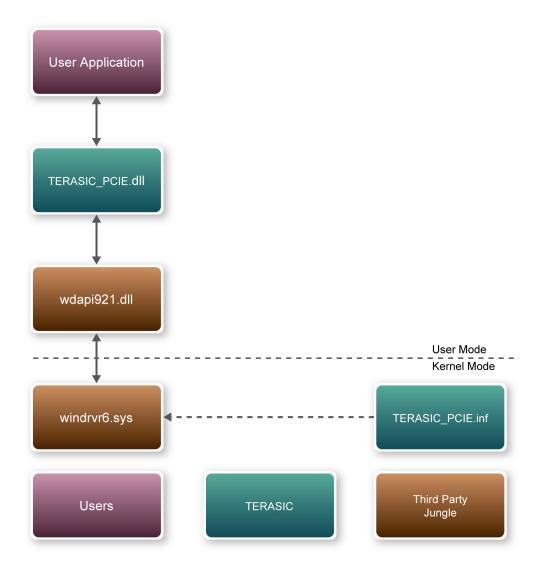

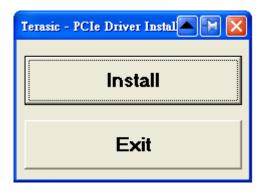

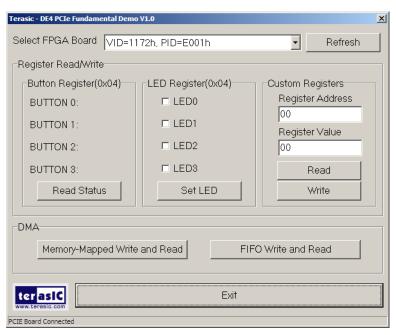

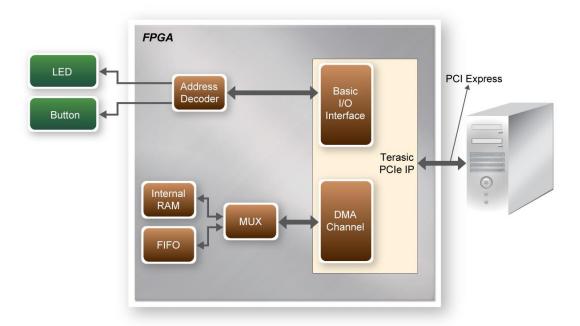

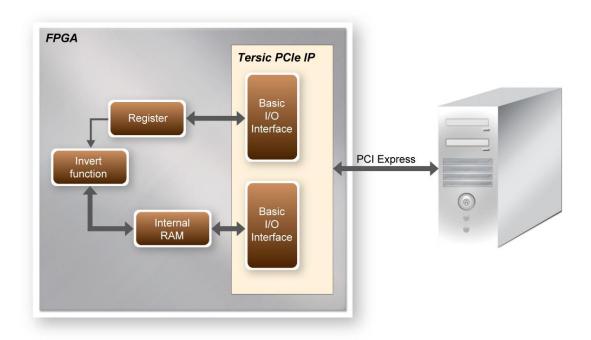

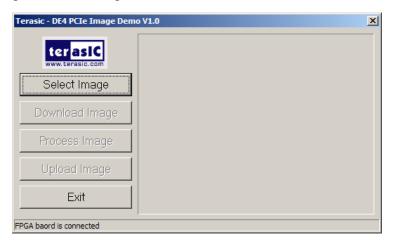

### 2.7 DDR2 SO-DIMM