Copyright © Terasic Inc. All rights reserved.

# **Content**

| Chapter 1        | OpenVINO Stater Kit GT Edition                         | 4   |

|------------------|--------------------------------------------------------|-----|

| 1.1 Package C    | ontents                                                | 4   |

| 1.2 OpenVINO     | O Starter Kit GT Edition System CD                     | 5   |

|                  | elp                                                    |     |

| Chapter 2        | Introduction of the OpenVINO Starter Kit GT Edition    | n 6 |

| 2.1 Layout and   | d Components                                           | 6   |

| 2.2 Block Diag   | gram of the OpenVINO Starter Kit GT Edition            | 7   |

| Chapter 3        | Using the OpenVINO Starter Kit GT Edition              | 10  |

| 3.1 Configurin   | g the Cyclone V FPGA                                   | 10  |

| 3.2 Board Stat   | us Elements                                            | 15  |

| 3.3 Clock Circ   | uitry                                                  | 16  |

| 3.4 Peripherals  | s Connected to the FPGA                                | 16  |

|                  | Push-buttons, Switches and LEDs                        |     |

|                  | gment Displays                                         |     |

| 3.4.3 SDR        | AM Memory                                              | 21  |

| 3.4.4 DDR        | 3 Memory                                               | 22  |

| 3.4.5 UAR        | T to USB                                               | 25  |

| 3.4.6 Ardu       | ino Uno R3 Expansion Header                            | 26  |

| 3.4.7 2x20       | GPIO Expansion Header                                  | 31  |

| Chapter 4        | OpenVINO Starter Kit GT Edition System Builder         | 37  |

| 4.1 Introduction | on                                                     | 37  |

| 4.2 General De   | esign Flow                                             | 37  |

|                  | nVINO Starter Kit GT Edition System Builder            |     |

| Chapter 5        | Examples of Advanced Demonstrations                    | 44  |

| 5.1 OpenVINO     | O Starter Kit GT Edition Factory Default Configuration | 44  |

| 5.2 Nios II SDI                  | RAM Test45                          |  |  |  |  |

|----------------------------------|-------------------------------------|--|--|--|--|

| 5.3 Verilog SD                   | RAM Test48                          |  |  |  |  |

| 5.4 DDR3 SDR                     | RAM Test50                          |  |  |  |  |

| 5.5 DDR3 SDR                     | RAM Test by Nios II                 |  |  |  |  |

| 5.6 UART Con                     | trol                                |  |  |  |  |

| 5.7 ADC Readi                    | ing59                               |  |  |  |  |

| Chapter 6                        | Programming the EPCQ64              |  |  |  |  |

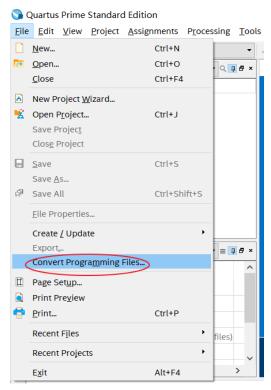

| 6.1 Convert .so                  | of File to .jic File64              |  |  |  |  |

| 6.2 Write a .jic                 | File to the EPCQ67                  |  |  |  |  |

| 6.3 Erase the E                  | PCQ device69                        |  |  |  |  |

| Chapter 7                        | PCIe Reference Design for Windows70 |  |  |  |  |

| 7.1 PCI Expres                   | s System Infrastructure70           |  |  |  |  |

| 7.2 PCI Expres                   | s Software SDK71                    |  |  |  |  |

| 7.3 PCI Expres                   | s Software Stack71                  |  |  |  |  |

| 7.4 PCIe Librai                  | ry API                              |  |  |  |  |

| 7.5 PCIe Refer                   | ence Design - Fundamental81         |  |  |  |  |

| 7.6 PCIe Refer                   | ence Design – DDR3 <b>86</b>        |  |  |  |  |

| Chapter 8                        | PCIe Reference Design for Linux93   |  |  |  |  |

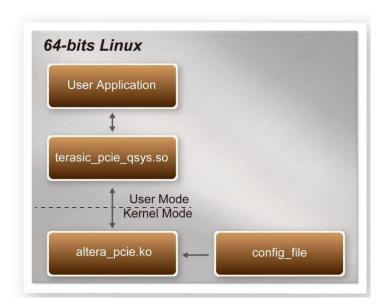

| 8.1 PCI Expres                   | s System Infrastructure93           |  |  |  |  |

| 8.2 PCI Expres                   | s Software SDK94                    |  |  |  |  |

| 8.3 PCI Expres                   | s Software Stack94                  |  |  |  |  |

| 8.4 PCI Expres                   | s Library API97                     |  |  |  |  |

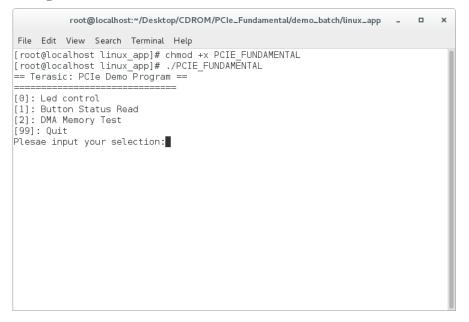

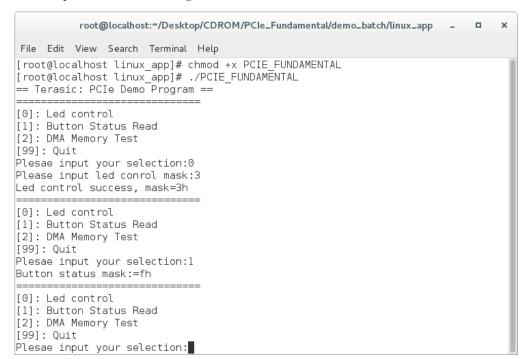

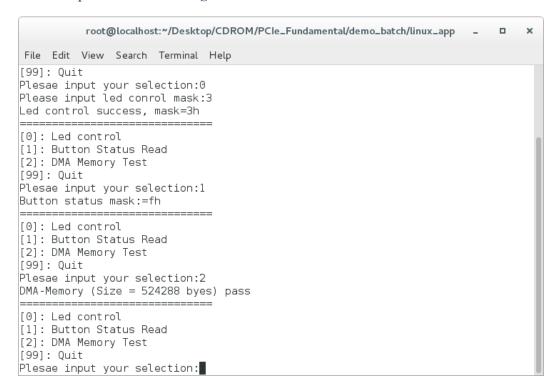

| 8.5 PCIe Refer                   | ence Design – Fundamental97         |  |  |  |  |

| 8.6 PCIe Reference Design – DDR3 |                                     |  |  |  |  |

# **Chapter 1**

# OpenVINO Stater Kit GT Edition

The OpenVINO Starter Kit GT Edition presents a robust hardware design platform built around the Intel Cyclone V FPGA, it also provides a powerful platform of reconfigurable power with high performance and low power processing system. The OpenVINO Starter Kit GT Edition is equipped with PCIe Gen2x4, high-speed DDR3 memory, GPIO, Arduino and much more that promises many exciting applications.

The OpenVINO Starter Kit GT Edition is equipped with PCIe Gen2x4 interface, it is low development cost, and can support users who develop mainstream applications and OpenCL applications based on PCIe, as well as a wide range of high-speed connectivity applications.

The OpenVINO Starter Kit GT Edition contains all the tools needed to use the board in conjunction with a computer that runs the Microsoft Windows 7 or later.

## 1.1 Package Contents

Figure 1-1 OpenVINO Starter Kit GT Edition package contents

## OpenVINO Starter Kit GT Edition package includes

- 1. OpenVINO Starter Kit GT Edition

- 2. OpenVINO Starter Kit GT Edition Quick Start Guide

- 3. PCIe Bracket (Installed)

- 4. Fan (Installed)

- 5. Screw and Silicon Footstands Package

- 6. AC Power Cord

- 7. Power Adapter

- 8. USB to mini-USB Cable

## 1.2 OpenVINO Starter Kit GT Edition System CD

The OpenVINO Starter Kit GT Edition System CD contains all the documents and supporting materials associated with OpenVINO Starter Kit GT Edition, including the user manual, system builder, reference designs, and device datasheets. Users can download this system CD from the link <a href="http://OpenVINO Starter Kit.terasic.com/">http://OpenVINO Starter Kit.terasic.com/</a>.

## 1.3 Getting Help

Here are the addresses where you can get help if you encounter any problems:

- Terasic Inc.

- 9F., No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan

- Email: support@terasic.com.cn

- Tel.: +886-3-575-0880

- Website: http://OpenVINO Starter Kit.terasic.com/

# Chapter 2

# Introduction of the OpenVINO Starter Kit GT Edition

This chapter provides an introduction to the features and design characteristics of the OpenVINO Starter Kit GT Edition.

## 2.1 Layout and Components

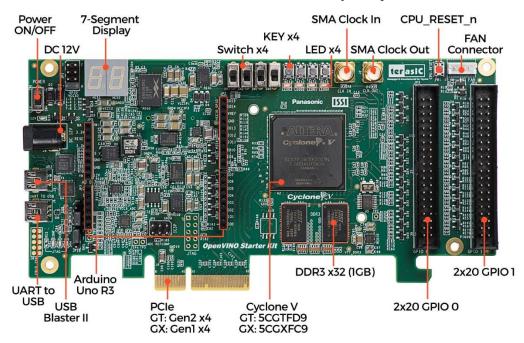

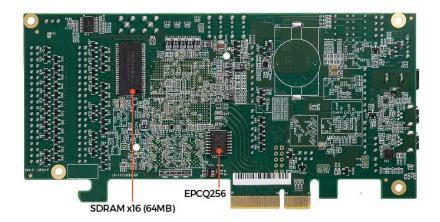

**Figure 2-1** and **Figure 2-2** shows a photograph of the board. It depicts the layout of the board and indicates the location of the connectors and key components.

Figure 2-1 OpenVINO Starter Kit GT Edition (top view)

Figure 2-2 OpenVINO Starter Kit GT Edition (bottom view)

The OpenVINO Starter Kit GT Edition board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects:

- Intel FPGA Cyclone® V GT 5CGTFD9D5F27C7N device

- Serial configuration device EPCQ256

- USB-Blaster II onboard for programming; JTAG Mode

- UART to USB (USB Mini-B connector)

- PCIe Gen2x4

- 1GB DDR3 SDRAM (32-bit data bus)

- 64MB SDRAM (16-bit data bus)

- 4 push-buttons

- 4 slide switches

- 4 green LED

- Two 7-segment displays

- Four 50MHz clock sources from the clock generator

- One Arduino header

- Two 40 pin GPIO header

# 2.2 Block Diagram of the OpenVINO Starter Kit GT Edition

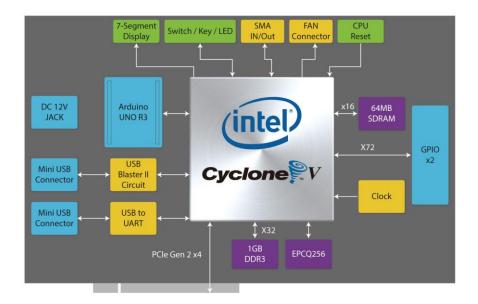

**Figure 2-3** is the block diagram of the board. All the connections are established through the Cyclone V FPGA device to provide maximum flexibility for users. Users can configure the FPGA to implement any system design.

Figure 2-3 Block diagram of OpenVINO Starter Kit GT Edition board

Detailed information about Figure 2-3 are listed below.

#### **■** FPGA Device

- Cyclone V 5CGTFD9D5F27C7N device

- 301K programmable logic elements

- 13,917 Kbit/s embedded memory

- 8 fractional PLLs

- 2 hard memory controllers

- Nine 3.125G Transceivers

## **■** Configuration and Debug

- Quad Serial Configuration device EPCQ256

- Onboard USB-Blaster II (Mini-B USB connector)

### **■** Memory Device

- 64MB (32Mx16) SDRAM

- 1GB (2x256Mx16) DDR3 SDRAM

#### **■** Communication

- UART to USB (USB Mini-B connector)

- PCIe Gen2x4

#### Connectors

- Two 40 Pin GPIO header, features of each GPIO connector

- 36 General GPIO Pins

- Support to configure 8 LVDS TX and LVDS RX

- With diode protection

- Configurable I/O standards (voltage levels: 3.3/2.5/1.8/1.5V)

- One Arduino Uno Revision 3 header

- Analog ADC

- Interface: SPI

- Fast through put rate: 500Ksps

- Channel number: 8

- Resolution: 12-bit

- Analog input range:  $0 \sim 4.096 \text{ V}$

- Digital IO

- With diode protection

- SMA IN/OUT 3.3V Single-end input and output

#### ■ Switches/ Buttons/ Indicators

- 5 user Keys (4 general keys, 1 CPU\_RESET\_n)

- 4 user switches

- 4 LEDG

- Two 7-segment displays

#### ■ Power

- 12V DC Input

- PCIe 12V Input

## **■** Cooling System

• 12V Fan with 5000 Rotational Speed

# Chapter 3

# Using the OpenVINO Starter Kit GT Edition

This chapter provides instructions to how to use the board and describes the peripherals.

## 3.1 Configuring the Cyclone V FPGA

There are two types of programming method supported by OpenVINO Starter Kit GT Edition:

- 1. JTAG programming: It is named after the IEEE standards Joint Test Action Group. The configuration bitstream is downloaded directly into the Cyclone V FPGA. The FPGA will retain its current status as long as power is applied to the board; the configuration information will be lost when the power is off.

- 2. AS programming: The other programming method is Active Serial configuration. The configuration bitstream is downloaded into the Intel FPGA EPCQ256 device, which provides non-volatile storage for the bit stream. The information is retained within EPCQ256 even if the OpenVINO Starter Kit GT Edition board is turned off. When the board is powered on, the configuration data in the EPCQ256 device is automatically loaded into the Cyclone V FPGA.

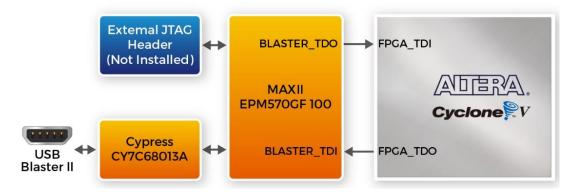

## ■ JTAG Chain on the OpenVINO Starter Kit GT Edition Board

The FPGA device can be configured through JTAG interface on the OpenVINO Starter Kit GT Edition board, but the JTAG chain must form a closed loop, which allows a Quartus Prime programmer to detect the FPGA device.

Figure 3-1 illustrates the JTAG chain on the OpenVINO Starter Kit GT Edition board.

Figure 3-1 Path of the JTAG chain

### ■ Configure the FPGA in JTAG Mode

There is one FPGA device on the JTAG chain. The following shows how the FPGA is programmed in JTAG mode step by step.

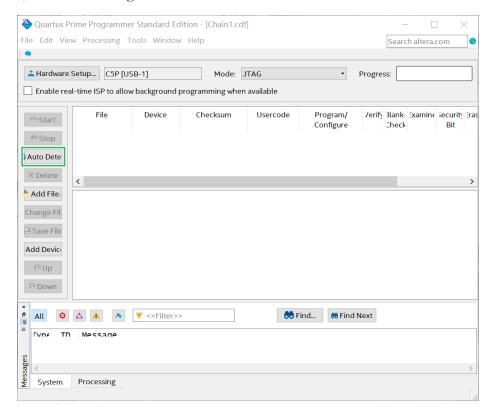

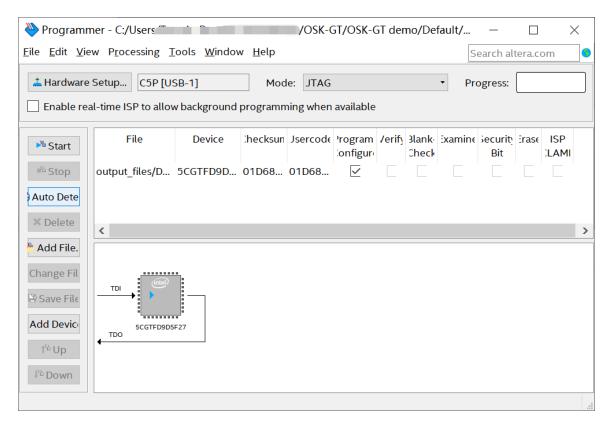

1. Open the Quartus Prime programmer under Quartus Prime Tools and click "Auto Detect", as circled in **Figure 3-2**.

Figure 3-2 Detect FPGA device in JTAG mode

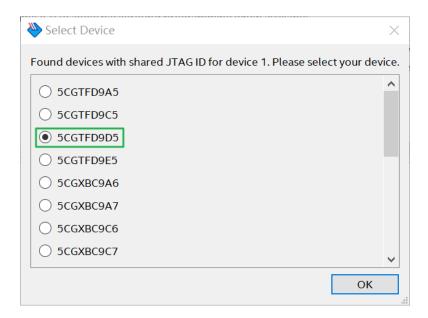

2. Select detected device associated with the board, as circled in **Figure 3-3**.

Figure 3-3 Select 5CGTFD9D5

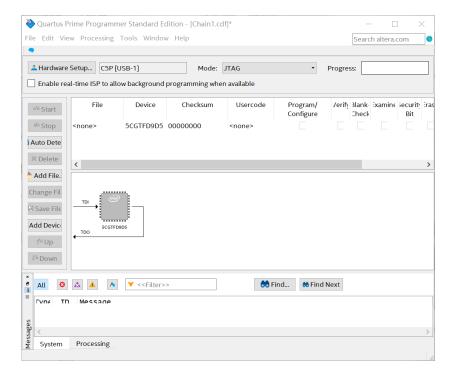

3. The FPGA is detected, as shown in **Figure 3-4**.

Figure 3-4 FPGA detected in Quartus programmer

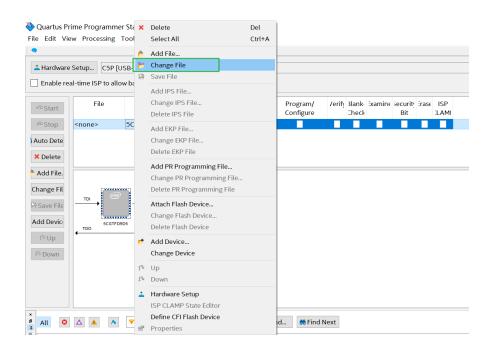

4. Right click on the FPGA device and select Change File to open the .sof file to be programmed, as highlighted in **Figure 3-5**.

Figure 3-5 Open the .sof file to be programmed into the FPGA device

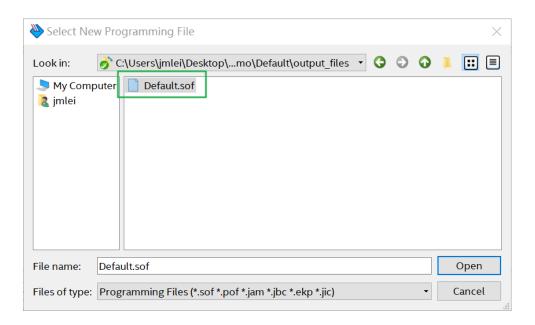

5. Select the .sof file to be programmed, as shown in **Figure 3-6**.

Figure 3-6 Select the .sof file to be programmed into the FPGA device

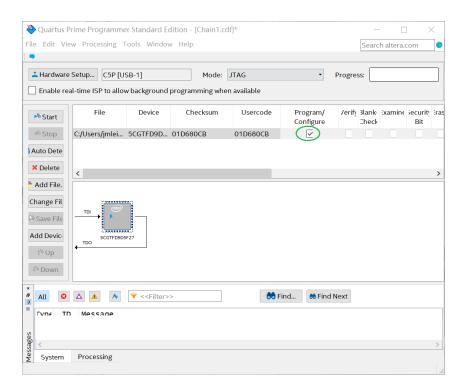

6. Click "Program/Configure" check box and then click "Start" button to download the .sof file into the FPGA device, as shown in **Figure 3-7**.

Figure 3-7 Program .sof file into the FPGA device

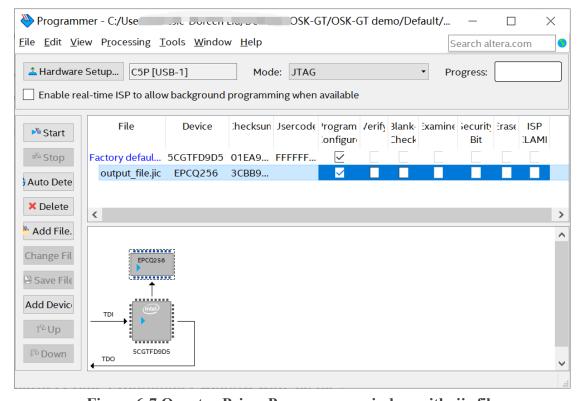

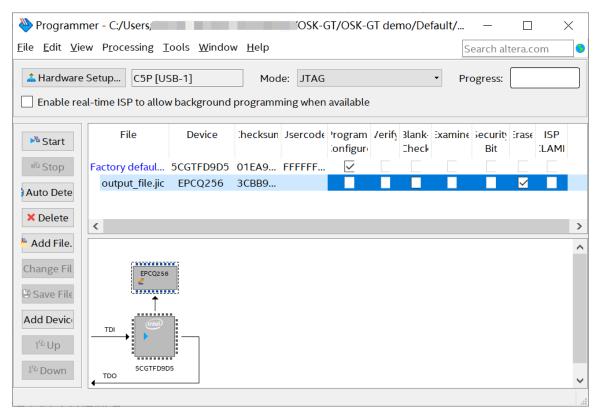

#### ■ Configure the FPGA in AS Mode

- The OpenVINO Starter Kit GT Edition board uses the EPCQ256 device to store configuration data for the Cyclone V FPGA. This configuration data is automatically loaded from the quad serial configuration device chip into the FPGA when the board is powered up

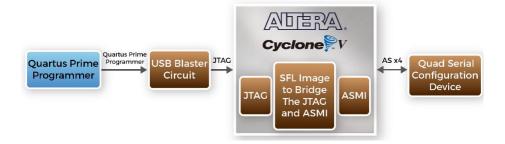

- Users need to use Serial Flash Loader (SFL) to program the EPCQ256 device via JTAG interface.

- The FPGA-based SFL is a soft intellectual property (IP) core within the FPGA that bridges the JTAG and Flash interfaces. The SFL Megafunction is available in the Quartus Prime. **Figure 3-8** shows the programming method when adopting SFL solution.

- Please refer to Chapter 6 Program the EPCQ for the basic programming instructions on the serial configuration device.

Figure 3-8 Programming a quad serial configuration device with SFL solution

## 3.2 Board Status Elements

In addition to the 4 LEDs that the FPGA device can control, there are 4 indicators which can indicate the board status, as shown in **Figure 3-9**, please refer to the details in **Table 3-1**.

Figure 3-9 LED Indicators on the OpenVINO Starter Kit GT Edition

**Table 3-1 LED Indicators**

| LED Name | Signal Name | Description                                   |

|----------|-------------|-----------------------------------------------|

| D10      | 12V Power   | Light up when 12V power is active             |

| D43      | JTAG_RX     | Light up when USB Blaster II receives data    |

| D44      | JTAG_TX     | Light up when USB Blaster II transmits data   |

| D42      | CONF_DONE   | Light up when FPGA is configured successfully |

## 3.3 Clock Circuitry

**Figure 3-10** shows the default frequency of all external clocks to the Cyclone V FPGA. The 50MHz is generated by a crystal oscillator. The 50MHz clock signals connected to the FPGA are used as clock sources for user logic. The board also includes two SMA connectors which can be used to connect an external clock source to the board or to drive a clock signal in/out through the SMA connector. All these clock inputs are connected to the phase locked loops (PLL) clock input pins of the FPGA to allow users to use these clocks as a source clock for the PLL circuit.

The associated pin assignment for clock inputs to FPGA I/O pins is listed in **Table 3-2**.

Figure 3-10 Block diagram of the clock distribution on OpenVINO Starter Kit GT

Edition

**FPGA Pin Signal Name** Direction **Description** I/O Standard No. CLOCK 50 B3B 1.5 V PIN T13 Input 50MHz clock input (Bank 3B) CLOCK 50 B4A 50MHz clock input (Bank 4A) 1.5 V PIN U12 Input CLOCK 50 B5B PIN R20 50MHz clock input (Bank 5B) 3.3-V LVTTL Input CLOCK 50 B6A PIN N20 Input 50MHz clock input (Bank 6A) 3.3-V LVTTL CLOCK 50 B7A PIN H12 Input 50MHz clock input (Bank 7A) 3.3-V LVTTL CLOCK 50 B8A 50MHz clock input (Bank 8A) 3.3-V LVTTL PIN N9 Input SMA CLKIN PIN T21 Externa (SMA) clock input 3.3-V LVTTL Input SMA CLKOUT PIN Y25 Output Externa (SMA) clock output 3.3-V LVTTL

**Table 3-2 Pin Assignment of Clock Inputs**

## 3.4 Peripherals Connected to the FPGA

This section describes the interfaces connected to the FPGA. Users can control or monitor different interfaces with user logic from the FPGA.

## 3.4.1 User Push-buttons, Switches and LEDs

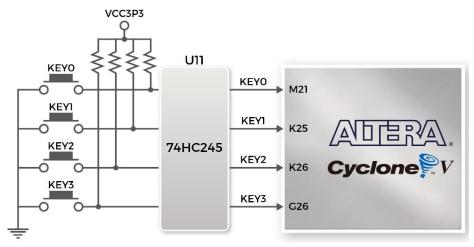

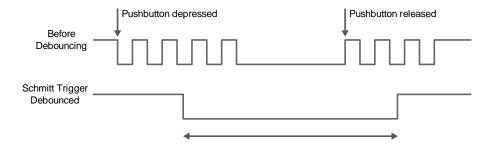

The board has four push-buttons connected to the FPGA, as shown in Figure 3-11. Schmitt

trigger circuit is implemented and acts as a switch debounce in **Figure 3-12** for the push-buttons connector. The four push-buttons are named KEY0, KEY1, KEY2, and KEY3; they are coming out of the Schmitt trigger device and are connected directly to the Cyclone V FPGA. The push-button generates a high logic level when it is not pressed and provides a low logic level when pressed. Since the push-buttons are debounced, they can be used as reset inputs in a circuit.

Figure 3-11 Connections between the push-buttons and the Cyclone V FPGA

Figure 3-12 Switch debouncing

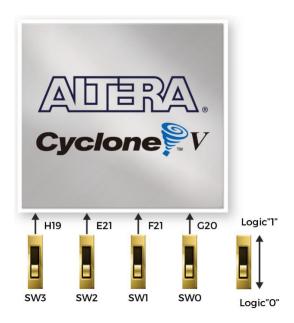

There are four slide switches connected to the FPGA, as shown in **Figure 3-13**. These switches are not debounced and are to be used as level-sensitive data inputs to a circuit. Each switch is connected directly and individually to the FPGA. When the switch is set to the DOWN position (towards the edge of the board), it generates a low logic level to the FPGA. When the switch is set to the UP position, a high logic level is generated to the FPGA.

Figure 3-13 Connections between the slide switches and Cyclone V FPGA

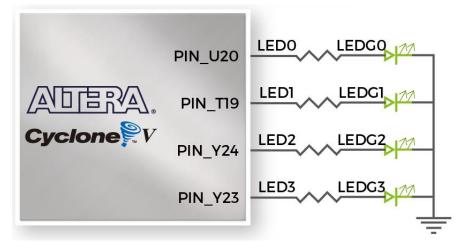

There are also four user-controllable LEDs connected to the FPGA. Each LED is driven directly and individually by the Cyclone V FPGA; driving its associated pin to a high logic level or low level to turn the LED on or off, respectively. **Figure 3-14** shows the connections between LEDs and Cyclone V FPGA. **Table 3-3**, **Table 3-4** and **Table 3-5** list the pin assignment of user push-buttons, switches, and LEDs.

Figure 3-14 Connections between the LEDs and the Cyclone V FPGA

Table 3-3 Pin Assignment of Slide Switches

| Switch Name | FPGA Pin No. | Direction | Description      | I/O Standard |

|-------------|--------------|-----------|------------------|--------------|

| SW[0]       | PIN_G20      | Input     | Slide Switch [0] | 3.3-V LVTTL  |

| SW[1]       | PIN_F21      | Input     | Slide Switch [1] | 3.3-V LVTTL  |

| SW[2] | PIN_E21 | Input | Slide Switch [2] | 3.3-V LVTTL |

|-------|---------|-------|------------------|-------------|

| SW[3] | PIN_H19 | Input | Slide Switch [3] | 3.3-V LVTTL |

**Table 3-4 Pin Assignment of Push-buttons**

| Key Name    | FPGA Pin No. | Direction | Description                                                           | I/O<br>Standard |  |

|-------------|--------------|-----------|-----------------------------------------------------------------------|-----------------|--|

| CPU_RESET_n | PIN_AB24     | Input     | Generate a high logic level when it is not pressed                    | 3.3-V<br>LVTTL  |  |

| KEY[0]      | PIN_M21      | Input     |                                                                       | 3.3-V<br>LVTTL  |  |

| KEY[1]      | PIN_K25      | Input     | Generate a high logic level when it is not pressed. Four push-buttons |                 |  |

| KEY[2]      | PIN_K26      | Input     | (KEY0, KEY1, KEY2 and KEY3) are debounced.                            | 3.3-V<br>LVTTL  |  |

| KEY[3]      | PIN_G26      | Input     |                                                                       | 3.3-V<br>LVTTL  |  |

Table 3-5 LED Pin Assignment of LEDs

|             | 140.10 0 1 110.00 01 1110.00 01 1110.00 01 1110.00 01 1110.00 01 1110.00 01 1110.00 01 1110.00 01 1110.00 01 11 |           |                                                    |                 |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------|-----------------|--|--|

| LED<br>Name | FPGA Pin No.                                                                                                    | Direction | Description                                        | I/O<br>Standard |  |  |

| LED[0]      | PIN_U20                                                                                                         | Output    |                                                    | 3.3-V<br>LVTTL  |  |  |

| LED[1]      | PIN_T19                                                                                                         | Output    | Drive high logic 1 to I/O pin to turn the LED on.  | 3.3-V<br>LVTTL  |  |  |

| LED[2]      | PIN_Y24                                                                                                         | Output    | Drive lowh logic 0 to I/O pin to turn the LED off. | 3.3-V<br>LVTTL  |  |  |

| LED[3]      | PIN_Y23                                                                                                         | Output    |                                                    | 3.3-V<br>LVTTL  |  |  |

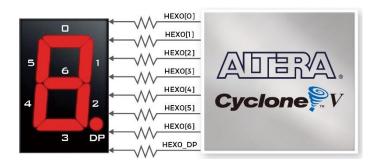

## 3.4.2 7-Segment Displays

OpenVINO Starter Kit GT Edition has two 7-segment displays. **Figure 3-15** shows the connection of seven segments (common anode) to pins on Cyclone V FPGA. The segment can be turned on or off by applying a low logic level or high logic level from the FPGA, respectively. Each segment in a display is indexed from 0 to 6, with the corresponding positions given in the **Figure 3-15**. **Table 3-6** shows the pin assignment of FPGA to the 7-

segment displays.

Figure 3-15 Connections between the 7-segment displays and Cyclone V FPGA

Table 3-6 Pin Assignment of 7-segment Displays

| HIEW NI    | FPGA Pin            | D: 4:     | D '4'                    | I/O      |

|------------|---------------------|-----------|--------------------------|----------|

| HEX Name   | No.                 | Direction | Description              | Standard |

| HEX0 DP    | PIN AA6             | Output    | Seven Segment Digit 0 DP | 3.3-V    |

| HEAU_DF    | rin_AA0             | Output    | Seven Segment Digit 0 DF | LVTTL    |

| HEX0[0]    | PIN T8              | Output    | Seven Segment Digit 0[0] | 3.3-V    |

| IILAU[U]   | 1111_10             |           | Seven Segment Digit 0[0] | LVTTL    |

| HEX0[1]    | PIN P26             | Output    | Seven Segment Digit 0[1] | 3.3-V    |

| IILAU[1]   | 1111_120            |           | Seven Segment Digit 0[1] | LVTTL    |

| HEX0[2]    | PIN V8              | Output    | Seven Segment Digit 0[2] | 3.3-V    |

| IILA0[2]   | 1111_10             |           | Seven Segment Digit 0[2] | LVTTL    |

| HEX0[3]    | PIN U7              | Output    | Seven Segment Digit 0[3] | 3.3-V    |

| TIEA0[3]   | 1111_07             |           | Seven Segment Digit 0[3] | LVTTL    |

| HEX0[4]    | PIN U25             | Output    | Seven Segment Digit 0[4] | 3.3-V    |

| TIL/XV[+]  | 1111_023            |           | Seven Segment Digit 0[4] | LVTTL    |

| HEX0[5]    | PIN W8              | Output    | Seven Segment Digit 0[5] | 3.3-V    |

| 111210[3]  | 1111_1110           |           | Seven segment Bight o[3] | LVTTL    |

| HEX0[6]    | PIN U26             | Output    | Seven Segment Digit 0[6] | 3.3-V    |

| TILMO[0]   | 1111_020            |           | Seven Segment Digit 0[0] | LVTTL    |

| HEX1 DP    | PIN V25             | Output    | Seven Segment Digit 1 DP | 3.3-V    |

| TILXI_DI   | 1111_123            |           | Seven Segment Digit 1 Di | LVTTL    |

| HEX1[0]    | EX1[0] PIN T7 Outpu | Output    | Seven Segment Digit 1[0] | 3.3-V    |

| TIL/XI[0]  | 111,_1,             |           | Seven Segment Digit I[0] | LVTTL    |

| HEX1[1]    | PIN W20             | Output    | Seven Segment Digit 1[1] | 3.3-V    |

| 1112/11[1] | 1111_1120           |           | Seven Segment Digit 1[1] | LVTTL    |

| HEX1[2]    | PIN_AB6             | Output    | Seven Segment Digit 1[2] | 3.3-V    |

|          |          |        |                           | LVTTL |

|----------|----------|--------|---------------------------|-------|

| HEV1[2]  | DIN AC22 | Output | Savan Saamant Dinit 1521  | 3.3-V |

| HEX1[3]  | PIN_AC22 |        | Seven Segment Digit 1[3]  | LVTTL |

| 11EV1[/] | DIN VO   | Output | Savan Saamant Dinit 1[4]  | 3.3-V |

| HEX1[4]  | PIN_Y9   |        | Seven Segment Digit 1[4]  | LVTTL |

| HEXALE]  | DIN W21  | Output | Course Comment Divit 1551 | 3.3-V |

| HEX1[5]  | PIN_W21  |        | Seven Segment Digit 1[5]  | LVTTL |

| HEX1[6]  | PIN_N25  | Output | G G (D) (416)             | 3.3-V |

|          |          |        | Seven Segment Digit 1[6]  | LVTTL |

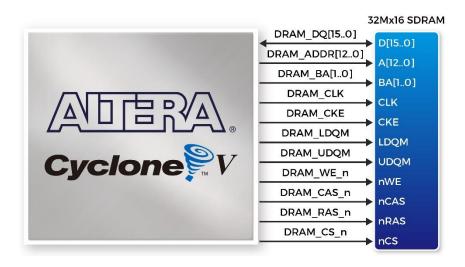

## 3.4.3 SDRAM Memory

The OpenVINO Starter Kit GT Edition features 64MB of SDRAM with a single 64MB (32Mx16) SDRAM chip. The chip consists of 16-bit data line, control line, and address line connected to the FPGA. This chip uses the 3.3V LVCMOS signaling standard. Connections between the FPGA and SDRAM are shown in **Figure 3-16**, and the pin assignment is listed in

**Table 3-7**.

Figure 3-16 Connections between the FPGA and SDRAM

**Table 3-7 Pin Assignment of SDRAM**

| Signal Name  | FPGA Pin No. | Direction | Description        | I/O Standard |

|--------------|--------------|-----------|--------------------|--------------|

| DRAM_CLK     | PIN_F26      | Output    | SDRAM Clock        | 3.3-V LVTTL  |

| DRAM_CKE     | PIN_E25      | Output    | SDRAM Clock Enable | 3.3-V LVTTL  |

| DRAM_ADDR[0] | PIN_D26      | Output    | SDRAM Address[0]   | 3.3-V LVTTL  |

| DRAM_ADDR[1] | PIN_H20      | Output    | SDRAM Address[1]   | 3.3-V LVTTL  |

| DRAM_ADDR[2] | PIN_F23      | Output    | SDRAM Address[2]   | 3.3-V LVTTL  |

| DRAM_ADDR[3]  | PIN_G22 | Output | SDRAM Address[3]            | 3.3-V LVTTL |

|---------------|---------|--------|-----------------------------|-------------|

| DRAM_ADDR[4]  | PIN_B25 | Output | SDRAM Address[4]            | 3.3-V LVTTL |

| DRAM_ADDR[5]  | PIN_D22 | Output | SDRAM Address[5]            | 3.3-V LVTTL |

| DRAM_ADDR[6]  | PIN_C25 | Output | SDRAM Address[6]            | 3.3-V LVTTL |

| DRAM_ADDR[7]  | PIN_E23 | Output | SDRAM Address[7]            | 3.3-V LVTTL |

| DRAM_ADDR[8]  | PIN_B26 | Output | SDRAM Address[8]            | 3.3-V LVTTL |

| DRAM_ADDR[9]  | PIN_E24 | Output | SDRAM Address[9]            | 3.3-V LVTTL |

| DRAM_ADDR[10] | PIN_D25 | Output | SDRAM Address[10]           | 3.3-V LVTTL |

| DRAM_ADDR[11] | PIN_M26 | Output | SDRAM Address[11]           | 3.3-V LVTTL |

| DRAM_ADDR[12] | PIN_M25 | Output | SDRAM Address[12]           | 3.3-V LVTTL |

| DRAM_BA[0]    | PIN_J20 | Output | SDRAM Bank Address[0]       | 3.3-V LVTTL |

| DRAM_BA[1]    | PIN_H22 | Output | SDRAM Bank Address[1]       | 3.3-V LVTTL |

| DRAM_DQ[0]    | PIN_L24 | Inout  | SDRAM Data[0]               | 3.3-V LVTTL |

| DRAM_DQ[1]    | PIN_M24 | Inout  | SDRAM Data[1]               | 3.3-V LVTTL |

| DRAM_DQ[2]    | PIN_N23 | Inout  | SDRAM Data[2]               | 3.3-V LVTTL |

| DRAM_DQ[3]    | PIN_K23 | Inout  | SDRAM Data[3]               | 3.3-V LVTTL |

| DRAM_DQ[4]    | PIN_H24 | Inout  | SDRAM Data[4]               | 3.3-V LVTTL |

| DRAM_DQ[5]    | PIN_J23 | Inout  | SDRAM Data[5]               | 3.3-V LVTTL |

| DRAM_DQ[6]    | PIN_K24 | Inout  | SDRAM Data[6]               | 3.3-V LVTTL |

| DRAM_DQ[7]    | PIN_L22 | Inout  | SDRAM Data[7]               | 3.3-V LVTTL |

| DRAM_DQ[8]    | PIN_G25 | Inout  | SDRAM Data[8]               | 3.3-V LVTTL |

| DRAM_DQ[9]    | PIN_G24 | Inout  | SDRAM Data[9]               | 3.3-V LVTTL |

| DRAM_DQ[10]   | PIN_H25 | Inout  | SDRAM Data[10]              | 3.3-V LVTTL |

| DRAM_DQ[11]   | PIN_J21 | Inout  | SDRAM Data[11]              | 3.3-V LVTTL |

| DRAM_DQ[12]   | PIN_L23 | Inout  | SDRAM Data[12]              | 3.3-V LVTTL |

| DRAM_DQ[13]   | PIN_K21 | Inout  | SDRAM Data[13]              | 3.3-V LVTTL |

| DRAM_DQ[14]   | PIN_N24 | Inout  | SDRAM Data[14]              | 3.3-V LVTTL |

| DRAM_DQ[15]   | PIN_M22 | Inout  | SDRAM Data[15]              | 3.3-V LVTTL |

| DRAM_LDQM     | PIN_H23 | Output | DQ[7:0] SDRAM Data Mask     | 3.3-V LVTTL |

| DRAM_UDQM     | PIN_F24 | Output | DQ[15:8] SDRAM Data Mask    | 3.3-V LVTTL |

| DRAM_CS_n     | PIN_F22 | Output | SDRAM Chip Select           | 3.3-V LVTTL |

| DRAM_WE_n     | PIN_J25 | Output | SDRAM Write Enable          | 3.3-V LVTTL |

| DRAM_CAS_n    | PIN_J26 | Output | SDRAM Column Address Strobe | 3.3-V LVTTL |

| DRAM_RAS_n    | PIN_E26 | Output | SDRAM Row Address Strobe    | 3.3-V LVTTL |

|               |         |        |                             |             |

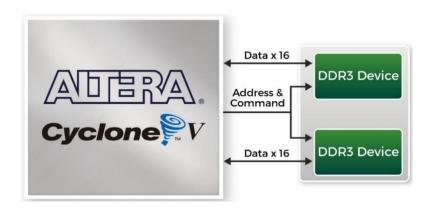

# 3.4.4 DDR3 Memory

OpenVINO Starter Kit GT Edition supports 1GB of DDR3 SDRAM comprising of two

x16 bit DDR3 devices. The signals are connected to the dedicated Hard Memory Controller for FPGA I/O banks and the target speed is 400MHz. **Figure 3-17** shows the connections between the DDR3 and Cyclone V FPGA. **Table 3-8** lists the pin assignment of the DDR3 and its description with I/O standard.

Figure 3-17 Connections between FPGA and DDR3

Table 3-8 Pin Assignment of DDR3 Memory

| Signal Name   | FPGA Pin No. | Direction | Description          | I/O Standard            |

|---------------|--------------|-----------|----------------------|-------------------------|

| DDR3_ADDR[0]  | PIN_AE6      | Output    | DDR3 Address[0]      | SSTL-15 Class I         |

| DDR3_ADDR[1]  | PIN_AF6      | Output    | DDR3 Address[1]      | SSTL-15 Class I         |

| DDR3_ADDR[2]  | PIN_AF7      | Output    | DDR3 Address[2]      | SSTL-15 Class I         |

| DDR3_ADDR[3]  | PIN_AF8      | Output    | DDR3 Address[3]      | SSTL-15 Class I         |

| DDR3_ADDR[4]  | PIN_U10      | Output    | DDR3 Address[4]      | SSTL-15 Class I         |

| DDR3_ADDR[5]  | PIN_U11      | Output    | DDR3 Address[5]      | SSTL-15 Class I         |

| DDR3_ADDR[6]  | PIN_AE9      | Output    | DDR3 Address[6]      | SSTL-15 Class I         |

| DDR3_ADDR[7]  | PIN_AF9      | Output    | DDR3 Address[7]      | SSTL-15 Class I         |

| DDR3_ADDR[8]  | PIN_AB12     | Output    | DDR3 Address[8]      | SSTL-15 Class I         |

| DDR3_ADDR[9]  | PIN_AB11     | Output    | DDR3 Address[9]      | SSTL-15 Class I         |

| DDR3_ADDR[10] | PIN_AC9      | Output    | DDR3 Address[10]     | SSTL-15 Class I         |

| DDR3_ADDR[11] | PIN_AC8      | Output    | DDR3 Address[11]     | SSTL-15 Class I         |

| DDR3_ADDR[12] | PIN_AB10     | Output    | DDR3 Address[12]     | SSTL-15 Class I         |

| DDR3_ADDR[13] | PIN_AC10     | Output    | DDR3 Address[13]     | SSTL-15 Class I         |

| DDR3_ADDR[14] | PIN_W11      | Output    | DDR3 Address[14]     | SSTL-15 Class I         |

| DDR3_BA[0]    | PIN_V10      | Output    | DDR3 Bank Address[0] | SSTL-15 Class I         |

| DDR3_BA[1]    | PIN_AD8      | Output    | DDR3 Bank Address[1] | SSTL-15 Class I         |

| DDR3_BA[2]    | PIN_AE8      | Output    | DDR3 Bank Address[2] | SSTL-15 Class I         |

| DDD2 CV n     | DD 1 3110    | Output    | DDR3 Clock p         | Differential 1.5-V SSTL |

| DDR3_CK_p     | PIN_N10      |           |                      | Class I                 |

|               |                                    | Output                      |                         | Differential 1.5-V SSTL |

|---------------|------------------------------------|-----------------------------|-------------------------|-------------------------|

| DDR3_CK_n     | PIN_P10                            |                             | DDR3 Clock n            | Class I                 |

| DDR3_CKE      | PIN_AF14                           | Output                      | DDR3 Clock Enable       | SSTL-15 Class I         |

|               |                                    | Inout                       |                         | Differential 1.5-V SSTL |

| DDR3_DQS_p[0] | PIN_V13                            |                             | DDR3 Data Strobe p[0]   | Class I                 |

| DDD2 DOG [1]  | DINI 1114                          | Inout                       | DDD2 D 4 G4 1 [1]       | Differential 1.5-V SSTL |

| DDR3_DQS_p[1] | PIN_U14                            |                             | DDR3 Data Strobe p[1]   | Class I                 |

| DDD2 DOS ~[2] | DIM 3/15                           | Inout                       | DDD2 Data Stroka n[2]   | Differential 1.5-V SSTL |

| DDR3_DQS_p[2] | PIN_V15                            |                             | DDR3 Data Strobe p[2]   | Class I                 |

| DDD2 DOS n[2] | DIN W16                            | Inout                       | DDD2 Data Straha n[2]   | Differential 1.5-V SSTL |

| DDR3_DQS_p[3] | PIN_W16                            |                             | DDR3 Data Strobe p[3]   | Class I                 |

| DDR3 DQS n[0] | DIN W12                            | Inout                       | DDP2 Data Straha n[0]   | Differential 1.5-V SSTL |

|               | PIN_W13                            |                             | DDR3 Data Strobe n[0]   | Class I                 |

| DDD2 DOS n[1] | PIN V14                            | Inout                       | DDR3 Data Strobe n[1]   | Differential 1.5-V SSTL |

| DDR3_DQS_n[1] | F1IN_V14                           |                             | DDR3 Data Strobe II[1]  | Class I                 |

| DDR3_DQS_n[2] | PIN_W15                            | Inout                       | DDR3 Data Strobe n[2]   | Differential 1.5-V SSTL |

|               | 111N_W13                           |                             | DDR3 Data Strobe II[2]  | Class I                 |

| DDD2 DOS n[2] | PIN_W17                            | Inout DDR3 Data Strobe n[3] | Differential 1.5-V SSTL |                         |

| DDR3_DQS_n[3] | 1 11\(\frac{1}{2}\)\(\frac{1}{2}\) |                             | DDR3 Data Strote II[3]  | Class I                 |

| DDR3_DQ[0]    | PIN_AA14                           | Inout                       | DDR3 Data[0]            | SSTL-15 Class I         |

| DDR3_DQ[1]    | PIN_Y14                            | Inout                       | DDR3 Data[1]            | SSTL-15 Class I         |

| DDR3_DQ[2]    | PIN_AD11                           | Inout                       | DDR3 Data[2]            | SSTL-15 Class I         |

| DDR3_DQ[3]    | PIN_AD12                           | Inout                       | DDR3 Data[3]            | SSTL-15 Class I         |

| DDR3_DQ[4]    | PIN_Y13                            | Inout                       | DDR3 Data[4]            | SSTL-15 Class I         |

| DDR3_DQ[5]    | PIN_W12                            | Inout                       | DDR3 Data[5]            | SSTL-15 Class I         |

| DDR3_DQ[6]    | PIN_AD10                           | Inout                       | DDR3 Data[6]            | SSTL-15 Class I         |

| DDR3_DQ[7]    | PIN_AF12                           | Inout                       | DDR3 Data[7]            | SSTL-15 Class I         |

| DDR3_DQ[8]    | PIN_AC15                           | Inout                       | DDR3 Data[8]            | SSTL-15 Class I         |

| DDR3_DQ[9]    | PIN_AB15                           | Inout                       | DDR3 Data[9]            | SSTL-15 Class I         |

| DDR3_DQ[10]   | PIN_AC14                           | Inout                       | DDR3 Data[10]           | SSTL-15 Class I         |

| DDR3_DQ[11]   | PIN_AF13                           | Inout                       | DDR3 Data[11]           | SSTL-15 Class I         |

| DDR3_DQ[12]   | PIN_AB16                           | Inout                       | DDR3 Data[12]           | SSTL-15 Class I         |

| DDR3_DQ[13]   | PIN_AA16                           | Inout                       | DDR3 Data[13]           | SSTL-15 Class I         |

| DDR3_DQ[14]   | PIN_AE14                           | Inout                       | DDR3 Data[14]           | SSTL-15 Class I         |

| DDR3_DQ[15]   | PIN_AF18                           | Inout                       | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[16]   | PIN_AD16                           | Inout                       | DDR3 Data[16]           | SSTL-15 Class I         |

| DDR3_DQ[17]   | PIN_AD17                           | Inout                       | DDR3 Data[17]           | SSTL-15 Class I         |

| DDR3_DQ[18]  | PIN_AC18 | Inout  | DDR3 Data[18]                                        | SSTL-15 Class I |

|--------------|----------|--------|------------------------------------------------------|-----------------|

| DDR3_DQ[19]  | PIN_AF19 | Inout  | DDR3 Data[19]                                        | SSTL-15 Class I |

| DDR3_DQ[20]  | PIN_AC17 | Inout  | DDR3 Data[20]                                        | SSTL-15 Class I |

| DDR3_DQ[21]  | PIN_AB17 | Inout  | DDR3 Data[21]                                        | SSTL-15 Class I |

| DDR3_DQ[22]  | PIN_AF21 | Inout  | DDR3 Data[22]                                        | SSTL-15 Class I |

| DDR3_DQ[23]  | PIN_AE21 | Inout  | DDR3 Data[23]                                        | SSTL-15 Class I |

| DDR3_DQ[24]  | PIN_AE15 | Inout  | DDR3 Data[24]                                        | SSTL-15 Class I |

| DDR3_DQ[25]  | PIN_AE16 | Inout  | DDR3 Data[25]                                        | SSTL-15 Class I |

| DDR3_DQ[26]  | PIN_AC20 | Inout  | DDR3 Data[26]                                        | SSTL-15 Class I |

| DDR3_DQ[27]  | PIN_AD21 | Inout  | DDR3 Data[27]                                        | SSTL-15 Class I |

| DDR3_DQ[28]  | PIN_AF16 | Inout  | DDR3 Data[28]                                        | SSTL-15 Class I |

| DDR3_DQ[29]  | PIN_AF17 | Inout  | DDR3 Data[29]                                        | SSTL-15 Class I |

| DDR3_DQ[30]  | PIN_AD23 | Inout  | DDR3 Data[30]                                        | SSTL-15 Class I |

| DDR3_DQ[31]  | PIN_AF23 | Inout  | DDR3 Data[31]                                        | SSTL-15 Class I |

| DDR3_DM[0]   | PIN_AF11 | Output | DDR3 Data Mask[0]                                    | SSTL-15 Class I |

| DDR3_DM[1]   | PIN_AE18 | Output | DDR3 Data Mask[1]                                    | SSTL-15 Class I |

| DDR3_DM[2]   | PIN_AE20 | Output | DDR3 Data Mask[2]                                    | SSTL-15 Class I |

| DDR3_DM[3]   | PIN_AE24 | Output | DDR3 Data Mask[3]                                    | SSTL-15 Class I |

| DDR3_CS_n    | PIN_R11  | Output | DDR3 Chip Select                                     | SSTL-15 Class I |

| DDR3_WE_n    | PIN_T9   | Output | DDR3 Write Enable                                    | SSTL-15 Class I |

| DDR3_CAS_n   | PIN_W10  | Output | DDR3 Column Address<br>Strobe                        | SSTL-15 Class I |

| DDR3_RAS_n   | PIN_Y10  | Output | DDR3 Row Address Strobe                              | SSTL-15 Class I |

| DDR3_RESET_n | PIN_AE19 | Output | DDR3 Reset                                           | SSTL-15 Class I |

| DDR3_ODT     | PIN_AD13 | Output | DDR3 On-die Termination                              | SSTL-15 Class I |

| DDR3_RZQ     | PIN_AE11 | Input  | External reference ball for output drive calibration | 1.5 V           |

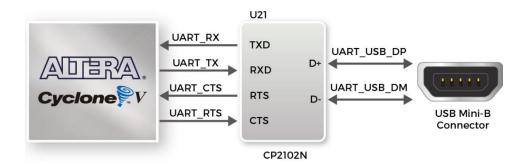

## 3.4.5 UART to USB

The OpenVINO Starter Kit GT Edition has one UART interface. The physical interface is implemented by UART-USB onboard bridge from a CP2102N chip to the host with a USB Mini-B connector. More information about the chip is available on the manufacturer's website, or in the directory \Datasheets\UART TO USB of OpenVINO Starter Kit GT Edition system CD. **Figure 3-18** shows the connections between the FPGA, CP2102N chip, and the USB Mini-B connector. **Table 3-9** lists the pin assignment of UART interface connected to the FPGA.

Figure 3-18 Connections between the FPGA, CP2102N chip and USB Mini-B connector

**Table 3-9 Pin Assignment of UART Interface**

| e e e e e e e e e e e e e e e e e e e |              |           |                      |              |  |  |

|---------------------------------------|--------------|-----------|----------------------|--------------|--|--|

| Signal Name                           | FPGA Pin No. | Direction | Description          | I/O Standard |  |  |

| UART_TX                               | PIN_P21      | Output    | UART Transmitter     | 3.3-V LVTTL  |  |  |

| UART_RX                               | PIN_P22      | Input     | UART Receiver        | 3.3-V LVTTL  |  |  |

| UART_CTS                              | PIN_W25      | Input     | UART Clear to Send   | 3.3-V LVTTL  |  |  |

| UART RTS                              | PIN W26      | Output    | UART Request to Send | 3.3-V LVTTL  |  |  |

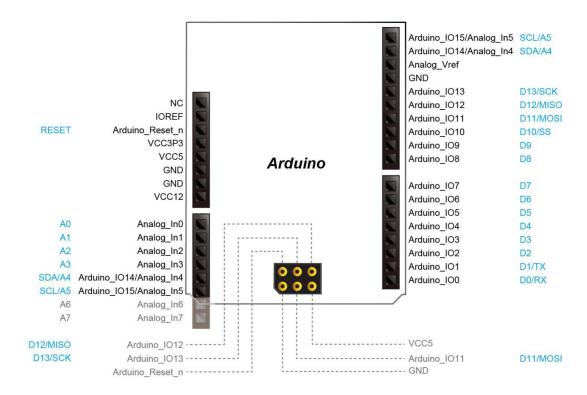

## 3.4.6 Arduino Uno R3 Expansion Header

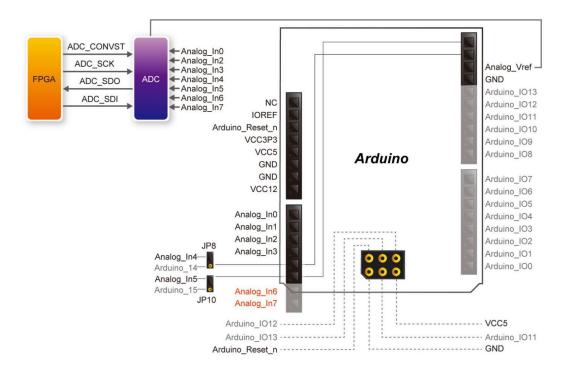

The OpenVINO Starter Kit GT Edition provides Arduino Uno revision 3 compatibility expansion header which comes with four independent headers. The expansion header has 17 user pins (16 GPIO pins and 1 Reset pin) connected directly to Cyclone V GT FPGA. 8-Pin Analog input connects to the ADC, and also provides DC +5V (VCC5), DC +3.3V (VCC3P3 and IOREF), and three GND pins. Please refer to **Figure 3-19** for detailed pinout information. The blue font represents the Arduino Uno R3 board pin-out definition.

Figure 3-19 All the pin-out signal name of the Arduino Uno connector

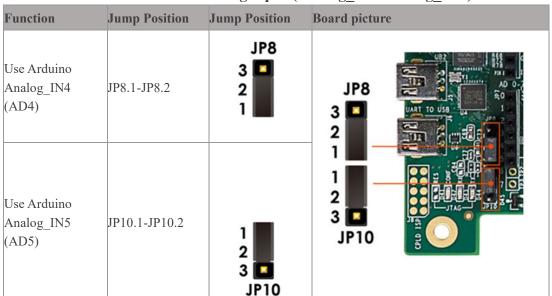

The 16 GPIO pins are provided to the Arduino Header for digital I/O. Among these 16 GPIO pins, two pins possess both analog and digital functionalities according to the Arduino Header settings. The MCU on the Arduino main board can select either the analog or digital function. Unfortunately, this selection can't be done with the FPGA and users would have to use the corresponding jumpers to make the selection. **Table 3-10** lists all the pin assignments of the Arduino Uno connector (digital), signal names relative to Cyclone V GT FPGA.

Table 3-10 Pin Assignments for Arduino Uno Expansion Header connector

| Signal Name | FPGA Pin No. | Direction | Description             | I/O Standard |

|-------------|--------------|-----------|-------------------------|--------------|

| ADC_SCK     | PIN_R26      | Output    | Serial Data Clock       | 3.3-V LVTTL  |

| ADC SDO     | DINI AD26    |           | Serial Data Out (ADC to | 3.3-V LVTTL  |

| ADC_SDO     | PIN_AB26     | Input     | FPGA)                   | 3.3-V LVIIL  |

| ADC_SDI     | PIN_AA26     | Output    | Serial Data Input (FPGA | 3.3-V LVTTL  |

|             |              |           | to ADC)                 | 3.3-V LVIIL  |

| ADC_CONVST  | PIN_T26      | Ouput     | Conversion Start        | 3.3-V LVTTL  |

| ARD_IO[0]   | PIN_Y26      | Inout     | Arduino IO0             | 3.3-V LVTTL  |

| ARD_IO[1]   | PIN_V23      | Inout     | Arduino IO1             | 3.3-V LVTTL  |

| ARD_IO[2]   | PIN_V24      | Inout     | Arduino IO2             | 3.3-V LVTTL  |

| ARD_IO[3]   | PIN_U24      | Inout     | Arduino IO3             | 3.3-V LVTTL  |

| ARD_IO[4]  | PIN_T24  | Inout | Arduino IO4  | 3.3-V LVTTL |

|------------|----------|-------|--------------|-------------|

| ARD_IO[5]  | PIN_T23  | Inout | Arduino IO5  | 3.3-V LVTTL |

| ARD_IO[6]  | PIN_T22  | Inout | Arduino IO6  | 3.3-V LVTTL |

| ARD_IO[7]  | PIN_R24  | Inout | Arduino IO7  | 3.3-V LVTTL |

| ARD_IO[8]  | PIN_P20  | Inout | Arduino IO8  | 3.3-V LVTTL |

| ARD_IO[9]  | PIN_R23  | Inout | Arduino IO9  | 3.3-V LVTTL |

| ARD_IO[10] | PIN_R25  | Inout | Arduino IO10 | 3.3-V LVTTL |

| ARD_IO[11] | PIN_P23  | Inout | Arduino IO11 | 3.3-V LVTTL |

| ARD_IO[12] | PIN_AC25 | Inout | Arduino IO12 | 3.3-V LVTTL |

| ARD_IO[13] | PIN_AD25 | Inout | Arduino IO13 | 3.3-V LVTTL |

| ARD_IO[14] | PIN_AB25 | Inout | Arduino IO14 | 3.3-V LVTTL |

| ARD_IO[15] | PIN_AA24 | Inout | Arduino IO15 | 3.3-V LVTTL |

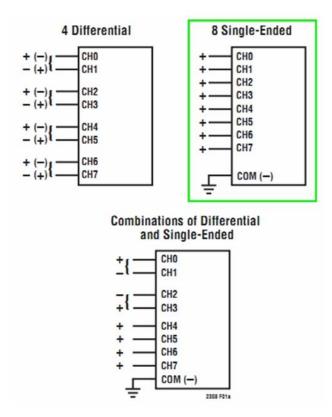

Besides 16 pins for digital GPIO, there are also 8 analog inputs on the Arduino Uno R3 Expansion Header. Consequently, we use ADC LTC2308 from Linear Technology on the board for possible future analog-to-digital applications.

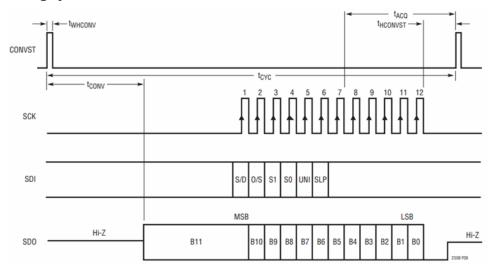

The LTC2308 is a low noise, 500ksps, 8-channel, 12-bit ADC with a SPI/MICROWIRE compatible serial interface. This ADC includes an internal reference and a fully differential sample-and-hold circuit to reduce common mode noise. The internal conversion clock allows the external serial output data clock (SCK) to operate at any frequency up to 40MHz.

The LTC2308 is controlled via a serial SPI bus interface, which is connected to pins on the Cyclone V GT FPGA. A schematic diagram of the ADC circuitry is shown in **Figure 3-20.** Detailed information for using the LTC2308 is available on its datasheet, which can be found on the manufacturer's website, or under the Datasheets\ADC folder of the OpenVINO Starter Kit GT Edition System CD.

Figure 3-20 Connection and pin assignments of Arduino analog input (ADC)

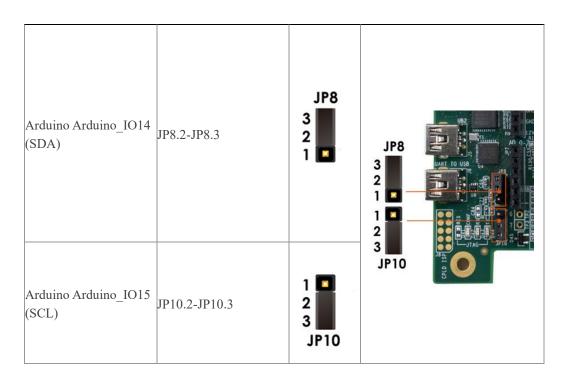

When users wish to use Analog\_IN4(AD4) and Analog\_IN5(AD5), they would need to make their choices through corresponding jumpers. This is because following the Arduino Header definition, these two pins possess both analog/digital functionalities and can be controlled by the MCU on the Arduino main board. However, this can't be done with the FPGA. Therefore, users have to use the corresponding jumpers to make their selection.

**Table** 3-11 lists the settings to select the Arduino interface as Digital I/O mode. **Table 3-12** lists the settings to select the Arduino interface as Analog I/O mode.

Table 3-11 Select Arduino expansion header for Digital I/O Mode

| Function Jump Position | Jump Board picture Position |

|------------------------|-----------------------------|

|------------------------|-----------------------------|

Table 3-12 Select Analog input (Analog\_IN4/Analog\_IN5)

Besides, there are no components pre-soldered on the Analog\_IN6 and Analog\_IN7. Therefore, if users wish to use these two inputs, they would need to solder components such as female headers before it can be connected to the object to be measured.

Note: We urge users to carefully install Arduino Shield after installing parts on Analog IN6(7) in order to avoid shift when inserting the shield board.

**Table 3-13** lists the ADC SPI Interface pin assignments, signal names relative to the Cyclone V GT device.

Table 3-13 ADC SPI Interface Pin Assignments and Signal Names

| Signal Name | Description                     | I/O Standard | Cyclone V GT Pin Number |

|-------------|---------------------------------|--------------|-------------------------|

| ADC_CONVST  | Conversion Start                | 1.2-V        | PIN_T26                 |

| ADC_SCK     | Serial Data Clock               | 1.2-V        | PIN_R26                 |

| IADC SDI    | Serial Data Input (FPGA to ADC) | 1.2-V        | PIN_AA26                |

| IADC SDO    | Serial Data Out (ADC to FPGA)   | 1.2-V        | PIN_AB26                |

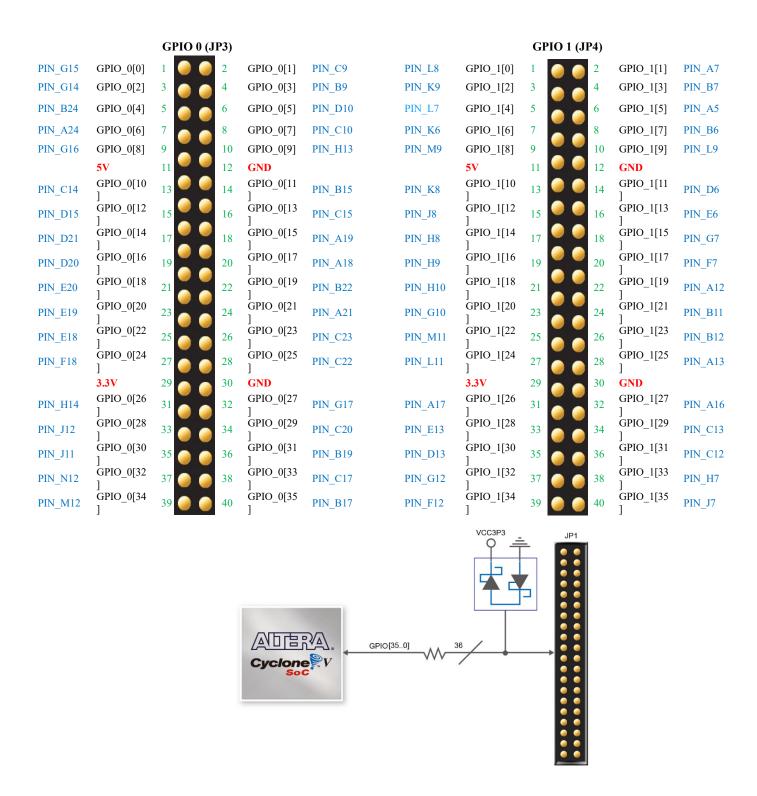

## 3.4.7 2x20 GPIO Expansion Header

The OpenVINO Starter Kit GT Edition has two 40-pin expansion headers. Each header has 36 user pins connected directly to the Cyclone V FPGA. It also comes with DC +5V (VCC5), DC +3.3V (VCC3P3), and two GND pins. The maximum power consumption allowed for a daughter card connected to one GPIO port is shown in **Table 3-14**.

Table 3-14 Voltage and Max. Current Limit of Expansion Headers

| Supplied Voltage | Max. Current Limit |

|------------------|--------------------|

| 5V               | 1A                 |

| 3.3V             | 1.5A               |

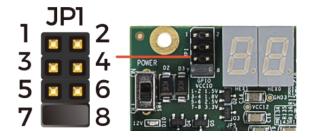

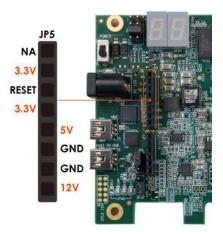

Each GPIO header has eight TX and eight RX channels. The voltage level of the I/O pins on the expansion headers can be adjusted to 3.3V, 2.5V, 1.8V, or 1.5V by using JP1 (The default value is 3.3V). Because the expansion I/Os are connected to Bank 7A and 8A of the FPGA, and the VCCIO voltage of these banks (VCCIO7A and VCCIO8A) is controlled by the header JP1, users can use a jumper to select the input voltage of VCCIO7A and VCCIO8A to 3.3V, 2.5V, 1.8V, and 1.5V to control the voltage level of the I/O pins. Table 3-15 lists the jumper settings of the JP1. **Figure 3-21** and **Figure 3-22** show the jumper setting for shorting pin 5 and pin 6 and shorting pin 7 and pin 8 of JP1.

Table 3-15 Voltage Level Setting of the Expansion Headers Using JP1

| JP1 Jumper Settings   | Supplied Voltage to VCCIO7A | IO Voltage of GPIO Expansion |  |

|-----------------------|-----------------------------|------------------------------|--|

| Jr 1 Jumper Settings  | and VCCIO8A                 | Headers                      |  |

| Short pin 1 and pin 2 | 1.5V                        | 1.5V                         |  |

| Short pin 3 and pin 4 | 1.8V                        | 1.8V                         |  |

| Short pin 5 and pin 6 | 2.5V                        | 2.5V                         |  |

| Short pin 7 and pin 8 | 3.3V                        | 3.3V (default)               |  |

Figure 3-21 Short pin5 and pin 6 of JP1

Figure 3-22 Short pin 7 and pin 8 of JP1

The GPIO I/O pins support 16-channel LVDS transmission standard. The maximum transmission rate of loopback test is up to 840 Mbps. The I/O valtage standard of LVDS transmission needs to be set at 2.5V.

Each pin on the expansion headers is connected to two diodes and a resistor that provides protection against high and low voltages. **Figure 3-23** shows the protection circuitry for 36 data pins. **Table 3-16** shows all the pin assignments of the GPIO expansion headers.

Figure 3-23 Connections between the GPIO connector and Cyclone V FPGA

**Table 3-16 Pin Assignments for Expansion Headers**

|             | Table 5-16 Pin Assignments for Expansion Headers |           |                          |               |  |  |

|-------------|--------------------------------------------------|-----------|--------------------------|---------------|--|--|

| Signal Name | FPGA Pin<br>No.                                  | Direction | Description              | I/O Standard  |  |  |

| GPIO_0[0]   | PIN_G15                                          | inout     | GPIO 0 DATA0/LVDS RX0_p  | Depend on JP1 |  |  |

| GPIO_0[1]   | PIN_C9                                           | inout     | GPIO 0 DATA1/LVDS TX0_p  | Depend on JP1 |  |  |

| GPIO_0[2]   | PIN_G14                                          | inout     | GPIO 0 DATA2/LVDS RX0_n  | Depend on JP1 |  |  |

| GPIO_0[3]   | PIN_B9                                           | inout     | GPIO 0 DATA3/LVDS TX0_n  | Depend on JP1 |  |  |

| GPIO_0[4]   | PIN_B24                                          | inout     | GPIO 0 DATA4/LVDS RX1_p  | Depend on JP1 |  |  |

| GPIO_0[5]   | PIN_D10                                          | inout     | GPIO 0 DATA5/LVDS TX1_p  | Depend on JP1 |  |  |

| GPIO_0[6]   | PIN_A24                                          | inout     | GPIO 0 DATA6/LVDS RX1_n  | Depend on JP1 |  |  |

| GPIO_0[7]   | PIN_C10                                          | inout     | GPIO 0 DATA7/LVDS TX1_n  | Depend on JP1 |  |  |

| GPIO_0[8]   | PIN_G16                                          | inout     | GPIO 0 DATA8             | Depend on JP1 |  |  |

| GPIO_0[9]   | PIN_H13                                          | inout     | GPIO 0 DATA9             | Depend on JP1 |  |  |

| GPIO_0[10]  | PIN_C14                                          | inout     | GPIO 0 DATA10/LVDS RX2_p | Depend on JP1 |  |  |

| GPIO_0[11]  | PIN_B15                                          | inout     | GPIO 0 DATA11/LVDS TX2_p | Depend on JP1 |  |  |

| GPIO_0[12]  | PIN_D15                                          | inout     | GPIO 0 DATA12/LVDS_RX2_n | Depend on JP1 |  |  |

| GPIO_0[13]  | PIN_C15                                          | inout     | GPIO 0 DATA13/LVDS_TX2_n | Depend on JP1 |  |  |

| GPIO_0[14]  | PIN_D21                                          | inout     | GPIO 0 DATA14/LVDS RX3_p | Depend on JP1 |  |  |

| GPIO_0[15]  | PIN_A19                                          | inout     | GPIO 0 DATA15/LVDS TX3_p | Depend on JP1 |  |  |

| GPIO_0[16]  | PIN_D20                                          | inout     | GPIO 0 DATA16/LVDS_RX3_n | Depend on JP1 |  |  |

| GPIO_0[17]  | PIN_A18                                          | inout     | GPIO 0 DATA17/LVDS TX3_n | Depend on JP1 |  |  |

| GPIO_0[18]  | PIN_E20                                          | inout     | GPIO 0 DATA18/LVDS RX4_p | Depend on JP1 |  |  |

| GPIO_0[19]  | PIN_B22                                          | inout     | GPIO 0 DATA19/LVDS TX4_p | Depend on JP1 |  |  |

| GPIO_0[20]  | PIN_E19                                          | inout     | GPIO 0 DATA20/LVDS_RX4_n | Depend on JP1 |  |  |

| GPIO_0[21]  | PIN_A21                                          | inout     | GPIO 0 DATA21/LVDS_TX4_n | Depend on JP1 |  |  |

| GPIO_0[22]  | PIN_E18                                          | inout     | GPIO 0 DATA22/LVDS RX5_p | Depend on JP1 |  |  |

| GPIO_0[23]  | PIN_C23                                          | inout     | GPIO 0 DATA23/LVDS TX5_p | Depend on JP1 |  |  |

| GPIO_0[24]  | PIN_F18                                          | inout     | GPIO 0 DATA24/LVDS_RX5_n | Depend on JP1 |  |  |

| GPIO_0[25]  | PIN_C22                                          | inout     | GPIO 0 DATA25/LVDS TX5_n | Depend on JP1 |  |  |

| GPIO_0[26]  | PIN_H14                                          | inout     | GPIO 0 DATA26            | Depend on JP1 |  |  |

| GPIO_0[27]  | PIN_G17                                          | inout     | GPIO 0 DATA27            | Depend on JP1 |  |  |

| GPIO_0[28]  | PIN_J12                                          | inout     | GPIO 0 DATA28/LVDS RX6_p | Depend on JP1 |  |  |

| GPIO_0[29]  | PIN_C20                                          | inout     | GPIO 0 DATA29/LVDS TX6_p | Depend on JP1 |  |  |

| GPIO_0[30]  | PIN_J11                                          | inout     | GPIO 0 DATA30/LVDS RX6_n | Depend on JP1 |  |  |

| GPIO_0[31]  | PIN_B19                                          | inout     | GPIO 0 DATA31/LVDS TX6_n | Depend on JP1 |  |  |

| GPIO_0[32]  | PIN_N12                                          | inout     | GPIO 0 DATA32/LVDS RX7_p | Depend on JP1 |  |  |

| GPIO_0[33]  | PIN_C17                                          | inout     | GPIO 0 DATA33/LVDS TX7_p | Depend on JP1 |  |  |

|            | 1       |       |                          |               |

|------------|---------|-------|--------------------------|---------------|

| GPIO_0[34] | PIN_M12 | inout | GPIO 0 DATA34/LVDS RX7_n | Depend on JP1 |

| GPIO_0[35] | PIN_B17 | inout | GPIO 0 DATA35/LVDS TX7_n | Depend on JP1 |

| GPIO_1[0]  | PIN_L8  | inout | GPIO 1 DATA0/LVDS RX0_p  | Depend on JP1 |

| GPIO_1[1]  | PIN_A7  | inout | GPIO 1 DATA1/LVDS TX0_p  | Depend on JP1 |

| GPIO_1[2]  | PIN_K9  | inout | GPIO 1 DATA2/LVDS RX0_n  | Depend on JP1 |

| GPIO_1[3]  | PIN_B7  | inout | GPIO 1 DATA3/LVDS TX0_n  | Depend on JP1 |

| GPIO_1[4]  | PIN_L7  | inout | GPIO 1 DATA4/LVDS RX1_p  | Depend on JP1 |

| GPIO_1[5]  | PIN_A5  | inout | GPIO 1 DATA5/LVDS TX1_p  | Depend on JP1 |

| GPIO_1[6]  | PIN_K6  | inout | GPIO 1 DATA6/LVDS RX1_n  | Depend on JP1 |

| GPIO_1[7]  | PIN_B6  | inout | GPIO 1 DATA7/LVDS TX1_n  | Depend on JP1 |

| GPIO_1[8]  | PIN_M9  | inout | GPIO 1 DATA8             | Depend on JP1 |

| GPIO_1[9]  | PIN_L9  | inout | GPIO 1 DATA9             | Depend on JP1 |

| GPIO_1[10] | PIN_K8  | inout | GPIO 1 DATA10/LVDS RX2_p | Depend on JP1 |

| GPIO_1[11] | PIN_D6  | inout | GPIO 1 DATA11/LVDS TX2_p | Depend on JP1 |

| GPIO_1[12] | PIN_J8  | inout | GPIO 1 DATA12/LVDS_RX2_n | Depend on JP1 |

| GPIO_1[13] | PIN_E6  | inout | GPIO 1 DATA13/LVDS_TX2_n | Depend on JP1 |

| GPIO_1[14] | PIN_H8  | inout | GPIO 1 DATA14/LVDS RX3_p | Depend on JP1 |

| GPIO_1[15] | PIN_G7  | inout | GPIO 1 DATA15/LVDS TX3_p | Depend on JP1 |

| GPIO_1[16] | PIN_H9  | inout | GPIO 1 DATA16/LVDS_RX3_n | Depend on JP1 |

| GPIO_1[17] | PIN_F7  | inout | GPIO 1 DATA17/LVDS TX3_n | Depend on JP1 |

| GPIO_1[18] | PIN_H10 | inout | GPIO 1 DATA18/LVDS RX4_p | Depend on JP1 |

| GPIO_1[19] | PIN_A12 | inout | GPIO 1 DATA19/LVDS TX4_p | Depend on JP1 |

| GPIO_1[20] | PIN_G10 | inout | GPIO 1 DATA20/LVDS_RX4_n | Depend on JP1 |

| GPIO_1[21] | PIN_B11 | inout | GPIO 1 DATA21/LVDS_TX4_n | Depend on JP1 |

| GPIO_1[22] | PIN_M11 | inout | GPIO 1 DATA22/LVDS RX5_p | Depend on JP1 |

| GPIO_1[23] | PIN_B12 | inout | GPIO 1 DATA23/LVDS TX5_p | Depend on JP1 |

| GPIO_1[24] | PIN_L11 | inout | GPIO 1 DATA24/LVDS_RX5_n | Depend on JP1 |

| GPIO_1[25] | PIN_A13 | inout | GPIO 1 DATA25/LVDS TX5_n | Depend on JP1 |

| GPIO_1[26] | PIN_A17 | inout | GPIO 1 DATA26            | Depend on JP1 |

| GPIO_1[27] | PIN_A16 | inout | GPIO 1 DATA27            | Depend on JP1 |

| GPIO_1[28] | PIN_E13 | inout | GPIO 1 DATA28/LVDS RX6_p | Depend on JP1 |

| GPIO_1[29] | PIN_C13 | inout | GPIO 1 DATA29/LVDS TX6_p | Depend on JP1 |

| GPIO_1[30] | PIN_D13 | inout | GPIO 1 DATA30/LVDS RX6_n | Depend on JP1 |

| GPIO_1[31] | PIN_C12 | inout | GPIO 1 DATA31/LVDS TX6_n | Depend on JP1 |

| GPIO_1[32] | PIN_G12 | inout | GPIO 1 DATA32/LVDS RX7_p | Depend on JP1 |

| GPIO_1[33] | PIN_H7  | inout | GPIO 1 DATA33/LVDS TX7_p | Depend on JP1 |

| GPIO_1[34] | PIN_F12 | inout | GPIO 1 DATA34/LVDS RX7_n | Depend on JP1 |

| GPIO 1[35] | PIN J7 | inout | GPIO 1 DATA35/LVDS TX7 n | Depend on JP1 |

|------------|--------|-------|--------------------------|---------------|

| _ L1       |        |       |                          | 1             |

# Chapter 4 OpenVINO Starter Kit GT Edition System Builder

This chapter describes how users can create a custom design project on the board by using the OpenVINO Starter Kit GT Edition System Builder.Besides, users can also use the Quartus Golden top for the project building. Golden top project is located in folder: CD\Demonstration.

# 4.1 Introduction

The OpenVINO Starter Kit GT Edition System Builder is a Windows-based software utility, designed to assist users to create a Quartus Prime project for the board within minutes. The generated Quartus Prime project files include:

- Quartus Prime project file (.qpf)

- Quartus Prime setting file (.qsf)

- Top-level design file (.v or .vhd)

- Synopsis design constraints file (.sdc)

- Pin assignment document (.htm)

By providing the above files, the OpenVINO Starter Kit GT Edition System Builder prevents occurrence of situations that are prone to errors when users manually edit the top-level design file or place pin assignments. The common mistakes that users encounter are shown below:

- OpenVINO Starter Kit GT Edition board damage due to wrong pin/bank voltage assignments.

- OpenVINO Starter Kit GT Edition board malfunction caused by wrong device connections or missing pin counts for connected ends.

- Performance degradation due to improper pin assignments.

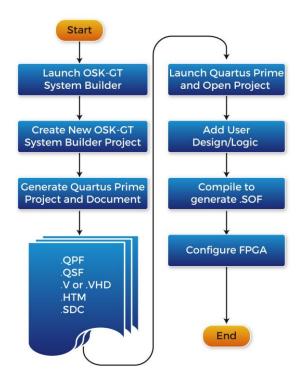

# **4.2 General Design Flow**

This section will introduce the general design flow to build a project for the development board via the OpenVINO Starter Kit GT Edition System Builder. The general design flow is illustrated in **Figure 4-1**.

Users should launch the OpenVINO Starter Kit GT Edition System Builder and create a new project according to their design requirements. When users complete the settings, the

OpenVINO Starter Kit GT Edition System Builder will generate two major files, a top-level design file (.v or .vhd) and a Quartus Prime setting file (.qsf).

The top-level design file contains top-level Verilog or VHDL HDL wrapper for users to add their own design/logic. The Quartus Prime setting file contains information such as FPGA device type, top-level pin assignments, and the I/O standard for each user-defined I/O pin.

Finally, the Quartus Prime programmer must be used to download .sof file to the OpenVINO Starter Kit GT Edition development board using a JTAG interface.

Figure 4-1 The general design flow of building a design

# 4.3 Using OpenVINO Starter Kit GT Edition System Builder

This section provides detailed procedures on how to use the OpenVINO Starter Kit GT Edition System Builder.

# ■ Install and launch OpenVINO Starter Kit GT Edition System Builder

The OpenVINO Starter Kit GT Edition System Builder is located in the directory: "Tools\SystemBuilder" in the OpenVINO Starter Kit GT Edition System CD. Users can copy the whole folder to a host computer without installing the utility. Launch the

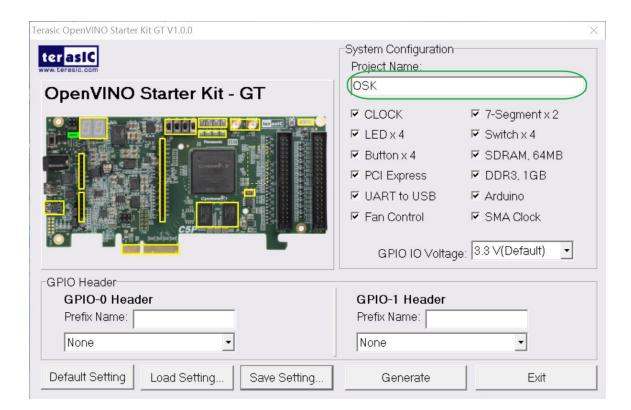

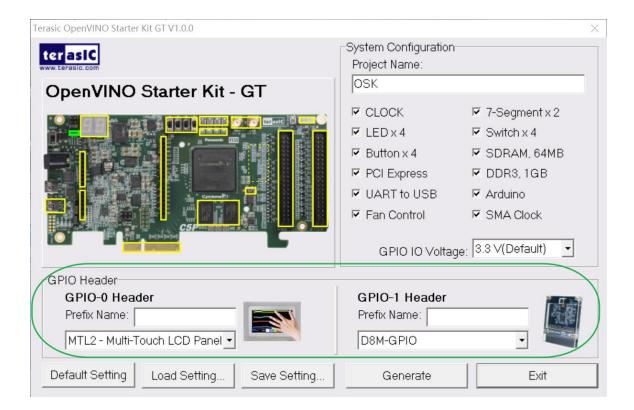

OpenVINO Starter Kit GT Edition System Builder by executing the OpenVINO Starter Kit GT Edition \_SystemBuilder.exe on the host computer and the GUI window will appear as shown in **Figure 4-2**.

Figure 4-2 OpenVINO Starter Kit GT EditionSystem Builder window

# **■** Input Project Name

Input project name as shown in **Figure 4-3**, type in an appropriate name in the green circled area, it will automatically be assigned as the name of your top-level design entity.

Figure 4-3 Board Type and Project Name

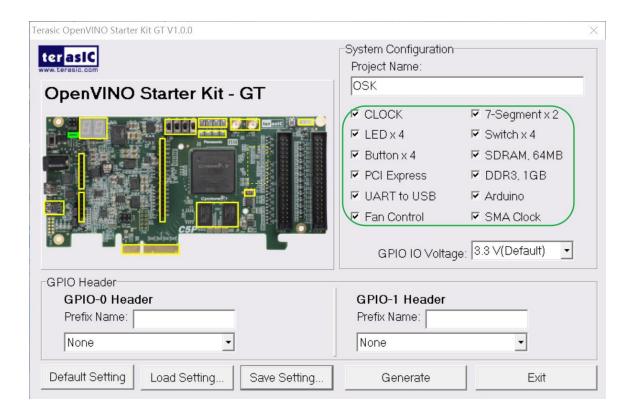

# **■** System Configuration

Under the System Configuration users are given the flexibility of enabling their choice of components included on the board as shown in **Figure 4-4**, each component of the board is listed where users can enable or disable a component according to their design by simply marking a check or removing the check in the field provided. If the component is enabled, the OpenVINO Starter Kit GT Edition System Builder will automatically generate the associated pin assignments including the pin name, pin location, pin direction, and I/O standard.

Figure 4-4 System Configuration Group

# **■ GPIO Expansion**

Users can connect Terasic GPIO daughter cards onto the GPIO connector located on the development board. As shown in **Figure 4-5**, the OpenVINO Starter Kit GT Edition System Builder will generate a project that includes related module. It will automatically generate the associated pin assignment including pin name, pin location, pin direction, and I/O standard.

Figure 4-5 GPIO Expansion

The "Prefix Name" is an optional feature that denotes the pin name of the daughter card assigned in your design. Users may leave this field empty.

# **■** Project Setting Management

The OpenVINO Starter Kit GT Edition System Builder also provides functions to restore the default setting, loading a setting, and saving users' board configuration file shown in **Figure 4-6**, Users can save the current board configuration information into a .cfg file and load it to the OpenVINO Starter Kit GT Edition System Builder.

Figure 4-6 Project Management

# Project Generation

When users press the Generate button, the OpenVINO Starter Kit GT Edition System Builder will generate the corresponding Quartus Prime files and documents as listed in **Table 4-1**.

Table 4-1 The file generated by OpenVINO Starter Kit GT Edition System Builder

| No. | File Name                       | Description                                    |

|-----|---------------------------------|------------------------------------------------|

| 1   | <project name="">.v</project>   | Top Verilog Quartus Prime File                 |

| 2   | <project name="">.qpf</project> | Quartus Prime Project File                     |

| 3   | <project name="">.qsf</project> | Quartus Prime Setting File                     |

| 4   | <project name="">.sdc</project> | Quartus Prime Synopsis Design Constraints File |

| 5   | <project name="">.htm</project> | Pin Assignment Document                        |

Users can use Quartus Prime software to add custom logic into the project and compile the project to generate the SRAM Object File (.sof).

# Chapter 5 Examples of Advanced Demonstrations

This chapter introduces several advanced demos designed by using RTL or Qsys. These examples provide demonstrations of the major features which are connected to the FPGA interface on the board, such as audio, SDRAM and IR Receiver. All these associated files can be found in the Demonstrations folder on the OpenVINO Starter Kit GT Edition System CD.

#### **■ Demonstration Installation**

How to run the Demonstaions with the computer:

Copy the Demonstration folder to the selected local directory, make sure that the path to the local directory does not contain the whitespace, otherwise the Nios II will run with error. Note that you must install the v17.1 or later Quartus Prime (including Cyclone V device) to run the OpenVINO Starter Kit GT Edition design example.

# 5.1 OpenVINO Starter Kit GT Edition Factory Default

# **Configuration**

The OpenVINO Starter Kit GT Edition is shipped from the factory with a default configuration bit-stream that demonstrates some of the basic features of the board, such as scrolling LED Marquee, HEX goes from 0 to F. The setup required for this demonstration, and the locations of its files are explained below.

# ■ Demonstration Setup and Instructions

- Project directory: Default.

- Demo Batch File: Default\demo batch jic\test.bat.

- FPGA Configure File: Default.sof or Default.jic.

- Connect the USB cable provided to the USB Blaster II port on the OpenVINO Starter Kit GT Edition. Ensure that power is applied to the OpenVINO Starter Kit GT Edition. If necessary(EPCQ is erased), please program the default code into EPCQ via the JTAG connection for the factory default configuration.

- Now, the 7-segment displays are enabled to display from 0 to F, and the LED is flashing.

- The project also provides the demo batch folder for running easily. By running

the test.bat, it is not only able to download the .sof into FPGA by command, but also to enable it to convert .sof to .jic file, which can be used to program the EPCQ device.

- The result of running the demo is as shown in **Figure 5-1**.

- If users want to reprogram the EPCQ device, the easiest method is to copy the. sof to demo\_batch\_jic folder, and change the name as Default. Or open the .bat file by **Text Editor**, modify the name to the new .sof file, execute the test.bat. First select "2" to convert .sof file to .jic file, then select the option "3" to program the .jic into EPCQ device.

```

*************

Please choose your operation

"1" for programming .sof to FPGA.

"2" for converting .sof to .jic

"3" for programming .jic to EPCQ.

"4" for erasing .jic from EPCQ.

****************

Please enter your choice: [1, 2, 3, 4]?

```

Figure 5-1 The command line in the .batfile for FPGA and EPCQ Programming

• It will take 3-4 mins for the .jic file downloading, once the programming operation is finished, reset the board by turning the power switch off and back on; this action causes the new configuration data in the EPCQ256 device to be loaded into the FPGA chip.

### 5.2 Nios II SDRAM Test

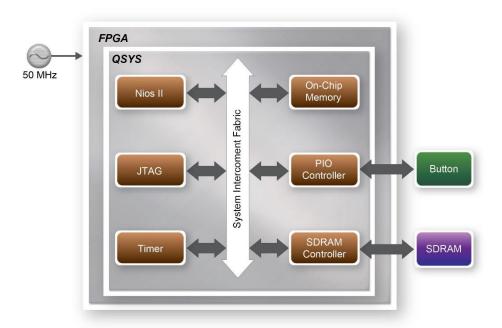

Many applications use a high-performance RAM, such as a SDRAM, to provide temporary storage. In this demonstration the hardware and software designs are provided to illustrate how to perform SDRAM memory access in QSYS. We describe how the Intel FPGA SDRAM Controller IP is used to access the SDRAM, and how the Nios II processor is used to read and write the SDRAM for hardware verification. The SDRAM controller handles the complex aspects of using SDRAM by initializing the memory devices, managing SDRAM banks, and keeping the devices refreshed at appropriate intervals.

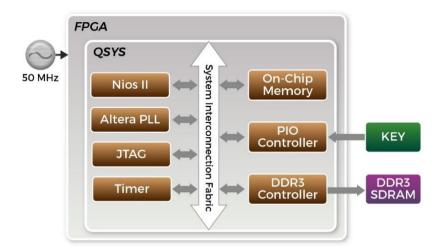

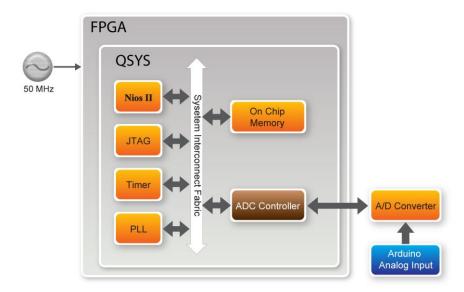

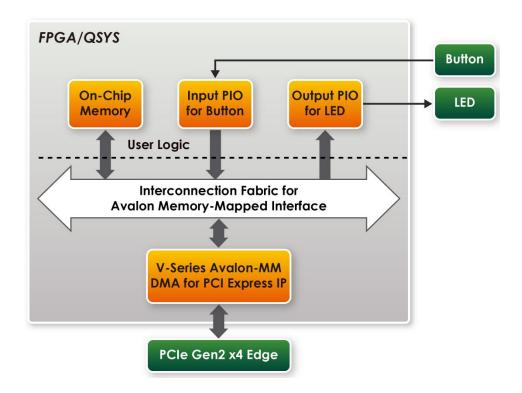

# ■ System Block Diagram

**Figure 5-2** shows the system block diagram of this demonstration. The system requires a 50MHz clock provided from the board. The SDRAM Controller is configured as a 64MB controller working at 100MHz frequency. Although the SDRAM hardware also works at

100MHz, it requires a delay to ensure the timing is correct, and the Nios II program is running in the on-chip memory.

Figure 5-2 Nios II SDRAM Test System Block

The system flow is controlled by a Nios II program. First, the Nios II program writes test patterns into the whole 64MB of SDRAM. Then, it calls Nios II system function, alt\_dcache\_flush\_all, to make sure all data has been written to the SDRAM. Finally, it reads data from the SDRAM for data verification. The program will show progress in the JTAG-Terminal when writing/reading data to/from the SDRAM. When the verification process is completed, the result is displayed in the JTAG-Terminal.

# Design Tools

- Quartus Prime v17.1

- Nios II Eclipse v17.1

#### **■** Demonstration Source Code

- Quartus Project directory: SDRAM Nios Test

- Nios II Eclipse directory: SDRAM Nios Test\Software

# ■ Nios II Project Compilation

Before you attempt to compile the reference design under Nios II Eclipse, make sure the project is cleaned first by clicking 'Clean' from the 'Project' menu of

Nios II Eclipse. Refer to the OpenVINO Starter Kit\_My\_First\_NiosII document for more details.

#### **■ Demonstration Batch File**

Demo Batch File Folder: SDRAM\_Nios\_Test \demo\_batch.

The demo batch file includes following files:

• USB-Blaster II Batch File: test.bat、test.sh

• FPGA Configuration File: SDRAM Nios Test.sof

• Nios II Program: SDRAM Nios Test.elf

### **■** Demonstration Setup

- Make sure the Quartus Prime v17.1, Nios II v17.1 and USB-Blaster II driver are installed on your PC.

- Use USB cable to connect PC and the OpenVINO Starter Kit GT Edition(J5), power on the board.

- Execute the demo batch file "test.bat" under the batch file folder: SDRAM\_Nios\_Test\demo\_batch for project running.

- After Nios II program is downloaded and executed successfully, a prompt message will be displayed in nios2-terminal.

- Press KEY0 or KEY1 of the OpenVINO Starter Kit GT Edition to start the SDRAM verify process. Press KEY0 for test continued.

- The program will display progressing and result information, as shown in Figure

5-3.

Figure 5-3 Display Progress and Result Information for the Nios II SDRAM Demo

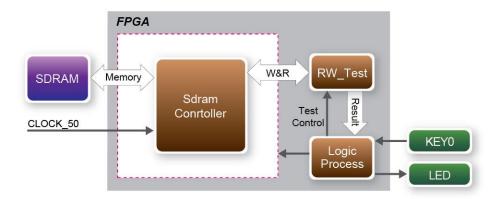

# **5.3 Verilog SDRAM Test**

OpenVINO Starter Kit GT Edition System CD provides another RTL based example designed for SDRAM test. The memory size of the SDRAM bank is still 64MB.

# **■** Function Block Diagram

**Figure 5-4** shows the function block diagram of this demonstration. The SDRAM controller uses 50MHz as a reference clock, generates one 100MHz as memory clock.

Figure 5-4 Block Diagram of Verilog SDRAM Test

RW\_test modules read and write the entire memory space of the SDRAM through the Avalon interface of the controller. In this project, the Avalon bus read/write test module will first write the entire memory and then compare the read back data with the regenerated data (the same sequence as the write data). KEY0 will trigger test control signals for the SDRAM, and the LEDs will indicate the test results according to **Table 5-1.**

# Design Tools

• Quartus Prime 17.1

#### **■** Demostration Source Code

Project directory: SDRAM\_RTL\_Test

• Bit stream used: SDRAM\_RTL\_Test.sof

#### **■** Demonstration Batch File

Demo Batch File Folder: SDRAM\_RTL\_Test\demo\_batch The demo batch file includes following files:

• Batch File: test.bat

• FPGA Configure File: OSDRAM RTL Test.sof

#### **■** Demonstration Setup

- Make sure the Quartus Prime 17.1 and USB-Blaster II driver are installed on your PC.

- Connect the USB cable to the OpenVINO Starter Kit GT Edition USB Blaster connector (J5) and the host PC.

- Power on the OpenVINO Starter Kit GT Edition.

- Execute the demo batch file "Test.bat" under the batch file folder: SDRAM RTL Test\demo batch.

- Press KEY0 on the OpenVINO Starter Kit GT Edition to start the verification process. When KEY0 is pressed, the LEDs (LEDG [2:0]) should turn on. At the instant of releasing KEY0, LEDG1 & LEDG2 should start blinking.

- After approximately 8 secords, LED1 should stop blinking and stay on to indicate that the SDRAM test PASS,

- **Table 5-1** lists the LED indicators.

- If LEDG2 is not blinking, it means 50MHz clock source is not working.

- If LEDG1 fails to remain on after 8 seconds, the corresponding SDRAM test has failed.

• Press KEY0 again to regenerate the test control signals for a new test.

**Table 5-1 LED Indicators**

| Name  | Description                                       |

|-------|---------------------------------------------------|

| LEDG0 | Reset                                             |

| LEDG1 | If light after KEY0 releasing, SDRAM test pass    |

| LEDG2 | It blinks indicating 50MHz clock source work well |

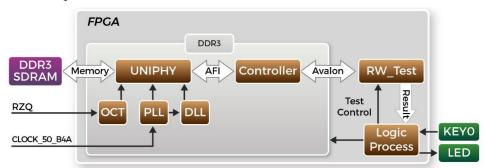

# **5.4 DDR3 SDRAM Test**

This demonstration presents a memory test function on the bank of DDR3 SDRAM on the OpenVINO Starter Kit GT Edition. The memory size of the DDR3 SDRAM bank is 1GB. Cyclone V device supports both hard memory controller and software memory controller. In this demo, the hard memory controller is used.

# **■** Function Block Diagram

**Figure 5-5** shows the function block diagram of this demonstration. The DDR3 controller uses 50MHz as a reference clock, generates one 400MHz clock as memory clock, and generates one full-rate system clock 200MHz for the controller itself, so the data rate for DDR3 is 800Mbps.

Figure 5-5 Block Diagram of DDR3 Demostration

RW\_test modules read and write the entire memory space of the DDR3 through the Avalon interface of the controller. In this project, the Avalon bus read/write test module will first write the entire memory and then compare the read back data with the regenerated data (the same sequence as the write data). KEY0 will trigger test control signals for the DDR3, and the LEDGs will indicate the test results according to **Table 5-2**.

Table 5-2 LED indicator

| LED Name | Description |

|----------|-------------|

| LEDG0    | Reset       |

| LEDG1 | If light, DDR3 test pass                     |  |

|-------|----------------------------------------------|--|

|       | It blinks indicating 50MHz clock source work |  |

| LEDG2 | well                                         |  |

# **■ DDR3 SDRAM Controller with UniPHY**

To use DDR3 controller, users need to perform the three major steps:

- Create correct pin assignments for the DDR3.

- Perform "Analysis and Synthesis" by selecting from the Quartus Prime menu

Processing→Start→Start Analysis & Synthesis.

- Run the TCL files generated by DDR3 IP by selecting from the Quartus Prime menu Tools→TCL Scripts.

# Design Tools

• Quartus Prime v17.1

#### **■** Demonstration Source Code

• Project directory: DDR3\_RTL\_Test

• Bitstream File: DDR3\_RTL\_Test.sof

#### **■ Demonstration Batch File**

Demo Batch File Folder: DDR3\_RTL\_Test \demo\_batch

The demo batch file includes following files:

Batch File: test.bat

• FPGA Configure File: DDR3 RTL Test.sof

# **■** Demonstration Setup

- Make sure the Quartus Prime v17.1 & USB-Blaster II driver are installed on your PC.

- Connect the USB cable to the USB Blaster II connector (J5) on the OpenVINO Starter Kit GT Edition and host PC.

- Power on the OpenVINO Starter Kit GT Edition.

- Execute the demo batch file "test.bat" under the batch file folder: DDR3 RTL Test\demo batch.

- Press KEY0 on the OpenVINO Starter Kit GT Edition to start the verification process. When KEY0 is pressed, the LEDs (LEDG [2:0]) should turn on. At the instant of releasing KEY0, LEDG1, LEDG2 should start blinking. After

approximately 1 seconds, LEDG1 should stop blinking and stay on to indicate that the DDR3 has passed the test, respectively, **Table 5-2** lists the LED indicators.

- If LEDG2 is not blinking, it means 50MHz clock source is not working.

- If LEDG1 does not light up after releasing KEY0, it indicates the DDR3 initializing failed.

- If LEDG1 still keeps flashing after 1 second, the corresponding DDR3 test has failed.

- Press KEY0 again to regenerate the test control signals for a new test.

# 5.5 DDR3 SDRAM Test by Nios II

Many applications use a high-performance RAM, such as a DDR3 SDRAM Controller with UniPHY IP, to provide temporary storage. In this demonstration hardware and software designs are provided to illustrate how to perform DDR3 memory access in QSYS. We describe how the Altera's "DDR3 SDRAM Controller with UniPHY IP" is used to access the DDR3-SDRAM, and how the Nios II processor is used to read and write the SDRAM for hardware verification. The DDR3 SDRAM controller handles the complex aspects of using DDR3 SDRAM by initializing the memory devices, managing SDRAM banks, and keeping the devices refreshed at appropriate intervals. Cyclone V series deivce supports both hard memory IP and soft memory IP. In this demonstration, it uses the hard memory IP.

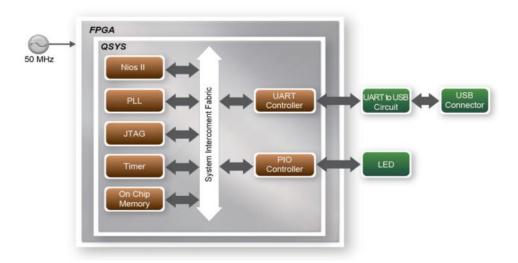

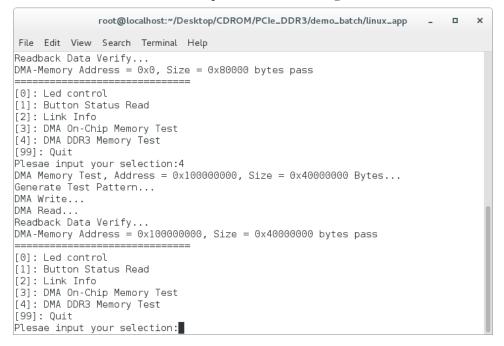

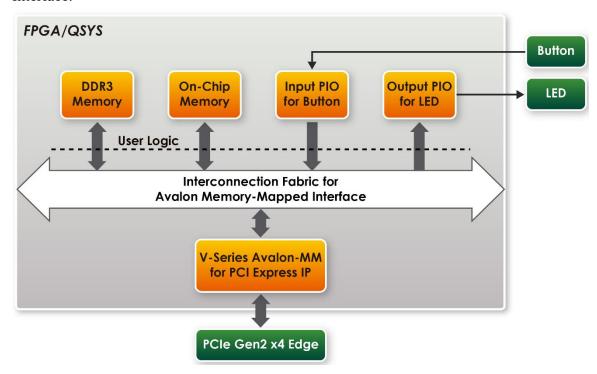

# ■ System Block Diagram

**Figure 5-6** shows the system block diagram of this demonstration. The system requires a 50MHz clock provided from the board. The DDR3 controller is configured as a 1GB DDR3-400 controller with the DDR3 data rate of 800Mbps. DDR3 IP generates one 400MHz clock as DDR3's data clock and one half-rate system clock 200MHz for those host controllers. In the QSYS, Nios II and the On-Chip Memory are designed running with the 100MHz clock, and the Nios II program is running in the on-chip memory.

Figure 5-6 Block diagram of the DDR3 Demonstration

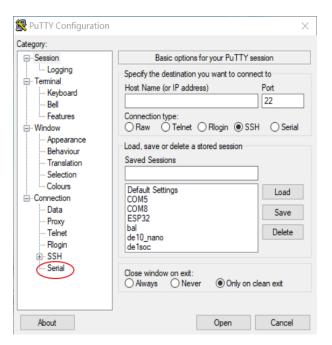

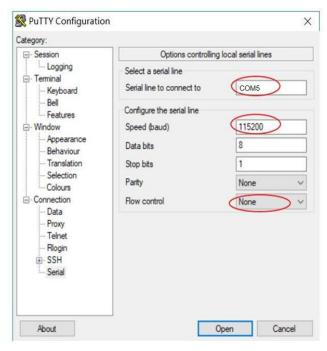

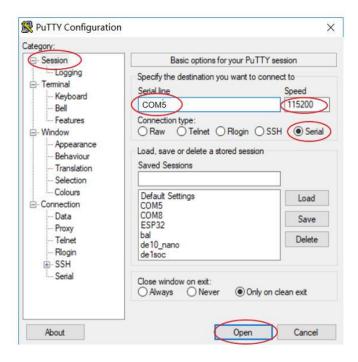

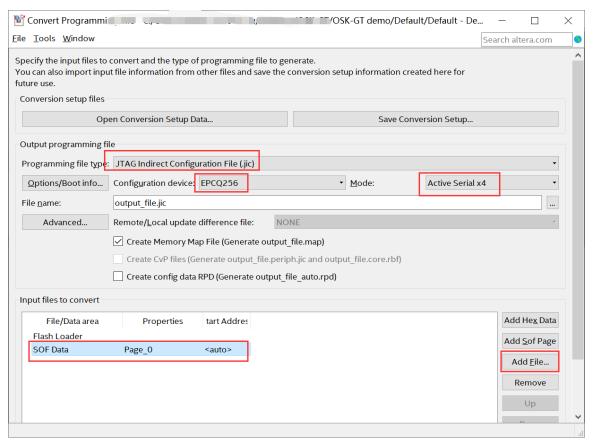

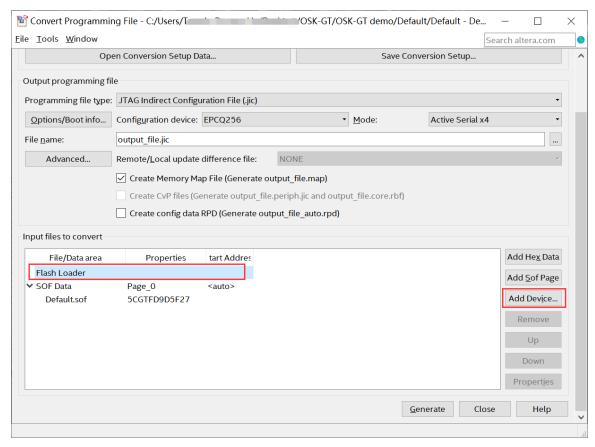

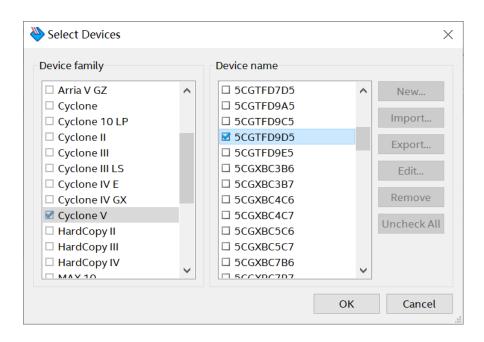

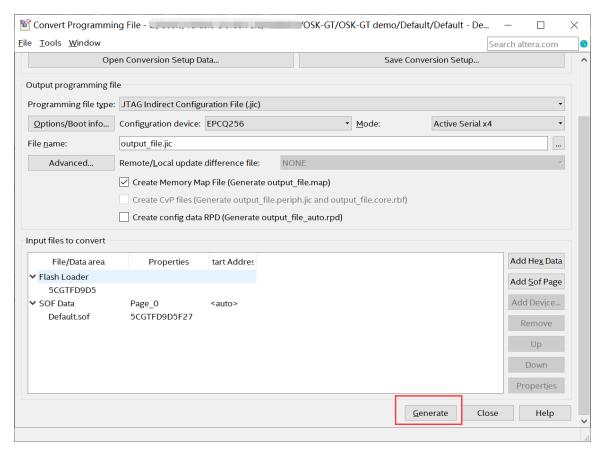

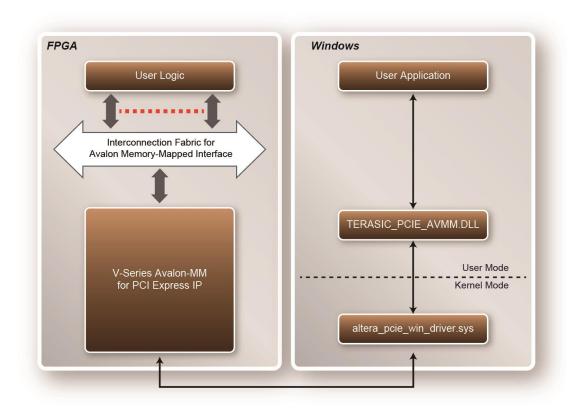

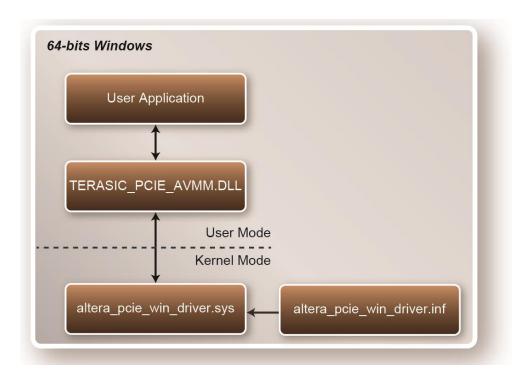

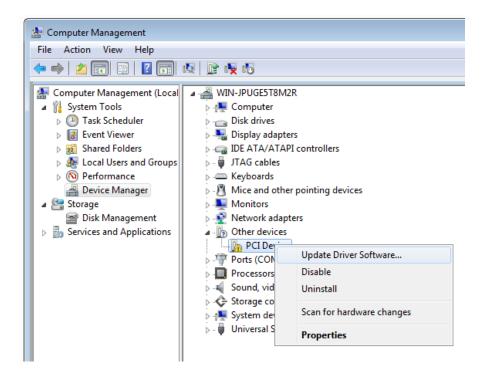

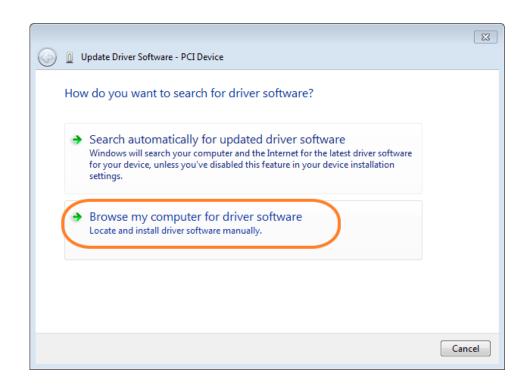

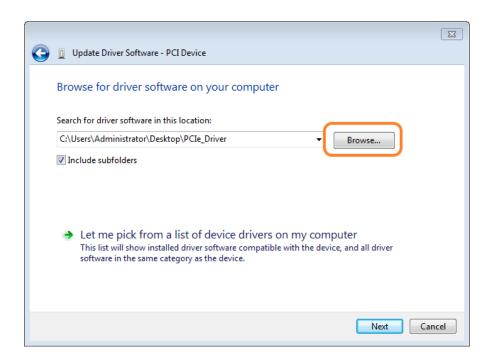

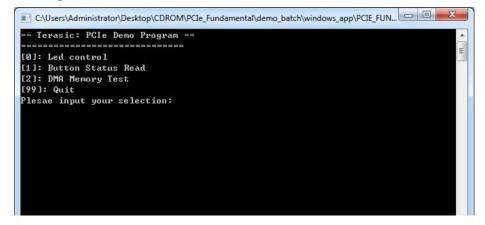

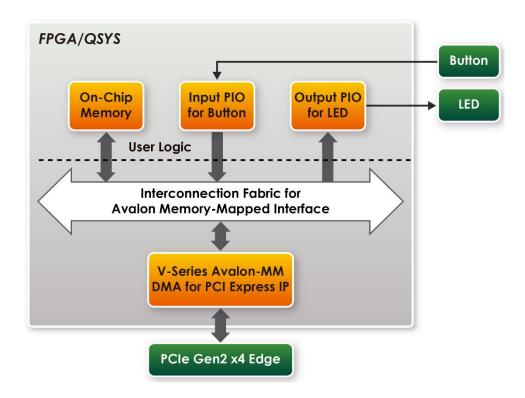

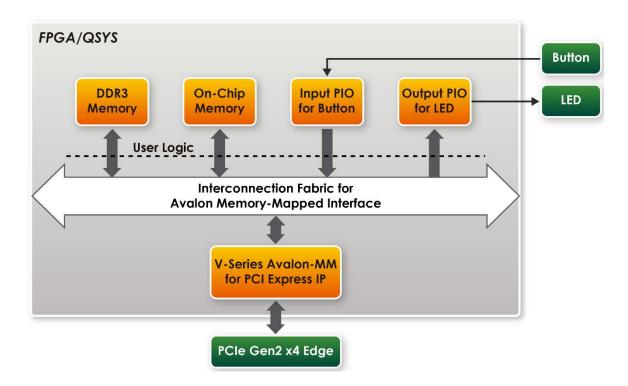

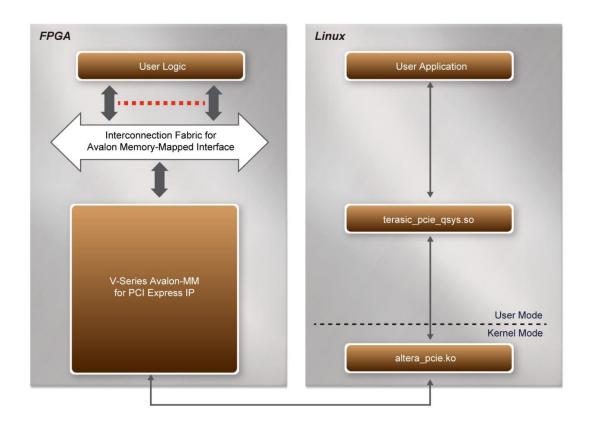

The system flow is controlled by a Nios II program. First, the Nios II program writes test patterns into the whole 1GB of DDR3. Then, it reads data from the DDR3 for data verification. The program will show progress in JTAG-Terminal when writing/reading data to/from the DDR3. When the verification process is completed, the result is displayed in the JTAG-Terminal.