# MAX10-Plus

### **CONTENTS**

| Chapter 1     | MAX 10 Plus Development Kit          | 4  |

|---------------|--------------------------------------|----|

| 1.1 Package   | e Contents                           | 4  |

| 1.2 MAX 10    | 0 Plus System CD                     | 5  |

| 1.3 Getting I | Help                                 | 5  |

| Chapter 2     | Introduction of the MAX 10 Plus      | 6  |

| 2.1 Layout a  | and Components                       | 6  |

| 2.2 Block Di  | Diagram of the MAX 10 Plus           | 7  |

| Chapter 3     | Using the MAX 10 Plus                | 10 |

| 3.1 Configur  | ration of MAX 10 FPGA on MAX 10 Plus | 10 |

| 3.2 Board St  | Status Elements                      | 14 |

| 3.3 Clock Ci  | Circuitry                            | 15 |

| 3.4 Periphera | rals Connected to the FPGA           | 16 |

| 3.4.1         | User Push-buttons, Switches, LEDs    | 16 |

| 3.4.2         | 7-segment Displays                   | 19 |

| 3.4.3         | Power Monitor                        | 20 |

| 3.4.4         | 2x6 TMD Expansion Header             | 21 |

| 3.4.5         | 24-bit Audio CODEC                   | 22 |

| 3.4.6         | Two Analog Input SMA Connectors      | 23 |

| 3.4.7         | DDR3 Memory                          | 23 |

| 3.4.8         | QSPI Flash                           | 25 |

| 3.4.9         | Ethernet                             | 26 |

| 3.4.10        | HDMI RX                              | 28 |

| 3.4.11        | 2x10 ADC Header                      | 29 |

| 3.4.12        | Potentiometer                        | 30 |

| 3.4.13        | On-board Microphone                  | 30 |

| 3.4.14        | PS/2 Serial Port                     | 30 |

| 3.4.15        | Digital-to-Analog Converter (DAC)          | 31 |

|---------------|--------------------------------------------|----|

| 3.4.16        | UART to USB                                | 32 |

| 3.4.17        | Ambient Light Sensor                       | 33 |

| 3.4.18        | Humidity and Temperature Sensor            | 33 |

| 3.4.19        | Accelerometer Sensor                       | 34 |

| 3.4.20        | Micro SD Card Socket                       | 35 |

| 3.4.21        | Power Distribution System                  | 35 |

| Chapter 4     | The MAX 10 Plus System Builder             | 37 |

| 4.1 Introduc  | ction                                      | 37 |

| 4.2 General   | Design Flow                                | 37 |

| 4.3 Using M   | IAX 10 Plus System Builder                 | 38 |

| Chapter 5     | RTL Example Codes                          | 44 |

| 5.1 PS/2 Mo   | ouse Demonstration                         | 44 |

| 5.2 ADC Po    | otentiometer                               | 46 |

| 5.3 DAC De    | emonstration                               | 48 |

| 5.4 ADC/M     | IC/LED Demonstration                       | 51 |

| Chapter 6     | NIOS Based Example Codes                   | 54 |

| 6.1 Power M   | Monitor                                    | 54 |

| 6.2 UART to   | o USB Control LED                          | 58 |

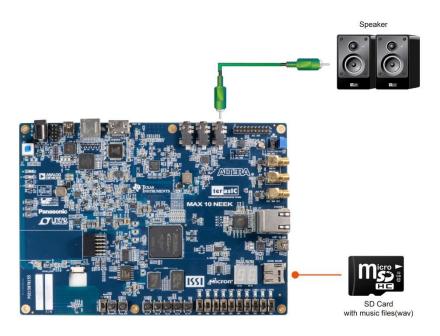

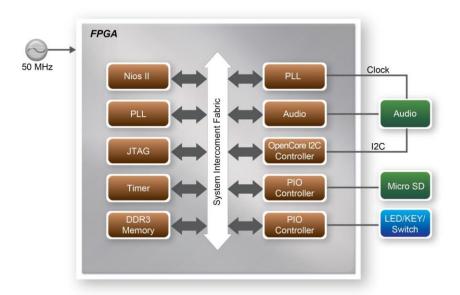

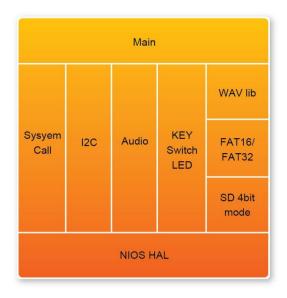

| 6.3 SD Card   | d Audio Demonstration                      | 61 |

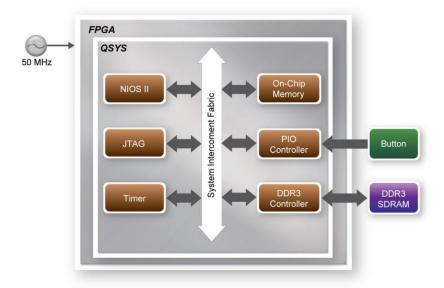

| 6.4 DDR3 S    | SDRAM Test by Nios II                      | 65 |

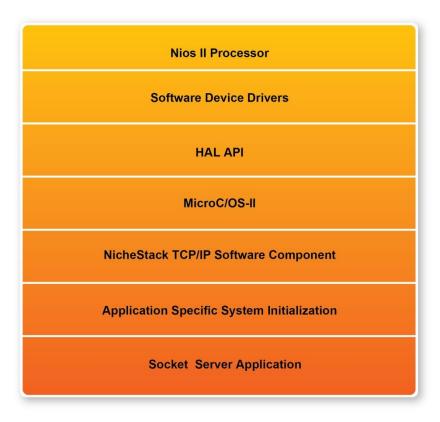

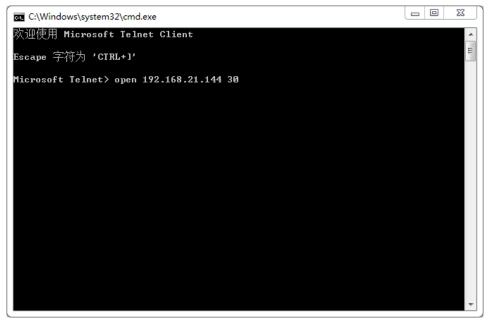

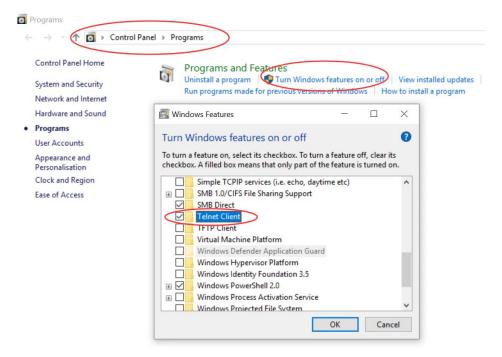

| 6.5 Ethernet  | t Socket server                            | 68 |

| 6.6 Digital A | Accelerometer Demonstration                | 75 |

| 6.7 Humidit   | ty/Temperature Sensor                      | 77 |

| Chapter 7     | Programming the Configuration Flash Memory | 79 |

| 7.1 Internal  | Configuration                              | 79 |

| 7.2 Using D   | Oual Compressed Images                     | 81 |

| 7 3 Nios II I | Load In Single Root Image                  | 84 |

#### Chapter 1

## MAX 10 Plus Development Kit

The MAX 10 Plus board from Terasic is a full featured embedded evaluation kit based upon the MAX10 family of Intel FPGAs. It offers a comprehensive design environment with everything embedded developers need to create a processing-based system.

The MAX 10 Plus board delivers an integrated platform that includes hardware, design tools, intellectual property and reference designs for developing a wide range of audio, video and many other exciting applications.

The fully integrated kit allows developers to rapidly customize their processor and IP to suit their specific needs, rather than constraining their software around the fixed feature set of the processor. The all-in-one embedded solution, the MAX 10 Plus, making the best use of the parallel nature of FPGAs.

#### 1.1 Package Contents

Figure 1-1 shows a photograph of the MAX 10 Plus board package.

Figure 1-1 The MAX 10 Plus Board Package Contents

The MAX 10 Plus board package includes:

- 1. MAX 10 Plus board

- 2. MAX 10 Plus Quick Start Guide

- 3. 5V DC power adapter

4. One USB cables (Type A to Mini-B) for USB control and FPGA programming and control

#### 1.2 MAX 10 Plus System CD

The MAX 10 Plus System CD contains all the documents and supporting materials associated with MAX 10 Plus, including the user manual, system builder, reference designs, and device datasheets. Users can download this system CD from the link: http://max10-plus.terasic.com/cd.

#### 1.3 Getting Help

Here are the addresses where you can get help if you encounter any problems:

- Terasic Technologies

- 9F., No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan

Email: <a href="mailto:support@terasic.com">support@terasic.com</a>

Tel.: +886-3-575-0880

Website: max10-plus.terasic.com

#### Chapter 2

# Introduction of the MAX 10 Plus

#### 2.1 Layout and Components

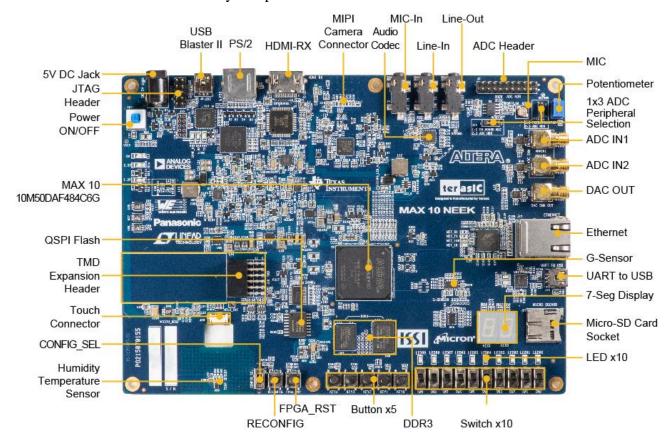

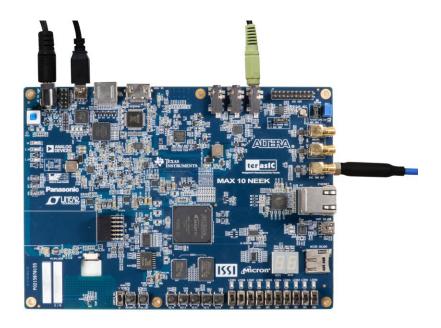

**Figure 2-1** shows a photograph of the board. It depicts the layout of the board and indicates the location of the connectors and key components.

Figure 2-1 MAX 10 Plus Development Board (top view)

The MAX 10 Plus board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects.

The following hardware is provided on the board:

- Intel MAX® 10 10M50DAF484C6G device

- USB-Blaster II onboard for programming; JTAG Mode

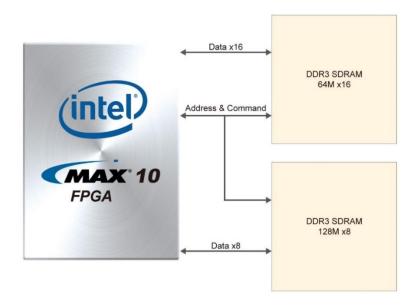

- 256MB DDR3 SDRAM (64Mx16 and 128Mx8)

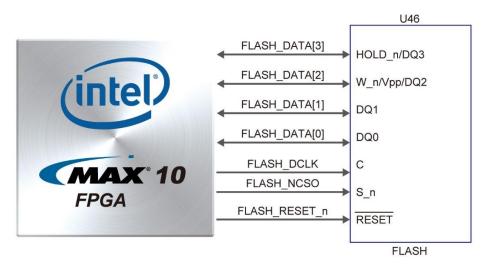

- 64MB QSPI Flash

- Micro SD card socket

- Five push-buttons

- Ten slide switches

- Ten red user LEDs

- Two 7-segment displays

- Three 50MHz clock sources from the clock generator

- 24-bit CD-quality audio CODEC with line-in, line-out jacks

- On-board microphone

- HDMI RX, incorporates HDM v1.4a features, including 3D video supporting

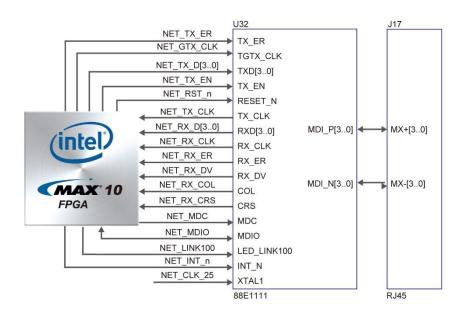

- Gigabit Ethernet PHY with RJ45 connector

- UART to USB, USB Mini-B connector

- One ambient light sensor

- One humidity and temperature sensor

- One accelerometer

- One external 16bit digital-to-analog converter (DAC) device with SMA output

- Potentiometer input to ADC

- Two MAX 10 FPGA ADC SMA inputs

- One 2x10 ADC header with 16 analog inputs connected to MAX10 ADCs

#### 2.2 Block Diagram of the MAX 10 Plus

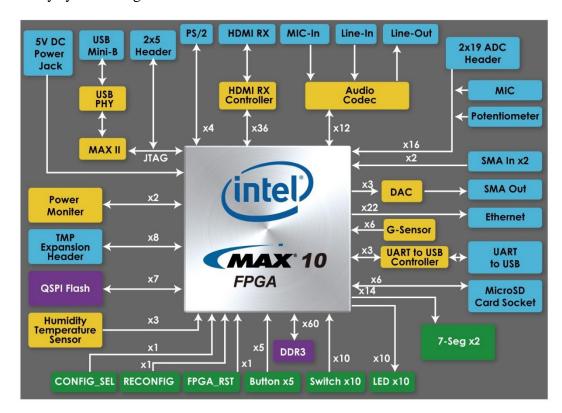

**Figure 2-2** is the block diagram of the board. All the connections are established through the MAX 10 FPGA device to provide maximum flexibility for users. Users can configure the FPGA to implement any system design.

Figure 2-2 Block Diagram of MAX 10 Plus Board

#### **FPGA Device**

- MAX 10 10M50DAF484C6G Device

- Integrated dual ADCs, each ADC supports 1 dedicated analog input and 8 dual function pins

- 50K programmable logic elements

- 1,638Kbits embedded memory

- 5,888Kbits user flash memory

- 4 PLLs

#### **Configuration and Debug**

- On-board USB-Blaster II (Mini USB type B connector)

- Optional JTAG direct via 10-pin header

- One slide switch for dual boot image selection

#### **Memory Device**

- 256MB DDR3 SDRAM (64Mx16 and 128Mx8)

- 512MB QSPI Flash

- Micro SD card socket

#### **Communication and Expansion Header**

- Gigabit Ethernet PHY with RJ45 connector

- UART to USB, USB Mini-B connector

- PS/2 mouse/keyboard connector

- 2x6 TMD (Terasic Mini Digital) Expansion Header

#### **Audio**

• 24-bit CD-quality audio CODEC with line-in, line-out jacks

#### **Video Input**

HDMI RX, incorporates HDM v1.4a features, including 3D video supporting

#### **Analog**

- Two MAX 10 FPGA ADC SMA inputs

- Potentiometer input to ADC

- On-Board MIC input to ADC

- 2x10 ADC header with 16 analog inputs connected to MAX10 ADCs

- One DAC SMA output

#### Switches, Buttons, and Indicators

- Five push-buttons

- Ten slide switches

- Ten red user LEDs

- Two 7-segment displays

#### **Sensors**

- Ambient light sensor

- Humidity and temperature sensor

- Accelerometer

- Power monitor

#### **Power**

• 5V/3A DC input

# Chapter 3 Using the MAX 10 Plus

This chapter provides an instruction to use the board and describes the peripherals.

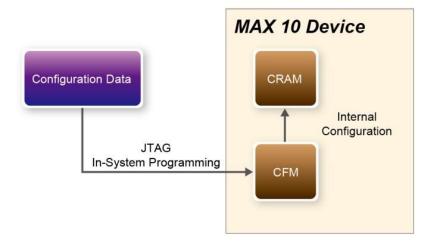

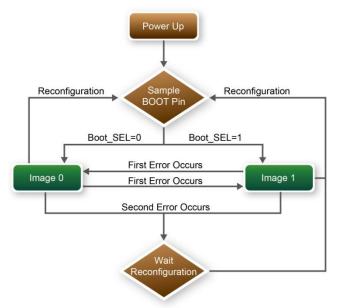

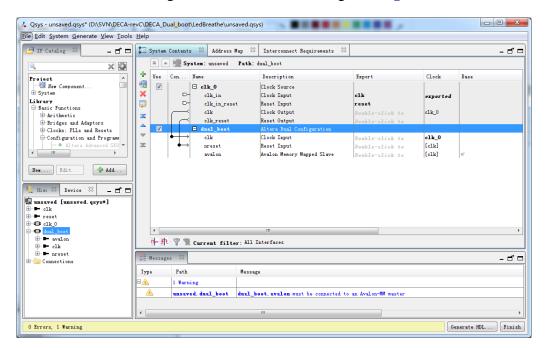

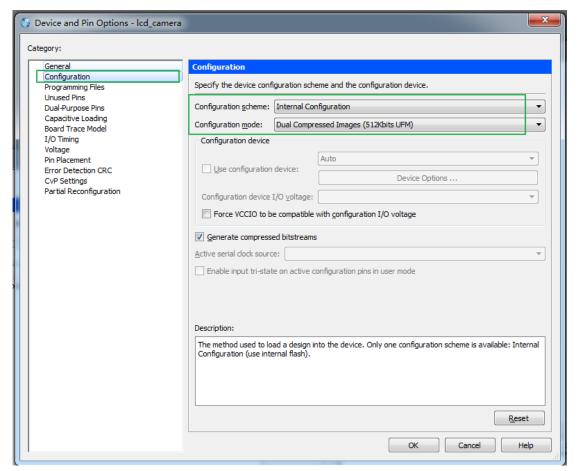

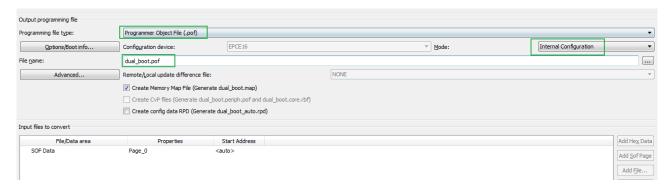

#### 3.1 Configuration of MAX 10 FPGA on MAX 10 Plus

There are two types of configuration method supported by MAX 10 Plus:

1. JTAG configuration: configuration using JTAG port.

JTAG configuration scheme allows you to directly configure the device core through JTAG pins - TDI, TDO, TMS, and TCK pins. The Quartus II software automatically generates .sof that is used for JTAG configuration with a download cable in the Quartus II software programmer.

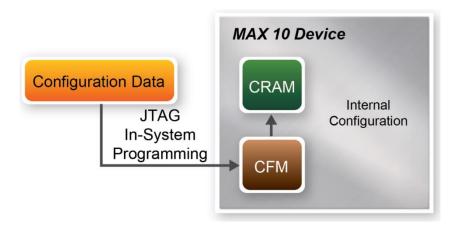

2. Internal configuration: configuration using internal flash.

Before internal configuration, you need to program the configuration data into the configuration flash memory (CFM) which provides non-volatile storage for the bit stream. The information is retained within CFM even if the MAX 10 Plus is turned off. When the board is powered on, the configuration data in the CFM is automatically loaded into the MAX 10 FPGA.

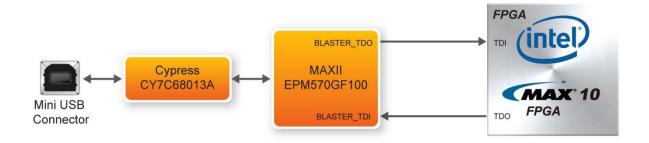

#### ■ JTAG Chain on MAX 10 Plus

The FPGA device can be configured through JTAG interface on MAX 10 Plus board, but the JTAG chain must form a closed loop, which allows Quartus II programmer to the detect FPGA device. **Figure 3-1** illustrates the JTAG chain on MAX 10 Plus.

Figure 3-1 Path of the JTAG Chain

#### ■ Configure the FPGA in JTAG Mode

The following shows how the FPGA is programmed in JTAG mode step by step.

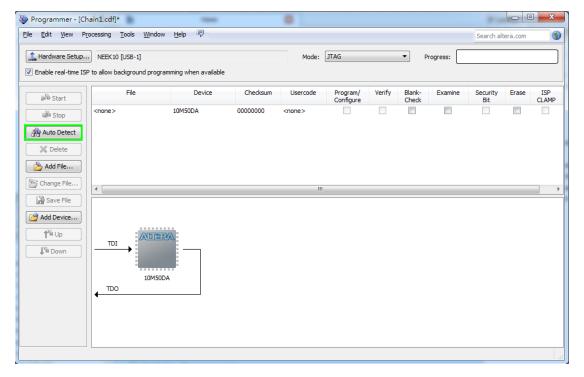

1. Open the Quartus II programmer and click **Auto Detect**, as circled in **Figure 3-2**.

Figure 3-2 Detect FPGA Device in JTAG Mode

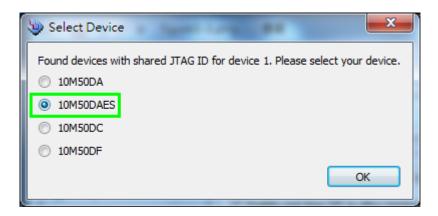

2. Select detected device associated with the board, as circled in **Figure 3-3**.

Figure 3-3 Select 10M50DAES Device

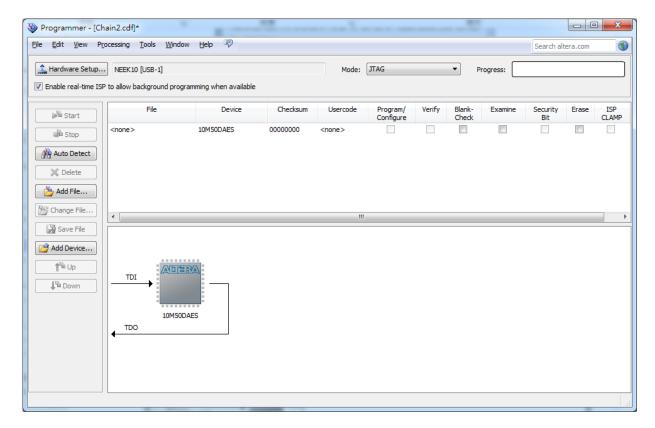

3. FPGA is detected, as shown in Figure 3-4.

Figure 3-4 FPGA Detected in Quartus Programmer

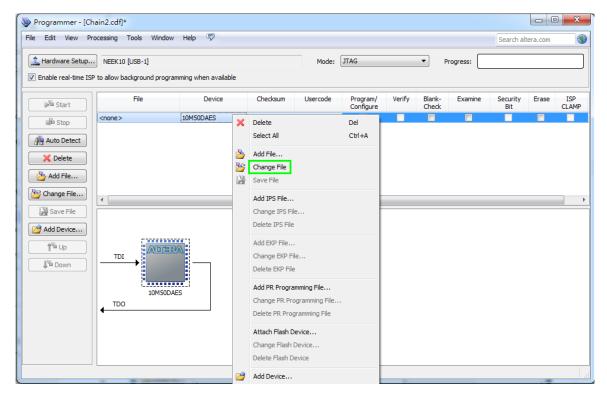

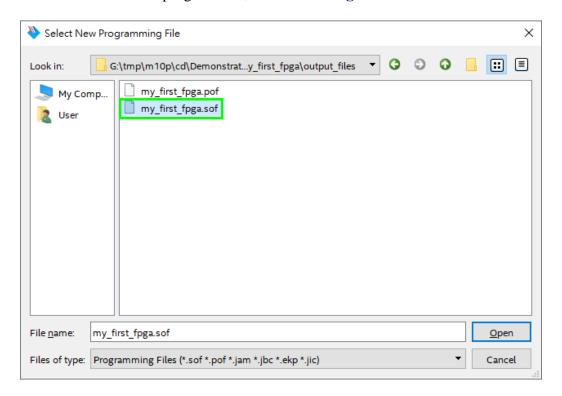

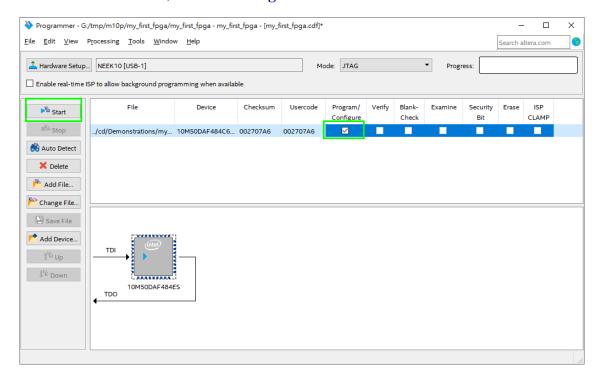

4. Right click on the FPGA device and open the .sof file to be programmed, as highlighted in **Figure 3-5**.

Figure 3-5 Open the .sof File to be Programmed into the FPGA Device

5. Select the .sof file to be programmed, as shown in **Figure 3-6**.

Figure 3-6 Select the .sof File to be Programmed into the FPGA Device

6. Click **Program/Configure** check box and then click **Start** button to download the .sof file into the FPGA device, as shown in **Figure 3-7**.

Figure 3-7 Program. sof File into the FPGA Device

#### **■** Internal Configuration

- The configuration data to be written to CFM will be part of the programmer object file (.pof). This configuration data is automatically loaded from the CFM into the MAX 10 devices when the board is powered up.

- Please refer to *Chapter 7 Programming the Configuration Flash Memory* for the basic programming instruction on the configuration flash memory (CFM).

Figure 3-8 High-Level Overview of Internal Configuration for MAX 10 Devices

#### 3.2 Board Status Elements

In addition to the 10 LEDs that FPGA device can control, there are 4 indicators which can indicate the board status (See **Figure 3-9**), please refer the details in **Table 3-1**.

Figure 3-9 LED Indicators on MAX 10 Plus

**Table 3-1 LED Indicators**

| <b>Board Reference</b> | LED Name   | Description                                                                    |

|------------------------|------------|--------------------------------------------------------------------------------|

| D13                    | 5V Power   | Illuminate when 5V power is active.                                            |

| D14                    | 2.5V Power | Illuminate when 2.5V power is active.                                          |

| D16                    | 1.2V Power | Illuminate when 1.2V power is active.                                          |

| D6                     | CONF_DONE  | Illuminate when configuration data is loaded into MAX 10 device without error. |

| D7                     | JTAG_RX    | Illuminate during data is uploaded from MAX 10 device to PC through UB2.       |

| D8                     | JTAG_TX    | Illuminate during configuration data is loaded into MAX 10 device from UB2.    |

| TXD                    | TXD        | Illuminate during transmitting data via USB.                                   |

| RXD                    | RXD        | Illuminate during receiving data via USB.                                      |

#### 3.3 Clock Circuitry

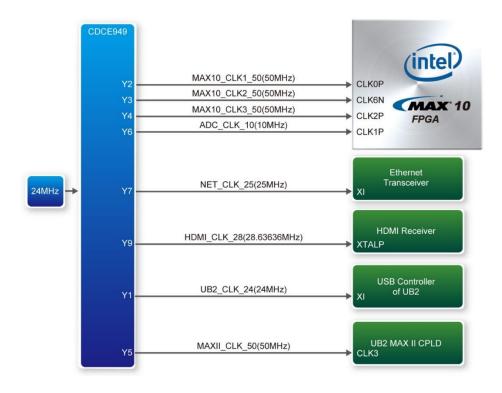

**Figure 3-10** shows the default frequency of all external clocks to the MAX 10 FPGA. A clock generator is used to distribute clock signals with low jitter. The three 50MHz clock signals connected to the FPGA are used as clock sources for user logic. One 25MHz clock signal is connected to the clock input of Gigabit Ethernet Transceiver. One 24MHz clock signal is connected to the clock inputs of USB microcontroller of USB Blaster II. One 28.63636MHz clock signal is connected to the clock input of HDMI Receiver chip. The other 50MHz clock signal is connected to MAX CPLD of USB Blaster II. One 10MHz clock signal is connected to the PLL1 and PLL3 of FPGA, the outputs of these two PLLs can drive ADC clock. The associated pin assignment for clock inputs to FPGA I/O pins is listed in **Table 3-2.**

Figure 3-10 Block Diagram of the Clock Distribution on MAX 10 Plus

**Table 3-2 Pin Assignment of Clock Inputs**

| Signal Name   | FPGA Pin No. | Description       | I/O Standard |

|---------------|--------------|-------------------|--------------|

| MAX10_CLK1_50 | PIN_N5       | 50MHz clock input | 2.5V         |

| MAX10_CLK2_50 | PIN_V9       | 50MHz clock input | 3.3V         |

| MAX10_CLK3_50 | PIN_N14      | 50MHz clock input | 1.5V         |

| ADC_CLK_10    | PIN_M9       | 10MHz clock input | 3.3V         |

#### 3.4 Peripherals Connected to the FPGA

This section describes the interfaces connected to the FPGA. User can control or monitor different interfaces with user logic from the FPGA.

#### 3.4.1 User Push-buttons, Switches, LEDs

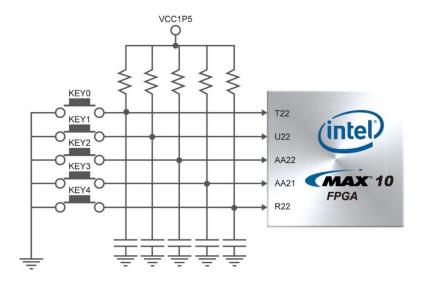

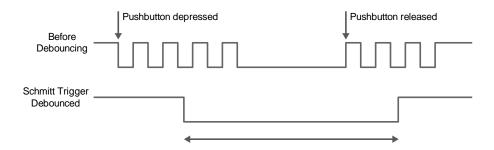

The board has five push-buttons connected to the FPGA, as shown in **Figure 3-11.** MAX 10 devices support Schmitt trigger input on all I/O pins. A Schmitt trigger feature introduces hysteresis to the input signal for improved noise immunity, especially for signal with slow edge rate and act as switch debounce in **Figure 3-12** for the push-buttons connected.

16

Figure 3-11 Connections between the Push-buttons and the MAX 10 FPGA

Figure 3-12 Switch Debouncing

There are two ten switches connected to the FPGA, as shown in **Figure 3-13**. These switches are used as level-sensitive data inputs to a circuit. Each switch is connected directly and individually to the FPGA. When the switch is set to the DOWN position (towards the edge of the board), it generates a low logic level to the FPGA. When the switch is set to the UP position, a high logic level is generated to the FPGA.

Figure 3-13 Connections between the Slide Switches and the MAX 10 FPGA

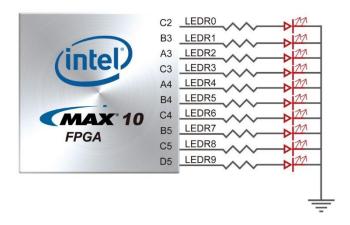

There are also ten user-controllable LEDs connected to the FPGA. Each LED is driven directly and individually by the MAX 10 FPGA; driving its associated pin to a high logic level or low level to turn the LED on or off, respectively. **Figure 3-14** shows the connections between LEDs and MAX 10 FPGA. **Table 3-3**, **Table 3-4** and **Table 3-5** list the pin assignment of user push-buttons, switches, and LEDs.

Figure 3-14 Connections between the LEDs and the MAX 10 FPGA

**Table 3-3 Pin Assignment of Push-buttons**

| Signal Name | FPGA Pin No. | Description    | I/O Standard |

|-------------|--------------|----------------|--------------|

| KEY[0]      | PIN_T22      | Push-button[0] | 1.5V         |

| KEY[1]      | PIN_U22      | Push-button[1] | 1.5V         |

| KEY[2]      | PIN_AA22     | Push-button[2] | 1.5V         |

| KEY[3]      | PIN_AA21     | Push-button[3] | 1.5V         |

18

| KEY[4]   | DIN R22  | Puch button[4] | 1 5V  |

|----------|----------|----------------|-------|

| KL 1 [4] | FIIN_K22 | Push-button[4] | 1.J V |

**Table 3-4 Pin Assignment of Slide Switches**

| Signal Name | FPGA Pin No. | Description     | I/O Standard |

|-------------|--------------|-----------------|--------------|

| SW[0]       | PIN_N22      | Slide Switch[0] | 1.5V         |

| SW[1]       | PIN_M22      | Slide Switch[1] | 1.5V         |

| SW[2]       | PIN_N21      | Slide Switch[2] | 1.5V         |

| SW[3]       | PIN_L22      | Slide Switch[3] | 1.5V         |

| SW[4]       | PIN_J22      | Slide Switch[4] | 1.5V         |

| SW[5]       | PIN_H22      | Slide Switch[5] | 1.5V         |

| SW[6]       | PIN_J21      | Slide Switch[6] | 1.5V         |

| SW[7]       | PIN_C21      | Slide Switch[7] | 1.5V         |

| SW[8]       | PIN_G19      | Slide Switch[8] | 1.5V         |

| SW[9]       | PIN_H21      | Slide Switch[9] | 1.5V         |

**Table 3-5 Pin Assignment of LEDs**

| Signal Name | FPGA Pin No. | Description | I/O Standard |

|-------------|--------------|-------------|--------------|

| LEDR[0]     | PIN_C2       | LEDR [0]    | 3.3V         |

| LEDR[1]     | PIN_B3       | LEDR [1]    | 3.3V         |

| LEDR[2]     | PIN_A3       | LEDR [2]    | 3.3V         |

| LEDR[3]     | PIN_C3       | LEDR [3]    | 3.3V         |

| LEDR[4]     | PIN_A4       | LEDR [4]    | 3.3V         |

| LEDR[5]     | PIN_B4       | LEDR [5]    | 3.3V         |

| LEDR[6]     | PIN_C4       | LEDR [6]    | 3.3V         |

| LEDR[7]     | PIN_B5       | LEDR [7]    | 3.3V         |

| LEDR[8]     | PIN_C5       | LEDR [8]    | 3.3V         |

| LEDR[9]     | PIN_D5       | LEDR [9]    | 3.3V         |

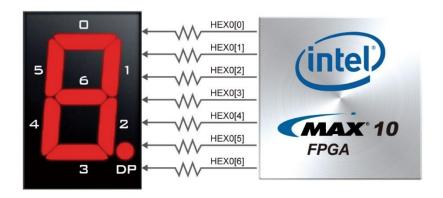

#### 3.4.2 7-segment Displays

The MAX 10 Plus has two 7-segment displays. These displays are paired to display numbers in various sizes. **Figure 3-15** shows the connection of seven segments (common anode) to pins on MAX 10 FPGA. The segment can be turned on or off by applying a low logic level or high logic level from the FPGA, respectively.

Each segment in a display is indexed from 0 to 6, with corresponding positions given in **Figure 3-15**. **Table 3-6** shows the pin assignment of FPGA to the 7-segment displays.

Figure 3-15 Connections between the 7-segment Display HEX0 and the MAX 10 FPGA

Table 3-6 Pin Assignment of 7-segment Displays

| Signal Name | FPGA Pin No. | Description              | I/O Standard |  |  |

|-------------|--------------|--------------------------|--------------|--|--|

| HEX0[0]     | PIN_D6       | Seven Segment Digit 0[0] | 3.3V         |  |  |

| HEX0[1]     | PIN_A5       | Seven Segment Digit 0[1] | 3.3V         |  |  |

| HEX0[2]     | PIN_C6       | Seven Segment Digit 0[2] | 3.3V         |  |  |

| HEX0[3]     | PIN_A6       | Seven Segment Digit 0[3] | 3.3V         |  |  |

| HEX0[4]     | PIN_F7       | Seven Segment Digit 0[4] | 3.3V         |  |  |

| HEX0[5]     | PIN_D7       | Seven Segment Digit 0[5] | 3.3V         |  |  |

| HEX0[6]     | PIN_B7       | Seven Segment Digit 0[6] | 3.3V         |  |  |

| HEX1[0]     | PIN_C7       | Seven Segment Digit 1[0] | 3.3V         |  |  |

| HEX1[1]     | PIN_C8       | Seven Segment Digit 1[1] | 3.3V         |  |  |

| HEX1[2]     | PIN_D8       | Seven Segment Digit 1[2] | 3.3V         |  |  |

| HEX1[3]     | PIN_D10      | Seven Segment Digit 1[3] | 3.3V         |  |  |

| HEX1[4]     | PIN_E10      | Seven Segment Digit 1[4] | 3.3V         |  |  |

| HEX1[5]     | PIN_H11      | Seven Segment Digit 1[5] | 3.3V         |  |  |

| HEX1[6]     | PIN_E6       | Seven Segment Digit 1[6] | 3.3V         |  |  |

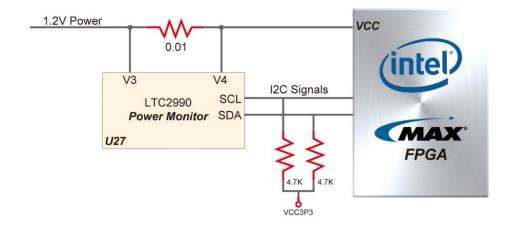

#### 3.4.3 Power Monitor

The MAX 10 Plus has implemented three power monitor chips to monitor the FPGA core power and VCCIO power voltage and current. **Figure 3-16** shows the connection between the power monitor chip and the MAX 10 FPGA. Through the I2C serial interface, the power monitor can be configured to measure remote voltage and remote current. Programmable calibration value, conversion times, and averaging, combined with an internal multiplier, enable direct readouts of current in amperes and power in watts. **Table 3-7** shows the pin assignment of power monitor I2C bus.

Figure 3-16 Connections between the Power Monitor Chip and the MAX 10 FPGA

**Table 3-7 Pin Assignment of Power Monitor I2C Bus**

| Signal Name | FPGA Pin No. | Description       | I/O Standard |

|-------------|--------------|-------------------|--------------|

| PM_I2C_SCL  | PIN_E8       | Power Monitor SCL | 3.3V         |

| PM_I2C_SDA  | PIN_E9       | Power Monitor SDA | 3.3V         |

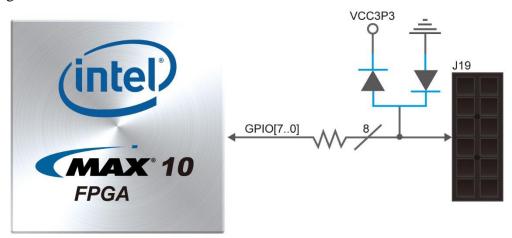

#### 3.4.4 2x6 TMD Expansion Header

The board has one 2x6 TMD (Terasic Mini Digital) expansion header. The TMD header has 8 digital GPIO user pins connected to the MAX 10 FPGA, two 3.3V power pins and two ground pins. There are two Transient Voltage Suppressor diode arrays used to implement ESD protection for 8 GPIO user pins.

**Figure 3-17** shows the connection between the TMD header and MAX 10 FPGA. **Table 3-8** shows the pin assignment of 2x6 TMD header.

Figure 3-17 Connections between the 2x6 TMD Header and MAX 10 FPGA

Manual

Table 3-8 Pin Assignment of 2x6 TMD Header

| Signal Name | FPGA Pin No. | Description         | I/O Standard |

|-------------|--------------|---------------------|--------------|

| GPIO[0]     | PIN_Y17      | GPIO Connection [0] | 3.3V         |

| GPIO[1]     | PIN_AA17     | GPIO Connection [1] | 3.3V         |

| GPIO[2]     | PIN_V16      | GPIO Connection [2] | 3.3V         |

| GPIO[3]     | PIN_W15      | GPIO Connection [3] | 3.3V         |

| GPIO[4]     | PIN_AB16     | GPIO Connection [4] | 3.3V         |

| GPIO[5]     | PIN_AA16     | GPIO Connection [5] | 3.3V         |

| GPIO[6]     | PIN_Y16      | GPIO Connection [6] | 3.3V         |

| GPIO[7]     | PIN_W16      | GPIO Connection [7] | 3.3V         |

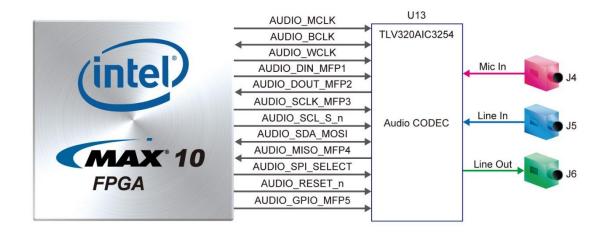

#### 3.4.5 24-bit Audio CODEC

The MAX 10 Plus offers high-quality 24-bit audio via the Texas Instruments TLV320AIC3254 audio CODEC (Encoder/Decoder). This chip on MAX 10 Plus supports, line-in, line-out and microphone-in ports with adjustable sample rate from 8KHz to 192KHz. The connection of the audio circuitry to the FPGA is shown in **Figure 3-18**, and the associated pin assignment to the FPGA is listed in **Table 3-9**. More information about the TLV320AIC3254 CODEC is available in its datasheet, which can be found on the manufacturer's website, or in the directory \Datasheet\Audio CODEC of MAX 10 Plus System CD.

Figure 3-18 Connections between the FPGA and Audio CODEC

**Table 3-9 Pin Assignment of Audio CODEC**

| Signal Name     | FPGA<br>Pin No. | Description                                                 | I/O<br>Standard |

|-----------------|-----------------|-------------------------------------------------------------|-----------------|

| AUDIO_MCLK      | PIN_J11         | Master output Clock                                         | 2.5V            |

| AUDIO_BCLK      | PIN_J12         | Audio serial data bus (primary) bit clock                   | 2.5V            |

| AUDIO_WCLK      | PIN_H12         | Audio serial data bus (primary) word clock                  | 2.5V            |

| AUDIO_DIN_MFP1  | PIN_J13         | Audio serial data bus data output/digital microphone output | 2.5V            |

| AUDIO_DOUT_MFP2 | PIN_H13         | Audio serial data bus data input/general purpose input      | 2.5V            |

| AUDIO_SCLK_MFP3 | PIN_H14         | SPI serial Clock/headphone-detect output                    | 2.5V            |

| AUDIO_SCL_SS_n  | PIN F15 | I2C Clock/SPI interface mode chip-select signal | 2.5V |

|-----------------|---------|-------------------------------------------------|------|

| AUDIO_SDA_MOSI  |         | I2C Data/SPI interface mode serial data output  | 2.5V |

| AUDIO_MISO_MFP4 |         | Serial data input/General purpose input         | 2.5V |

|                 | 1       | Control mode select pin                         | 2.5V |

| AUDIO_RESET_n   | PIN_D13 | Reset signal                                    | 2.5V |

| AUDIO_GPIO_MFP5 | PIN_D14 | General Purpose digital IO/CLKOUT input         | 2.5V |

#### 3.4.6 Two Analog Input SMA Connectors

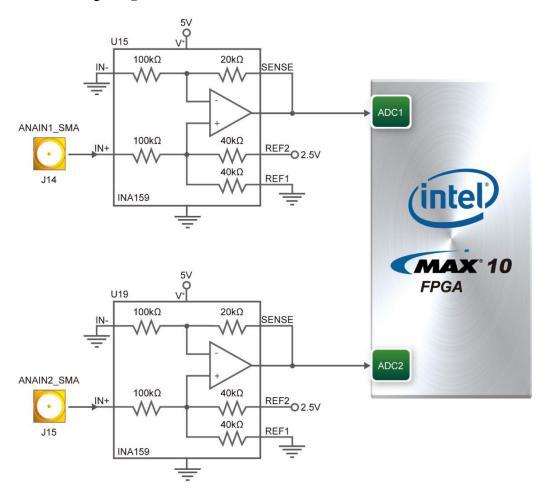

The MAX 10 Plus implements two analog input SMA connectors. The analog inputs are amplified and translated by Texas Instruments INA159 gain of 0.2 level translation difference amplifier, then the amplifier's outputs are fed to dedicated single-ended analog input pins for MAX 10 build-in ADC1 and ADC2 respectively. With the amplifiers, the analog input of two SMAs support from -6.25V to +6.25V range. **Figure 3-19** shows the connection of SMA connectors to the FPGA.

Figure 3-19 Connection of SMA Connectors to the FPGA

#### 3.4.7 DDR3 Memory

The board supports 256MB of DDR3 SDRAM comprising of one 16bit (64Mx16) DDR3 device and one 8bit (128Mx8) device. The DDR3 devices shipped with this board are running at 300MHz with the soft IP of MAX 10 external memory interface solution. **Figure 3-20** shows the connections

between the DDR3 and MAX 10 FPGA. Table 3-10 shows the DDR3 interface pin assignments.

Figure 3-20 Connections between the DDR3 and FPGA

Table 3-10 Pin Assignment of FPGA DDR3 Memory

| Signal Name | FPGA Pin No.             | Description                | I/O Standard            |

|-------------|--------------------------|----------------------------|-------------------------|

| DDR3_A[0]   | PIN_U20                  | DDR3 Address[0]            | SSTL-15 Class I         |

| DDR3_A[1]   | PIN_F19                  | DDR3 Address[1]            | SSTL-15 Class I         |

| DDR3_A[2]   | PIN_V20                  | DDR3 Address[2]            | SSTL-15 Class I         |

| DDR3_A[3]   | PIN_G20                  | DDR3 Address[3]            | SSTL-15 Class I         |

| DDR3_A[4]   | PIN_F20                  | DDR3 Address[4]            | SSTL-15 Class I         |

| DDR3_A[5]   | PIN_E20                  | DDR3 Address[5]            | SSTL-15 Class I         |

| DDR3_A[6]   | PIN_E21                  | DDR3 Address[6]            | SSTL-15 Class I         |

| DDR3_A[7]   | PIN_Y20                  | DDR3 Address[7]            | SSTL-15 Class I         |

| DDR3_A[8]   | PIN_C22                  | DDR3 Address[8]            | SSTL-15 Class I         |

| DDR3_A[9]   | PIN_D22                  | DDR3 Address[9]            | SSTL-15 Class I         |

| DDR3_A[10]  | PIN_J14                  | DDR3 Address[10]           | SSTL-15 Class I         |

| DDR3_A[11]  | PIN_E22                  | DDR3 Address[11]           | SSTL-15 Class I         |

| DDR3_A[12]  | PIN_G22                  | DDR3 Address[12]           | SSTL-15 Class I         |

| DDR3_A[13]  | PIN_D19                  | DDR3 Address[13]           | SSTL-15 Class I         |

| DDR3_A[14]  | PIN_C20                  | DDR3 Address[14]           | SSTL-15 Class I         |

| DDR3_BA[0]  | PIN_W22                  | DDR3 Bank Address[0]       | SSTL-15 Class I         |

| DDR3_BA[1]  | PIN_Y21                  | DDR3 Bank Address[1]       | SSTL-15 Class I         |

| DDR3_BA[2]  | PIN_Y22                  | DDR3 Bank Address[2]       | SSTL-15 Class I         |

| DDR3_CAS_n  | PIN_U19                  | DDR3 Column Address Strobe | SSTL-15 Class I         |

| DDR3_CKE    | PIN_V18                  | Clock Enable pin for DDR3  | SSTL-15 Class I         |

| DDD2 CLV    | PIN_E18 Clock n for DDR3 | Cl. 1 C DDD2               | DIFFERENTIAL 1.5-V      |

| DDR3_CLK_n  |                          | SSTL Class I               |                         |

| DDR3_CLK_p  | PIN_D18                  | Clock p for DDR3           | Differential 1.5-V SSTL |

|                |            |                         | Class I                 |

|----------------|------------|-------------------------|-------------------------|

| DDR3_CS_n      | PIN_W20    | DDR3 Chip Select        | SSTL-15 Class I         |

| DDR3_DM[0]     | PIN_J15    | DDR3 Data Mask[0]       | SSTL-15 Class I         |

| DDR3_DM[1]     | PIN_N19    | DDR3 Data Mask[1]       | SSTL-15 Class I         |

| DDR3_DQ[0]     | PIN_J18    | DDR3 Data[0]            | SSTL-15 Class I         |

| DDR3_DQ[1]     | PIN_H19    | DDR3 Data[1]            | SSTL-15 Class I         |

| DDR3_DQ[2]     | PIN_K20    | DDR3 Data[2]            | SSTL-15 Class I         |

| DDR3_DQ[3]     | PIN_H18    | DDR3 Data[3]            | SSTL-15 Class I         |

| DDR3_DQ[4]     | PIN_K18    | DDR3 Data[4]            | SSTL-15 Class I         |

| DDR3_DQ[5]     | PIN_H20    | DDR3 Data[5]            | SSTL-15 Class I         |

| DDR3_DQ[6]     | PIN_K19    | DDR3 Data[6]            | SSTL-15 Class I         |

| DDR3_DQ[7]     | PIN_J20    | DDR3 Data[7]            | SSTL-15 Class I         |

| DDR3_DQ[8]     | PIN_L18    | DDR3 Data[8]            | SSTL-15 Class I         |

| DDR3_DQ[9]     | PIN_M18    | DDR3 Data[9]            | SSTL-15 Class I         |

| DDR3_DQ[10]    | PIN_M14    | DDR3 Data[10]           | SSTL-15 Class I         |

| DDR3_DQ[11]    | PIN_N20    | DDR3 Data[11]           | SSTL-15 Class I         |

| DDR3_DQ[12]    | PIN_L20    | DDR3 Data[12]           | SSTL-15 Class I         |

| DDR3_DQ[13]    | PIN_M20    | DDR3 Data[13]           | SSTL-15 Class I         |

| DDR3_DQ[14]    | PIN_M15    | DDR3 Data[14]           | SSTL-15 Class I         |

| DDR3_DQ[15]    | PIN_L19    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[16]    | PIN_T19    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[17]    | PIN_R20    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[18]    | PIN_R15    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[19]    | PIN_P15    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[20]    | PIN_P19    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[21]    | PIN_P14    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[22]    | PIN_R14    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQ[23]    | PIN_P20    | DDR3 Data[15]           | SSTL-15 Class I         |

| DDR3_DQS_n[0]  | PIN_K15    | DDR3 Data Strobe n[0]   | Differential 1.5-V SSTL |

| [ט]וו_פטע_כאעע | PIN_KI3    | DDR3 Data Strobe n[0]   | Class I                 |

| DDR3_DQS_n[1]  | PIN_L15    | DDR3 Data Strobe n[1]   | Differential 1.5-V SSTL |

| [1]וו_פטע_כאעע | PIN_LIS    | DDR3 Data Strobe II[1]  | Class I                 |

| DDR3_DQS_p[0]  | PIN K14    | DDR3 Data Strobe p[0]   | Differential 1.5-V SSTL |

| DDK3_DQs_p[0]  | 1 111_1X14 | DDR3 Data Suobe p[0]    | Class I                 |

| DDR3_DQS_p[1]  | PIN_L14    | DDR3 Data Strobe p[1]   | Differential 1.5-V SSTL |

| DDK3_DQs_p[1]  | I II\_L14  | DDR3 Data Suote p[1]    | Class I                 |

| DDR3_ODT       | PIN_V22    | DDR3 On-die Termination | SSTL-15 Class I         |

| DDR3_RAS_n     | PIN_N18    | DDR3 Row Address Strobe | SSTL-15 Class I         |

| DDR3_RESET_n   | PIN_B22    | DDR3 Reset              | SSTL-15 Class I         |

| DDR3_WE_n      | PIN_W19    | DDR3 Write Enable       | SSTL-15 Class I         |

#### 3.4.8 QSPI Flash

The MAX 10 Plus supports a 512M-bit serial NOR flash device for non-volatile storage, user data and program. This device has a 4-bit data interface and uses 3.3V CMOS signaling standard. Connections between MAX 10 FPGA and Flash are shown in **Figure 3-21**. **Table 3-11** shows the

#### DDR3 interface pin assignments.

Figure 3-21 Connections between MAX 10 FPGA and QSPI Flash

Table 3-11 Pin Assignment of QSPI Flash

| Signal Name   | FPGA Pin No. | Description       | I/O<br>Standard |

|---------------|--------------|-------------------|-----------------|

| FLASH_DATA[0] | PIN_AB18     | FLASH Data[0]     | 3.3V            |

| FLASH_DATA[1] | PIN_AA19     | FLASH Data[1]     | 3.3V            |

| FLASH_DATA[2] | PIN_AB19     | FLASH Data[2]     | 3.3V            |

| FLASH_DATA[3] | PIN_AA20     | FLASH Data[3]     | 3.3V            |

| FLASH_DCLK    | PIN_AB17     | FLASH Data Clock  | 3.3V            |

| FLASH_NCSO    | PIN_AB21     | FLASH Chip Enable | 3.3V            |

| FLASH_RESET_n | PIN_AB20     | FLASH Chip Reser  | 3.3V            |

#### 3.4.9 Ethernet

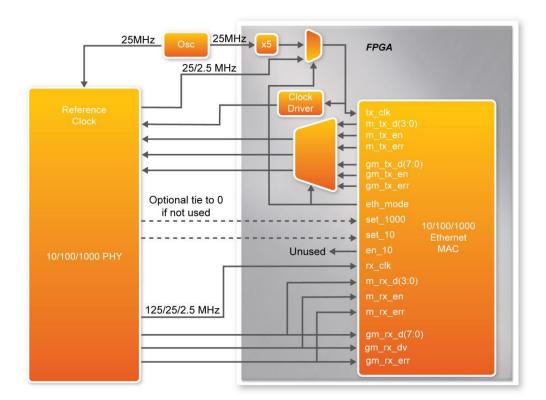

The board supports Gigabit Ethernet transfer by an external Marvell 88E1111 PHY chip. The 88E1111 chip with integrated 10/100/1000 Mbps Gigabit Ethernet transceiver support GMII/MII/RGMII/TBI MAC interfaces. **Figure 3-22** shows the connections between the MAX 10 FPGA, Ethernet PHY, and RJ-45 connector. The pin assignment associated to Gigabit Ethernet interface is listed in **Table 3-12**.

Figure 3-22 Connections between the MAX 10 FPGA and Gigabit Ethernet

**Table 3-12 Pin Assignment of Ethernet PHY**

|             |              | signment of Ethernet 1111              | T/O             |

|-------------|--------------|----------------------------------------|-----------------|

| Signal Name | FPGA Pin No. | Description                            | I/O<br>Standard |

|             |              |                                        |                 |

| NET_TX_EN   | PIN_C10      | GMII and MII transmit enable           | 2.5V            |

| NET_TX_ER   | PIN_C12      | GMII and MII transmit error            | 2.5V            |

| NET_TX_CLK  | PIN_E11      | MII transmit clock                     | 3.3V            |

| NET_TX_D[0] | PIN_A12      | MII transmit data[0]                   | 2.5V            |

| NET_TX_D[1] | PIN_B12      | MII transmit data[1]                   | 2.5V            |

| NET_TX_D[2] | PIN_A13      | MII transmit data[2]                   | 2.5V            |

| NET_TX_D[3] | PIN_A14      | MII transmit data[3]                   | 2.5V            |

| NET_RX_DV   | PIN_A8       | GMII and MII receive data valid        | 2.5V            |

| NET_RX_ER   | PIN_B8       | GMII and MII receive data valid        | 2.5V            |

| NET_RX_D[0] | PIN_A10      | GMII and MII receive data[0]           | 2.5V            |

| NET_RX_D[1] | PIN_B10      | GMII and MII receive data[1]           | 2.5V            |

| NET_RX_D[2] | PIN_A11      | GMII and MII receive data[2]           | 2.5V            |

| NET_RX_D[3] | PIN_B11      | GMII and MII receive data[3]           | 2.5V            |

| NET_RX_CLK  | PIN_J10      | GMII and MII receive clock             | 3.3V            |

| NET_RST_n   | PIN_C14      | Hardware Reset Signal                  | 2.5V            |

| NET_MDIO    | PIN_E12      | Management Data                        | 2.5V            |

| NET_MDC     | PIN_D12      | Management Data Clock Reference        | 2.5V            |

| NET_RX_COL  | PIN_C9       | GMII and MII collision                 | 2.5V            |

| NET_RX_CRS  | PIN_A9       | GMII and MII carrier sense             | 2.5V            |

| NET_GTX_CLK | PIN_C11      | GMII Transmit Clock                    | 2.5             |

| NET_LINK100 | PIN_A7       | Parallel LED output of 100BASE-TX link | 2.5V            |

| NET_INT_n   | PIN_C13      | Interrupt open drain output            | 2.5V            |

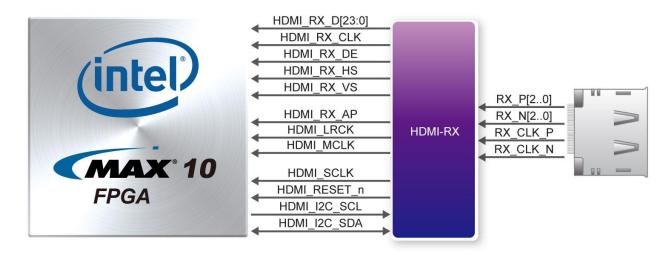

#### 3.4.10 HDMI RX

The development board provides High Performance HDMI Receiver via the Analog Devices ADV7611 which incorporates HDMI v1.4a features, including 3D video support, and 165MHz supports all video formats up to 1080p and UXGA. The ADV7611 is controlled via a serial I2C bus interface, which is connected to pins on the MAX 10 FPGA. A schematic diagram of the HDMI RX circuitry is shown in **Figure 3-23**. Detailed information on using the ADV7611 HDMI RX is available on the manufacturer's website, or under the Datasheets\HDMI folder on the Kit System CD.

**Table 3-13** lists the HDMI Interface pin assignments and signal names relative to the MAX 10 device.

Figure 3-23 Connection between the MAX 10 FPGA and HDMI Receiver

Table 3-13 Pin Assignment of HDMI RX

| Signal Name | FPGA Pin No. | Description             | I/O Standard |

|-------------|--------------|-------------------------|--------------|

| HDMI_RX_D0  | PIN_AA9      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D1  | PIN_AB9      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D2  | PIN_Y10      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D3  | PIN_AA10     | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D4  | PIN_AB10     | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D5  | PIN_Y11      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D6  | PIN_AA11     | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D7  | PIN_AB11     | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D8  | PIN_Y14      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D9  | PIN_AB15     | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D10 | PIN_AA15     | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D11 | PIN_W14      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D12 | PIN_V14      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D13 | PIN_V15      | Video Pixel Output Port | 3.3V         |

| HDMI_RX_D14 | PIN_U15      | Video Pixel Output Port | 3.3V         |

28

| HDMI_RX_D15     | PIN_AB14 | Video Pixel Output Port               | 3.3V |

|-----------------|----------|---------------------------------------|------|

| HDMI_RX_D16     | PIN_AA14 | Video Pixel Output Port               | 3.3V |

| HDMI_RX_D17     | PIN_AB13 | Video Pixel Output Port               | 3.3V |

| HDMI_RX_D18     | PIN_Y13  | Video Pixel Output Port               | 3.3V |

| HDMI_RX_D19     | PIN_AB12 | Video Pixel Output Port               | 3.3V |

| HDMI_RX_D20     | PIN_AA12 | Video Pixel Output Port               | 3.3V |

| HDMI_RX_D21     | PIN_W13  | Video Pixel Output Port               | 3.3V |

| HDMI_RX_D22     | PIN_W12  | Video Pixel Output Port               | 3.3V |

| HDMI_RX_D23     | PIN_V13  | Video Pixel Output Port               | 3.3V |

| HDMI_RX_CLK     | PIN_P11  | Line-Locked Output Clock              | 3.3V |

| HDMI_RX_DE      | PIN_W10  | Data Enable Signal for Digital Video. | 3.3V |

| HDMI_RX_HS      | PIN_V12  | Horizontal Synchronization            | 3.3V |

| HDMI_RX_VS      | PIN_W11  | Vertical Synchronization              | 3.3V |

| HDMI_RX_INT1    | PIN_P12  | Interrupt Signal                      | 3.3V |

| HDMI_I2C_SCL    | PIN_R13  | I2C Clock                             | 3.3V |

| HDMI_I2C_SDA    | PIN_P13  | I2C Data                              | 3.3V |

| HDMI_MCLK       | PIN_R12  | Audio Master Output Clock             | 3.3V |

| HDMI_LRCLK      | PIN_V11  | Audio Left/Right Clock                | 3.3V |

| HDMI_SCLK       | PIN_W8   | Audio Serial Output Clock             | 3.3V |

| HDMI_AP         | PIN_W9   | Audio Output Pin                      | 3.3V |

| HDMI_RX_RESET_n | PIN_AA13 | System Reset Input                    | 3.3V |

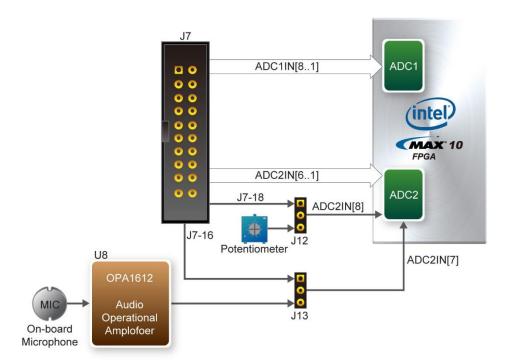

#### **3.4.11 2x10 ADC Header**

The board has a 2x10 ADC header with sixteen analog inputs connected to FPGA ADC1 and ADC2 respectively. The 1x3 header J12 is used to select pin 18 of 2x10 header J7 or potentiometer input to be connected to the channel 8 of FPGA ADC2. Short pin 1 and pin 2 of J12 to select potentiometer, short pin 3 and pin 4 to select pin 18 of 2x10 header J7. The 1x3 header J13 is used to select pin 16 of 2x10 header J7 or on-board microphone to be connected to the channel 7 of FPGA ADC2. Short pin 1 and pin 2 of J13 to select on-board microphone, short pin 3 and pin 4 to select pin 16 of 2x10 header J7. **Figure 3-24** shows the connection of 2x10 ADC header and MAX 10 FPGA.

Figure 3-24 Connections between 2x10 ADC Header, Potentiometer, On-board Microphone and MAX 10 FPGA

#### 3.4.12 Potentiometer

Short pin 1 and pin 2 of J12 will select potentiometer for providing adjustable voltage to the channel 8 of FPGA ADC2.

#### 3.4.13 On-board Microphone

The board provides an on-board microphone for audio applications. Short pin 1 and pin 2 of J13 to select on-board microphone to be connected to the channel 7 of FPGA ADC2. The output audio signal from on-board microphone will be pre-amplified by audio operational amplifier OPA1612, then fed into the FPGA ADC. **Figure 3-24** shows the connection of on-board microphone and MAX 10 FPGA.

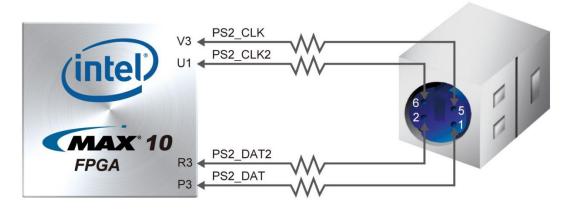

#### 3.4.14 PS/2 Serial Port

The MAX 10 Plus comes with a standard PS/2 interface and a connector for a PS/2 keyboard or mouse. **Figure 3-25** shows the connection of PS/2 circuit to the FPGA. Users can use the PS/2 keyboard and mouse on the MAX 10 Plus simultaneously by a PS/2 Y-Cable, as shown in **Figure 3-26**. Instructions on how to use PS/2 mouse and/or keyboard can be found on various educational websites. The pin assignment associated to this interface is shown in **Table 3-14**.

Note: If users connect only one PS/2 equipment, the PS/2 signals connected to the FPGA I/O should be "PS2 CLK" and "PS2 DAT".

Figure 3-25 Connections between the MAX 10 FPGA and PS/2

Figure 3-26 Y-Cable for Using Keyboard and Mouse Simultaneously

Table 3-14 Pin Assignment of PS/2

| Signal Name | FPGA Pin No. | Description                                  | I/O<br>Standard |

|-------------|--------------|----------------------------------------------|-----------------|

| PS2_CLK     | PIN_V3       | PS/2 Clock                                   | 3.3V            |

| PS2_DAT     | PIN_P3       | PS/2 Data                                    | 3.3V            |

| PS2_CLK2    | PIN_U1       | PS/2 Clock (reserved for second PS/2 device) | 3.3V            |

| PS2_DAT2    | PIN_R3       | PS/2 Data (reserved for second PS/2 device)  | 3.3V            |

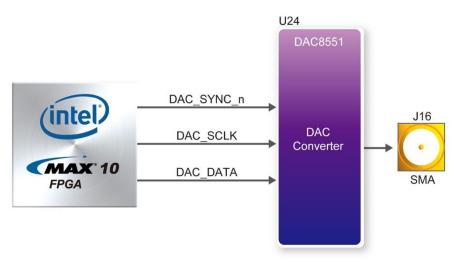

#### 3.4.15 Digital-to-Analog Converter (DAC)

The board provides a Texas Instruments DAC8551 16-bit digital-to-analog converter (DAC). It is a small, low power, voltage output DAC. The DAC8551 used a versatile 3-wire serial interface that operates at clock rates to 30MHz and is compatible with standard SPI, QSPI, Microwire and DSP interfaces. The analog voltage output of DAC8551 is connected to a SMA connector. **Figure 3-27** shows the connection between DAC and MAX 10 FPGA. The pin assignment associated to this DAC is shown in **Table 3-15**.

Figure 3-27 Connection between DAC and MAX 10 FPGA

Table 3-15 Pin Assignment of DAC

| Signal Name | FPGA Pin No. | Description                      | I/O Standard |

|-------------|--------------|----------------------------------|--------------|

| DAC_SYNC_n  | PIN_B2       | Frame Sync Signal for Input Data | 3.3V         |

| DAC_SCLK    | PIN_B1       | Serial Clock Input               | 3.3V         |

| DAC_DATA    | PIN_A2       | Serial Data Input                | 3.3V         |

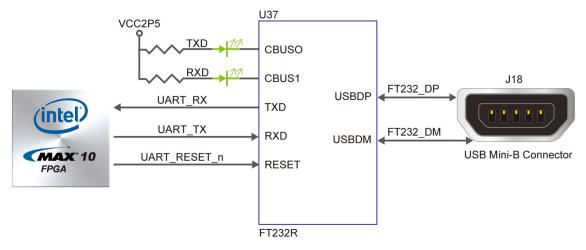

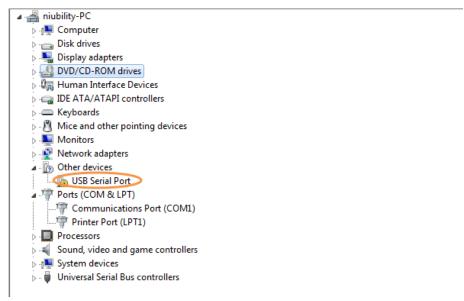

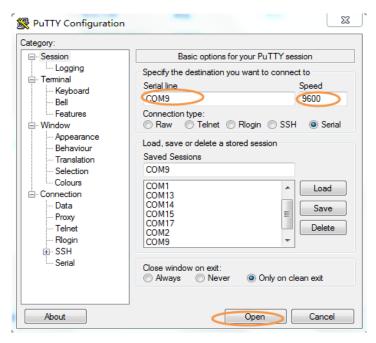

#### **3.4.16 UART to USB**

The board has one UART interface connected for communication with the MAX 10 FPGA. This interface doesn't support HW flow control signals. The physical interface is implemented by UART-USB onboard bridge from a FT232R chip to the host with an USB Mini-B connector. More information about the chip is available on the manufacturer's website, or in the directory \Datasheets\UART TO USB of MAX 10 Plus system CD. **Figure 3-28** shows the connections between the MAX 10 FPGA, FT232R chip, and the USB Mini-B connector. **Table 3-16** lists the pin assignment of UART interface connected to the MAX 10 FPGA.

Figure 3-28 Connections between the HPS and FT232R Chip

**Table 3-16 Pin Assignment of UART Interface**

| Signal Name  | FPGA Pin No. | Description                  | I/O Standard |

|--------------|--------------|------------------------------|--------------|

| UART_RX      | PIN_E16      | FPGA UART Receiver           | 2.5V         |

| UART_TX      | PIN_E15      | FPGA UART Transmitter        | 2.5V         |

| UART_RESET_n | PIN_D15      | Reset Signal for UART Device | 2.5V         |

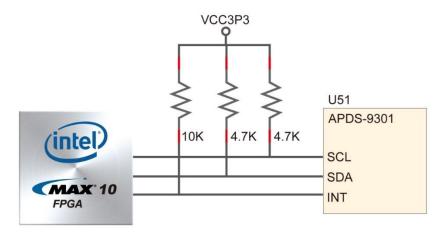

#### 3.4.17 Ambient Light Sensor

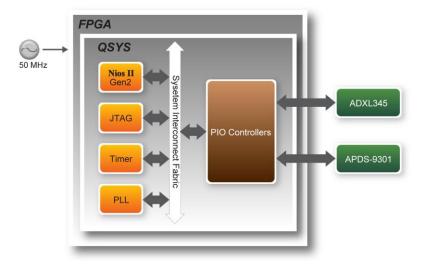

The MAX 10 Plus has a Light-to-Digital Ambient Light Sensor (APDS-9301) that converts light intensity to digital signal output capable of I2C interface. with I2C digital interface and programmable-event interrupt output. The digital output of APDS-9301 will be input to the MAX 10 FPGA where illuminance I lux is derived using an empirical formula to approximate the human-eye response. **Figure 3-29** shows the connection of APDS-9301 to the MAX 10 FPGA. **Table 3-17** lists the Ambient Light Sensor pin assignments.

Figure 3-29 The Connections between the MAX 10 FPGA and Ambient Light Sensor

**Table 3-17 Pin Assignment of Ambient Light Sensor**

| Signal Name | FPGA Pin No. | Description                  | I/O Standard |

|-------------|--------------|------------------------------|--------------|

| LSENSOR_SCL | PIN_M1       | I2C Serial Clock             | 3.3V         |

| LSENSOR_SDA | PIN_T3       | I2C Serial Data              | 3.3V         |

| LSENSOR_INT | PIN_M2       | Interrupt signal from Sensor | 3.3V         |

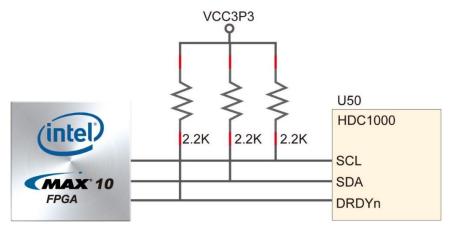

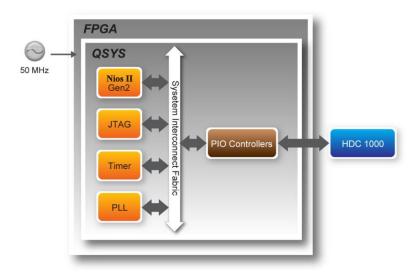

#### 3.4.18 Humidity and Temperature Sensor

The MAX 10 Plus has a humidity and temperature sensor (HDC1000) that provides excellent measurement accuracy at very low power. The HDC1000 sensor is placed at board edge and away from the heat source of MAX 10 Plus so that user can make ambient temperature measurement without heat interference from the heat source of MAX 10 Plus. **Figure 3-30** shows the connection of humidity and temperature sensor to MAX 10 FPGA. **Table 3-18** lists the humidity and temperature sensor pin assignments.

Figure 3-30 The Connections between the MAX 10 FPGA and Humidity and Temperature Sensor

Table 3-18 Pin Assignment of Humidity and Temperature Sensor

| Signal Name     | FPGA Pin No. | Description                          | I/O Standard |

|-----------------|--------------|--------------------------------------|--------------|

| RH_TEMP_I2C_SCL | PIN_Y18      | I2C Clock for HDC1000 Sensor         | 3.3V         |

| RH_TEMP_I2C_SDA | PIN_W18      | I2C Data for HDC1000 Sensor          | 3.3V         |

| RH_TEMP_DRDY_n  | PIN_Y19      | Data ready input from HDC1000 Sensor | 3.3V         |

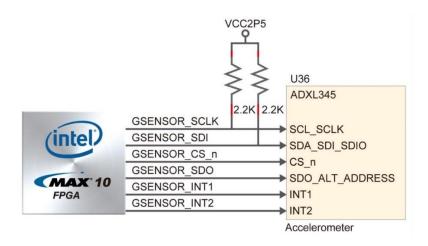

#### 3.4.19 Accelerometer Sensor

The board comes with a digital accelerometer sensor module (ADXL345), commonly known as G-sensor. This G-sensor is a small, thin, ultralow power assumption 3-axis accelerometer with high-resolution measurement. Digitalized output is formatted as 16-bit in two's complement and can be accessed through I2C interface. The I2C address of accelerometer is 0xA6/0xA7. More information about this chip can be found in its datasheet, which is available on manufacturer's website or in the directory \Datasheet folder of MAX 10 Plus system CD. **Figure 3-31** shows the connections between the MAX 10 FPGA and accelerometer. **Table 3-19** lists the pin assignment of accelerometer to the MAX 10 FPGA.

Figure 3-31 The Connections between the MAX 10 FPGA and Accelerometer Sensor

**Table 3-19 Pin Assignment of Accelerometer Sensor**

| Signal Name  | FPGA Pin No. | Description                                                                                                            | I/O<br>Standard |

|--------------|--------------|------------------------------------------------------------------------------------------------------------------------|-----------------|

| GSENSOR_SDI  | PIN_C15      | I2C serial data/SPI serial data input/3-wire interface serial dta output                                               | 2.5V            |

| GSENSOR_SDO  | PIN_B16      | SPI serial data output/I2C less significant bit of the device address                                                  | 2.5V            |

| GSENSOR_CS_n | PIN_C16      | SPI enable, I2C/SPI mode selection: 1: SPI idle mode/I2C communication enabled, 0: SPI communication mode/I2C disabled |                 |

| GSENSOR_SCLK | PIN_A15      | I2C serial clock/SPI serial port clock                                                                                 | 2.5V            |

| GSENSOR_INT1 | PIN_B15      | Interrupt pin 1                                                                                                        | 2.5V            |

| GSENSOR_INT2 | PIN_D17      | Interrupt pin 2                                                                                                        | 2.5V            |

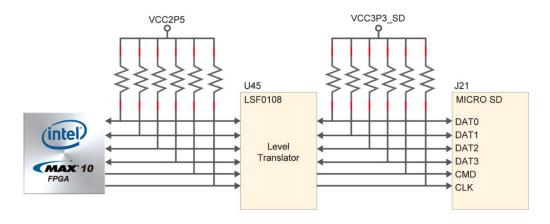

#### 3.4.20 Micro SD Card Socket

The board supports Micro SD card interface with x4 data lines. It serves not only an external storage for the HPS, but also an alternative boot option for MAX 10 Plus. **Figure 3-32** shows signals connected between the HPS and Micro SD card socket.

**Table 3-20** lists the pin assignment of Micro SD card socket to the MAX 10 FPGA.

Figure 3-32 Connections between the MAX 10 FPGA and SD Card Socket

**Table 3-20 Pin Assignment of Micro SD Card Socket**

| Signal Name | FPGA Pin No. | Description     | I/O Standard |

|-------------|--------------|-----------------|--------------|

| SD_CLK      | PIN_A16      | SD Clock        | 2.5V         |

| SD_CMD      | PIN_C18      | SD Command Line | 2.5V         |

| SD_DATA[0]  | PIN_A17      | SD Data[0]      | 2.5V         |

| SD_DATA[1]  | PIN_A18      | SD Data[1]      | 2.5V         |

| SD_DATA[2]  | PIN_B17      | SD Data[2]      | 2.5V         |

| SD_DATA[3]  | PIN_C17      | SD Data[3]      | 2.5V         |

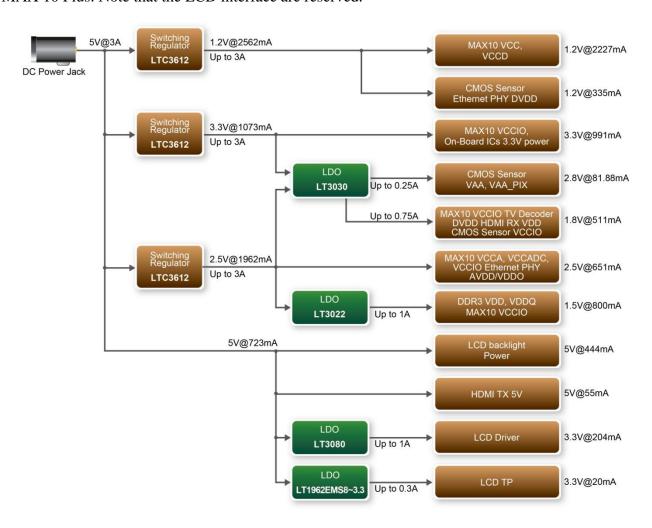

#### 3.4.21 Power Distribution System

The MAX 10 Plus is powered by Linear Technology's power solution which provides

high-efficiency power management for FPGAs and SoCs. **Figure 3-33** shows the power tree of MAX 10 Plus. Note that the LCD interface are reserved.

Figure 3-33 Power Tree of MAX 10 Plus

# **Chapter 4**

# The MAX 10 Plus System Builder

This chapter introduces the MAX 10 Plus System Builder to help users get started in creating their own projects in literally minutes. It also describes the design flow and includes an example for users to get familiar with the tool.

### 4.1 Introduction

The MAX 10 Plus System Builder is a Windows-based utility. It is created to help users build a top project for MAX 10 Plus within minutes. The generated Quartus II project files include:

- Quartus II project file (.qpf)

- Quartus II setting file (.qsf)

- Top-level design file (.v)

- Synopsis design constraints file (.sdc)

- Pin assignment document (.htm)

The above files generated by the MAX 10 Plus System Builder can also prevent situations that are prone to compilation error when users manually edit the top-level design file or place pin assignment. The common mistakes that users encounter are:

- Board is damaged due to incorrect bank voltage setting or pin assignment.

- Board is malfunctioned because of wrong device chosen, declaration of pin location, or the direction is incorrect/forgotten.

- Performance degradation due to improper pin assignment.

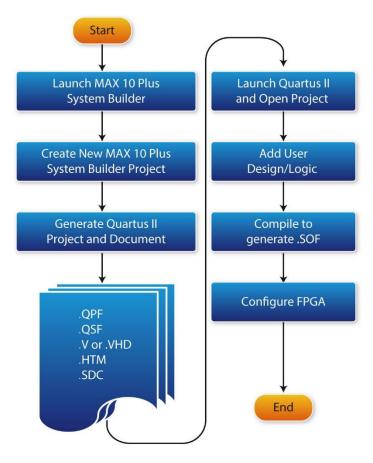

# 4.2 General Design Flow

The design flow of building a Quartus II project for MAX 10 Plus using the MAX 10 Plus System Builder is illustrated in **Figure 4-1**. It gives users an overview about the steps, starting from launching the System Builder to configuring the FPGA. The left-hand side of the chart can be done within minutes. After users enter the design requirements, the MAX 10 Plus System Builder will generate Quartus II project files, Quartus II setting file, top-level design file, Synopsis design constraint file, and the pin assignment document.

The top-level design file contains a top-level Verilog HDL wrapper for users to add their own design/logic. The Quartus II setting file contains information such as FPGA device type, top-level pin assignment, and the I/O standard for each user-defined I/O pin. These files can be modified according to the project requirements. After the compilation is successful, users can download the .sof file to the development board via JTAG interface using the Quartus II programmer.

37

Manual

Figure 4-1 Design Flow of Building a Project from the beginning to the end

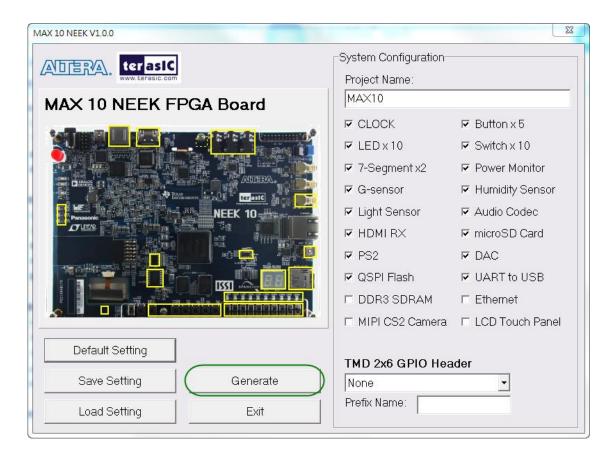

# 4.3 Using MAX 10 Plus System Builder

This section provides the procedures in details on how to use the MAX 10 Plus System Builder.

# ■ Install and Launch the MAX 10 Plus System Builder

The MAX 10 Plus System Builder is located in the directory Tools\SystemBuilder of the MAX 10 Plus System CD. Users can copy the entire folder to a host PC without installing the utility. After the execution of the MAX 10 Plus SystemBuilder.exe on the host PC, a window will pop up, as shown in **Figure 4-2.**

Figure 4-2 The GUI of MAX 10 Plus System Builder

# **■** Enter Project Name

The project name entered in the circled area, as shown in **Figure 4-3**, will be assigned automatically as the name of the top-level design entity.

Figure 4-3 Enter the Project Name

# ■ System Configuration

Users are given the flexibility in the System Configuration to include one or more onboard peripherals in the project, as shown in **Figure 4-4**. If a component is enabled, the MAX 10 Plus System Builder will automatically generate its associated pin assignment, including the pin name, pin location, pin direction, and I/O standard.

Note: The MIPI CS2 Camera and LCD Touch Panel interfaces are reserved, users can choose to buy MAX 10 NEEK instead if needed these two interfaces.

Figure 4-4 List of onboard Peripherals in System Configuration

# **■** Project Settings

The MAX 10 Plus System Builder also provides the option to load a setting or save the current board configuration in .cfg file, as shown in **Figure 4-5.**

**Figure 4-5 Manage Project Settings**

# ■ Project Generation

When users press the Generate button, as shown in **Figure 4-6**, the MAX 10 Plus System Builder will generate the corresponding Quartus II files and documents, as listed in **Table 4-1**.

Figure 4-6 Generate Quartus Project

Table 4-1 Files Generated by the MAX 10 Plus System Builder

| No. | Filename                        | Description                                     |

|-----|---------------------------------|-------------------------------------------------|

| 1   | <project name="">.v</project>   | Top-level Verilog HDL file for Quartus II       |

| 2   | <project name="">.qpf</project> | Quartus II project file                         |

| 3   | <project name="">.qsf</project> | Quartus II setting file                         |

| 4   | <project name="">.sdc</project> | Synopsis design constraints file for Quartus II |

| 5   | <project name="">.htm</project> | Pin assignment document                         |

Users can add custom logic into the project and compile the project in Quartus II to generate the SRAM Object File (.sof).

# Chapter 5 RTL Example Codes

This chapter provides examples of advanced designs implemented by RTL on the MAX 10 Plus board. These reference designs cover the features of peripherals connected to the FPGA, such as PS/2 mouse, ADC/DAC application. All the associated files can be found in the directory \Demonstrations of System CD. Note: The output files generated after compilation in Quartus II e.g. .sof and .pof files, are saved in the folder "output\_files" under the directory of demo project.

### 5.1 PS/2 Mouse Demonstration

We offer this simple PS/2 controller coded in Verilog HDL to demonstrate bidirectional communication between PS/2 controller and the device, the PS/2 mouse. You can treat it as a how-to basis and develop your own controller that could accomplish more sophisticated instructions, like setting the sampling rate or resolution, which need to transfer two data bytes.

More information about the PS/2 protocol can be found on various websites.

### **■** Introduction

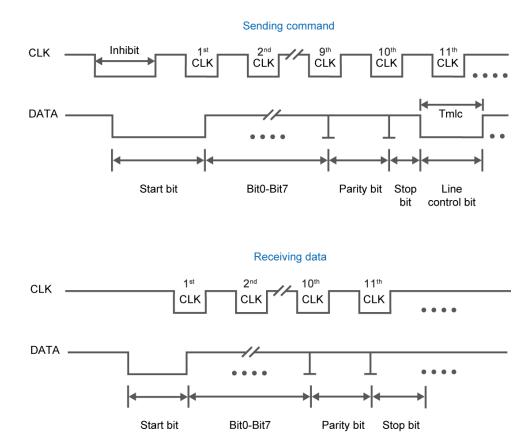

PS/2 protocol uses two wires for bi-directional communication. One is the clock line and the other one is the data line. The PS/2 controller always has total control over the transmission line, but it is the PS/2 device which generates the clock signal during data transmission.

#### ■ Data Transmission from Device to the Controller

After the PS/2 mouse receives an enabling signal at stream mode, it will start sending out displacement data, which consists of 33bits. The frame data is cut into three sections and each of them contains a start bit (always zero), eight data bits (with LSB first), one parity check bit (odd check), and one stop bit (always one).

The PS/2 controller samples the data line at the falling edge of the PS/2 clock signal. This is implemented by a shift register, which consists of 33bits, but please be cautious with the clock domain crossing problem.

### ■ Data Transmission from the Controller to Device

When the PS/2 controller wants to transmit data to device, it first pulls the clock line low for more than one clock cycle to inhibit the current transmission process or to indicate the start of a new transmission process, which is usually called as inhibit state. It then pulls low the data line before releasing the clock line. This is called the request state. The rising edge on the clock line formed by the release action can also be used to indicate the sample time point as for a start bit. The device will detect this succession and generates a clock sequence in less than 10ms time. The transmit data consists of 12bits, one start bit (as explained before), eight data bits, one parity check bit (odd check), one stop bit (always one), and one acknowledge bit (always zero).

After sending out the parity check bit, the controller should release the data line, and the device will detect any state change on the data line in the next clock cycle. If there's no change on the data line for one clock cycle, the device will pull low the data line again as an acknowledgement which means that the data is correctly received.

After the power-on cycle of the PS/2 mouse, it enters into stream mode automatically and disable data transmit unless an enabling instruction is received. **Figure 5-1** shows the waveform while communication happening on two lines.

Figure 5-1 Waveform of Clock and Data Signals during Data Transmission

# Design Tools

• Quartus II v15.0 64-bit

### **■ Demonstration Source Code**

Project directory: ps2\_mouseBitstream used: ps2\_mouse.sof

### **■ Demonstration Batch File**

• Demo batch file folder: Demonstrations\ps2\_mouse\demo\_batch

• Batch file: ps2\_mouse.bat

• FPGA configuration file: ps2\_mouse.sof

### **■** Demonstration Setup

- Please make sure Quartus II and USB-Blaster II driver are installed on the host PC.

- Connect the USB cable from the USB-Blaster II port (J8) on the MAX 10 Plus board to the host PC and power on the MAX 10 Plus board.

- Execute the demo batch file "ps2\_mouse.bat" under the folder Demonstrations\ps2\_mouse\demo\_batch\.

- Plug in the PS/2 mouse.

- Press KEY0 to enable data transfer.

- Press KEY1 to clear the display data cache.

- The 7-segment display shows X displacement when SW0 is low, and Y displacement when SW0 is high. The display should change when the PS/2 mouse moves.

- The LEDR [2:0] will blink according to **Table 5-1** when the left-button, right-button, and/or middle-button is pressed.

Table 5-1 Description of 7-segment Display and LED Indicators

| <b>Indicator Name</b> | Description                   |

|-----------------------|-------------------------------|

| LEDR0                 | Left button press indicator   |

| LEDR1                 | Right button press indicator  |

| LEDR2                 | Middle button press indicator |

| HEX0                  | Low byte of X/Y displacement  |

| HEX1                  | High byte of X/Y displacement |

### **5.2 ADC Potentiometer**

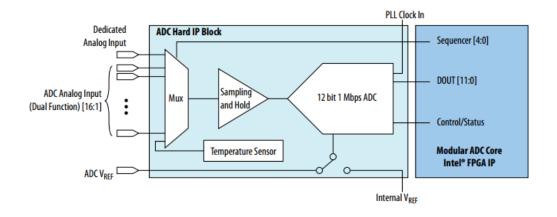

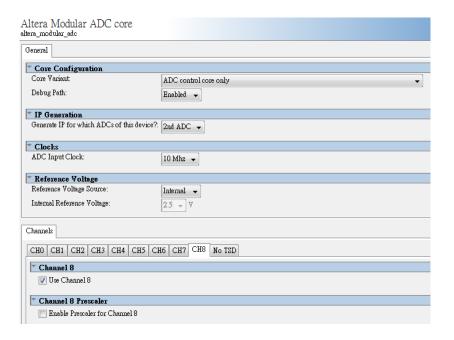

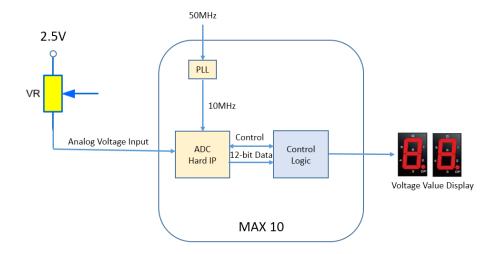

Nowadays voltage and current monitors play a significant role in high-reliability system. Most of applications can be implemented by an Analog-to-Digital Converter (ADC). MAX 10 Plus board provides a potentiometer demonstration using the ADC in MAX10. This ADC solution consists of hard IP blocks in MAX 10 device and soft logic through Intel Modular ADC IP core. **Figure 5-2** shows the block diagram of ADC hard IP block in MAX10 device.

Figure 5-2 Block Diagram of ADC Hard IP Block

This demo uses 2nd ADC of MAX10 on channel 8. The ADC settings are shown in **Figure 5-3**.

Figure 5-3 Settings of ADC Hard IP

The MAX 10 Plus board has a Variable Resistor (VR) onboard, which acts as a potentiometer in this demonstration. **Figure 5-4** shows the block diagram of Power Monitor demonstration. The ADC reference clock running at 10MHz is generated by PLL. It feeds into the ADC Hard IP in MAX10 device. The analog voltage input comes from the VR controls the voltage level. The control logic within the ADC Hard IP reads the digitized voltage data. It then converts the data and displays the level value on two 7-segments. Since none of the dot points of two 7-segments is connected to the MAX 10, so HEX1 and HEX0 shows the decimal point and the first digit after the decimal point respectively.

Figure 5-4 Block Diagram of ADC Potentiometer

# **■** Design Tools

• Quartus II v15.0 64-bit

#### Demonstration Source Code

Project directory: Demonstrations\adc\_potentionmeter

• Bitstream used: adc\_potentionmeter.sof

### **■** Demonstration Batch File

Demo batch file folder: Demonstrations\adc\_potentionmeter \demo\_batch

• Batch file: test.bat

• FPGA configuration file: adc\_potentionmeter.sof

# **■** Demonstration Setup

- Please make sure Quartus II and USB-Blaster II driver are installed on the host PC.

- Connect the USB cable from the USB-Blaster II port (J8) on the MAX 10 Plus board to the host PC.

- Power on the MAX 10 Plus board.

- Execute the demo batch file "test.bat" under the folder Demonstrations\ adc\_potentionmeter \demo batch.

- Rotate the VR resistor POT1 with a screwdriver. HEX1 and HEX0 will display the voltage value.

### **5.3 DAC Demonstration**

This demonstration uses the 16-bit Digital to analog converter (DAC) built-in the MAX 10 device to generate square wave in 8 difference frequencies. The signal coming out of the SMA connector on MAX 10 Plus board is transmitted to the oscilloscope. The oscilloscope will display the square wave in different frequencies by switching SW [2:0] on the MAX 10 Plus board.

# **■** Function Block Diagram

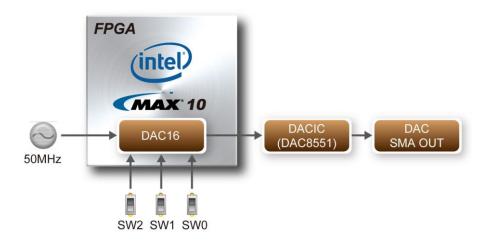

**Figure 5-5** is the function block diagram of this demonstration. The source data in parallel is converted to serial data by the DAC16 module. The DAC chip (DAC8551) then converts the serial data from digital to analog. The analog signal coming out of the DAC SMA connector is connected to the oscilloscope and shown in square wave. Users can switch the SW0~2 to change the frequency of the square wave.

Figure 5-5 Block Diagram of the DAC Demo

# Design Tools

• Quartus II v15.0 64-bit

### **■ Demonstration Source Code**

Project directory: Demonstrations\ dac\_sma

• Bitstream used: dac\_sma.sof

### **■ Demonstration Batch File**

• Demo batch file folder: Demonstrations\ dac\_sma\demo\_batch

• Batch file: test.bat

• FPGA configuration file: dac\_sma.sof

# **■** Demonstration Setup

- Please make sure Quartus II and USB-Blaster II driver are installed on the host PC.

- Connect the USB cable from the USB-Blaster II port (J8) to the host PC.

- Plug in the 5V adapter to the MAX 10 Plus board and power it up.

- Execute the demo batch file "test.bat" from the directory \ dac\_sma\demo\_batch.

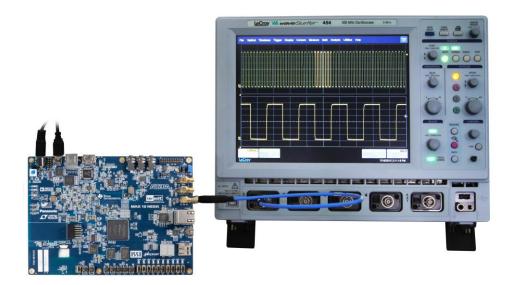

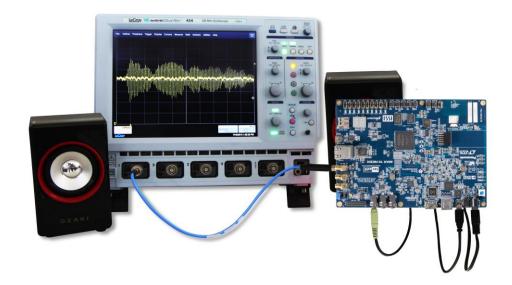

- Connect the probe of the oscilloscope to the DAC SMA OUT of the MAX 10 Plus board and adjust the display until the square wave is visible, as **Figure 5-6** and **Figure 5-7**.

- Switch SW [2:0] from 000 to 111 and the frequency of the square will be changing. The square-wave frequency is twice higher. When SW [2:0]=000, the square wave frequency is about 2.6KHz; When SW[2:0]=111, the frequency is about 112KHz.

Figure 5-6 Use the Oscilloscope to Observe the Square Wave

Figure 5-7 Probe DAC SMA OUT from the Oscilloscope

### 5.4 ADC/MIC/LED Demonstration

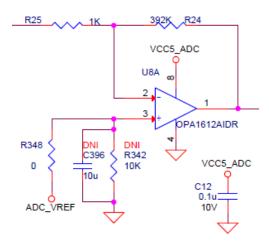

There is a high-sensitive microphone on the MAX 10 Plus board to receive the surrounding sound. After the sound is collected and amplified approximately 392 times, as shown in **Figure 5-8**, it is feed into the ADC of MAX 10 device. The digitized waveform will be displayed on the LED. Meanwhile the signal will be sent to the Line-out via audio codec and DAC SMA OUT connector. Both of which can be connected to an external speaker. The data will also be processed based on the volume to be displayed on the 10 LEDs onboard.

Figure 5-8 Onboard Microphone Amplifier with Gain (R24/R25) = 392

# **■** Function Block Diagram

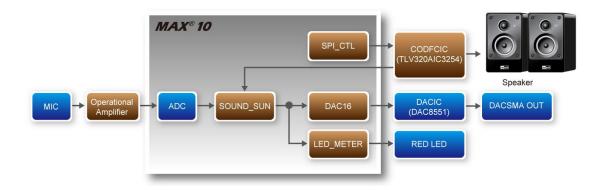

**Figure 5-9** is the function block diagram of this demonstration. The built-in MIC is amplified approximately 392 times via two operational amplifiers. The signal is then feed into the ADC of MAX 10 device for conversion. This demonstration uses the timing from the audio codec ((TLV320AIC3254) via I2S protocol to sync the entire system. The module SPI\_CTL sets the registers for the audio codec. The module SOUND\_SUM syncs the digitized signal coming out of the ADC of the MAX 10 device with the system and converts the data format i.e. adjust unsign 12-bit to sign 16-bit etc. The module DAC16 converts the digitized signal in parallel to 16-bit serial format for the DAC chip (DAC8551) to the Line-out via audio codec (TLV320AIC3254). The module LED\_METER displays the volume of the sound on the 8 LEDs onboard.

Figure 5-9 Block Diagram of the ADC/MIC/LED Demonstration

# **■** Design Tools

• Quartus II v15.0 64-bit

### **■** Demonstration Source Code

• Project directory: Demonstrations\ adc\_mic

• Bitstream used: adc\_mic.sof

### **■** Demonstration Batch File

• Demo batch file folder: Demonstrations\adc\_mic\demo\_batch

• Batch file: test.bat

• FPGA configuration file: adc\_mic.sof

# **■ Demonstration Setup**

- Please make sure Quartus II and USB-Blaster II driver are installed on the host PC.

- Connect the USB cable from the USB-Blaster II port (J8) to the host PC.

- Plug in the 5V adapter to the MAX 10 Plus board and power it up.

- Execute the demo batch file "test.bat" from the directory \adc\_mic \demo\_batch.

- The sound wave from the MIC can be observed on the LED and probed through DAC SMA OUT from the oscilloscope, or we can also connect external speaker to Line-out to hear the sound, as **Figure 5-10**. The volume of the sound from the MIC is displayed digitally on LEDR0~7, as **Figure 5-11**.

Figure 5-10 The Waveform of onboard MIC is Displayed on the Oscilloscope. Its Sound is Played out from the Speaker

Figure 5-11 LEDR0~7 Displays the Volume Level of onboard MIC

# Chapter 6

# NIOS Based Example Codes

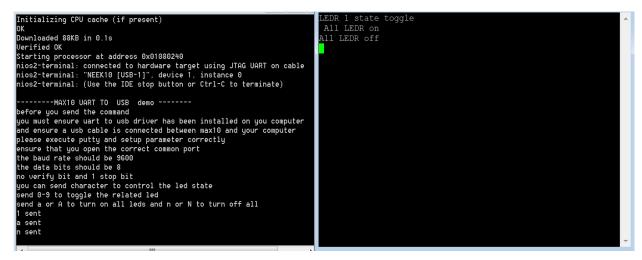

There are several NIOS based examples for users to get started and try them on the MAX 10 Plus board. All the NIOS based examples can be found in the system CD under the folder named Demonstrations. Users are free to use or modify these examples for personal use or education purpose.

Note: The output files generated after compilation in Quartus II e.g. .sof and .pof files, are saved in the folder "output\_files" under the directory of demo project. The workspace of Nios II Eclipse project is located in the folder "software" under the directory of demo project.

### **6.1 Power Monitor**

The power monitor demo shows how to measure the power consumed through the onboard power monitor chip LTC2990. There are three LTC2990 to monitor the following power rails:

- 3.3V VCCIO

- 2.5V Core

- 2.5V VCCIO

- 1.5V VCCIO

- 1.2V VCC

The power monitor chip LTC2990 communicates with the FPGA via I2C protocol. The I2C OpenCore IP is used in this demonstration for the MAX 10 device to communicate with the three LTC2990, which have different I2C slave address 98h, 9Ah, and 9Ch.

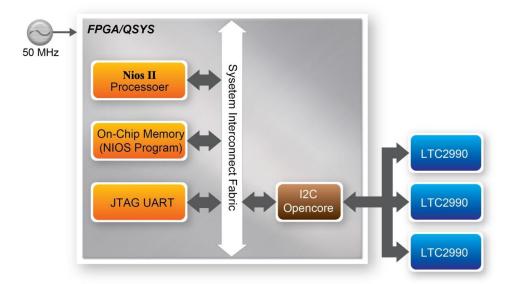

### **■** Block Diagram

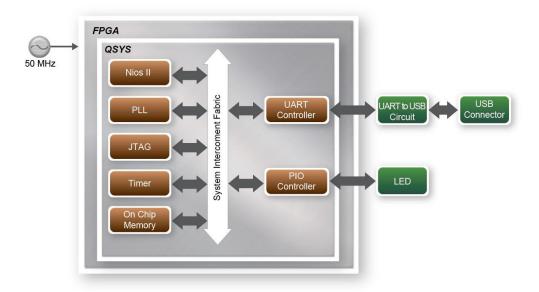

**Figure 6-1** shows the system block diagram of this demonstration. The NIOS program is stored in the onchip memory and the Nios II processor is running at 50MHz. The I2C library is located in the files named I2C\_core.cpp and I2C\_core.h. The I2C OpenCore IP is located in the folder "ip/i2c\_opencores" under the project directory.

Figure 6-1 Block Diagram of Power Monitor Demonstration

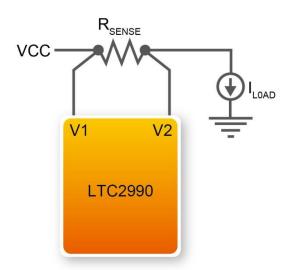

**Figure 6-2** illustrates the idea of how to measure the current for each power rail. A current sense resistor **R**<sub>SENSE</sub> is added to the path of each power rail. LTC2990 measures the voltage difference (V1-V2) and calculate the current based on the formula below:

Current =  $(V1-V2) / \mathbf{R}_{SENSE}$

The power consumption can be calculated by the following formula:

Power Consumption = VCC x Current = VCC x (V1-V2) /  $\mathbf{R}_{SENSE}$

Figure 6-2 Schematic of Current Sense

**Figure 6-3** shows the register content of LTC2990. The voltage difference (V1-V2) measured are written into two registers, MSB (register 06h) and LSB (register 07h). The most significant bit (7<sup>th</sup> bit) of MSB register is the data\_valid bit, which indicates whether the current register content has been accessed since the result was last written to the register. This bit will be "set" i.e. 1 when the register content is renewed and "cleared" i.e. 0 when the register content is accessed. Bit 6 of the

MSB register is the sign bit, Bit 5 through 0 represent the result of bits D[13:8] in two's complement conversion. The LSB register holds the conversion bits D[7:0]. The following equations are used to convert the register values to get the differential voltage:

$$V_{DIFFERENTIAL} = D[14:0] \cdot 19.42 \mu V$$

, if Sign = 0  $V_{DIFFERENTIAL} = (\overline{D[14:0]} + 1) \cdot -19.42 \mu V$ , if Sign = 1

| REGISTER ADDRESS*†        | REGISTER NAME          | READ/WRITE | DESCRIPTION                                  |

|---------------------------|------------------------|------------|----------------------------------------------|

| 00h STATUS                |                        | R          | Indicates BUSY State, Conversion Status      |

| 01h                       | CONTROL                | R/W        | Controls Mode, Single/Repeat, Celsius/Kelvin |

| 02h                       | TRIGGER**              | R/W        | Triggers an Conversion                       |

| 03h                       | N/A                    |            | Unused Address                               |

| 04h                       | T <sub>INT</sub> (MSB) | R          | Internal Temperature MSB                     |

| 05h                       | T <sub>INT</sub> (LSB) | R          | Internal Temperature LSB                     |

| 06h                       | V1 (MSB)               | R          | V1, V1 – V2 or T <sub>R1</sub> MSB           |

| 07h                       | V1 (LSB)               | R          | V1, V1 – V2 or T <sub>R1</sub> LSB           |

| 08h                       | V2 (MSB)               | R          | V2, V1 – V2 or T <sub>R1</sub> MSB           |

| 09h                       | V2 (LSB)               | R          | V2, V1 – V2 or T <sub>R1</sub> LSB           |

| 0Ah                       | V3 (MSB)               | R          | V3, V3 – V4 or T <sub>R2</sub> MSB           |

| 0Bh                       | V3 (LSB)               | R          | V3, V3 – V4 or T <sub>R2</sub> LSB           |

| 0Ch                       | V4 (MSB)               | R          | V4, V3 – V4 or T <sub>R2</sub> MSB           |

| 0Dh                       | V4 (LSB)               | R          | V4, V3 – V4 or T <sub>R2</sub> LSB           |

| 0Eh                       | V <sub>CC</sub> (MSB)  | R          | V <sub>CC</sub> MSB                          |

| 0Fh V <sub>CC</sub> (LSB) |                        | R          | V <sub>CC</sub> LSB                          |

Figure 6-3 Register of LTC2990

**Figure 6-4** shows the control register of LTC2990. The control register must be configured properly to measure the voltage difference (V1-V2). Bits b[2:0] should be set to '110' for measuring voltage difference (V1-V2) and (V3-V4). Bits [4:3] should be set to 00 for all measurements.

| BIT    | NAME               |   |    | OPERATION                                                  |

|--------|--------------------|---|----|------------------------------------------------------------|

| b7     | Temperature Format |   |    | Temperature Reported In; Celsius = 0 (Default), Kelvin = 1 |

| b6     | Repeat/Single      |   |    | Repeated Acquisition = 0 (Default), Single Acquisition = 1 |

| b5     | Reserved           |   |    | Reserved                                                   |

| b[4:3] | Mode [4:3]         |   |    | Mode Description                                           |

|        | 0                  |   | 0  | Internal Temperature Only (Default)                        |

|        | 0                  |   | 1  | T <sub>R1</sub> , V1 or V1 – V2 Only per Mode [2:0]        |

|        | 1                  |   | 0  | T <sub>R2</sub> , V3 or V3 – V4 Only per Mode [2:0]        |

|        | 1                  |   | 1  | All Measurements per Mode [2:0]                            |

| b[2:0] | Mode [2:0]         |   |    | Mode Description                                           |

|        | 0                  | 0 | 0  | V1, V2, T <sub>R2</sub> (Default)                          |

|        | 0                  | 0 | 1  | V1 – V2, T <sub>R2</sub>                                   |

|        | 0                  | 1 | 0  | V1 – V2, V3, V4                                            |

|        | 0                  | 1 | 1  | T <sub>R1</sub> , V3, V4                                   |

|        | 1                  | 0 | 0  | T <sub>R1</sub> , V3 – V4                                  |

|        | 1                  | 0 | 1  | T <sub>R1</sub> , T <sub>R2</sub>                          |

|        | 1                  | 1 | 0) | V1 - V2, V3 - V4                                           |

|        | 1                  | 1 | 1  | V1, V2, V3, V4                                             |

Figure 6-4 Control Register of LTC2990

**Figure 6-5** shows the status register of LTC2990. Bit b2 should be checked before reading the voltage difference registers to make sure the measurement is finished and register values is the latest for reading.

| BIT | NAME                                | OPERATION                                                                               |

|-----|-------------------------------------|-----------------------------------------------------------------------------------------|

| b7  | 0                                   | Always Zero                                                                             |

| b6  | V <sub>CC</sub> Ready               | 1 = V <sub>CC</sub> Register Contains New Data, 0 = V <sub>CC</sub> Register Read       |

| b5  | V4 Ready                            | 1 = V4 Register Contains New Data, 0 = V4 Register Read                                 |

| b4  | V3, T <sub>R2</sub> , V3 – V4 Ready | 1 = V3 Register Contains New Data, 0 = V3 Register Data Old                             |

| b3  | V2 Ready                            | 1 = V2 Register Contains New Data, 0 = V2 Register Data Old                             |

| b2  | V1, T <sub>R1</sub> V1 – V2 Ready   | 1 = V1 Register Contains New Data, 0 = V1 Register Data Old                             |

| b1  | T <sub>INT</sub> Ready              | 1 = T <sub>INT</sub> Register Contains New Data, 0 = T <sub>INT</sub> Register Data Old |

| b0  | Busy*                               | 1= Conversion In Process, 0 = Acquisition Cycle Complete                                |

Figure 6-5 Status Register of LTC2990

# Design Tools

- Quartus II v15.0 64-bit

- Nios II Eclipse 15.0

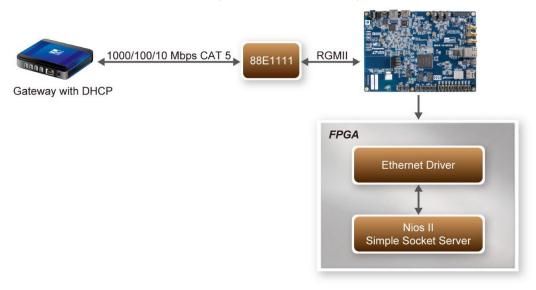

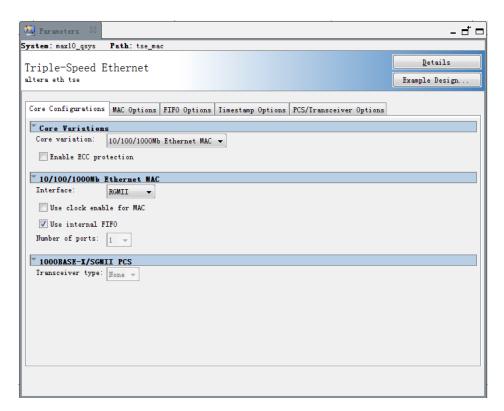

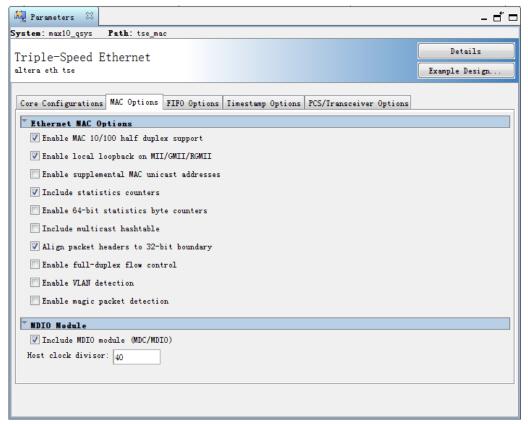

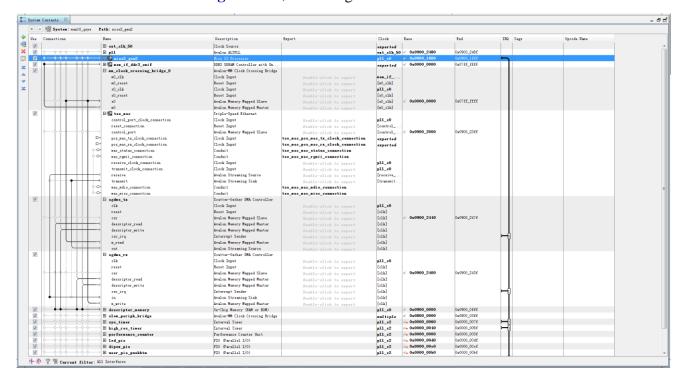

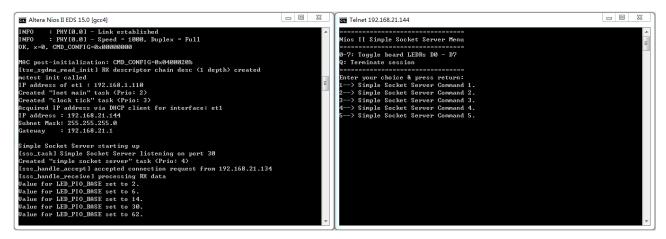

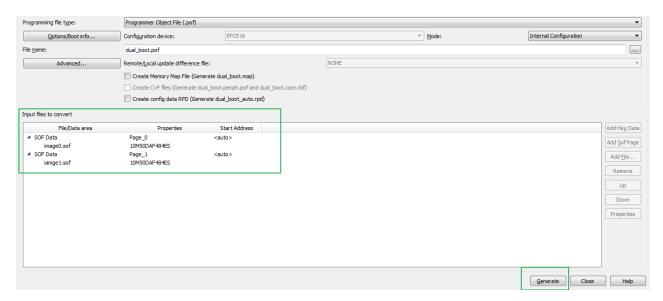

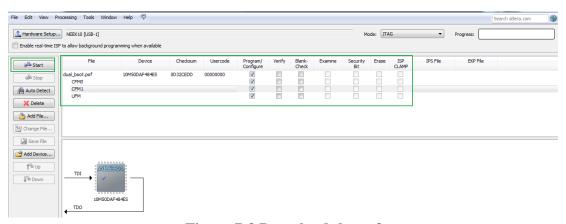

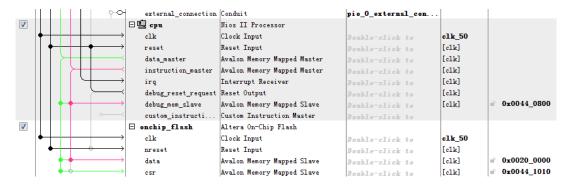

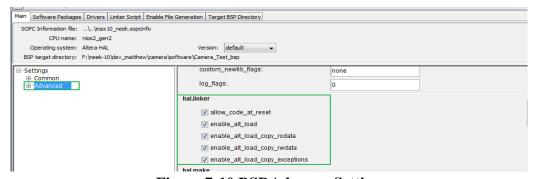

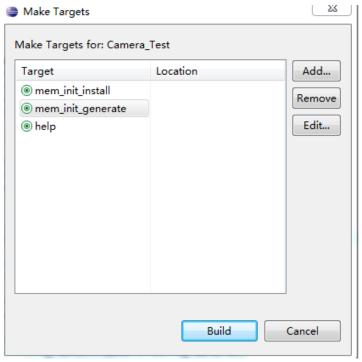

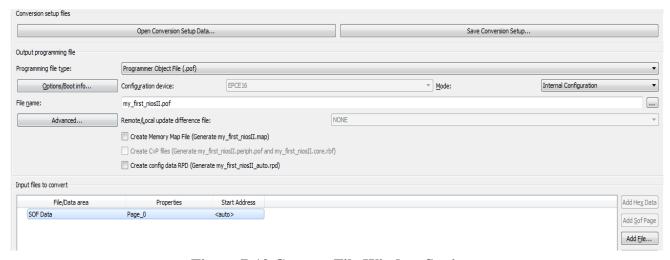

### **■** Demonstration Source Code