ADS8555

SBAS531D - DECEMBER 2010 - REVISED FEBRUARY 2016

# **ADS8555**

# 16-Bit, Six-Channel, Simultaneous Sampling Analog-to-Digital Converter

#### **Features**

- Six SAR ADCs Grouped in Three Pairs

- Maximum Data Rate Per Channel With Internal Clock and Reference: 630 kSPS (Parallel) or 450 kSPS (Serial)

- Maximum Data Rate Per Channel With External Clock and Reference: 800 kSPS (Parallel) or 500 kSPS (Serial)

- Pin-Selectable or Programmable Input Voltage Ranges: Up to ±12 V

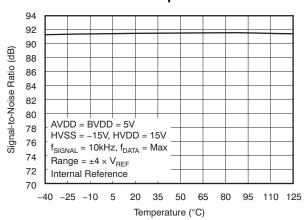

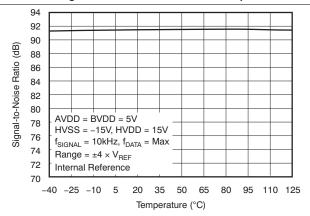

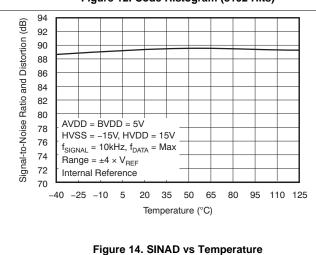

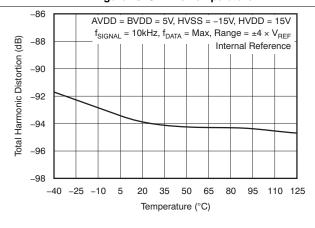

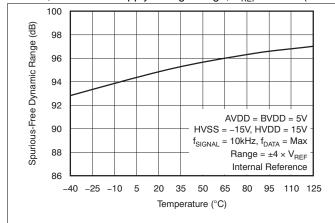

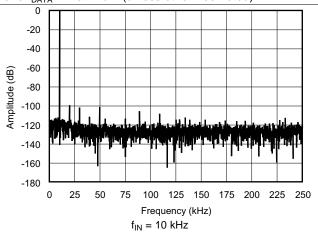

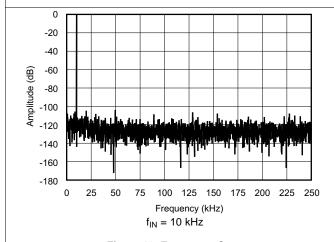

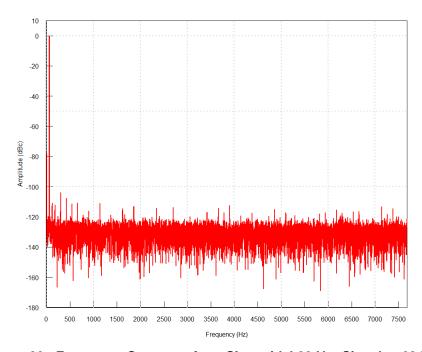

- **Excellent AC Performance:** 91.5-dB SNR, -94-dB THD

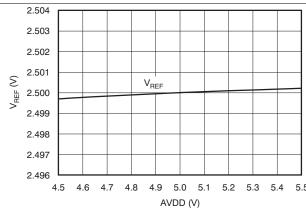

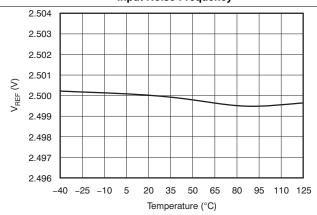

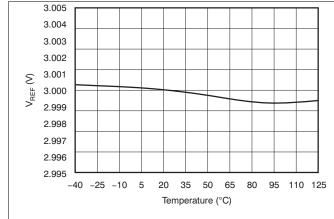

- Programmable and Buffered Internal Reference: 0.5 V to 2.5 V and 0.5 V to 3 V

- Comprehensive Power-Down Modes:

- Deep Power Down (Standby Mode)

- Auto-Nap Power Down

- Selectable Parallel or Serial Interface

- Operating Temperature Range: -40°C to 125°C

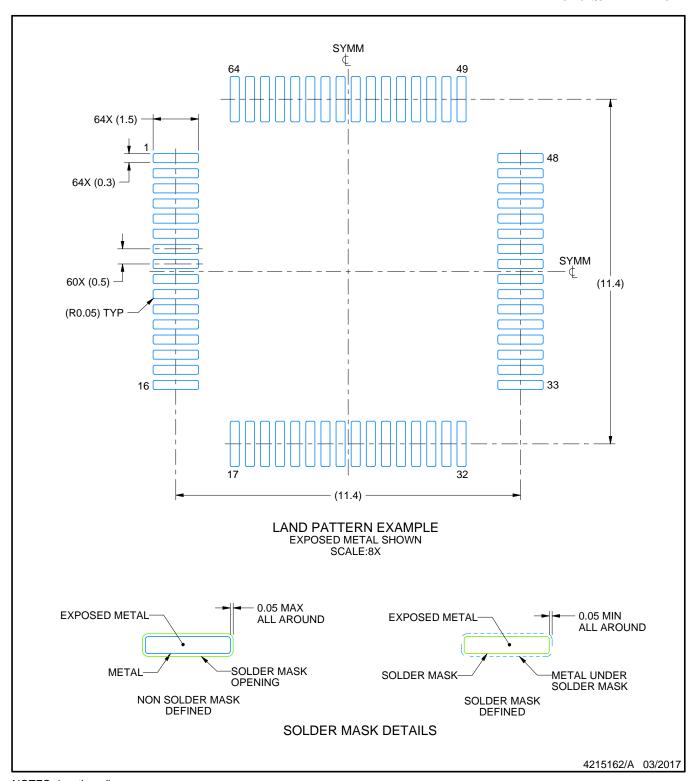

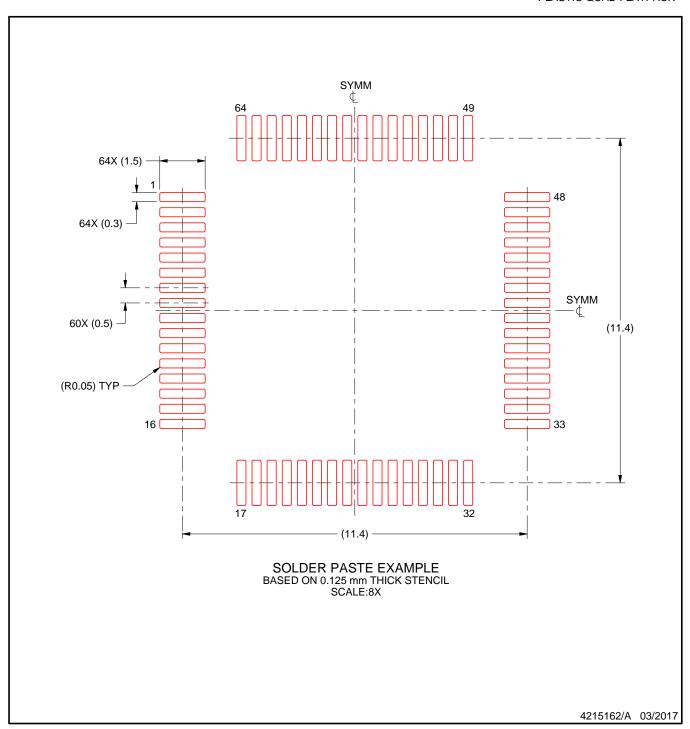

- LQFP-64 Package

# **Applications**

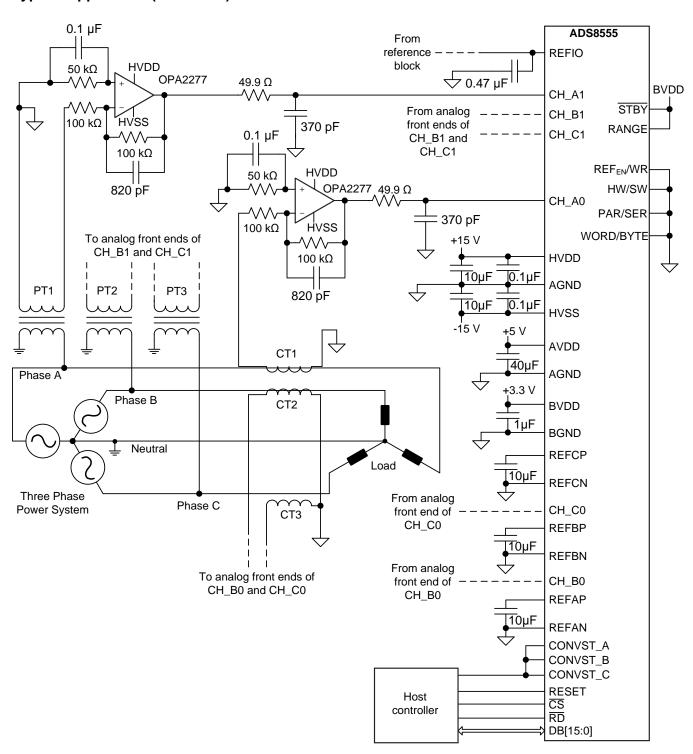

- **Power Quality Measurements**

- **Protection Relays**

- Multi-Axis Motor Controls

- Programmable Logic Controllers

- Industrial Data Acquisition

#### **SNR vs Temperature**

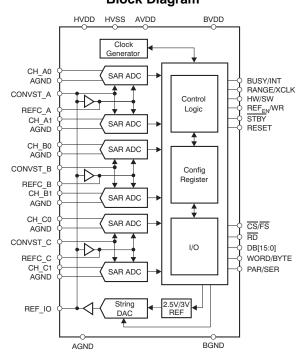

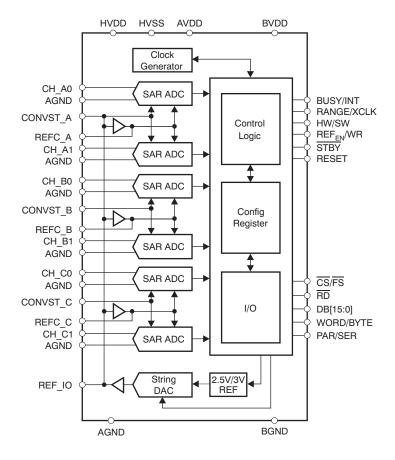

# 3 Description

The ADS8555 device contains six low-power, 16-bit, successive approximation register (SAR)-based analog-to-digital converters (ADCs) with true bipolar inputs. Each channel contains a sample-and-hold circuit that allows simultaneous high-speed multichannel signal acquisition.

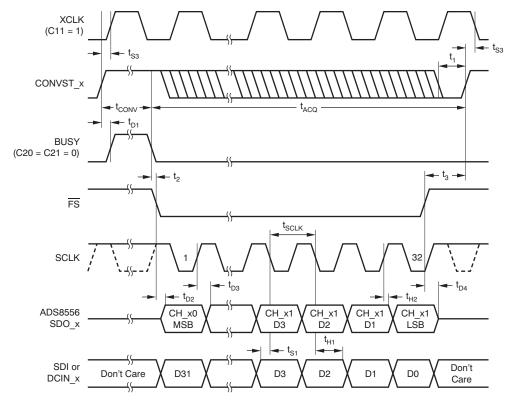

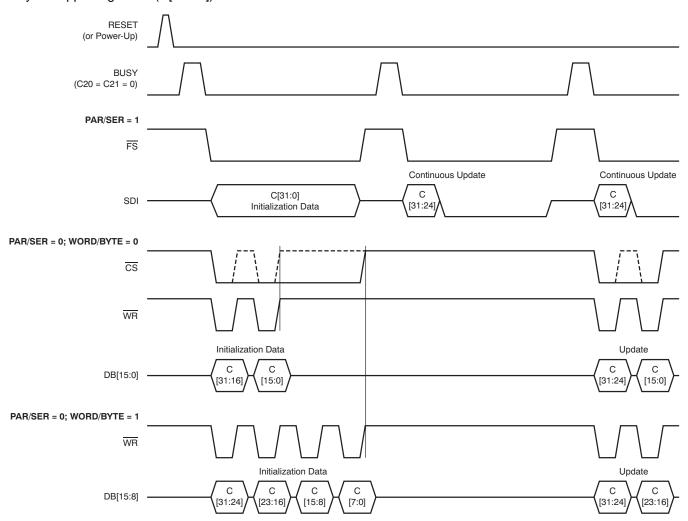

The ADS8555 device supports data rates of up to 630 kSPS in parallel interface mode or up to 450 kSPS if the serial interface is used. The bus width of the parallel interface can be set to eight or 16 bits. In serial mode, up to three output channels can be activated.

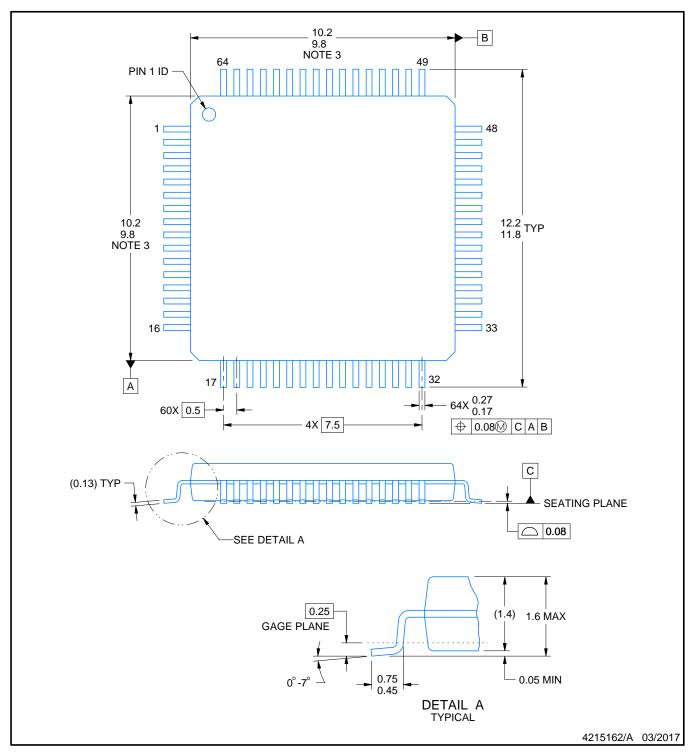

The ADS8555 device is specified over the extended industrial temperature range of -40°C to 125°C and is available in an LQFP-64 package.

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

| ADS8555     | LQFP (64) | 10.00 mm × 10.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# **Block Diagram**

# **Table of Contents**

| 1 | Features 1                                        | 7.2 Functional Block Diagram            |

|---|---------------------------------------------------|-----------------------------------------|

| 2 | Applications 1                                    | 7.3 Feature Description                 |

| 3 | Description 1                                     | 7.4 Device Functional Modes             |

| 4 | Revision History                                  | 7.5 Register Maps29                     |

| 5 | Pin Configuration and Functions                   | 8 Applications and Implementation 31    |

| 6 | Specifications                                    | 8.1 Application Information             |

| • | 6.1 Absolute Maximum Ratings                      | 8.2 Typical Application                 |

|   | 6.2 ESD Ratings                                   | 9 Power Supply Recommendations 35       |

|   | 6.3 Recommended Operating Conditions              | 10 Layout 35                            |

|   | 6.4 Thermal Information                           | 10.1 Layout Guidelines                  |

|   | 6.5 Electrical Characteristics 8                  | 10.2 Layout Example                     |

|   | 6.6 Serial Interface Timing Requirements          | 11 Device and Documentation Support 37  |

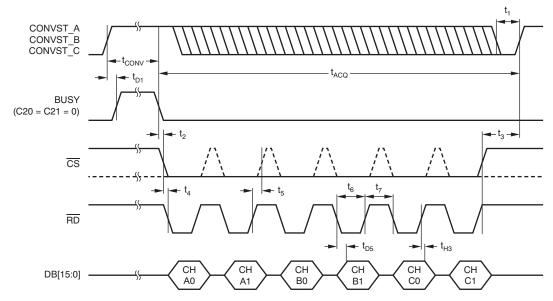

|   | 6.7 Parallel Interface Timing Requirements (Read  | 11.1 Documentation Support              |

|   | Access) 11                                        | 11.2 Community Resources                |

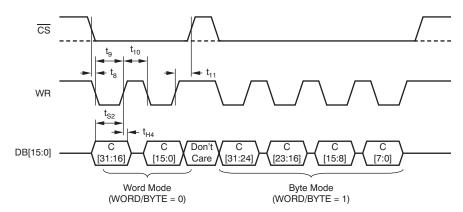

|   | 6.8 Parallel Interface Timing Requirements (Write | 11.3 Trademarks                         |

|   | Access) 11                                        | 11.4 Electrostatic Discharge Caution    |

|   | 6.9 Typical Characteristics                       | 11.5 Glossary                           |

| 7 | Detailed Description 19                           | 12 Mechanical, Packaging, and Orderable |

|   | 7.1 Overview 19                                   | Information                             |

|   |                                                   |                                         |

| _ | ovision History                                   |                                         |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI       | hanges from Revision C (October 2015) to Revision D                                                                                                                                                                                                                                 | Page |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Changed Figure 36: changed capacitor values from 820 nF to 820 pF                                                                                                                                                                                                                   | 32   |

| CI       | hanges from Revision B (February 2011) to Revision C                                                                                                                                                                                                                                | Page |

| •        | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1    |

| CI       | hanges from Revision A (January 2011) to Revision B                                                                                                                                                                                                                                 | Page |

| •        | Changed description of pin 18 in Pin Descriptions table                                                                                                                                                                                                                             | 5    |

| •        | Added clarification of INT in BUSY/INT section                                                                                                                                                                                                                                      | 23   |

| •        | Updated Table 4                                                                                                                                                                                                                                                                     | 28   |

| <u>•</u> | Changed bit C20 in Table 5                                                                                                                                                                                                                                                          | 30   |

| CI       | hanges from Original (December 2010) to Revision A                                                                                                                                                                                                                                  | Page |

| •        | Changed description of CONVST_C, CONVST_B, and CONVST_A pins in Pin Descriptions table                                                                                                                                                                                              | 5    |

| •        | Changed description of CONVST_x section                                                                                                                                                                                                                                             | 22   |

Product Folder Links: ADS8555

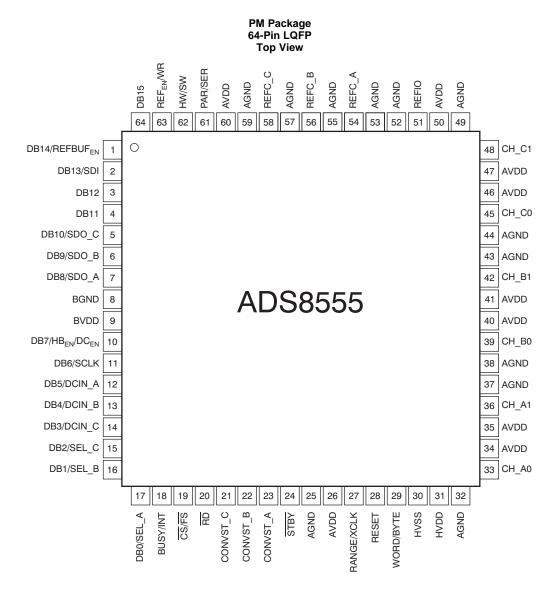

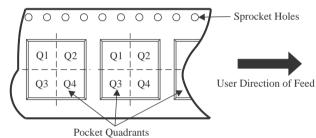

# 5 Pin Configuration and Functions

#### Pin Functions

|                                        | Pin Functions |           |                                                                                                                                                              |                                                                                                                                                                                                              |  |  |  |

|----------------------------------------|---------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN                                    |               | TYPE(1)   | Di                                                                                                                                                           | ESCRIPTION                                                                                                                                                                                                   |  |  |  |

| NAME                                   | NO.           |           | PARALLEL INTERFACE (PAR/SER = 0)                                                                                                                             | SERIAL INTERFACE (PAR/SER = 1)                                                                                                                                                                               |  |  |  |

| DB14/REFBUF <sub>EN</sub>              | 1             | DIO/DI    | Data bit 14 input/output                                                                                                                                     | Hardware mode (HW/SW = 0):<br>Reference buffers enable input.<br>When low, all reference buffers are enabled (mandatory if<br>internal reference is used). When high, all reference buffers<br>are disabled. |  |  |  |

|                                        | The r control |           |                                                                                                                                                              | Software mode (HW/SW = 1):Connect to BGND or BVDD. The reference buffers are controlled by bit C24 (REFBUF) in control register (CR).                                                                        |  |  |  |

| DB13/SDI                               | 2             | DIO/DI    | Data bit 13 input/output                                                                                                                                     | Hardware mode (HW/SW = 0): Connect to BGND                                                                                                                                                                   |  |  |  |

| DB12                                   | 3             | DIO       | Data hit 12 input/gutaut                                                                                                                                     | Software mode (HW/SW = 1): Serial data input  Connect to BGND                                                                                                                                                |  |  |  |

| DB12                                   | 4             | DIO       | Data bit 12 input/output  Data bit 11 input/output                                                                                                           | Connect to BGND                                                                                                                                                                                              |  |  |  |

|                                        |               |           | Data bit 11 input/output                                                                                                                                     | When SEL_C = 1, data output for channel C                                                                                                                                                                    |  |  |  |

| DB10/SDO_C                             | 5             | DIO/DO    | Data bit 10 input/output                                                                                                                                     | When SEL_C = 0, tie this pin to BGND                                                                                                                                                                         |  |  |  |

| DB9/SDO_B                              | 6             | DIO/DO    | Data bit 9 input/output                                                                                                                                      | When SEL_B = 1, data output for channel B When SEL_B = 0, tie this pin to BGND When SEL_C = 0, data from channel C1 are also available on this output                                                        |  |  |  |

| DB8/SDO_A                              | 7             | DIO/DO    | Data bit 8 input/output                                                                                                                                      | Data output for channel A When SEL_C = 0, data from channel C0 are also available on this output When SEL_C = 0 and SEL_B = 0, SDO_A acts as the single data output for all channels                         |  |  |  |

| BGND                                   | BGND 8 P      |           | Buffer I/O ground, connect to digital ground plane                                                                                                           |                                                                                                                                                                                                              |  |  |  |

| BVDD                                   | 9             | Р         | Buffer I/O supply, connect to digital supply (2.7 V to combination of 100-nF and 10-µF ceramic capacitor                                                     | s.5.5 V). Decouple with a 1-μF ceramic capacitor or a rs to BGND.                                                                                                                                            |  |  |  |

|                                        | 10            |           | Word mode (WORD/BYTE = 0):<br>Data bit 7 input/output                                                                                                        |                                                                                                                                                                                                              |  |  |  |

| DB7/HB <sub>EN</sub> /DC <sub>EN</sub> |               | DIO/DI/DI | Byte mode (WORD/BYTE = 1): High byte enable input. When high, the high byte is output first on DB[15:8]. When low, the low byte is output first on DB[15:8]. | Daisy-chain enable input.  When high, DB[5:3] serve as daisy-chain inputs DCIN[A:C].  If daisy-chain mode is not used, connect to BGND.                                                                      |  |  |  |

| DB6/9CLV                               | 11            | DIO/DI    | Word mode (WORD/BYTE = 0):<br>Data bit 6 input/output                                                                                                        | Social interface clock input (26 MHz, may)                                                                                                                                                                   |  |  |  |

| DB6/SCLK                               | 11            | טוט/טו    | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                        | Serial interface clock input (36 MHz, max)                                                                                                                                                                   |  |  |  |

| DB5/DCIN A                             | 12            | DIO/DI    | Word mode (WORD/BYTE = 0):<br>Data bit 5 input/output                                                                                                        | When DC <sub>EN</sub> = 1, daisy-chain data input for channel A                                                                                                                                              |  |  |  |

|                                        | .2            | 510/51    | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                        | When DC <sub>EN</sub> = 0, connect to BGND                                                                                                                                                                   |  |  |  |

| DB4/DCIN_B                             | 13            | DIO/DI    | Word mode (WORD/BYTE = 0): Data bit 4 input/output                                                                                                           | When SEL_B = 1 and DC <sub>EN</sub> = 1, daisy-chain data input for channel B                                                                                                                                |  |  |  |

|                                        |               |           | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                        | When DC <sub>EN</sub> = 0, connect to BGND                                                                                                                                                                   |  |  |  |

| DB3/DCIN_C                             | 14            | DIO/DI    | Word mode (WORD/BYTE = 0): Data bit 3 input/output                                                                                                           | When SEL_C = 1 and DC <sub>EN</sub> = 1, daisy-chain data input for channel C                                                                                                                                |  |  |  |

|                                        |               |           | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                        | When DC <sub>EN</sub> = 0, connect to BGND                                                                                                                                                                   |  |  |  |

| DB2/SEL_C                              | 15            | DIO/DI    | Word mode (WORD/BYTE = 0):<br>Data bit 2 input/output                                                                                                        | Select SDO_C input.                                                                                                                                                                                          |  |  |  |

|                                        | 10            | 2.0/01    | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                        | When high, SDO_C is active. When low, SDO_C is disabled.                                                                                                                                                     |  |  |  |

| DB1/SEL_B                              | 16            | חוט/טו    | Word mode (WORD/BYTE = 0):<br>Data bit 1 input/output                                                                                                        | Select SDO_B input.                                                                                                                                                                                          |  |  |  |

| DD I/OLL_D                             | 10            | DIO/DI    | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                        | When high, SDO_B is active. When low, SDO_B is disabled.                                                                                                                                                     |  |  |  |

<sup>(1)</sup> Al = analog input; AlO = analog input/output; DI = digital input; DO = digital output; DIO = digital input/output; and P = power supply.

# Pin Functions (continued)

| PIN TYPE <sup>(1)</sup> |                                                               |          | DESCRIPTION                                                                                                                                                                                                                                                                |                                                                                                                                                                                |  |  |  |

|-------------------------|---------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                    | NO.                                                           | TIPE     | PARALLEL INTERFACE (PAR/SER = 0)                                                                                                                                                                                                                                           | SERIAL INTERFACE (PAR/SER = 1)                                                                                                                                                 |  |  |  |

| DBO/SEL A               | 17                                                            | DIO/DI   | Word mode (WORD/BYTE = 0):<br>Data bit 0 (LSB) input/output                                                                                                                                                                                                                | Select SDO_A input.                                                                                                                                                            |  |  |  |

| DB0/SEL_A               | 17                                                            | DIO/DI   | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                                                                                                                                      | When high, SDO_A is active. When low, SDO_A is disabled. Must always be high.                                                                                                  |  |  |  |

| BUSY/INT                | 18                                                            | DO       | remains high during the entire process. Transitions in the output register and remains low thereafter. In sequential mode (SEQ = 1 in the CR), the BUSY for a single conversion clock cycle (t <sub>CCLK</sub> ) whenever                                                  | ut. This bit transitions high after a conversion completes and                                                                                                                 |  |  |  |

| CS/FS                   | 19                                                            | DI/DI    | Chip select input.<br>When low, the parallel interface is enabled. When<br>high, the interface is disabled.                                                                                                                                                                | Frame synchronization. The falling edge of FS controls the frame transfer.                                                                                                     |  |  |  |

| RD                      | 20                                                            | DI       | Read data input. When low, the parallel data output is enabled. When high, the data output is disabled.                                                                                                                                                                    | Connect to BGND                                                                                                                                                                |  |  |  |

| CONVST_C                | 21                                                            | DI       | Hardware mode (HW/SW = 0): Conversion start of c<br>The rising edge of this signal initiates simultaneous of                                                                                                                                                               |                                                                                                                                                                                |  |  |  |

| 0014731_0               | 21                                                            | ы        | Software mode (HW/SW = 1): Conversion start of channel to BGND or BVDD otherwise                                                                                                                                                                                           | nannel pair C in sequential mode (CR bit C23 = 1) only;                                                                                                                        |  |  |  |

| CONVST B                | 22                                                            | DI       | Hardware mode (HW/SW = 0): Conversion start of c<br>The rising edge of this signal initiates simultaneous of                                                                                                                                                               | HW/SW = 0): Conversion start of channel pair B.  If this signal initiates simultaneous conversion of analog signals at inputs CH_B[1:0].                                       |  |  |  |

| CONVOT_D                | 22                                                            | ы        | Software mode (HW/SW = 1): Conversion start of channel to BGND or BVDD otherwise                                                                                                                                                                                           | ion start of channel pair B in sequential mode (CR bit C23 = 1) only;                                                                                                          |  |  |  |

| CONVST_A                | 23                                                            | DI       | Hardware mode (HW/SW = 0): Conversion start of c<br>The rising edge of this signal initiates simultaneous of                                                                                                                                                               |                                                                                                                                                                                |  |  |  |

| 0011101_1               | 20                                                            | <u> </u> | Software mode (HW/SW = 1): Conversion start of all selected channels except in sequential mode (CR bit C23 = 1): Conversion start of channel pair A only                                                                                                                   |                                                                                                                                                                                |  |  |  |

| STBY                    | 24                                                            | DI       | Standby mode input. When low, the entire device is When high, the device operates in normal mode.                                                                                                                                                                          | powered down (including the internal clock and reference).                                                                                                                     |  |  |  |

| AGND                    | 25, 32,<br>37, 38,<br>43, 44,<br>49, 52,<br>53, 55,<br>57, 59 | Р        | Analog ground, connect to analog ground plane Pin 25 can have a dedicated ground if the difference mV.                                                                                                                                                                     | e between its potential and AGND is always kept within ±300                                                                                                                    |  |  |  |

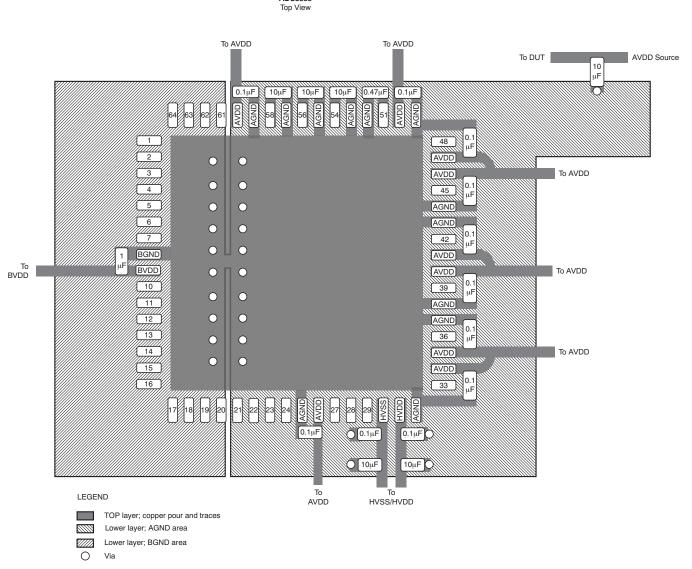

| AVDD                    | 26, 34,<br>35, 40,<br>41, 46,<br>47, 50,<br>60                | Р        | additional 10-µF capacitor to AGND close to the dev                                                                                                                                                                                                                        | th pin with a 100-nF ceramic capacitor to AGND. Use an vice but without compromising the placement of the smaller y if the difference between its potential and AVDD is always |  |  |  |

| RANGE/XCLK              | 27                                                            | DI/DIO   | Hardware mode (HW/SW = 0): Input voltage range s When low, the analog input range is $\pm 4$ V <sub>REF</sub> . When                                                                                                                                                       |                                                                                                                                                                                |  |  |  |

| TO IN OLI NOLIN         | 21                                                            | DI/DIO   |                                                                                                                                                                                                                                                                            | clock input, if CR bit C11 (CLKSEL) is set high or internal N) is set high. If not used, connect to BVDD or BGND.                                                              |  |  |  |

| RESET                   | 28                                                            | DI       | Reset input, active high. Aborts any ongoing convers RESET pulse must be at least 50 ns long.                                                                                                                                                                              | sions. Resets the internal control register to 0x000003FF. The                                                                                                                 |  |  |  |

| WORD/BYTE               | 29                                                            | DI       | Output mode selection input. When low, data are transferred in word mode using DB[15:0]. When high, data are transferred in byte mode using DB[15:8] with the byte order controlled by HB <sub>EN</sub> pin when two accesses are required for a complete 16-bit transfer. | v, data are transferred in word mode using . When high, data are transferred in byte ing DB[15:8] with the byte order controlled pin when two accesses are required for a      |  |  |  |

| HVSS                    | 30                                                            | Р        | Negative supply voltage for the analog inputs (-16.5 V to -5 V).  Decouple with a 10-0nF ceramic capacitor to AGND placed next to the device and a 10-µF capacitor to AGND close to the device but without compromising the placement of the smaller capacitor.            |                                                                                                                                                                                |  |  |  |

| HVDD                    | 31                                                            | Р        | Positive supply voltage for the analog inputs (5 V to 16.5 V). Decouple with a 100-nF ceramic capacitor to AGND placed next to the device and a 10-µF capacitor to AGND close to the device but without compromising the placement of the smaller capacitor.               |                                                                                                                                                                                |  |  |  |

| CH_A0                   | 33                                                            | AI       | Analog input of channel A0. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C26 (RANGE_A) in software mode.                                                                                                                                  |                                                                                                                                                                                |  |  |  |

| CH_A1                   | 36                                                            | AI       | Analog input of channel A1. The input voltage range (RANGE_A) in software mode.                                                                                                                                                                                            | is controlled by RANGE pin in hardware mode or CR bit C26                                                                                                                      |  |  |  |

# Pin Functions (continued)

| Analog input of channel B0. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C27 (RANGE_B) in software mode.  CH_B1 42 AI Analog input of channel B1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C27 (RANGE_B) in software mode.  CH_C0 45 AI Analog input of channel C0. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  CH_C1 48 AI Analog input of channel C1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  REFIO 51 AIO Analog input of channel C1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RRNGE_C) in software mode.  REFIO 51 AIO Analog input of channel C1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (REF <sub>EN</sub> ) in software mode.  REFIO 51 AIO Analog input of channel C1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (REF <sub>EN</sub> ) in software mode.  REFIO 52 AI Decoupling capacitor between this in and pin 52.  REFIC_B 54 AI Decoupling capacitor for reference of channels A. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 53.  REFIC_B 55 AI Decoupling capacitor for reference of channels B. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  REFIC_C 58 AI Decoupling capacitor for reference of channels C. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 57.  HARVSER 61 DI Interface mode selection input.  When low, the parallel interface is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device works according to the settings of external pins. When high, the internal reference enable input.  When low, the parallel interface is enabled (the reference buffers are to be enabled). When low, the internal reference enable input.  When low, the internal reference is enabled to the reference is ena | PIN                   |     | <b>-</b> > (-) | DE                                                                                                                                                                                                                                                 | ESCRIPTION                                                                                                                                                                                                          |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CH_B1 42 Al Analog input of channel B1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C27 (RANGE_B) in software mode.  CH_CO 45 Al Analog input of channel CO. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  CH_CO 48 Al Analog input of channel CO. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  CH_CO 48 Al Analog input of channel CO. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  REFIO 51 AlO 52 Reference voltage input/output (0.5 V to 3.025 V).  REFIO 52 Analog input ference is enabled through REF <sub>EN</sub> /WR pin in hardware mode or CR bit C28 (REF <sub>EN</sub> ) in software mode.  REFC_A 54 Al Decoupling capacitor between this pin and pin 52.  REFC_B 56 Al Decoupling capacitor for reference of channels A. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 53.  REFC_C 58 Al Decoupling capacitor for reference of channels B.  REFC_C 58 Al Decoupling capacitor for reference of channels C. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  REFC_C 58 Al Decoupling capacitor for reference of channels C. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  REFC_C 58 Al Decoupling capacitor for reference of channels C. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor between this pin and pin 57.  Hardware mode (Becompting capacitor betwee | NAME                  | NO. | IYPE           | PARALLEL INTERFACE (PAR/SER = 0)                                                                                                                                                                                                                   | SERIAL INTERFACE (PAR/SER = 1)                                                                                                                                                                                      |  |

| CH_C0 45 AI (RANGE_B) in software mode.  CH_C0 45 AI Analog input of channel C0. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  CH_C1 48 AI Analog input of channel C1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  REFIO 51 AIO Reference voltage input/output (0.5 V to 3.025 V).  The internal reference is enabled through REF <sub>EN</sub> WR pin in hardware mode or CR bit C25 (REF <sub>EN</sub> ) in software mode. The output value is controlled by the internal DAC (CR bits C[9:0]). Connect a 470-nF ceramic decoupling capacitor between this pin and pin 53.  REFC_B 56 AI Decoupling capacitor for reference of channels B. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 53.  REFC_C 58 AI Decoupling capacitor for reference of channels B. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  REFC_C 58 AI Decoupling capacitor for reference of channels B. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 57.  HW/SW 62 DI Interface mode selection input.  When low, the parallel interface is selected. When high, the serial interface is enabled.  Mode selection input.  When low, the hardware mode is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device is configured by writing into the control register.  HARD HARD HARD HARD HARD HARD HARD HARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CH_B0                 | 39  | AI             |                                                                                                                                                                                                                                                    | is controlled by RANGE pin in hardware mode or CR bit C27                                                                                                                                                           |  |

| CH_C1 48 AI (RANGE_C) in software mode.  CH_C1 48 AI Analog input of channel C1. The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 (RANGE_C) in software mode.  Reference voltage input/output (0.5 V to 3.025 V). The internal reference is enabled through REF <sub>EN</sub> /WR pin in hardware mode or CR bit C25 (REF <sub>EN</sub> ) in software mode.  Reference voltage input/output (0.5 V to 3.025 V). The internal reference is enabled through REF <sub>EN</sub> /WR pin in hardware mode or CR bit C25 (REF <sub>EN</sub> ) in software mode. The output value is controlled by the internal DAC (CR bits C[9:0]). Connect a 470-nF ceramic decoupling capacitor between this pin and pin 52.  REFC_A 54 AI Decoupling capacitor for reference of channels A. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 53.  REFC_C 58 AI Decoupling capacitor for reference of channels B. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  PAR/SER 61 DI Interface mode selection input. When low, the parallel interface is selected. When high, the serial interface is enabled.  Mode selection input. When low, the parallel interface is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device is configured by writing into the control register.  Hardware mode (HW/SW = 0): Internal reference is anabled (the reference buffers are to be enabled). When low, the internal reference is ableid and an external reference enable input. When high, the internal reference is adsisted and an external reference must be applied at reference is applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                            | CH_B1                 | 42  | AI             |                                                                                                                                                                                                                                                    | is controlled by RANGE pin in hardware mode or CR bit C27                                                                                                                                                           |  |

| REFIO 51 AIO Reference voltage input/output (0.5 V to 3.025 V). The internal reference is enabled through REF <sub>EV</sub> WR pin in hardware mode or CR bit C25 (REF <sub>EN</sub> ) in software mode. The output value is controlled by the internal DAC (CR bits C[9:0]). Connect a 470-nF ceramic decoupling capacitor between this pin and pin 52.  REFC_A 54 AI Decoupling capacitor for reference of channels A. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 53.  REFC_B 56 AI Decoupling capacitor for reference of channels B. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  REFC_C 58 AI Decoupling capacitor for reference of channels C. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  PAR/SER 61 DI Interface mode selection input. When low, the parallel interface is selected. When high, the serial interface is enabled.  Mode selection input. When low, the hardware mode is selected and the device works according to the settings of external pins. When high, the internal reference enable input. When low, the hardware mode is selected in which the device is configured by writing into the control register.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference enable input. When hi | CH_C0                 | 45  | AI             |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |  |

| The internal reference is enabled through REF <sub>EN</sub> /WR pin in hardware mode or CR bit C25 (REF <sub>EN</sub> ) in software mode. The output value is controlled by the internal DAC (CR bits C[9:0]). Connect a 470-nF ceramic decoupling capacitor between this pin and pin 52.  REFC_A  AI  Decoupling capacitor for reference of channels A. Connect a 10-μF ceramic decoupling capacitor between this pin and pin 53.  Decoupling capacitor for reference of channels A. Connect a 10-μF ceramic decoupling capacitor between this pin and pin 53.  REFC_B  AI  Decoupling capacitor for reference of channels B. Connect a 10-μF ceramic decoupling capacitor between this pin and pin 55.  PAR/SER  AI  Decoupling capacitor for reference of channels C. Connect a 10-μF ceramic decoupling capacitor between this pin and pin 57.  Interface mode selection input. When low, the parallel interface is selected. When high, the serial interface is enabled.  Mode selection input. When low, the parallel interface is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device is configured by writing into the control register.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference is enabled (the reference enable input. When high, the internal reference is enabled). When low, the internal reference is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                | CH_C1                 | 48  | AI             |                                                                                                                                                                                                                                                    | is controlled by RANGE pin in hardware mode or CR bit C28                                                                                                                                                           |  |

| REFC_B  54  Al Connect a 10-µF ceramic decoupling capacitor between this pin and pin 53.  REFC_B  56  Al Decoupling capacitor for reference of channels B. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  REFC_C  58  Al Decoupling capacitor for reference of channels C. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 57.  PAR/SER  61  DI Interface mode selection input. When low, the parallel interface is selected. When high, the serial interface is enabled.  HW/SW  62  DI When low, the hardware mode is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device is configured by writing into the control register.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference enabled (the reference buffers are to be enabled). When low, the internal reference is disabled and an external reference enabled by the internal reference must be applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).  Software mode (HW/SW = 1): Connect to BGND or BVDD. The internal reference is enabled by CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REFIO                 | 51  | AIO            | The internal reference is enabled through REF <sub>EN</sub> /WR pin in hardware mode or CR bit C25 (REF <sub>EN</sub> ) in software mode. The output value is controlled by the internal DAC (CR bits C[9:0]). Connect a 470-nF ceramic decoupling |                                                                                                                                                                                                                     |  |

| Connect a 10-µF ceramic decoupling capacitor between this pin and pin 55.  REFC_C 58 Al Decoupling capacitor for reference of channels C. Connect a 10-µF ceramic decoupling capacitor between this pin and pin 57.  PAR/SER 61 DI Interface mode selection input. When low, the parallel interface is selected. When high, the serial interface is enabled.  Mode selection input. When low, the hardware mode is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device is configured by writing into the control register.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference is enabled (the reference buffers are to be enabled). When low, the internal reference enable input. When high, the internal reference is disabled and an external reference enable input. When high, the internal reference is disabled and an external reference enable input. When high, the internal reference is disabled and an external reference must be applied at reference is applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | REFC_A                | 54  | AI             |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |  |

| Connect a 10-µF ceramic decoupling capacitor between this pin and pin 57.    PAR/SER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | REFC_B                | 56  | AI             |                                                                                                                                                                                                                                                    | reen this pin and pin 55.                                                                                                                                                                                           |  |

| When low, the parallel interface is selected. When high, the serial interface is enabled.  Mode selection input. When low, the hardware mode is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device is configured by writing into the control register.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference is enabled (the reference buffers are to be enabled). When low, the internal reference buffers are to be enabled). When high, the internal reference is disabled and an external reference must be applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).  When high, the serial interface is enabled.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the serial interface is enabled.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference is disabled and an external reference buffers are to be enabled). When low, the internal reference is disabled and an external reference must be applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by The internal reference is enabled by CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REFC_C                | 58  | AI             |                                                                                                                                                                                                                                                    | veen this pin and pin 57.                                                                                                                                                                                           |  |

| When low, the hardware mode is selected and the device works according to the settings of external pins. When high, the software mode is selected in which the device is configured by writing into the control register.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference is enabled (the reference buffers are to be enabled). When low, the internal reference is disabled and an external reference is applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).  When low, the hardware mode is selected and the device works according to the settings of external pins. When low, the control register.  Hardware mode (HW/SW = 0): Internal reference enable input. When high, the internal reference is enabled (the reference buffers are to be enabled). When low, the internal reference is disabled and an external reference must be applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PAR/SER               | 61  | DI             |                                                                                                                                                                                                                                                    | igh, the serial interface is enabled.                                                                                                                                                                               |  |

| Internal reference enable input.  When high, the internal reference is enabled (the reference buffers are to be enabled). When high, the internal reference buffers are to be enabled). When low, the internal reference is disabled and an external reference is disabled and an external reference must be applied at REFIO.  Software mode (HW/SW = 1): Write input. The parallel data input is enabled when CS and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).  Internal reference enable input. When high, the internal reference is enabled). When low, the internal reference is disabled and an external reference must be applied at REFIO.  Software mode (HW/SW = 1): Connect to BGND or BVDD. The internal reference is enabled by CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HW/SW                 | 62  | DI             | When low, the hardware mode is selected and the d                                                                                                                                                                                                  |                                                                                                                                                                                                                     |  |

| The parallel data input is enabled when $\overline{\text{CS}}$ and WR are low. The internal reference is enabled by the CR bit C25 (REF <sub>EN</sub> ).  Software mode (HW/SW = 1): Connect to BGND or BVDD. The internal reference is enabled by CR bit C25 (REF <sub>EN</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REF <sub>EN</sub> /WR | 63  | DI             | Internal reference enable input. When high, the internal reference is enabled (the reference buffers are to be enabled). When low, the internal reference is disabled and an external reference is applied at REFIO.                               | Internal reference enable input.  When high, the internal reference is enabled (the reference buffers are to be enabled). When low, the internal reference is disabled and an external reference must be applied at |  |

| DB15 64 DIO Data bit 15 (MSB) input/output Connect to BGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       |     |                | The parallel data input is enabled when $\overline{\text{CS}}$ and WR are low. The internal reference is enabled by                                                                                                                                | To CS and Software mode (HW/SW = 1): Connect to BGND or BVDD                                                                                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DB15                  | 64  | DIO            | Data bit 15 (MSB) input/output                                                                                                                                                                                                                     | Connect to BGND                                                                                                                                                                                                     |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                      | MIN        | MAX        | UNIT |

|------------------------------------------------------|------------|------------|------|

| Supply voltage, HVDD to AGND                         | -0.3       | 18         | V    |

| Supply voltage, HVSS to AGND                         | -18        | 0.3        | V    |

| Supply voltage, AVDD to AGND                         | -0.3       | 6          | V    |

| Supply voltage, BVDD to BGND                         | -0.3       | 6          | V    |

| Analog input voltage                                 | HVSS - 0.3 | HVDD + 0.3 | V    |

| Reference input voltage with respect to AGND         | AGND – 0.3 | AVDD + 0.3 | V    |

| Digital input voltage with respect to BGND           | BGND - 0.3 | BVDD + 0.3 | V    |

| Ground voltage difference AGND to BGND               |            | ±0.3       | V    |

| Input current to all pins except supply              | -10        | 10         | mA   |

| Maximum virtual junction temperature, T <sub>J</sub> |            | 150        | °C   |

| Storage temperature, T <sub>stg</sub>                | -65        | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Flootroototic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

- JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

|                                               |                                      | MIN                   | NOM | MAX                                                                                                                                 | UNIT |  |

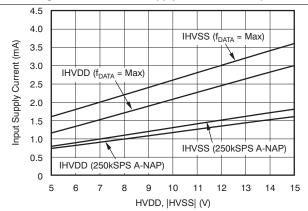

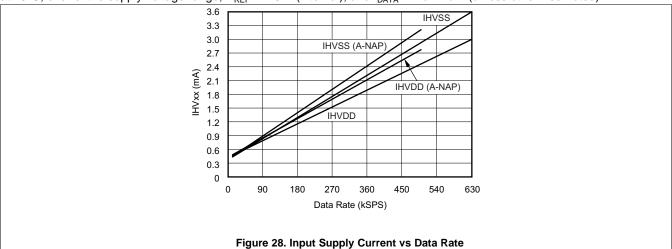

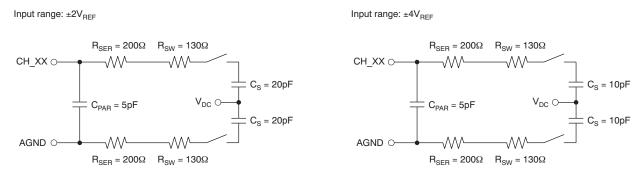

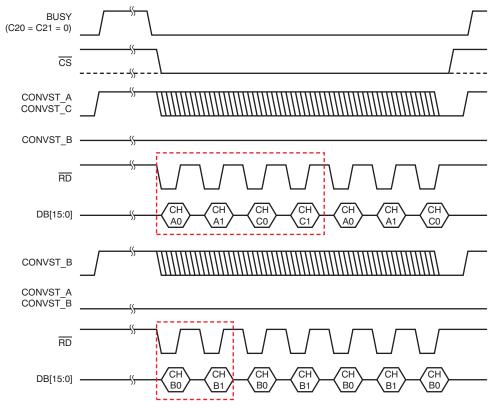

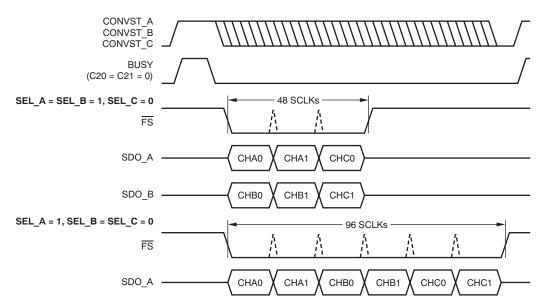

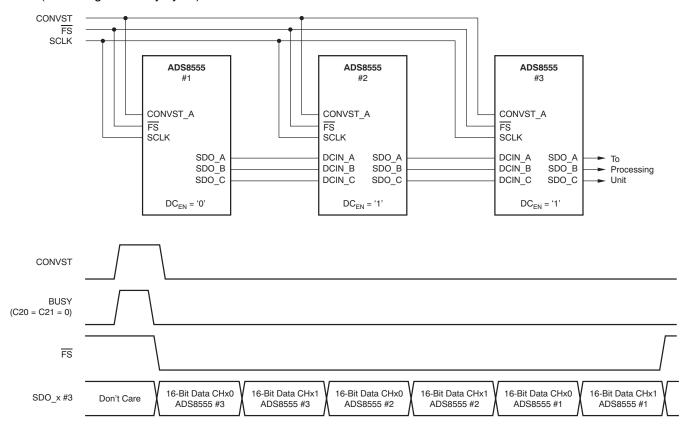

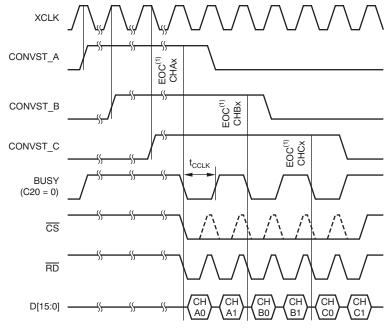

|-----------------------------------------------|--------------------------------------|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|------|--|