**AWR1243** ZHCSHS1D - MAY 2017 - REVISED DECEMBER 2021

# AWR1243 单芯片 77GHz 和 79GHz FMCW 收发器

## 1 特性

- FMCW 收发器

- 集成 PLL、发送器、接收器、基带和 ADC

- 76GHz 至 81GHz 的覆盖范围, 具有 4GHz 的可 用带宽

- 四个接收通道

- 三个发送通道(可以同时使用两个通道)

- 基于分数 N PLL 的超精确线性调频脉冲引擎

- TX 功率: 12dBm

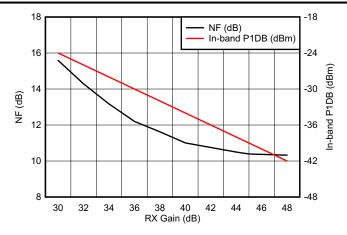

- RX 噪声系数:

- 14dB (76 至 77GHz)

- 15dB (77 至 81GHz)

- 1MHz 时的相位噪声:

- 95dBc/Hz (76 至 77GHz)

- 93dBc/Hz (77 至 81GHz)

- 内置校准和自检

- 内置固件 (ROM)

- 针对工艺和温度进行自校准的系统

- 主机接口

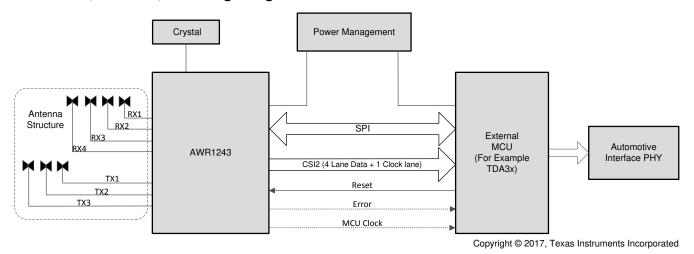

- 通过 SPI 与外部处理器进行控制连接

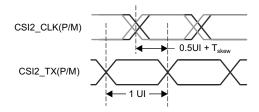

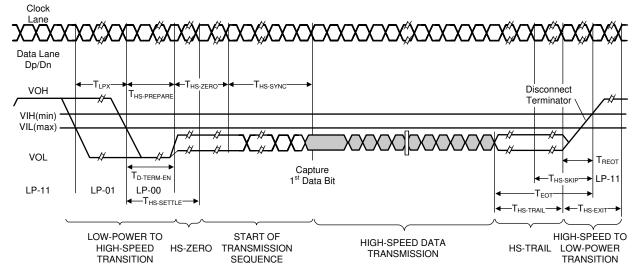

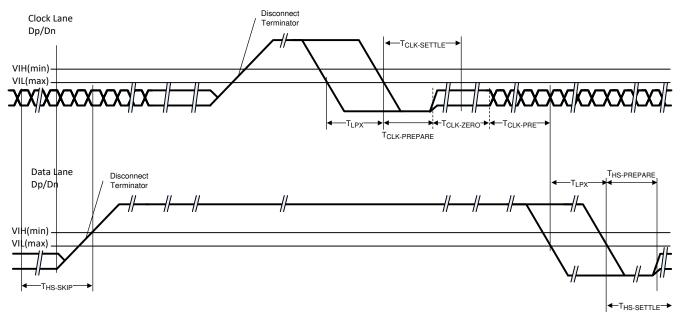

- 通过 MIPI D-PHY 和 CSI2 V1.1 与外部处理器进 行数据连接

- 用于故障报告的中断

- 符合功能安全标准

- 专为功能安全应用开发

- 文档有助于使 ISO 26262 功能安全系统设计满 足 ASIL-D 级要求

- 硬件完整性高达 ASIL-B 级

- 安全相关认证

- 经 TUV SUD 进行 ISO 26262 认证达到 ASIL

- 符合 AEC-Q100 标准

- 器件高级特性

- 嵌入式自监控,无需使用主机处理器

- 复基带架构

- 嵌入式干扰检测功能

- 电源管理

- 内置 LDO 网络,可增强 PSRR

- I/O 支持双电压 3.3V/1.8V

- 时钟源

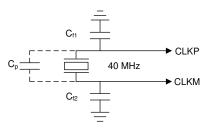

- 支持外部驱动、频率为 40MHz 的时钟 (方波/正

- 支持 40MHz 晶体与负载电容器相连接

- 轻松的硬件设计

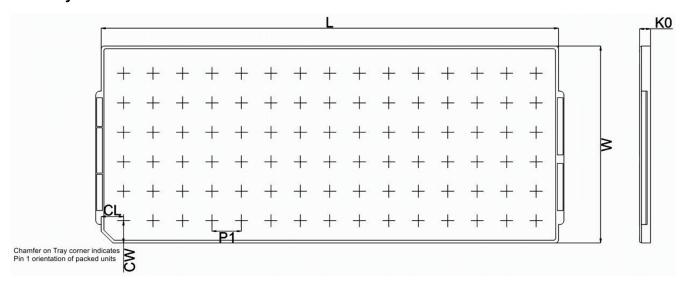

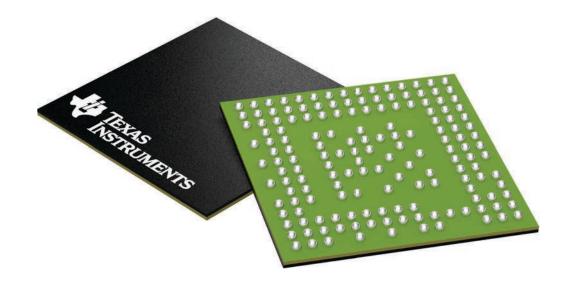

- 0.65mm 间距、161 引脚 10.4mm × 10.4mm 覆 晶 BGA 封装,可实现轻松组装和低成本 PCB 设计

- 小尺寸解决方案

- 运行条件

- 结温范围: -40°C至 125°C

## 2 应用

- 自动紧急刹车

- 自适应巡航控制

- 用于测量距离、速度和角度的汽车传感器

- 自动公路驾驶

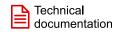

图 2-1. 适用于汽车应用的自主雷达传感器

## 3 说明

AWR1243 器件是一款能够在 76 至 81GHz 频带内运行的集成式单芯片 FMCW 收发器。该器件在极小的封装中实现了出色的集成度。AWR1243 是适用于汽车领域中的低功耗、自监控、超精确雷达系统的理想解决方案。

AWR1243 器件是一种自包含 FMCW 收发器单芯片解决方案,能够简化 76 至 81GHz 频带中的汽车雷达传感器实施。它基于 TI 的低功耗 45nm RFCMOS 工艺构建,从而实现了一个具有内置 PLL 和 ADC 转换器的单片实施 3TX、4RX 系统。简单编程模型更改可支持各种传感器实施(近距离、中距离和远距离),并且能够进行动态重新配置,从而实现多模式传感器。此外,该器件作为完整的平台解决方案进行提供,其中包括 TI 参考设计、软件驱动程序、示例配置、API 指南以及用户文档。

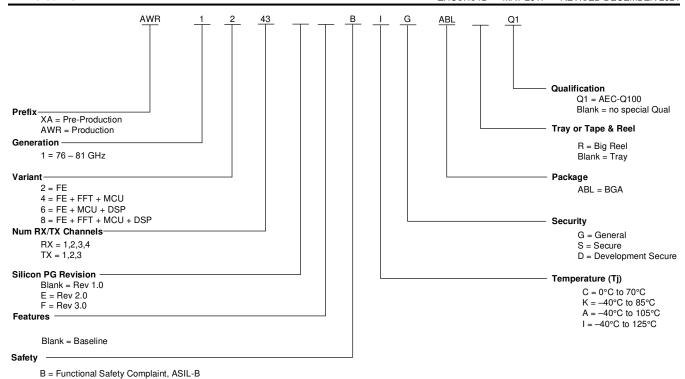

## 器件信息

| 器件型号(2)           | 封装 <sup>(1)</sup> | 封装尺寸                  | 托盘/卷带包装 |  |

|-------------------|-------------------|-----------------------|---------|--|

| AWR1243FBIGABLQ1  | FCBGA (161)       | 10.4mm × 10.4mm       | 托盘      |  |

| AWR1243FBIGABLRQ1 | PODGA (101)       | 10.411111 ^ 10.411111 | 卷带包装    |  |

- (1) 如需更多信息,请参阅节 13 机械、封装和可订购信息。

- (2) 如需更多信息,请参阅节 12.1,器件命名规则。

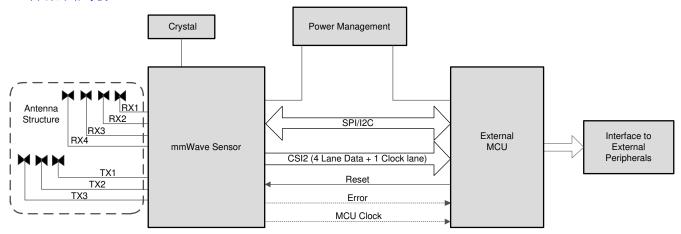

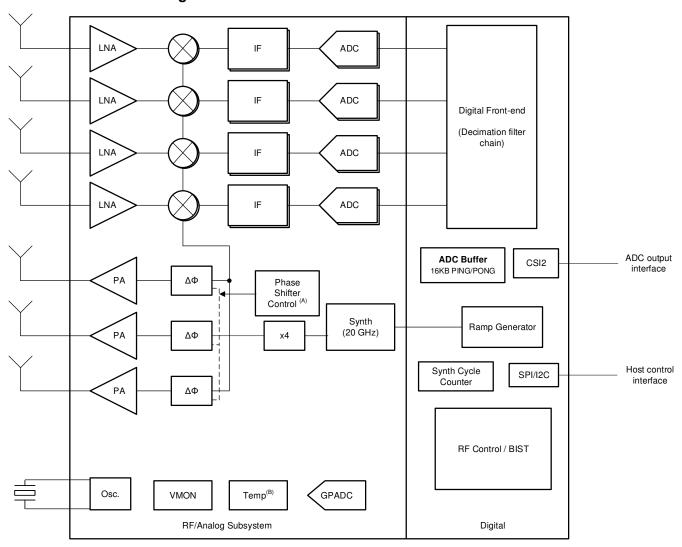

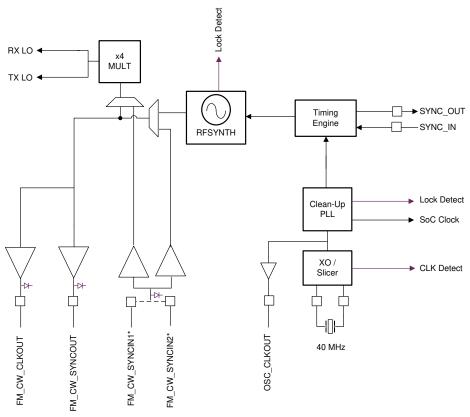

# **4 Functional Block Diagram**

- A. Phase Shift Control:

- 0° / 180° BPM for AWR1243

- B. Internal temperature sensor accuracy is ± 7 °C.

图 4-1. Functional Block Diagram

# **Table of Contents**

| 1 特性                                             | 1  | 9.1 Overview                                | 33 |

|--------------------------------------------------|----|---------------------------------------------|----|

| 2 应用                                             |    | 9.2 Functional Block Diagram                | 33 |

| - <del>/</del>                                   |    | 9.3 Subsystems                              |    |

| 4 Functional Block Diagram                       |    | 9.4 Other Subsystems                        |    |

| 5 Revision History                               |    | 10 Monitoring and Diagnostics               | 39 |

| 6 Device Comparison                              |    | 10.1 Monitoring and Diagnostic Mechanisms   | 39 |

| 6.1 Related Products                             |    | 11 Applications, Implementation, and Layout | 42 |

| 7 Terminal Configuration and Functions           |    | 11.1 Application Information                | 42 |

| 7.1 Pin Diagram                                  |    | 11.2 Short-, Medium-, and Long-Range Radar  | 42 |

| 7.2 Signal Descriptions                          |    | 11.3 Reference Schematic                    | 43 |

| 8 Specifications                                 |    | 12 Device and Documentation Support         | 44 |

| 8.1 Absolute Maximum Ratings                     |    | 12.1 Device Nomenclature                    | 44 |

| 8.2 ESD Ratings                                  |    | 12.2 Tools and Software                     | 45 |

| 8.3 Power-On Hours (POH)                         |    | 12.3 Documentation Support                  | 45 |

| 8.4 Recommended Operating Conditions             |    | 12.4 支持资源                                   | 45 |

| 8.5 Power Supply Specifications                  |    | 12.5 Trademarks                             | 46 |

| 8.6 Power Consumption Summary                    |    | 12.6 Electrostatic Discharge Caution        | 46 |

| 8.7 RF Specification                             |    | 12.7 术语表                                    | 46 |

| 8.8 Thermal Resistance Characteristics for FCBGA |    | 13 Mechanical, Packaging, and Orderable     |    |

| Package [ABL0161]                                | 21 | Information                                 | 47 |

| 8.9 Timing and Switching Characteristics         |    | 13.1 Packaging Information                  | 47 |

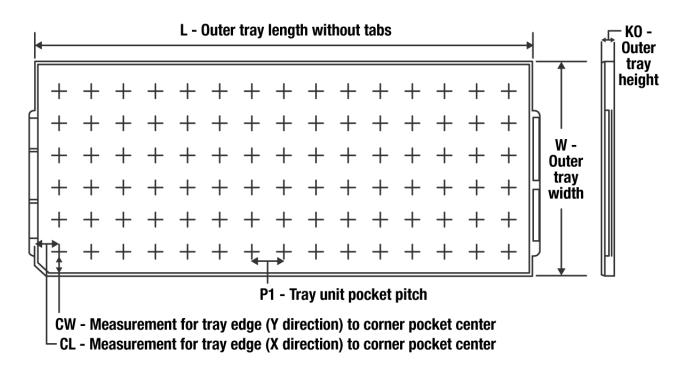

| 9 Detailed Description                           |    | 13.2 Tray Information for                   |    |

| •                                                |    | ·                                           |    |

# **5 Revision History**

|   | ecember 2021))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ge  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | <i>通篇</i> :进行了更新,以反映功能安全合规性及相关认证资料                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1   |

| • | 通篇:将 "A2D" 替换为 "ADC";将 "主子系统"和 "主 R4F"更改为 "主要子系统"和 "主要 R4F";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 在   |

|   | 主/从术语方面改用了更具包容性的措辞                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| • | (特性):提及了毫米波传感器的额定工作温度范围                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1   |

| • | (应用):修订了图示并更新了应用链接                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2   |

| • | (器件信息):从表格中删除了可订购的预量产器件型号(XA1243FPBGABL)及其相关特性                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 2 |

| • | Updated/Changed Functional Block Diagram to remove XA1243FPBGABL OPN specific features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 3 |

| • | (Device Comparison): Removed a row on Functionaly-Safety compliance and instead added a table-note for this and LVDS Interface; modified the existing table-note on simultaneous TX operation; Additional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | or  |

|   | information on Device security added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0   |

| • | (Device Comparison): Updated/Changed RF Specification Receiver from "Max real sampling rate (Msps)" to "Max real/complex 2x sampling rate (Msps)"; and "Max complex sampling rate (Msps)" to "Max complex 1x sampling rate (Msps)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| • | (Signal Descriptions): Removed XA1243FPBGABL OPN specific pin functions; updated descriptions for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|   | CLKP and CLKM pins for Reference Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12  |

| • | (Absolute Maximum Ratings): Added entries for externally supplied power on the RF inputs (TX and RX) and table-note for the signal level applied on TX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16  |

| • | (Power Supply Specifications): Updated/Changed footnote in 表 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18  |

| • | (Maximum Current Rating at Power Terminals): Updated footnotes section to add estimation assumption for VIOIN rail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| • | (Average Power Consumption at Power Terminals): Removed 3TX, 4RX power numbers since only 2TX are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Э   |

|   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19  |

| • | (RF Specification): Updated/Changed RF Specification Receiver from "A2D sampling rate (complex)" to "AE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|   | sampling rate (complex 1x)"; and "A2D sampling rate (real)" to "ADC sampling rate (real/complex 2x)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| • | (RF Specification): Updated/Changed the table to remove XA1243FPBGABL specific features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

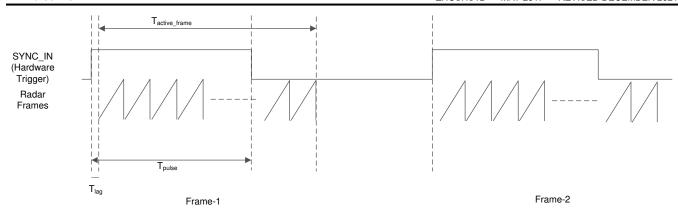

| • | (Synchronized Frame Triggering): Updated the maximum pulse width to 4ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

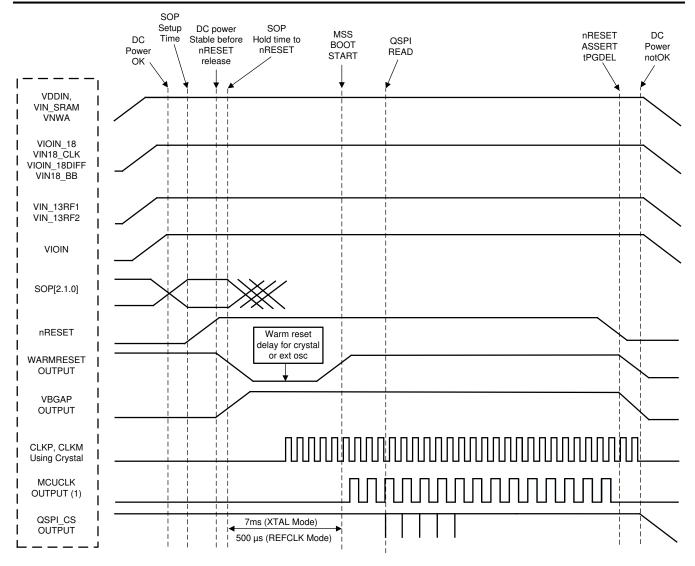

| • | (Clock Specifications): Updated/Changed 表 8-6 to reflect correct device operating temperature range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| • | (Table. External Clock Mode Specifications): Revised frequency tolerance specs from +/-50 to +/-100 ppm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24  |

| • | (Switching Characteristics for Output Timing versus Load Capacitance): Updated/Modified the table to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00  |

|   | remove Slew Rate = 1 condition; removed a footnote                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| • | ☑ 9-1: Updated the figure to remove XA1243FPBGABL OPN specific features.  ✓ Maniferrior and Diagnostic Manhamana.  Added a new particular and Diagnostic Manhamanana.  Added a new particular and Diagnostic Manhamananana.  Added a new particular and Diagnostic Manhamananananananananananananananananana |     |

| • | (Monitoring and Diagnostic Mechanisms): Added a new section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| • | (Reference Schematics): Added weblinks to AWR1243 EVM documentation collateral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| • | (Device Nomenclature):Updated/changed Device Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44  |

# **6 Device Comparison**

| FUNCTION                                     |                                                                  | AWR1243 <sup>(1)</sup> | AWR1443 | AWR1642 | AWR1843          |

|----------------------------------------------|------------------------------------------------------------------|------------------------|---------|---------|------------------|

| Number of receivers                          |                                                                  | 4                      | 4       | 4       | 4                |

| Number of transmitter                        | s                                                                | 3                      | 3       | 2       | 3                |

| On-chip memory                               |                                                                  | _                      | 576KB   | 1.5MB   | 2MB              |

| Max I/F (Intermediate                        | Frequency) (MHz)                                                 | 15                     | 5       | 5       | 10               |

| Max real/complex 2x s                        | sampling rate (Msps)                                             | 37.5                   | 12.5    | 12.5    | 25               |

| Max complex 1x samp                          | oling rate (Msps)                                                | 18.75                  | 6.25    | 6.25    | 12.5             |

| Device Security <sup>(2)</sup>               |                                                                  | _                      | _       | Yes     | Yes              |

| Processor                                    |                                                                  |                        |         |         |                  |

| MCU (R4F)                                    |                                                                  | _                      | Yes     | Yes     | Yes              |

| DSP (C674x)                                  |                                                                  | _                      | _       | Yes     | Yes              |

| Peripherals                                  |                                                                  |                        |         |         |                  |

| Serial Peripheral Inter                      | face (SPI) ports                                                 | 1                      | 1       | 2       | 2                |

| Quad Serial Periphera                        | Il Interface (QSPI)                                              | _                      | Yes     | Yes     | Yes              |

| Inter-Integrated Circui                      | t (I <sup>2</sup> C) interface                                   | _                      | 1       | 1       | 1                |

| Controller Area Netwo                        | rk (DCAN) interface                                              | _                      | Yes     | Yes     | Yes              |

| CAN-FD                                       |                                                                  | _                      | _       | Yes     | Yes              |

| Trace                                        |                                                                  | _                      | _       | Yes     | Yes              |

| PWM                                          |                                                                  | _                      | _       | Yes     | Yes              |

| Hardware In Loop (HII                        | L/DMM)                                                           | _                      | _       | Yes     | Yes              |

| GPADC                                        |                                                                  | _                      | Yes     | Yes     | Yes              |

| LVDS/Debug <sup>(3)</sup>                    |                                                                  | Yes                    | Yes     | Yes     | Yes              |

| CSI2                                         |                                                                  | Yes                    | _       | _       | _                |

| Hardware accelerator                         |                                                                  | _                      | Yes     | _       | Yes              |

| 1-V bypass mode                              |                                                                  | Yes                    | Yes     | Yes     | Yes              |

| Cascade (20-GHz syn                          | ic)                                                              | _                      | _       | _       | _                |

| JTAG                                         |                                                                  | _                      | Yes     | Yes     | Yes              |

| Number of Tx that can be simultaneously used |                                                                  | 2                      | 2       | 2       | 3 <sup>(4)</sup> |

| Per chirp configurable Tx phase shifter      |                                                                  | _                      | _       | _       | Yes              |

| etatus <sup>(5)</sup> ADVAN                  | UCT PREVIEW (PP),<br>NCE INFORMATION (AI),<br>NDUCTION DATA (PD) | PD                     | PD      | PD      | PD               |

<sup>(1)</sup> Developed for Functional Safety applications, the device supports hardware integrity upto ASIL-B. Refer to the related documentation for more details.

<sup>(2)</sup> Device security features including Secure Boot and Customer Programmable Keys are available in select devices for only select part variants as indicated by the Device Type identifier in Section 3, Device Information table.

<sup>(3)</sup> The LVDS interface is not a production interface and is only used for debug.

<sup>(4) 3</sup> Tx Simultaneous operation is supported only in AWR1843 with 1V LDO bypass and PA LDO disable mode. In this mode 1V supply needs to be fed on the VOUT PA pin. Rest of the other devices only support simultaneous operation of 2 Transmitters.

<sup>(5)</sup> PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### **6.1 Related Products**

For information about other devices in this family of products or related products see the links that follow.

mmWave Sensors

TI's mmWave sensors rapidly and accurately sense range, angle and velocity with less power using the smallest footprint mmWave sensor portfolio for automotive applications.

Automotive mmWave Sensors

TI's automotive mmWave sensor portfolio offers high-performance radar front end to ultra-high resolution, small and low-power single-chip radar solutions. TI's scalable sensor portfolio enables design and development of ADAS system solution for every performance, application and sensor configuration ranging from comfort functions to safety functions in all vehicles.

Companion Products for AWR1243

Review products that are frequently purchased or used in conjunction with this product.

# 7 Terminal Configuration and Functions

# 7.1 Pin Diagram

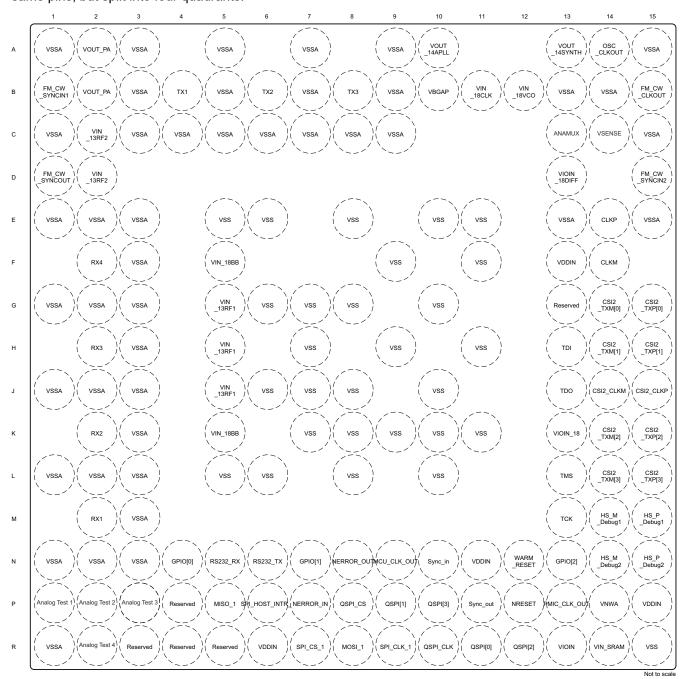

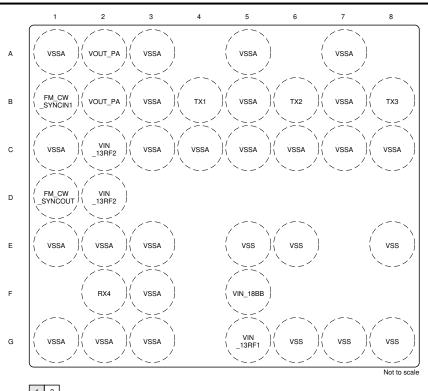

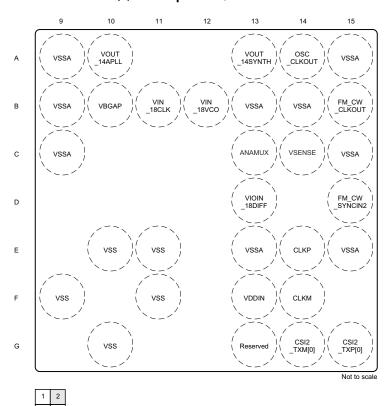

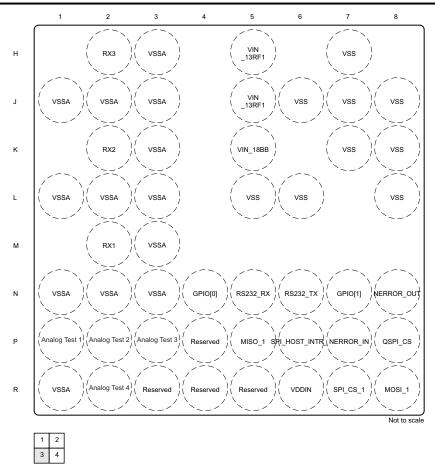

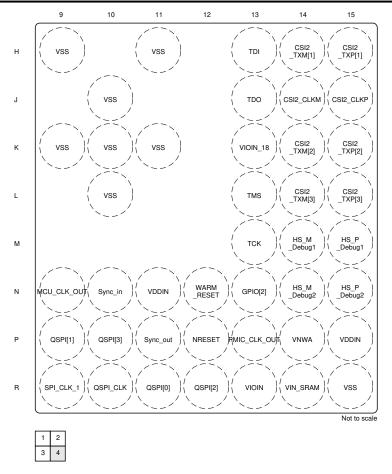

图 7-1 shows the pin locations for the 161-pin FCBGA package. 图 7-2, 图 7-3, 图 7-4, and 图 7-5 show the same pins, but split into four quadrants.

图 7-1. Pin Diagram

图 7-2. Top Left Quadrant

图 7-3. Top Right Quadrant

图 7-4. Bottom Left Quadrant

图 7-5. Bottom Right Quadrant

# 7.2 Signal Descriptions

† 7.2.1 lists the pins by function and describes that function.

□ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function. □ 1.2.1 lists the pins by function and describes that function are the pins by function and describes the pins by functi

## 备注

All IO pins of the device (except NERROR IN, NERROR\_OUT, and WARM\_RESET) are non-failsafe; hence, care needs to be taken that they are not driven externally without the VIO supply being present to the device.

## 7.2.1 Signal Descriptions

| FUNCTION        | SIGNAL NAME   | PIN<br>NUMBER | PIN<br>TYPE | DEFAULT PULL<br>STATUS <sup>(1)</sup> | DESCRIPTION                                                                                                             |

|-----------------|---------------|---------------|-------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|                 | TX1           | B4            | 0           | _                                     | Single-ended transmitter1 o/p                                                                                           |

| Transmitters    | TX2           | B6            | 0           | _                                     | Single-ended transmitter2 o/p                                                                                           |

|                 | TX3           | B8            | 0           | _                                     | Single-ended transmitter3 o/p                                                                                           |

|                 | RX1           | M2            | I           | _                                     | Single-ended receiver1 i/p                                                                                              |

| Receivers       | RX2           | K2            | I           | _                                     | Single-ended receiver2 i/p                                                                                              |

|                 | RX3           | H2            | ı           | _                                     | Single-ended receiver3 i/p                                                                                              |

|                 | RX4           | F2            | ı           | _                                     | Single-ended receiver4 i/p                                                                                              |

|                 | CSI2_TXP[0]   | G15           | 0           | _                                     | Differential data Out - Lane 0 (for CSI and LVDS                                                                        |

|                 | CSI2_TXM[0]   | G14           | 0           | _                                     | debug interface)                                                                                                        |

|                 | CSI2_CLKP     | J15           | 0           | _                                     | Differential clock Out (for CSI and LVDS debug                                                                          |

|                 | CSI2_CLKM     | J14           | 0           | _                                     | interface)                                                                                                              |

|                 | CSI2_TXP[1]   | H15           | 0           | _                                     | Differential data Out - Lane 1 (for CSI and LVDS                                                                        |

|                 | CSI2_TXM[1]   | H14           | 0           | _                                     | debug interface)                                                                                                        |

| CSI2 TX         | CSI2_TXP[2]   | K15           | 0           | _                                     | Differential data Out - Lane 2 (for CSI and LVDS                                                                        |

| C312 1X         | CSI2_TXM[2]   | K14           | 0           | _                                     | debug interface)                                                                                                        |

|                 | CSI2_TXP[3]   | L15           | 0           | _                                     | Differential data Out - Lane 3 (for CSI and LVDS                                                                        |

|                 | CSI2_TXM[3]   | L14           | 0           | _                                     | debug interface)                                                                                                        |

|                 | HS_DEBUG1_P   | M15           | 0           | _                                     | Differential debug port 1 (for LVDS debug interface)                                                                    |

|                 | HS_DEBUG1_M   | M14           | 0           | _                                     | — Differential debug port 1 (for EVD3 debug interface)                                                                  |

|                 | HS_DEBUG2_P   | N15           | 0           | _                                     | Differential debug port 2 (for LVDS debug interface)                                                                    |

|                 | HS_DEBUG2_M   | N14           | 0           | _                                     | — Differential debug port 2 (for EVD3 debug interface)                                                                  |

|                 | FM_CW_CLKOUT  | B15           | 0           |                                       | Pecerved Signal Net applicable in AWP1242                                                                               |

| Reserved        | FM_CW_SYNCOUT | D1            | ]           | _                                     | Reserved Signal. Not applicable in AWR1243.                                                                             |

| Space           | FM_CW_SYNCIN1 | B1            |             |                                       | Reserved Signal. Not applicable in AWR1243.                                                                             |

|                 | FM_CW_SYNCIN2 | D15           | ] '         | _                                     | Reserved Signal. Not applicable III AWK 1243.                                                                           |

| Reference clock | OSC_CLKOUT    | A14           | 0           | _                                     | Reference clock output from clocking subsystem after cleanup PLL. Can be used by peripheral chip in multichip cascading |

| System          | SYNC_OUT      | P11           | 0           | Pull Down                             | Low-frequency frame synchronization signal output. Can be used by peripheral chip in multichip cascading                |

| synchronization | SYNC_IN       | N10           | ı           | Pull Down                             | Low-frequency frame synchronization signal input. This signal could also be used as a hardware trigger for frame start  |

www.ti.com.cn

| FUNCTION            | SIGNAL NAME               | PIN<br>NUMBER     | PIN<br>TYPE | DEFAULT PULL<br>STATUS <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                   |

|---------------------|---------------------------|-------------------|-------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI control         | SPI_CS_1                  | R7                | I           | Pull Up                               | SPI chip select                                                                                                                                                                               |

| interface from      | SPI_CLK_1                 | R9                | ı           | Pull Down                             | SPI clock                                                                                                                                                                                     |

| peripheral          | MOSI_1                    | R8                | I           | Pull Up                               | SPI data input                                                                                                                                                                                |

|                     | MISO_1                    | P5                | 0           | Pull Up                               | SPI data output                                                                                                                                                                               |

| mode)               | SPI_HOST_INTR_1           | P6                | 0           | Pull Down                             | SPI interrupt to host                                                                                                                                                                         |

|                     | RESERVED                  | R3, R4, R5,<br>P4 |             | _                                     |                                                                                                                                                                                               |

|                     | NRESET                    | P12               | I           | _                                     | Power on reset for chip. Active low                                                                                                                                                           |

| Reset               | WARM_RESET <sup>(2)</sup> | N12               | Ю           | Open Drain                            | Open-drain fail-safe warm reset signal. Can be driven from PMIC for diagnostic or can be used as status signal that the device is going through reset.                                        |

|                     | SOP2                      | P13               | ı           |                                       | The SOP pins are driven externally (weak drive) and                                                                                                                                           |

| Sense on Power      | SOP1                      | P11               | ı           | _                                     | the AWR device senses the state of these pins during bootup to decide the bootup mode. After boot                                                                                             |

|                     | SOP0                      | J13               | I           |                                       | the same pins have other functionality.  [SOP2 SOP1 SOP0] = [0 0 1] → Functional SPI mode  [SOP2 SOP1 SOP0] = [1 0 1] → Flashing mode  [SOP2 SOP1 SOP0] = [0 1 1] → debug mode                |

| Cafaba              | NERROR_OUT                | N8                | 0           | Open Drain                            | Open-drain fail-safe output signal. Connected to PMIC/Processor/MCU to indicate that some severe criticality fault has happened. Recovery would be through reset.                             |

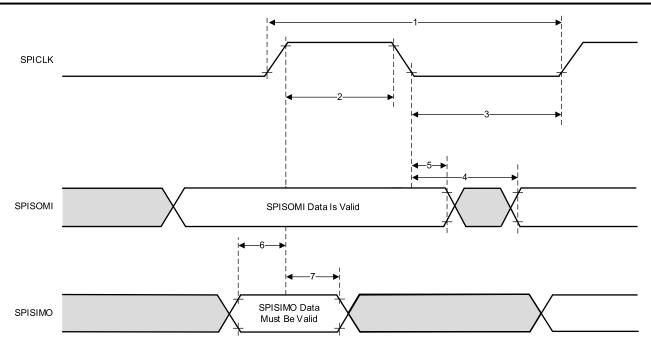

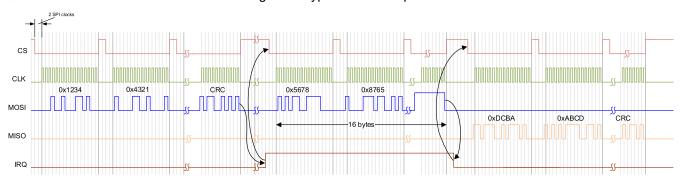

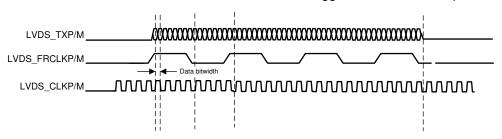

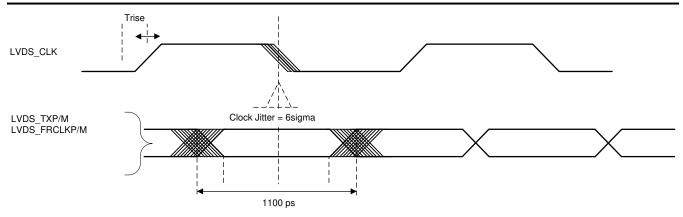

| Safety              | NERROR_IN                 | P7                | I           | Open Drain                            | Fail-safe input to the device. Error output from any other device can be concentrated in the error signaling monitor module inside the device and appropriate action can be taken by firmware |