DAC81404, DAC61404

# ZHCSLN8A - NOVEMBER 2020 - REVISED MAY 2021 具有内部基准的 DACx1404 四路 16 位和 12 位高压输出 DAC

### 1 特性

性能:

- 在 16 位分辨率下具有单调性

- INL: 16 位分辨率下为 ±1LSB(最大值)

- TUE: ±0.05% FSR(最大值)

集成输出缓冲器

满量程输出电压:±5V、±10V、±20V、5V、

10V、20V、40V - 高驱动能力: ±15mA

- 每通道检测引脚

• 集成 2.5V 精密基准

- 初始精度: ±2.5mV(最大值)

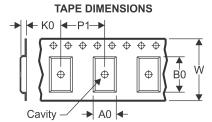

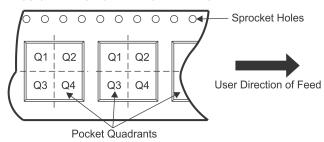

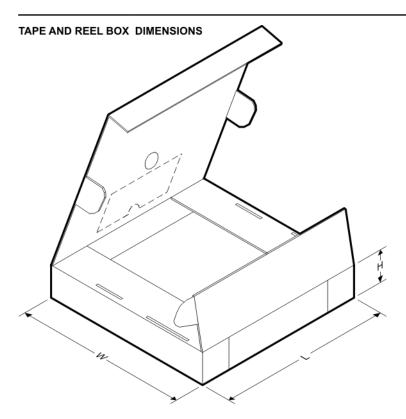

- 低漂移:10ppm/°C(最大值)

可靠性特性:

- CRC 误差校验

- 短路保护

- 故障引脚

50MHz SPI 兼容型串行接口

- 4 线制模式,工作电压为 1.7V 至 5.5V

- 回读和菊链运行方式

• 温度范围: - 40°C 至 +125°C

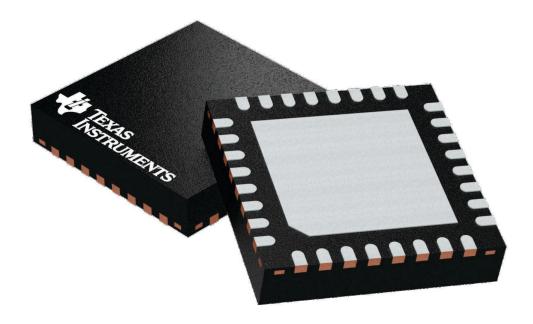

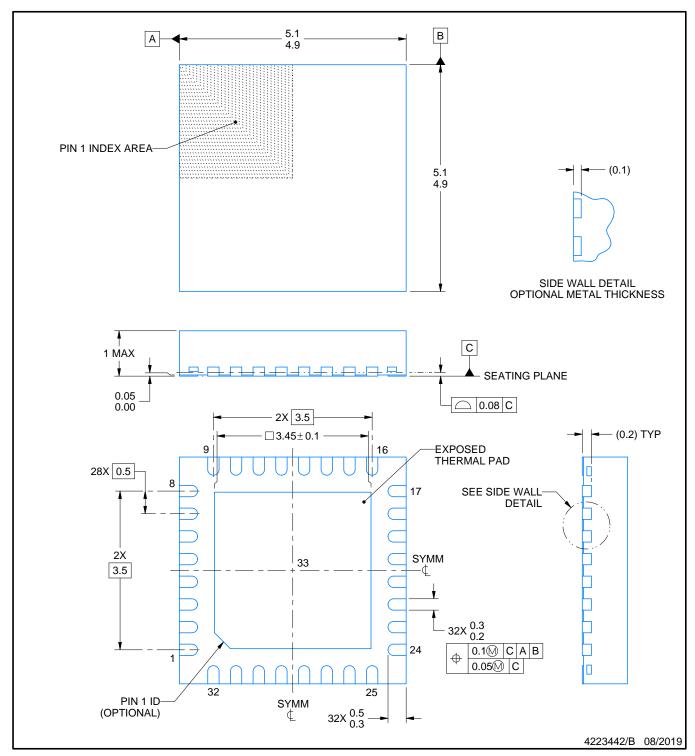

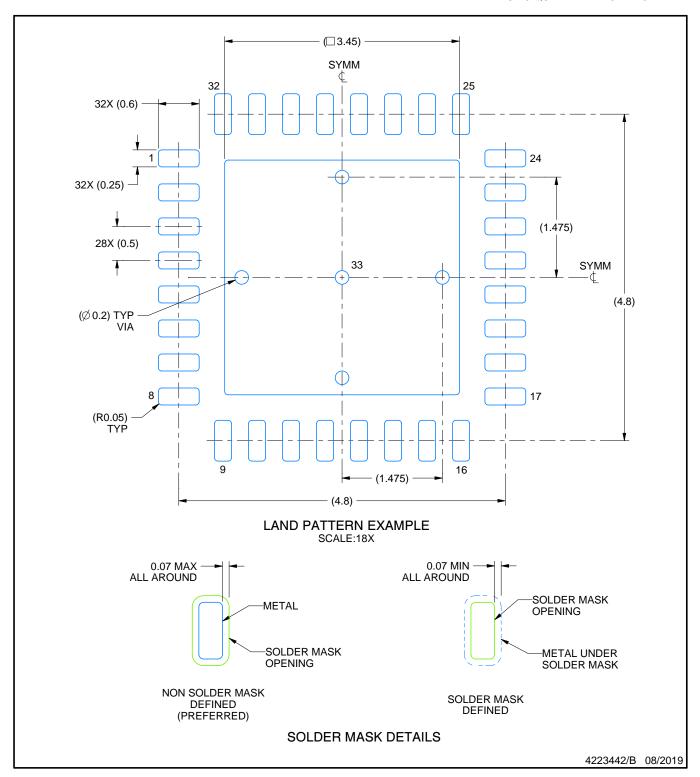

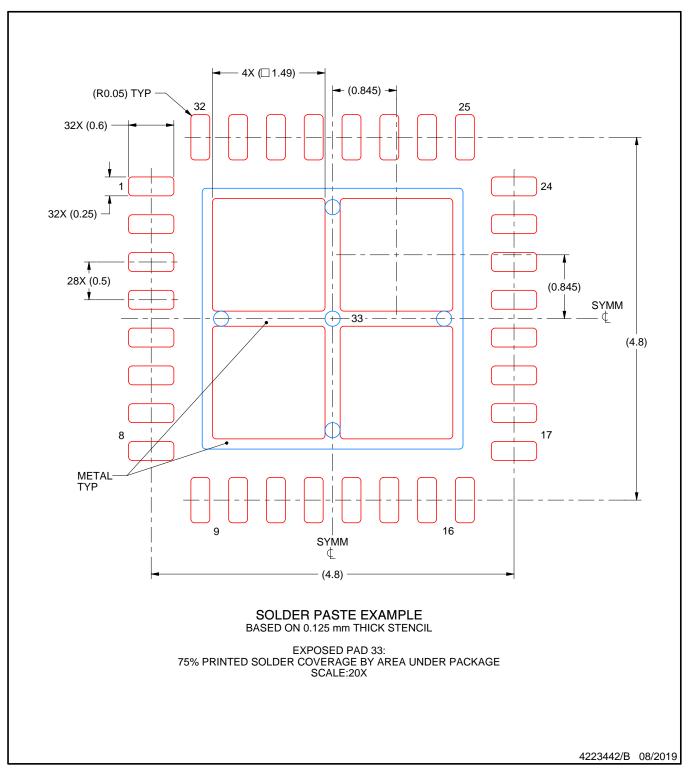

• 封装:5mm×5mm 32 引脚 QFN

#### 2 应用

- 半导体测试

- 实验室和现场仪表

- 模拟输出模块

- 数据采集 (DAQ)

- LCD 测试

- 伺服驱动器控制模块

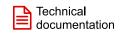

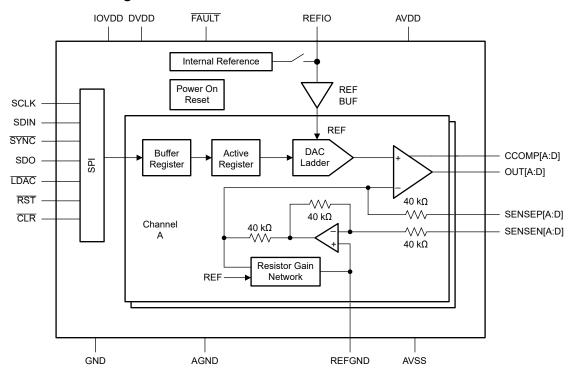

功能方框图

# 3 说明

16 位 DAC81404 和 12 位 DAC61404 (DACx1404) 是 引脚兼容的四通道缓冲式高压输出数模转换器 (DAC)。这些器件包括一个低漂移 2.5V 内部电压基 准,因此在大多数应用中无需使用外部精密基准。这些 器件具有单调性,并能提供 ±1LSB INL 的高线性度。 此外,这些器件采用每通道检测引脚来消除 IR 压降并 可检测高达 ±12V 的地弹。

用户可自行选择输出配置,包括满量程双极输出电压 ±20V、±10V 和 ±5V,以及满量程非双极输出电压 40V、20V、10V 和 5V。而且,每个 DAC 通道的满量 程输出范围都是独立可编程的。集成的 DAC 输出缓冲 器可实现高达 15mA 的灌电流或拉电流,从而减少了 对额外的运算放大器的需求。

DACx1404 包含的上电复位电路可在上电时将 DAC 输 出端连接至接地端。输出端会保持该模式,直至器件得 到适当的运行配置。这些器件还包括其他可靠性特性, 例如 CRC 误差校验、短路保护以及过热报警。

通过一个支持 1.7V 至 5.5V 工作电压的 4 线制串行接 口,支持器件间通信。

#### 器件信息

| 器件型号     | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |

|----------|-------------------|-----------------|

| DAC81404 | VQFN (32)         | 5.00mm × 5.00mm |

| DAC61404 | VQ1 14 (32)       | 3.00mm ^ 3.00mm |

如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

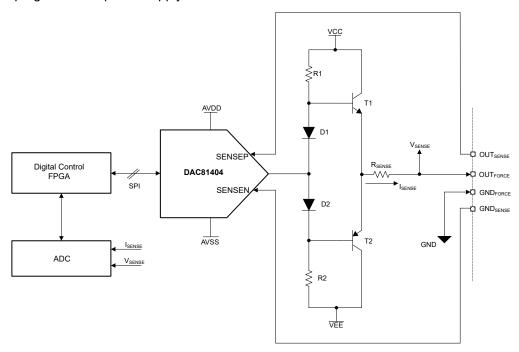

大电流驱动 (1A) 应用

# **Table of Contents**

| 1 特性                                                             | 7.13 Typical Characteristics            | 1              |

|------------------------------------------------------------------|-----------------------------------------|----------------|

| 2 应用                                                             | 8 Detailed Description                  |                |

| 3 说明                                                             | 8.1 Overview                            |                |

| 4 Revision History                                               | 8.2 Functional Block Diagram            | 2              |

| 5 Device Comparison Table                                        | 8.3 Feature Description                 | 20             |

| 6 Pin Configuration and Functions                                | 8.4 Device Functional Modes             |                |

| 7 Specifications                                                 | 8.5 Programming                         | 3 <sup>.</sup> |

| 7.1 Absolute Maximum Ratings5                                    | 8.6 Register Map                        |                |

| 7.2 ESD Ratings5                                                 | 9 Application and Implementation        | 4              |

| 7.3 Recommended Operating Conditions6                            | 9.1 Application Information             | 4              |

| 7.4 Thermal Information6                                         | 9.2 Typical Application                 | 4 <sup>2</sup> |

| 7.5 Electrical Characteristics7                                  | 10 Power Supply Recommendations         | 43             |

| 7.6 Timing Requirements: Write, IOV <sub>DD</sub> : 1.7 V to 2.7 | 11 Layout                               | 43             |

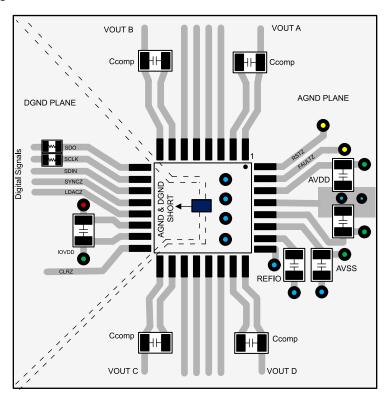

| V                                                                | 11.1 Layout Guidelines                  | 43             |

| 7.7 Timing Requirements: Write, IOV <sub>DD</sub> : 2.7 V to 5.5 | 11.2 Layout Example                     | 43             |

| V                                                                | 12 Device and Documentation Support     | 4              |

| 7.8 Timing Requirements: Read and Daisy Chain,                   | 12.1 Documentation Support              | 4              |

| FSDO = 0, IOV <sub>DD</sub> : 1.7 V to 2.7 V                     | 12.2 接收文档更新通知                           | 4              |

| 7.9 Timing Requirements: Read and Daisy Chain,                   | 12.3 支持资源                               | 4              |

| FSDO = 1, IOV <sub>DD</sub> : 1.7 V to 2.7 V                     | 12.4 Trademarks                         | 4              |

| 7.10 Timing Requirements: Read and Daisy Chain,                  | 12.5 Electrostatic Discharge Caution    | 4              |

| FSDO = 0, IOV <sub>DD</sub> : 2.7 V to 5.5 V                     | 12.6 Glossary                           | 4              |

| 7.11 Timing Requirements: Read and Daisy Chain,                  | 13 Mechanical, Packaging, and Orderable |                |

| FSDO = 1, IOV <sub>DD</sub> : 2.7 V to 5.5 V                     | Information                             | 4              |

| 7.12 Timing Diagrams                                             |                                         |                |

|                                                                  |                                         |                |

|                                                                  |                                         |                |

|                                                                  |                                         |                |

# **4 Revision History**

| CI | anges from Revision * (November 2020) to Revision A (May 2021) | Page |

|----|----------------------------------------------------------------|------|

| •  | 添加了 DAC61404 和相关内容                                             | 1    |

# **5 Device Comparison Table**

| DEVICE   | RESOLUTION |

|----------|------------|

| DAC81404 | 16-bit     |

| DAC61404 | 12-bit     |

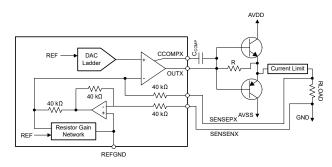

# **6 Pin Configuration and Functions**

图 6-1. RHB (32-pin VQFN) Package, Top View

表 6-1. Pin Functions

|     | PIN     | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                  |

|-----|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME    | ITPE   | DESCRIPTION                                                                                                                                                                                                                                                                  |

| 1   | OUTA    | Output | Channel-A analog output voltage.                                                                                                                                                                                                                                             |

| 2   | ССОМРА  | Input  | Channel-A external compensation capacitor connection.  The addition of an external capacitor improves the output buffer stability with high capacitive loads at the OUTA pin by reducing the bandwidth of the output amplifier at the expense of increased settling time.    |

| 3   | SENSEPA | Input  | Channel-A sense pin for the positive voltage output load connection.                                                                                                                                                                                                         |

| 4   | SENSENA | Input  | Channel-A sense pin for the negative voltage output load connection.                                                                                                                                                                                                         |

| 5   | SENSENB | Input  | Channel-B sense pin for the negative voltage output load connection.                                                                                                                                                                                                         |

| 6   | SENSEPB | Input  | Channel-B sense pin for the positive voltage output load connection.                                                                                                                                                                                                         |

| 7   | ССОМРВ  | Input  | Channel-B external compensation capacitor connection pin. The addition of an external capacitor improves the output buffer stability with high capacitive loads at the OUTB pin by reducing the bandwidth of the output amplifier at the expense of increased settling time. |

| 8   | OUTB    | Output | Channel-B analog output voltage.                                                                                                                                                                                                                                             |

| 9   | SDO     | Output | Serial interface data output. The SDO pin must be enabled before operation by setting the SDO-EN bit. Data are clocked out of the input shift register on either rising or falling edges of the SCLK pin as specified by the FSDO bit (rising edge by default).              |

# 表 6-1. Pin Functions (continued)

|                | PIN         | TVDE         | DESCRIPTION                                                                                                                                                                                                                                                                   |  |

|----------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.            | NAME        | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                   |  |

| 10             | SCLK        | Input        | Serial interface clock.                                                                                                                                                                                                                                                       |  |

| 11             | SDIN        | Input        | Serial interface data input. Data are clocked into the input shift register on each falling edge of the SCLK pin.                                                                                                                                                             |  |

| 12             | SYNC        | Input        | Active low serial data enable. This input is the frame synchronization signal for the serial data. The serial interface input shift register is enabled when SYNC is low.                                                                                                     |  |

| 13             | LDAC        | Input        | Active low synchronization signal. The DAC outputs of those channels configured in synchronous mode are updated simultaneously when the $\overline{\text{LDAC}}$ pin is low. Connect to IOVDD if unused.                                                                      |  |

| 14             | GND         | Ground       | ground reference point.                                                                                                                                                                                                                                                       |  |

| 15             | IOVDD       | Power        | IO supply voltage. This pin sets the digital I/O operating voltage for the device.                                                                                                                                                                                            |  |

| 16             | CLR         | Input        | Active-low clear input. Logic low on this pin clears all outputs to their clear code. Connect to IOVDD if unused.                                                                                                                                                             |  |

| 17             | OUTC        | Output       | Channel-C analog output voltage.                                                                                                                                                                                                                                              |  |

| 18             | CCOMPC      | Input        | Channel-C external compensation capacitor connection pin.  The addition of an external capacitor improves the output buffer stability with high capacitive loads at the OUTC pin by reducing the bandwidth of the output amplifier at the expense of increased settling time. |  |

| 19             | SENSEPC     | Input        | Channel-C sense pin for the positive voltage output load connection.                                                                                                                                                                                                          |  |

| 20             | SENSENC     | Input        | Channel-C sense pin for the negative voltage output load connection.                                                                                                                                                                                                          |  |

| 21             | SENSEND     | Input        | Channel-D sense pin for the negative voltage output load connection.                                                                                                                                                                                                          |  |

| 22             | SENSEPD     | Input        | Channel-D sense pin for the positive voltage output load connection.                                                                                                                                                                                                          |  |

| 23             | CCOMPD      | Input        | Channel-D external compensation capacitor connection pin. The addition of an external capacitor improves the output buffer stability with high capacitive loads at the OUTD pin by reducing the bandwidth of the output amplifier at the expense of increased settling time.  |  |

| 24             | OUTD        | Output       | Channel-D analog output voltage.                                                                                                                                                                                                                                              |  |

| 25             | REFGND      | Ground       | Ground reference point for the internal reference.                                                                                                                                                                                                                            |  |

| 26             | REFIO       | Input/Output | Reference input to the device when operating with an external reference. Reference output voltage pin when using the internal reference. Connect a 150-nF capacitor to ground.                                                                                                |  |

| 27             | AVSS        | Power        | Output buffers negative supply voltage.                                                                                                                                                                                                                                       |  |

| 28             | AVDD        | Power        | Output buffers positive supply voltage.                                                                                                                                                                                                                                       |  |

| 29             | AGND        | Ground       | Analog ground reference point.                                                                                                                                                                                                                                                |  |

| 30             | DVDD        | Power        | Digital and analog supply voltage.                                                                                                                                                                                                                                            |  |

| 31             | FAULT       | Output       | $\overline{\text{FAULT}}$ is an open-drain, fault-condition output. An external 10-k $\Omega$ pullup resistor to a voltage no higher than $\text{IOV}_{\text{DD}}$ is required.                                                                                               |  |

| 32             | RST         | Input        | Active-low reset input. Logic low on this pin causes the device to issue a power-on-reset event.                                                                                                                                                                              |  |

| Thermal<br>Pad | Thermal pad | _            | The thermal pad is located on the package underside. The thermal pad should be connected to any internal PCB ground plane through multiple vias for good thermal performance.                                                                                                 |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                      | ,                                    | MIN                    | MAX                     | UNIT |

|------------------|----------------------|--------------------------------------|------------------------|-------------------------|------|

|                  |                      | DV <sub>DD</sub> to GND              | - 0.3                  | 6                       |      |

|                  |                      | IOV <sub>DD</sub> to GND             | - 0.3                  | 6                       |      |

|                  | Supply voltage       | AV <sub>DD</sub> to GND              | - 0.3                  | 44                      | V    |

|                  |                      | AV <sub>SS</sub> to GND              | - 22                   | 0.3                     |      |

|                  |                      | AV <sub>DD</sub> to AV <sub>SS</sub> | - 0.3                  | 44                      | 3 3  |

|                  |                      | V <sub>OUTX</sub> to GND             | AV <sub>SS</sub> - 0.3 | AV <sub>DD</sub> + 0.3  |      |

|                  |                      | V <sub>SENSEPX</sub> to GND          | AV <sub>SS</sub> - 0.3 | AV <sub>DD</sub> + 0.3  |      |

|                  |                      | V <sub>SENSENX</sub> to GND          | AV <sub>SS</sub> - 0.3 | AV <sub>DD</sub> + 0.3  |      |

|                  | Din voltage          | V <sub>REFIO</sub> to GND            | - 0.3                  | DV <sub>DD</sub> + 0.3  | V    |

|                  | Pin voltage          | V <sub>REFGND</sub> to GND           | - 0.3                  | +0.3                    | V    |

|                  |                      | Digital inputs to GND                | - 0.3                  | IOV <sub>DD</sub> + 0.3 |      |

|                  |                      | SDO to GND                           | - 0.3                  | IOV <sub>DD</sub> + 0.3 |      |

|                  |                      | FAULT to GND                         | - 0.3                  | 6                       |      |

|                  | Input current        | Current into any digital pin         | - 10                   | 10                      | mA   |

| TJ               | Junction temperature | 9                                    | - 40                   | 150                     | °C   |

| T <sub>stg</sub> | Storage temperature  |                                      | - 60                   | 150                     | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 7.2 ESD Ratings

|                    |                          |                                                                                | VALUE | UNIT |

|--------------------|--------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Cleatra static disabarga | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001 <sup>(1)</sup>          | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                   |                                      | MIN    | NOM MAX | UNIT |

|----------------|-------------------|--------------------------------------|--------|---------|------|

|                |                   | DV <sub>DD</sub> to GND              | 4.5    | 5.5     |      |

|                |                   | IOV <sub>DD</sub> to GND             | 1.7    | 5.5     |      |

|                | Supply voltage    | AV <sub>DD</sub> to GND              | 4.5    | 41.5    | V    |

|                |                   | AV <sub>SS</sub> to GND              | - 21.5 | 0       |      |

|                |                   | AV <sub>DD</sub> to AV <sub>SS</sub> | 4.5    | 43      |      |

|                | Pin voltage       | V <sub>SENSENX</sub> to GND          | - 12   | 12      | V    |

| T <sub>A</sub> | Ambient temperatu | re                                   | - 40   | 125     | °C   |

### 7.4 Thermal Information

|                        |                                              | DACx1404   |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN) | UNIT |

|                        |                                              | 32 PINS    |      |

| R <sub>⊕JA</sub>       | Junction-to-ambient thermal resistance       | 29.3       | °C/W |

| R <sub>⊕ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 17.0       | °C/W |

| R <sub>⊕JB</sub>       | Junction-to-board thermal resistance         | 9.5        | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.2        | °C/W |

| Ψ ЈВ                   | Junction-to-board characterization parameter | 9.5        | °C/W |

| R <sub>⊙ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

all minimum/maximum specifications at  $T_A$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C and all typical specifications at  $T_A$  = 25 $^{\circ}$ C, AV<sub>DD</sub> = 4.5 V to 41.5 V, AV<sub>SS</sub> = -21.5 V to 0 V, DV<sub>DD</sub> = 5.0 V, internal reference enabled, IOV<sub>DD</sub> = 1.7 V, V<sub>SENSEN</sub>X = 0 V, C<sub>COMP</sub>X floating, DAC outputs unloaded, and digital inputs at IOV<sub>DD</sub> or GND (unless otherwise noted)

|          | PARAMETER                                                     | TEST CONDITIONS                                                                                                                  | MIN    | TYP | MAX  | UNIT             |

|----------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------|-----|------|------------------|

| STATIC F | PERFORMANCE                                                   |                                                                                                                                  |        |     |      |                  |

|          | Pacelution                                                    | DAC81404                                                                                                                         | 16     |     |      | Dito             |

|          | Resolution                                                    | DAC61404                                                                                                                         | 12     |     |      | Bits             |

| INL      |                                                               | DAC81404. All ranges, except 0-V to 40-V and overranges                                                                          | - 1    |     | 1    |                  |

|          | Relative accuracy <sup>(1)</sup>                              | DAC81404. 0-V to 40-V range                                                                                                      | - 2    |     | 2    | LSB              |

|          |                                                               | DAC61404                                                                                                                         | - 1    |     | 1    |                  |

| DNL      | Differential nonlinearity <sup>(1)</sup>                      |                                                                                                                                  | - 1    |     | 1    | LSB              |

|          |                                                               | Unipolar ranges, AV <sub>SS</sub> = 0 V                                                                                          | - 0.07 |     | 0.07 |                  |

| TUE      | Total unadjusted error <sup>(1)</sup>                         | Unipolar ranges, AV <sub>SS</sub> = 0 V, $0^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ 50°                                          | - 0.05 |     | 0.05 | %FSR             |

|          |                                                               | Bipolar ranges, −21.5 V ≤ AV <sub>SS</sub> < 0 V                                                                                 | - 0.05 |     | 0.05 |                  |

|          | Offset error <sup>(1)</sup>                                   | Unipolar ranges, AV <sub>SS</sub> = 0 V<br>Bipolar ranges, −21.5 V ≤ AV <sub>SS</sub> < 0<br>V                                   | - 0.05 |     | 0.05 | %FSR             |

|          | Offset error temperature coefficient                          | Unipolar ranges, AV <sub>SS</sub> = 0 V<br>Bipolar ranges, −21.5 V ≤ AV <sub>SS</sub> < 0<br>V                                   |        | ±2  |      | ppmFSR/°C        |

|          |                                                               | All unipolar ranges, AV <sub>SS</sub> = 0 V                                                                                      |        |     | 0.15 |                  |

|          | Zero-code (negative full scale) error                         | All bipolar ranges,<br>- 21.5 V ≤ AV <sub>SS</sub> < 0 V                                                                         |        |     | 0.05 | %FSR             |

|          | Zero-code (negative full scale) error temperature coefficient | All unipolar ranges, AV <sub>SS</sub> = 0 V<br>All bipolar ranges,<br>$-21.5 \text{ V} \leq \text{AV}_{\text{SS}} < 0 \text{ V}$ |        | ±2  |      | ppm of<br>FSR/°C |

|          | Full-scale error <sup>(2)</sup>                               |                                                                                                                                  | - 0.06 |     | 0.06 | %FSR             |

|          | Full-scale error temperature coefficient <sup>(2)</sup>       |                                                                                                                                  |        | ±3  |      | ppm of<br>FSR/°C |

|          | Gain error <sup>(1)</sup>                                     |                                                                                                                                  | - 0.06 |     | 0.06 | %FSR             |

|          | Gain error temperature coefficient                            |                                                                                                                                  |        | ±2  |      | ppm of<br>FSR/°C |

|          | Bipolar-zero (midscale) error                                 | All bipolar ranges,<br>- 21.5 V ≤ AV <sub>SS</sub> < 0 V                                                                         | - 0.03 |     | 0.03 | %FSR             |

|          | Bipolar-zero (midscale) error temperature coefficient         | All bipolar ranges,<br>- 21.5 V ≤ AV <sub>SS</sub> < 0 V                                                                         |        | ±2  |      | ppm of<br>FSR/°C |

|          | Output voltage drift over time                                | T <sub>A</sub> = 40°C, DAC code = full scale,<br>1000 hours                                                                      |        | ±6  |      | ppm FSR          |

|        | PARAMETER                               | TEST CONDITIONS                                                                                                                | MIN  | TYP  | MAX | UNIT                |  |

|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|-----|---------------------|--|

| OUTPUT | CHARACTERISTICS                         |                                                                                                                                |      |      |     |                     |  |

|        |                                         |                                                                                                                                | 0    |      | 5   |                     |  |

|        |                                         | 20% overrange                                                                                                                  | 0    |      | 6   |                     |  |

|        |                                         |                                                                                                                                | 0    | ,    | 10  |                     |  |

|        |                                         | 20% overrange                                                                                                                  | 0    |      | 12  |                     |  |

|        |                                         |                                                                                                                                | 0    |      | 20  |                     |  |

|        |                                         | 20% overrange                                                                                                                  | 0    |      | 24  |                     |  |

| VouT   | Output voltage                          |                                                                                                                                | 0    |      | 40  | V                   |  |

|        |                                         |                                                                                                                                | -5   |      | 5   |                     |  |

|        |                                         | 20% overrange                                                                                                                  | -6   |      | 6   |                     |  |

|        |                                         |                                                                                                                                | - 10 | ,    | 10  |                     |  |

|        |                                         | 20% overrange                                                                                                                  | - 12 |      | 12  |                     |  |

|        |                                         |                                                                                                                                | - 20 |      | 20  |                     |  |

|        |                                         | to AV <sub>SS</sub> and AV <sub>DD</sub> $-10 \text{ mA} \leqslant \text{load current} \leqslant 10 \text{ mA}$                | 1.25 |      |     |                     |  |

|        | Output voltage headroom and footroom    | to AV <sub>SS</sub> and AV <sub>DD</sub> , $5.5~V < AV_{DD} \leqslant 41.5~V,$ $-15~mA \leqslant load~current \leqslant 15~mA$ | 1.5  |      |     | V                   |  |

|        |                                         | Full-scale output shorted to AV <sub>SS</sub>                                                                                  |      | 40   |     |                     |  |

|        | Short circuit current <sup>(3)</sup>    | Zero-scale output shorted to AV <sub>DD</sub> , $5.5 \text{ V} < \text{AV}_{\text{DD}} \leqslant 41.5 \text{ V},$              |      | 40   |     | mA                  |  |

|        |                                         | Zero-scale output shorted to AV <sub>DD</sub> , 4.5 V $\leq$ AV <sub>DD</sub> $\leq$ 5.5 V                                     |      | 25   |     |                     |  |

|        | Load regulation                         | DAC at midscale,<br>-15 mA ≤ load current ≤ 15 mA                                                                              |      | 50   |     | μV/mA               |  |

|        |                                         | R <sub>LOAD</sub> = open, C <sub>COMPX</sub> pin left floating                                                                 | 0    |      | 2   | nF                  |  |

| CL     | Capacitive load <sup>(4)</sup>          | R <sub>LOAD</sub> = open,<br>C <sub>COMPX</sub> = 500 pF ± 10% to V <sub>OUTX</sub>                                            |      |      | 1   | μF                  |  |

|        | 1 1                                     | 5.5 V < AV <sub>DD</sub> ≤ 41.5 V                                                                                              |      |      | 15  | A                   |  |

|        | Load current <sup>(4)</sup>             | $4.5 \text{ V} \leqslant \text{AV}_{\text{DD}} \leqslant 5.5 \text{ V}$                                                        |      |      | 10  | mA                  |  |

|        |                                         | DAC code at midscale, DAC unloaded                                                                                             |      | 0.05 |     |                     |  |

|        | V <sub>OUT</sub> dc output impedance    | DAC code at full scale, DAC unloaded                                                                                           |      | 0.05 |     | Ω                   |  |

|        | VOUT do output impedance                | DAC code at negative full scale,<br>DAC unloaded                                                                               |      | 25   |     | 52                  |  |

|        |                                         | DAC code at midscale, 10-V span                                                                                                |      | 55   |     | , -                 |  |

|        | V <sub>SENSEP</sub> dc output impedance | DAC disabled                                                                                                                   |      | 45   |     | $\mathbf{k} \Omega$ |  |

|        |                                         | DAC code at midscale, 10-V span                                                                                                |      | 45   |     |                     |  |

|        | V <sub>SENSEN</sub> dc output impedance | DAC disabled                                                                                                                   |      | 45   |     | $\mathbf{k} \Omega$ |  |

|          | PARAMETER                       | DV <sub>DD</sub> or GND (unless otherwise noted)  TEST CONDITIONS                                                                                                                                          | MIN TYP | MAX | UNIT                 |

|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|----------------------|

| YNAMIC P | ERFORMANCE                      |                                                                                                                                                                                                            |         |     |                      |

|          |                                 | 5-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to ±2 LSB                                                                                                                                   | 7       |     |                      |

|          | 1<br>2<br>1<br>4<br>1           | 10-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to ±2 LSB                                                                                                                                  | 8       |     | μs                   |

|          |                                 | 20-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to ±2 LSB                                                                                                                                  | 12      |     | μο                   |

|          |                                 | 40-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to ±2 LSB                                                                                                                                  | 22      |     |                      |

|          | Output voltage settling time    | 5-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to $\pm 2$ LSB, $C_L = 1 \ \mu F$ , $C_{COMPX} = 500 \ pF$ to $V_{OUTX}$                                                                    | 0.6     |     |                      |

|          |                                 | 10-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to ±2 LSB, C <sub>L</sub> = 1 μF, C <sub>COMPX</sub> = 500 pF to V <sub>OUTX</sub>                                                         | 0.6     |     | me                   |

|          |                                 | 20-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to ±2 LSB, C <sub>L</sub> = 1 μF, C <sub>COMPX</sub> = 500 pF to V <sub>OUTX</sub>                                                         | 0.6     |     | ms                   |

|          |                                 | 40-V span, 1/4 to 3/4 scale and 3/4 to 1/4 scale, settling time to $\pm 2$ LSB, $C_L = 1 \ \mu F$ , $C_{COMPX} = 500 \ pF$ to $V_{OUTX}$                                                                   | 1.2     |     |                      |

|          |                                 | 0-V to 5-V range (10% to 90% of full-scale range)                                                                                                                                                          | 0.8     |     |                      |

|          | Claus rata                      | All other output ranges except 40-V span (10% to 90% of full-scale range)                                                                                                                                  | 4       |     | \//ua                |

|          | Slew rate                       | 0-V to 5-V range, $C_L = 1 \mu F$ ,<br>$C_{COMPX} = 500 \text{ pF to V}_{OUTX}$                                                                                                                            | 0.04    |     | V/µs                 |

|          |                                 | All other ranges, $C_L = 1 \mu F$ , $C_{COMPX} = 500 \text{ pF to } V_{OUTX}$                                                                                                                              | 0.04    |     |                      |

|          | Power-on glitch magnitude       | AV <sub>SS</sub> and AV <sub>DD</sub> ramped symmetrically, ramp rate = 18 V/ms, output unloaded, internal reference                                                                                       | 0.1     |     | ٧                    |

|          | Output enable glitch magnitude  | AV <sub>SS</sub> and AV <sub>DD</sub> ramped, output unloaded, internal reference, gain = 1x                                                                                                               | 0.35    |     | V                    |

|          | Output noise                    | 0.1 Hz to 10 Hz, DAC code at midscale, 5-V span, external reference = 2.5 V, output unloaded                                                                                                               | 25      |     | $\mu V_{PP}$         |

|          | - Culput Holde                  | 0.1 Hz to 10 Hz, DAC code at midscale, 5-V span, internal reference = 2.5 V, output unloaded                                                                                                               | 30      |     | <u>₩</u> <b>v</b> PP |

|          | Output noise density            | 1 kHz, DAC code at midscale, 5-V span, output unloaded, external reference                                                                                                                                 | 115     |     | nV/√ <del>H</del> ;  |

|          | Output noise delisity           | 10 kHz, DAC code at midscale, 5-V span, output unloaded, external reference                                                                                                                                | 105     |     | IIV/ √ HZ            |

| HD       | Total harmonic distortion       | 1-kHz sine wave on V <sub>OUTX</sub> , output unloaded, DAC update rate = 400 kHz                                                                                                                          | 88      |     | dB                   |

| SRR-AC   | Power supply ac rejection ratio | V <sub>OUTX</sub> = 0 V (midscale), output<br>unloaded, ±10-V output,<br>frequency = 60 Hz,<br>amplitude 200 mV <sub>PP</sub> ,<br>superimposed on AV <sub>DD</sub> , DV <sub>DD</sub> or AV <sub>SS</sub> | 75      |     | dB                   |

| PARAMETER |                                 | TEST CONDITIONS                                                                                                                 | MIN T | YP MAX | UNIT |

|-----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|--------|------|

|           |                                 | $V_{OUTX}$ = 0 V (midscale), ±10-V output,<br>$DV_{DD}$ = 5 V, $AV_{DD}$ = 15 V ± 20%,<br>$AV_{SS}$ = -15 V, output unloaded    |       | 5      |      |

| PSRR-DC   | Power supply dc rejection ratio | $V_{OUTX}$ = 0 V (midscale), ±10-V output,<br>$DV_{DD}$ = 5 V, $AV_{DD}$ = 15 V,<br>$AV_{SS}$ = -15 V ± 20%, output<br>unloaded |       | 10     | μV/V |

|           |                                 | $V_{OUTX}$ = 0 V (midscale), ±10-V output,<br>$DV_{DD}$ = 5 V ± 5%, $AV_{DD}$ = 15 V,<br>$AV_{SS}$ = -15 V, output unloaded     |       | 0.2    | mV/V |

|           |                                 | 1-LSB change around midscale,<br>0-V to 5-V range, output unloaded                                                              |       | 1      |      |

|           | Code change glitch impulse      | 1-LSB change around midscale,<br>0-V to 10-V range, output unloaded                                                             |       | 2      |      |

|           |                                 | 1-LSB change around midscale, - 5-V to +5-V range, output unloaded                                                              |       | 2      | nV-s |

|           |                                 | 1-LSB change around midscale, - 10-V to +10-V range, output unloaded                                                            |       | 4      |      |

|           | Code change glitch amplitude    | 1-LSB change around midscale,<br>0-V to 5-V, 0-V to 10-V, - 5-V to +5-V<br>and - 10-V to +10-V ranges, output<br>unloaded       | :     | ±10    | mV   |

|           | Channel-to-channel ac crosstalk | 10-V span, full-scale swing on all other channel, measured channel at midscale, output unloaded                                 |       | 1      | nV-s |

|           | Channel-to-channel dc crosstalk | 10-V span, full-scale swing on all other channel, measured channel at midscale, output unloaded                                 |       | 1      | LSB  |

|           | Digital crosstalk               | 10-V span, full-scale swing on all other input buffer, measured channel at midscale, output unloaded                            |       | 1      | nV-s |

|           | Digital feedthrough             | DAC code at midscale, f <sub>SCLK</sub> = 1 MHz, output unloaded                                                                |       | 1      | nV-s |

|                    | PARAMETER                        | TEST CONDITIONS                    | MIN                         | TYP  | MAX                      | UNIT                |

|--------------------|----------------------------------|------------------------------------|-----------------------------|------|--------------------------|---------------------|

| EXTERNA            | L REFERENCE INPUT                |                                    |                             |      |                          |                     |

| V <sub>REFIO</sub> | Reference input voltage          |                                    | 2.49                        | 2.5  | 2.51                     | V                   |

|                    | Reference input current          |                                    |                             | 50   |                          | μA                  |

|                    | Reference input impedance        |                                    |                             | 50   |                          | <b>k</b> Ω          |

|                    | Reference input capacitance      |                                    |                             | 90   |                          | pF                  |

| INTERNAL           | REFERENCE                        |                                    | <u> </u>                    |      |                          |                     |

|                    | Reference output voltage         | T <sub>A</sub> = 25°C              | 2.4975                      |      | 2.5025                   | V                   |

|                    | Reference output drift           |                                    |                             | 5    | 10                       | ppm/°C              |

|                    | Reference output impedance       |                                    |                             | 0.15 |                          | Ω                   |

|                    | Reference output noise           | 0.1 Hz to 10 Hz                    |                             | 12   |                          | μV <sub>PP</sub>    |

|                    | Reference output noise density   | 10 kHz, V <sub>REFIO</sub> = 10 nF |                             | 240  |                          | nV/ √ <del>Hz</del> |

|                    | Reference load current           |                                    |                             | 5    |                          | mA                  |

|                    | Reference load regulation        | Source                             |                             | 120  |                          | μV/mA               |

|                    | Reference line regulation        |                                    |                             | 100  |                          | μV/V                |

|                    | Reference output drift over time | T <sub>A</sub> = 40°C, 1000 hours  |                             | ±300 |                          | μV                  |

|                    | Reference thermal hysteresis     | First cycle                        |                             | ±125 |                          | μV                  |

|                    | Reference thermal hysteresis     | Additional cycle                   |                             | ±25  |                          | μν                  |

| DIGITAL II         | NPUTS AND OUTPUTS                |                                    |                             |      | ·                        |                     |

| V <sub>IH</sub>    | Input high voltage               |                                    | 0.7 × IO<br>V <sub>DD</sub> |      |                          | V                   |

| V <sub>IL</sub>    | Input low voltage                |                                    |                             | ×    | 0.3<br>IOV <sub>DD</sub> | V                   |

|                    | Input current                    |                                    |                             | ±2   |                          | μA                  |

|                    | Input pin capacitance            |                                    |                             | 2    |                          | pF                  |

| V <sub>OH</sub>    | SDO, high-level output voltage   | SDO load current = 0.2 mA          | IOV <sub>DD</sub><br>- 0.2  |      |                          | V                   |

| V <sub>OL</sub>    | SDO, low-level output voltage    | SDO load current = 0.2 mA          |                             |      | 0.4                      | V                   |

|                    | FAULT, low-level output voltage  | FAULT load current = 10 mA         |                             |      | 0.4                      | V                   |

|                    | Output pin capacitance           |                                    |                             | 5    |                          | pF                  |

| PARAMETER          |                                                 | TEST CONDITIONS                 | MIN  | TYP | MAX | UNIT |  |

|--------------------|-------------------------------------------------|---------------------------------|------|-----|-----|------|--|

| POWER F            | POWER REQUIREMENTS                              |                                 |      |     |     |      |  |

|                    |                                                 | Normal mode, internal reference |      |     | 8   | m Λ  |  |

| $AI_{DD}$          | AV <sub>DD</sub> supply current <sup>(5)</sup>  | Normal mode, external reference |      |     | 7   | mA   |  |

|                    |                                                 | Power-down mode                 |      |     | 10  | μΑ   |  |

| $DI_DD$            | DV <sub>DD</sub> supply current <sup>(5)</sup>  | Digital interface static        |      |     | 8   | mA   |  |

|                    |                                                 | Normal mode, internal reference | - 8  |     |     | m Λ  |  |

| $AI_{SS}$          | AV <sub>SS</sub> supply current <sup>(5)</sup>  | Normal mode, external reference | - 7  |     |     | mA   |  |

|                    |                                                 | Power-down mode                 | - 10 |     |     | μA   |  |

| I <sub>IOVDD</sub> | IOV <sub>DD</sub> supply current <sup>(5)</sup> | SCLK toggling at 1 MHz          |      |     | 100 | μA   |  |

- (1) End point fit between codes. 16-bit: 512 to 65024 for  $AV_{DD} \geqslant 5.5$  V, 512 to 63488 for  $AV_{DD} \leqslant 5.5$  V, 0.2-V headroom between  $V_{REFIO}$  and  $AV_{DD}$ ; 12-bit: 32 to 4064 for  $AV_{DD} \geqslant 5.5$  V, 32 to 3968 for  $AV_{DD} \leqslant 5.5$  V, 0.2-V headroom between  $V_{REFIO}$  and  $AV_{DD}$ .

- (2) Full-scale code written to the DAC for AV<sub>DD</sub>  $\geqslant$  5.5 V. 16-bit: code 63488 written to the DAC for AV<sub>DD</sub>  $\leqslant$  5.5 V; 12-bit: code 3968 written to the DAC for AV<sub>DD</sub>  $\leqslant$  5.5 V.

- (3) Temporary overload condition protection. junction temperature can be exceeded during current limit. operation above the specified maximum junction temperature may impair device reliability.

- (4) Specified by design and characterization, not production tested.

- (5) AV<sub>DD</sub> = +15 V, AV<sub>SS</sub> = -15 V, DV<sub>DD</sub> = 5 V, SPI static, 10-V output span, all DAC at full scale, V<sub>OUTX</sub> unloaded.

# 7.6 Timing Requirements: Write, IOV $_{\text{DD}}$ : 1.7 V to 2.7 V

all specifications at  $T_A$  =  $-40^{\circ}$ C to +125°C, input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, 1.7 V  $\leq$  IOV<sub>DD</sub> < 2.7 V

|                        | PARAMETER                             | MIN | NOM | MAX | UNIT |

|------------------------|---------------------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>      | SCLK frequency                        |     |     | 25  | MHz  |

| t <sub>SCLKHIGH</sub>  | SCLK high time                        | 20  |     |     | ns   |

| t <sub>sclklow</sub>   | SCLK low time                         | 20  |     |     | ns   |

| t <sub>SDIS</sub>      | SDIN setup                            | 10  |     |     | ns   |

| t <sub>SDIH</sub>      | SDIN hold                             | 10  |     |     | ns   |

| t <sub>CSS</sub>       | SYNC to SCLK falling edge setup       | 30  |     |     | ns   |

| t <sub>CSH</sub>       | SCLK falling edge to SYNC rising edge | 10  |     |     | ns   |

| t <sub>csніgн</sub>    | SYNC high time                        | 50  |     |     | ns   |

| t <sub>DACWAIT</sub>   | Sequential DAC update wait time       | 2.4 |     |     | μs   |

| t <sub>BCASTWAIT</sub> | Broadcast DAC update wait time        | 4   |     |     | μs   |

| t <sub>LDACAL</sub>    | SYNC rising edge to LDAC falling edge | 80  |     |     | ns   |

| t <sub>LDACW</sub>     | LDAC low time                         | 20  |     |     | ns   |

| t <sub>CLRW</sub>      | CLR low time                          | 20  |     |     | ns   |

| t <sub>RSTW</sub>      | RST low time                          | 20  |     |     | ns   |

# 7.7 Timing Requirements: Write, IOV<sub>DD</sub>: 2.7 V to 5.5 V

all specifications at  $T_A$  =  $-40^{\circ}$ C to +125°C, input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, 2.7 V  $\leq$  IOV<sub>DD</sub>  $\leq$  5.5 V

|                        | PARAMETER                             | MIN | NOM | MAX | UNIT |

|------------------------|---------------------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>      | SCLK frequency                        |     |     | 50  | MHz  |

| t <sub>SCLKHIGH</sub>  | SCLK high time                        | 10  |     |     | ns   |

| t <sub>SCLKLOW</sub>   | SCLK low time                         | 10  |     |     | ns   |

| t <sub>SDIS</sub>      | SDIN setup                            | 5   |     |     | ns   |

| t <sub>SDIH</sub>      | SDIN hold                             | 5   |     |     | ns   |

| t <sub>CSS</sub>       | SYNC to SCLK falling edge setup       | 15  |     |     | ns   |

| t <sub>CSH</sub>       | SCLK falling edge to SYNC rising edge | 5   |     |     | ns   |

| t <sub>CSHIGH</sub>    | SYNC high time                        | 25  |     |     | ns   |

| t <sub>DACWAIT</sub>   | Sequential DAC update wait time       | 2.4 |     |     | μs   |

| t <sub>BCASTWAIT</sub> | Broadcast DAC update wait time        | 4   |     |     | μs   |

| t <sub>LDACAL</sub>    | SYNC rising edge to LDAC falling edge | 40  |     |     | ns   |

| t <sub>LDACW</sub>     | LDAC low time                         | 20  |     |     | ns   |

| t <sub>CLRW</sub>      | CLR low time                          | 20  |     |     | ns   |

| t <sub>RSTW</sub>      | RST low time                          | 20  |     |     | ns   |

# 7.8 Timing Requirements: Read and Daisy Chain, FSDO = 0, $IOV_{DD}$ : 1.7 V to 2.7 V

all specifications at  $T_A$  =  $-40^{\circ}$ C to +125°C, input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, 1.7 V  $\leq$  IOV<sub>DD</sub> < 2.7 V

|                       | PARAMETER                              |    | NOM | MAX  | UNIT |

|-----------------------|----------------------------------------|----|-----|------|------|

| f <sub>SCLK</sub>     | SCLK frequency                         |    |     | 12.5 | MHz  |

| t <sub>SCLKHIGH</sub> | SCLK high time                         | 33 |     |      | ns   |

| t <sub>SCLKLOW</sub>  | SCLK low time                          | 33 |     |      | ns   |

| t <sub>SDIS</sub>     | SDIN setup                             | 10 |     |      | ns   |

| t <sub>SDIH</sub>     | SDIN hold                              | 10 |     |      | ns   |

| t <sub>CSS</sub>      | SYNC to SCLK falling edge setup        | 30 |     |      | ns   |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edge  | 10 |     |      | ns   |

| t <sub>CSHIGH</sub>   | SYNC high time                         | 50 |     |      | ns   |

| t <sub>SDOZ</sub>     | SDO driven to tri-state mode           | 0  |     | 30   | ns   |

| t <sub>SDODLY</sub>   | SDO output delay from SCLK rising edge | 0  |     | 30   | ns   |

# 7.9 Timing Requirements: Read and Daisy Chain, FSDO = 1, $IOV_{DD}$ : 1.7 V to 2.7 V

all specifications at  $T_A$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C, input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, 1.7 V  $\leq$  IOV<sub>DD</sub> < 2.7 V

|                       | PARAMETER                              |    | NOM | MAX | UNIT |

|-----------------------|----------------------------------------|----|-----|-----|------|

| f <sub>SCLK</sub>     | SCLK frequency                         |    |     | 25  | MHz  |

| t <sub>SCLKHIGH</sub> | SCLK high time                         | 20 |     |     | ns   |

| t <sub>SCLKLOW</sub>  | SCLK low time                          | 20 |     |     | ns   |

| t <sub>SDIS</sub>     | SDIN setup                             | 10 | -   |     | ns   |

| t <sub>SDIH</sub>     | SDIN hold                              | 10 |     |     | ns   |

| t <sub>CSS</sub>      | SYNC to SCLK falling edge setup        | 30 |     |     | ns   |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edge  | 10 |     |     | ns   |

| t <sub>CSHIGH</sub>   | SYNC high time                         | 50 |     |     | ns   |

| t <sub>SDOZ</sub>     | SDO driven to tri-state mode           | 0  | -   | 30  | ns   |

| t <sub>SDODLY</sub>   | SDO output delay from SCLK rising edge | 0  |     | 30  | ns   |

Submit Document Feedback

# 7.10 Timing Requirements: Read and Daisy Chain, FSDO = 0, $IOV_{DD}$ : 2.7 V to 5.5 V

all specifications at  $T_A$  =  $-40^{\circ}$ C to +125°C, input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, 2.7 V  $\leq$  IOV<sub>DD</sub>  $\leq$  5.5 V

|                       | PARAMETER                              |    | NOM | MAX | UNIT |

|-----------------------|----------------------------------------|----|-----|-----|------|

| f <sub>SCLK</sub>     | SCLK frequency                         |    |     | 20  | MHz  |

| t <sub>SCLKHIGH</sub> | SCLK high time                         | 25 |     |     | ns   |

| t <sub>SCLKLOW</sub>  | SCLK low time                          | 25 |     |     | ns   |

| t <sub>SDIS</sub>     | SDIN setup                             | 5  |     |     | ns   |

| t <sub>SDIH</sub>     | SDIN hold                              | 5  |     |     | ns   |

| t <sub>CSS</sub>      | SYNC to SCLK falling edge setup        | 20 |     |     | ns   |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edge  | 5  |     |     | ns   |

| t <sub>CSHIGH</sub>   | SYNC high time                         | 25 |     |     | ns   |

| t <sub>SDOZ</sub>     | SDO driven to tri-state mode           | 0  |     | 20  | ns   |

| t <sub>SDODLY</sub>   | SDO output delay from SCLK rising edge | 0  |     | 20  | ns   |

# 7.11 Timing Requirements: Read and Daisy Chain, FSDO = 1, $IOV_{DD}$ : 2.7 V to 5.5 V

all specifications at  $T_A$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C, input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, 2.7 V  $\leq$  IOV<sub>DD</sub>  $\leq$  5.5 V

|                       | PARAMETER                              | MIN | NOM | MAX | UNIT |

|-----------------------|----------------------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>     | SCLK frequency                         |     |     | 35  | MHz  |

| t <sub>SCLKHIGH</sub> | SCLK high time                         | 14  |     |     | ns   |

| t <sub>SCLKLOW</sub>  | SCLK low time                          | 14  |     |     | ns   |

| t <sub>SDIS</sub>     | SDIN setup                             | 5   |     |     | ns   |

| t <sub>SDIH</sub>     | SDIN hold                              | 5   |     |     | ns   |

| t <sub>CSS</sub>      | SYNC to SCLK falling edge setup        | 20  |     |     | ns   |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edge  | 5   |     |     | ns   |

| t <sub>CSHIGH</sub>   | SYNC high time                         | 25  |     |     | ns   |

| t <sub>SDOZ</sub>     | SDO driven to tri-state mode           | 0   |     | 20  | ns   |

| t <sub>SDODLY</sub>   | SDO output delay from SCLK rising edge | 0   |     | 20  | ns   |

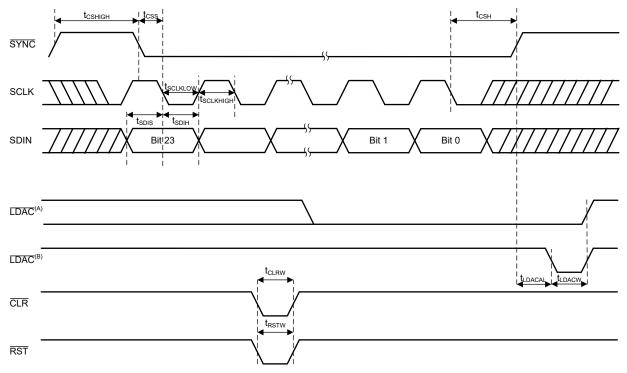

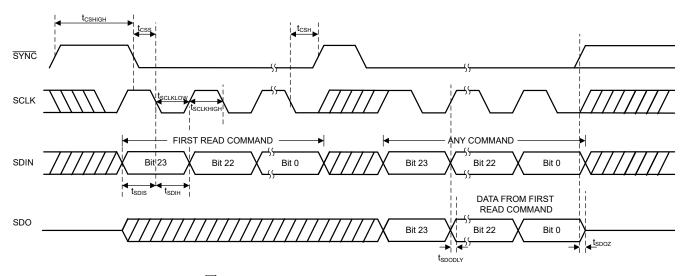

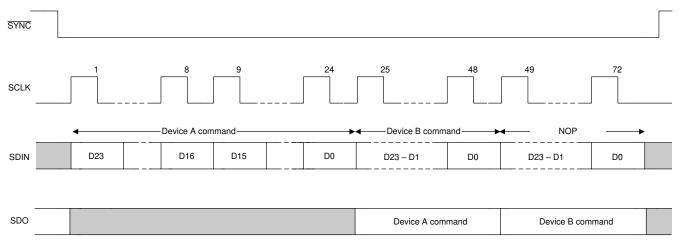

# 7.12 Timing Diagrams

- A. Asynchronous update.

- B. Synchronous update.

图 7-1. Serial Interface Write Timing Diagram

图 7-2. Serial Interface Read Timing Diagram

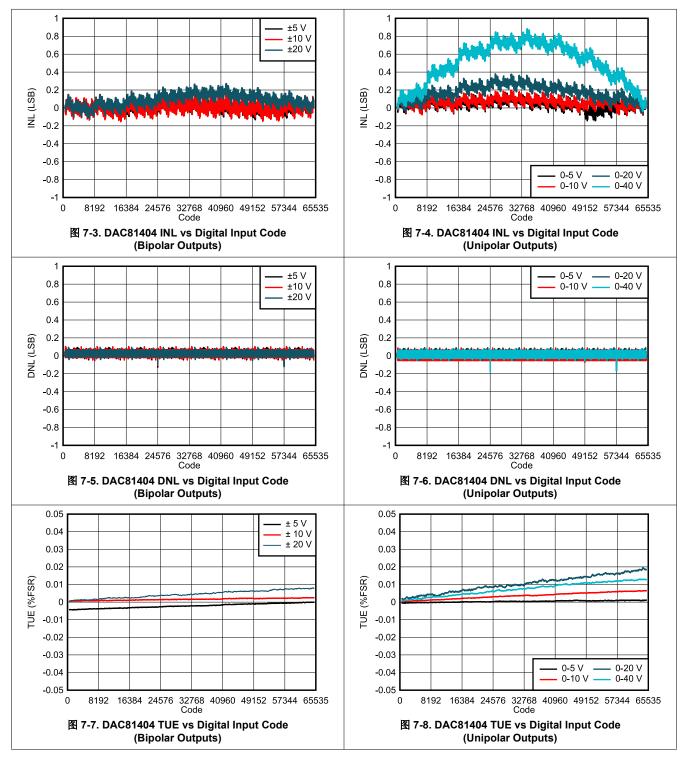

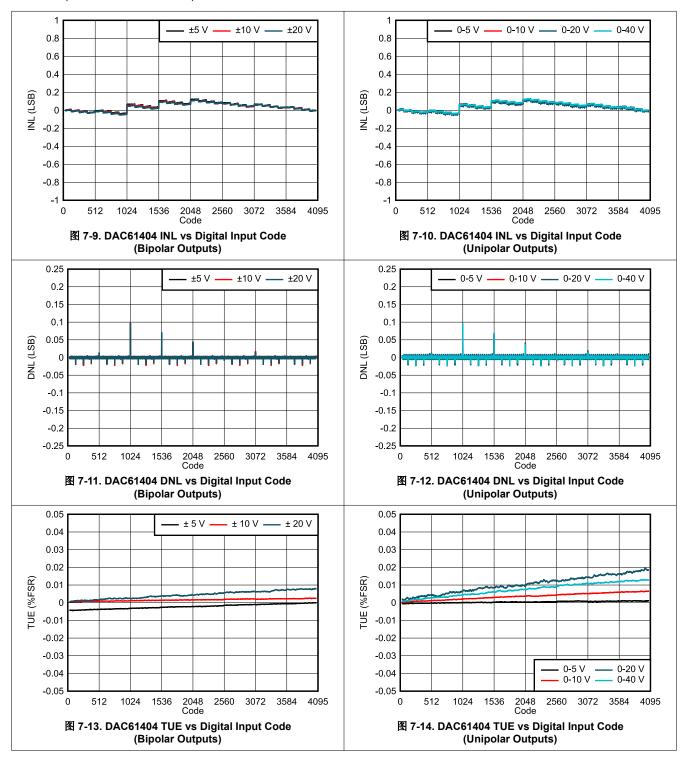

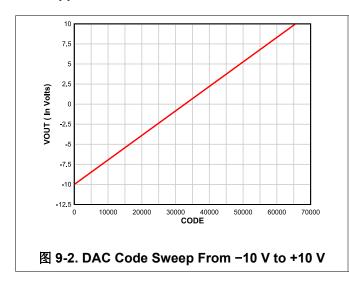

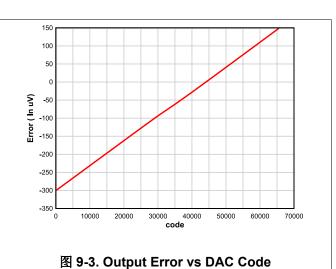

### 7.13 Typical Characteristics

# 8 Detailed Description

#### 8.1 Overview

The 16-bit DAC81404 and 12-bit DAC61404 (DACx1404) are pin-compatible, quad-channel, high-voltage output, digital-to-analog converters (DACs). The DACx1404 consist of an R-2R-based ladder followed by an output buffer. The devices also include a precision reference and a reference buffer. The R-2R-based ladder is production trimmed to provide monotonicity and a linearity of ±1 LSB. The devices are also optimized to reduce the code-to-code change glitch to less than 2 nV-s.

The DACx1404 output amplifier provides bipolar voltage outputs up to ±20 V, and unipolar voltage outputs up to 40 V. Each output channel includes sense pins to eliminate the IR drop across load connections, and sense a difference of up to ±12 V between the load and DAC grounds. Alternatively, the sense pins can also be used for output offset adjustment. An external capacitor compensation pin is also provided to stabilize the output amplifier for high capacitive loads.

Communication to the DACx1404 is performed through a 4-wire serial interface that supports stand-alone and daisy-chain operation. An optional frame-error check provides added robustness to the device serial interface.

The DACx1404 incorporate a power-on-reset circuit that connects the DAC outputs to ground at power up. The outputs remain in this mode until the device is properly configured for operation. The devices include additional reliability features such as short-circuit protection and a thermal alarm.

#### 8.2 Functional Block Diagram

### **8.3 Feature Description**

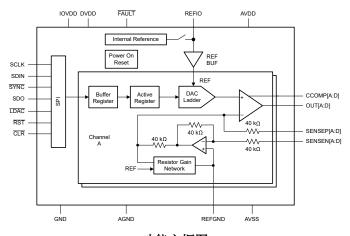

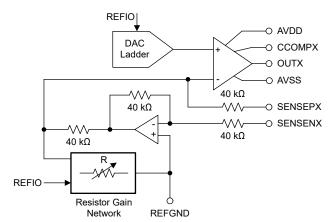

Each output channel in the device consists of an R-2R ladder digital-to-analog converter (DAC) with dedicated reference and ground buffers, and an output buffer amplifier capable of rail-to-rail operation. The device also includes an internal 2.5-V reference. 图 8-1 shows a simplified diagram of the device architecture.

图 8-1. Device Architecture

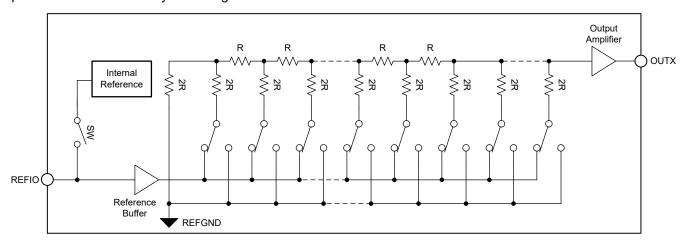

#### 8.3.1 R-2R Ladder DAC

The DAC architecture consists of a voltage-output, segmented, R-2R ladder as shown in 88-2. The device incorporates a dedicated reference buffer per output channel that provides constant input impedance with code at the REFIO pin. The output of the reference buffers drives the R-2R ladders. A production trim process provides excellent linearity and low glitch.

图 8-2. R-2R Ladder

#### 8.3.2 Programmable-Gain Output Buffer

The voltage output stage as conceptualized in 8-3 provides the voltage output according to the DAC code and the output range setting.

图 8-3. Voltage Output Buffer

For unipolar output mode, the output range can be programmed as:

- 0 V to 5 V

- 0 V to 10 V

- 0 V to 20 V

- 0 V to 40 V

For bipolar output mode, the output reange can be programmed as:

- ±5 V

- ±10 V

- ±20 V

In addition, 20% overrange is available on all ranges except for 0 V to 40 V and ±20 V.

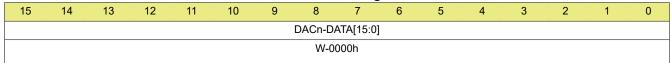

The input data are written to the individual DAC data registers in straight-binary format for all output ranges. The output voltage ( $V_{OUTX}$ ) can be expressed as 方程式 1 and 方程式 2.

For unipolar output mode

$$V_{OUTX} = V_{REFIO} \times GAIN \times \frac{CODE}{2^{N}}$$

(1)

For bipolar output mode

$$V_{OUTX} = V_{REFIO} \times GAIN \times \frac{CODE}{2^{N}} - GAIN \times \frac{V_{REFIO}}{2}$$

(2)

where:

- CODE is the decimal equivalent of the binary code loaded to the DAC data register.

- N is the DAC resolution in bits.

- V<sub>REFIO</sub> is the reference voltage (internal or external).

- GAIN is the gain factor assigned to each output voltage output range as shown in 表 8-1.

表 8-1. Voltage Output Range vs Gain Setting

| MODE     | VOLTAGE OUTPUT RANGE  | GAIN |

|----------|-----------------------|------|

|          | 5 V                   | 2.0  |

|          | 6 V (20% overrange)   | 2.4  |

|          | 10 V                  | 4.0  |

| Unipolar | 12 V (20% overrange)  | 4.8  |

|          | 20 V                  | 8.0  |

|          | 24 V (20% overrange)  | 9.6  |

|          | 40 V                  | 16.0 |

|          | ±5 V                  | 4.0  |

|          | ±6 V (20% overrange)  | 4.8  |

| Bipolar  | ±10 V                 | 8.0  |

|          | ±12 V (20% overrange) | 9.6  |

|          | ±20 V                 | 16.0 |

The output amplifiers can drive up to ±15 mA with 1.5-V supply headroom while maintaining the specified TUE specification for the device. The output stage has short-circuit current protection that limits the output current to 40 mA. The device is able to drive capacitive loads up to 1 µF. For loads greater than 2 nF, an external compensation capacitor must be connected between the CCOMPx and OUTx pins to keep the output voltage stable, but at the expense of reduced bandwidth and increased settling time.

#### 8.3.2.1 Sense Pins

The SENSEPx pins are provided to enable sensing of the load by connecting to points electrically closer to the load. This configuration allows the internal output amplifier to make sure that the correct voltage is applied across the load, as long as headroom is available on the power supply. The SENSEPx pins are used to correct for resistive drops on the system board, and are connected to  $V_{OUTX}$  at the pins. In some cases, both  $V_{OUTX}$  and  $V_{SENSEPX}$  are brought out through separate lines and connected remotely together at the load. In such cases, if the  $V_{SENSEPX}$  line is cut, then the amplifier loop is broken; use a 5-k  $\Omega$  resistor between the OUTx and SENSEPx pins to maintain proper amplifier operation.

The SENSENx pins are provided as remote ground sense reference outputs from the internal  $V_{OUTX}$  amplifier. The output swing of the  $V_{OUTX}$  amplifier is relative to the voltage seen at these pins. The voltage difference between  $V_{SENSENX}$  and the device ground must be lower than  $\pm 12$  V.

At device start up, the power-on-reset circuit makes sure that all registers are at default values. The voltage output buffer is in a Hi-Z state; however, the SENSEPx pins connect to the amplifier inputs through an internal 40-k  $\Omega$  feedback resistor ( $\boxtimes$  8-3). If the OUTx and SENSEPx pins are connected together, the OUTx pins are also connected to the same node through the feedback resistor. This node is protected by internal circuitry and settles to a value between GND and the reference input.

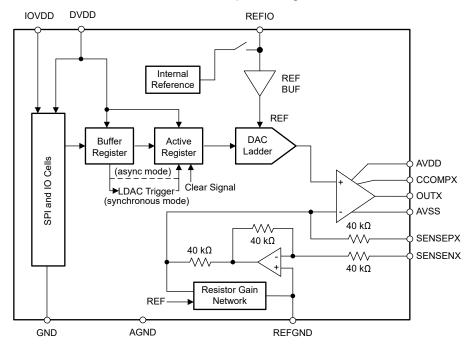

#### 8.3.3 DAC Register Structure

Data written to the DAC data registers is initially stored in the DAC buffer registers. The transfer of data from the DAC buffer registers to the active registers can be configured to occur immediately (asynchronous mode) or be initiated by a DAC trigger signal (synchronous mode). After the active registers are updated, the DAC outputs change to the new values.

After a power-on or reset event, all DAC registers set to zero code, the DAC output amplifiers power down, and the DAC outputs connect to ground.

#### 8.3.3.1 DAC Output Update

The DAC double-buffered architecture enables data updates without disturbing the analog outputs. Data updates can be performed either in synchronous or asynchronous mode. The device offers both software and hardware data update control.

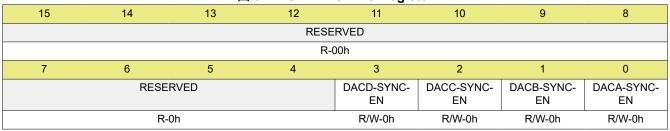

The update mode for each DAC channel is determined by the status of the corresponding SYNC-EN bit. In both update modes, a minimum wait time of  $2.4 \mu s$  is required between DAC output updates.

#### 8.3.3.1.1 Synchronous Update

In synchronous mode, writing to the DAC data register does not automatically update the DAC output. Instead the update occurs only after a trigger event. A DAC trigger signal is generated eigher through the SOFT-LDAC bit or by the LDAC pin. The synchronous update mode enables simultaneous update of multiple DAC outputs.

#### 8.3.3.1.2 Asynchronous Update

In asynchronous mode, a DAC data register write results in an immediate update of the DAC active register and DAC output on a SYNC rising edge.

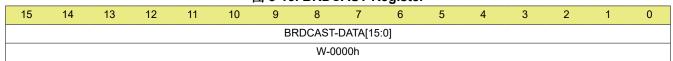

### 8.3.3.2 Broadcast DAC Register

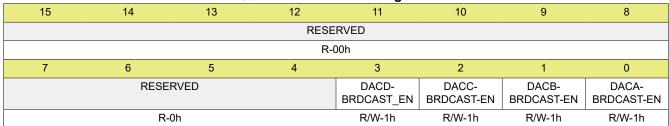

The DAC broadcast register enables a simultaneous update of multiple DAC outputs with the same value with a single register write.

Each DAC channel can be configured to update or remain unaffected by a broadcast command by setting the corresponding DAC-BRDCAST-EN bit. A register write to the BRDCAST-DATA register forces those DAC channels that have been configured for broadcast operation to update their DAC buffer registers to this value. The DAC outputs update to the broadcast value according to their synchronous mode configuration.

#### 8.3.3.3 Clear DAC Operation

The DAC outputs are set in clear mode either through the  $\overline{\text{CLR}}$  pin or the SOFT-CLR bit. In clear mode, each DAC data register is set to either zero code (if configured for unipolar range operation) or midscale code (if set for bipolar range operation). A clear command forces all DAC channels to clear the contents of their buffer and active registers to the clear code regardless of their synchronization setting.

Copyright © 2021 Texas Instruments Incorporated

#### 8.3.4 Internal Reference

The device includes a precision 2.5-V band-gap reference with a maximum temperature drift of 10 ppm/°C. The internal reference is in power-down mode by default.

The internal reference voltage is available at the REFIO pin and can source up to 5 mA. To filter noise, place a minimum 150-nF capacitor between the reference output and ground.

External reference operation is also supported. The external reference is applied to the REFIO pin. If using an external reference, power down the internal reference.

#### 8.3.5 Power-On Reset (POR)

The device incorporates a power-on-reset function. After the supplies reach their minimum specified values, a POR event is issued. Additionally, a POR event can be initiated by the RST pin or a SOFT-RESET command.

A POR event causes all registers to initialize to default values, and communication with the device is valid only after a 1 ms POR delay. After a POR event, the device is set to power-down mode, where all DAC channels and internal reference are powered down and the DAC outputs are connected to ground through a  $10-k\Omega$  internal resistor.

#### 8.3.5.1 Hardware Reset

A device hardware reset event is initiated by a minimum 20-ns logic low on the RST pin.

#### 8.3.5.2 Software Reset

The device implements a software reset feature. A device software reset is initiated by writing reserved code 0x1010 to SOFT-RESET in the TRIGGER register. The software reset command is triggered on the SYNC rising edge of the instruction.

#### 8.3.6 Thermal Alarm

The device incorporates a thermal shutdown that is triggered when the die temperature exceeds 140°C. A thermal shutdown sets the TEMP-ALM bit, and causes all DAC outputs to power-down; however, the internal reference remains powered on. The FAULT pin can be configured to monitor a thermal shutdown condition by setting the TEMPALM-EN bit. After a thermal shutdown is triggered, the device stays in shutdown even after the device temperature lowers.

The die temperature must fall to less than 140°C before the device can be returned to normal operation. To resume normal operation, the thermal alarm must be cleared through the ALM-RESET bit while the DAC channels are in power-down mode.

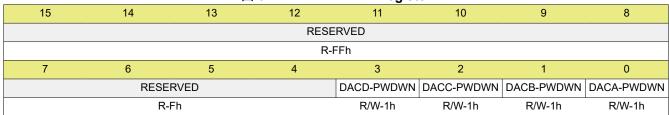

#### 8.4 Device Functional Modes

#### 8.4.1 Power-Down Mode

The device output amplifiers and internal reference power-down status can be individually configured and monitored though the PWDWN registers. Setting a DAC channel in power-down mode disables the output amplifier and clamps the output pin to ground through an internal  $10-k\Omega$  resistor.

The DAC data registers are not cleared when the DAC goes into power-down mode. Therefore, upon return to normal operation, the DAC output voltages return to the same respective voltages prior to the device entering power-down mode. The DAC data registers can be updated while in power-down mode, which allows for changing the power-on voltage, if required.

After a power-on or reset event, all the DAC channels and the internal reference are in power-down mode. The entire device can be configured into power-down or active modes through the DEV-PWDWN bit.

### 8.5 Programming