DAC7562T, DAC7563T, DAC8162T DAC8163T, DAC8562T, DAC8563T

ZHCSE89A - SEPTEMBER 2015 - REVISED OCTOBER 2015

# DACxx6xT 具有 2.5V、4PPM/°C 内部基准和 5V TTL I/O 的双路 16 位、14 位、12 位低功耗电压输出 DAC

# 1 特性

- 相对精度: 16 位时为 4 最低有效位 (LSB) 最大积分非线性 (INL)

- 低毛刺脉冲: 0.1nV-s

- 双向基准引脚: 输入或 2.5V 输出

- 4ppm/°C 温度漂移(典型值)

- 上电复位至零量程或量程中点

- 低功耗: 5V AVDD 时为 4mW

- 宽电源范围: 2.7V 至 5.5V

- 带有施密特触发输入的 50MHz 串行外设接口 (SPI)

- LDAC 和 CLR 功能

- 支持轨到轨运行的输出缓冲器

- 与 DAC8562 系列引脚到引脚兼容

- 支持 5V 晶体管晶体管逻辑电路 (TTL) I/O

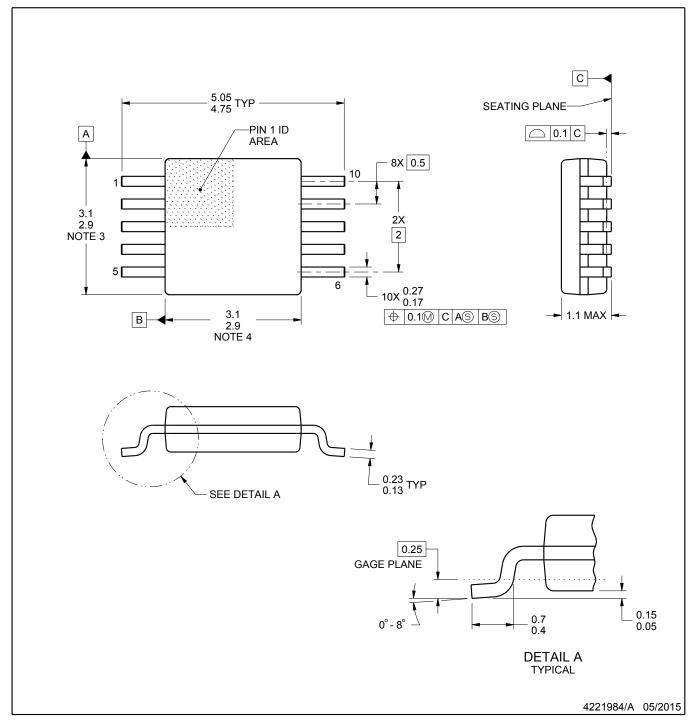

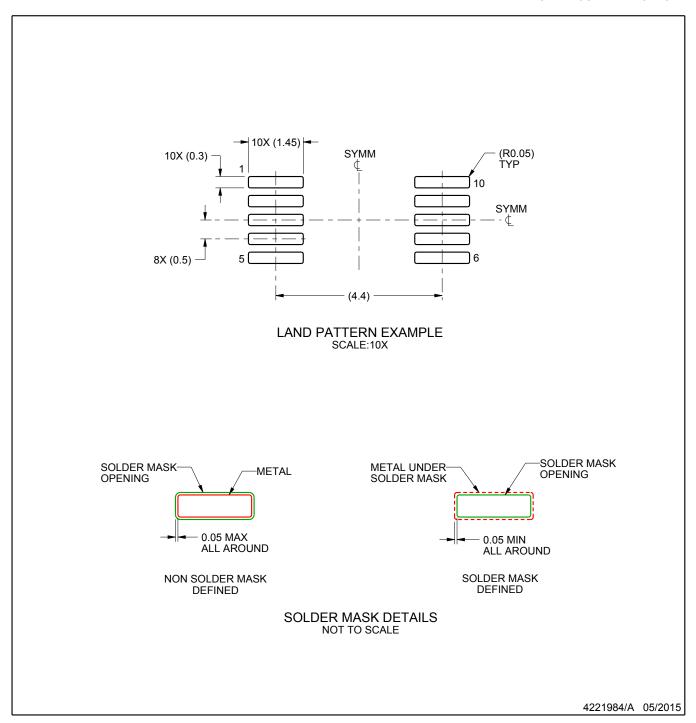

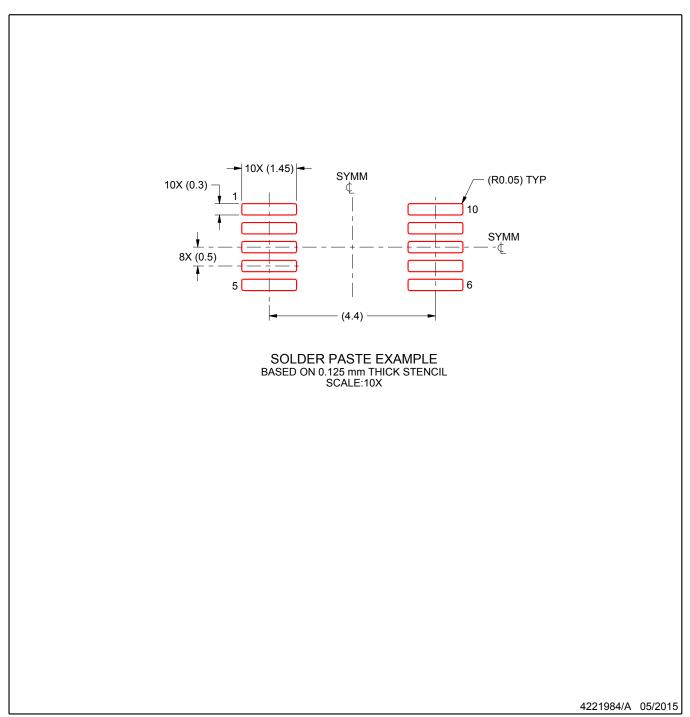

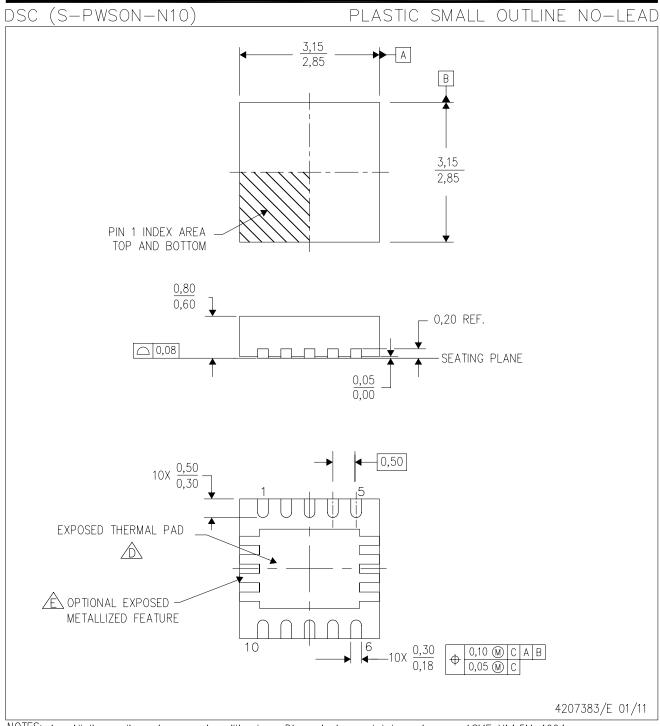

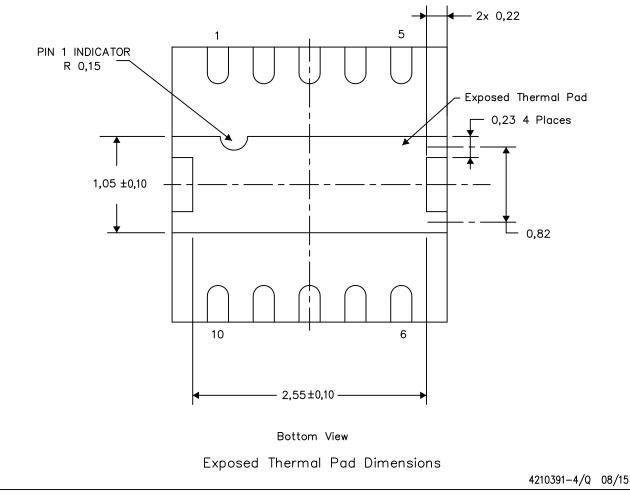

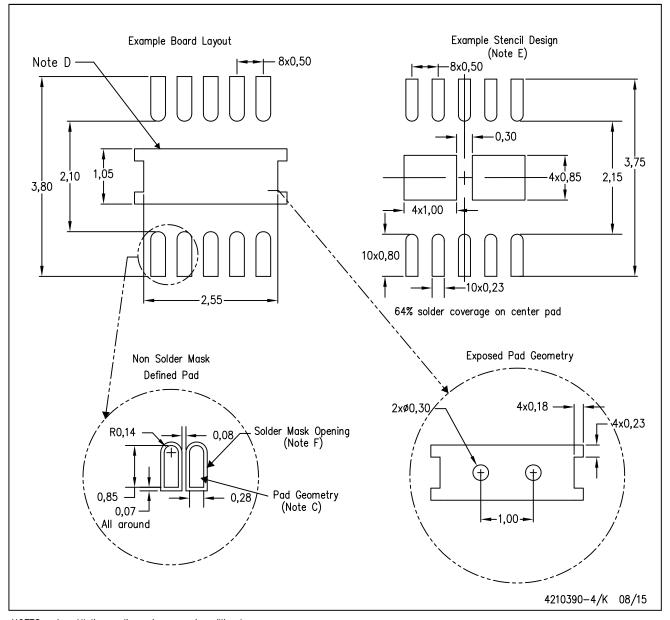

- 封装:晶圆级小外形无引线 (WSON)-10 (3mm x 3mm),超薄小外形尺寸 (VSSOP)-10

- 温度范围: -40℃至 125℃

#### 2 应用

- 便携式仪表

- 可编程逻辑控制器 (PLC) 模拟输出模块

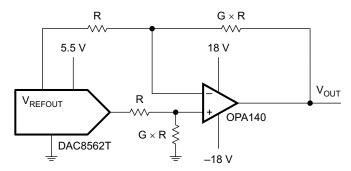

- 双极输出 (第 9.2.2 节)

- 闭环伺服器控制

- 压控振荡器调谐

- 数据采集系统

- 可编程增益和偏移调整

## 3 说明

DAC856xT、DAC816xT 和 DAC756xT 器件分别为 16 位、14 位和 12 位低功耗电压输出双通道数模转换器 (DAC)。 这些器件包括一个 2.5V、

4ppm/°C 内部基准,从而提供了一个 2.5V 或 5V 的满量程输出电压范围。 此内部基准有一个 ±5mV 的初始精度,并且能够在 V<sub>REFIN</sub>/V<sub>REFOUT</sub>引脚上提供或吸收高达 20mA 的电流。

这些器件是单片器件,从而提供了出色的线性并大大降低了有害的代码至代码转换时的瞬态电压(毛刺脉冲)。它们使用一个运行时钟速率高达 50MHz 的多用途 3 线制串口。此接口与标准 SPI™,QSPI™,Microwire,以及数字信号处理器 (DSP) 接口兼容。DACxx62T 器件配有一个上电复位电路,此电路可确保在一个有效代码被写入此器件前,DAC 输出上电并保持零量程,而 DACxx63T 在量程中点上电。这些器件包含一个断电特性,此特性可将 5V 电压时的流耗减少至 550nA(典型值)。此低功耗、内部基准和小封装尺寸使得这些器件非常适合于便携式、电池供电运行类设备。

与 DACxx62T 器件一样,DACxx63T 器件之间可互相插接并且功能兼容。 整个系列均提供 VSSOP-10 和WSON-10 封装。

器件信息(1)

|          | , , ,                    |                 |

|----------|--------------------------|-----------------|

| 器件型号     | 封装                       | 封装尺寸 (标称值)      |

| DAC8562T |                          |                 |

| DAC8162T | VSSOP (10),<br>WSON (10) | 3.00mm × 3.00mm |

| DAC7562T | (10)                     |                 |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

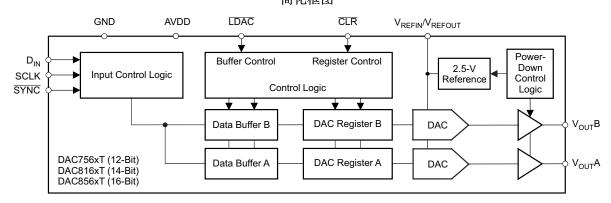

# 简化框图

| _ |            |

|---|------------|

|   | <b>—</b> . |

|   | 772        |

|   | 71         |

|   |            |

| 1 | 特性1                                  |    | 8.4 Device Functional Modes          | 32 |

|---|--------------------------------------|----|--------------------------------------|----|

| 2 | 应用 1                                 |    | 8.5 Programming                      | 36 |

| 3 |                                      | 9  | Application and Implementation       | 39 |

| 4 | 修订历史记录                               |    | 9.1 Application Information          | 39 |

| 5 | Device Comparison Table              |    | 9.2 Typical Applications             | 41 |

| 6 | Pin Configuration and Functions 4    |    | 9.3 System Examples                  | 45 |

| 7 | Specifications5                      | 10 | Power Supply Recommendations         | 46 |

| ′ | 7.1 Absolute Maximum Ratings         | 11 | Layout                               | 46 |

|   | 7.2 ESD Ratings                      |    | 11.1 Layout Guidelines               | 46 |

|   | 7.3 Recommended Operating Conditions |    | 11.2 Layout Example                  | 47 |

|   | 7.4 Thermal Information              | 12 | 器件和文档支持                              | 49 |

|   | 7.5 Electrical Characteristics       |    | 12.1 相关链接                            | 49 |

|   | 7.6 Timing Requirements9             |    | 12.2 社区资源                            | 49 |

|   | 7.7 Typical Characteristics          |    | 12.3 Trademarks                      | 49 |

| 8 | Detailed Description                 |    | 12.4 Electrostatic Discharge Caution | 49 |

| • | 8.1 Overview                         |    | 12.5 Glossary                        | 49 |

|   | 8.2 Functional Block Diagram         | 13 | 机械、封装和可订购信息                          | 49 |

|   | 8.3 Feature Description              |    |                                      |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Original (September 2015) to Revision A

**Page**

# 5 Device Comparison Table

| DEVICE   | MAXIMUM RELATIVE<br>ACCURACY (LSB) | MAXIMUM<br>DIFFERENTIAL<br>NONLINEARITY (LSB) | MAXIMUM REFERENCE<br>DRIFT (ppm/°C) | RESET TO  |

|----------|------------------------------------|-----------------------------------------------|-------------------------------------|-----------|

| DAC7562T | ±0.75                              | ±0.25                                         | 10                                  | Zero      |

| DAC7563T |                                    | ±0.25                                         | 10                                  | Mid-scale |

| DAC8162T | .0                                 | ±0.5                                          | 40                                  | Zero      |

| DAC8163T | ±3                                 |                                               | 10                                  | Mid-scale |

| DAC8562T | .40                                | 40                                            |                                     | Zero      |

| DAC8563T | ±12                                | ±1                                            | 10                                  | Mid-scale |

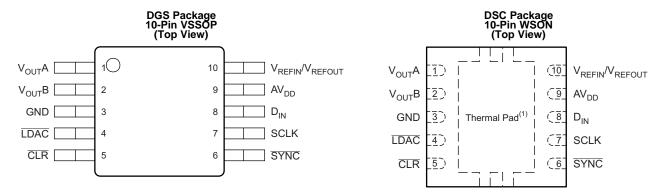

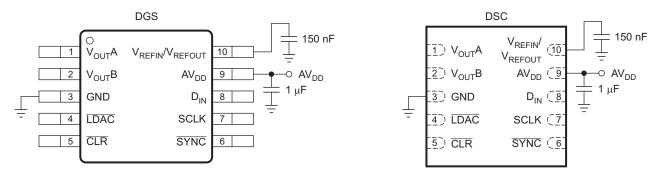

# 6 Pin Configuration and Functions

(1) TI recommends connecting the thermal pad to the ground plane for better thermal dissipation.

## **Pin Functions**

| PIN                    |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| $AV_{DD}$              | 9   | I   | Power-supply input, 2.7 V to 5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CLR                    | 5   | I   | Asynchronous clear input. The $\overline{\text{CLR}}$ input is falling-edge sensitive. On activation of $\overline{\text{CLR}}$ , zero scale (DACxx62T) or mid-scale (DACxx63T) is loaded to all input and DAC registers. This sets the DAC output voltages accordingly. The device exits clear code mode on the 24 <sup>th</sup> falling edge of the next write to the device. Activating $\overline{\text{CLR}}$ during a write sequence aborts the write.                                                                                                                                                                                               |  |  |

| D <sub>IN</sub>        | 8   | I   | Serial data input. Data are clocked into the 24-bit input shift register on each falling edge of the serial clock input. Schmitt-trigger logic input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| GND                    | 3   | _   | Ground reference point for all circuitry on the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LDAC                   | 4   | I   | In <i>synchronous</i> mode, data update occurs with the falling edge of the 24 <sup>th</sup> SCLK cycle, which follows a falling edge of SYNC. Such <i>synchronous</i> updates do not require the LDAC, which must be connected to GND permanently or asserted and held low before sending commands to the device.  In <i>asynchronous</i> mode, the LDAC pin is used as a negative edge-triggered timing signal for simultaneous DAC updates. Multiple single-channel commands can be written in order to set different channel buffers to desired values and then make a falling edge on the LDAC pin to update the DAC output registers simultaneously. |  |  |

| SCLK                   | 7   | I   | Serial clock input. Data can be transferred at rates up to 50 MHz. Schmitt-trigger logic input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SYNC                   | 6   | I   | Level-triggered control input (active-low). This input is the frame synchronization signal for the input data. When \$\overline{SYNC}\$ goes low, it enables the input shift register, and data are sampled on subsequent falling clock edges. The DAC output updates following the 24th clock falling edge. If \$\overline{SYNC}\$ is taken high before the 23rd clock edge, the rising edge of \$\overline{SYNC}\$ acts as an interrupt, and the write sequence is ignored by the DAC756xT, DAC816xT, and DAC856xT devices. Schmitt-trigger logic input                                                                                                  |  |  |

| V <sub>OUT</sub> A     | 1   | 0   | Analog output voltage from DAC-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| V <sub>OUT</sub> B     | 2   | 0   | Analog output voltage from DAC-B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| $V_{REFIN}/V_{REFOUT}$ | 10  | I/O | Bidirectional voltage reference pin. If internal reference is used, 2.5-V output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating ambient temperature range (unless otherwise noted).

|                                                                 | MIN  | MAX             | UNIT |

|-----------------------------------------------------------------|------|-----------------|------|

| AV <sub>DD</sub> to GND                                         | -0.3 | 6               | V    |

| CLR, D <sub>IN</sub> , LDAC, SCLK and SYNC input voltage to GND | -0.3 | $AV_{DD} + 0.3$ | V    |

| V <sub>OUT</sub> [A, B] to GND                                  | -0.3 | $AV_{DD} + 0.3$ | V    |

| V <sub>REFIN</sub> /V <sub>REFOUT</sub> to GND                  | -0.3 | $AV_{DD} + 0.3$ | V    |

| Operating temperature range                                     | -40  | 125             | °C   |

| Junction temperature, T <sub>J</sub>                            |      | 150             | ů    |

| Storage temperature, T <sub>stg</sub>                           | -65  | 150             | ô    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

| MAX       | UNIT             |

|-----------|------------------|

|           |                  |

| 5.5       | V                |

|           |                  |

| $AV_{DD}$ | V                |

| •         |                  |

| $AV_{DD}$ | V                |

|           |                  |

| 125       | °C               |

|           | AV <sub>DD</sub> |

# 7.4 Thermal Information

|                       |                                              | DAC756xT, DAC | DAC756xT, DAC816xT, DAC856xT |      |  |  |

|-----------------------|----------------------------------------------|---------------|------------------------------|------|--|--|

|                       | THERMAL METRIC                               | DSC (WSON)    | DGS (VSSOP)                  | UNIT |  |  |

|                       |                                              | 10 PINS       | 10 PINS                      |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 62.8          | 173.8                        | °C/W |  |  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 44.3          | 48.5                         | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 26.5          | 79.9                         | °C/W |  |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.4           | 1.7                          | °C/W |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 25.5          | 68.4                         | °C/W |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 46.2          | N/A                          | °C/W |  |  |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.5 Electrical Characteristics

At  $AV_{DD} = 2.7 \text{ V}$  to 5.5 V and  $T_A = -40^{\circ}\text{C}$  to 125°C (unless otherwise noted).

| F                        | PARAMETER                      | TEST CONDITIONS                                                     | MIN | TYP   | MAX              | UNIT               |  |

|--------------------------|--------------------------------|---------------------------------------------------------------------|-----|-------|------------------|--------------------|--|

| STATIC PER               | FORMANCE <sup>(1)</sup>        |                                                                     |     |       |                  |                    |  |

|                          | Resolution                     |                                                                     | 12  |       |                  | Bits               |  |

| DAC756xT                 | Relative accuracy              | Using line passing through codes 32 and 4,064                       |     | ±0.3  | ±0.75            | 1.00               |  |

|                          | Differential nonlinearity      | 12-bit monotonic                                                    |     | ±0.05 | ±0.25            | LSB                |  |

|                          | Resolution                     |                                                                     | 14  |       |                  | Bits               |  |

| DAC816xT                 | Relative accuracy              | Using line passing through codes 128 and 16,256                     |     | ±1    | ±3               | LCD                |  |

|                          | Differential nonlinearity      | 14-bit monotonic                                                    |     | ±0.1  | ±0.5             | LSB                |  |

|                          | Resolution                     |                                                                     | 16  |       |                  | Bits               |  |

| DAC856xT                 | Relative accuracy              | Using line passing through codes 512 and 65,024                     |     | ±4    | ±12              | LCD                |  |

|                          | Differential nonlinearity      | 16-bit monotonic                                                    |     | ±0.2  | ±1               | LSB                |  |

| Offset error             |                                | Extrapolated from two-point line (1), unloaded                      |     | ±1    | ±4               | mV                 |  |

| Offset error d           | rift                           |                                                                     |     | ±2    |                  | μV/°C              |  |

| Full-scale erre          | or                             | DAC register loaded with all 1s, DAC output unloaded                |     | ±0.03 | ±0.2             | % FSR              |  |

| Zero-code eri            | ror                            | DAC register loaded with all 0s, DAC output unloaded                |     | 1     | 4                | mV                 |  |

| Zero-code eri            | ror drift                      |                                                                     |     | ±2    |                  | μV/°C              |  |

| Gain error               |                                | Extrapolated from two-point line <sup>(1)</sup> , unloaded          |     | ±0.01 | ±0.15            | % FSR              |  |

| Gain tempera             | ature coefficient              |                                                                     |     | ±1    |                  | ppm<br>FSR/°C      |  |

| OUTPUT CH                | ARACTERISTICS(2)               | 1                                                                   |     |       |                  |                    |  |

| Output voltag            | e range                        |                                                                     | 0   |       | $AV_DD$          | V                  |  |

| (0)                      |                                | DACs unloaded                                                       |     | 7     |                  |                    |  |

| Output voltag            | e settling time <sup>(3)</sup> | $R_L = 1 \text{ M}\Omega$                                           |     | 10    |                  | μs                 |  |

| Slew rate                |                                | Measured between 20%–80% of a full-scale transition                 |     | 0.75  |                  | V/µs               |  |

|                          |                                | R <sub>L</sub> = ∞                                                  |     | 1     |                  |                    |  |

| Capacitive loa           | ad stability                   | $R_L = 2 k\Omega$                                                   |     | 3     |                  | nF                 |  |

| Code-change              | glitch impulse                 | 1-LSB change around major carry                                     |     | 0.1   |                  | nV-s               |  |

| Digital feedth           | rough                          | SCLK toggling, SYNC high                                            |     | 0.1   |                  | nV-s               |  |

| Power-on glit            | ch impulse                     | $R_L = 2 k\Omega$ , $C_L = 470 pF$ , $AV_{DD} = 5.5 V$              |     | 40    |                  | mV                 |  |

|                          |                                | Full-scale swing on adjacent channel,<br>External reference         |     | 5     |                  |                    |  |

| Channel-to-ch            | nannel dc crosstalk            | Full-scale swing on adjacent channel,<br>Internal reference         |     | 15    |                  | μV                 |  |

| DC output im             | pedance                        | At mid-scale input                                                  |     | 5     |                  | Ω                  |  |

| Short-circuit of         | current                        | DAC outputs at full-scale, DAC outputs shorted to GND               |     | 40    |                  | mA                 |  |

| Power-up tim             | e, including settling time     | Coming out of power-down mode                                       |     | 50    |                  | μs                 |  |

| AC PERFOR                | MANCE <sup>(2)</sup>           | 1                                                                   |     |       |                  | -                  |  |

| DAC output noise density |                                | T <sub>A</sub> = 25°C, at mid-scale input, f <sub>OUT</sub> = 1 kHz |     | 90    |                  | nV/√ <del>Hz</del> |  |

| DAC output noise         |                                | T <sub>A</sub> = 25°C, at mid-scale input, 0.1 Hz to 10 Hz          |     | 2.6   |                  | μV <sub>PP</sub>   |  |

| LOGIC INPU               | TS <sup>(2)</sup>              | ,                                                                   |     |       | I                |                    |  |

| Input-pin leak           |                                |                                                                     | -1  | ±0.1  | 1                | μA                 |  |

|                          | OW voltage V <sub>IL</sub>     |                                                                     | 0   |       | 0.8              | V                  |  |

| · ·                      | IGH voltage V <sub>IH</sub>    |                                                                     | 2.1 |       | AV <sub>DD</sub> | V                  |  |

| Pin capacitan            |                                |                                                                     |     |       | 3                | pF                 |  |

<sup>(1) 16-</sup>bit: codes 512 and 65,024; 14-bit: codes 128 and 16,256; 12-bit: codes 32 and 4,064, All digital inputs kept at same IO levels before and after write to the DAC

<sup>(2)</sup> Specification based on design or characterization

<sup>(3)</sup> Transition time between 1 / 4 scale and 3 / 4 scale, including settling to within ±0.024% FSR

# **Electrical Characteristics (continued)**

At AV<sub>DD</sub> = 2.7 V to 5.5 V and  $T_A = -40^{\circ}C$  to 125°C (unless otherwise noted).

| PARAMETER                                           | TEST CONDITIONS                                                                                             | MIN   | TYP  | MAX   | UNIT               |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|------|-------|--------------------|

| REFERENCE                                           |                                                                                                             |       |      |       |                    |

| External reference current                          | External V <sub>REF</sub> = 2.5 V (when internal reference is disabled), all channels active using gain = 1 |       | 15   |       | μΑ                 |

| Defense in the invader                              | Internal reference disabled, gain = 1                                                                       |       | 170  |       | 1.0                |

| Reference input impedance                           | Internal reference disabled, gain = 2                                                                       |       | 85   |       | kΩ                 |

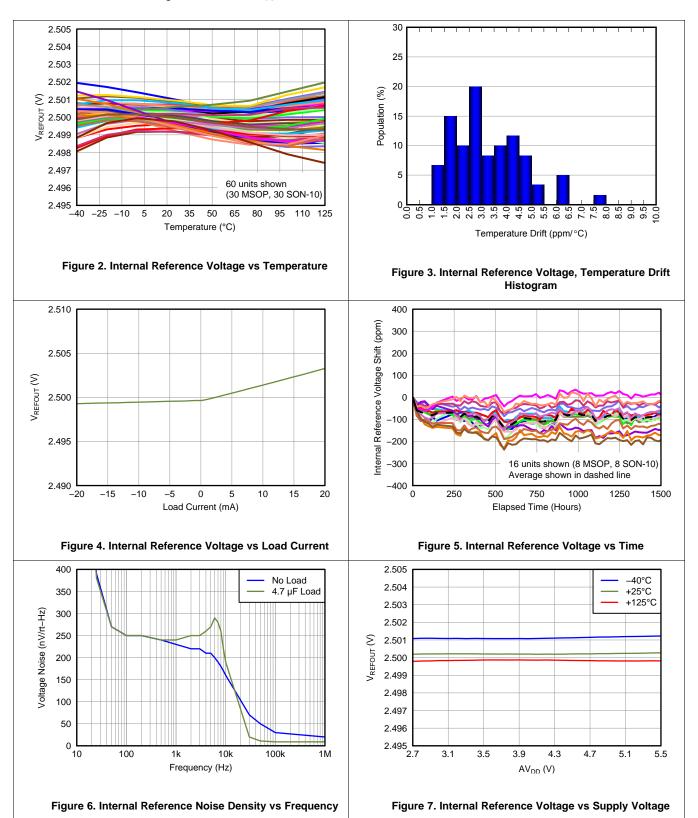

| REFERENCE OUTPUT                                    |                                                                                                             |       |      |       |                    |

| Output voltage                                      | T <sub>A</sub> = 25°C                                                                                       | 2.495 | 2.5  | 2.505 | V                  |

| Initial accuracy                                    | T <sub>A</sub> = 25°C                                                                                       | -5    | ±0.1 | 5     | mV                 |

| Output-voltage temperature drift                    | Internal reference output voltage temperature drift is characterized from –40°C to 125°C.                   |       | 4    | 10    | ppm/°C             |

| Output-voltage noise                                | f = 0.1 Hz to 10 Hz                                                                                         |       | 12   |       | $\mu V_{PP}$       |

| Output-voltage noise density (high-frequency noise) | $T_A = 25^{\circ}C$ , $f = 1 \text{ kHz}$ , $C_L = 0 \mu\text{F}$                                           |       | 250  |       |                    |

|                                                     | $T_A = 25^{\circ}C$ , f = 1 MHz, $C_L = 0 \mu F$                                                            |       | 30   |       | nV/√ <del>Hz</del> |

|                                                     | $T_A = 25^{\circ}C$ , f = 1 MHz, $C_L = 4.7 \mu F$                                                          |       | 10   |       |                    |

| Load regulation, sourcing <sup>(4)</sup>            | T <sub>A</sub> = 25°C                                                                                       |       | 20   |       | μV/mA              |

| Load regulation, sinking <sup>(4)</sup>             | T <sub>A</sub> = 25°C                                                                                       |       | 185  |       | μV/mA              |

| Output-current load capability <sup>(2)</sup>       |                                                                                                             |       | ±20  |       | mA                 |

| Line regulation                                     | T <sub>A</sub> = 25°C                                                                                       |       | 50   |       | μV/V               |

| Long-term stability or drift (aging) (4)            | $T_A = 25$ °C, time = 0 to 1900 hours                                                                       |       | 100  |       | ppm                |

| Thermal hysteresis (4)                              | First cycle                                                                                                 |       | 200  |       | nnm                |

| Thermal hysteresis ·                                | Additional cycles                                                                                           |       | 50   |       | ppm                |

| POWER REQUIREMENTS <sup>(5)</sup>                   |                                                                                                             |       |      |       |                    |

|                                                     | $AV_{DD}$ = 3.6 V to 5.5 V, normal mode, internal reference off, Digital inputs at VDD or GND               |       | 0.25 | 0.5   |                    |

|                                                     | AV <sub>DD</sub> = 3.6 V to 5.5 V, normal mode, internal reference off, Digital inputs at TTL level         |       |      | 4     |                    |

|                                                     | AV <sub>DD</sub> = 3.6 V to 5.5 V, normal mode, internal reference on, Digital inputs at VDD or GND         |       | 0.9  | 1.6   | mA                 |

|                                                     | AV <sub>DD</sub> = 3.6 V to 5.5 V, normal mode, internal reference on, Digital inputs at TTL level          |       |      | 5     |                    |

| 5                                                   | AV <sub>DD</sub> = 3.6 V to 5.5 V, power-down modes, Digital inputs at VDD or GND                           |       | 0.55 | 4     | μΑ                 |

| Power supply current (I <sub>DD</sub> )             | AV <sub>DD</sub> = 2.7 V to 3.6 V, normal mode, internal reference off, Digital inputs at VDD or GND        |       | 0.2  | 0.4   |                    |

|                                                     | AV <sub>DD</sub> = 2.7 V to 3.6 V, normal mode, internal reference off, Digital inputs at TTL level         |       |      | 0.8   | ^                  |

|                                                     | AV <sub>DD</sub> = 2.7 V to 3.6 V, normal mode, internal reference on, Digital inputs at VDD or GND         |       | 0.73 | 1.4   | mA                 |

|                                                     | AV <sub>DD</sub> = 2.7 V to 3.6 V, normal mode, internal reference on, Digital inputs at TTL level          |       |      | 1.8   |                    |

|                                                     | AV <sub>DD</sub> = 2.7 V to 3.6 V, power-down modes, Digital inputs at VDD or GND                           |       | 0.35 | 3     | μΑ                 |

<sup>(4)</sup> See the *Application Information* section of this data sheet.

<sup>(5)</sup> Input code = mid-scale, no load

# **Electrical Characteristics (continued)**

At AV<sub>DD</sub> = 2.7 V to 5.5 V and  $T_A = -40^{\circ}C$  to 125°C (unless otherwise noted).

| PARAMETER         | TEST CONDITIONS                                                                                      | MIN | TYP  | MAX  | UNIT  |

|-------------------|------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Power dissipation | AV <sub>DD</sub> = 3.6 V to 5.5 V, normal mode, internal reference off, Digital inputs at VDD or GND |     | 0.9  | 2.75 | ma\\\ |

|                   | AV <sub>DD</sub> = 3.6 V to 5.5 V, normal mode, internal reference on, Digital inputs at VDD or GND  |     | 3.2  | 8.8  | mW    |

|                   | $AV_{DD}$ = 3.6 V to 5.5 V, power-down modes, Digital inputs at VDD or GND                           |     | 2    | 22   | μW    |

|                   | AV <sub>DD</sub> = 2.7 V to 3.6 V, normal mode, internal reference off, Digital inputs at VDD or GND |     | 0.54 | 1.44 | >4/   |

|                   | AV <sub>DD</sub> = 2.7 V to 3.6 V, normal mode, internal reference on, Digital inputs at VDD or GND  |     | 1.97 | 5    | mW    |

|                   | $AV_{DD}$ = 2.7 V to 3.6 V, power-down modes, Digital inputs at VDD or GND                           |     | 0.95 | 10.8 | μW    |

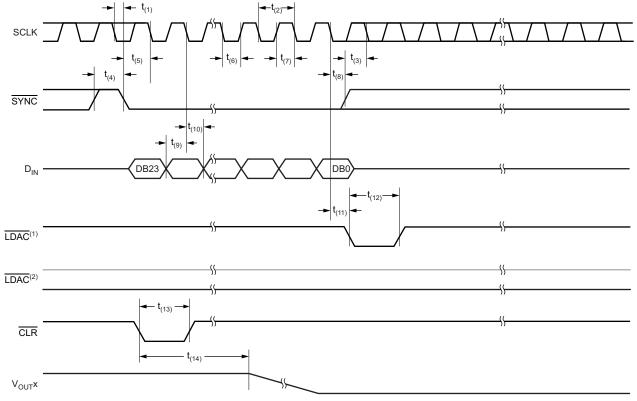

# 7.6 Timing Requirements (1)(2)

At  $AV_{DD} = 2.7 \text{ V}$  to 5.5 V, external  $V_{REFIN} = 2.5 \text{ V}$  to 5.5 V, and over  $-40^{\circ}\text{C}$  to 125°C (unless otherwise noted). See Figure 1.

|                     |                                                                                        | DAC756xT, DAC816xT, DAC856xT |     | UNIT |     |

|---------------------|----------------------------------------------------------------------------------------|------------------------------|-----|------|-----|

|                     |                                                                                        | MIN                          | TYP | MAX  |     |

| f <sub>(SCLK)</sub> | Serial clock frequency                                                                 |                              |     | 50   | MHz |

| t <sub>(1)</sub>    | SCLK falling edge to SYNC falling edge (for successful write operation)                | 10                           |     |      | ns  |

| t <sub>(2)</sub>    | SCLK cycle time                                                                        | 20                           |     |      | ns  |

| t <sub>(3)</sub>    | SYNC rising edge to 23 <sup>rd</sup> SCLK falling edge (for successful SYNC interrupt) | 13                           |     |      | ns  |

| t <sub>(4)</sub>    | Minimum SYNC HIGH time                                                                 | 15                           |     |      | ns  |

| t <sub>(5)</sub>    | SYNC to SCLK falling edge setup time                                                   | 13                           |     |      | ns  |

| t <sub>(6)</sub>    | SCLK LOW time                                                                          | 8                            |     |      | ns  |

| t <sub>(7)</sub>    | SCLK HIGH time                                                                         | 8                            |     |      | ns  |

| t <sub>(8)</sub>    | SCLK falling edge to SYNC rising edge                                                  | 10                           |     |      | ns  |

| t <sub>(9)</sub>    | Data setup time                                                                        | 6                            |     |      | ns  |

| t <sub>(10)</sub>   | Data hold time                                                                         | 6                            |     |      | ns  |

| t <sub>(11)</sub>   | SCLK falling edge to LDAC falling edge for asynchronous LDAC update mode               | 5                            |     |      | ns  |

| t <sub>(12)</sub>   | LDAC pulse duration, LOW time                                                          | 10                           |     |      | ns  |

| t <sub>(13)</sub>   | CLR pulse duration, LOW time                                                           | 80                           |     |      | ns  |

| t <sub>(14)</sub>   | CLR falling edge to start of V <sub>OUT</sub> transition                               |                              |     | 100  | ns  |

- (1) All input signals are specified with  $t_r = t_f = 1 \text{ ns/V}$  (10% to 90% of AV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2.

- (2) See the Serial Write Operation timing diagram (Figure 1).

- (1) Asynchronous LDAC update mode. For more information, see the LDAC Functionality section.

- (2) Synchronous LDAC update mode; LDAC remains low. For more information, see the LDAC Functionality section.

Figure 1. Timing Diagram, Serial Write Operation

# 7.7 Typical Characteristics

**Table 1. Typical Characteristics: Internal Reference Performance**

| MEASUREMENT                                            | POWER-SUPPLY<br>VOLTAGE | FIGURE NUMBER |

|--------------------------------------------------------|-------------------------|---------------|

| Internal Reference Voltage vs Temperature              |                         | Figure 2      |

| Internal Reference Voltage Temperature Drift Histogram |                         | Figure 3      |

| Internal Reference Voltage vs Load Current             | 5.5 V                   | Figure 4      |

| Internal Reference Voltage vs Time                     |                         | Figure 5      |

| Internal Reference Noise Density vs Frequency          |                         | Figure 6      |

| Internal Reference Voltage vs Supply Voltage           | 2.7 V-5.5 V             | Figure 7      |

**Table 2. Typical Characteristics: DAC Static Performance**

| MEASUREMENT                                        |           | POWER-SUPPLY<br>VOLTAGE | FIGURE NUMBER |

|----------------------------------------------------|-----------|-------------------------|---------------|

| FULL-SCALE, GAIN, OFFSET AND ZERO-CODE             | ERRORS    | '                       |               |

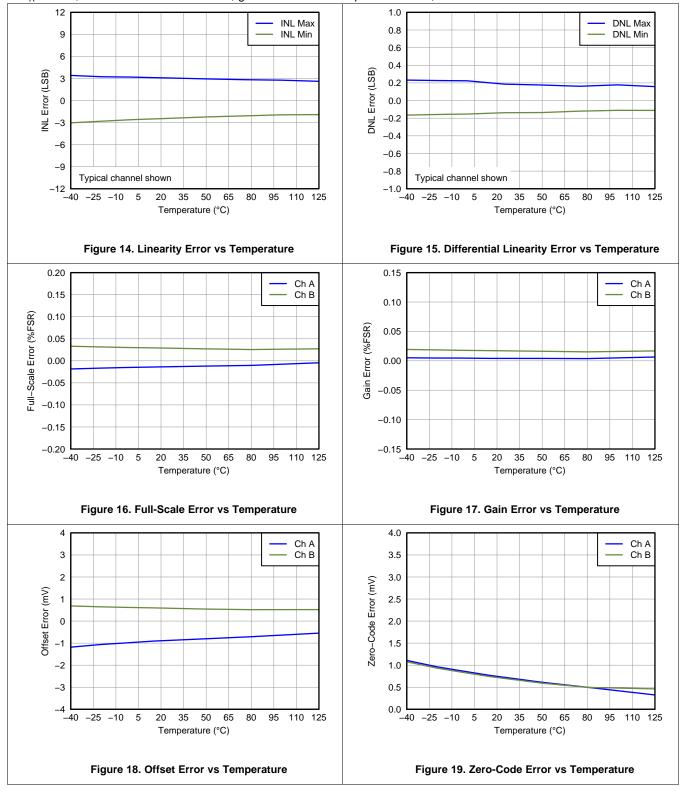

| Full-Scale Error vs Temperature                    |           |                         | Figure 16     |

| Gain Error vs Temperature                          |           | 5.5 V                   | Figure 17     |

| Offset Error vs Temperature                        |           | 5.5 V                   | Figure 18     |

| Zero-Code Error vs Temperature                     |           |                         | Figure 19     |

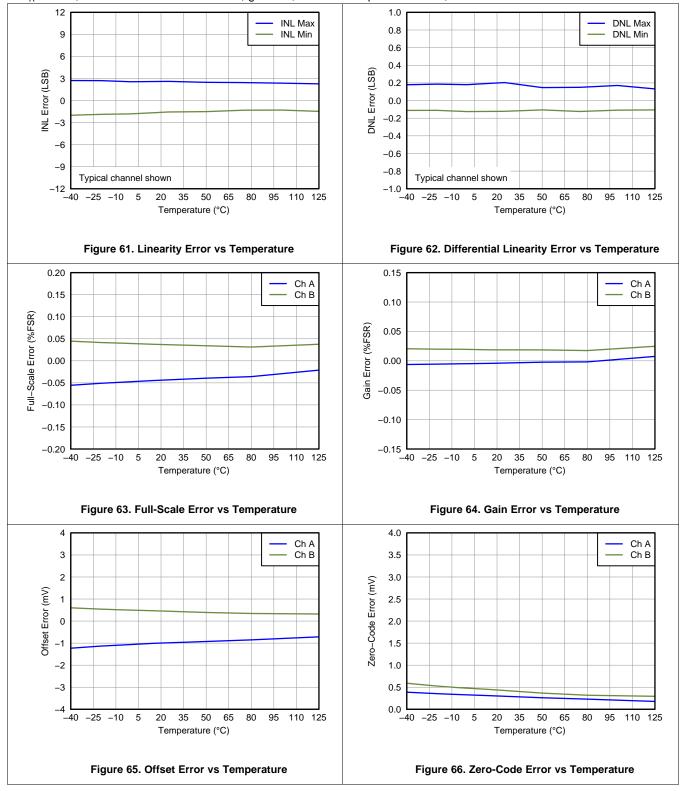

| Full-Scale Error vs Temperature                    |           |                         | Figure 63     |

| Gain Error vs Temperature                          |           | 2.7 V                   | Figure 64     |

| Offset Error vs Temperature                        |           | 2.7 V                   | Figure 65     |

| Zero-Code Error vs Temperature                     |           |                         | Figure 66     |

| LOAD REGULATION                                    |           |                         |               |

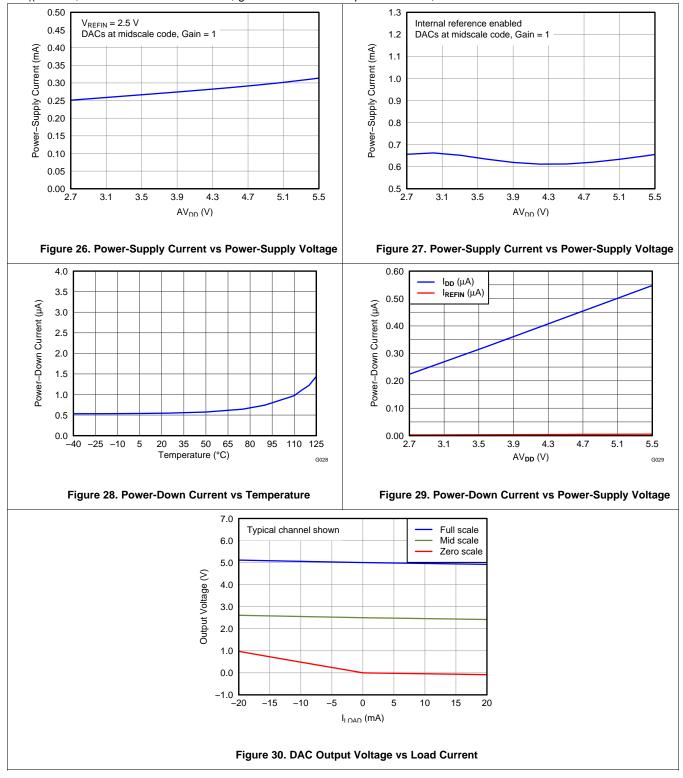

| DAC Output Voltage up Lood Current                 |           | 5.5 V                   | Figure 30     |

| DAC Output Voltage vs Load Current                 |           | 2.7 V                   | Figure 74     |

| DIFFERENTIAL NONLINEARITY ERROR                    |           |                         |               |

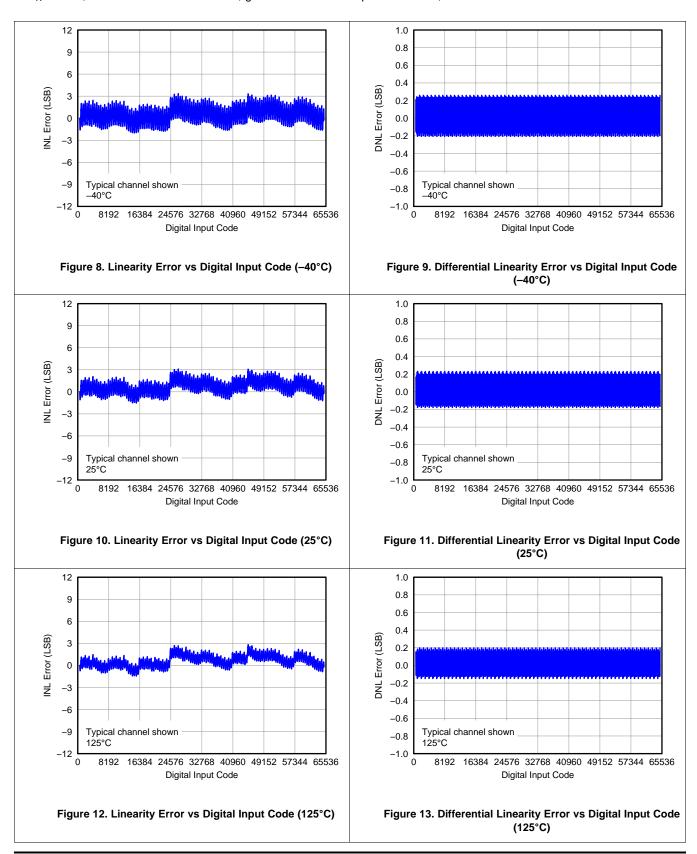

|                                                    | T = -40°C |                         | Figure 9      |

| Differential Linearity Error vs Digital Input Code | T = 25°C  | 5.5 V                   | Figure 11     |

|                                                    | T = 125°C | 5.5 V                   | Figure 13     |

| Differential Linearity Error vs Temperature        |           |                         | Figure 15     |

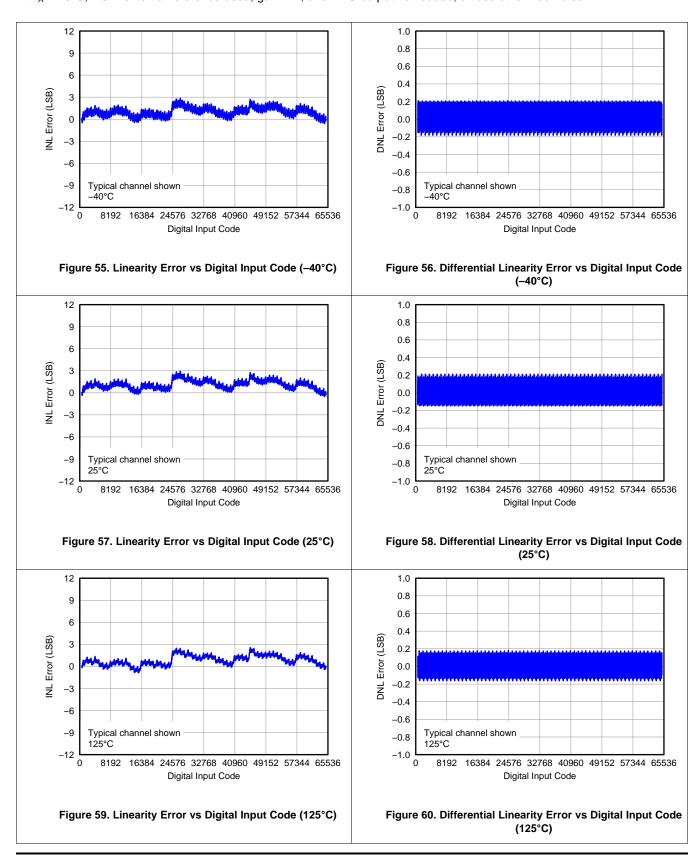

|                                                    | T = -40°C |                         | Figure 56     |

| Differential Linearity Error vs Digital Input Code | T = 25°C  | 2.7 V                   | Figure 58     |

|                                                    | T = 125°C | 2.1 V                   | Figure 60     |

| Differential Linearity Error vs Temperature        |           |                         | Figure 62     |

| INTEGRAL NONLINEARITY ERROR (RELATIVE              | ACCURACY) |                         |               |

|                                                    | T = -40°C |                         | Figure 8      |

| Linearity Error vs Digital Input Code              | T = 25°C  | 5.5 V                   | Figure 10     |

|                                                    | T = 125°C | 5.5 V                   | Figure 12     |

| Linearity Error vs Temperature                     |           |                         | Figure 14     |

|                                                    | T = -40°C |                         | Figure 55     |

| Linearity Error vs Digital Input Code              | T = 25°C  | 2.7 V                   | Figure 57     |

|                                                    | T = 125°C | 2.1 V                   | Figure 59     |

| Linearity Error vs Temperature                     |           |                         | Figure 61     |

# Table 2. Typical Characteristics: DAC Static Performance (continued)

| MEASUREMENT                                   |                           | POWER-SUPPLY<br>VOLTAGE | FIGURE NUMBER |

|-----------------------------------------------|---------------------------|-------------------------|---------------|

| POWER-DOWN CURRENT                            |                           | <u> </u>                |               |

| Power-Down Current vs Temperature             |                           | 5.5 V                   | Figure 28     |

| Power-Down Current vs Power-Supply Voltage    |                           | 2.7 V - 5.5 V           | Figure 29     |

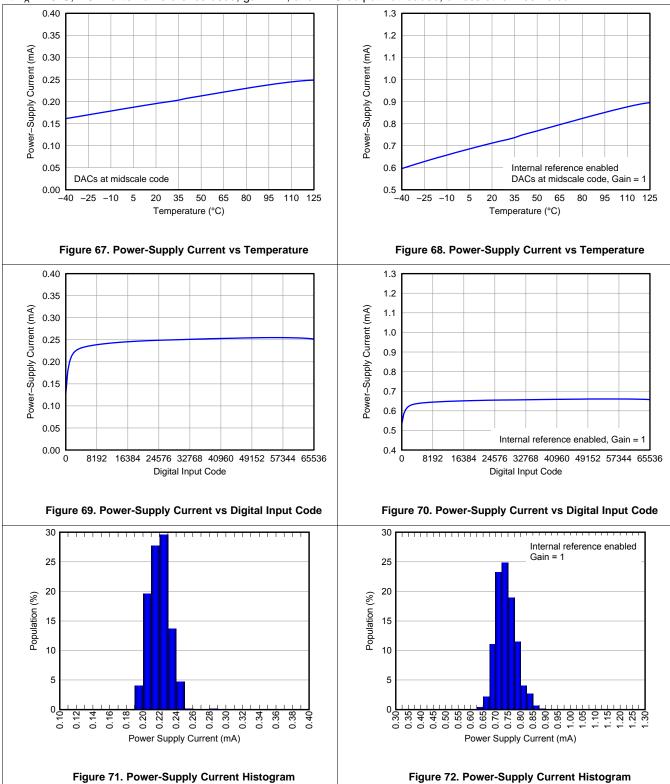

| Power-Down Current vs Temperature             |                           | 2.7 V                   | Figure 73     |

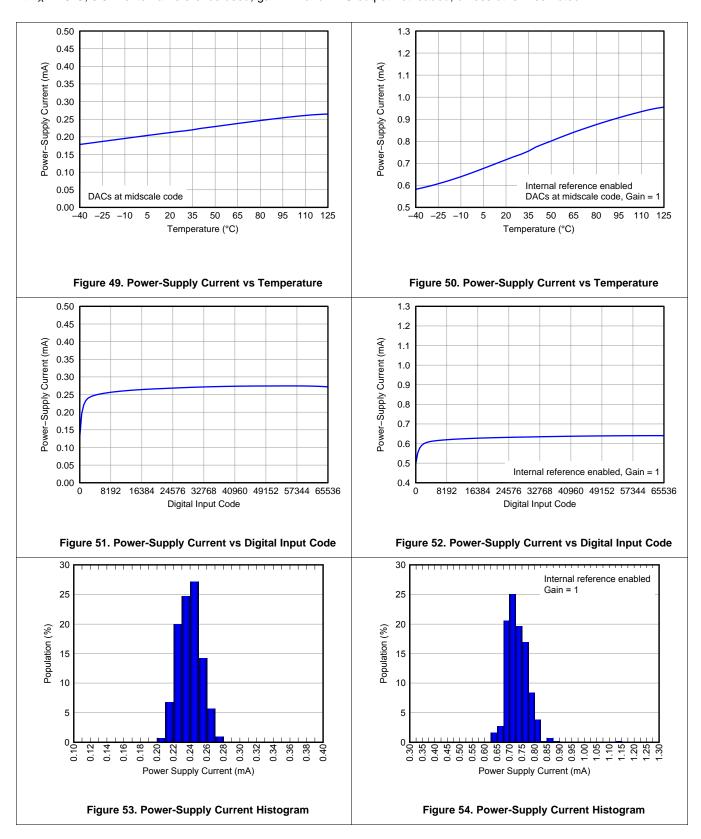

| POWER-SUPPLY CURRENT                          |                           |                         |               |

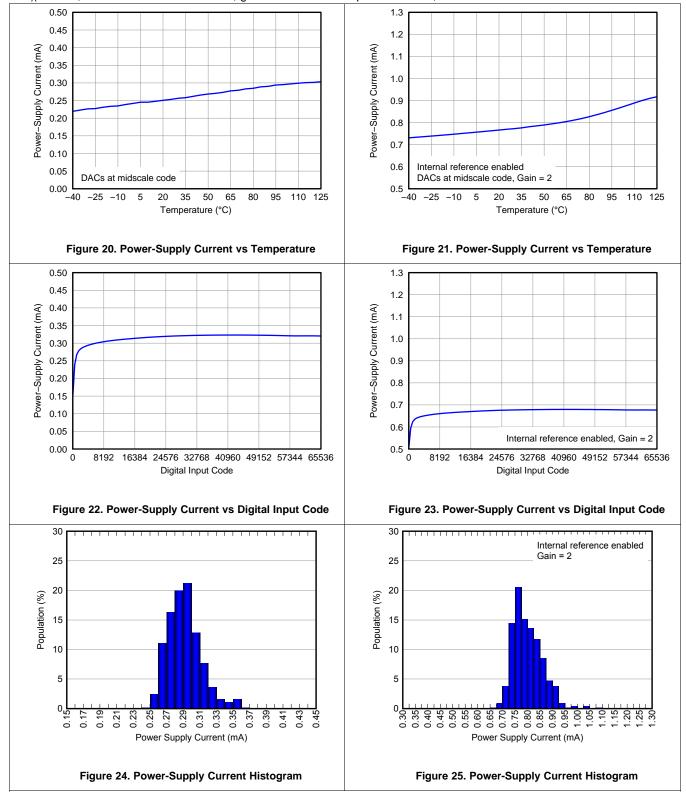

| Downer Supply Current ve Temperature          | External V <sub>REF</sub> |                         | Figure 20     |

| Power-Supply Current vs Temperature           | Internal V <sub>REF</sub> |                         | Figure 21     |

| Power-Supply Current vs Digital Input Code    | External V <sub>REF</sub> | 5.5 V                   | Figure 22     |

| Power-Supply Current vs Digital Input Code    | Internal V <sub>REF</sub> | 5.5 V                   | Figure 23     |

| Devices Councils Councils Histories           | External V <sub>REF</sub> |                         | Figure 24     |

| Power-Supply Current Histogram                | Internal V <sub>REF</sub> |                         | Figure 25     |

| Davier County County to Davier County Valtage | External V <sub>REF</sub> | 2.7 V – 5.5 V           | Figure 26     |

| Power-Supply Current vs Power-Supply Voltage  | Internal V <sub>REF</sub> | 2.7 V - 5.5 V           | Figure 27     |

| Dower Supply Current ve Temperature           | External V <sub>REF</sub> |                         | Figure 49     |

| Power-Supply Current vs Temperature           | Internal V <sub>REF</sub> |                         | Figure 50     |

| Devices Comply Company on Digital India Conde | External V <sub>REF</sub> | 3.6 V                   | Figure 51     |

| Power-Supply Current vs Digital Input Code    | Internal V <sub>REF</sub> | 3.6 V                   | Figure 52     |

| Dower Cumply Current Histogram                | External V <sub>REF</sub> |                         | Figure 53     |

| Power-Supply Current Histogram                | Internal V <sub>REF</sub> |                         | Figure 54     |

| Device County County to Terror control        | External V <sub>REF</sub> |                         | Figure 67     |

| Power-Supply Current vs Temperature           | Internal V <sub>REF</sub> |                         | Figure 68     |

| Douge Cumply Current ve Digital Innut Code    | External V <sub>REF</sub> | 2.7 V                   | Figure 69     |

| Power-Supply Current vs Digital Input Code    | Internal V <sub>REF</sub> | Z.1 V                   | Figure 70     |

| Power Supply Current Histogram                | External V <sub>REF</sub> |                         | Figure 71     |

| Power-Supply Current Histogram                | Internal V <sub>REF</sub> |                         | Figure 72     |

**Table 3. Typical Characteristics: DAC Dynamic Performance**

| MEASUREMENT                  |                                   | POWER-SUPPLY<br>VOLTAGE | FIGURE NUMBER |

|------------------------------|-----------------------------------|-------------------------|---------------|

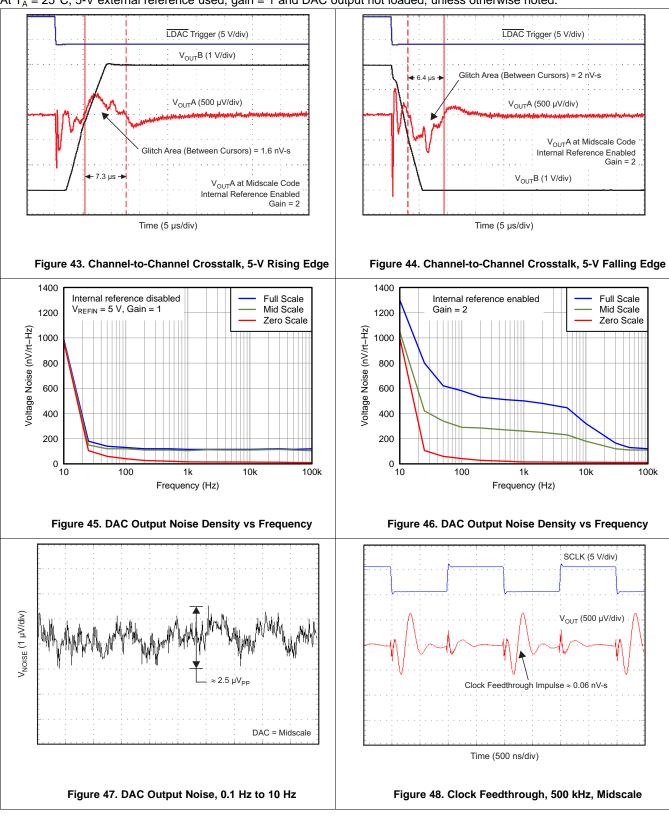

| CHANNEL-TO-CHANNEL CROSS     | STALK                             |                         |               |

| Channel-to-Channel Crosstalk | 5-V Rising Edge                   | F.F.V                   | Figure 43     |

| Channel-to-Channel Crosstalk | 5-V Falling Edge                  | 5.5 V                   | Figure 44     |

| CLOCK FEEDTHROUGH            |                                   | •                       |               |

| Clark Frankhaussk            | COO Id la Midagala                | 5.5 V<br>2.7 V          | Figure 48     |

| Clock Feedthrough            | 500 kHz, Midscale                 |                         | Figure 87     |

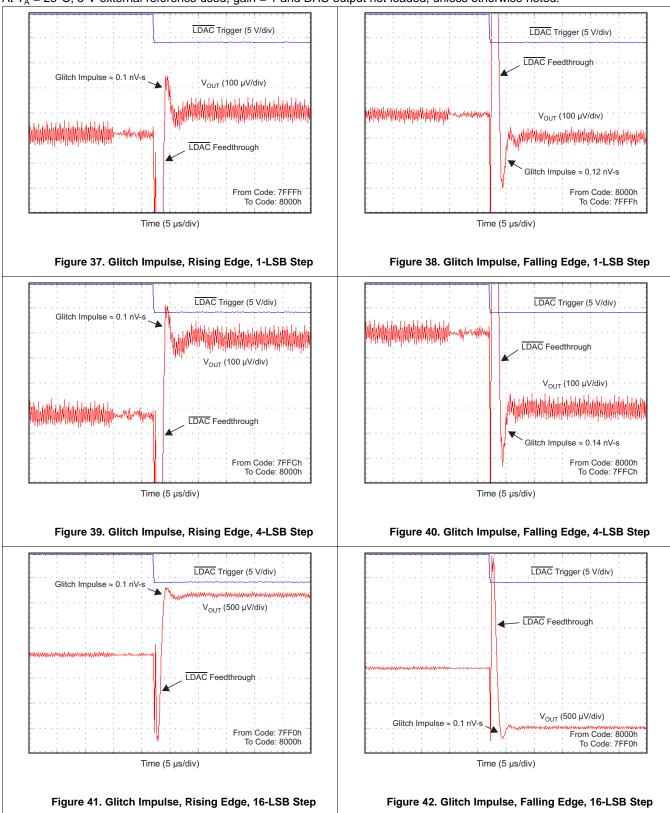

| GLITCH IMPULSE               |                                   |                         |               |

| Clitch Impulse 4 LCD Step    | Rising Edge, Code 7FFFh to 8000h  |                         | Figure 37     |

| Glitch Impulse, 1-LSB Step   | Falling Edge, Code 8000h to 7FFFh |                         | Figure 38     |

| Clitch Impulses A LCD Cton   | Rising Edge, Code 7FFCh to 8000h  | Ī                       | Figure 39     |

| Glitch Impulse, 4-LSB Step   | Falling Edge, Code 8000h to 7FFCh | 5.5 V                   | Figure 40     |

| Clitch Issaulas AC LCD Ctar  | Rising Edge, Code 7FF0h to 8000h  |                         | Figure 41     |

| Glitch Impulse, 16-LSB Step  | Falling Edge, Code 8000h to 7FF0h |                         | Figure 42     |

# Table 3. Typical Characteristics: DAC Dynamic Performance (continued)

| MEA                              | ASUREMENT                         | POWER-SUPPLY<br>VOLTAGE | FIGURE NUMBER |

|----------------------------------|-----------------------------------|-------------------------|---------------|

| Clitch Impulse 4 I CD Step       | Rising Edge, Code 7FFFh to 8000h  |                         | Figure 79     |

| Glitch Impulse, 1-LSB Step       | Falling Edge, Code 8000h to 7FFFh |                         | Figure 80     |

| Glitch Impulse, 4-LSB Step       | Rising Edge, Code 7FFCh to 8000h  | 2.7 V                   | Figure 81     |

| Giller Impulse, 4-LSB Step       | Falling Edge, Code 8000h to 7FFCh | 2.7 V                   | Figure 82     |

| Clitch Impulse 46 LCB Step       | Rising Edge, Code 7FF0h to 8000h  |                         | Figure 83     |

| Glitch Impulse, 16-LSB Step      | Falling Edge, Code 8000h to 7FF0h |                         | Figure 84     |

| NOISE                            |                                   |                         |               |

| DAC Output Noise Density vs      | External V <sub>REF</sub>         |                         | Figure 45     |

| Frequency                        | Internal V <sub>REF</sub>         | 5.5 V                   | Figure 46     |

| DAC Output Noise 0.1 Hz to 10 Hz | External V <sub>REF</sub>         |                         | Figure 47     |

| POWER-ON GLITCH                  |                                   |                         |               |

|                                  | Reset to Zero Scale               | <i>5.5.</i> V           | Figure 35     |

| Power-On Glitch                  | Reset to Midscale                 | 5.5 V                   | Figure 36     |

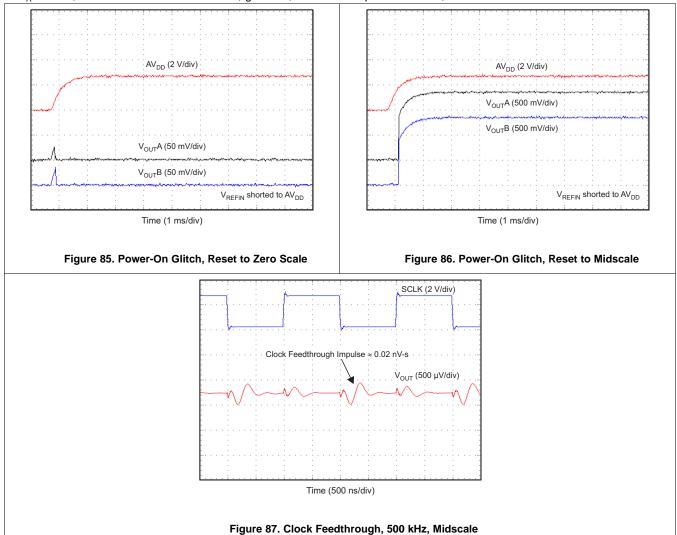

| Power-On Gillen                  | Reset to Zero Scale               | 2.7 V                   | Figure 85     |

|                                  | Reset to Midscale                 |                         | Figure 86     |

| SETTLING TIME                    |                                   |                         |               |

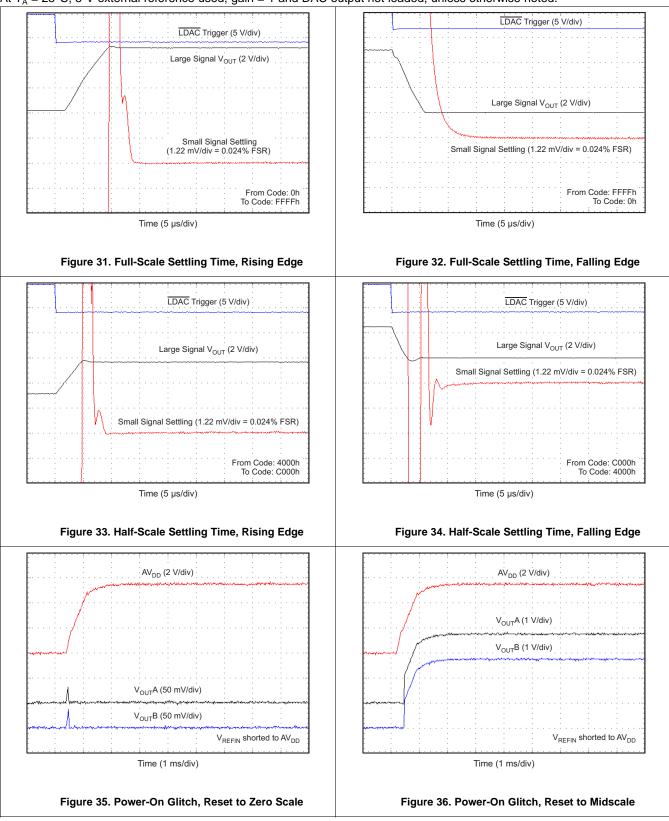

| Full Cools Cottling Times        | Rising Edge, Code 0h to FFFFh     |                         | Figure 31     |

| Full-Scale Settling Time         | Falling Edge, Code FFFFh to 0h    | 5.5 V                   | Figure 32     |

| Light Cools Cattling Time        | Rising Edge, Code 4000h to C000h  | 5.5 V                   | Figure 33     |

| Half-Scale Settling Time         | Falling Edge, Code C000h to 4000h |                         | Figure 34     |

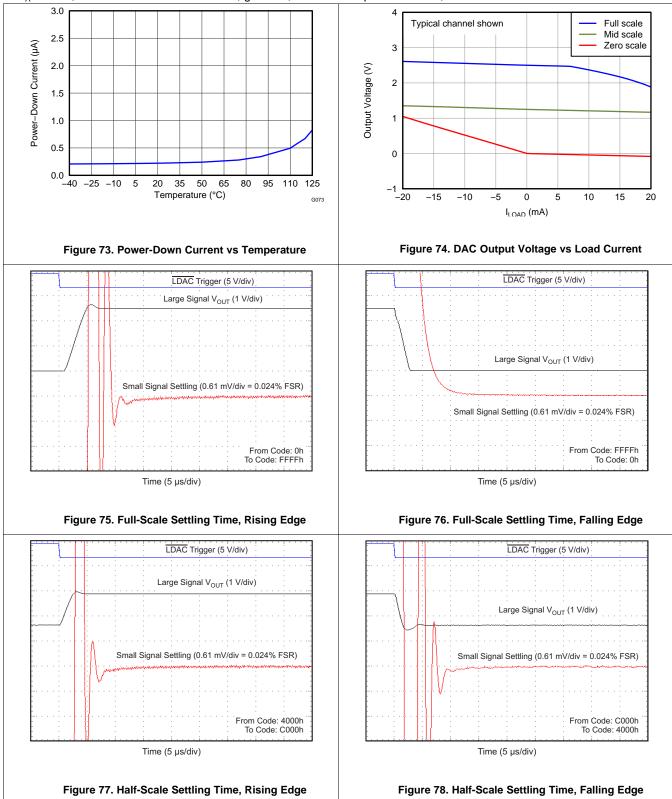

| Full Ocale Calling Time          | Rising Edge, Code 0h to FFFFh     |                         | Figure 75     |

| Full-Scale Settling Time         | Falling Edge, Code FFFFh to 0h    | 2.7 V                   | Figure 76     |

| Holf Cools Cottling Time         | Rising Edge, Code 4000h to C000h  | Z./ V                   | Figure 77     |

| Half-Scale Settling Time         | Falling Edge, Code C000h to 4000h |                         | Figure 78     |

## 7.7.1 Typical Characteristics: Internal Reference

At  $T_A = 25$ °C,  $AV_{DD} = 5.5$  V, gain = 2, and  $V_{REFOUT}$  unloaded, unless otherwise noted.

# 7.7.2 Typical Characteristics: DAC at $AV_{DD} = 5.5 \text{ V}$

At T<sub>A</sub> = 25°C, 5-V external reference used, gain = 1 and DAC output not loaded, unless otherwise noted.

## 7.7.3 Typical Characteristics: DAC at $AV_{DD} = 3.6 \text{ V}$

## 7.7.4 Typical Characteristics: DAC at $AV_{DD} = 2.7 \text{ V}$

At T<sub>A</sub> = 25°C, 2.5-V external reference used, gain = 1, and DAC output not loaded, unless otherwise noted.

## 8 Detailed Description

#### 8.1 Overview

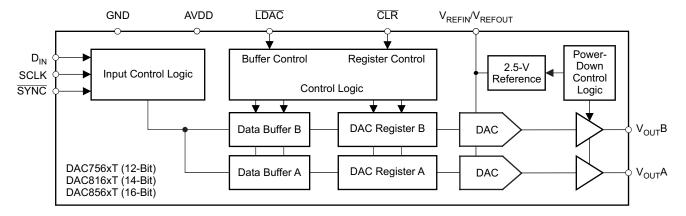

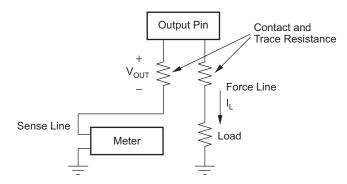

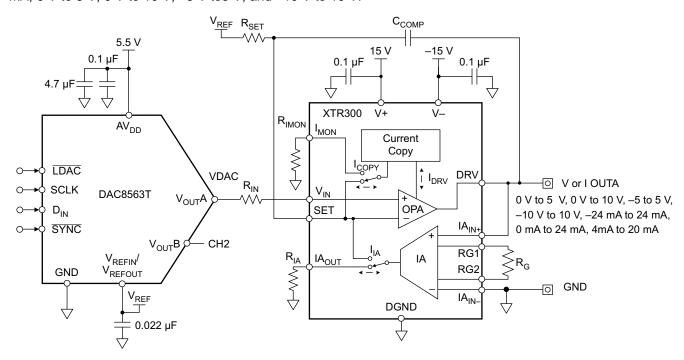

The DAC756xT, DAC816xT, and DAC856xT devices are low-power, voltage-output, dual-channel, 16-, 14-, and 12-bit digital-to-analog converters (DACs), respectively. These devices include a 2.5-V, 4-ppm/ $^{\circ}$ C internal reference, giving a full-scale output voltage range of 2.5 V or 5 V. The internal reference has an initial accuracy of  $\pm 5$  mV and can source or sink up to 20 mA at the  $V_{REFOUT}$  pin.

#### 8.2 Functional Block Diagram

## 8.3 Feature Description

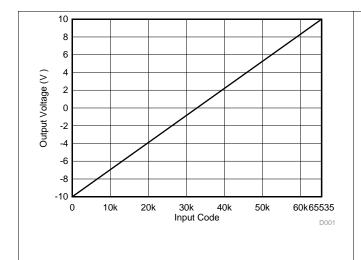

## 8.3.1 Digital-to-Analog Converter (DAC)

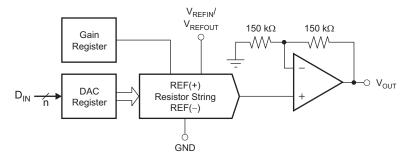

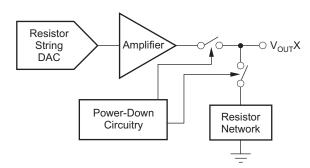

The DAC756xT, DAC816xT, and DAC856xT architecture consists of two string DACs, each followed by an output buffer amplifier. The devices include an internal 2.5-V reference with 4-ppm/°C temperature drift performance. Figure 88 shows a principal block diagram of the DAC architecture.

Figure 88. DAC Architecture

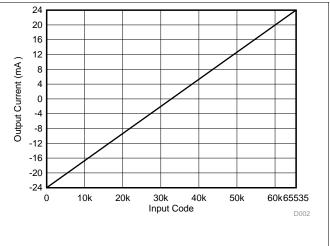

The input coding to the DAC756xT, DAC816xT, and DAC856xT devices is straight binary, so the ideal output voltage is given by Equation 1:

$$V_{OUT} = \left(\frac{D_{IN}}{2^n}\right) \times V_{REF} \times Gain$$

(1)

where:

n = resolution in bits; either 12 (DAC756xT), 14 (DAC816xT) or 16 (DAC856xT)

$D_{IN}$  = decimal equivalent of the binary code that is loaded to the DAC register.  $D_{IN}$  ranges from 0 to  $2^n - 1$ .  $V_{REF}$  = DAC reference voltage; either  $V_{REFOUT}$  from the internal 2.5-V reference or  $V_{REFIN}$  from an external reference.

Gain = 1 by default when internal reference is disabled (using external reference), and gain = 2 by default when using internal reference. Gain can also be manually set to either 1 or 2 using the gain register. See the *Gain Function* section for more information.

## **Feature Description (continued)**

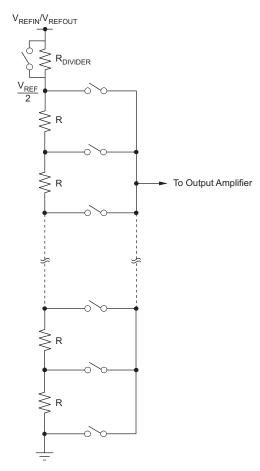

#### 8.3.1.1 Resistor String

The resistor string section is shown in Figure 89. It is simply a string of resistors, each of value *R*. The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier by closing one of the switches connecting the string to the amplifier. The resistor string architecture results in monotonicity. The R<sub>DIVIDER</sub> switch is controlled by the gain registers (see the *Gain Function* section). Because the output amplifier has a gain of 2, R<sub>DIVIDER</sub> is not shorted when the DAC-n gain is set to 1 (default if internal reference is disabled), and is shorted when the DAC-n gain is set to 2 (default if internal reference is enabled).

Figure 89. Resistor String

#### 8.3.1.2 Output Amplifier

The output buffer amplifier is capable of generating rail-to-rail voltages on its output, giving a maximum output range of 0 V to  $AV_{DD}$ . It is capable of driving a load of 2 k $\Omega$  in parallel with 3 nF to GND. The typical slew rate is 0.75 V/ $\mu$ s, with a typical full-scale settling time of 14  $\mu$ s as shown in Figure 31, Figure 32, Figure 75 and Figure 76.

#### **Feature Description (continued)**

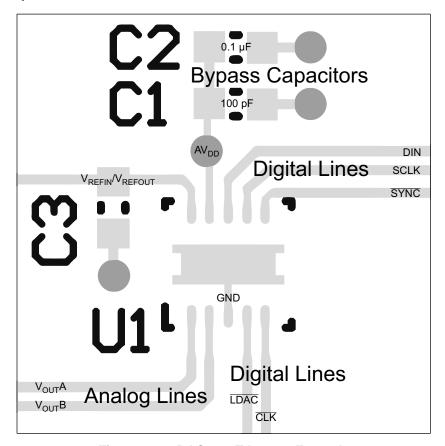

#### 8.3.2 Internal Reference

The DAC756xT, DAC816xT, and DAC856xT devices include a 2.5-V internal reference that is disabled by default. The internal reference is externally available at the  $V_{REFIN}/V_{REFOUT}$  pin. The internal reference output voltage is 2.5 V and can sink and source up to 20 mA.

A minimum 150-nF capacitor is recommended between the reference output and GND for noise filtering.

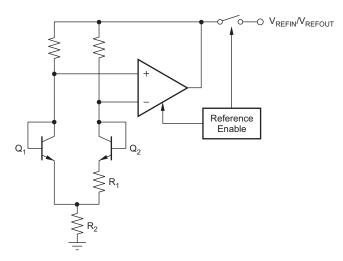

The internal reference of the DAC756xT, DAC816xT, and DAC856xT devices is a bipolar transistor-based precision band-gap voltage reference. Figure 90 shows the basic band-gap topology. Transistors  $Q_1$  and  $Q_2$  are biased such that the current density of  $Q_1$  is greater than that of  $Q_2$ . The difference of the two base-emitter voltages ( $V_{BE1} - V_{BE2}$ ) has a positive temperature coefficient and is forced across resistor  $R_1$ . This voltage is amplified and added to the base-emitter voltage of  $Q_2$ , which has a negative temperature coefficient. The resulting output voltage is virtually independent of temperature. The short-circuit current is limited by design to approximately 100 mA.

Figure 90. Band-Gap Reference Simplified Schematic

#### 8.3.3 Power-On Reset

## 8.3.3.1 Power-On Reset to Zero-Scale

The DAC7562T, DAC8162T, and DAC8562T devices contain a power-on-reset circuit that controls the output voltage during power up. All device registers are reset as shown in Table 4. At power up, all DAC registers are filled with zeros and the output voltages of all DAC channels are set to zero volts. Each DAC channel remains that way until a valid load command is written to it. The power-on reset is useful in applications where it is important to know the state of the output of each DAC while the device is in the process of powering up. No device pin should be brought high before applying power to the device. The internal reference is disabled by default and remains that way until a valid reference-change command is executed.

#### 8.3.3.2 Power-On Reset to Mid-Scale

The DAC7563T, DAC8163T, and DAC8563T devices contain a power-on reset circuit that controls the output voltage during power up. At power up, all DAC registers are reset to mid-scale code and the output voltages of all DAC channels are set to  $V_{REFIN}$  / 2 volts. Each DAC channel remains that way until a valid load command is written to it. The power-on reset is useful in applications where it is important to know the state of the output of each DAC while the device is in the process of powering up. No device pin should be brought high before applying power to the device. The internal reference is powered off or down by default and remains that way until a valid reference-change command is executed. If using an external reference, it is acceptable to power on the  $V_{REFIN}$  pin either at the same time as or after applying  $AV_{DD}$ .

Table 4. DACxx62T and DACxx63T Power-On Reset Values

| REGISTER                    |                                    | DEFAULT SETTING |

|-----------------------------|------------------------------------|-----------------|

| DAC and input registers     | DACxx62T                           | Zero-scale      |

| DAC and input registers     | DACxx63T                           | Mid-scale       |

| LDAC registers              | LDAC pin enabled for both channels |                 |

| Power-down registers        | DACs powered up                    |                 |

| Internal reference register | Internal reference di              | sabled          |

| Gain registers              | Gain = 1 for both channels         |                 |

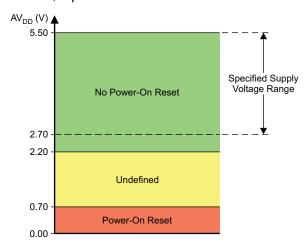

#### 8.3.3.3 Power-On Reset (POR) Levels

When the device powers up, a POR circuit sets the device in default mode as shown in Table 4. The POR circuit requires specific  $AV_{DD}$  levels, as indicated in Figure 91, to ensure discharging of internal capacitors and to reset the device on power up. In order to ensure a power-on reset,  $AV_{DD}$  must be below 0.7 V for at least 1 ms. When  $AV_{DD}$  drops below 2.2 V but remains above 0.7 V (shown as the undefined region), the device may or may not reset under all specified temperature and power-supply conditions. In this case, TI recommends a power-on reset. When  $AV_{DD}$  remains above 2.2 V, a power-on reset does not occur.

Figure 91. Relevant Voltage Levels for POR Circuit

#### 8.4 Device Functional Modes

#### 8.4.1 Power-Down Modes

The DAC756xT, DAC816xT, and DAC856xT devices have two separate sets of power-down commands. One set is for the DAC channels and the other set is for the internal reference. The internal reference is forced to a powered-down state while both DAC channels are powered down, and is only enabled if any DAC channel is also in the normal mode of operation. For more information on the internal reference control, see the *Internal Reference Enable Register* section.

#### 8.4.1.1 DAC Power-Down Commands

The DAC756xT, DAC816xT, and DAC856xT DACs use four modes of operation. These modes are accessed by setting the serial interface command bits to 100. Once the command bits are set correctly, the four different power-down modes are software programmable by setting bits DB5 and DB4 in the shift register. Table 5 and Table 6 show the different power-down options. For more information on how to set the DAC operating mode see Table 17.

DB5

DB4

DAC Modes of Operation

0

0

Selected DACs power up (normal mode, default)

0

1

Selected DACs power down, output 1 kΩ to GND

1

0

Selected DACs power down, output 100 kΩ to GND

1

1

Selected DACs power down, output Hi-Z to GND

1

1

Selected DACs power down, output Hi-Z to GND

**Table 5. DAC-n Operating Modes**

Table 6. DAC-n Selection for Operating Modes

| DAC-B (DB1), DAC-A (DB0) | Operating Mode                                     |  |

|--------------------------|----------------------------------------------------|--|

| 0                        | DAC-n does not change operating mode               |  |

| 1                        | 1 DAC-n operating mode set to value on PD1 and PD0 |  |

It is possible to write to the DAC register or buffer of the DAC channel that is powered down. When the DAC channel is then powered up, it powers up to this new value.

The advantage of the available power-down modes is that the output impedance of the device is known while it is in power-down mode. As described in Table 5, there are three different power-down options.  $V_{OUT}$  can be connected internally to GND through a 1-k $\Omega$  resistor, a 100-k $\Omega$  resistor, or open-circuited (Hi-Z). The DAC power-down circuitry is shown in Figure 92.

Figure 92. Output Stage

#### 8.4.2 Gain Function

The gain register controls the GAIN setting in the DAC transfer function:

$$V_{OUT} = \left(\frac{D_{IN}}{2^n}\right) \times V_{REF} \times Gain$$

(2)

The DAC756xT, DAC816xT, and DAC856xT devices have a gain register for each channel. The gain for each channel, in Equation 2, is either 1 or 2. This gain is automatically set to 2 when using the internal reference, and is automatically set to 1 when the internal reference is disabled (default). However, each channel can have either gain by setting the registers appropriately. The gain registers are accessible by setting the serial interface command bits to 000, address bits to 010, and using DB1 for DAC-B and DB0 for DAC-A. See Table 7 and Table 17 for the full command structure. The gain registers are automatically reset to provide either gain of 1 or 2 when the internal reference is powered off or on, respectively. After the reference is powered off or on, the gain register is again accessible to change the gain.

Table 7. DAC-n Selection for Gain Register Command

| DB1, DB0 | Value | Gain                                                  |  |

|----------|-------|-------------------------------------------------------|--|

| DB0      | 0     | PAC-A uses gain = 2 (default with internal reference) |  |

|          | 1     | DAC-A uses gain = 1 (default with external reference) |  |

| DB1      | 0     | DAC-B uses gain = 2 (default with internal reference) |  |

|          | 1     | DAC-B uses gain = 1 (default with external reference) |  |

#### 8.4.3 Software Reset Function

The DAC756xT, DAC816xT, and DAC856xT devices contain a software reset feature. The software reset function is accessed by setting the serial interface command bits to 101. The software reset command contains two reset modes which are software-programmable by setting bit DB0 in the shift register. Table 8 and Table 17 show the available software reset commands.

**Table 8. Software Reset**

| DB0 | Registers Reset to Default Values                                                                            |

|-----|--------------------------------------------------------------------------------------------------------------|

| 0   | DAC registers Input registers                                                                                |

| 1   | DAC registers Input registers LDAC registers Power-down registers Internal reference register Gain registers |

#### 8.4.4 Internal Reference Enable Register

The internal reference in the DAC756xT, DAC816xT, and DAC856xT devices is disabled by default for debugging, evaluation purposes, or when using an external reference. The internal reference can be powered up and powered down by setting the serial interface command bits to 111 and configuring DB0 (see Table 9). The internal reference is forced to a powered down state while both DAC channels are powered down, and can only be enabled if any DAC channel is in normal mode of operation. During the time that the internal reference is disabled, the DAC functions normally using an external reference. At this point, the internal reference is disconnected from the  $V_{REFIN}/V_{REFOUT}$  pin (Hi-Z output).

**Table 9. Internal Reference**

| DB0                                                    | Internal Reference Configuration                      |  |

|--------------------------------------------------------|-------------------------------------------------------|--|

| 0                                                      | Disable internal reference and reset DACs to gain = 1 |  |

| 1 Enable internal reference and reset DACs to gain = 2 |                                                       |  |

#### 8.4.4.1 Enabling Internal Reference

To enable the internal reference, refer to the command structure in Table 17. When performing a power cycle to reset the device, the internal reference is switched off (default mode). In the default mode, the internal reference is powered down until a valid write sequence powers up the internal reference. However, the internal reference is forced to a disabled state while both DAC channels are powered down, and remains disabled until either DAC channel is returned to the normal mode of operation. See *DAC Power-Down Commands* for more information on DAC channel modes of operation.

#### 8.4.4.2 Disabling Internal Reference

To disable the internal reference, refer to the command structure in Table 17. When performing a power cycle to reset the device, the internal reference is disabled (default mode).

#### 8.4.5 CLR Functionality

The edge-triggered  $\overline{\text{CLR}}$  pin can be used to set the input and DAC registers immediately according to Table 10. When the  $\overline{\text{CLR}}$  pin receives a falling edge signal the clear mode is activated and changes the DAC output voltages accordingly. The device exits clear mode on the 24<sup>th</sup> falling edge of the next write to the device. If the  $\overline{\text{CLR}}$  pin receives a falling edge signal during a write sequence in normal operation, the clear mode is activated and changes the input and DAC registers immediately according to Table 10.

**Table 10. Clear Mode Reset Values**

| DEVICE                       | DAC Output Entering Clear Mode |

|------------------------------|--------------------------------|

| DAC8562T, DAC8162T, DAC7562T | Zero-scale                     |

| DAC8563T, DAC8163T, DAC7563T | Mid-scale                      |

## 8.4.6 LDAC Functionality

The DAC756xT, DAC816xT, and DAC856xT devices offer both a software and hardware simultaneous update and control function. The DAC double-buffered architecture has been designed so that new data can be entered for each DAC without disturbing the analog outputs.

DAC756xT, DAC816xT, and DAC856xT data updates can be performed either in synchronous or in asynchronous mode.

In asynchronous mode, the  $\overline{\text{LDAC}}$  pin is used as a negative edge-triggered timing signal for simultaneous DAC updates. Multiple single-channel writes can be done in order to set different channel buffers to desired values and then make a falling edge on  $\overline{\text{LDAC}}$  pin to simultaneously update the DAC output registers. Data buffers of all channels must be loaded with desired data before an  $\overline{\text{LDAC}}$  falling edge. After a high-to-low  $\overline{\text{LDAC}}$  transition, all DACs are simultaneously updated with the last contents of the corresponding data buffers. If the content of a data buffer is not changed, the corresponding DAC output remains unchanged after the  $\overline{\text{LDAC}}$  pin is triggered.  $\overline{\text{LDAC}}$  must be returned high before the next serial command is initiated.

In <u>synchronous</u> mode, data are updated with the <u>falling</u> edge of the 24<sup>th</sup> SCLK cycle, which follows a falling edge of SYNC. For such <u>synchronous</u> updates, the <u>LDAC</u> pin is not required, and it must be connected to GND permanently or asserted and held low before sending commands to the device.

Alternatively, all DAC outputs can be updated simultaneously using the built-in software function of LDAC. The LDAC register offers additional flexibility and control by allowing the selection of which DAC channel(s) should be updated simultaneously when the LDAC pin is being brought low. The LDAC register is loaded with a 2-bit word (DB1 and DB0) using command bits C2, C1, and C0 (see Table 17). The default value for each bit, and therefore for each DAC channel, is zero. If the LDAC register bit is set to 1, it overrides the LDAC pin (the LDAC pin is internally tied low for that particular DAC channel) and this DAC channel updates synchronously after the falling edge of the 24<sup>th</sup> SCLK cycle. However, if the LDAC register bit is set to 0, the DAC channel is controlled by the LDAC pin.

The combination of software and hardware simultaneous update functions is particularly useful in applications when updating a DAC channel, while keeping the other channel unaffected; see Table 11 and Table 17 for more information.

DB1, DB0

Value

\$\overline{LDAC}\$ Pin Functionality

DB0

0

DAC-A uses \$\overline{LDAC}\$ pin

1

DAC-A operates in synchronous mode

DB1

0

DAC-B uses \$\overline{LDAC}\$ pin

1

DAC-B operates in synchronous mode

Table 11. DAC-n Selection for LDAC Register Command

## 8.5 Programming

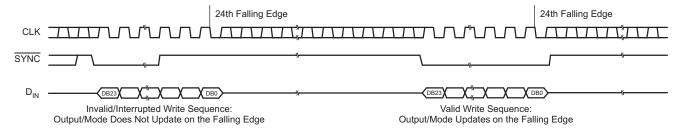

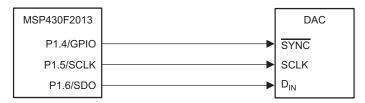

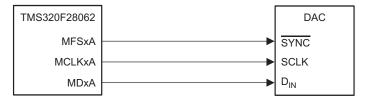

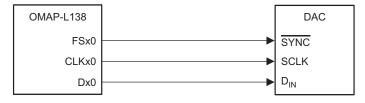

The DAC756xT, DAC816xT, and DAC856xT devices have a three-wire serial interface ( $\overline{\text{SYNC}}$ , SCLK, and D<sub>IN</sub>; see the table) compatible with SPI, QSPI, and Microwire interface standards, as well as most DSPs. See the Serial Write Operation timing diagram (Figure 1) for an example of a typical write sequence.

The DAC756xT, DAC816xT, or DAC856xT input shift register is 24 bits wide, consisting of two *don't care* bits (DB23 to DB22), three command bits (DB21 to DB19), three address bits (DB18 to DB16), and 16 data bits (DB15 to DB0). All 24 bits of data are loaded into the DAC under the control of the serial clock input, SCLK. DB23 (MSB) is the first bit that is loaded into the DAC shift register. DB23 is followed by the rest of the 24-bit word pattern, left-aligned. This configuration means that the first 24 bits of data are latched into the shift register, and any further clocking of data is ignored.

The write sequence begins by bringing the  $\overline{\text{SYNC}}$  line low. Data from the  $D_{\text{IN}}$  line are clocked into the 24-bit shift register on each falling edge of SCLK. The serial clock frequency can be as high as 50 MHz, making the DAC756xT, DAC816xT, and DAC856xT devices compatible with high-speed DSPs. On the 24<sup>th</sup> falling edge of the serial clock, the last data bit is clocked into the shift register and the shift register locks. Further clocking does not change the shift register data.

After receiving the 24<sup>th</sup> falling clock edge, the DAC756xT, DAC816xT, and DAC856xT devices decode the three command bits, three address bits and 16 data bits to perform the required function, without waiting for a SYNC rising edge. After the 24<sup>th</sup> falling edge of SCLK is received, the SYNC line may be kept low or brought high. In either case, the minimum delay time from the 24<sup>th</sup> falling SCLK edge to the next falling SYNC edge must be met in order to begin the next cycle properly; see the Serial Write Operation timing diagram (Figure 1).

A rising edge of SYNC before the 24-bit sequence is complete resets the SPI interface; no data transfer occurs. A new write sequence starts at the next falling edge of SYNC. To assure the lowest power consumption of the device, care should be taken that the levels are as close to each rail as possible.

### 8.5.1 SYNC Interrupt

In a normal write sequence, the SYNC line stays low for at least 24 falling edges of SCLK and the addressed DAC register updates on the 24<sup>th</sup> falling edge. However, if SYNC is brought high before the 23<sup>rd</sup> falling edge, it acts as an interrupt to the write sequence; the shift register resets and the write sequence is discarded. Neither an update of the data buffer contents, DAC register contents, nor a change in the operating mode occurs (as shown in Figure 93).

Figure 93. SYNC Interrupt Facility

### **Programming (continued)**

# 8.5.2 DAC Register Configuration

When the DAC registers are being written to, the DAC756xT, DAC816xT, and DAC856xT devices receive all 24 bits of data, ignore DB23 and DB22, and decode the next three bits (DB21 to DB19) in order to determine the DAC operating or control mode (see Table 12). Bits DB18 to DB16 are used to address the DAC channels (see Table 13).

Table 12. Commands for the DAC756xT, DAC816xT, and DAC856xT Devices

| C2<br>(DB21) | C1<br>(DB20) | C0<br>(DB19) | Command                                                           |

|--------------|--------------|--------------|-------------------------------------------------------------------|

| 0            | 0            | 0            | Write to input register n (Table 13)                              |

| 0            | 0            | 1            | Software LDAC, update DAC register n (Table 13)                   |

| 0            | 1            | 0            | Write to input register n (Table 13) and update all DAC registers |

| 0            | 1            | 1            | Write to input register n and update DAC register n (Table 13)    |

| 1            | 0            | 0            | Set DAC power up or -down mode                                    |

| 1            | 0            | 1            | Software reset                                                    |

| 1            | 1            | 0            | Set LDAC registers                                                |

| 1            | 1            | 1            | Enable or disable the internal reference                          |

Table 13. Address Select for the DAC756xT, DAC816xT, and DAC856xT Devices

| A2<br>(DB18) | A1<br>(DB17) | A0<br>(DB16) | Channel (n)                      |

|--------------|--------------|--------------|----------------------------------|

| 0            | 0            | 0            | DAC-A                            |

| 0            | 0            | 1            | DAC-B                            |

| 0            | 1            | 0            | Gain (only use with command 000) |

| 0            | 1            | 1            | Reserved                         |

| 1            | 0            | 0            | Reserved                         |

| 1            | 0            | 1            | Reserved                         |

| 1            | 1            | 0            | Reserved                         |

| 1            | 1            | 1            | DAC-A and DAC-B                  |

When writing to the DAC input registers the next 16, 14, or 12 bits of data that follow are decoded by the DAC to determine the equivalent analog output (see Table 14 through Table 16). The data format is straight binary, with all 0s corresponding to 0-V output and all 1s corresponding to full-scale output. For all documentation purposes, the data format and representation used here is a true 16-bit pattern (that is, FFFFh data word for full scale) that the DAC756xT, DAC816xT, and DAC856xT devices require.

Table 14. DAC856xT Data Input Register Format

|                  |   | CC | AMM | ND | ΑĽ | DRE | SS | DATA |     |     |     |     |     |    |    |    |    |    |    |    |    |    |     |

|------------------|---|----|-----|----|----|-----|----|------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----|

| X <sup>(1)</sup> | Χ | C2 | C1  | CO | A2 | A1  | Α0 | D15  | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| DB23             | 3 |    |     |    |    |     |    |      |     |     |     |     |     |    |    |    |    |    |    |    |    |    | DB0 |

(1) X' denotes don't care bits.

#### Table 15. DAC816xT Data Input Register Format

|     |   | CC | ОММА | ND | ΑĽ | DDRE | SS |                                               |  |  |  |  |  | DA | TA |  |  |   |   |  |     |

|-----|---|----|------|----|----|------|----|-----------------------------------------------|--|--|--|--|--|----|----|--|--|---|---|--|-----|

| Χ   | Х | C2 | C1   | C0 | A2 | A1   | A0 | D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 |  |  |  |  |  |    |    |  |  | Χ | Χ |  |     |

| DB2 | 3 |    |      |    |    |      |    |                                               |  |  |  |  |  |    |    |  |  |   |   |  | DB0 |

#### Table 16. DAC756xT Data Input Register Format