www.ti.com

SNLS282F - MAY 2008 - REVISED APRIL 2013

# DS32EL0421, DS32ELX0421 125 - 312.5 MHz FPGA-Link Serializer with DDR LVDS Parallel Interface

Check for Samples: DS32EL0421, DS32ELX0421

## **FEATURES**

- 5-bit DDR LVDS Parallel Data Interface

- **Programmable Transmit De-emphasis**

- Configurable Output Levels (V<sub>OD</sub>)

- Selectable DC-balanced Encoder

- **Selectable Data Scrambler**

- Remote Sense for Automatic Detection and **Negotiation of Link Status**

- On Chip LC VCOs

- Redundant Serial Output (ELX device only)

- **Data Valid Signaling to Assist with** Synchronization of Multiple Receivers

- Supports AC- and DC-coupled Signaling

- **Integrated CML and LVDS Terminations**

- Configurable PLL Loop Bandwidth

- Programmable Output Termination (50Ω or  $75\Omega$ ).

- **Built-in Test Pattern Generator**

- Loss of Lock and Error Reporting

- Configurable via SMBus

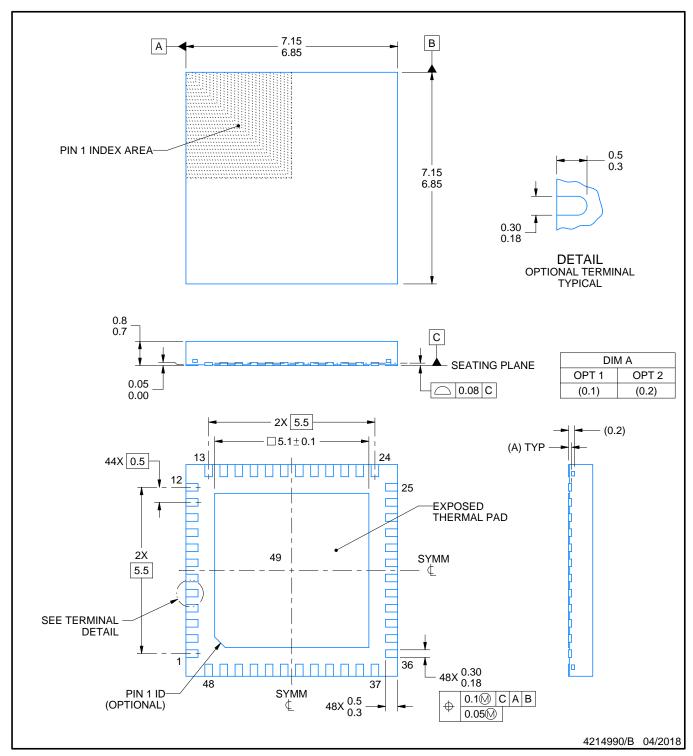

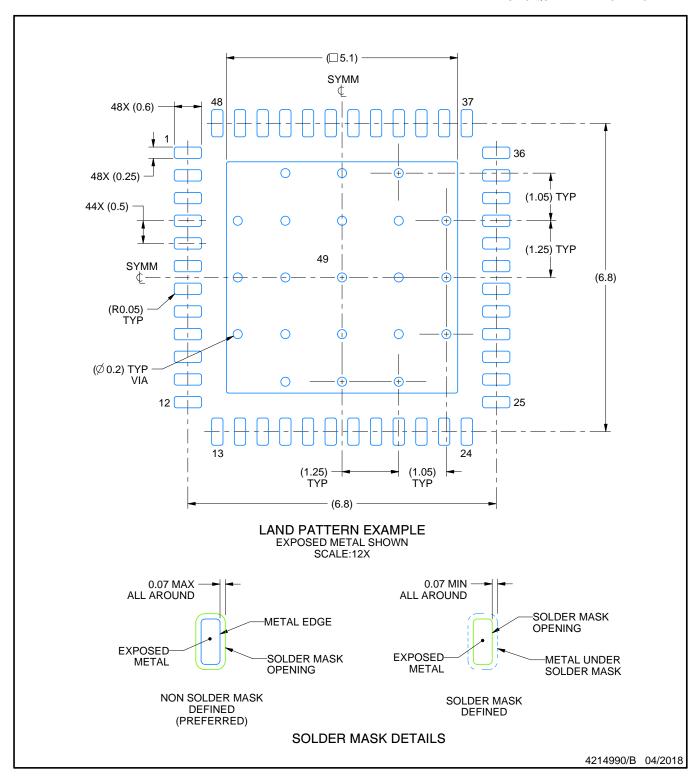

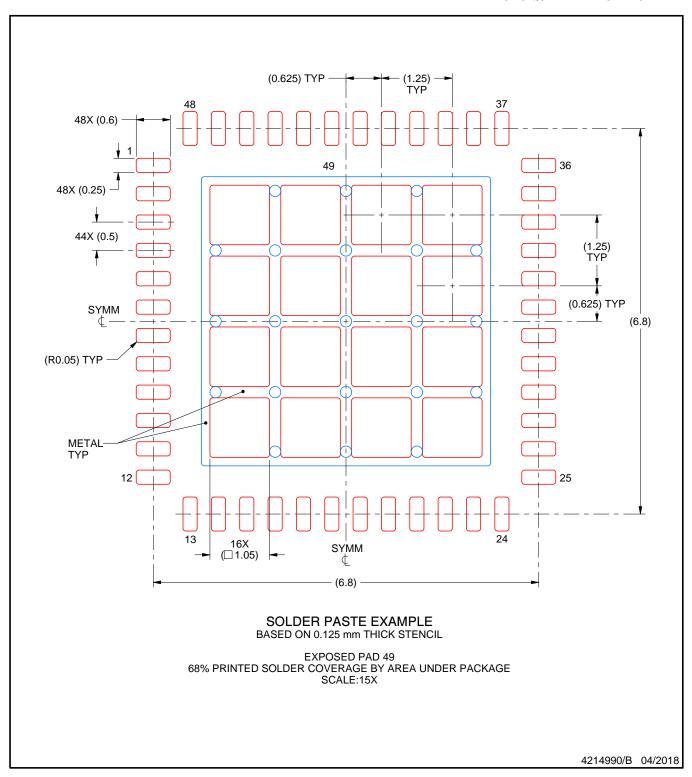

- 48-pin WQFN Package with Exposed DAP

## TARGET APPLICATIONS

- Imaging: Industrial, Medical Security, Printers

- **Displays: LED Walls, Commercial**

- **Video Transport**

- **Communication Systems**

- **Test and Measurement**

- **Industrial Bus**

#### **KEY SPECIFICATIONS**

- 1.25 to 3.125 Gbps Serial Data Rate

- 125 to 312.5 MHz DDR Parallel Clock

- -40° to +85°C Temperature Range

- >8 kV ESD (HBM) Protection

- Low Intrinsic Jitter 35ps at 3.125 Gbps

#### DESCRIPTION

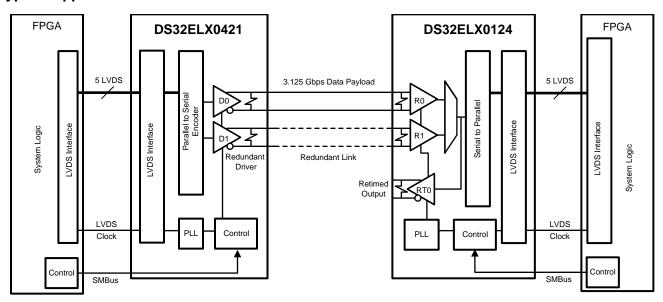

The DS32EL0421/DS32ELX0421 is a 125 MHz to 312.5 MHz (DDR) serializer for high-speed serial transmission over FR-4 printed circuit board backplanes, balanced cables, and optical fiber. This easy-to-use chipset integrates advanced signal and clock conditioning functions, with an FPGA friendly interface.

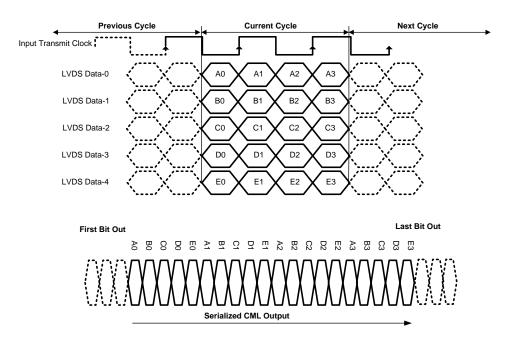

The DS32EL0421/DS32ELX0421 serializes up to 5 parallel input LVDS channels to create a maximum data payload of 3.125 Gbps. If the integrated DCbalance encoding is enabled, the maximum data payload achievable is 2.5 Gbps.

The DS32EL0421/DS32ELX0421 serializers feature remote sense capability to automatically detect and negotiate link status with its companion DS32EL0124/DS32ELX0124 deserializers without requiring an additional feedback path.

The parallel LVDS interface reduces FPGA I/O pins, board trace count and alleviates EMI issues, when compared to traditional single-ended wide bus interfaces.

The DS32EL0421/DS32ELX0421 is programmable through a SMBus interface as well as through control pins.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

## **Typical Application**

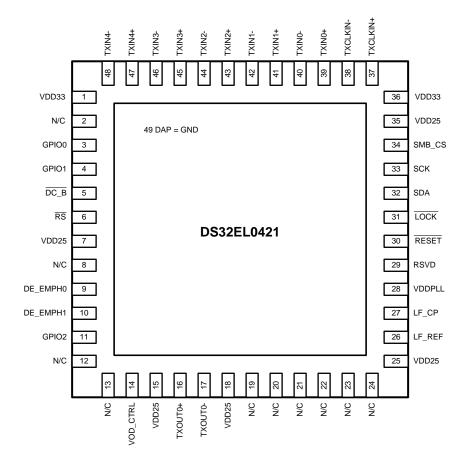

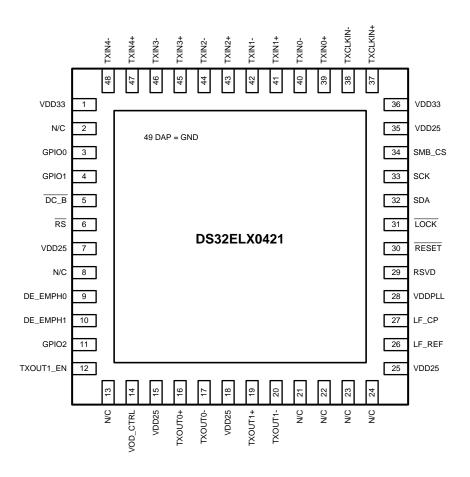

# **Connection Diagram**

See Package Number RHS0048A TOP VIEW

# See Package Number RHS0048A TOP VIEW

## **PIN DESCRIPTIONS**

| Pin Name           | Pin Number           | I/O, Type | Description                                                                                                                                                                                                       |

|--------------------|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power, Groun       | d and Analog         | Reference |                                                                                                                                                                                                                   |

| VDD33              | 1, 36                | I, VDD    | 3.3V supply                                                                                                                                                                                                       |

| VDD25              | 7, 15, 18, 25,<br>35 | I, VDD    | 2.5V supply                                                                                                                                                                                                       |

| VDDPLL             | 28                   | I, VDD    | 3.3V supply                                                                                                                                                                                                       |

| VOD_CTRL           | 14                   | Analog    | V <sub>OD</sub> control. The serializer output amplitude can be adjusted by connecting this pin to a pull-down resistor. The value of the resistor determines the VOD. See CML LAUNCH AMPLITUDE for more details. |

| LF_CP              | 27                   | Analog    | Loop filter connection for PLL                                                                                                                                                                                    |

| LF_REF             | 26                   | Analog    | Loop filter ground reference                                                                                                                                                                                      |

| Exposed Pad        | 49                   | GND       | Exposed Pad must be connected to GND by 9 vias                                                                                                                                                                    |

| CML I/O            |                      | •         |                                                                                                                                                                                                                   |

| TxOUT0+<br>TxOUT0- | 16<br>17             | O, CML    | Inverting and non-inverting high speed CML differential outputs of the serializer. These outputs are internally terminated.                                                                                       |

| TxOUT1+<br>TxOUT1- | 19<br>20             | O, CML    | DS32ELX0421 ONLY. Redundancy output. Inverting and non-inverting high speed CML differential outputs of the serializer. These outputs are internally terminated                                                   |

# PIN DESCRIPTIONS (continued)

| Pin Name             | Pin Number                                         | I/O, Type      | Description                                                                                                                         |

|----------------------|----------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| LVDS Parallel        | Data Bus                                           |                |                                                                                                                                     |

| TxCLKIN+<br>TxCLKIN- | 37<br>38                                           | I, LVDS        | Serializer input clock. TxCLKIN+/- are the inverting and non-inverting LVDS transmit clock input pins.                              |

| TxIN[4:0]+/-         | 39, 40,<br>41, 42,<br>43, 44,<br>45, 46,<br>47, 48 | I, LVDS        | Serializer input data. TxIN[4:0]+/- are the inverting and non-inverting LVDS serializer input data pins.                            |

| LVCMOS Con           | trol Pins                                          |                |                                                                                                                                     |

| DC_B<br>RS           | 5<br>6                                             | I,<br>LVCMOS   | DC-balance and Remote Sense pins. See Device Configuration section DEVICE CONFIGURATION for device behavior.                        |

| DE_EMPH0<br>DE_EMPH1 | 9<br>10                                            | I,<br>LVCMOS   | DE_EMPH0, DE_EMPH1 select the output de-emphasis level. These pins are internally pull-down. 00: Off 01: Low 10: Medium 11: Maximum |

| TXOUT1_EN            | 12                                                 | I,<br>LVCMOS   | <b>DS32ELX0421 ONLY.</b> When held high, redundant output TxOUT1+/- is enabled. This pin must be tied high when using TxOUT1+/      |

| RESET                | 30                                                 | I,<br>LVCMOS   | When held low, reset the device.  0 = Device Reset  1 = Normal operation                                                            |

| LOCK                 | 31                                                 | O,<br>LVCMOS   | Lock indication output. The input data on TxIN[0:4]+/- pins is ignored when LOCK pin is high.                                       |

| SMBus Interfa        | ace                                                |                |                                                                                                                                     |

| SCK                  | 33                                                 | I/O,<br>SMBus  | SMBus compatible clock.                                                                                                             |

| SDA                  | 32                                                 | I/O,<br>SMBus  | SMBus compatible data line.                                                                                                         |

| SMB_CS               | 34                                                 | I, SMBus       | SMBus chip select. When held high, SMBus management control is enabled.                                                             |

| Other                |                                                    |                |                                                                                                                                     |

| GPIO0                | 3                                                  | I/O,<br>LVCMOS | Software configurable I/O pin.                                                                                                      |

| GPIO1                | 4                                                  | I/O,<br>LVCMOS | Software configurable I/O pin.                                                                                                      |

| GPIO2                | 11                                                 | I/O,<br>LVCMOS | Software configurable I/O pin.                                                                                                      |

| NC                   | 2, 8, 12, 13,<br>19, 20, 21,<br>22, 23, 24,<br>29  | Misc.          | No Connect, for DS32EL0421                                                                                                          |

|                      | 2, 8, 13, 21,<br>22, 23, 24,<br>29                 | Misc.          | No Connect, for DS32ELX0421                                                                                                         |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

# Absolute Maximum Ratings (1)(2)

| Supply Voltage (3.3V V <sub>DD33</sub> ) | -0.3V to +4V                      |

|------------------------------------------|-----------------------------------|

| Supply Voltage (2.5V V <sub>DD25</sub> ) | -0.3V to +3V                      |

| LVCMOS Input Voltage                     | $-0.3V$ to $(V_{DD} + 0.3V)$      |

| LVCMOS Output Voltage                    | -0.3V to (V <sub>DD</sub> + 0.3V) |

| LVDS Input Voltage (IN+, IN-)            | -0.3V to +3.6V                    |

| CML Output Voltage                       | -0.3V to +3.6V                    |

| Junction Temperature                     | +125°C                            |

| Storage Temperature Range                | -65°C to +150°C                   |

| Lead Temperature Range                   |                                   |

| Soldering (4 sec.)                       | +260°C                            |

| Thermal Resistance, $\theta_{JA}$        | 25°C/W                            |

| ESD Susceptibility                       |                                   |

| HBM <sup>(3)</sup>                       | >8 kV                             |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

- (2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

- (3) Human Body Model, applicable std. JESD22-A114C

**Recommended Operating Conditions**

|                                             | Min   | Тур | Max   | Units      |

|---------------------------------------------|-------|-----|-------|------------|

| Supply Voltage (V <sub>DD33</sub> – GND)    | 3.135 | 3.3 | 3.465 | V          |

| Supply Voltage (V <sub>DD25</sub> – GND)    | 2.375 | 2.5 | 2.625 | V          |

| Supply Noise Amplitude from 10 Hz to 50 MHz |       |     | 100   | $mV_{P-P}$ |

| Ambient Temperature (T <sub>A</sub> )       | -40   | +25 | +85   | °C         |

## **Power Supply Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol            | Parameter                                | Condition  | Min | Тур | Max | Unit |

|-------------------|------------------------------------------|------------|-----|-----|-----|------|

| I <sub>DD25</sub> | 2.5V supply current                      | 1.25 Gbps  |     | 87  | 94  |      |

|                   | 1 Output Enabled                         | 2.5 Gbps   |     | 95  | 105 |      |

|                   |                                          | 3.125 Gbps |     | 101 | 112 | ^    |

|                   | 2.5V supply current<br>2 Outputs Enabled | 1.25 Gbps  |     | 126 | 135 | mA   |

|                   |                                          | 2.5 Gbps   |     | 136 | 145 |      |

|                   |                                          | 3.125 Gbps |     | 142 | 152 |      |

| I <sub>DD33</sub> | 3.3V supply current                      | 1.25 Gbps  |     | 74  | 85  |      |

|                   | 1 Output Enabled                         | 2.5 Gbps   |     | 74  | 85  |      |

|                   |                                          | 3.125 Gbps |     | 74  | 85  | A    |

|                   | 3.3V supply current                      | 1.25 Gbps  |     | 80  | 92  | mA   |

|                   | 2 Outputs Enabled                        | 2.5 Gbps   |     | 80  | 92  |      |

|                   |                                          | 3.125 Gbps |     | 80  | 92  |      |

<sup>(1)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

<sup>(2)</sup> Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

## **Power Supply Specifications (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol  | Parameter         | Condition  | Min | Тур | Max | Unit  |

|---------|-------------------|------------|-----|-----|-----|-------|

| 1 Outpu |                   | 1.25 Gbps  |     | 460 | 540 |       |

|         |                   | 2.5 Gbps   |     | 485 | 560 |       |

|         |                   | 3.125 Gbps |     | 500 | 575 | mW    |

|         | Power Consumption | 1.25 Gbps  |     | 580 | 670 | IIIVV |

|         |                   | 2.5 Gbps   |     | 605 | 695 |       |

|         |                   | 3.125 Gbps |     | 620 | 710 |       |

## **LVCMOS Electrical Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. Applies to GPIO0, GPIO1, GPIO2, RESET, LOCK, RS, and DC BAL. (1) (2) (3)

| Symbol          | Parameter                    | Conditions                       | Min | Тур   | Max      | Units |

|-----------------|------------------------------|----------------------------------|-----|-------|----------|-------|

| V <sub>IH</sub> | High Level Input Voltage     |                                  | 2.0 |       | $V_{DD}$ | V     |

| V <sub>IL</sub> | Low Level Input Voltage      |                                  | 0   |       | 0.8      | V     |

| V <sub>OH</sub> | High Level Output Voltage    | I <sub>OH</sub> = -2mA           | 2.7 | 3.3   |          | V     |

| V <sub>OL</sub> | Low Level Output Voltage     | $I_{OL} = 2mA$                   |     |       | 0.3      | V     |

| V <sub>CL</sub> | Input Clamp Voltage          | I <sub>CL</sub> = -18mA          |     | -0.79 | -1.5     | V     |

| I <sub>IN</sub> | Input Current                | $V_{IN} = 0.4V, 2.5V, or V_{DD}$ | -35 |       | 35       | μΑ    |

| Ios             | Output Short Circuit Current | V <sub>OUT</sub> = 0V            |     | 42    |          | mA    |

- (1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (2) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>.

- (3) Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

- (4) Output short circuit current (Ios) is specified as magnitude only, minus sign indicates direction only.

## **SMBus Electrical Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2) (3)

| Symbol          | Parameter                      | Conditions                          | Min   | Тур  | Max       | Units |

|-----------------|--------------------------------|-------------------------------------|-------|------|-----------|-------|

| $V_{SIL}$       | Data, Clock Input Low Voltage  |                                     |       |      | 0.8       | V     |

| $V_{SIH}$       | Data, Clock Input High Voltage |                                     | 2     |      | $V_{SDD}$ | V     |

| $V_{SDD}$       | Nominal Bus Voltage            |                                     | 2.375 |      | 3.6       | V     |

| İSLEAKB         | Input Leakage Per Bus Segment  |                                     |       | ±200 |           | μΑ    |

| C <sub>SI</sub> | Capacitance for SDA and SCLK   | See <sup>(4)</sup> , <sup>(5)</sup> |       | 10   |           | pF    |

- (1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (2) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>.

- (3) Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

- (4) Recommended value, parameter is not tested.

- (5) Recommended maximum capacitance load per bus segment is 400 pF.

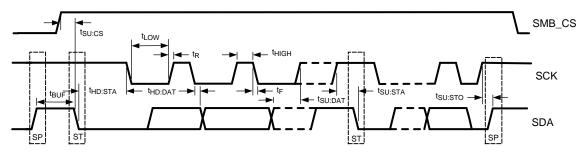

## SMBus Timing Specifications

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol              | Parameter                                                                                    | Conditions | Min | Тур | Max  | Units |

|---------------------|----------------------------------------------------------------------------------------------|------------|-----|-----|------|-------|

| t <sub>SMB</sub>    | Bus Operating Frequency                                                                      |            | 10  |     | 100  | kHz   |

| t <sub>BUF</sub>    | Bus Free Time between Stop and Start Condition                                               |            | 4.7 |     |      | μs    |

| t <sub>HD:STA</sub> | Hold time after (repeated) start condition. After this period, the first clock is generated. |            | 4.0 |     |      | μs    |

| t <sub>SU:STA</sub> | Repeated Start Condition Setup Time                                                          |            | 4.7 |     |      | μs    |

| t <sub>SU:STO</sub> | Stop Condition Setup Time                                                                    |            | 4.0 |     |      | μs    |

| t <sub>HD:DAT</sub> | Data Hold Time                                                                               |            | 300 |     |      | ns    |

| t <sub>SU:DAT</sub> | Data Setup Time                                                                              |            | 250 |     |      | ns    |

| t <sub>LOW</sub>    | Clock Low Time                                                                               |            | 4.7 |     |      | μs    |

| t <sub>HIGH</sub>   | Clock High Time                                                                              |            | 4.0 |     | 50   | μs    |

| t <sub>F</sub>      | Clock/Data Fall Time                                                                         | 20% to 80% |     |     | 300  | ns    |

| t <sub>R</sub>      | Clock/Data Rise Time                                                                         |            |     |     | 1000 | ns    |

| t <sub>SU:CS</sub>  | SMB_CS Setup Time                                                                            |            |     | 30  |      | ns    |

| t <sub>POR</sub>    | Time in which the device must be operation after power on                                    | See (3)    |     |     | 500  | ms    |

- (1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (2) Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

- (3) Parameter is ensured by characterization and is not tested at production.

## **LVDS Electrical Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2) (3)

| Symbol            | Parameter                         | Conditions                                                  | Min  | Тур | Max                      | Units             |

|-------------------|-----------------------------------|-------------------------------------------------------------|------|-----|--------------------------|-------------------|

| $V_{TH}$          | Differential Input High Threshold | 0.051/ .1/                                                  |      |     | +100                     | mV                |

| $V_{TL}$          | Differential Input Low Threshold  | $0.05V < V_{LVCM} < V_{DD25} - 0.05V$                       | -100 |     |                          | mV                |

| $V_{LVCM}$        | LVDS Input Common Mode Voltage    |                                                             | 0.05 |     | V <sub>DD25</sub> – 0.05 | V                 |

| V <sub>LVOS</sub> | LVDS Input Loss of Signal         | LVDS input loss of signal level.<br>See <sup>(4)</sup>      |      | 20  |                          | mV <sub>P-P</sub> |

| R <sub>LVIN</sub> | Input Impedance                   | Internal LVDS input termination between differential pairs. | 85   | 100 | 115                      | Ω                 |

- (1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (2) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>.

- (3) Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

- (4) If input LVDS signal is below 20mV<sub>P-P</sub>, loss of signal (LOS) is detected. The device will flag a valid input signal if the signal level is above 100mV<sub>P-P</sub>

#### LVDS Timing Specifications

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol           | Parameter                                 | Conditions   | Min | Тур | Max   | Units |

|------------------|-------------------------------------------|--------------|-----|-----|-------|-------|

| f                | Input DDR Clock (TxCLKIN) Frequency Range |              | 125 |     | 312.5 | MHz   |

| t <sub>CIP</sub> | TxCLKIN Period                            | See Figure 3 | 3.2 | 2T  | 8     | ns    |

- (1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (2) Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

## LVDS Timing Specifications (continued)

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol             | Parameter                        | Conditions                                                                  | Min  | Тур | Max  | Units |

|--------------------|----------------------------------|-----------------------------------------------------------------------------|------|-----|------|-------|

| t <sub>CIT</sub>   | TxCLKIN Transition Time          | See Figure 2<br>See <sup>(3)</sup>                                          | 0.5  | 1.0 | 3.0  | ns    |

| t <sub>XIT</sub>   | TxIN Transition Time             |                                                                             | 0.15 |     | 3    | ns    |

| t <sub>CIH</sub>   | TxCLKIN High Time                | See Figure 3                                                                | 0.7T | Т   | 1.3T | ns    |

| t <sub>CIL</sub>   | TxCLKIN Low Time                 | See Figure 3                                                                | 0.7T | Т   | 1.3T | ns    |

| t <sub>STC</sub>   | TxIN Setup to TxCLKIN            |                                                                             | -550 |     |      | ps    |

| t <sub>HTC</sub>   | TxIN Hold to TxCLKIN             |                                                                             | 900  |     |      | ps    |

| t <sub>LVDLS</sub> | LVDS Input Clock Delay Step Size | Programmable through the SMBus, register 30'h Default setting = 011'b [7:5] |      | 100 |      | ps    |

<sup>(3)</sup> Parameter is ensured by characterization and is not tested at production.

## **CML Electrical Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2) (3)

| Symbol          | Parameter                                | Conditions                                                                        | Min  | Тур  | Max  | Units      |

|-----------------|------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------------|

| R <sub>OT</sub> | Output Terminations                      | On chip termination from TxOUT0/1 + and TxOUT0/1 - to $V_{DD25} \\ 50\Omega$ mode | 40   | 50   | 60   | Ω          |

|                 |                                          | 75Ω mode                                                                          | 60   | 75   | 90   | Ω          |

| $\Delta R_{OT}$ | Mismatch in Output Termination Resistors |                                                                                   |      |      | 5    | %          |

| V <sub>OD</sub> | Output Differential Voltage Swing        | Based on VOD_CTRL = 9.1 k $\Omega$                                                | 1175 | 1350 | 1450 | $mV_{P-P}$ |

- (1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (2) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>.

- (3) Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

## **CML Timing Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol            | Parameter                                | Conditions                                                                                                                                    | Min  | Тур                       | Max   | Units |

|-------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------|-------|-------|

| LR                | Line Rate                                | Tested with alternating 1-0 pattern.                                                                                                          | 1.25 |                           | 3.125 | Gbps  |

| tos               | Output Overshoot                         | See (3)                                                                                                                                       |      |                           | 10    | %     |

| $t_R$             | Differential Low to High Transition Time | See (3)                                                                                                                                       |      | 60                        | 90    | ps    |

| $t_{F}$           | Differential High to Low Transition Time |                                                                                                                                               |      | 60                        | 90    | ps    |

| t <sub>RFMM</sub> | Mismatch in Rise/Fall Time               | See (3)                                                                                                                                       |      |                           | 15    | ps    |

| t <sub>DE</sub>   | De-emphasis width                        | Measured from zero-crossing at rising edge to 80% of VOD from zero-crossing at falling edge. TDE is measured at the High setting during test. |      | 1                         |       | UI    |

| t <sub>BIT</sub>  | Serializer Bit Width                     |                                                                                                                                               |      | 0.2 x<br>t <sub>CIP</sub> |       | ns    |

| t <sub>SD</sub>   | Serializer Propagation Delay – Latency   | Depends on mode — see Table 3                                                                                                                 |      | (10 –<br>14) T+<br>5.5    |       | ns    |

<sup>(1)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

<sup>(2)</sup> Typical values represent most likely parametric norms for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

<sup>(3)</sup> Parameter is ensured by characterization and is not tested at production.

# **CML Timing Specifications (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol            | Parameter                                | Conditions                                                                                                                                                                                                                                             | Min | Тур        | Max | Units             |

|-------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|-------------------|

| t <sub>JIND</sub> | Serializer Output Deterministic Jitter   | Serializer output intrinsic deterministic jitter. Measure with PRBS-7 test pattern De-emphasis disabled. See <sup>(3)</sup> 1.25 Gbps                                                                                                                  |     | 10         |     | ps                |

|                   |                                          | 2.5 Gbps                                                                                                                                                                                                                                               |     | 24         |     | ps                |

|                   |                                          | 3.125 Gbps                                                                                                                                                                                                                                             |     | 21         |     | ps                |

| t <sub>JINR</sub> | Serializer Output Random Jitter          | Serializer output intrinsic random jitter. Bit error rate ≥10 <sup>-15</sup> . Alternating–10 pattern. De-emphasis disabled. See <sup>(3)</sup> 1.25 Gbps                                                                                              |     | 1.3        |     | ps <sub>RMS</sub> |

|                   |                                          | 2.5 Gbps                                                                                                                                                                                                                                               |     | 1.15       |     | ps <sub>RMS</sub> |

|                   |                                          | 3.125 Gbps                                                                                                                                                                                                                                             |     | 1.14       |     | ps <sub>RMS</sub> |

| t <sub>JINT</sub> | Peak-to-peak Serializer Output Jitter    | Serializer output peak-to-peak jitter includes deterministic jitter, random jitter, and jitter transfer from serializer input. Measure with PRBS-7 test pattern. Bit error rate ≥10 <sup>-15</sup> . Deemphasis disabled. See <sup>(3)</sup> 1.25 Gbps |     | 28         |     | ps                |

|                   |                                          | 2.5 Gbps                                                                                                                                                                                                                                               |     | 38         |     | ps                |

|                   |                                          | 3.125 Gbps                                                                                                                                                                                                                                             |     | 35         |     | ps                |

| $\lambda_{TXBW}$  | Jitter Transfer Function -3 dB Bandwidth | 1.25 Gbps<br>3.125 Gbps                                                                                                                                                                                                                                |     | 100<br>300 |     | kHz<br>kHz        |

| $\delta_{TX}$     | Jitter Transfer Function Peaking         |                                                                                                                                                                                                                                                        |     | 0.5        |     | dB                |

(4) Parameter is ensured by characterization and is not tested at production.

## **Timing Diagrams**

Figure 1. SMBus timing parameters

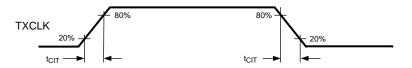

Figure 2. Serializer Input Clock Transition Time

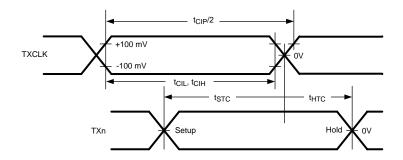

Figure 3. Serializer (LVDS Interface) Setup/Hold and High/Low Times

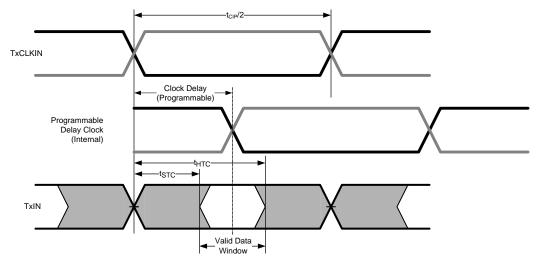

Figure 4. LVDS Input Clock Delay

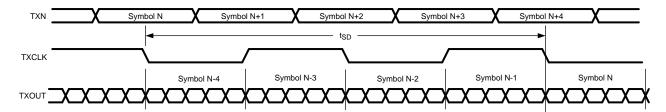

Figure 5. Propagation Delay Timing Diagram

Figure 6. 5-Bit Parallel LVDS Inputs Mapped to CML Output

#### **FUNCTIONAL DESCRIPTION**

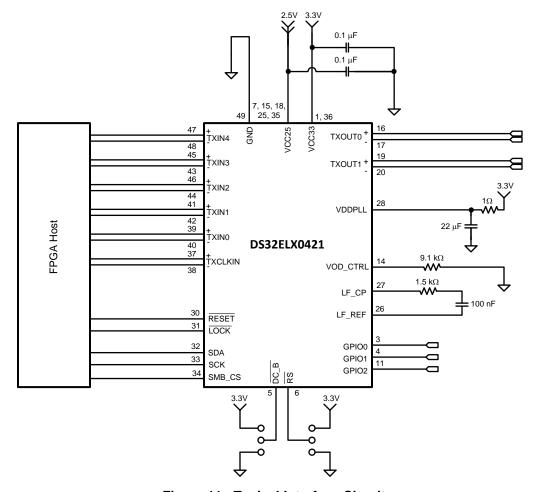

## **POWER SUPPLIES**

The DS32EL0421 and DS32ELX0421 have several power supply pins, at 2.5V as well as 3.3V. It is important that these pins all be connected and properly bypassed. Bypassing should consist of parallel  $4.7\mu F$  and  $0.1\mu F$  capacitors as a minimum, with a  $0.1\mu F$  capacitor on each power pin. A 22  $\mu F$  capacitor is required on the VDDPLL pin which is connected to the 3.3V rail.

These devices have a large contact in the center on the bottom of the package. This contact must be connected to the system GND as it is the major ground connection for the device.

#### **POWER UP**

It is recommended, although not necessary, to bring up the 3.3V power supply before the 2.5V supply. If the 2.5V supply is powered up first, an initial current draw of approximately 600mA from the 2.5V rail may occur before settling to its final value. Regardless of the sequence, both power rails should monotonically ramp up to their final values.

#### **POWER MANAGEMENT**

These devices have two methods to reduce power consumption. To enter the first power save mode, the on board host FPGA or controlling device can cease to output the DDR transmit clock. To further reduce power consumption, write 40'h to register 26'h and 10'h to register 01'h. This will put the device in its lowest power consumption mode.

## **RESET**

There are three ways to reset these devices. A reset occurs automatically during power-up. The device can also be reset by pulling the RESET pin low, with normal operation resuming when the pin is driven high again. The device can also be reset by writing to the reset register. This reset will put all of the register values back to their default values, except it will not affect the address register value if the SMBus default address has been changed.

#### **LVDS INPUTS**

The DS32EL0421 and DS32ELX0421 have standard 2.5V LVDS inputs which are compliant with ANSI/TIA/EIA-644. These inputs have internal  $100\Omega$  termination resistors. It is recommended that the PCB trace between the FPGA and the serializer be less than 40-inches. Longer PCB traces may degrade the quality of the input signal. The connection between the host and the DS32EL0421 or DS32ELX0421 should be over a controlled impedance transmission line with impedance that matches the termination resistor – usually  $100\Omega$ . Setup and hold times are specified in the LVDS Timing Specifications, however the clock delay can be adjusted by writing to register 30'h.

#### **LOOP FILTER**

The DS32EL0421 and DS32ELX0421 have an internal PLL which is used to generate the serialization clock from the parallel clock input. The loop filter for this PLL is external; and for optimum results, a 100nF capacitor and a 1.5 k $\Omega$  resistor in series should be connected between pins 26 and 27. See typical interface circuit (Figure 11).

## **CML LAUNCH AMPLITUDE**

The launch amplitude of the CML output(s) is controlled by placing a single resistor from the VOD\_CTRL pin to ground. Use the following equation to obtain the desired  $V_{OD}$  by selecting the corresponding resistor value.

$$R = (1400 \text{ mV} / V_{OD}) \times 9.1 \text{ k}\Omega$$

(1)

The CML output launch amplitude can also be adjusted by writing to SMBus register 69'h, bits 2:0. This register is meant to assist system designers during the initial prototype design phase. For final production, it is recommended that the appropriate resistor value be selected for the desired  $V_{OD}$  and that register 69'h be left to its default value.

#### **REMOTE SENSE**

The remote sense feature can be used when a DS32EL0421 or DS32ELX0421 serializer is directly connected to a DS32EL0124 or DS32ELX0124 deserializer. Active components in the signal path between the serializer and the deserializer may interfere with the back channel signaling of the devices.

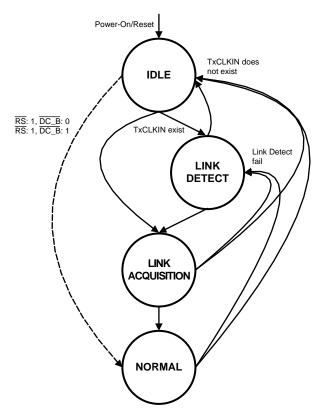

When remote sense is enabled, the serializer will cycle through four states to successfully establish a link and align the data. The state diagram for the serializer is shown in Figure 7. The serializer will remain in the low power IDLE state until it receives an input clock. Once the PLL of the serializer has locked to the input clock, the device will enter the LINK DETECT state. While in this state, the serializer will monitor the line to see if the deserializer is present. If a deserializer is detected, the serializer will enter the LINK ACQUISITION state. The serializer will transmit the entire training pattern and then enter the NORMAL state. If the deserializer is unable to successfully lock or maintain lock it will break the link, sending the serializer back to the IDLE or LINK DETECT states.

With the Remote Sense feature active, the serializer can be forced out of lock due to events on the high speed serial line in two ways, a serial channel reset signal is sent upstream from the deserializer or the near end termination detect circuit signals and open termination was detected. The upstream signal sent from the deserializer that resets the serializer is called the link detect signal. Since the serializer and deserializer may power up at different times, the deserializer will transmit this link detect signal periodically, once it detects that a serializer is active on the other side of the high speed line. When a serializer receives the link detect signal, it will return to the LINK DETECT state. The near end open termination detection circuit will trigger only for near end open termination events, such as unplugging the cable on the serializer end of the line.

## **DC-BALANCE ENCODER**

The DS32EL0421 and DS32ELX0421 have a built-in DC-balance encoder to support AC-coupled applications. When enabled, the input signal on TXIN4+/- is treated as a data valid bit. If TXIN4+/- is low, then the four bit nibbles from TXIN0-TXIN3 are taken to form a 16 bit word. This 16 bit word is processed as two 8 bit words and converted to two 10 bit words by using the standard 8b/10b data coding scheme. The two 10 bit words are then combined to create a 20 bit code. This 20 bit word is serialized and driven on the output. The nibble taken in on the rising edge of the clock is the most significant nibble and the nibble taken in on the falling edge is the least significant nibble. If TXIN4+/TXIN4- is high, then the inputs TXIN0 -TXIN3 are ignored and a programmable DC-balanced SYNC character is inserted in the output stream. The default character is a K28.5 code. In order to send other K codes, they must first be programmed into the serializer via the SMBus. The SMBus registers allows for only a single programmable character.

Figure 7. Serializer State Diagram

## **SCRAMBLER** and NRZI Encoder

The CDR of the DS32EL0124 and the DS32ELX0124 expect a transition density of 20% for a period of 200  $\mu$ s. If the scrambler and NRZI encoder are enabled, the raw or DC-balanced serialized data is scrambled to improve transition density. The scrambler accepts 20 bits of data and encodes it using the polynomial  $X^9 + X^4 + 1$ . The data can then be sent to the NRZ-to-NRZI converter before being output.

Enabling the scrambler can help to lower EMI emissions by spreading the spectrum of the data. Scrambling also creates transitions for the deserializer's CDR to properly lock onto.

The scrambler and NRZI encoder are enabled or disabled by default depending on how the  $\overline{DC_B}$  and  $\overline{RS}$  pins are configured. To override the default scrambler setting two register writes must be performed. First, write to register 22'h and set bit 3 to unlock the scrambler register. Next write to register 21'h and change bit 4 to the desired value. The NRZI encoder can be enabled or disabled independently of the scrambler by controlling bit 7 of register 21'h and bit 4 of register 22'h.

## **CML OUTPUT DATA INTERFACING**

The serial outputs provide low-skew differential signals. Internal resistors connected from TxOUTn+ and TxOUTn- to VDD25 terminate the outputs. The output level can be programmed by adjusting the pull-down resistor to the VOD CTRL pin. The output terminations can also be programmed to be either 50  $\Omega$  or 75  $\Omega$ .

The output buffer consists of a current mode logic (CML) driver with user configurable de-emphasis control, which can be used to optimize performance over a wide range of transmission line lengths and attenuation distortions resulting from low cost CAT(-5, -6, -7) cable or FR-4 backplane. Output de-emphasis is user programmable through either device pins DE\_EMPH0 and DE\_EMPH1 or SMBus interface. Users can control the strength of the de-emphasis to optimize for a specific system environment. Please see Table 1 for details.

## **Table 1. De-Emphasis Control Table**

| DE_EMPH[1:0] | Output De-Emphasis Level |

|--------------|--------------------------|

| 00'b         | Off                      |

| 01'b         | Low                      |

| 10'b         | Medium                   |

| 11'b         | High                     |

The DS32ELX0421 provides a secondary serial output, supporting redundancy applications. The redundant output driver can be enabled by setting TXOUT1\_EN pin to HIGH or by activating it through the SMBus reigsters.

#### **DEVICE CONFIGURATION**

There are four ways to configure the DS32EL0421 and DS32ELX0421 serializers, these combinations are shown in Table 2. Refer to Figure 7 to see how the combinations of the RS and DC\_B pins change the link startup behavior of the serializers. When connecting to a deserializer other than the DS32EL0124 or DS32ELX0124, Remote Sense should be disabled. The scrambler and NRZI encoder shown in Table 2 can be enabled or disabled through register programming.

When Remote Sense is enabled, with  $\overline{\text{RS}}$  pin tied low, the serializer must be connected directly to a DS32EL0124 or DS32ELX0124 deserializer without any active components between them. The Remote Sense module features an upstream communication method for the serializer and deserializer to communicate. This feature is used to pass link status information between the 2 devices. When Remote Sense is enabled the serializer will send a training pattern to the deserializer to establish lock and lane alignment.

If DC-Balance is enabled, a maximum of 4 parallel LVDS lanes can be used to receive data. The fifth lane (TXIN4±) is used for Data Valid signaling. Each time a serializer establishes a link to a deserializer with DC-Balance enabled and Remote Sense disabled, the Data Valid input to the serializer must be held high for 110 LVDS clock periods. If the Data Valid input to the serializer is logic HIGH, then SYNC characters are transmitted. If the deserializer receives a SYNC character, then the LVDS data outputs will all be logic low and the Data Valid output will be logic high. If the deserializer detects a DC-Balance code error, the output data pins will be set to logic high with the Data Valid output also set to logic high.

In the case where DC-Balance is enabled and Remote Sense is disabled, with  $\overline{\text{RS}}$  set to high and  $\overline{\text{DC}_{-}}$ B set to low, it is recommended that the host device periodically toggle the Data Valid input to the serializer, to transmit SYNC symbols on the line, to ensure that the deserializer is and remains locked. In this configuration the deserializer or receiving device does not have a way to directly notify the serializer if it has lost lock. Periodically sending SYNC symbols will allow the receiving system to reacquire lock if a problem has occurred. With these pin settings the DS32EL0421/DS32ELX0421 and DS32EL0124/DS32ELX0124 devices can interface with other active component in the high speed signal path, such as fiber modules.

When both Remote Sense and DC-Balance are disabled,  $\overline{RS}$  and  $\overline{DC_B}$  pins set to high, the LVDS lane alignment is not maintained. In this configuration, data formatting is handled by an FPGA or external source. This pin setting combination also allows for the DS32EL0421/DS32ELX0421 devices to interface with active components other than the DS32EL0124/DS32ELX0124 in the high speed signal path. In this configuration the host device is responsible for DC balancing the data in an AC coupled application.

## **Table 2. Device Configuration Table**

| Remote <u>Sense Pin</u><br>(RS) | DC-Balance Pin (DC_B) | Configuration                                                                                              |

|---------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------|

| 0                               | 0                     | Remote Sense enabled DC-Balance enabled Data Alignment Scrambler and NRZI encoder disabled by default      |

| 0                               | 1                     | Remote Sense enabled DC-Balance disabled Data Alignment Scrambler and NRZI encoder enabled by default      |

| 1                               | 0                     | Remote Sense disabled DC-Balance enabled Data Alignment Scrambler and NRZI encoder enabled by default      |

| 1                               | 1                     | Remote Sense disabled DC-Balance disabled No Data Alignment Scrambler and NRZI encoder disabled by default |

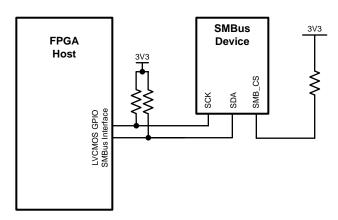

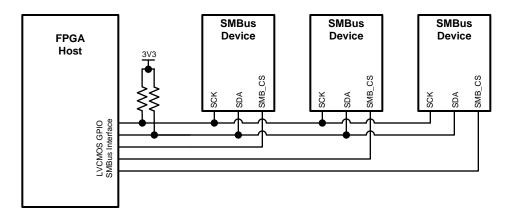

## **SMBus INTERFACE**

The System Management Bus interface is compatible to SMBus 2.0 physical layer specification. The use of the Chip Select signal is **required**. Holding the SMB\_CS pin HIGH enables the SMBus port, allowing access to the configuration registers. Holding the SMB\_CS pin LOW disables the device's SMBus, allowing communication from the host to other slave devices on the bus. In the STANDBY state, the System Management Bus remains active. When communication to other devices on the SMBus is active, the SMB\_CS signal for the serializer must be driven LOW.

The address byte for all DS32EL0421 and DS32ELX0421 devices is AE'h. Based on the SMBus 2.0 specification, these devices have a 7-bit slave address of 1010111'b. The LSB is set to 0'b (for a WRITE), thus the 8-bit value is 1010 1110 'b or AE'h.

The SCK and SDA pins are 3.3V LVCMOS signaling and include high-Z internal pull up resistors. External low impedance pull up resistors maybe required depending upon SMBus loading and speed. Note, these pins are not 5V tolerant.

#### Transfer of Data via the SMBus

During normal operation the data on SDA must be stable during the time when SCK is HIGH.

There are three unique states for the SMBus:

START A HIGH to LOW transition on SDA while SCK is HIGH indicates a message START condition STOP A LOW to HIGH transition on SDA while SCK is HIGH indicates a message STOP condition.

IDLE If SCK and SDA are both high for a time exceeding t<sub>BUF</sub> from the last detected STOP condition or if they are HIGH for a total exceeding the maximum specification for t<sub>HIGH</sub> then the bus will transfer to the IDLE state.

#### SMBus Transactions

The devices support WRITE and READ transactions. See Register Description Table for register address, type (Read/ Write, Read Only), default value and function information.

## Writing to a Register

To write a register, the following protocol is used (see SMBus 2.0 specification).

- 1. The Host (Master) selects the device by driving its SMBus Chip Select (SMB\_CS) signal HIGH.

- 2. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 3. The Device (Slave) drives the ACK bit ("0").

- 4. The Host drives the 8-bit Register Address.

- 5. The Device drives an ACK bit ("0").

- 6. The Host drive the 8-bit data byte.

- 7. The Device drives an ACK bit ("0").

- 8. The Host drives a STOP condition.

- 9. The Host de-selects the device by driving its SMBus CS signal Low.

The WRITE transaction is completed, the bus goes IDLE and communication with other SMBus devices may now occur.

## Reading a Register

To read a register, the following protocol is used (see SMBus 2.0 specification).

- 1. The Host (Master) selects the device by driving its SMBus Chip Select (SMB\_CS) signal HIGH.

- 2. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 3. The Device (Slave) drives the ACK bit ("0").

- The Host drives the 8-bit Register Address.

- 5. The Device drives an ACK bit ("0").

- 6. The Host drives a START condition.

- 7. The Host drives the 7-bit SMBus Address, and a "1" indicating a READ.

- 8. The Device drives an ACK bit "0".

- 9. The Device drives the 8-bit data value (register contents).

- 10. The Host drives a NACK bit "1" indicating end of the READ transfer.

- 11. The Host drives a STOP condition.

- 12. The Host de-selects the device by driving its SMBus CS signal Low.

The READ transaction is completed, the bus goes IDLE and communication with other SMBus devices may now occur.

## **SMBus Configurations**

Many different configurations of the SMBus are possible and depend upon the specific requirements of the applications. Several possible applications are described.

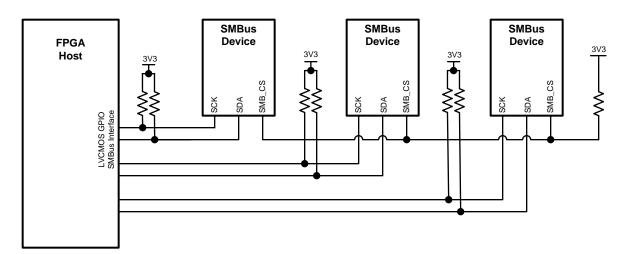

#### **Configuration 1**

The deserializer SMB\_CS may be tied High (always enabled) since it is the only device on the SMBus. See Figure 8.

#### **Configuration 2**

Since the multiple SER devices have the same address, the use of the individual SMB\_CS signals is required. To communicate with a specific device, its SMB\_CS is driven High to select the device. After the transaction is complete, its SMB\_CS is driven Low to disable its SMB interface. Other devices on the bus may now be selected with their respective chip select signals and communicated with. See Figure 9.

#### **Configuration 3**

The addressing field is limited to 7-bits by the SMBus protocol. Thus it is possible that multiple devices may share the same 7-bit address. An optional feature in the SMBus 2.0 specification supports an Address Resolution Protocol (ARP). This optional feature is not supported by the DS32EL0421/DS32ELX0421 devices. Solutions for this include: the use of the independent SMB\_CS signals, independent SMBus segments, or other means.

Figure 8. SMBus Configuration 1

Figure 9. SMBus Configuration 2

Figure 10. SMBus Daisy Chained CS Configuration

#### PROPAGATION DELAY

Once the serializer is locked, the amount of time it takes for a bit to travel into the device through the DDR LVDS inputs and out through the CML serial output is defined to be the propagation delay. The propagation delay through the DS32EL0421/DS32ELX0421 due to the analog circuitry is considered negligible compared to the time delay caused by the digital components. The information presented in this section allows system designers to predict the propagation delay through the device in terms of clock cycles which are proportional to the high speed serial line rate.

Each clock cycle shown in Table 3 is defined to be  $1/2 t_{CIP}$ . Note at 3.125 Gbps,  $t_{CIP}$  is 312.5 MHz, T is 1/2 tCIP or 156.25 MHz which is 6.40 ns per clock..

Config. Pins (DC\_B, RS) LVDS DC Balance NRZ CML Scrambler Total Analog Interface Encoder Encoder interface Delay Propagation Delay Data Flow (left to right) 3 clocks 5 - 6 clocks 11 - 12 clocks 0, 0 1 clock 2 clocks + ~5.5ns + ~5.5ns 0, 1 3 clocks 1 clock 1 clock 1 clock 5 - 6 clocks 2 clocks 13 - 14 clocks + ~5.5ns + ~5.5ns 1, 0 3 clocks 1 clock 1 clock 5 - 6 clocks 2 clocks 12 - 13 clocks + ~5.5ns + ~5.5ns 2 clocks 10 - 11 clocks 1.1 3 clocks 5 - 6 clocks + ~5.5ns + ~5.5ns

**Table 3. Serializer Propagation Delay**

## **Application Information**

#### **GPIO PINS**

The GPIO pins can be useful tools when debugging or evaluating the system. For specific GPIO configurations and functions refer to registers 2, 3, 4, 5 and 6 in the device register map.

GPIO pins are commonly used when there are multiple serializers on the same SMBus. In order to program individual settings into each serializer, they will each need to have a unique SMBus address. To reprogram multiple serializers on a single SMBus, configure the first serializer such that the SMBus lines are connected to the FPGA or host controller. The CS pin of the second serializer should be tied to GPIO0 of the first serializer, with the CS pin of the next serializer tied to GPIO0 of its preceding serializer. By holding all of the GPIO0 pins low, the first serializer's address may now be reprogrammed by writing to register 0. The first serializer's GPIO pin can now be asserted and the second serializer's address may now be reprogrammed.

## HIGH SPEED COMMUNICATION MEDIA

Using the serializer's integrated de-emphasis blocks in combination with the DS32EL0124 or DS32ELX0124's integrated equalization blocks allows data to be transmitted across a variety of media at high speeds. Factors that can limit device performance include excessive input clock jitter, noisy power rails, EMI from nearby noisy components and poor layout techniques. Although many cables contain wires of similar gauge and shielding, performance can vary greatly depending on the quality of the connector.

#### **REDUNDANCY APPLICATIONS**

The DS32ELX0421 has two high speed CML serial outputs. SMBus register control allows the device to use a single output exclusively, or both outputs simultaneously. This allows a single serializer to transmit data to two independant receiving systems, a primary and secondary endpoint. Some applications require a redundancy measure in case the primary signal path is compromised. The secondary output can be activated "on-the-go", if a problem is detected on the primary link. See the Redundancy / Fail Over Configuration section located under Register Recipes.

#### **LINK AGGREGATION**

Multiple DS32EL0421/DS32ELX0421 serializers and D32EL0124/DS32ELX0124 deserializers can be aggregated together if an application requires a data throughput of more than 3.125 Gbps. By utilizing the data valid signal of each device, the system can be properly deskewed to allow for a single cable, such as CAT-6, DVI-D, or HDMI, to carry data payloads beyond 3.125 Gbps.

Link aggregation configurations can also be implemented in applications which require longer cable lengths. In these type of applications the data rate of each serializer and deserializer chipset can be reduced, such that the applications' net data throughput is still the same. Since each high speed channel is now operating at a fraction of the original data rate, the loss over the cable is reduced, allowing for greater lengths of cable to be used in the system.

For more information regarding link aggregation please see SNLA109, Expanding the Payload with TI's FPGA-Link DS32ELX0421 and DS32ELX0124 Serializer and Deserializer.

#### **LAYOUT GUIDELINES**

It is important to follow good layout practices for high speed devices. The length of LVDS input traces should not exceed 40 inches. In noisy environment the LVDS traces may need to be shorter to prevent data corruption due to EMI. Noisy components should not be placed next to the LVDS or CML traces. The LVDS and CML traces must have a controlled differential impedance of 100  $\Omega$ . Do not place termination resistor at the LVDS inputs or CML outputs, the DS32EL0421 and DS32ELX0421 have internal termination resistors. It is recommended to avoid using vias. Vias create an impedance mismatch in the transmission line and result in reflections, which can greatly lower the maximum distance of the high speed data link. If vias are required, they should be placed symmetrically on each side of the differential pair. For more tips and detailed suggestions regarding high speed board layout principles, please consult the LVDS Owner's Manual.

Figure 11. Typical Interface Circuit

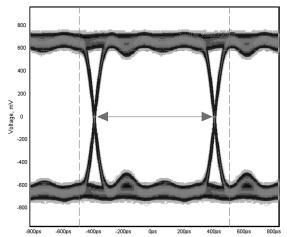

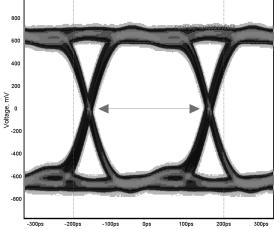

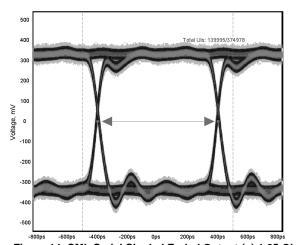

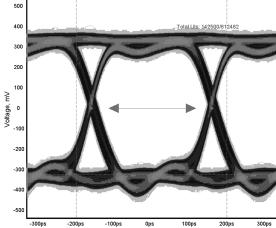

# **Typical Performance Characteristics**

The eye diagrams shown below illustrate the typical performace of the DS32ELX0421/DS32EL0421 configured with  $\overline{RS} = 0$ ,  $\overline{DC}_{\overline{B}} = 0$ , for the conditions listed below each figure. The PRBS-15 data was generated by a low cost FPGA, which used an LMK03000C to generate the various clock frequencies.

Figure 12. CML Serial Differential Output 1.25 Gbps

Figure 13. CML Serial Differential Output 3.125 Gbps

Figure 14. CML Serial Singled Ended Output (+) 1.25 Gbps

Figure 15. CML Serial Single Ended Output (+) 3.125 Gbps

# **Register Map**

The register information for the serializer is shown in the table below. Some registers have been omitted or marked as reserved; these are for internal testing and should not be written to. Some register bits require an override bit to be set before they can be written to.

| Addr<br>(Hex) | Name                          | Bits | Field          | R/W | Default | Description                                                                                                                                                                                                                                                 |

|---------------|-------------------------------|------|----------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00            | Device ID                     | 7:1  | SMBus Address  | R/W | 57'h    | Some systems will use all 8 bits as the device ID. This will shift the value from 57'h to AE'h                                                                                                                                                              |

|               |                               | 0    | Reserved       |     | 0       |                                                                                                                                                                                                                                                             |

| 01            | Reset                         | 7:5  | Reserved       |     | 0       |                                                                                                                                                                                                                                                             |

|               |                               | 4    | Analog Disable | R/W | 0       | 1: Disables analog blocks. Power save feature                                                                                                                                                                                                               |

|               |                               | 3:1  | Reserved       |     | 0       |                                                                                                                                                                                                                                                             |

|               |                               | 0    | Software Reset |     | 0       | 1: Reset the device. Does not affect device ID.                                                                                                                                                                                                             |

| 02            | GPIO0 Config                  | 7:4  | GPIO0 Mode     | R/W | 0       | 0000: GP out register<br>0001: Link loss indicator<br>0011: TxCLKIN loss of signal<br>0100: TxCLKIN detect<br>All others: Reserved                                                                                                                          |

|               |                               | 3:2  | GPIO0 R Enable | R/W | 01'b    | 00: Pullup/down disabled 01: Pulldown enabled 10: Pullup enabled 11: Reserved                                                                                                                                                                               |

|               |                               | 1    | Input Enable   | R/W | 0       | Input buffer disabled     Input buffer enabled                                                                                                                                                                                                              |

|               |                               | 0    | Output Enable  | R/W | 1'b     | 0: OutputTtri-State™<br>1: Output enabled                                                                                                                                                                                                                   |

| 03            | GPIO1 Config                  | 7:4  | GPIO1 Mode     | R/W | 0       | 0000: Power on reset 0001: GP out register 0010: PLL lock indicator 0011: TxIN0 loss of signal 0100: TxIN1 loss of signal 0101: TxIN2 loss of signal 0110: TxIN3 loss of signal 0111: TxIN4 loss of signal 0111: TxIN4 loss of signal All others: Reserverd |

|               |                               | 3:2  | GPIO1 R Enable | R/W | 01'b    | 00: Pullup/down disabled 01: Pulldown enabled 10: Pullup enabled 11: Reserved                                                                                                                                                                               |

|               |                               | 1    | Input Enable   | R/W | 0       | 0: Input buffer disabled 1: Input buffer enabled                                                                                                                                                                                                            |

|               |                               | 0    | Output Enable  | R/W | 1'b     | 0: Output Tri-State <sup>™</sup> 1: Output enabled                                                                                                                                                                                                          |

| 04            | O4 GPIO2 Config 7:4 GPIO2 Mod |      | GPIO2 Mode     | R/W | 0       | 0000: GP out register 0001: Always on clock out 0010: Parallel-to-serial clock out 0100: Digital clock out All others: Reserverd                                                                                                                            |

|               |                               | 3:2  | GPIO2 R Enable | R/W | 01'b    | 00: Pullup/down disabled 01: Pulldown enabled 10: Pullup enabled 11: Reserved                                                                                                                                                                               |

|               |                               | 1    | Input Enable   | R/W | 0       | 0: Input buffer disabled 1: Input buffer enabled                                                                                                                                                                                                            |

|               |                               | 0    | Output Enable  | R/W | 1'b     | 0: Output Tri-State™<br>1: Output enabled                                                                                                                                                                                                                   |

# SNLS282F -MAY 2008-REVISED APRIL 2013

| Addr<br>(Hex) | Name                       | Bits | Field                             | R/W | Default | Description                                                                                                                                                                                                |

|---------------|----------------------------|------|-----------------------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05            | GP In                      | 7:3  | Reserved                          |     | 0       |                                                                                                                                                                                                            |

|               |                            | 2    | GP In 2                           | R   | 0       | Input value on GPIO2                                                                                                                                                                                       |

|               |                            | 1    | GP In 1                           | R   | 0       | Input value on GPIO1                                                                                                                                                                                       |

|               |                            | 0    | GP In 0                           | R   | 0       | Input value on GPIO0                                                                                                                                                                                       |

| 06            | GP Out                     | 7:3  | Reserved                          |     | 0       |                                                                                                                                                                                                            |

|               |                            | 2    | GP Out 2                          | R/W | 0       | Output value on GPIO2                                                                                                                                                                                      |

|               |                            | 1    | GP Out 1                          | R/W | 0       | Output value on GPIO1                                                                                                                                                                                      |

|               |                            | 0    | GP Out 0                          | R/W | 0       | Output value on GPIO0                                                                                                                                                                                      |

| 07–1F R       | eserved                    |      |                                   |     |         |                                                                                                                                                                                                            |

| 20            | De-Emphasis                | 7:3  | Reserved                          |     | 0       |                                                                                                                                                                                                            |

|               |                            | 2    | Pin Override                      | R/W | 0       | Pin values determine setting     Register overrides pin values                                                                                                                                             |

|               |                            | 1:0  | De-emphasis<br>level              | R/W | 0       | 00: No de-emphasis<br>01: Low<br>10: Medium<br>11: High                                                                                                                                                    |

| 21            | Device Config              | 7    | NRZI enable                       | R/W | 0       | 1: Enable NRZI, if override bit is set                                                                                                                                                                     |

|               |                            | 6    | DV disable                        | R/W | 0       | 1: Disable Data Valid                                                                                                                                                                                      |

|               |                            | 5    | Reserved                          | R/W | 0       |                                                                                                                                                                                                            |

|               |                            | 4    | Scrambler Enable                  | R/W | 0       | 1: Scrambler enable, requires override bit to change setting                                                                                                                                               |

|               |                            | 3    | DC Bal encoder bypass             | R/W | 0       | 1: Bypass encoder, requires override bit to change setting                                                                                                                                                 |

|               |                            | 2    | Training<br>Sequence Enable       | R/W | 0       | 1: Enable training sequence, requires override bit to change setting                                                                                                                                       |

|               |                            | 1:0  | Device<br>Configuration           | R/W | 0       | MSB: Remote Sense enable, active low LSB: DC balance encoder enable, active low Requires override bit to change settings through registers. Normally controlled by pins. See Table 2 for more information. |

| 22            | Device Config              | 7:5  | Reserved                          |     | 0       |                                                                                                                                                                                                            |