#### SNLS012H - MAY 2000 - REVISED APRIL 2013

DS90C387, DS90CF388 Dual Pixel LVDS Display Interface (LDI)-SVGA/QXGA

Check for Samples: DS90C387, DS90CF388

# **FEATURES**

- **Complies with OpenLDI Specification for Digital Display Interfaces**

- 32.5 to 112/170MHz Clock Support for DS90C387, 40 to 112MHz Clock Support for DS90CF388

- Supports SVGA through QXGA Panel Resolutions

- **Drives Long, Low Cost Cables**

- Up to 5.38Gbps Bandwidth .

- **Pre-Emphasis Reduces Cable Loading Effects**

- **DC Balance Data Transmission Provided bv Transmitter Reduces ISI Distortion**

- Cable Deskew of +/-1 LVDS Data Bit Time (up to 80 MHz Clock Rate) of Pair-to-Pair Skew at **Receiver Inputs; Intra-Pair Skew Tolerance of** 300ps

- **Dual Pixel Architecture Supports Interface to GUI and Timing Controller; Optional Single Pixel Transmitter Inputs Support Single Pixel GUI Interface**

- Transmitter Rejects Cycle-to-Cycle Jitter

- 5V Tolerant on Data and Control Input Pins

- **Programmable Transmitter Data and Control** Strobe Select (Rising or Falling Edge Strobe)

- **Backward Compatible Configuration Select** with FPD-Link

- **Optional Second LVDS Clock for Backward** Compatibility w/ FPD-Link

- Support for Two Additional User-Defined **Control Signals in DC Balanced Mode**

- Compatible with ANSI/TIA/EIA-644-1995 LVDS ٠ Standard

# DESCRIPTION

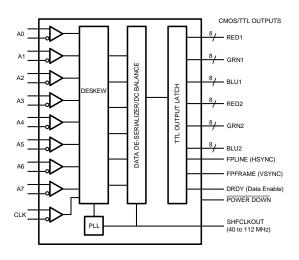

The DS90C387/DS90CF388 transmitter/receiver pair is designed to support dual pixel data transmission between Host and Flat Panel Display up to QXGA resolutions. The transmitter converts 48 bits (Dual Pixel 24-bit color) of CMOS/TTL data into 8 LVDS (Low Voltage Differential Signalling) data streams. Control signals (VSYNC, HSYNC, DE and two userdefined signals) are sent during blanking intervals. At a maximum dual pixel rate of 112MHz, LVDS data line speed is 672Mbps, providing a total throughput of 5.38Gbps (672 Megabytes per second). Two other modes are also supported. 24-bit color data (single pixel) can be clocked into the transmitter at a maximum rate of 170MHz. In this mode, the transmitter provides single-to-dual pixel conversion, and the output LVDS clock rate is 85MHz maximum. The third mode provides inter-operability with FPD-Link devices.

The LDI chipset is improved over prior generations of FPD-Link devices and offers higher bandwidth support and longer cable drive with three areas of enhancement. To increase bandwidth, the maximum pixel clock rate is increased to 112 (170) MHz and 8 serialized LVDS outputs are provided. Cable drive is enhanced with a user selectable pre-emphasis feature that provides additional output current during transitions to counteract cable loading effects. DC balancing on a cycle-to-cycle basis, is also provided to reduce ISI (Inter-Symbol Interference). With preemphasis and DC balancing, a low distortion evepattern is provided at the receiver end of the cable. A cable deskew capability has been added to deskew long cables of pair-to-pair skew of up to +/-1 LVDS data bit time (up to 80 MHz Clock Rate). These three enhancements allow cables 5+ meters in length to be driven. This chipset is an ideal means to solve EMI and cable size problems for high-resolution flat panel applications. It provides a reliable interface based on LVDS technology that delivers the bandwidth needed for high-resolution panels while maximizing bit times, and keeping clock rates low to reduce EMI and shielding requirements. For more details, please refer to Applications Information.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

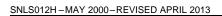

# **Transmitter Block Diagram**

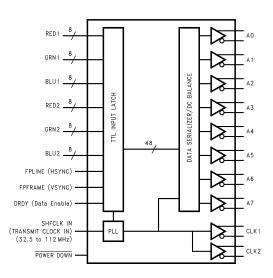

# **Receiver Block Diagram**

# **Generalized Block Diagram**

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

# Absolute Maximum Ratings<sup>(1)(2)</sup>

| Supply Voltage (V <sub>CC</sub> ) |                                        |                   | -0.3V to +4V                      |

|-----------------------------------|----------------------------------------|-------------------|-----------------------------------|

| CMOS/TTL Input Voltage            |                                        |                   | -0.3V to +5.5V                    |

| CMOS/TTL Output Voltage           |                                        |                   | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Receiver Input Voltage       | ge                                     |                   | -0.3V to +3.6V                    |

| LVDS Driver Output Voltag         | e                                      |                   | -0.3V to +3.6V                    |

| LVDS Output Short Circuit         | Duration                               |                   | Continuous                        |

| Junction Temperature              |                                        |                   | +150°C                            |

| Storage Temperature               |                                        |                   | -65°C to +150°C                   |

| Lead Temperature (Solderi         | ng, 4 seconds)                         |                   | +260°C                            |

| Maximum Package Power             | Dissipation Capacity at 25°C, 100 TQFP | DS90C387          | 2.8W                              |

| Package                           |                                        | DS90CF388         | 2.8W                              |

| Deckers Dereting                  |                                        | DS90C387          | 18.2mW/°C above +25°C             |

| Package Derating                  |                                        | DS90CF388         | 18.2mW/°C above +25°C             |

|                                   |                                        | HBM, 1.5kΩ, 100pF | > 6 kV                            |

| ESD Dating                        | DS90C387                               | EIAJ, 0Ω, 200pF   | > 300 V                           |

| ESD Rating                        | DS90CF388                              | HBM, 1.5kΩ, 100pF | > 2 kV                            |

|                                   | D330CF300                              | EIAJ, 0Ω, 200pF   | > 200 V                           |

"Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and

specifications.

## **Recommended Operating Conditions**

|                                                 | Min | Nom | Max | Unit              |

|-------------------------------------------------|-----|-----|-----|-------------------|

| Supply Voltage (V <sub>CC</sub> )               | 3.0 | 3.3 | 3.6 | V                 |

| Operating Free Air Temperature (T <sub>A)</sub> | -10 | +25 | +70 | °C                |

| Receiver Input Range                            | 0   |     | 2.4 | V                 |

| Supply Noise Voltage (V <sub>CC</sub> )         |     |     | 100 | mV <sub>p-p</sub> |

# Electrical Characteristics<sup>(1)</sup>

Over recommended operating supply and temperature ranges unless otherwise specified.

during storage or handling to prevent electrostatic damage to the MOS gates.

| Symbol          | Parameter                    | Conditions                                | Min   | Тур   | Max  | Unit |

|-----------------|------------------------------|-------------------------------------------|-------|-------|------|------|

| CMOS/TTL        | DC SPECIFICATIONS (Tx in     | puts, Rx outputs, control inputs and outp | outs) | -i    |      |      |

| VIH             | High Level Input Voltage     |                                           | 2.0   |       | 5.0  | V    |

| V <sub>IL</sub> | Low Level Input Voltage      |                                           | GND   |       | 0.8  | V    |

| V <sub>OH</sub> | High Level Output Voltage    | $I_{OH} = -0.4 \text{ mA}$                | 2.7   | 2.9   |      | V    |

|                 |                              | $I_{OH} = -2 \text{ mA}$                  | 2.7   | 2.85  |      | V    |

| V <sub>OL</sub> | Low Level Output Voltage     | I <sub>OL</sub> = 2 mA                    |       | 0.1   | 0.3  | V    |

| V <sub>CL</sub> | Input Clamp Voltage          | I <sub>CL</sub> = −18 mA                  |       | -0.79 | -1.5 | V    |

| I <sub>IN</sub> | Input Current                | $V_{IN} = 0.4V, 2.5V \text{ or } V_{CC}$  |       | +1.8  | +15  | μA   |

|                 |                              | V <sub>IN</sub> = GND                     | -15   | 0     |      | μA   |

| I <sub>OS</sub> | Output Short Circuit Current | V <sub>OUT</sub> = 0V                     |       |       | -120 | mA   |

(1) Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{OD}$  and  $\Delta V_{OD}$ ).

Texas Instruments

www.ti.com

# Electrical Characteristics<sup>(1)</sup> (continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                                                           | Conditio                                              | ons                                         | Min   | Тур  | Max   | Unit |

|------------------|---------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|-------|------|-------|------|

| LVDS DRI         | VER DC SPECIFICATIONS                                               |                                                       |                                             |       |      |       |      |

| V <sub>OD</sub>  | Differential Output Voltage                                         | R <sub>L</sub> = 100Ω                                 |                                             | 250   | 345  | 450   | mV   |

| ΔV <sub>OD</sub> | Change in V <sub>OD</sub> between<br>Complimentary Output<br>States | -                                                     |                                             |       |      | 35    | mV   |

| V <sub>OS</sub>  | Offset Voltage                                                      | -                                                     |                                             | 1.125 | 1.25 | 1.375 | V    |

| ΔV <sub>OS</sub> | Change in V <sub>OS</sub> between<br>Complimentary Output<br>States | *                                                     |                                             |       |      | 35    | mV   |

| l <sub>os</sub>  | Output Short Circuit Current                                        | $V_{OUT} = 0V, R_L = 100\Omega$                       |                                             |       | -3.5 | -10   | mA   |

| I <sub>OZ</sub>  | Output TRI-STATE Current                                            | $\overline{PD} = 0V, V_{OUT} = 0V \text{ or } V_{CC}$ |                                             |       | ±1   | ±10   | μA   |

| LVDS REC         | EIVER DC SPECIFICATIONS                                             | •                                                     |                                             |       |      |       |      |

| V <sub>TH</sub>  | Differential Input High<br>Threshold                                | V <sub>CM</sub> = +1.2V                               |                                             |       |      | +100  | mV   |

| V <sub>TL</sub>  | Differential Input Low<br>Threshold                                 |                                                       |                                             | -100  |      |       | mV   |

| I <sub>IN</sub>  | Input Current                                                       | V <sub>IN</sub> = +2.4V, V <sub>CC</sub> = 3.6V       |                                             |       |      | ±10   | μA   |

|                  |                                                                     | $V_{IN} = 0V, V_{CC} = 3.6V$                          |                                             |       |      | ±10   | μA   |

| TRANSMI          | ITER SUPPLY CURRENT                                                 |                                                       |                                             |       |      |       |      |

| ICCTW            | Transmitter Supply Current,                                         | $R_{L} = 100\Omega, C_{L} = 5 \text{ pF},$            | f = 32.5 MHz                                |       | 91.4 | 140   | mA   |

|                  | Worst Case                                                          | Worst Case Pattern<br>(Figure 1 and Figure 3),        | f = 65 MHz                                  |       | 106  | 160   | mA   |

|                  |                                                                     | DUAL=High (48-bit RGB),                               | f = 85 MHz                                  |       | 135  | 183   | mA   |

|                  |                                                                     | BAL=High (enabled)                                    | BAL=High (enabled) f = 112 MHz              |       | 155  | 210   | mA   |

| ICCTG            | Transmitter Supply Current,                                         | $R_L = 100\Omega, C_L = 5 \text{ pF},$                | f = 32.5 MHz                                |       | 62.6 | 120   | mA   |

|                  | 16 Grayscale                                                        | 16 Grayscale Pattern<br>(Figure 2 and Figure 3),      | f = 65 MHz                                  |       | 84.4 | 130   | mA   |

|                  |                                                                     |                                                       | f = 85 MHz                                  |       | 89.0 | 145   | mA   |

|                  |                                                                     | BAL=High (enabled)                                    | f = 112 MHz                                 |       | 94.5 | 155   | mA   |

| ICCTZ            | Transmitter Supply Current,                                         | PD = Low                                              |                                             |       | 4.8  | 50    | μA   |

|                  | Power Down                                                          | Driver Outputs in TRI-STAT<br>Mode                    | Driver Outputs in TRI-STATE under Powerdown |       |      |       |      |

4

Copyright © 2000–2013, Texas Instruments Incorporated

www.ti.com

# Electrical Characteristics<sup>(1)</sup> (continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol   | Parameter                                                                                                         | Condit                                                      | ions             | Min | Тур | Max | Unit |

|----------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|-----|-----|-----|------|

| RECEIVER | SUPPLY CURRENT                                                                                                    |                                                             |                  |     |     |     |      |

| ICCRW    | / Receiver Supply Current,<br>Worst Case C <sub>L</sub> = 8 pF,<br>Worst Case Pattern<br>(Figure 1 and Figure 4), | f = 40MHz                                                   |                  | 125 | 160 | mA  |      |

|          |                                                                                                                   | f = 65 MHz                                                  |                  | 200 | 250 | mA  |      |

|          |                                                                                                                   | DUAL (48-bit RGB),                                          | f = 85 MHz       |     | 240 | 275 | mA   |

|          | BAL=High (enabled)                                                                                                | f = 112 MHz                                                 |                  | 250 | 300 | mA  |      |

| ICCRG    | Receiver Support Current,                                                                                         | C <sub>L</sub> = 8 pF,                                      | f = 40MHz        |     | 60  | 95  | mA   |

|          | 16 Grayscale                                                                                                      | 16 Grayscale Pattern<br>(Figure 2 and Figure 4),            | f = 65 MHz       |     | 95  | 125 | mA   |

|          |                                                                                                                   | DUAL (48-bit RGB),                                          | f = 85 MHz       |     | 115 | 150 | mA   |

|          |                                                                                                                   | BAL=High (enabled)                                          | f = 112 MHz      |     | 150 | 270 | mA   |

| ICCRZ    | Receiver Supply Current,<br>Power Down                                                                            | PD = Low           Receiver Outputs stay low           mode | during Powerdown |     | 255 | 300 | μA   |

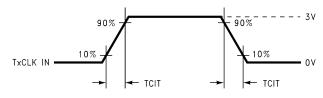

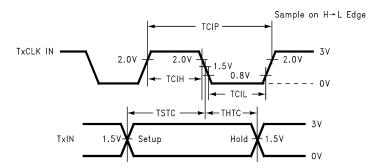

## **Recommended Transmitter Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                           |                 | Min   | Тур  | Max   | Unit |

|--------|-------------------------------------|-----------------|-------|------|-------|------|

| TCIT   | TxCLK IN Transition Time (Figure 5) | DUAL=Gnd or Vcc | 1.0   | 2.0  | 3.0   | ns   |

|        |                                     | DUAL=1/2Vcc     | 1.0   | 1.5  | 1.7   | ns   |

| TCIP   | TxCLK IN Period (Figure 6)          | DUAL=Gnd or Vcc | 8.928 | Т    | 30.77 | ns   |

|        |                                     | DUAL=1/2Vcc     | 5.88  |      | 15.38 | ns   |

| TCIH   | TxCLK in High Time (Figure 6)       |                 | 0.35T | 0.5T | 0.65T | ns   |

| TCIL   | TxCLK in Low Time (Figure 6)        |                 | 0.35T | 0.5T | 0.65T | ns   |

| TXIT   | TxIN Transition Time                |                 | 1.5   |      | 6.0   | ns   |

## **Transmitter Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                        |                       | Min  | Тур      | Max  | Unit |

|--------|--------------------------------------------------|-----------------------|------|----------|------|------|

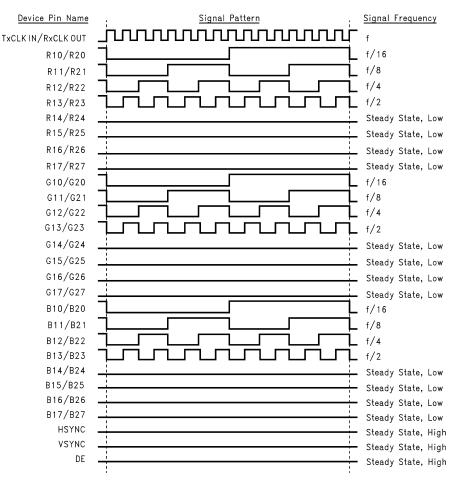

| LLHT   | LVDS Low-to-High Transition Time (Figure 3), PF  | RE = 0.75V (disabled) |      | 0.14     | 0.7  | ns   |

|        | LVDS Low-to-High Transition Time (Figure 3), PF  | RE = Vcc (max)        |      | 0.11     | 0.6  | ns   |

| LHLT   | LVDS High-to-Low Transition Time (Figure 3), PF  | RE = 0.75V (disabled) |      | 0.16     | 0.8  | ns   |

|        | LVDS High-to-Low Transition Time (Figure 3), PF  | RE = Vcc (max)        |      | 0.11     | 0.7  | ns   |

| TBIT   | Transmitter Output Bit Width                     | DUAL=Gnd or Vcc       |      | 1/7 TCIP |      | ns   |

|        |                                                  | DUAL=1/2Vcc           |      | 2/7 TCIP |      | ns   |

| TPPOS  | OS Transmitter Pulse Positions - Normalized      | f = 33 to 70 MHz      | -250 | 0        | +250 | ps   |

|        |                                                  | f = 70 to 112 MHz     | -200 | 0        | +200 | ps   |

| TCCS   | TxOUT Channel to Channel Skew                    |                       |      | 100      |      | ps   |

| TSTC   | TxIN Setup to TxCLK IN (Figure 6)                |                       | 2.7  |          |      | ns   |

| THTC   | TxIN Hold to TxCLK IN (Figure 6)                 |                       | 0    |          |      | ns   |

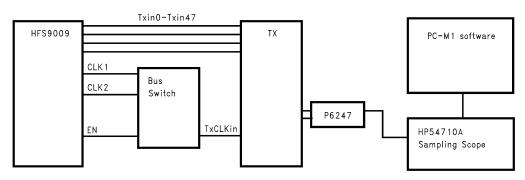

| TJCC   | Transmitter Jitter Cycle-to-cycle (Figure 14 and | f = 112 MHz           |      | 85       | 100  | ps   |

|        | Figure 15), DUAL=Vcc <sup>(1)</sup>              | f = 85 MHz            |      | 60       | 75   | ps   |

|        |                                                  | f = 65 MHz            |      | 70       | 80   | ps   |

|        |                                                  | f = 56 MHz            |      | 100      | 120  | ps   |

|        |                                                  | f = 32.5 MHz          |      | 75       | 110  | ps   |

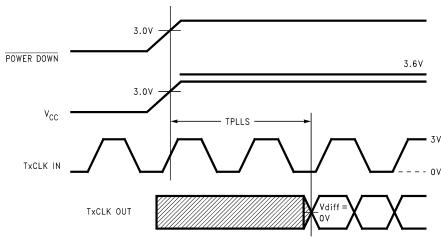

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 8)       |                       |      |          | 10   | ms   |

(1) The limits are based on bench characterization of the device's jitter response over the power supply voltage range. Output clock jitter is measured with a cycle-to-cycle jitter of ±3ns applied to the input clock signal while data inputs are switching (see Figure 14 and Figure 15). A jitter event of 3ns, represents worse case jump in the clock edge from most graphics VGA chips currently available. This parameter is used when calculating system margin as described in AN-1059 (SNLA050).

Copyright © 2000-2013, Texas Instruments Incorporated

www.ti.com

# **Transmitter Switching Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                               | Min | Тур | Max | Unit |

|--------|-----------------------------------------|-----|-----|-----|------|

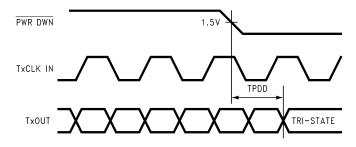

| TPDD   | Transmitter Powerdown Delay (Figure 10) |     |     | 100 | ns   |

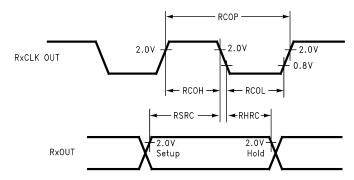

# **Receiver Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                          |                 | Min   | Тур  | Max | Unit |

|--------|----------------------------------------------------|-----------------|-------|------|-----|------|

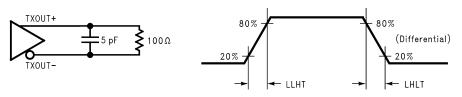

| CLHT   | CMOS/TTL Low-to-High Transition Time (Figure 4     | ), Rx data out  |       | 1.52 | 2.0 | ns   |

|        | CMOS/TTL Low-to-High Transition Time (Figure 4     | ), Rx clock out |       | 0.5  | 1.0 | ns   |

| CHLT   | CMOS/TTL High-to-Low Transition Time (Figure 4     | ), Rx data out  |       | 1.7  | 2.0 | ns   |

|        | CMOS/TTL High-to-Low Transition Time (Figure 4     | ), Rx clock out |       | 0.5  | 1.0 | ns   |

| RCOP   | RxCLK OUT Period (Figure 7)                        |                 | 8.928 | Т    | 25  | ns   |

| RCOH   | RxCLK OUT High Time (Figure 7) <sup>(1)</sup>      | f = 112 MHz     | 3.5   |      |     | ns   |

|        |                                                    | f = 85 MHz      | 4.5   |      |     | ns   |

| RCOL   | RxCLK OUT Low Time (Figure 7) <sup>(1)</sup>       | f = 112 MHz     | 3.5   |      |     | ns   |

|        |                                                    | f = 85 MHz      | 4.5   |      |     | ns   |

| RSRC   | RxOUT Setup to RxCLK OUT (Figure 7) <sup>(1)</sup> | f = 112 MHz     | 2.4   |      |     | ns   |

|        |                                                    | f = 85 MHz      | 3.0   |      |     | ns   |

| RHRC   | RxOUT Hold to RxCLK OUT (Figure 7) <sup>(1)</sup>  | f = 112 MHz     | 3.4   |      |     | ns   |

|        |                                                    | f = 85 MHz      | 4.75  |      |     | ns   |

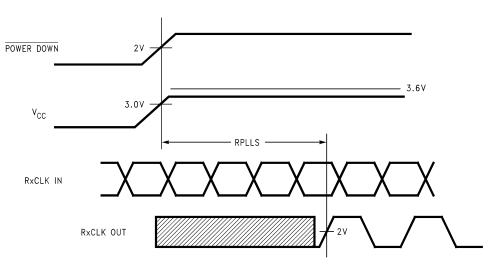

| RPLLS  | Receiver Phase Lock Loop Set (Figure 9)            | u               |       |      | 10  | ms   |

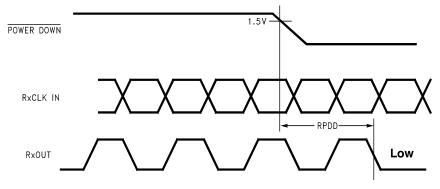

| RPDD   | Receiver Powerdown Delay (Figure 11)               |                 |       |      | 1   | μs   |

(1) The Minimum and Maximum Limits are based on statistical analysis of the device performance over voltage and temperature ranges. This parameter is functionally tested on Automatic Test Equipment (ATE). ATE is limited to 85MHz. A sample of characterization parts have been bench tested to verify functional performance.

# **Chipset RSKM Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.<sup>(1)</sup> <sup>(2)</sup>. See Applications Information for more details on this parameter and how to apply it.

| Symbol | Parameter                                                                         |             | Min | Тур | Max | Unit |

|--------|-----------------------------------------------------------------------------------|-------------|-----|-----|-----|------|

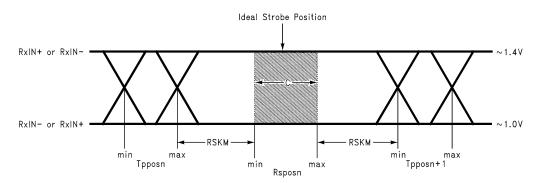

| RSKM   | Receiver Skew Margin without Deskew in non-DC Balance Mode, (Figure 12), $^{(3)}$ | f = 112 MHz | 170 |     |     | ps   |

|        |                                                                                   | f = 100 MHz | 170 | 240 |     | ps   |

|        |                                                                                   | f = 85MHz   | 300 | 350 |     | ps   |

|        |                                                                                   | f = 66MHz   | 300 | 350 |     | ps   |

| RSKM   |                                                                                   | f = 112 MHz | 170 |     |     | ps   |

|        | (Figure 12) <sup>(3)</sup>                                                        | f = 100 MHz | 170 | 200 |     | ps   |

|        |                                                                                   | f = 85 MHz  | 250 | 300 |     | ps   |

|        |                                                                                   | f = 66 MHz  | 250 | 300 |     | ps   |

|        |                                                                                   | f = 50MHz   | 100 | 350 |     | ps   |

|        |                                                                                   | f = 40MHz   | 94  | 530 |     | ps   |

- (1) The Minimum and Maximum Limits are based on statistical analysis of the device performance over voltage and temperature ranges. This parameter is functionally tested on Automatic Test Equipment (ATE). ATE is limited to 85MHz. A sample of characterization parts have been bench tested to verify functional performance.

- (2) Typical values for RSKM and RSKMD are applicable for fixed  $V_{CC}$  and T A for the Transmitter and Receiver (both are assumed to be at the same  $V_{CC}$  and T A points).

- (3) Receiver Skew Margin (RSKM) is defined as the valid data sampling region at the receiver inputs. This margin takes into account transmitter output pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window RSPOS). This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type/length of cable) and clock jitter.RSKM ≥ cable skew (type, length) + source clock jitter (cycle to cycle, TJCC) + ISI (if any). See Applications Information for more details.

#### www.ti.com

### Chipset RSKM Characteristics (continued)

Over recommended operating supply and temperature ranges unless otherwise specified.<sup>(1) (2)</sup>. See Applications Information for more details on this parameter and how to apply it.

| Symbol | Parameter                                                                  |                  | Min      | Тур      | Мах | Unit |

|--------|----------------------------------------------------------------------------|------------------|----------|----------|-----|------|

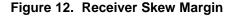

| RSKMD  | Receiver Skew Margin with Deskew in DC Balance, (Figure 13) <sup>(4)</sup> | f = 40 to 80 MHz | 0.25TBIT |          |     | ps   |

| RDR    | Receiver Deskew Range                                                      | f = 80 MHz       | ± 1      |          |     | TBIT |

| RDSS   | Receiver Deskew Step Size                                                  | f = 80 MHz       |          | 0.3 TBIT |     | ns   |

(4) Receiver Skew Margin with Deskew (RSKMD) is defined as the valid data sampling region at the receiver inputs. The DESKEW function will constrain the receiver's sampling strobes to the middle half of the LVDS bit and removes (adjusts for) fixed interconnect skew. This margin (RSKMD) allows for inter-symbol interference (dependent on type/length of cable), Transmitter Pulse Position (TPPOS) variance, and LVDS clock jitter (TJCC).RSKMD ≥ ISI + TPPOS(variance) + source clock jitter (cycle to cycle). See Applications Information for more details.

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and CMOS/TTL I/O.

- B. Figure 1 and Figure 2 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

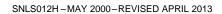

#### Figure 1. "Worst Case" Test Pattern

- A. The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

- B. Figure 1 and Figure 2 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

Figure 2. "16 Grayscale" Test Pattern

Figure 3. DS90C387 (Transmitter) LVDS Output Load and Transition Times

Figure 4. DS90CF388 (Receiver) CMOS/TTL Output Load and Transition Times

8

XAS

**STRUMENTS**

SNLS012H - MAY 2000 - REVISED APRIL 2013

Figure 5. DS90C387 (Transmitter) Input Clock Transition Time

Figure 6. DS90C387 (Transmitter) Setup/Hold and High/Low Times (Falling Edge Strobe)

Figure 7. DS90CF388 (Receiver) Setup/Hold and High/Low Times

Figure 8. DS90C387 (Transmitter) Phase Lock Loop Set Time

# DS90C387, DS90CF388

SNLS012H-MAY 2000-REVISED APRIL 2013

www.ti.com

Figure 9. DS90CF388 (Receiver) Phase Lock Loop Set Time

Figure 10. Transmitter Power Down Delay

Figure 11. Receiver Power Down Delay

**ISTRUMENTS**

C — Setup and Hold Time (Internal data sampling window) defined by RSPOS (receiver input strobe position) min and max

TPPOS — Transmitter output pulse position (min and max)

RSKM ≥ Cable Skew (type, length) + LVDS Source Clock Jitter (cycle to cycle) + ISI (Inter-symbol interference) ■ Cable Skew—typically 10 ps to 40 ps per foot, media dependent

■ TJCC — Cycle-to-cycle LVDS Output jitter (TJCC) is less than 100 ps (worse case estimate).

■ ISI is dependent on interconnect length; may be zero

See Applications Information for more details.

C — Setup and Hold Time (Internal data sampling window) defined by Rspos (receiver input strobe position) min and max

RSKMD ≥ TPPOSvariance (d) + TJCC (output jitter)(f) + ISI (m)

■ d = Tppos — Transmitter output pulse position (min and max)

f = TJCC — Cycle-to-cycle LVDS Output jitter (TJCC) is less than 100 ps (worse case estimate).

■ m = extra margin - assigned to ISI in long cable applications

See Applications Information for more details.

# DS90C387, DS90CF388

www.ti.com

### SNLS012H-MAY 2000-REVISED APRIL 2013

Figure 15. Timing Diagram of the Input Cycle-to-Cycle Clock Jitter

## TEXAS INSTRUMENTS

# DS90C387, DS90CF388

www.ti.com

### SNLS012H - MAY 2000 - REVISED APRIL 2013

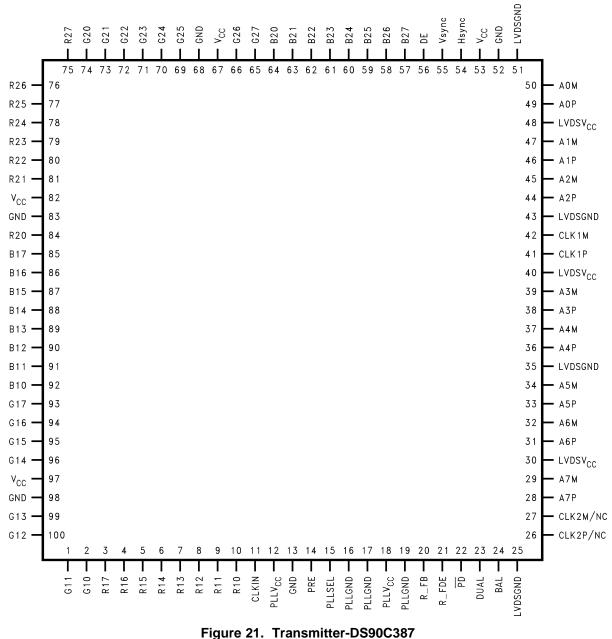

| DS90C387 PIN DESCRIPTIONS — | FPD LINK TRANSMITTER |

|-----------------------------|----------------------|

|-----------------------------|----------------------|

| Pin Name                        | I/O | No. | Description                                                                                                                                                                                                                                                                                                                            |  |  |

|---------------------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rn, Gn, Bn, DE,<br>HSYNC, VSYNC | Ι   | 51  | TTL level input. This includes: 16 Red, 16 Green, 16 Blue, and 3 control lines HSYNC, VSYNC, DE (Data Enable). <sup>(1)</sup>                                                                                                                                                                                                          |  |  |

| AnP                             | 0   | 8   | Positive LVDS differential data output.                                                                                                                                                                                                                                                                                                |  |  |

| AnM                             | 0   | 8   | Negative LVDS differential data output.                                                                                                                                                                                                                                                                                                |  |  |

| CLKIN                           | I   | 1   | TTL level clock input.                                                                                                                                                                                                                                                                                                                 |  |  |

| R_FB                            | I   | 1   | Programmable data strobe select. Rising data strobe edge selected when input is high. (1)                                                                                                                                                                                                                                              |  |  |

| R_FDE                           | I   | 1   | Programmable control (DE) strobe select. Tied high for data active when DE is high. <sup>(1)</sup>                                                                                                                                                                                                                                     |  |  |

| CLK1P                           | 0   | 1   | Positive LVDS differential clock output.                                                                                                                                                                                                                                                                                               |  |  |

| CLK1M                           | 0   | 1   | Negative LVDS differential clock output.                                                                                                                                                                                                                                                                                               |  |  |

| PD                              | I   | 1   | TTL level input. Assertion (low input) tri-states the outputs, ensuring low current at power down. <sup>(1)</sup>                                                                                                                                                                                                                      |  |  |

| PLLSEL                          | I   | 1   | PLL range select. This pin must be tied to $V_{CC}$ for auto-range. NC or tied to Ground is reserved for future use. Typical shift point is between 55 and 68 MHz. <sup>(1)</sup> <sup>(2)</sup>                                                                                                                                       |  |  |

| BAL                             | I   | 1   | Mode select for DC Balanced (new) or non-DC Balanced (backward compatible) interface. DC Balance is active when input is high. NC or tied to Ground, the DC Balance function is disabled. $^{(1)}$                                                                                                                                     |  |  |

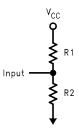

| PRE                             | I   | 1   | Pre-emphasis level select. Pre-emphasis is active when input is tied to V <sub>CC</sub> through external pull-up resistor. Resistor value determines pre-emphasis level (see Pre-Emphasis). For normal LVDS drive level (No pre-emphasis) leave this pin open (do not tie to ground). <sup>(1)</sup>                                   |  |  |

| DUAL                            | I   | 1   | Three-mode select for dual pixel, single pixel, or single pixel input to dual pixel output operation.<br>Single pixel mode when input is low (only LVDS channels A0 thru A3 and CLK1 are active) for power savings. Dual mode is active when input is high. Single in - dual out when input is at 1/2 Vcc. <sup>(1)</sup><br>Figure 16 |  |  |

| V <sub>CC</sub>                 | I   | 4   | Power supply pins for TTL inputs and digital circuitry.                                                                                                                                                                                                                                                                                |  |  |

| GND                             | I   | 5   | Ground pins for TTL inputs and digital circuitry.                                                                                                                                                                                                                                                                                      |  |  |

| PLLV <sub>CC</sub>              | I   | 2   | Power supply pin for PLL circuitry.                                                                                                                                                                                                                                                                                                    |  |  |

| PLLGND                          | I   | 3   | Ground pins for PLL circuitry.                                                                                                                                                                                                                                                                                                         |  |  |

| LVDSV <sub>CC</sub>             | I   | 3   | Power supply pin for LVDS outputs.                                                                                                                                                                                                                                                                                                     |  |  |

| LVDSGND                         | I   | 4   | Ground pins for LVDS outputs.                                                                                                                                                                                                                                                                                                          |  |  |

| CLK2P/NC                        | 0   | 1   | Additional positive LVDS differential clock output. Identical to CLK1P. No connect if not used.                                                                                                                                                                                                                                        |  |  |

| CLK2M/NC                        | 0   | 1   | Additional negative LVDS differential clock output. Identical to CLK1M. No connect if not used.                                                                                                                                                                                                                                        |  |  |

(1) Inputs default to "low" when left open due to internal pull-down resistor.

(2) The PLL range shift point is in the 55 - 68 MHz range, typically the shift will occur during the lock time.

(3) DC Balancing is functionally tested on Automatic Test Equipment (ATE) at 85 MHz only. A sample of characterization units have been bench tested at 112 MHz to verify full speed performance.

(4) The DS90CF388 is designed to automatically detect the DC Balance or non-DC Balance transmitted data from the DS90C387 and deserialize the LVDS data according to the defined bit mapping.

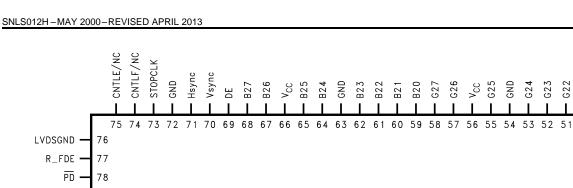

### DS90CF388 PIN DESCRIPTIONS — FPD LINK RECEIVER

| Pin Name                        | I/O | No. | Description                                                                                                                                                                                  |

|---------------------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AnP                             | I   | 8   | Positive LVDS differential data inputs.                                                                                                                                                      |

| AnM                             | I   | 8   | Negative LVDS differential data inputs.                                                                                                                                                      |

| Rn, Gn, Bn, DE,<br>HSYNC, VSYNC | 0   | 51  | TTL level data outputs. This includes: 16 Red, 16 Green, 16 Blue, and 3 control lines— HSYNC (LP), VSYNC (FLM), DE (Data Enable).                                                            |

| RxCLK INP                       | I   | 1   | Positive LVDS differential clock input.                                                                                                                                                      |

| RxCLK INM                       | I   | 1   | Negative LVDS differential clock input.                                                                                                                                                      |

| RxCLK OUT                       | 0   | 1   | TTL level clock output. The falling edge acts as data strobe.                                                                                                                                |

| R_FDE                           | I   | 1   | Programmable control (DE) strobe select. Tied high for data active when DE is high. (1)                                                                                                      |

| PLLSEL                          | I   | 1   | PLL range select. This pin must be tied to V <sub>CC</sub> for auto-range. NC or tied to Ground is reserved for future use. Typical shift point is between 55 and 68 MHz. <sup>(2)</sup> (3) |

(1) Inputs default to "low" when left open due to internal pull-down resistor.

(2) DC Balancing is functionally tested on Automatic Test Equipment (ATE) at 85 MHz only. A sample of characterization units have been bench tested at 112 MHz to verify full speed performance.

(3) The PLL range shift point is in the 55 - 68 MHz range, typically the shift will occur during the lock time.

Copyright © 2000–2013, Texas Instruments Incorporated

TEXAS INSTRUMENTS

www.ti.com

SNLS012H-MAY 2000-REVISED APRIL 2013

### DS90CF388 PIN DESCRIPTIONS — FPD LINK RECEIVER (continued)

| Pin Name            | I/O | No. | Description                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BAL                 | I   | 1   | Mode select for DC Balanced (new) or non-DC Balanced (backward compatible) interface. BAL = LOW for non-DC Balanced mode. BAL = HIGH for DC Balanced Mode (Auto-detect mode), with this pin HIGH the received LVDS clock signal is used to determine if the interface is in new or backward compatible mode. <sup>(1)</sup> <sup>(2)</sup> <sup>(4)</sup> |  |

| DESKEW              | I   | 1   | Deskew and oversampling "on/off" select. Deskew is active when input is high. Only supported in DC Balance mode (BAL=High). To complete the deskew operation, a minimum of four clock cycles is required during blanking time. <sup>(1)</sup>                                                                                                             |  |

| PD                  | I   | 1   | $TTL_{(1)}$ level input. When asserted (low input) the receiver data outputs are low and clock output is high.                                                                                                                                                                                                                                            |  |

| STOPCLK             | 0   | 1   | Indicates receiver clock input signal is not present with a logic high. With a clock input present, a low logic is indicated.                                                                                                                                                                                                                             |  |

| V <sub>CC</sub>     | I   | 6   | Power supply pins for TTL outputs and digital circuitry.                                                                                                                                                                                                                                                                                                  |  |

| GND                 | I   | 8   | Ground pins for TTL outputs and digital circuitry                                                                                                                                                                                                                                                                                                         |  |

| PLLV <sub>CC</sub>  | I   | 1   | Power supply for PLL circuitry.                                                                                                                                                                                                                                                                                                                           |  |

| PLLGND              | I   | 2   | Ground pin for PLL circuitry.                                                                                                                                                                                                                                                                                                                             |  |

| LVDSV <sub>CC</sub> | I   | 2   | wer supply pin for LVDS inputs.                                                                                                                                                                                                                                                                                                                           |  |

| LVDSGND             | I   | 3   | round pins for LVDS inputs.                                                                                                                                                                                                                                                                                                                               |  |

| CNTLE, CNTLF        | 0   | 2   | TTL level data outputs. User-defined control signals - no connect when not used.                                                                                                                                                                                                                                                                          |  |

(4) The DS90CF388 is designed to automatically detect the DC Balance or non-DC Balance transmitted data from the DS90C387 and deserialize the LVDS data according to the defined bit mapping.

Recommend using R1=R2=10k $\Omega$  for single to dual mode

### Figure 16. Resistor Network for "DUAL" pin input

# LVDS Interface

### Table 1. LVDS DATA BIT NAMING CONVENTION

| X   | Y   | Z     | Description                                     |  |  |

|-----|-----|-------|-------------------------------------------------|--|--|

| X=R |     |       | Red                                             |  |  |

| X=G |     |       | Green                                           |  |  |

| X=B |     |       | Blue                                            |  |  |

|     | Y=1 |       | Odd (First) Pixel                               |  |  |

|     | Y=2 |       | Even (Second) Pixel                             |  |  |

|     |     | Z=0-7 | LVDS bit number (not VGA controller LSB to MSB) |  |  |

### Table 2. SINGLE PIXEL PER CLOCK INPUT APPLICATION DATA MAPPING (DUAL=GND)

| VGA - TFT | Data Signals | S Color Bits | Transmitter input pin names | Receiver output pin names | TFT Panel Data<br>Signals |        |

|-----------|--------------|--------------|-----------------------------|---------------------------|---------------------------|--------|

|           | 24-bit       | 18-bit       | DS90C387                    | DS90CF388                 | 18-bit                    | 24-bit |

| LSB       | R0           |              | R16                         | R16                       |                           | R0     |

|           | R1           |              | R17                         | R17                       |                           | R1     |

|           | R2           | R0           | R10                         | R10                       | R0                        | R2     |

# DS90C387, DS90CF388

www.ti.com

SNLS012H - MAY 2000 - REVISED APRIL 2013

### Table 2. SINGLE PIXEL PER CLOCK INPUT APPLICATION DATA MAPPING (DUAL=GND) (continued)

| VGA - TFT Data Signals Color Bits |    |    | TFT Data Signals Color Bits Transmitter input pin names | Receiver output pin names | TFT Panel Data<br>Signals |    |

|-----------------------------------|----|----|---------------------------------------------------------|---------------------------|---------------------------|----|

|                                   | R3 | R1 | R11                                                     | R11                       | R1                        | R3 |

|                                   | R4 | R2 | R12                                                     | R12                       | R2                        | R4 |

|                                   | R5 | R3 | R13                                                     | R13                       | R3                        | R5 |

|                                   | R6 | R4 | R14                                                     | R14                       | R4                        | R6 |

| MSB                               | R7 | R5 | R15                                                     | R15                       | R5                        | R7 |

| LSB                               | G0 |    | G16                                                     | G16                       |                           | G0 |

|                                   | G1 |    | G17                                                     | G17                       |                           | G1 |

|                                   | G2 | G0 | G10                                                     | G10                       | G0                        | G2 |

|                                   | G3 | G1 | G11                                                     | G11                       | G1                        | G3 |

|                                   | G4 | G2 | G12                                                     | G12                       | G2                        | G4 |

|                                   | G5 | G3 | G13                                                     | G13                       | G3                        | G5 |

|                                   | G6 | G4 | G14                                                     | G14                       | G4                        | G6 |

| MSB                               | G7 | G5 | G15                                                     | G15                       | G5                        | G7 |

| LSB                               | B0 |    | B16                                                     | B16                       |                           | B0 |

|                                   | B1 |    | B17                                                     | B17                       |                           | B1 |

|                                   | B2 | B0 | B10                                                     | B10                       | B0                        | B2 |

|                                   | B3 | B1 | B11                                                     | B11                       | B1                        | B3 |

|                                   | B4 | B2 | B12                                                     | B12                       | B2                        | B4 |

|                                   | B5 | B3 | B13                                                     | B13                       | B3                        | B5 |

|                                   | B6 | B4 | B14                                                     | B14                       | B4                        | B6 |

| MSB                               | B7 | B5 | B15                                                     | B15                       | B5                        | B7 |

# Table 3. DUAL PIXEL PER CLOCK INPUT APPLICATION DATA MAPPING (DUAL=VCC)

| VGA - TFT Data Signals Color Bits |        | s Color Bits | Transmitter input pin names | Receiver output pin names | TFT Panel Data<br>Signals |        |

|-----------------------------------|--------|--------------|-----------------------------|---------------------------|---------------------------|--------|

|                                   | 48-bit | 36-bit       | DS90C387                    | DS90CF388                 | 36-bit                    | 48-bit |

| LSB                               | RO0    |              | R16                         | R16                       |                           | RO0    |

|                                   | RO1    |              | R17                         | R17                       |                           | RO1    |

|                                   | RO2    | RO0          | R10                         | R10                       | RO0                       | RO2    |

|                                   | RO3    | RO1          | R11                         | R11                       | RO1                       | RO3    |

|                                   | RO4    | RO2          | R12                         | R12                       | RO2                       | RO4    |

|                                   | RO5    | RO3          | R13                         | R13                       | RO3                       | RO5    |

|                                   | RO6    | RO4          | R14                         | R14                       | RO4                       | RO6    |

| MSB                               | RO7    | RO5          | R15                         | R15                       | RO5                       | RO7    |

| LSB                               | GO0    |              | G16                         | G16                       |                           | GO0    |

|                                   | GO1    |              | G17                         | G17                       |                           | GO1    |

|                                   | GO2    | GO0          | G10                         | G10                       | GO0                       | GO2    |

|                                   | GO3    | GO1          | G11                         | G11                       | GO1                       | GO3    |

|                                   | GO4    | GO2          | G12                         | G12                       | GO2                       | GO4    |

|                                   | GO5    | GO3          | G13                         | G13                       | GO3                       | GO5    |

|                                   | GO6    | GO4          | G14                         | G14                       | GO4                       | GO6    |

| MSB                               | G07    | GO5          | G15                         | G15                       | GO5                       | GO7    |

| LSB                               | BO0    |              | B16                         | B16                       |                           | BO0    |

|                                   | BO1    |              | B17                         | B17                       |                           | BO1    |

|                                   | BO2    | BO0          | B10                         | B10                       | BO0                       | BO2    |

|                                   | BO3    | BO1          | B11                         | B11                       | BO1                       | BO3    |

|                                   | BO4    | BO2          | B12                         | B12                       | BO2                       | BO4    |

Copyright © 2000–2013, Texas Instruments Incorporated

Submit Documentation Feedback 15

www.ti.com

# Table 3. DUAL PIXEL PER CLOCK INPUT APPLICATION DATA MAPPING (DUAL=VCC) (continued)

| VGA - TFT Data Signals Color Bits |     | s Color Bits | Transmitter input pin names | Receiver output pin names | TFT Panel Data<br>Signals |     |  |

|-----------------------------------|-----|--------------|-----------------------------|---------------------------|---------------------------|-----|--|

|                                   | BO5 | BO3          | B13                         | B13                       | BO3                       | BO5 |  |

|                                   | BO6 | BO4          | B14                         | B14                       | BO4                       | BO6 |  |

| MSB                               | BO7 | BO5          | B15                         | B15                       | BO5                       | BO7 |  |

| LSB                               | RE0 |              | R26                         | R26                       |                           | RE0 |  |

|                                   | RE1 |              | R27                         | R27                       |                           | RE1 |  |

|                                   | RE2 | RE0          | R20                         | R20                       | RE0                       | RE2 |  |

|                                   | RE3 | RE1          | R21                         | R21                       | RE1                       | RE3 |  |

|                                   | RE4 | RE2          | R22                         | R22                       | RE2                       | RE4 |  |

|                                   | RE5 | RE3          | R23                         | R23                       | RE3                       | RE5 |  |

|                                   | RE6 | RE4          | R24                         | R24                       | RE4                       | RE6 |  |

| MSB                               | RE7 | RE5          | R25                         | R25                       | RE5                       | RE7 |  |

| LSB                               | GE0 |              | G26                         | G26                       |                           | GE0 |  |

|                                   | GE1 |              | G27                         | G27                       |                           | GE1 |  |

|                                   | GE2 | GE0          | G20                         | G20                       | GE0                       | GE2 |  |

|                                   | GE3 | GE1          | G21                         | G21                       | GE1                       | GE3 |  |

|                                   | GE4 | GE2          | G22                         | G22                       | GE2                       | GE4 |  |

|                                   | GE5 | GE3          | G23                         | G23                       | GE3                       | GE5 |  |

|                                   | GE6 | GE4          | G24                         | G24                       | GE4                       | GE6 |  |

| MSB                               | GE7 | GE5          | G25                         | G25                       | GE5                       | GE7 |  |

| LSB                               | BE0 |              | B26                         | B26                       |                           | BE0 |  |

|                                   | BE1 |              | B27                         | B27                       |                           | BE1 |  |

|                                   | BE2 | BE0          | B20                         | B20                       | BE0                       | BE2 |  |

|                                   | BE3 | BE1          | B21                         | B21                       | BE1                       | BE3 |  |

|                                   | BE4 | BE2          | B22                         | B22                       | BE2                       | BE4 |  |

|                                   | BE5 | BE3          | B23                         | B23                       | BE3                       | BE5 |  |

|                                   | BE6 | BE4          | B24                         | B24                       | BE4                       | BE6 |  |

| MSB                               | BE7 | BE5          | B25                         | B25                       | BE5                       | BE7 |  |

# Table 4. SINGLE PIXEL PER CLOCK INPUT-TO-DUAL PIXEL PER CLOCK OUTPUT DATA MAPPING (DUAL=1/2VCC)

| VGA - TFT Data Signals Color Bits |        | s Color Bits | Transmitter input pin names | Receiver output pin names | TFT Panel Data<br>Signals |        |

|-----------------------------------|--------|--------------|-----------------------------|---------------------------|---------------------------|--------|

|                                   | 24-bit | 18-bit       | DS90C387                    | DS90CF388                 | 36-bit                    | 48-bit |

| LSB                               | R0     |              | R16                         | R16                       |                           | RO0    |

|                                   | R1     |              | R17                         | R17                       |                           | RO1    |

|                                   | R2     | R0           | R10                         | R10                       | RO0                       | RO2    |

|                                   | R3     | R1           | R11                         | R11                       | RO1                       | RO3    |

|                                   | R4     | R2           | R12                         | R12                       | RO2                       | RO4    |

|                                   | R5     | R3           | R13                         | R13                       | RO3                       | RO5    |

|                                   | R6     | R4           | R14                         | R14                       | RO4                       | RO6    |

| MSB                               | R7     | R5           | R15                         | R15                       | RO5                       | RO7    |

| LSB                               | G0     |              | G16                         | G16                       |                           | GO0    |

|                                   | G1     |              | G17                         | G17                       |                           | GO1    |

|                                   | G2     | G0           | G10                         | G10                       | GO0                       | GO2    |

|                                   | G3     | G1           | G11                         | G11                       | GO1                       | GO3    |

|                                   | G4     | G2           | G12                         | G12                       | GO2                       | GO4    |

|                                   | G5     | G3           | G13                         | G13                       | GO3                       | GO5    |

Copyright © 2000–2013, Texas Instruments Incorporated

# DS90C387, DS90CF388

SNLS012H - MAY 2000 - REVISED APRIL 2013

www.ti.com

Table 4. SINGLE PIXEL PER CLOCK INPUT-TO-DUAL PIXEL PER CLOCK OUTPUT DATA MAPPING (DUAL=1/2VCC) (continued)

| VGA - TFT Data Signals Color Bits |    | s Color Bits | Transmitter input pin names | Receiver output pin names | TFT Panel Data<br>Signals |     |  |

|-----------------------------------|----|--------------|-----------------------------|---------------------------|---------------------------|-----|--|

|                                   | G6 | G4           | G14                         | G14                       | GO4                       | GO6 |  |

| MSB                               | G7 | G5           | G15                         | G15                       | GO5                       | GO7 |  |

| LSB                               | B0 |              | B16                         | B16                       |                           | BO0 |  |

|                                   | B1 |              | B17                         | B17                       |                           | BO1 |  |

|                                   | B2 | B0           | B10                         | B10                       | BO0                       | BO2 |  |

|                                   | B3 | B1           | B11                         | B11                       | BO1                       | BO3 |  |

|                                   | B4 | B2           | B12                         | B12                       | BO2                       | BO4 |  |

|                                   | B5 | B3           | B13                         | B13                       | BO3                       | BO5 |  |

|                                   | B6 | B4           | B14                         | B14                       | BO4                       | BO6 |  |

| MSB                               | B7 | B5           | B15                         | B15                       | BO5                       | BO7 |  |

|                                   |    |              | R16                         | R26                       |                           | RE0 |  |

|                                   |    |              | R17                         | R27                       |                           | RE1 |  |

|                                   |    |              | R10                         | R20                       | RE0                       | EO2 |  |

|                                   |    |              | R11                         | R21                       | RE1                       | RE3 |  |

|                                   |    |              | R12                         | R22                       | RE2                       | RE4 |  |

|                                   |    |              | R13                         | R23                       | RE3                       | RE5 |  |

|                                   |    |              | R14                         | R24                       | RE4                       | RE6 |  |

|                                   |    |              | R15                         | R25                       | RE5                       | RE7 |  |

|                                   |    |              | G16                         | G26                       |                           | GE0 |  |

|                                   |    |              | G17                         | G27                       |                           | GE1 |  |

|                                   |    |              | G10                         | G20                       | GE0                       | GE2 |  |

|                                   |    |              | G11                         | G21                       | GE1                       | GE3 |  |

|                                   |    |              | G12                         | G22                       | GE2                       | GE4 |  |

|                                   |    |              | G13                         | G23                       | GE3                       | GE5 |  |

|                                   |    |              | G14                         | G24                       | GE4                       | GE6 |  |

|                                   |    |              | G15                         | G25                       | GE5                       | GE7 |  |

|                                   |    |              | B16                         | B26                       |                           | BE0 |  |

|                                   |    |              | B17                         | B27                       |                           | BE1 |  |

|                                   |    |              | B10                         | B20                       | BE0                       | BE2 |  |

|                                   |    |              | B11                         | B21                       | BE1                       | BE3 |  |

|                                   |    |              | B12                         | B22                       | BE2                       | BE4 |  |

|                                   |    |              | B13                         | B23                       | BE3                       | BE5 |  |

|                                   |    |              | B14                         | B24                       | BE4                       | BE6 |  |

|                                   |    |              | B15                         | B25                       | BE5                       | BE7 |  |

# DS90C387, DS90CF388

SNLS012H-MAY 2000-REVISED APRIL 2013

www.ti.com

STRUMENTS

EXAS

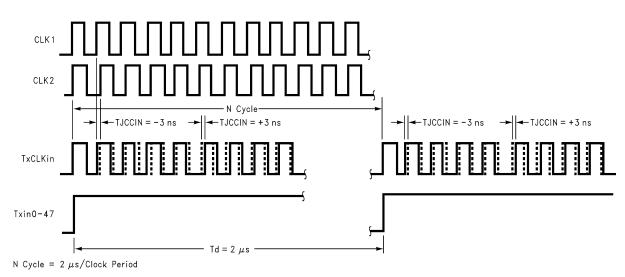

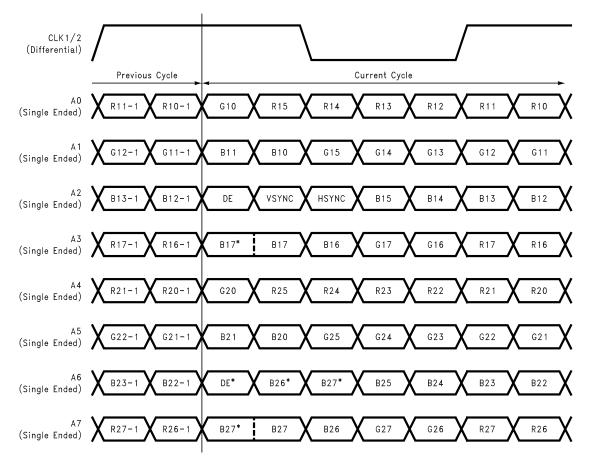

NOTE: Redundant copies of certain signals are also sent. These signals are denoted with an \* symbol. The DS90CF388 does not sample the bits show with an \* symbol. Optional feature supported: Pre-emphasis. See Applications Information for additional details.

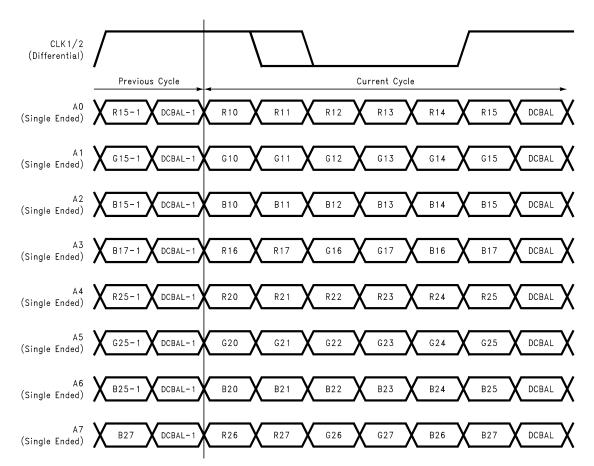

Figure 17. TTL Data Inputs Mapped to LVDS Outputs Non-DC Balanced Mode (Backward Compatible, BAL=Low)

SNLS012H-MAY 2000-REVISED APRIL 2013

NOTE: The LVDS Clock signal is also DC Balanced in this mode. The rising edge location is fixed, but the location of the falling edge will be in one of two locations as shown above. Optional features supported: Pre-emphasis, and Deskew.

Figure 18. 48 Parallel TTL Data Inputs Mapped to LVDS Outputs DC Balanced Mode - Data Enabled, BAL=High

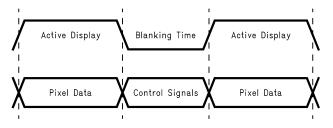

Figure 19. Control Signals Transmitted During Blanking

| SNLS012H-MA | / 2000- |  | 2013 |

|-------------|---------|--|------|

|             | 2000-   |  | 2010 |

| Control Signal | Signal<br>Level | Channel  | Pattern                  |

|----------------|-----------------|----------|--------------------------|

| DE             | HIGH            | TxCLKOUT | 1111000<br>or<br>1110000 |

|                | LOW             |          | 1111100<br>or<br>1100000 |

| HSYNC          | HIGH            | τχουτο   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

| VSYNC          | HIGH            | TXOUT1   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

| CNTLF          | HIGH            | TXOUT4   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

| CNTLE          | HIGH            | TXOUT5   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

NOTE: The control signal during blanking shown above is for R\_FDE=High, when R\_FDE=Low all the low/high patterns are reversed.

Figure 20. Control Signals Transmitted During Blanking

SNLS012H - MAY 2000 - REVISED APRIL 2013

# **APPLICATIONS INFORMATION**

# HOW TO CONFIGURE THE DS90C387 AND DS90CF388 FOR MOST COMMON APPLICATION

- 1. To configure for single input pixel-to-dual pixel output application, the DS90C387 "DUAL" pin must be set to 1/2 Vcc=1.65V. This may be implemented using pull-up and pull-down resistors of 10kΩ each as shown in Figure 16. A capacitor between "DUAL" pin and ground will help to stabilize the DC voltage level in a noisy environment. In this configuration, the input signals (single pixel) are split into odd and even pixel (dual pixels) starting with the odd (first) pixel outputs A0-to-A3 the next even (second) pixel outputs to A4-to-A7. The splitting of the data signal also starts with DE (data enable) transitioning from logic low to high indicating active data. The "R\_FDE" pin must be set high in this case. This is supported in DC Balanced and non-DC Balanced (BAL=low or high) data transmission. The number of clock cycles during blanking must be an EVEN number. This configuration will allow the user to interface to an LDI receiver (DS90CF384A). The DC Balance feature is recommended for monitor applications which require >2meters of cable length. Notebook applications should disable this feature to reduce the current consumption of the chipset. Note that only the DS90C387/DS90CF388 support the DC Balance data transmission feature.

- 2. To configure for single pixel or dual pixel application using the DS90C387/DS90CF388, the "DUAL" pin must be set to Vcc (dual) or Gnd (single). In dual mode, the transmitter-DS90C387 has two LVDS clock outputs enabling an interface to two FPD-Link 'notebook' receivers (DS90CF384A or DS90CF386). In single mode, outputs A4-to-A7 and CLK2 are disabled which reduces power dissipation. Both single and dual mode also support the DC Balance data transmission feature, which should only be used for monitor application.

- 3. The DS90CF388 is able to support single or dual pixel interface up to 112MHz operating frequency. This receiver may also be used to interface to a VGA controller with an integrated LVDS transmitter without DC Balance data transmission. In this case, the receivers "BAL" pin must be tied low (DC Balance disabled).

## **NEW FEATURES DESCRIPTION**

### **Pre-Emphasis**

Adds extra current during LVDS logic transition to reduce the cable loading effects. Pre-emphasis strength is set via a DC voltage level applied from min to max (0.75V to Vcc) at the "PRE" pin. A higher input voltage on the "PRE" pin increases the magnitude of dynamic current during data transition. The "PRE" pin requires one pull-up resistor (Rpre) to Vcc in order to set the DC level. There is an internal resistor network, which cause a voltage drop. See Table 5 and Table 6 to set the voltage level.