Order

Now

LF198-N, LF298, LF398-N LF198A-N, LF398A-N

ZHCSIW2C-JULY 2000-REVISED OCTOBER 2018

# LFx98x 单片采样保持电路

Technical

Documents

## 1 特性

- 通过 **±5**V 至 **±18**V 的电源工作

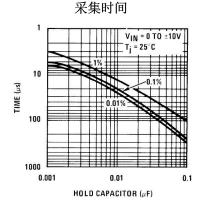

- 采集时间少于 10µs

- 逻辑输入与 TTL、PMOS、CMOS 兼容

- 在 Ch = 0.01µF 时保持步进为 0.5mV (典型值)

- 低输入偏移

- 增益精度为 0.002%

- 在保持模式下,输出噪声较低

- 在保持模式期间,输入特点不变

- 在采样或保持模式中,电源抑制比高

- 宽带宽

- 符合太空要求,符合 JM38510

## 2 应用

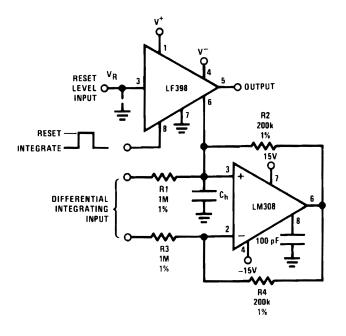

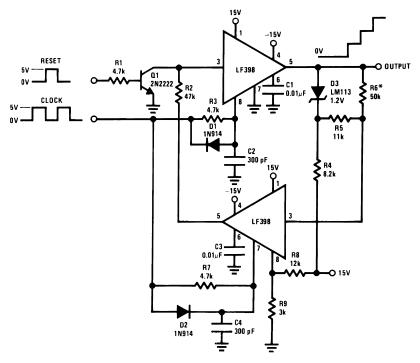

- 具有可变复位电平的斜坡发生器

- 具有可编程复位电平的积分器

- 同步相关器

- 双通道开关

- 直流和交流归零

- 阶梯生成器

# 3 说明

🥭 Tools &

Software

LFx98x 器件是采用 BI-FET 技术的单片采样保持电路,利用快速采集信号和低下降率获得超高的直流精度。作为单位增益跟随器,直流增益精度为 0.002% (典型值),采集时间低至 6μs (0.01%)。采用双极输入级以实现低偏移电压和宽带宽。输入偏移调整是通过 单个引脚完成的,不会降低输入偏移漂移。宽带宽允许 将 LFx98x 包含在 1MHz 运算放大器的反馈环路内, 而不会出现稳定性问题。输入阻抗为 10<sup>10</sup>Ω,允许使用 高源阻抗,而不会降低精度。

Support &

Community

22

P 通道结型 FET 与输出放大器中的双极器件相结合, 通过 1μF 保持电容器提供低至 5mV/min 的下降率。 JFET 的噪声显著低于先前设计中使用的 MOS 器件, 并且不会出现高温不稳定性。总体设计可确保在保持模 式下没有输入到输出的馈通,即使输入信号等于电源电 压。

LFx98x 上的逻辑输入与低输入电流完全不同,允许直接连接到 TTL、PMOS 和 CMOS。差分阈值为 1.4V。LFx98x 由 ±5V 至 ±18V 的电源供电。

A 版本可提供更严格的电气规格。

器件信息<sup>(1)</sup>

| 器件编号          | 封装        | 封装尺寸(标称值)       |  |  |  |  |

|---------------|-----------|-----------------|--|--|--|--|

| LF298、LF398-N | SOIC (14) | 8.65mm × 3.91mm |  |  |  |  |

| LFx98x        | TO-99 (8) | 9.08mm × 9.08mm |  |  |  |  |

| LF398-N       | PDIP (8)  | 9.81mm × 6.35mm |  |  |  |  |

(1)如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

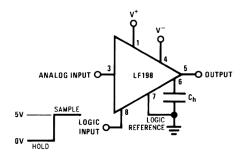

典型连接

h牛 hH

ZHCSIW2C-JULY 2000-REVISED OCTOBER 2018

# 目录

8.3

8.4

12.1

12.4 12.5

9

|   | 可口                                |                                                     |  |  |  |  |  |  |

|---|-----------------------------------|-----------------------------------------------------|--|--|--|--|--|--|

| 2 | 应用                                | 1                                                   |  |  |  |  |  |  |

| 3 | 说明                                | 1                                                   |  |  |  |  |  |  |

| 4 | 修订                                | 历史记录                                                |  |  |  |  |  |  |

| 5 | Pin Configuration and Functions 3 |                                                     |  |  |  |  |  |  |

| 6 | Spe                               | cifications                                         |  |  |  |  |  |  |

|   | 6.1                               | Absolute Maximum Ratings 4                          |  |  |  |  |  |  |

|   | 6.2                               | Recommended Operating Conditions 4                  |  |  |  |  |  |  |

|   | 6.3                               | Thermal Information 4                               |  |  |  |  |  |  |

|   | 6.4                               | Electrical Characteristics, LF198-N and LF298 5     |  |  |  |  |  |  |

|   | 6.5                               | Electrical Characteristics, LF198A-N 6              |  |  |  |  |  |  |

|   | 6.6                               | Electrical Characteristics, LF398-N7                |  |  |  |  |  |  |

|   | 6.7                               | Electrical Characteristics, LF398A-N (OBSOLETE) . 8 |  |  |  |  |  |  |

|   | 6.8                               | Typical Characteristics 9                           |  |  |  |  |  |  |

| 7 | Para                              | ameter Measurement Information 12                   |  |  |  |  |  |  |

|   | 7.1                               | TTL and CMOS 3 V ≤ $V_{LOGIC}$ (Hi State) ≤ 7 V 12  |  |  |  |  |  |  |

|   | 7.2                               | CMOS 7 V ≤ V <sub>LOGIC</sub> (Hi State) ≤ 15 V 12  |  |  |  |  |  |  |

|   | 7.3                               | Operational Amplifier Drive 13                      |  |  |  |  |  |  |

| 8 | Deta                              | ailed Description 14                                |  |  |  |  |  |  |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Cł | hanges from Revision B (October 2015) to Revision C                                                                         | Page |

|----|-----------------------------------------------------------------------------------------------------------------------------|------|

| •  | 更新了"器件信息"和"引脚功能"表                                                                                                           | 1    |

| •  | Separated <i>Electrical Characteristics</i> into four tables: LF198-N and LF298; LF198A-N; LF398-N; and LF398A-N (OBSOLETE) | 5    |

#### Changes from Revision A (July 2000) to Revision B

已添加 ESD 额定值表、热性能信息表、特性 说明部分、器件功能模式、应用和实施部分、电源建议部分、布局部 分、器件和文档支持部分以及机械、封装和可订购信息部分 ......1

2

EXAS STRUMENTS

8.1 Overview ...... 14 8.2 Functional Block Diagram ..... 14 Feature Description......14

Application and Implementation ...... 15

9.2 Typical Applications ..... 17 11 Layout...... 27 11.1 Layout Guidelines ...... 27 11.2 Layout Example ...... 27 12 器件和文档支持 ...... 28

Device Functional Modes......14

13 机械、封装和可订购信息...... 28

12.2 相关链接...... 28 12.3 社区资源...... 28

www.ti.com.cn

Page

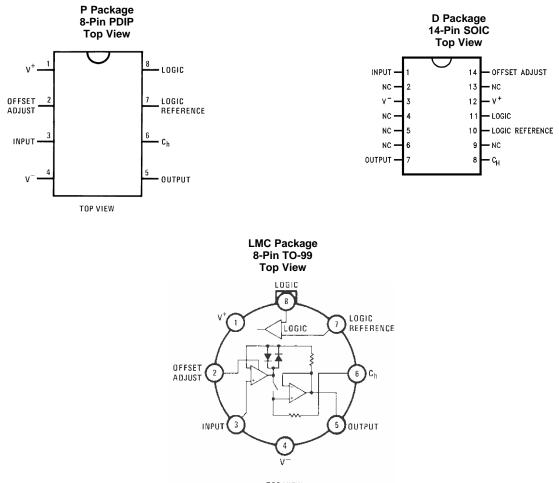

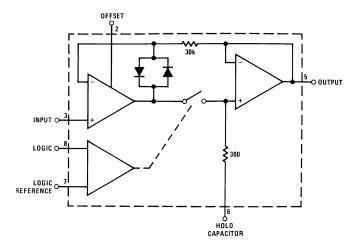

## 5 Pin Configuration and Functions

TOP VIEW

A military RETS electrical test specification is available on request. The LF198-N may also be procured to Standard Military Drawing #5962-8760801GA or to MIL-STD-38510 part ID JM38510/12501SGA.

#### **Pin Functions**

|                 | PIN               |        |         |                     |                                       |

|-----------------|-------------------|--------|---------|---------------------|---------------------------------------|

| NAME            | LF298, LF398-N    | LFx98x | LF398-N | TYPE <sup>(1)</sup> | DESCRIPTION                           |

| NAME            | SOIC-14           | TO-99  | PDIP-8  |                     |                                       |

| V+              | 12                | 1      | 1       | Р                   | Positive supply                       |

| OFFSET ADJUST   | 14                | 2      | 2       | А                   | DC offset compensation pin            |

| INPUT           | 1                 | 3      | 3       | А                   | Analog Input                          |

| V <sup>-</sup>  | 3                 | 4      | 4       | Р                   | Negative supply                       |

| OUTPUT          | 7                 | 5      | 5       | 0                   | Output                                |

| C <sub>h</sub>  | 8                 | 6      | 6       | А                   | Hold capacitor                        |

| LOGIC REFERENCE | 10                | 7      | 7       | I                   | Reference for LOGIC input             |

| LOGIC           | 11                | 8      | 8       | I                   | Logic input for Sample and Hold modes |

| NC              | 2, 4, 5, 6, 9, 13 | _      | _       | NA                  | No connect                            |

(1) P = Power, G = Ground, I = Input, O = Output, A = Analog

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                             |                                           | MIN  | MAX    | UNIT |

|---------------------------------------------|-------------------------------------------|------|--------|------|

| Supply voltage                              |                                           |      | ±18    | V    |

| Power dissipation                           | (Package limitation, see <sup>(3)</sup> ) |      | 500    | mW   |

|                                             | LF198-N, LF198A-N                         | -55  | 125    | °C   |

| Operating ambient temperature               | LF298                                     | -25  | 85     | °C   |

|                                             | LF398-N, LF398A-N                         | 0    | 70     | °C   |

| Input voltage                               |                                           |      | ±18    | V    |

| Logic-to-logic reference differential volta | ge (see <sup>(4)</sup> )                  | 7    | -30    | V    |

| Output short circuit duration               |                                           | Inde | finite |      |

| Hold capacitor short circuit duration       |                                           |      | 10     | sec  |

|                                             | H package (soldering, 10 sec.)            |      | 260    | °C   |

|                                             | N package (soldering, 10 sec.)            |      | 260    | °C   |

| Lead temperature                            | M package: vapor phase (60 sec.)          |      | 215    | °C   |

|                                             | Infrared (15 sec.)                        |      | 220    | °C   |

| Storage temperature, T <sub>stq</sub>       | · · ·                                     | -65  | 150    | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

(3) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, R<sub>θJA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any temperature is P<sub>D</sub> = (T<sub>JMAX</sub> - T<sub>A</sub>) / R<sub>θJA</sub>, or the number given in the Absolute Maximum Ratings, whichever is lower. The maximum junction temperature, T<sub>JMAX</sub>, for the LF198-N and LF198A-N is 150°C; for the LF298, 115°C; and for the LF398-N and LF398A-N, 100°C.

(4) Although the differential voltage may not exceed the limits given, the common-mode voltage on the logic pins may be equal to the supply voltages without causing damage to the circuit. For proper logic operation, however, one of the logic pins must always be at least 2 V below the positive supply and 3 V above the negative supply.

## 6.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|       |                     |                   | MIN | NOM MAX | UNIT |

|-------|---------------------|-------------------|-----|---------|------|

|       | Supply voltage      |                   |     | ±15     | V    |

|       |                     | LF198-N, LF198A-N | -55 | 125     |      |

| $T_J$ | Ambient temperature | LF298             | -25 | 85      | °C   |

|       |                     | LF398-N, LF398A-N | 0   | 70      |      |

#### 6.3 Thermal Information

|                       |                                              | LF398-N  | LF298, LF398-N | LFx98x            |      |

|-----------------------|----------------------------------------------|----------|----------------|-------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | P (PDIP) | D (SOIC)       | LMC (TO-99)       | UNIT |

|                       |                                              | 8 PINS   | 14 PINS        | 8 PINS            |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 48.9     | 80.6           | 85 <sup>(2)</sup> | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 37.3     | 38.1           | 20                | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 26.2     | 35.4           | —                 | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 14.3     | 5.8            | —                 | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 26.0     | 35.1           | _                 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) Board mount in 400 LF/min air flow.

## 6.4 Electrical Characteristics, LF198-N and LF298

The following specifications apply for  $-V_S + 3.5 \text{ V} \le V_{IN} \le +V_S - 3.5 \text{ V}$ ,  $+V_S = +15 \text{ V}$ ,  $-V_S = -15 \text{ V}$ ,  $T_A = T_J = 25^{\circ}\text{C}$ ,  $C_h = 0.01 \text{ }\mu\text{F}$ ,  $R_L = 10 \text{ }k\Omega$ , LOGIC REFERENCE = 0 V, LOGIC HIGH = 2.5 V, LOGIC LOW = 0 V unless otherwise specified.

| PARAMETER                                          | TEST CONDITIONS                                                          | MIN | TYP    | MAX    | UNIT |

|----------------------------------------------------|--------------------------------------------------------------------------|-----|--------|--------|------|

| 1                                                  | $T_J = 25^{\circ}C$                                                      |     | 1      | 3      | mV   |

| Input offset voltage <sup>(1)</sup>                | Full temperature range                                                   |     |        | 5      | mV   |

| Input bias current <sup>(1)</sup>                  | $T_J = 25^{\circ}C$                                                      |     | 5      | 25     | nA   |

| input bias current ?                               | Full temperature range                                                   |     |        | 75     | nA   |

| Input impedance                                    | $T_J = 25^{\circ}C$                                                      |     | 10     |        | GΩ   |

| Coin anna                                          | $T_{\rm J} = 25^{\circ} {\rm C}, \ {\rm R_L} = 10 \ {\rm k}$             |     | 0.002% | 0.005% |      |

| Gain error                                         | Full temperature range                                                   |     |        | 0.02%  |      |

| Feedthrough attenuation ratio at 1 kHz             | $T_{\rm J} = 25^{\circ} {\rm C}, \ {\rm C}_{\rm h} = 0.01 \ \mu {\rm F}$ | 86  | 96     |        | dB   |

| O traditional datas                                | $T_J = 25^{\circ}C$ , "HOLD" mode                                        |     | 0.5    | 2      | Ω    |

| Output impedance                                   | Full temperature range                                                   |     |        | 4      | Ω    |

| HOLD step <sup>(2)</sup>                           | $T_J = 25^{\circ}C, C_h = 0.01 \ \mu F, V_{OUT} = 0$                     |     | 0.5    | 2      | mV   |

| Supply current <sup>(1)</sup>                      | T <sub>J</sub> ≥ 25°C                                                    |     | 4.5    | 5.5    | mA   |

| Logic and logic reference input current            | $T_J = 25^{\circ}C$                                                      |     | 2      | 10     | μA   |

| Leakage current into hold capacitor <sup>(1)</sup> | $T_J = 25^{\circ}C$ , hold mode <sup>(3)</sup>                           |     | 30     | 100    | pА   |

|                                                    | $\Delta V_{OUT} = 10 \text{ V}, \text{ C}_{h} = 1000 \text{ pF}$         |     | 4      |        | μs   |

| Acquisition time to 0.1%                           | C <sub>H</sub> = 0.01 μF                                                 |     | 20     |        | μs   |

| Hold capacitor charging current                    | $V_{IN} - V_{OUT} = 2 V$                                                 |     | 5      |        | mA   |

| Supply voltage rejection ratio                     | $V_{OUT} = 0$                                                            | 80  | 110    |        | dB   |

| Differential logic threshold                       | T <sub>J</sub> = 25°C                                                    | 0.8 | 1.4    | 2.4    | V    |

(1) These parameters ensured over a supply voltage range of ±5 to ±18 V, and an input range of  $-V_S$  + 3.5 V  $\leq V_{IN} \leq +V_S - 3.5$  V.

(2) Hold step is sensitive to stray capacitive coupling between input logic signals and the hold capacitor. 1 pF, for instance, will create an additional 0.5-mV step with a 5-V logic swing and a 0.01-µF hold capacitor. Magnitude of the hold step is inversely proportional to hold capacitor value.

## 6.5 Electrical Characteristics, LF198A-N

The following specifications apply for  $-V_S + 3.5 \text{ V} \le V_{IN} \le +V_S - 3.5 \text{ V}$ ,  $+V_S = +15 \text{ V}$ ,  $-V_S = -15 \text{ V}$ ,  $T_A = T_J = 25^{\circ}\text{C}$ ,  $C_h = 0.01 \text{ }\mu\text{F}$ ,  $R_L = 10 \text{ }k\Omega$ , LOGIC REFERENCE = 0 V, LOGIC HIGH = 2.5 V, LOGIC LOW = 0 V unless otherwise specified.

| PARAMETER                                          | TEST CONDITIONS                                                          | MIN | TYP    | MAX    | UNIT |

|----------------------------------------------------|--------------------------------------------------------------------------|-----|--------|--------|------|

| 1                                                  | $T_J = 25^{\circ}C$                                                      |     | 1      | 1      | mV   |

| Input offset voltage <sup>(1)</sup>                | Full temperature range                                                   |     |        | 2      | mV   |

| Input biog surrent <sup>(1)</sup>                  | $T_J = 25^{\circ}C$                                                      |     | 5      | 25     | nA   |

| Input bias current <sup>(1)</sup>                  | Full temperature range                                                   |     |        | 75     | nA   |

| Input impedance                                    | $T_J = 25^{\circ}C$                                                      |     | 10     |        | GΩ   |

|                                                    | $T_{\rm J} = 25^{\circ} {\rm C}, \ {\rm R_L} = 10 \ {\rm k}$             |     | 0.002% | 0.005% |      |

| Gain error                                         | Full temperature range                                                   |     |        | 0.01%  |      |

| Feedthrough attenuation ratio at 1 kHz             | $T_{\rm J} = 25^{\circ} {\rm C}, \ {\rm C}_{\rm h} = 0.01 \ \mu {\rm F}$ | 86  | 96     |        | dB   |

|                                                    | $T_J = 25^{\circ}C$ , "HOLD" mode                                        |     | 0.5    | 1      | Ω    |

| Output impedance                                   | Full temperature range                                                   |     |        | 4      | Ω    |

| HOLD step <sup>(2)</sup>                           | $T_J = 25^{\circ}C, C_h = 0.01 \ \mu F, V_{OUT} = 0$                     |     | 0.5    | 1      | mV   |

| Supply current <sup>(1)</sup>                      | T <sub>J</sub> ≥ 25°C                                                    |     | 4.5    | 5.5    | mA   |

| Logic and logic reference input current            | $T_J = 25^{\circ}C$                                                      |     | 2      | 10     | μA   |

| Leakage current into hold capacitor <sup>(1)</sup> | $T_J = 25^{\circ}C$ , hold mode <sup>(3)</sup>                           |     | 30     | 100    | pА   |

| Accuration time to 0.40/                           | $\Delta V_{OUT} = 10 \text{ V}, \text{ C}_{h} = 1000 \text{ pF}$         |     | 4      | 6      | μs   |

| Acquisition time to 0.1%                           | C <sub>H</sub> = 0.01 μF                                                 |     | 20     | 25     | μs   |

| Hold capacitor charging current                    | $V_{IN} - V_{OUT} = 2 V$                                                 |     | 5      |        | mA   |

| Supply voltage rejection ratio                     | V <sub>OUT</sub> = 0                                                     | 90  | 110    |        | dB   |

| Differential logic threshold                       | T <sub>J</sub> = 25°C                                                    | 0.8 | 1.4    | 2.4    | V    |

(1) These parameters ensured over a supply voltage range of ±5 to ±18 V, and an input range of  $-V_S$  + 3.5 V  $\leq V_{IN} \leq +V_S - 3.5$  V.

(2) Hold step is sensitive to stray capacitive coupling between input logic signals and the hold capacitor. 1 pF, for instance, will create an additional 0.5-mV step with a 5-V logic swing and a 0.01-µF hold capacitor. Magnitude of the hold step is inversely proportional to hold capacitor value.

#### 6.6 Electrical Characteristics, LF398-N

The following specifications apply for  $-V_S + 3.5 \text{ V} \le V_{IN} \le +V_S - 3.5 \text{ V}$ ,  $+V_S = +15 \text{ V}$ ,  $-V_S = -15 \text{ V}$ ,  $T_A = T_J = 25^{\circ}\text{C}$ ,  $C_h = 0.01 \text{ }\mu\text{F}$ ,  $R_L = 10 \text{ }k\Omega$ , LOGIC REFERENCE = 0 V, LOGIC HIGH = 2.5 V, LOGIC LOW = 0 V unless otherwise specified.

| PARAMETER                                          | TEST CONDITIONS                                      | MIN | TYP    | MAX   | UNIT |

|----------------------------------------------------|------------------------------------------------------|-----|--------|-------|------|

| 1                                                  | $T_J = 25^{\circ}C$                                  |     | 2      | 7     | mV   |

| Input offset voltage <sup>(1)</sup>                | Full temperature range                               |     |        | 10    | mV   |

| Input bias current <sup>(1)</sup>                  | $T_J = 25^{\circ}C$                                  |     | 10     | 50    | nA   |

| input bias current ?                               | Full temperature range                               |     |        | 100   | nA   |

| Input impedance                                    | $T_J = 25^{\circ}C$                                  |     | 10     |       | GΩ   |

| Colin annua                                        | $T_{\rm J} = 25^{\circ}$ C, $R_{\rm L} = 10$ k       |     | 0.004% | 0.01% |      |

| Gain error                                         | Full temperature range                               |     |        | 0.02% |      |

| Feedthrough attenuation ratio at 1 kHz             | $T_J = 25^{\circ}C, C_h = 0.01 \ \mu F$              | 80  | 90     |       | dB   |

|                                                    | $T_J = 25^{\circ}C$ , "HOLD" mode                    |     | 0.5    | 4     | Ω    |

| Output impedance                                   | Full temperature range                               |     |        | 6     | Ω    |

| HOLD step <sup>(2)</sup>                           | $T_J = 25^{\circ}C, C_h = 0.01 \ \mu F, V_{OUT} = 0$ |     | 1      | 2.5   | mV   |

| Supply current <sup>(1)</sup>                      | T <sub>J</sub> ≥ 25°C                                |     | 4.5    | 6.5   | mA   |

| Logic and logic reference input current            | $T_J = 25^{\circ}C$                                  |     | 2      | 10    | μA   |

| Leakage current into hold capacitor <sup>(1)</sup> | $T_J = 25^{\circ}C$ , hold mode <sup>(3)</sup>       |     | 30     | 200   | pА   |

| Acquisition time to 0.19/                          | $\Delta V_{OUT}$ = 10 V, C <sub>h</sub> = 1000 pF    |     | 4      |       | μs   |

| Acquisition time to 0.1%                           | C <sub>H</sub> = 0.01 μF                             |     | 20     |       | μs   |

| Hold capacitor charging current                    | $V_{IN} - V_{OUT} = 2 V$                             |     | 5      |       | mA   |

| Supply voltage rejection ratio                     | V <sub>OUT</sub> = 0                                 | 80  | 110    |       | dB   |

| Differential logic threshold                       | $T_J = 25^{\circ}C$                                  | 0.8 | 1.4    | 2.4   | V    |

(1) These parameters ensured over a supply voltage range of ±5 to ±18 V, and an input range of  $-V_S$  + 3.5 V  $\leq V_{IN} \leq +V_S - 3.5$  V.

(2) Hold step is sensitive to stray capacitive coupling between input logic signals and the hold capacitor. 1 pF, for instance, will create an additional 0.5-mV step with a 5-V logic swing and a 0.01-µF hold capacitor. Magnitude of the hold step is inversely proportional to hold capacitor value.

## 6.7 Electrical Characteristics, LF398A-N (OBSOLETE)

The following specifications apply for  $-V_S + 3.5 \text{ V} \le V_{IN} \le +V_S - 3.5 \text{ V}$ ,  $+V_S = +15 \text{ V}$ ,  $-V_S = -15 \text{ V}$ ,  $T_A = T_J = 25^{\circ}\text{C}$ ,  $C_h = 0.01 \mu\text{F}$ ,  $R_L = 10 \text{ k}\Omega$ , LOGIC REFERENCE = 0 V, LOGIC HIGH = 2.5 V, LOGIC LOW = 0 V unless otherwise specified.

| PARAMETER                                          | TEST CONDITIONS                                                  | MIN | TYP    | MAX    | UNIT |

|----------------------------------------------------|------------------------------------------------------------------|-----|--------|--------|------|

| lanut affa at valta as (1)                         | $T_J = 25^{\circ}C$                                              |     | 2      | 2      | mV   |

| Input offset voltage <sup>(1)</sup>                | Full temperature range                                           |     |        | 3      | mV   |

| Input bias current <sup>(1)</sup>                  | $T_J = 25^{\circ}C$                                              |     | 10     | 25     | nA   |

| Input bias current '                               | Full temperature range                                           |     |        | 50     | nA   |

| Input impedance                                    | $T_J = 25^{\circ}C$                                              |     | 10     |        | GΩ   |

|                                                    | $T_J = 25^{\circ}C, R_L = 10 \text{ k}$                          |     | 0.004% | 0.005% |      |

| Gain error                                         | Full temperature range                                           |     |        | 0.01%  |      |

| Feedthrough attenuation ratio at 1 kHz             | $T_J = 25^{\circ}C, C_h = 0.01 \ \mu F$                          | 86  | 90     |        | dB   |

|                                                    | T <sub>J</sub> = 25°C, "HOLD" mode                               |     | 0.5    | 1      | Ω    |

| Output impedance                                   | Full temperature range                                           |     |        | 6      | Ω    |

| HOLD step <sup>(2)</sup>                           | $T_J = 25^{\circ}C, C_h = 0.01 \ \mu F, V_{OUT} = 0$             |     | 1      | 1      | mV   |

| Supply current <sup>(1)</sup>                      | T <sub>J</sub> ≥ 25°C                                            |     | 4.5    | 6.5    | mA   |

| Logic and logic reference input current            | $T_J = 25^{\circ}C$                                              |     | 2      | 10     | μA   |

| Leakage current into hold capacitor <sup>(1)</sup> | $T_J = 25^{\circ}C$ , hold mode <sup>(3)</sup>                   |     | 30     | 100    | pА   |

| Acquisition time to 0.19/                          | $\Delta V_{OUT} = 10 \text{ V}, \text{ C}_{h} = 1000 \text{ pF}$ |     | 4      | 6      | μs   |

| Acquisition time to 0.1%                           | C <sub>H</sub> = 0.01 μF                                         |     | 20     | 25     | μs   |

| Hold capacitor charging current                    | $V_{IN} - V_{OUT} = 2 V$                                         |     | 5      |        | mA   |

| Supply voltage rejection ratio                     | $V_{OUT} = 0$                                                    | 90  | 110    |        | dB   |

| Differential logic threshold                       | $T_J = 25^{\circ}C$                                              | 0.8 | 1.4    | 2.4    | V    |

(1) These parameters ensured over a supply voltage range of ±5 to ±18 V, and an input range of  $-V_S + 3.5 V \le V_{IN} \le +V_S - 3.5 V$ .

(2) Hold step is sensitive to stray capacitive coupling between input logic signals and the hold capacitor. 1 pF, for instance, will create an additional 0.5-mV step with a 5-V logic swing and a 0.01-µF hold capacitor. Magnitude of the hold step is inversely proportional to hold capacitor value.

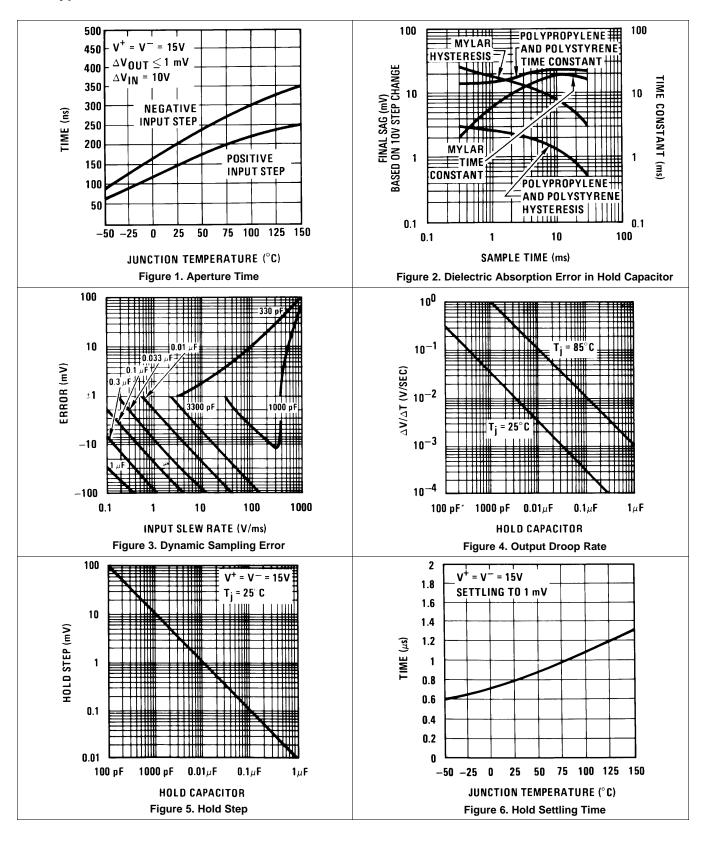

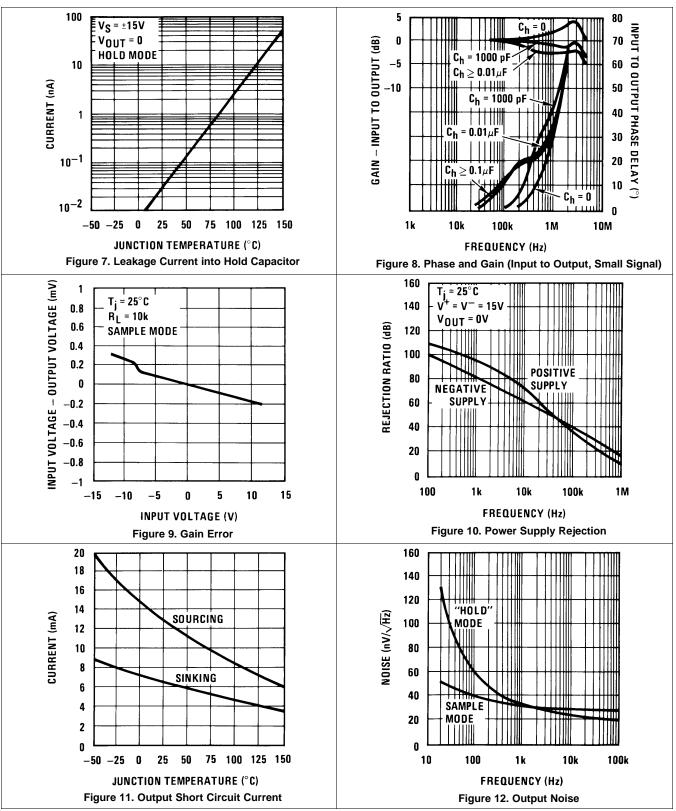

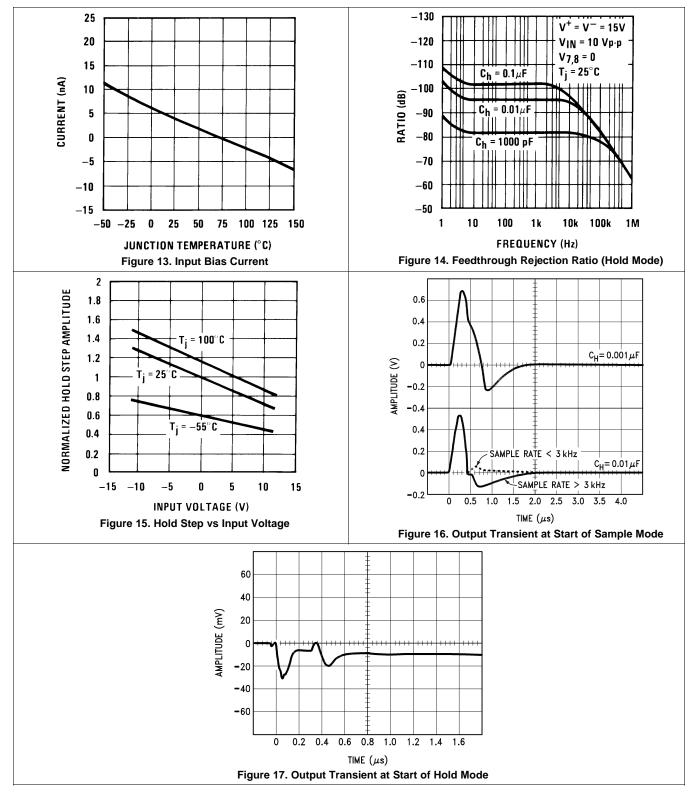

## 6.8 Typical Characteristics

## **Typical Characteristics (continued)**

www.ti.com.cn

#### **Typical Characteristics (continued)**

## 7 Parameter Measurement Information

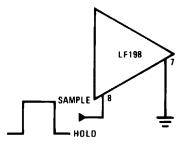

## 7.1 TTL and CMOS 3 V $\leq$ V<sub>LOGIC</sub> (Hi State) $\leq$ 7 V

Threshold = 1.4 V

#### Figure 18. Sample When Logic High With TTL and CMOS Biasing

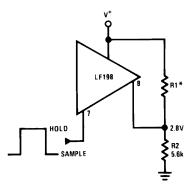

Threshold = 1.4 V Select for 2.8 V at pin 8

#### Figure 19. Sample When Logic Low With TTL and CMOS Biasing

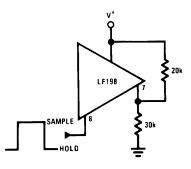

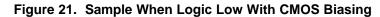

## 7.2 CMOS 7 V $\leq$ V<sub>LOGIC</sub> (Hi State) $\leq$ 15 V

Threshold =  $0.6 (V^+) + 1.4 V$

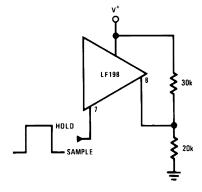

# CMOS 7 V $\leq$ V<sub>LOGIC</sub> (Hi State) $\leq$ 15 V (continued)

Threshold =  $0.6 (V^{+}) - 1.4V$

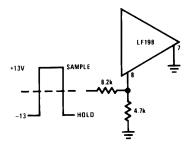

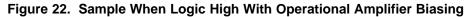

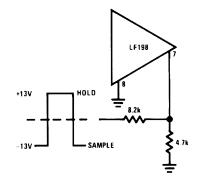

#### 7.3 Operational Amplifier Drive

Threshold ≈ +4 V

Threshold = -4 V

Figure 23. Sample When Logic Low With Operational Amplifier Biasing

## 8 Detailed Description

#### 8.1 Overview

The LFx98x devices are monolithic sample-and-hold circuits that utilize BI-FET technology to obtain ultrahigh DC accuracy with fast acquisition of signal and low droop rate. Operating as a unity-gain follower, DC gain accuracy is 0.002% typical and acquisition time is as low as 6  $\mu$ s to 0.01%. A bipolar input stage is used to achieve low offset voltage and wide bandwidth. Input offset adjust is accomplished with a single pin, and does not degrade input offset drift. The wide bandwidth allows the LF198-N to be included inside the feedback loop of 1-MHz operational amplifier without having stability problems. Input impedance of 10<sup>10</sup>  $\Omega$  allows high-source impedances to be used without degrading accuracy.

## 8.2 Functional Block Diagram

## 8.3 Feature Description

The LFx98x OUTPUT tracks the INPUT signal by charging and discharging the hold capacitor. The OUTPUT can be held at any given time by pulling the LOGIC input low relative to the LOGIC REFERENCE voltage and resume sampling when LOGIC returns high. Additionally, the OFFSET pin can be used to zero the offset voltage present at the INPUT.

#### 8.4 Device Functional Modes

The LFx98x devices have a *sample* mode and *hold* mode controlled by the LOGIC voltage relative to the LOGIC REFERENCE voltage. The device is in *sample* mode when the LOGIC input is pulled high relative to the LOGIC REFERENCE voltage and in *hold* mode when the LOGIC input is pulled low relative to the LOGIC REFERENCE. In *sample* mode, the output is tracking the input signal by charging and discharging the hold capacitor. Smaller values of hold capacitance will allow the output to track faster signals. In *hold* mode the input signal is disconnected from the signal path and the output retains the value on the hold capacitor. Larger values of capacitance will have a smaller droop rate as shown in Figure 4.

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

#### 9.1.1 Hold Capacitor

Hold step, acquisition time, and droop rate are the major trade-offs in the selection of a hold capacitor value. Size and cost may also become important for larger values. Use of the curves included with this data sheet should be helpful in selecting a reasonable value of capacitance. Keep in mind that for fast repetition rates or tracking fast signals, the capacitor drive currents may cause a significant temperature rise in the LF198-N.

A significant source of error in an accurate sample and hold circuit is dielectric absorption in the hold capacitor. A mylar cap, for instance, may *sag back* up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica and polycarbonate are not nearly as good. The advantage of polypropylene over polystyrene is that it extends the maximum ambient temperature from 85°C to 100°C. Most ceramic capacitors are unusable with > 1% hysteresis. Ceramic NPO or COG capacitors are now available for 125°C operation and also have low dielectric absorption. For more exact data, see Figure 2. The hysteresis numbers on the curve are final values, taken after full relaxation. The hysteresis error can be significantly reduced if the output of the LF198-N is digitized quickly after the hold mode is initiated. The hysteresis relaxation time constant in polypropylene, for instance, is 10 to 50 ms. If A-to-D conversion can be made within 1 ms, hysteresis error will be reduced by a factor of ten.

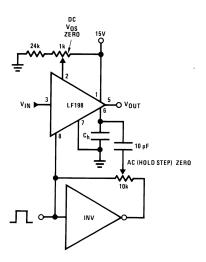

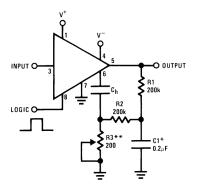

#### 9.1.2 DC and AC Zeroing

DC zeroing is accomplished by connecting the offset adjust pin to the wiper of a 1-k $\Omega$  potentiometer, which has one end tied to V+ and the other end tied through a resistor to ground. The resistor should be selected to give approximately 0.6 mA through the 1-k $\Omega$  potentiometer.

AC zeroing (hold step zeroing) can be obtained by adding an inverter with the adjustment pot tied input to output. A 10-pF capacitor from the wiper to the hold capacitor will give  $\pm$ 4-mV hold step adjustment with a 0.01-µF hold capacitor and 5-V logic supply. For larger logic swings, a smaller capacitor (< 10 pF) may be used.

#### 9.1.3 Logic Rise Time

For proper operation, logic signals into the LF198-N must have a minimum dV/dt of 1.0 V/ $\mu$ s. Slower signals will cause excessive hold step. If a R/C network is used in front of the logic input for signal delay, calculate the slope of the waveform at the threshold point to ensure that it is at least 1.0 V/ $\mu$ s.

#### 9.1.4 Sampling Dynamic Signals

Sample error to moving input signals probably causes more confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actuality, there are finite phase delays through the circuit creating an input-output differential for fast moving signals. In addition, although the output may have settled, the hold capacitor has an additional lag due to the  $300-\Omega$  series resistor on the chip. This means that at the moment the *hold* command arrives, the hold capacitor voltage may be somewhat different than the actual analog input. The effect of these delays is opposite to the effect created by delays in the logic which switches the circuit from sample to hold. For example, consider an analog input of 20 Vp-p at 10 kHz. Maximum dV/dt is 0.6 V/µs. With no analog phase delay and 100-ns logic delay, one could expect up to (0.1 µs) (0.6V/µs) = 60 mVerror if the hold signal arrived near maximum dV/dt of the input. A positive-going input would give a

#### **Application Information (continued)**

60-mV error. Now assume a 1-MHz (3-dB) bandwidth for the overall analog loop. This generates a phase delay of 160 ns. If the hold capacitor sees this exact delay, then error due to analog delay will be (0.16  $\mu$ s) (0.6 V/ $\mu$ s) = -96 mV. Total output error is 60 mV (digital) -96 mV (analog) for a total of -36 mV. To add to the confusion, analog delay is proportioned to hold capacitor value while digital delay remains constant. A family of curves (dynamic sampling error) is included to help estimate errors.

Figure 1 has been included for sampling conditions where the input is steady during the sampling period, but may experience a sudden change nearly coincident with the hold command. This curve is based on a 1-mV error fed into the output.

Figure 6 indicates the time required for the output to settle to 1 mV after the hold command.

#### 9.1.5 Digital Feedthrough

Fast rise time logic signals can cause hold errors by feeding externally into the analog input at the same time the amplifier is put into the hold mode. To minimize this problem, board layout should keep logic lines as far as possible from the analog input and the  $C_h$  pin. Grounded guarding traces may also be used around the input line, especially if it is driven from a high impedance source. Reducing high amplitude logic signals to 2.5 V will also help.

Use 10-pin layout. Guard around C<sub>H</sub> is tied to output.

Figure 24. Guarding Technique

#### 9.2 Typical Applications

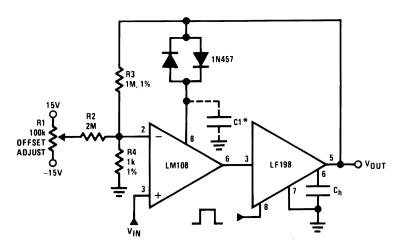

#### 9.2.1 X1000 Sample and Hold

The circuit configuration in Figure 25 shows how to incorporate an amplification factor of 1000 into the sample and hold stage. This may be particularly useful if the input signal has a very low amplitude. Equation 1 provides the appropriate value of capacitance for the COMP 2 pin capacitance of the LM108.

\*For lower gains, the LM108 must be frequency compensated

Figure 25. X1000 Sample and Hold

Use  $\approx \frac{100}{A_V}$  pF from comp 2 to ground

(1)

## 9.2.1.1 Design Requirements

Assume an unbuffered analog to digital converter with 1-Vpp dynamic range is used in a system which needs to sample an input signal with only 1-mVpp amplitude. Using the LF198-N and LM108 connect the input signal so that the maximum dynamic range is used by the 1-Vpp data converter.

#### 9.2.1.2 Detailed Design Procedure

Connect the LFx98x and LM108 as shown in Figure 25. To maximize the dynamic range of 1 Vpp a gain factor of 1000x is needed. Set R3 to 1 M $\Omega$  and R4 to 1 k $\Omega$  to give a noninverting gain of 1001. The calculated value of C1 is 0.1 pF according to Equation 1, which is negligibly small and may be left off of the design.

## **Typical Applications (continued)**

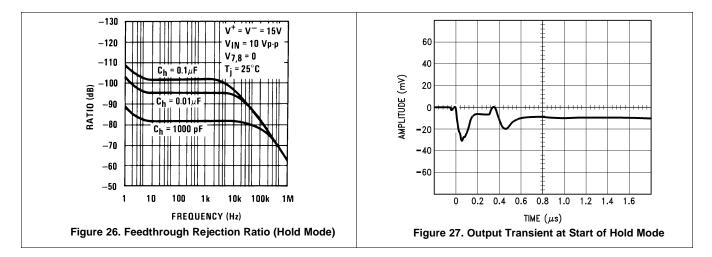

#### 9.2.1.3 Application Curves

The feedthrough rejection ratio of the LF198-N is extremely good and provides good isolation for a wide variety of hold capacitors as Figure 26 shows. Additionally, the output transient settles almost completely after 0.8 µs and would be ready to sample as shown in Figure 27.

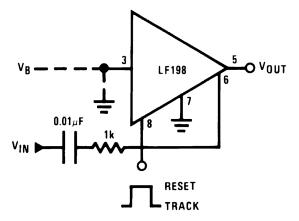

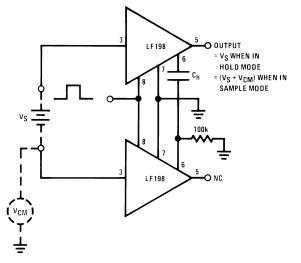

#### 9.2.2 Sample and Difference Circuit

The LFx98x may be used as a sample and difference circuit as shown in Figure 28 where the output follows the input in hold mode.

$V_{OUT} = V_B + \Delta V_{IN}$  (HOLD MODE)

Figure 28. Sample and Difference Circuit

## **Typical Applications (continued)**

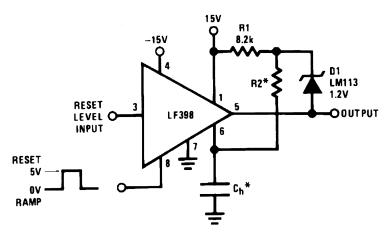

#### 9.2.3 Ramp Generator With Variable Reset Level

The circuit configuration shown in Figure 29 generates a ramp signal with variable reset level. The rise or fall time may be computed by Equation 2.

Figure 29. Ramp Generator With Variable Reset Level

$$\frac{\Delta V}{\Delta T} = \frac{1.2V}{(R2)(C_h)}$$

(2)

## 9.2.4 Integrator With Programmable Reset Level

The LFx98x may be used with LM308 to create an integrator circuit with programmable reset level as shown in Figure 30. The integrated output voltage in hold mode is computed with Equation 3.

$$V_{OUT} \text{ (Hold Mode)} = \left[\frac{1}{(R1)(C_h)}\int_0^t V_{IN} dt\right] + \left[V_R\right]$$

(3)

#### **Typical Applications (continued)**

#### 9.2.5 Output Holds at Average of Sampled Input

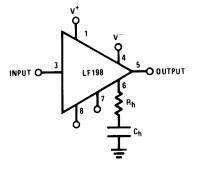

The LFx98x can be used to identify the average value of the input signal and hold the corresponding voltage on the output. Connect  $R_h$  and  $C_h$  as shown in Figure 31. The corresponding values may be calculated with Equation 4.

#### Figure 31. Output Holds at Average of Sampled Input

Select (R<sub>h</sub>) (C<sub>h</sub>)

$$\gg \frac{1}{2\pi f_{IN} (Min)}$$

.

(4)

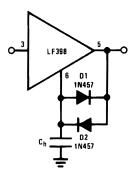

#### 9.2.6 Increased Slew Current

The slew current can be increased by connecting opposing diodes from the OUTPUT to the HOLD CAPACITOR pins as shown in Figure 32.

Figure 32. Increased Slew Current

# **Typical Applications (continued)**

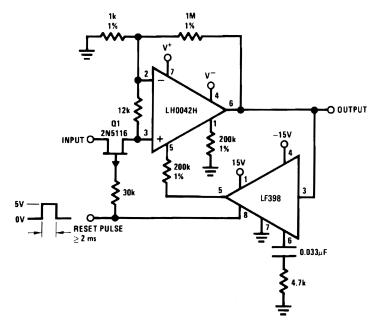

## 9.2.7 Reset Stabilized Amplifier

The LFx98x may be used with LH0042H to create a reset stabilized amplifier with a gain of 1000 as shown in Figure 33.

| $V_{OS} \le 20 \ \mu V$ (No trim) | Z <sub>IN</sub> ≈ 1 MΩ |

|-----------------------------------|------------------------|

|-----------------------------------|------------------------|

#### Figure 33. Reset Stabilized Amplifier

| $\frac{\Delta V_{OS}}{\Delta t} \approx 30 \mu V / \text{sec}$ | (5) |

|----------------------------------------------------------------|-----|

| $\frac{\Delta V_{OS}}{\Delta T} \approx 0.1 \mu V/^{\circ} C$  | (6) |

## **Typical Applications (continued)**

## 9.2.8 Fast Acquisition, Low Droop Sample and Hold

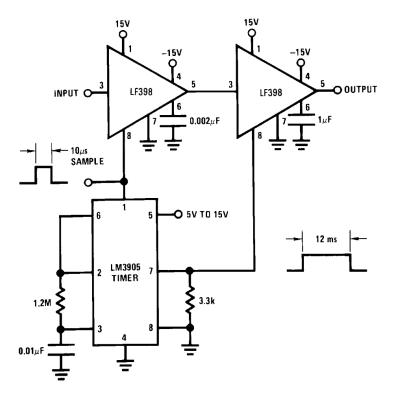

Two LFx98x devices may be used along with LM3905 TIMER to create a fast acquisition, low droop sample and hold circuit as shown in Figure 34.

Figure 34. Fast Acquisition, Low Droop Sample and Hold

#### **Typical Applications (continued)**

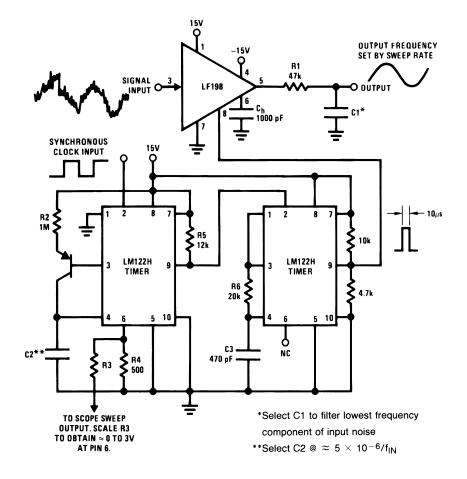

#### 9.2.9 Synchronous Correlator for Recovering Signals Below Noise Level

The LFx98x may be used with two LM122H TIMER devices to create a synchronous correlator for recovering signals below noise level as shown in Figure 35.

Figure 35. Synchronous Correlator for Recovering Signals Below Noise Level

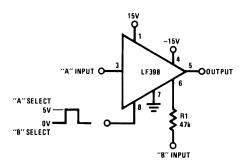

#### 9.2.10 2-Channel Switch

The HOLD CAPACITOR pin could be alternatively used as a second input to create a 2-channel switch shown Figure 36

Figure 36. 2-Channel Switch

In the configuration of Figure 36, input signal A and input signal B have the characteristics listed in Table 1.

## **Typical Applications (continued)**

|                   | Α                  | В        |

|-------------------|--------------------|----------|

| Gain              | 1 ± 0.02%          | 1 ± 0.2% |

| ZIN               | 10 <sup>10</sup> Ω | 47 kΩ    |

| BW                | ≈1 MHz             | ≈400 kHz |

| Crosstalk @ 1 kHz | –90 dB             | –90 dB   |

| Offset            | ≤ 6 mV             | ≤ 75 mV  |

#### **Table 1. 2-Channel Switch Characteristics**

## 9.2.11 DC and AC Zeroing

The LFLFx98x features an OFFSET ADJUST pin which can be connected to a potentiometer to zero the DC offset. Additionally, an inverter may be connected with an AC-coupled potentiometer to the HOLD CAPACITOR pin to create a DC- and AC-zeroing circuit as shown in Figure 37.

Figure 37. DC and AC Zeroing

#### 9.2.12 Staircase Generator

The LFx98x can be connected as shown in Figure 38 to create a staircase generator.

\*Select for step height: 50 k $\Omega \rightarrow$  1-V Step.

Figure 38. Staircase Generator

#### 9.2.13 Differential Hold

Two LFx98x devices may be connected as shown in Figure 39 to create a differential hold circuit.

Figure 39. Differential Hold

#### 9.2.14 Capacitor Hysteresis Compensation

The LFx98x devices may be used for capacitor hysteresis compensation as shown in Figure 40.

\*Select for time constant C1 =  $\tau/100 \text{ k}\Omega$

\*\*Adjust for amplitude

#### Figure 40. Capacitor Hysteresis Compensation

## **10 Power Supply Recommendations**

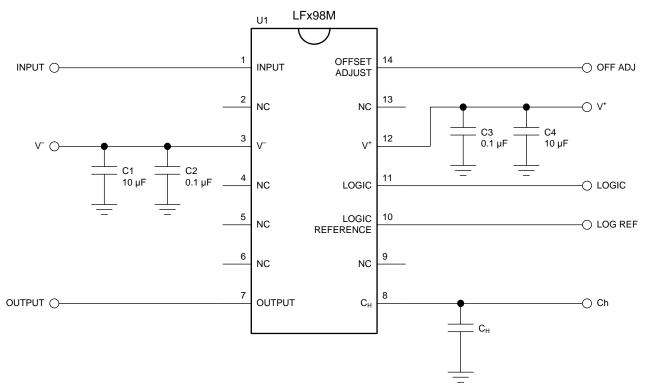

The LFx98x devices are rated for a typical supply voltage of ±15 V. To achieve noise immunity as appropriate to the application, it is important to use good printed-circuit-board layout practices for power supply rails and planes, as well as using bypass capacitors connected between the power supply pins and ground. All bypass capacitors must be rated to handle the supply voltage and be decoupled to ground. TI recommends to decouple each supply with two capacitors; a small value ceramic capacitor (approximately 0.1  $\mu$ F) placed close to the supply pin in addition to a large value Tantalum or Ceramic ( $\geq 10 \ \mu$ F). The large capacitor can be shared by more than one device if necessary. The small ceramic capacitor maintains low supply impedance at higher frequencies while the large capacitor will act as the charge bucket for fast load current spikes at the op amp output. The combination of these capacitors will provide supply decoupling and will help maintain stable operation for most loading conditions.

## 11 Layout

## 11.1 Layout Guidelines

Take care to minimize the loop area formed by the bypass capacitor connection between supply pins and ground. A ground plane underneath the device is recommended; any bypass components to ground should have a nearby via to the ground plane. The optimum bypass capacitor placement is closest to the corresponding supply pin. Use of thicker traces from the bypass capacitors to the corresponding supply pins will lower the power supply inductance and provide a more stable power supply. The feedback components should be placed as close to the device as possible to minimize stray parasitics.

## 11.2 Layout Example

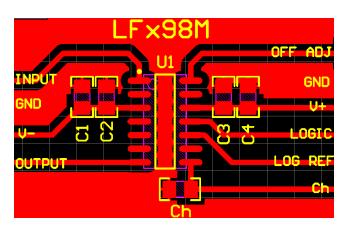

Figure 41 shows an example schematic and layout for the LFx98x 8-pin PDIP package.

Figure 41. Schematic Example

Figure 42. Layout Example

TEXAS INSTRUMENTS

#### 12 器件和文档支持

#### 12.1 器件支持

#### 12.1.1 器件命名规则

- 保持步进:当从采样模式切换到具有稳定(直流)模拟输入电压的保持模式时,采样和保持输出的电压步进。 逻辑摆幅为 5V。

- 采集时间: 以 10V 的输出步长获取新的模拟输入电压所需的时间。采集时间不仅仅是输出达到稳定所需的时间,还包括所有内部节点达到稳定所需的时间,从而在切换到保持模式时,输出为适当的值。

- 增益误差: 在采样模式下, 输出电压摆幅与输入电压摆幅的比值(以百分比差值表示)。

- 保持趋稳时间:在保持逻辑命令之后,输出稳定到最终值 1mV 范围内所需的时间。

- 动态采样误差:由于在给定保持命令时改变了模拟输入,而在保持输出中引入的误差。误差以给定保持电容器 值(以mV为单位)和输入转换率表示。即使采样时间较长,也会出现此误差项。

- 孔径时间:保持命令和输入模拟转换之间所需的延迟,以便转换不影响保持的输出。

#### 12.2 相关链接

下表列出了快速访问链接。类别包括技术文档、支持与社区资源、工具和软件,以及申请样片或购买产品的快速链接。

| 器件            | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持和社区 |  |  |  |  |  |

|---------------|-------|-------|-------|-------|-------|--|--|--|--|--|

| LF198-N       | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |  |  |  |  |  |

| LF298         | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |  |  |  |  |  |

| LF398-N       | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |  |  |  |  |  |

| LF198A-N      | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |  |  |  |  |  |

| LF398A-N(已淘汰) | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |  |  |  |  |  |

#### 表 2. 相关链接

#### 12.3 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范, 并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 **71 参考设计支持** 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 12.4 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.5 静电放电警告

这些装置包含有限的内置 ESD 保护。存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损

伤。

#### 12.6 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、缩写和定义。

#### 13 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且 不会对此文档进行修订。如需获取此产品说明书的浏览器版本,请查阅左侧的导航栏。

## **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)         | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-------------------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LF198AH/NOPB     | ACTIVE        | TO-99        | LMC                | 8    | 500            | RoHS & Green            | Call TI                              | Level-1-NA-UNLIM     | -55 to 125   | ( LF198AH, LF198AH<br>) | Samples |

| LF198H           | ACTIVE        | TO-99        | LMC                | 8    | 500            | Non-RoHS &<br>Non-Green | Call TI                              | Call TI              | -55 to 125   | ( LF198H, LF198H)       | Samples |

| LF198H/NOPB      | ACTIVE        | TO-99        | LMC                | 8    | 500            | RoHS & Green            | Call TI                              | Level-1-NA-UNLIM     | -55 to 125   | ( LF198H, LF198H)       | Samples |

| LF298M           | NRND          | SOIC         | D                  | 14   | 55             | Non-RoHS<br>& Green     | Call TI                              | Level-1-235C-UNLIM   | -25 to 85    | LF298M                  |         |

| LF298M/NOPB      | ACTIVE        | SOIC         | D                  | 14   | 55             | RoHS & Green            | SN                                   | Level-1-260C-UNLIM   | -25 to 85    | LF298M                  | Samples |

| LF298MX          | NRND          | SOIC         | D                  | 14   | 2500           | Non-RoHS<br>& Green     | Call TI                              | Level-1-235C-UNLIM   | -25 to 85    | LF298M                  |         |

| LF298MX/NOPB     | ACTIVE        | SOIC         | D                  | 14   | 2500           | RoHS & Green            | SN                                   | Level-1-260C-UNLIM   | -25 to 85    | LF298M                  | Samples |

| LF398AN/NOPB     | ACTIVE        | PDIP         | Р                  | 8    | 40             | RoHS & Green            | NIPDAU                               | Level-1-NA-UNLIM     | 0 to 70      | LF<br>398AN             | Samples |

| LF398H           | ACTIVE        | TO-99        | LMC                | 8    | 500            | RoHS & Green            | Call TI                              | Level-1-NA-UNLIM     | 0 to 70      | LF398H                  | Samples |

| LF398H/NOPB      | ACTIVE        | TO-99        | LMC                | 8    | 500            | RoHS & Green            | Call TI                              | Level-1-NA-UNLIM     | 0 to 70      | ( LF398H, LF398H)       | Samples |

| LF398M           | NRND          | SOIC         | D                  | 14   | 55             | Non-RoHS<br>& Green     | Call TI                              | Level-1-235C-UNLIM   | 0 to 70      | LF398M                  |         |

| LF398M/NOPB      | ACTIVE        | SOIC         | D                  | 14   | 55             | RoHS & Green            | SN                                   | Level-1-260C-UNLIM   | 0 to 70      | LF398M                  | Samples |

| LF398MX/NOPB     | ACTIVE        | SOIC         | D                  | 14   | 2500           | RoHS & Green            | SN                                   | Level-1-260C-UNLIM   | 0 to 70      | LF398M                  | Samples |

| LF398N/NOPB      | ACTIVE        | PDIP         | Р                  | 8    | 40             | RoHS & Green            | NIPDAU                               | Level-1-NA-UNLIM     | 0 to 70      | LF<br>398N              | Samples |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

#### www.ti.com

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

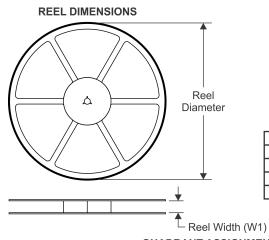

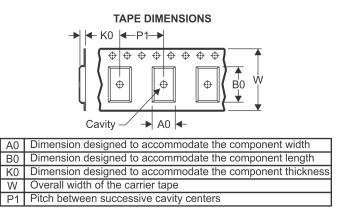

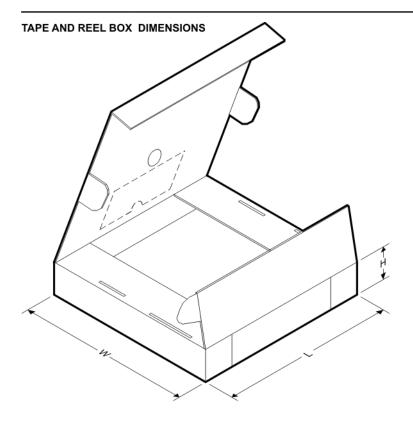

## TAPE AND REEL INFORMATION

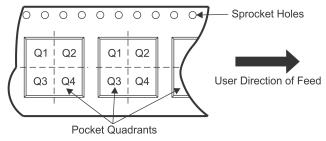

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LF298MX                     | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.35       | 2.3        | 8.0        | 16.0      | Q1               |

| LF298MX/NOPB                | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.35       | 2.3        | 8.0        | 16.0      | Q1               |

| LF398MX/NOPB                | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.35       | 2.3        | 8.0        | 16.0      | Q1               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

9-Apr-2022

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LF298MX      | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 35.0        |

| LF298MX/NOPB | SOIC         | D               | 14   | 2500 | 356.0       | 356.0      | 35.0        |

| LF398MX/NOPB | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 35.0        |

www.ti.com

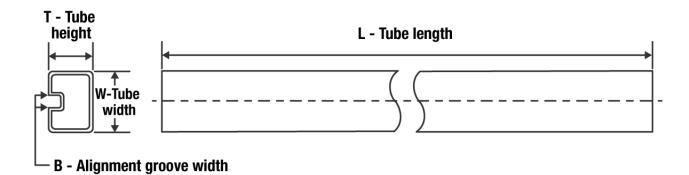

## TUBE

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LF298M       | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LF298M       | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LF298M/NOPB  | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LF398AN/NOPB | Р            | PDIP         | 8    | 40  | 502    | 14     | 11938  | 4.32   |

| LF398M       | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LF398M       | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LF398M/NOPB  | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LF398N/NOPB  | Р            | PDIP         | 8    | 40  | 502    | 14     | 11938  | 4.32   |

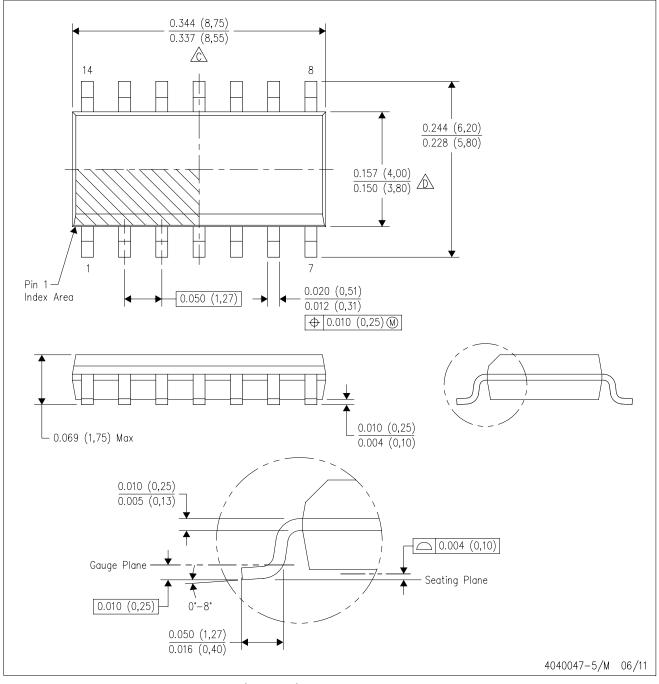

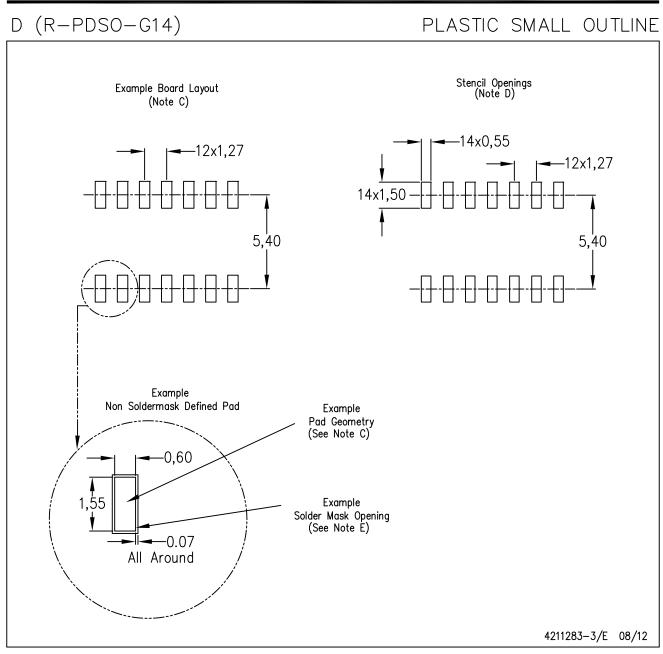

D (R-PDSO-G14)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AB.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

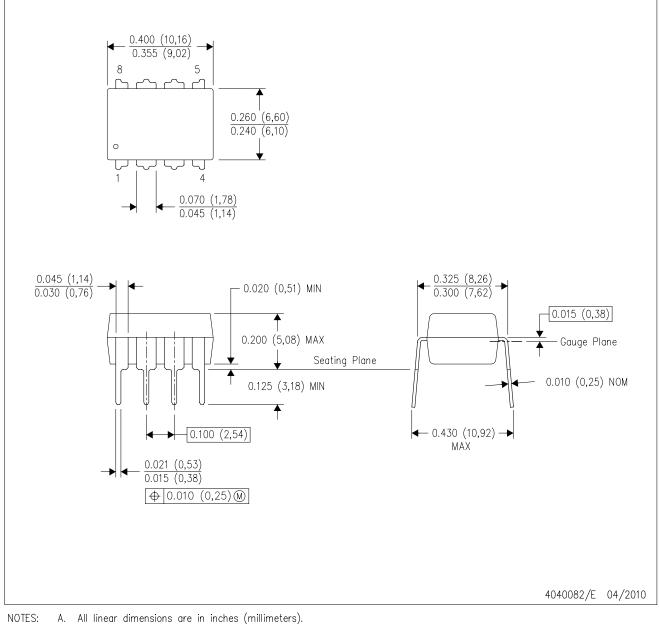

P(R-PDIP-T8)

PLASTIC DUAL-IN-LINE PACKAGE

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

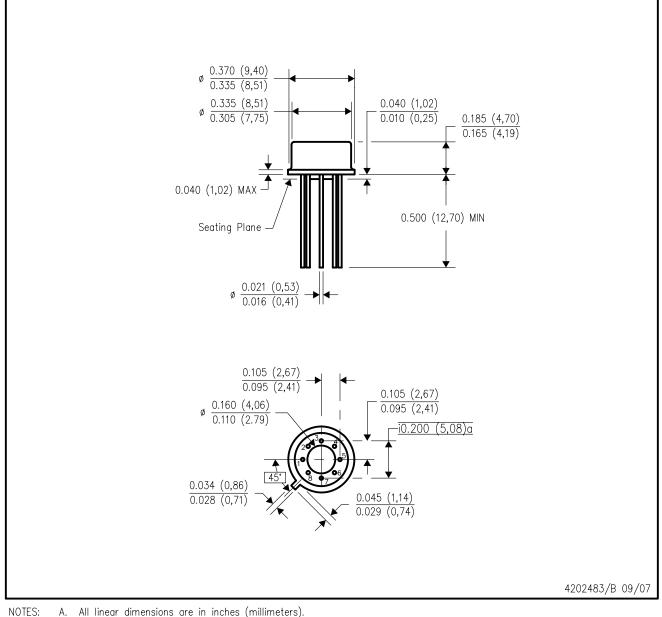

LMC (O-MBCY-W8)

# METAL CYLINDRICAL PACKAGE

- B. This drawing is subject to change without notice.

- C. Leads in true position within 0.010 (0,25) R @ MMC at seating plane.

- D. Pin numbers shown for reference only. Numbers may not be marked on package.

- E. Falls within JEDEC MO-002/TO-99.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Sample & Hold Amplifiers category:

Click to view products by Texas Instruments manufacturer:

Other Similar products are found below :

LF298MX/NOPB DS1843D+TRL HV257FG-G AD582SD/883B SMP04ESZ-REEL HA5351IBZ HA9P5320-5Z LF198AH/NOPB LF198H LF298H/NOPB LF298M/NOPB LF398AN/NOPB LF398H LF398M/NOPB LF398N/NOPB LF298H