Sample &

Buv

SNVS606L-JUNE 2009-REVISED DECEMBER 2014

# LM3530 High-Efficiency White-LED Driver with Programmable Ambient Light Sensing Capability and I<sup>2</sup>C-Compatible Interface

Technical

Documents

# 1 Features

- Drives up to 11 LEDs in series

- 1000:1 Dimming Ratio

- 90% Efficient

- Programmable Dual Ambient Light Sensor Inputs

with Internal ALS Voltage Setting Resistors

- I<sup>2</sup>C Programmable Logarithmic or Linear Brightness Control

- External PWM Input for Simple Brightness Adjustment

- True Shutdown Isolation for LEDs and Ambient Light Sensors

- Internal Soft-Start Limits Inrush Current

- Wide 2.7-V to 5.5-V Input Voltage Range

- 40-V and 25-V Overvoltage Protection Options

- 500-kHz Fixed Frequency Operation

- 839-mA Peak Current Limit

# 2 Applications

- Smartphone LCD Backlighting

- Personal Navigation LCD Backlighting

- 2 to 11 Series White-LED Backlit Display Power Source

# 3 Description

Tools &

Software

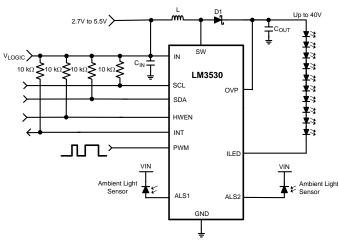

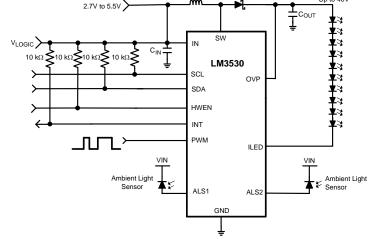

The LM3530 current mode boost converter supplies the power and controls the current in up to 11 series white LEDs. The 839-mA current limit and 2.7-V to 5.5-V input voltage range make the device a versatile backlight power source ideal for operation in portable applications.

Support &

Community

20

The LED current is adjustable from 0 mA to 29.5 mA via an I<sup>2</sup>C-compatible interface. The 127 different current steps and 8 different maximum LED current levels give over 1000 programmable LED current levels. Additionally, PWM brightness control is possible through an external logic level input.

The device also features two Ambient Light Sensor inputs. These are designed to monitor analog output ambient light sensors and provide programmable adjustment of the LED current with changes in ambient light. Each ambient light sensor input has independently programmable internal voltage setting resistors which can be made high impedance to reduce power during shutdown. The 500-kHz switching frequency allows for high converter efficiency over a wide output voltage range accommodating from 2 to 11 series LEDs. Finally, the support of Content Adjusted Backlighting maximizes battery life while maintaining display image quality.

The LM3530 operates over the  $-40^{\circ}$ C to  $85^{\circ}$ C temperature range.

### Device Information<sup>(1)</sup>

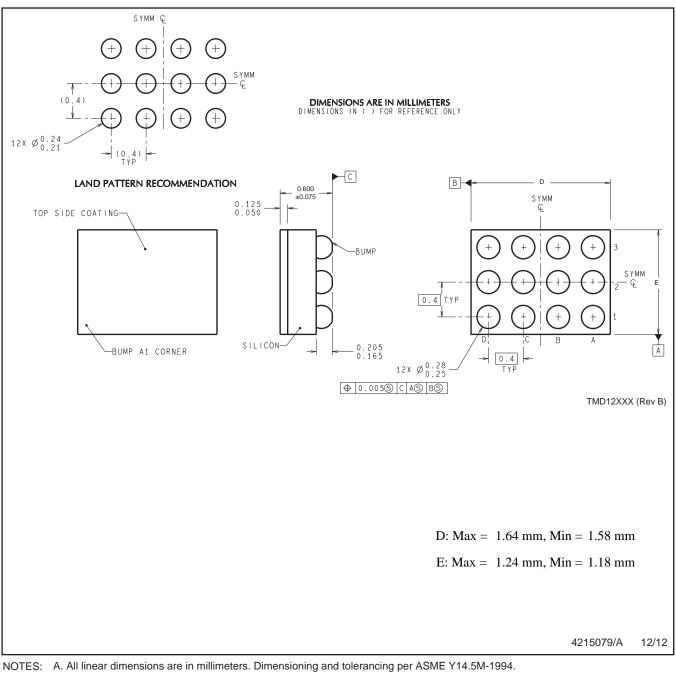

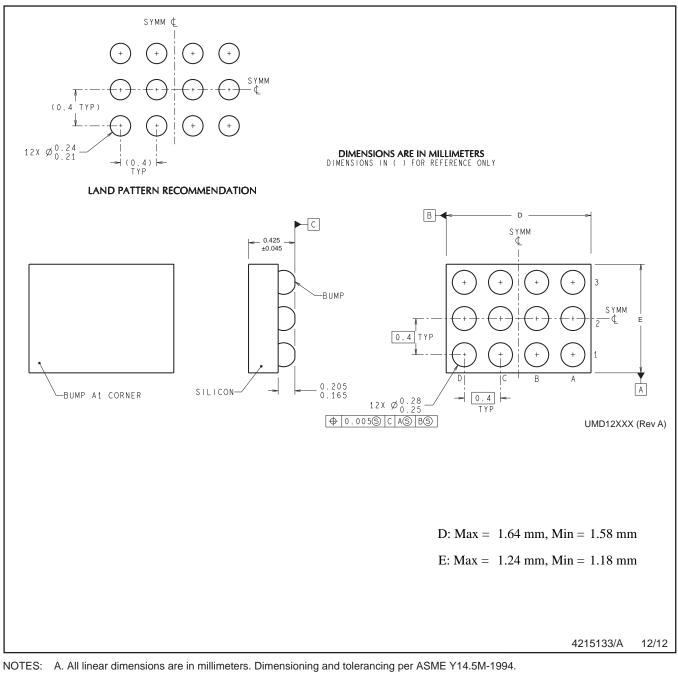

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)   |  |

|-------------|------------|-------------------|--|

| LM3530      | DSBGA (12) | 1.64 mm x 1.24 mm |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

### **Simplified Schematic**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

STRUMENTS

EXAS

# **Table of Contents**

| 1 | Feat | tures 1                                                      |

|---|------|--------------------------------------------------------------|

| 2 | Арр  | lications 1                                                  |

| 3 | Des  | cription 1                                                   |

| 4 | Rev  | ision History 2                                              |

| 5 | I2C  | Device Options                                               |

| 6 | Pin  | Configuration and Functions 3                                |

| 7 | Spe  | cifications 4                                                |

|   | 7.1  | Absolute Maximum Ratings 4                                   |

|   | 7.2  | ESD Ratings 4                                                |

|   | 7.3  | Recommended Operating Conditions 4                           |

|   | 7.4  | Thermal Information 4                                        |

|   | 7.5  | Electrical Characteristics 5                                 |

|   | 7.6  | I <sup>2</sup> C-Compatible Timing Requirements (SCL, SDA) 6 |

|   | 7.7  | Simple Interface Timing 6                                    |

|   | 7.8  | Typical Characteristics 7                                    |

| 8 | Deta | ailed Description 11                                         |

|   | 8.1  | Overview 11                                                  |

|   | 8.2  | Functional Block Diagram 11                                  |

|   |      |                                                              |

|    | 8.3  | Feature Description               | 12 |

|----|------|-----------------------------------|----|

|    | 8.4  | Device Functional Modes           | 26 |

|    | 8.5  | Programming                       | 27 |

|    | 8.6  | Register Maps                     | 28 |

| 9  | App  | lication and Implementation       | 34 |

|    | 9.1  | Application Information           | 34 |

|    | 9.2  | Typical Application               | 34 |

| 10 | Pow  | er Supply Recommendations         | 38 |

| 11 | Lay  | out                               | 38 |

|    | 11.1 | Layout Guidelines                 | 38 |

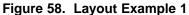

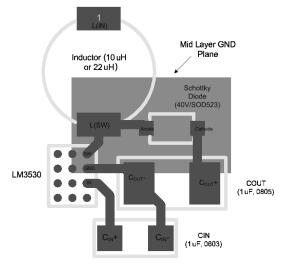

|    | 11.2 | Layout Example                    | 41 |

| 12 | Dev  | ice and Documentation Support     | 43 |

|    | 12.1 | Device Support                    | 43 |

|    | 12.2 |                                   |    |

|    | 12.3 | Trademarks                        | 43 |

|    | 12.4 | Electrostatic Discharge Caution   | 43 |

|    | 12.5 | Glossary                          | 43 |

| 13 | Мес  | hanical, Packaging, and Orderable |    |

|    |      | mation                            | 43 |

|    |      |                                   |    |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision K (March 2013) to Revision L                                                                                                                                                                                                                                                  | Page |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added Device Information and ESD Ratings tables, Detailed Description, Application and Implementation, Power<br>Supply Recommendations, Layout, Device and Documentation Support and Mechanical, Packaging, and Orderable<br>Information sections; moved some curves to Application Curves section |      |

| C  | hanges from Revision J (March 2013) to Revision K                                                                                                                                                                                                                                                  | Page |

| • | Changed layout of National Data Sheet to TI format | . 3 | 4 |

|---|----------------------------------------------------|-----|---|

|---|----------------------------------------------------|-----|---|

# 5 I<sup>2</sup>C Device Options

| ORDERABLE NUMBER | I <sup>2</sup> C DEVICE OPTION |

|------------------|--------------------------------|

| LM3530TME-40     | 0x38                           |

| LM3530TMX-40     | 0x38                           |

| LM3530UME-25A    | 0x36                           |

| LM3530UME-40     | 0x38                           |

| LM3530UME-40B    | 0x39                           |

| LM3530UMX-25A    | 0x36                           |

| LM3530UMX-40     | 0x38                           |

| LM3530UMX-40B    | 0x39                           |

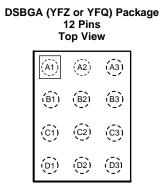

# 6 Pin Configuration and Functions

### **Pin Functions**

| PIN    |      | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                             |  |

|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NUMBER | NAME | TTPE | DESCRIPTION                                                                                                                                                                                                             |  |

| A1     | SDA  | I/O  | Serial data connection for I <sup>2</sup> C-compatible interface.                                                                                                                                                       |  |

| A2     | SCL  | I    | Serial data connection for I <sup>2</sup> C-compatible interface.                                                                                                                                                       |  |

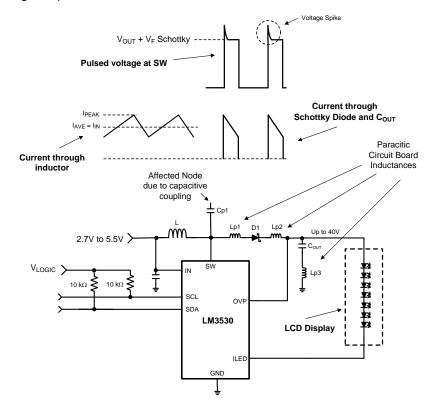

| A3     | SW   | PWR  | Inductor connection, diode anode connection, and drain connection for internal NFET. Connect the inductor and diode as close as possible to SW to reduce parasitic inductance and capacitive coupling to nearby traces. |  |

| B1     | PWM  | I    | External PWM brightness control input and simple enable input.                                                                                                                                                          |  |

| B2     | INT  | 0    | gic interrupt output signaling the ALS zone has changed.                                                                                                                                                                |  |

| B3     | GND  |      | und                                                                                                                                                                                                                     |  |

| C1     | ALS2 | I    | Ambient light sensor input 2 with programmable internal pull-down resistor.                                                                                                                                             |  |

| C2     | HWEN | I    | Active high hardware enable (active low reset). pull this pin high to enable the LM3530.                                                                                                                                |  |

| C3     | IN   | PWR  | Input voltage connection. Connect a 2.7-V to 5.5-V supply to IN and bypass to GND with a 2.2- $\mu F$ or greater ceramic capacitor.                                                                                     |  |

| D1     | ALS1 | I    | Ambient light sensor input 1 with programmable internal pulldown resistor.                                                                                                                                              |  |

| D2     | OVP  | I    | Output voltage sense connection for overvoltage sensing. Connect OVP to the positive terminal of the output capacitor.                                                                                                  |  |

| D3     | ILED | PWR  | Input terminal to internal current sink. The boost converter regulates ILED to 0.4 V.                                                                                                                                   |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                                                                                                                          | MIN       | MAX                     | UNIT |

|--------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|------|

| V <sub>IN</sub> to GND                                                                                                   | -0.3      | 6                       |      |

| V <sub>SW</sub> , V <sub>OVP</sub> , V <sub>ILED</sub> to GND                                                            |           | 45                      |      |

| V <sub>SCL</sub> , V <sub>SDA</sub> , V <sub>ALS1</sub> , V <sub>PWM</sub> , V <sub>INT</sub> , V <sub>HWEN</sub> to GND |           | 6                       | V    |

| V <sub>ALS2</sub> to GND                                                                                                 | –0.3 V to | V <sub>IN</sub> + 0.3 V |      |

| Continuous power dissipation                                                                                             | Internal  | ly limited              |      |

| Junction temperature (T <sub>J-MAX</sub> )                                                                               |           | 150                     | °C   |

| Maximum lead temperature (soldering, 10s)                                                                                | Se        | e <sup>(4)</sup>        |      |

| Storage temperature, T <sub>stg</sub>                                                                                    | -65       | 150                     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) All voltages are with respect to the potential at the GND pin.

(4) For detailed soldering specifications and information, please refer to Application Note 1112: DSBGA Wafer Level Chip Scale Package (SNVA009).

# 7.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                            | MIN | NOM MAX | UNIT |

|--------------------------------------------|-----|---------|------|

| V <sub>IN</sub> to GND                     | 2.7 | 5.5     | V    |

| $V_{SW}$ , $V_{OVP}$ , $V_{ILED}$ , to GND | 0   | 40      | v    |

| Junction temperature $(T_J)^{(1)}$         | -40 | 125     | °C   |

| Ambient temperature $(T_A)^{(2)}$          | -40 | 85      |      |

Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub>= 140°C (typ.) and disengages at T<sub>J</sub>= 125°C (typ.).

(2) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (R<sub>θJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

### 7.4 Thermal Information

|                                                                        | DSE  | UNIT |      |

|------------------------------------------------------------------------|------|------|------|

| THERMAL METRIC <sup>(1)</sup>                                          | YFQ  |      |      |

|                                                                        | 12 F | PINS |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance <sup>(2)</sup> | 61   | .7   | °C/W |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953. (2) Junction-to-ambient thermal resistance ( $R_{PA}$ ) is taken from a thermal modeling result, performed under the conditions and guidelines

(2) Junction-to-ambient thermal resistance (R<sub>0JA</sub>) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 102 mm x 76 mm x 1.6 mm with a 2 x 1 array of thermal vias. The ground plane on the board is 50 mm x 50 mm. Thickness of copper layers are 36 µm/18 µm/18 µm/3 6µm (1.5oz/1oz/1.5oz). Ambient temperature in simulation is 22°C in still air. Power dissipation is 1W. The value of R<sub>0JA</sub> of this product in the DSBGA package could fall in a range as wide as 60°C/W to 110°C/W (if not wider), depending on PCB material, layout, and environmental conditions. In applications where high maximum power dissipation exists special care must be paid to thermal dissipation issues.

# 7.5 Electrical Characteristics

Typical (TYP) limits are for  $T_A = 25^{\circ}$ C; minimum (MIN) and maximum (MAX) apply over the full operating ambient temperature range (-40°C ≤  $T_A ≤ 85^{\circ}$ C);  $V_{IN} = 3.6$  V, unless otherwise specified.<sup>(1)(2)</sup>

|                      | PARAMETER                                  | TEST CONDITIONS                                                                                                             |                 | MIN   | TYP    | MAX             | UNIT |

|----------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|-------|--------|-----------------|------|

| I <sub>LED</sub>     | Output current regulation                  | 2.7 V $\ge$ V <sub>IN</sub> $\ge$ 5.5 V, Full-scale current = 19 mA, BRT Code = 0x7F, ALS Select Bit = 0, $I^2C$ Enable = 1 |                 | 17.11 | 18.6   | 20.08           | mA   |

| V <sub>REG_CS</sub>  | Regulated current sink<br>headroom voltage |                                                                                                                             |                 |       | 400    |                 | mV   |

| V <sub>HR</sub>      | Current sink minimum headroom voltage      | $I_{LED} = 95\%$ of nominal                                                                                                 |                 |       | 200    |                 | mV   |

| R <sub>DSON</sub>    | NMOS switch on resistance                  | I <sub>SW</sub> = 100 mA                                                                                                    |                 |       | 0.25   |                 | Ω    |

| I <sub>CL</sub>      | NMOS switch current limit                  | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                             |                 | 739   | 839    | 936             | mA   |

|                      |                                            | ON Threshold, 2.7 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V                                                                     | 40-V<br>version | 40    | 41     | 42              |      |

| V <sub>OVP</sub>     | Output overvoltage protection              |                                                                                                                             | 25-V<br>version | 23.6  | 24     | 24.6            | V    |

|                      |                                            | Hysteresis                                                                                                                  |                 |       | 1      |                 |      |

| f <sub>SW</sub>      | Switching frequency                        | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5.5 \text{ V}$                                                                |                 | 450   | 500    | 550             | kHz  |

| D <sub>MAX</sub>     | Maximum duty cycle                         |                                                                                                                             |                 |       | 94%    |                 |      |

| D <sub>MIN</sub>     | Minimum duty cycle                         |                                                                                                                             |                 |       | 10%    |                 |      |

| l <sub>Q</sub>       | Quiescent current, device not switching    | V <sub>HWEN</sub> = V <sub>IN</sub>                                                                                         |                 |       | 490    | 600             | μA   |

| I <sub>Q_SW</sub>    | Switching supply current                   | I <sub>LED</sub> = 19 mA, V <sub>OUT</sub> = 36 V                                                                           |                 |       | 1.35   |                 | mA   |

| I <sub>SHDN</sub>    | Shutdown current                           | $V_{HWEN} = GND, 2.7 V \ge V_{IN} \ge 5.5$                                                                                  | V               |       | 1      | 2               | μA   |

| I <sub>LED_MIN</sub> | Minimum LED current                        | Full-scale current = 19 mA setting<br>BRT = 0x01                                                                            |                 |       | 9.5    |                 | μA   |

| V <sub>ALS</sub>     | Ambient light sensor<br>reference voltage  | $2.7 \text{ V} \ge \text{V}_{\text{IN}} \ge 5.5 \text{ V}^{(3)}$                                                            |                 | 0.97  | 1      | 1.03            | V    |

| V                    | Logic thresholds - logic low               |                                                                                                                             |                 | 0     |        | 0.4             | V    |

| V <sub>HWEN</sub>    | Logic thresholds - logic high              |                                                                                                                             |                 | 1.2   |        | V <sub>IN</sub> | V    |

| T <sub>SD</sub>      | Thermal shutdown                           |                                                                                                                             |                 |       | 140    |                 | °C   |

|                      | Hysteresis                                 |                                                                                                                             |                 |       | 15     |                 |      |

|                      |                                            |                                                                                                                             |                 | 12.77 | 13.531 | 14.29           |      |

|                      |                                            |                                                                                                                             |                 | 8.504 | 9.011  | 9.518           |      |

|                      |                                            |                                                                                                                             |                 | 5.107 | 5.411  | 5.715           |      |

|                      |                                            |                                                                                                                             |                 | 2.143 | 2.271  | 2.399           |      |

|                      |                                            |                                                                                                                             |                 | 1.836 | 1.946  | 2.055           |      |

|                      |                                            |                                                                                                                             |                 | 1.713 | 1.815  | 1.917           |      |

|                      |                                            |                                                                                                                             |                 | 1.510 | 1.6    | 1.69            |      |

| RALS1,<br>RALS2      | ALS input internal pull-down resistors     | 2.7 V ≥ V <sub>IN</sub> ≥ 5.5 V                                                                                             |                 | 1.074 | 1.138  | 1.202           | kΩ   |

| INALO2               | 1000010                                    |                                                                                                                             |                 | 0.991 | 1.050  | 1.109           |      |

|                      |                                            |                                                                                                                             |                 | 0.954 | 1.011  | 1.068           |      |

|                      |                                            |                                                                                                                             |                 | 0.888 | 0.941  | 0.994           |      |

|                      |                                            |                                                                                                                             |                 | 0.717 | 0.759  | 0.802           |      |

|                      |                                            |                                                                                                                             |                 | 0.679 | 0.719  | 0.760           |      |

|                      |                                            |                                                                                                                             |                 | 0.661 | 0.700  | 0.740           |      |

|                      |                                            |                                                                                                                             | -               | 0.629 | 0.666  |                 |      |

(1) All voltages are with respect to the potential at the GND pin.

(2) Min and Max limits are verified by design, test, or statistical analysis. Typical (typ.) numbers are not verified, but represent the most likely norm.

(3) The ALS voltage specification is the maximum trip threshold for the ALS zone boundary (Code 0xFF). Due to random offsets and the mechanism for which the hysteresis voltage varies, it is recommended that only Codes 0x04 and above be used for Zone Boundary Thresholds. See *Zone Boundary Trip Points and Hysteresis* and *Minimum Zone Boundary Settings* sections.

# **Electrical Characteristics (continued)**

Typical (TYP) limits are for  $T_A = 25^{\circ}$ C; minimum (MIN) and maximum (MAX) apply over the full operating ambient temperature range (-40°C ≤  $T_A \le 85^{\circ}$ C);  $V_{IN} = 3.6$  V, unless otherwise specified.<sup>(1)(2)</sup>

|                                                   | PARAMETER                   | TEST CONDITIONS                                              | MIN  | TYP MAX         | UNIT |  |

|---------------------------------------------------|-----------------------------|--------------------------------------------------------------|------|-----------------|------|--|

| LOGIC VOLTAGE SPECIFICATIONS (SCL, SDA, PWM, INT) |                             |                                                              |      |                 |      |  |

| VIL                                               | Input logic low             | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5.5 \text{ V}$ | 0    | 0.54            | V    |  |

| VIH                                               | Input logic high            | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$   | 1.26 | V <sub>IN</sub> | V    |  |

| V <sub>OL</sub>                                   | Output logic low (SDA, INT) | I <sub>LOAD</sub> = 3 mA                                     |      | 400             | mV   |  |

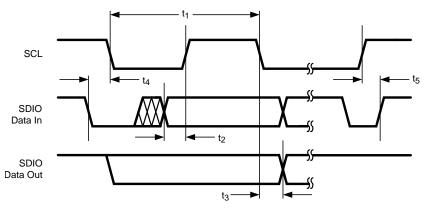

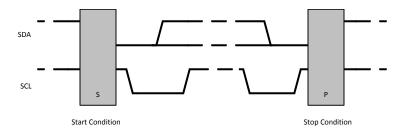

# 7.6 I<sup>2</sup>C-Compatible Timing Requirements (SCL, SDA)<sup>(1)</sup>

|                |                                          | MIN | NOM MAX | UNIT |

|----------------|------------------------------------------|-----|---------|------|

| t <sub>1</sub> | SCL (Clock Period)                       | 2.5 |         | μs   |

| t <sub>2</sub> | Data in setup time to SCL high           | 100 |         | ns   |

| t <sub>3</sub> | Data out stable after SCL low            | 0   |         | ns   |

| t4             | SDA low setup time to SCL low (start)    | 100 |         | ns   |

| t <sub>5</sub> | SDA high hold time after SCL High (stop) | 100 |         | ns   |

(1) SCL and SDA must be glitch-free in order for proper brightness control to be realized.

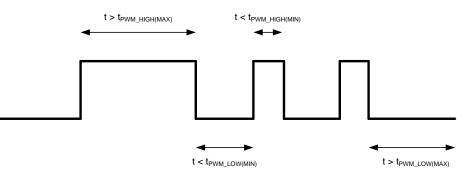

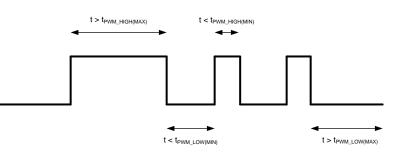

## 7.7 Simple Interface Timing

|                       |                                        | MIN  | NOM | MAX  | UNIT |

|-----------------------|----------------------------------------|------|-----|------|------|

| t <sub>PWM_HIGH</sub> | Enable time, PWM pin must be held high | 1.5  | 2   | 2.6  |      |

| t <sub>PWM_LOW</sub>  | Disable time, PWM pin must be held low | 1.48 | 2   | 2.69 | ms   |

Figure 2. Simple Enable/Disable Timing

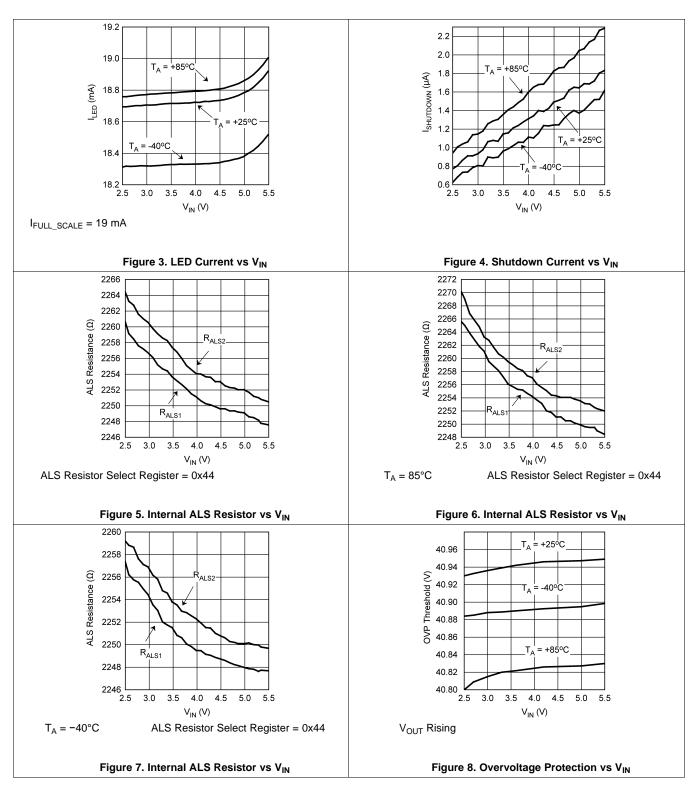

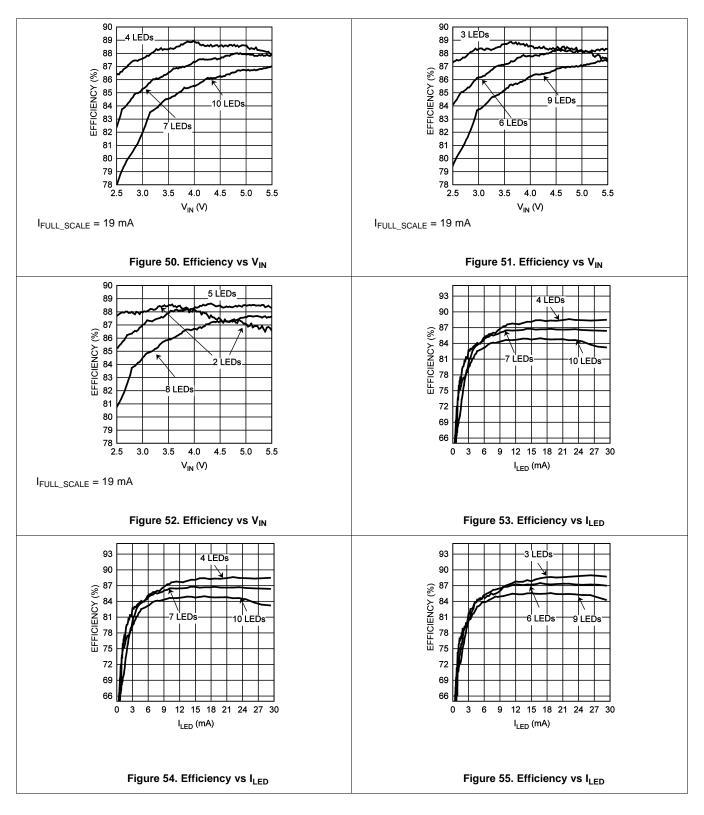

# 7.8 Typical Characteristics

$V_{\text{IN}} = 3.6 \text{ V}, \text{ LEDs are OVSRWAC1R6 from OPTEK Technology, } C_{\text{OUT}} = 1 \text{ }\mu\text{F}, \text{ } C_{\text{IN}} = 1 \text{ }\mu\text{F}, \text{ } L = \text{TDK VLF5012ST-100M1R0}, \\ (\text{R}_{\text{L}} = 0.24 \text{ }\Omega), \text{ } \text{I}_{\text{LED}} = 19 \text{ mA}, \text{ } \text{T}_{\text{A}} = 25^{\circ}\text{C}, \text{ unless otherwise specified}. }$

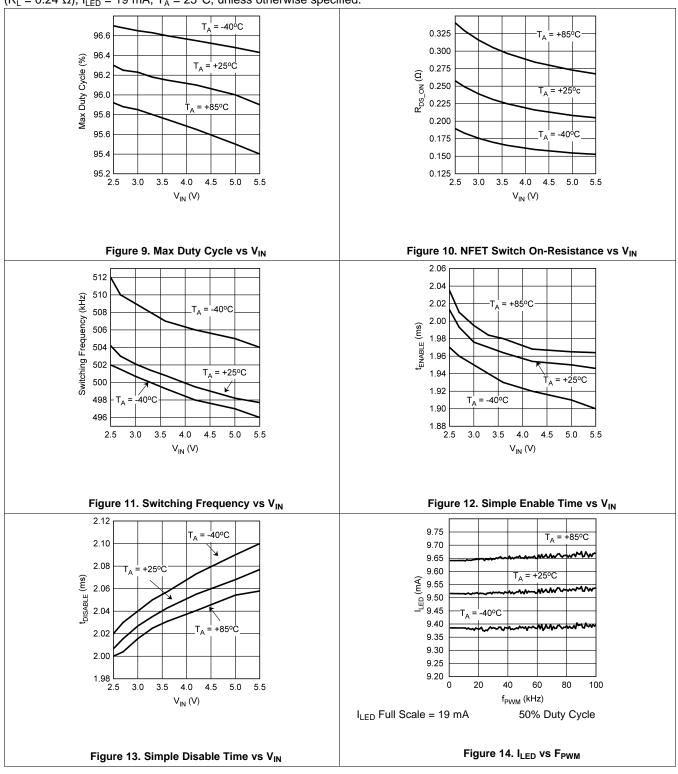

# **Typical Characteristics (continued)**

$V_{\text{IN}} = 3.6 \text{ V}, \text{ LEDs are OVSRWAC1R6 from OPTEK Technology, } C_{\text{OUT}} = 1 \text{ }\mu\text{F}, \text{ } C_{\text{IN}} = 1 \text{ }\mu\text{F}, \text{ } L = \text{TDK VLF5012ST-100M1R0}, \\ (R_{\text{L}} = 0.24 \text{ }\Omega), \text{ } I_{\text{LED}} = 19 \text{ }\text{mA}, \text{ } T_{\text{A}} = 25^{\circ}\text{C}, \text{ } \text{ }\text{unless otherwise specified}.$

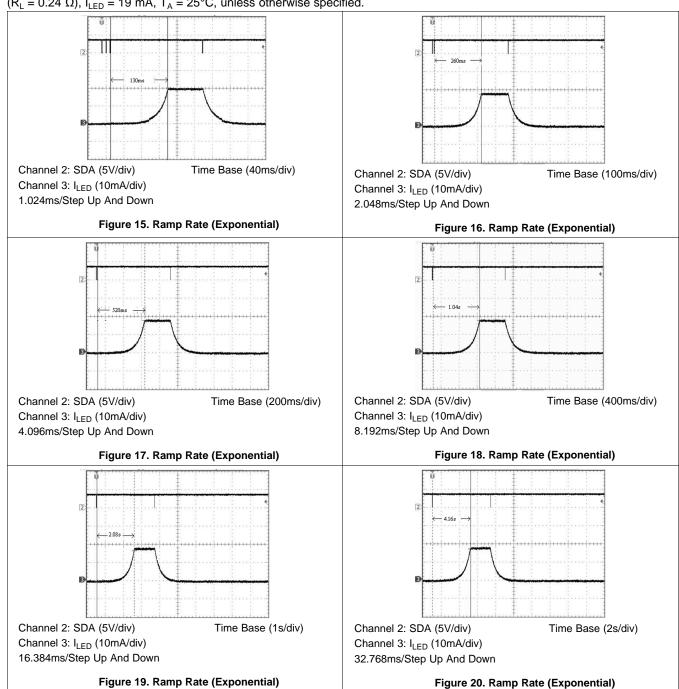

### **Typical Characteristics (continued)**

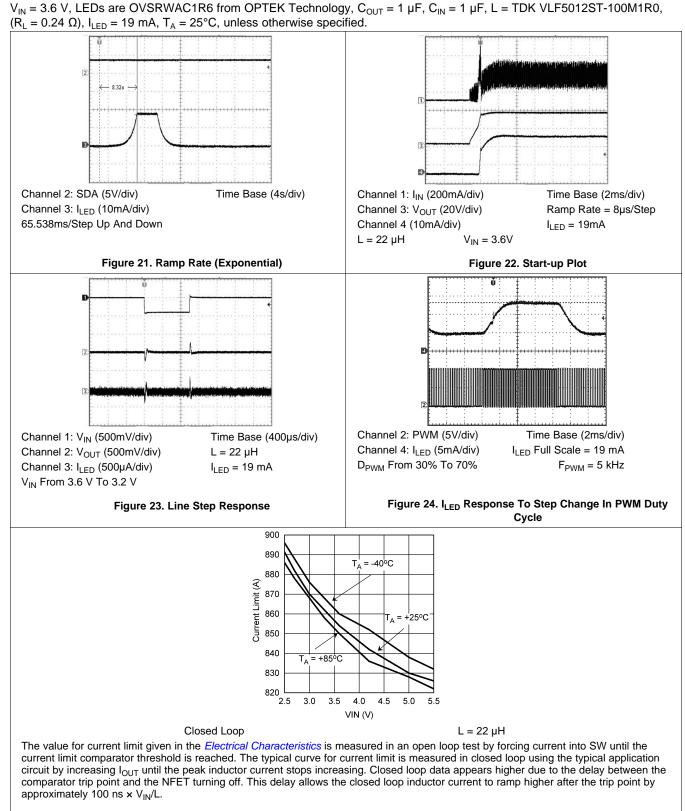

$V_{IN}$  = 3.6 V, LEDs are OVSRWAC1R6 from OPTEK Technology,  $C_{OUT}$  = 1 µF,  $C_{IN}$  = 1 µF, L = TDK VLF5012ST-100M1R0, (R<sub>L</sub> = 0.24 Ω), I<sub>LED</sub> = 19 mA, T<sub>A</sub> = 25°C, unless otherwise specified.

# **Typical Characteristics (continued)**

#### Figure 25. Current Limit vs VIN

## 8 Detailed Description

### 8.1 Overview

The LM3530 utilizes an asynchronous step-up, current mode, PWM controller and regulated current sink to provide an efficient and accurate LED current for white LED bias. The device powers a single series string of LEDs with output voltages of up to 40 V and a peak inductor current of typically 839 mA. The input active voltage range is from 2.7 V to 5.5 V.

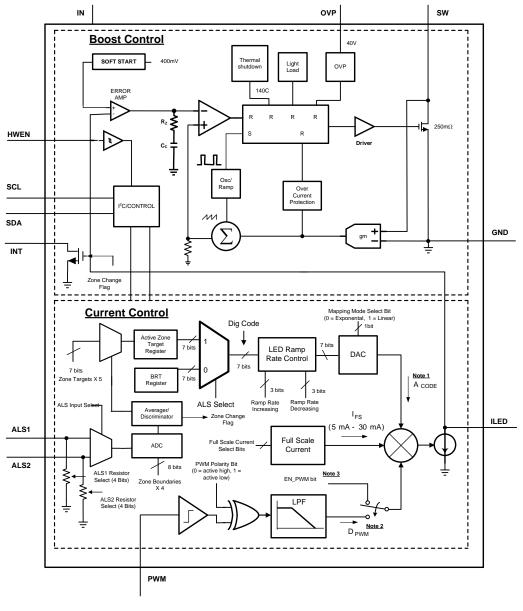

### 8.2 Functional Block Diagram

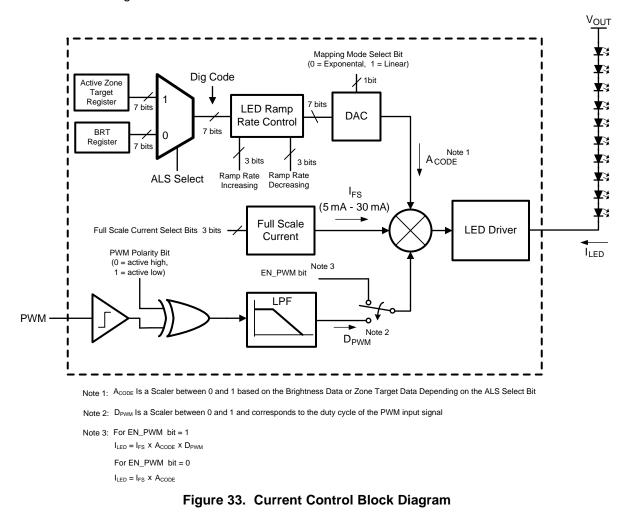

Note 1: A<sub>CODE</sub> Is a Scaler between 0 and 1 based on the Brightness Data or Zone Target Data Depending on the ALS Select Bit

Note 2: D<sub>PWM</sub> Is a Scaler between 0 and 1 and corresponds to the duty cycle of the PWM input signal

```

Note 3: For EN_PWM bit = 1

I_{LED} = I_{FS} \times A_{CODE} \times D_{PWM}

For EN_PWM bit = 0

I_{LED} = I_{FS} \times A_{CODE}

```

### 8.3 Feature Description

### 8.3.1 Start-Up

An internal soft-start prevents large inrush currents during start-up that can cause excessive current spikes at the input. For the typical application circuit (using a 10- $\mu$ H inductor, a 2.2- $\mu$ F input capacitor, and a 1- $\mu$ F output capacitor) the average input current during start-up ramps from 0 to 300 mA in 3 ms. See Figure 22 in the *Typical Characteristics*.

### 8.3.2 Light Load Operation

The LM3530 boost converter operates in three modes: continuous conduction, discontinuous conduction, and skip mode. Under heavy loads when the inductor current does not reach zero before the end of the switching period, the device switches at a constant frequency (500 kHz typical). As the output current decreases and the inductor current reaches zero before the end of the switching period, the device operates in discontinuous conduction. At very light loads the LM3530 will enter skip mode operation causing the switching period to lengthen and the device to only switch as required to maintain regulation at the output. Light load operation provides for improved efficiency at lighter LED currents compared to continuous and discontinuous conduction. This is due to the pulsed frequency operation resulting in decreased switching losses in the boost converter.

### 8.3.3 Ambient Light Sensor

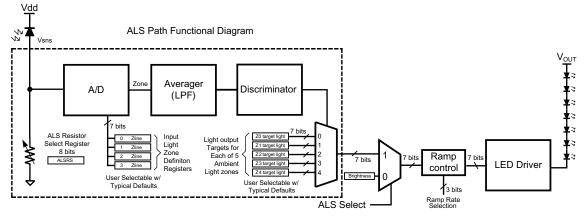

The LM3530 incorporates a dual input Ambient Light Sensing interface (ALS1 and ALS2) which translates an analog output ambient light sensor to a user-specified brightness level. The ambient light sensing circuit has 4 programmable boundaries (ZB0 – ZB3) which define 5 ambient brightness zones. Each ambient brightness zone corresponds to a programmable brightness threshold (Z0T – Z4T). The ALS interface is programmable to accept the ambient light information from either the highest voltage of ALS1 or ALS2, the average voltage of ALS1 or ALS2, or selectable from either ALS1 or ALS2.

Furthermore, each ambient light sensing input (ALS1 or ALS2) features 15 internal software selectable voltage setting resistors. This allows the LM3530 the capability of interfacing with a wide selection of ambient light sensors. Additionally, the ALS inputs can be configured as high impedance, thus providing for a true shutdown during low power modes. The ALS resistors are selectable through the ALS Resistor Select Register (see Table 9). Figure 26 shows a functional block diagram of the ambient light sensor input. VSNS represents the active input as described in Table 6 bits [6:5].

Figure 26. Ambient Light Sensor Functional Block Diagram

### Feature Description (continued)

### 8.3.4 ALS Operation

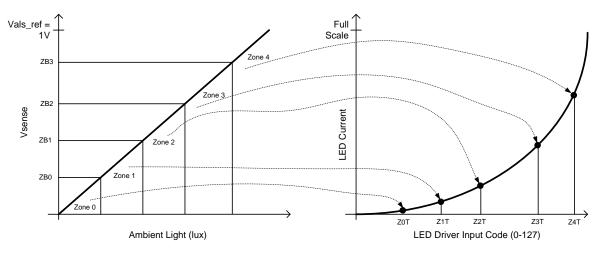

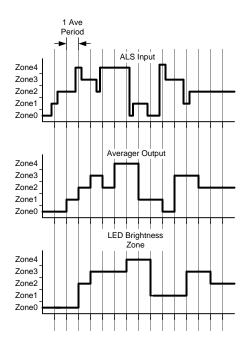

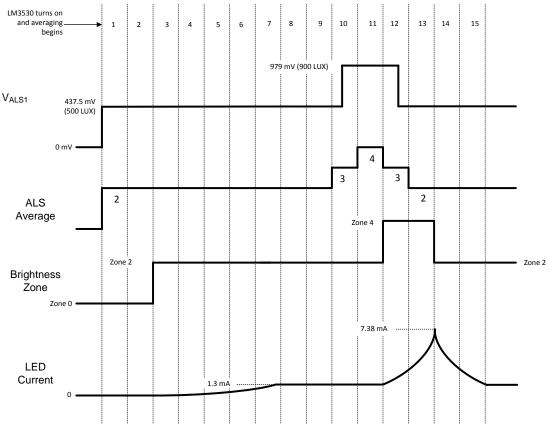

The ambient light sensor input has a 0-V to 1-V operational input voltage range. *LM3530 Typical Application* shows the LM3530 with dual ambient light sensors (AVAGO, APDS-9005) and the internal ALS Resistor Select Register set to 0x44 (2.27 k $\Omega$ ). This circuit converts 0 to 1000 LUX light into approximately a 0-mV to 850-mV linear output voltage. The voltage at the active ambient light sensor input (ALS1 or ALS2) is compared against the 8 bit values programmed into the Zone Boundary Registers (ZB0-ZB3). When the ambient light sensor output crosses one of the ZB0 – ZB3 programmed thresholds the internal ALS circuitry will smoothly transition the LED current to the new 7 bit brightness level as programmed into the appropriate Zone Target Register (Z0T – Z4T) (see Figure 27).

The ALS Configuration Register bits [6:5] programs which input is the active input, bits [4:3] control the on/off state of the ALS circuitry, and bits [2:0] control the ALS input averaging time. Additionally, the ALS Information Register is a read-only register which contains a flag (bit 3) which is set each time the active ALS input changes to a new zone. This flag is reset when the register is read back. Bits [2:0] of this register contain the current active zone information.

Figure 27. Ambient Light Input To Backlight Mapping

### 8.3.5 ALS Averaging Time

The ALS Averaging Time is the time over which the Averager block collects samples from the A/D converter and then averages them to pass to the discriminator block (see Figure 26). Ambient light sensor samples are averaged and then further processed by the discriminator block to provide rejection of noise and transient signals. The averager is configurable with 8 different averaging times to provide varying amounts of noise and transient rejection (see Table 5). The discriminator block algorithm has a maximum latency of two averaging cycles; therefore, the averaging time selection determines the amount of delay that will exist between a steady-state change in the ambient light conditions and the associated change of the backlight illumination. For example, the A/D converter samples the ALS inputs at 16 kHz. If the averaging time is set to 1024 ms then the Averager will send the updated zone information to the discriminator every 1024 ms. This zone information contains the average of 16384 samples (1024 ms  $\times$  16 kHz). Due to the latency of 2 averaging cycles, the LED current will not change until there has been a steady-state change in the ambient light for at least 2 averaging periods.

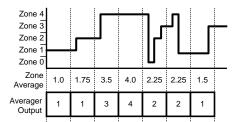

### 8.3.5.1 Averager Operation

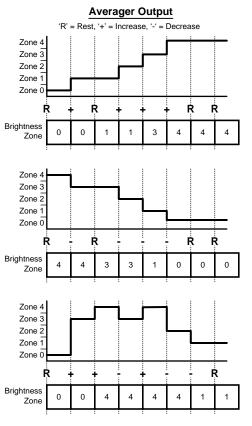

The magnitude and direction (either increasing or decreasing) of the Averager output is used to determine whether the LM3530 should change brightness zones. The Averager block functions as follows:

1. First, the Averager always begins with a Zone 0 reading stored at start-up. If the main display LEDs are active before the ALS block is enabled, it is recommended that the ALS Enable 1 bit is set to '1' at least 3 averaging periods before the ALS Enable 2 bit is set.

Copyright © 2009–2014, Texas Instruments Incorporated

### Feature Description (continued)

- 2. The Averager will always round down to the lower zone in the event of a non-integer zone average. For example, if during an averaging period the ALS input transitions between zones 1 and 2 resulting in an averager output of 1.75, then the averager output will round down to 1 (see Figure 28).

- 3. The two most current averaging samples are used to make zone change decisions.

- 4. To make a zone change, data from three averaging cycles are needed. (Starting Value, First Transition, Second Transition or Rest).

- 5. To Increase the brightness zone, the Averager output must have increased for at least 2 averaging periods or increased and remained at the new level for at least two averaging periods ('+' to '+' or '+' to 'Rest' in Figure 29).

- To decrease the brightness zone, the Averager output must have decreased for at least 2 averaging periods or decreased and remained at the new level for at least two averaging periods ('-' to '-' or '-' to 'Rest' in Figure 29).

In the case of two consecutive increases or decreases in the Averager output, the LM3530 will transition to zone equal to the last averager output (Figure 29).

Using the diagram for the ALS block (Figure 26), the flow of information is shown in (Figure 30). This starts with the ALS input into the A/D, into the Averager, and then into the Discriminator. Each state filters the previous output to help prevent unwanted zone to zone transitions.

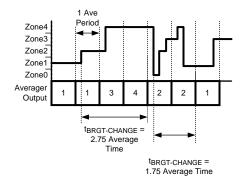

When using the ALS averaging function, it is important to remember that the averaging cycle is free running and is not synchronized with changing ambient lighting conditions. Due to the nature of the averager round down, an increase in brightness can take between 2 and 3 averaging cycles to change zones, while a decrease in brightness can take between 1 and 2 averaging cycles. See Table 6 for a list of possible Averager periods. Figure 31 shows an example of how the perceived brightness change time can vary.

Figure 28. Averager Calculation

Figure 29. Brightness Zone Change Examples

Figure 30. Ambient Light Input To Backlight Transition

Figure 31. Perceived Brightness Change Time

### 8.3.6 Zone Boundary Settings

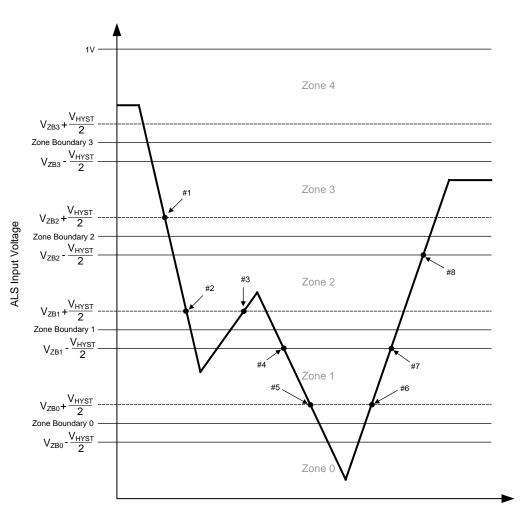

Registers 0x60, 0x61, 0x62, and 0x63 set the 4 zone boundaries (thresholds) for the ALS inputs. These 4 zone boundaries create 5 brightness zones which map over to 5 separate brightness zone targets (see Figure 27). Each 8-bit zone boundary register can set a threshold from typically 0 to 1 V with linear step sizes of approximately 1/255 = 3.92 mV. Additionally, each zone boundary has built in hysteresis which can be either lower or higher then the programmed Zone Boundary depending on the last direction (either up or down) of the ALS input voltage.

### 8.3.7 Zone Boundary Trip Points and Hysteresis

For each zone boundary setting, the trip point will vary above or below the nominal set point depending on the direction (either up or down) of the ALS input voltage. This is designed to keep the ALS input from oscillating back and forth between zones in the event that the ALS voltage is residing near to the programmed zone boundary threshold. The Zone Boundary Hysteresis will follow these 2 rules:

- If the last zone transition was from low to high, then the trip point (V<sub>TRIP</sub>) will be V<sub>ZONE\_BOUNDARY</sub> V<sub>HYST</sub>/2, where V<sub>ZONE\_BOUNDARY</sub> is the zone boundary set point as programmed into the Zone Boundary registers, and V<sub>HYST</sub> is typically 7 mV.

- 2. If the last zone transition was from high to low then the trip point ( $V_{TRIP}$ ) will be  $V_{ZONE BOUNDARY} + V_{HYST}/2$ .

Figure 32 details how the LM3530 ALS Input Zone Boundary Thresholds vary depending on the direction of the ALS input voltage.

Referring to Figure 32, each numbered trip point shown is determined from the direction of the previous ALS zone transition.

TEXAS INSTRUMENTS

www.ti.com

Figure 32. Zone Boundaries With Hysteresis

### 8.3.8 Minimum Zone Boundary Settings

The actual minimum zone boundary setting is code 0x03. Codes of 0x00, 0x01, and 0x02 are all mapped to code 0x03. Table 1 shows the Zone Boundary codes 0x00 through 0x04, the typical thresholds, and the high and low hysteresis values. The remapping of codes 0x00 - 0x02 plus the additional 4mV of offset voltage is necessary to prevent random offsets and noise on the ALS inputs from creating threshold levels that are below GND. This essentially guarantees that any Zone Boundary threshold selected is achievable with positive ALS voltages.

| Table 1. Ideal Zone Boundary | Settings with Hysteresis (Logical Setting) | ower 5 Codes) |

|------------------------------|--------------------------------------------|---------------|

|------------------------------|--------------------------------------------|---------------|

|                    | =                                       |                                        |                                        |

|--------------------|-----------------------------------------|----------------------------------------|----------------------------------------|

| ZONE BOUNDARY CODE | TYPICAL ZONE BOUNDARY<br>THRESHOLD (mV) | TYPICAL THRESHOLD +<br>HYSTERESIS (mV) | TYPICAL THRESHOLD -<br>HYSTERESIS (mV) |

| 0x00               | 15.8                                    | 19.3                                   | 12.3                                   |

| 0x01               | 15.8                                    | 19.3                                   | 12.3                                   |

| 0x02               | 15.8                                    | 19.3                                   | 12.3                                   |

| 0x03               | 15.8                                    | 19.3                                   | 12.3                                   |

| 0x04               | 19.7                                    | 23.2                                   | 16.2                                   |

### 8.3.9 LED Current Control

The LED current is is a function of the Full Scale Current, the Brightness Code, and the PWM input duty cycle. The Brightness Code can either come from the BRT Register (0xA0) in I<sup>2</sup>C-Compatible Current Control, or from the ALS Zone Target Registers (Address 0x70-0x74) in Ambient Light Current Control. Figure 33 shows the current control block diagram.

### 8.3.10 Exponential or Linear Brightness Mapping Modes

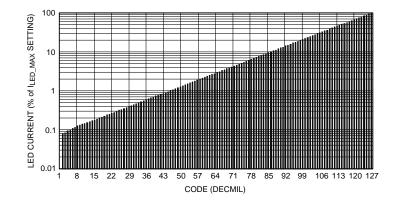

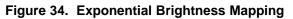

With bit [1] of the General Configuration Register set to 0 (default) exponential mapping is selected and the code in the Brightness Control Register corresponds to the Full-Scale LED current percentages in Table 2 and Figure 34. With bit [1] set to 1 linear mapping is selected and the code in the Brightness Control Register corresponds to the Full-Scale LED current percentages in Table 3 and Figure 35.

### 8.3.11 PWM Input Polarity

Bit [6] of the General Configuration Register controls the PWM input polarity. Setting this bit to 0 (default) selects positive polarity and makes the LED current (with PWM mode enabled) a function of the positive duty cycle at PWM. With this bit set to '0' the LED current (with PWM mode enabled) becomes a function of the negative duty cycle at PWM.

The PWM input is a logic level input with a frequency range of 400 Hz to 50 kHz. Internal filtering of the PWM input signal converts the duty cycle information to an average (analog) control signal which directly controls the LED current.

Copyright © 2009–2014, Texas Instruments Incorporated

# Example: PWM + $l^2$ C-Compatible Current Control:

As an example, assume the General Configuration Register is loaded with (0x2D). From Table 5, this sets up the LM3530 with:

Simple Enable OFF (bit 7 = 0)

Positive PWM Polarity (bit 6 = 0)

PWM Enabled (bit 5 = 1)

Full-Scale Current set at 15.5 mA (bits [4:2] = 100)

Brightness Mapping set for Exponential (bit 1 = 0)

Device Enabled via  $I^2C$  (bit 0 = 1)

Next, the Brightness Control Register is loaded with 0x73. This sets the LED current to 51.406% of full scale (see Equation 1). Finally, the PWM input is driven with a 0-V to 2-V pulse waveform at 70% duty cycle. The LED current under these conditions will be:

$I_{LED} = I_{LED_{FS}} \times BRT \times D = 15.5 \text{ mA} \times 51.4\% \times 70\% \approx 5.58 \text{ mA}.$

where

• BRT is the percentage of I<sub>LED\_FS</sub> as set in the Brightness Control Register

## 8.3.12 I<sup>2</sup>C-Compatible Current Control Only

$I^2$ C-Compatible Control is enabled by writing a '1' to the  $I^2$ C Device Enable bit (bit [0] of the General Configuration Register), a '0' to the Simple Enable bit (bit 7), and a '0' to the PWM Enable bit (bit 5). With bit 5 = 0, the duty cycle information at the PWM input is not used in setting the LED current.

In this mode the LED current is a function of the Full-Scale LED current bits (bits [4:2] of the General Configuration Register) and the code in the Brightness Control Register. The LED current mapping for the Brightness Control Register can be linear or exponential depending on bit [1] in the General Configuration Register (see *Exponential or Linear Brightness Mapping Modes* section). Using I<sup>2</sup>C-Compatible Control Only, the Full-Scale LED Current bits and the Brightness Control Register code provides nearly 1016 possible current levels selectable over the I<sup>2</sup>C-compatible interface.

Example: I<sup>2</sup>C-Compatible Current Control Only.

As an example, assume the General Configuration Register is loaded with 0x15. From Table 5 this sets up the LM3530 with:

Simple Enable OFF (bit 7 = 0)

Positive PWM Polarity (bit 6 = 0)

PWM Disabled (bit 5 = 0)

Full-Scale Current set at 22.5mA (bits [4:2] = 101)

Brightness Mapping set for Exponential (bit 1 = 0)

Device Enabled via  $I^2C$  (bit 0 = 1)

The Brightness Control Register is then loaded with 0x72 (48.438% of full-scale current from Equation 2). The LED current with this configuration becomes:

$I_{LED} = I_{LED_{FS}} \times BRT = 22.5 \text{ mA x } 0.48438 \approx 10.9 \text{ mA}.$

where

18

BRT is the % of I<sub>LED\_FS</sub> as set in the Brightness Control Register.

Next, the brightness mapping is set to linear mapping mode (bit [1] in General Configuration Register set to 1). Using the same Full-Scale current settings and Brightness Control Register settings as before, the LED current becomes:

$I_{LED} = I_{LED_{FS}} \times BRT = 22.5 \text{ mA x } 0.8976 \approx 20.2 \text{ mA}.$

Which is higher now since the code in the Brightness Control Register (0x72) corresponds to 89.76% of Full-Scale LED Current due to the different mapping mode given in Figure 34.

(1)

NSTRUMENTS

FXAS

(2)

(3)

Copyright © 2009–2014, Texas Instruments Incorporated

|                   | Table 2. I <sub>LED</sub> vs. Brightness Register Data (Exponential Mapping) |                |                                |                   |                                |                      |                                |  |  |  |

|-------------------|------------------------------------------------------------------------------|----------------|--------------------------------|-------------------|--------------------------------|----------------------|--------------------------------|--|--|--|

| BRT DATA<br>(HEX) | % FULL-SCALE<br>CURRENT                                                      | BRT DATA (HEX) | % OF FULL-<br>SCALE<br>CURRENT | BRT DATA<br>(HEX) | % OF FULL-<br>SCALE<br>CURRENT | BRT<br>DATA<br>(HEX) | % OF FULL-<br>SCALE<br>CURRENT |  |  |  |

| 0x00              | 0.00%                                                                        | 0x20           | 0.500%                         | 0x40              | 2.953%                         | 0x60                 | 17.813%                        |  |  |  |

| 0x01              | 0.080%                                                                       | 0x21           | 0.523%                         | 0x41              | 3.125%                         | 0x61                 | 18.750%                        |  |  |  |

| 0x02              | 0.086%                                                                       | 0x22           | 0.555%                         | 0x42              | 3.336%                         | 0x62                 | 19.922%                        |  |  |  |

| 0x03              | 0.094%                                                                       | 0x23           | 0.586%                         | 0x43              | 3.500%                         | 0x63                 | 20.859%                        |  |  |  |

| 0x04              | 0.102%                                                                       | 0x24           | 0.617%                         | 0x44              | 3.719%                         | 0x64                 | 22.266%                        |  |  |  |

| 0x05              | 0.109%                                                                       | 0x25           | 0.656%                         | 0x45              | 3.906%                         | 0x65                 | 23.438%                        |  |  |  |

| 0x06              | 0.117%                                                                       | 0x26           | 0.695%                         | 0x46              | 4.141%                         | 0x66                 | 24.844%                        |  |  |  |

| 0x07              | 0.125%                                                                       | 0x27           | 0.734%                         | 0x47              | 4.375%                         | 0x67                 | 26.250%                        |  |  |  |

| 0x08              | 0.133%                                                                       | 0x28           | 0.773%                         | 0x48              | 4.648%                         | 0x68                 | 27.656%                        |  |  |  |

| 0x09              | 0.141%                                                                       | 0x29           | 0.820%                         | 0x49              | 4.922%                         | 0x69                 | 29.297%                        |  |  |  |

| 0x0A              | 0.148%                                                                       | 0x2A           | 0.867%                         | 0x4A              | 5.195%                         | 0x6A                 | 31.172%                        |  |  |  |

| 0x0B              | 0.156%                                                                       | 0x2B           | 0.914%                         | 0x4B              | 5.469%                         | 0x6B                 | 32.813%                        |  |  |  |

| 0x0C              | 0.164%                                                                       | 0x2C           | 0.969%                         | 0x4C              | 5.781%                         | 0x6C                 | 34.453%                        |  |  |  |

| 0x0D              | 0.172%                                                                       | 0x2D           | 1.031%                         | 0x4D              | 6.125%                         | 0x6D                 | 35.547%                        |  |  |  |

| 0x0E              | 0.180%                                                                       | 0x2E           | 1.078%                         | 0x4E              | 6.484%                         | 0x6E                 | 38.828%                        |  |  |  |

| 0x0F              | 0.188%                                                                       | 0x2F           | 1.148%                         | 0x4F              | 6.875%                         | 0x6F                 | 41.016%                        |  |  |  |

| 0x10              | 0.203%                                                                       | 0x30           | 1.219%                         | 0x50              | 7.266%                         | 0x70                 | 43.203%                        |  |  |  |

| 0x11              | 0.211%                                                                       | 0x31           | 1.281%                         | 0x51              | 7.656%                         | 0x71                 | 45.938%                        |  |  |  |

| 0x12              | 0.227%                                                                       | 0x32           | 1.359%                         | 0x52              | 8.047%                         | 0x72                 | 48.438%                        |  |  |  |

| 0x13              | 0.242%                                                                       | 0x33           | 1.430%                         | 0x53              | 8.594%                         | 0x73                 | 51.406%                        |  |  |  |

| 0x14              | 0.250%                                                                       | 0x34           | 1.523%                         | 0x54              | 9.063%                         | 0x74                 | 54.141%                        |  |  |  |

| 0x15              | 0.266%                                                                       | 0x35           | 1.594%                         | 0x55              | 9.609%                         | 0x75                 | 57.031%                        |  |  |  |

| 0x16              | 0.281%                                                                       | 0x36           | 1.688%                         | 0x56              | 10.078%                        | 0x76                 | 60.703%                        |  |  |  |

| 0x17              | 0.297%                                                                       | 0x37           | 1.781%                         | 0x57              | 10.781%                        | 0x77                 | 63.984%                        |  |  |  |

| 0x18              | 0.320%                                                                       | 0x38           | 1.898%                         | 0x58              | 11.250%                        | 0x78                 | 67.813%                        |  |  |  |

| 0x19              | 0.336%                                                                       | 0x39           | 2.016%                         | 0x59              | 11.953%                        | 0x79                 | 71.875%                        |  |  |  |

| 0x1A              | 0.352%                                                                       | 0x3A           | 2.109%                         | 0x5A              | 12.656%                        | 0x7A                 | 75.781%                        |  |  |  |

| 0x1B              | 0.375%                                                                       | 0x3B           | 2.250%                         | 0x5B              | 13.359%                        | 0x7B                 | 79.688%                        |  |  |  |

| 0x1C              | 0.398%                                                                       | 0x3C           | 2.367%                         | 0x5C              | 14.219%                        | 0x7C                 | 84.375%                        |  |  |  |

|                   |                                                                              |                |                                |                   |                                |                      |                                |  |  |  |

| Table 2 | I VS    | <b>Brightness</b> | Register | Data | (Exponential Mapping) |   |

|---------|---------|-------------------|----------|------|-----------------------|---|

|         | IFD V3. | Dirgininess       | Negister | Data | (Exponential mapping) | 1 |

Copyright © 2009–2014, Texas Instruments Incorporated

| BRT DATA<br>(HEX) | % FULL-SCALE<br>CURRENT | BRT DATA (HEX) | % OF FULL-<br>SCALE<br>CURRENT | BRT DATA<br>(HEX) | % OF FULL-<br>SCALE<br>CURRENT | BRT<br>DATA<br>(HEX) | % OF FULL-<br>SCALE<br>CURRENT |

|-------------------|-------------------------|----------------|--------------------------------|-------------------|--------------------------------|----------------------|--------------------------------|

| 0x1D              | 0.422%                  | 0x3D           | 2.508%                         | 0x5D              | 15.000%                        | 0x7D                 | 89.844%                        |

| 0x1E              | 0.445%                  | 0x3E           | 2.648%                         | 0x5E              | 15.859%                        | 0x7E                 | 94.531%                        |

| 0x1F              | 0.469%                  | 0x3F           | 2.789%                         | 0x5F              | 16.875%                        | 0x7F                 | 100.00%                        |

Table 2. I<sub>LED</sub> vs. Brightness Register Data (Exponential Mapping) (continued)

Figure 35. Linear Brightness Mapping

|                   | Table 3. ILED VS. DIGITIESS Register Data (Linear Mapping) |                   |                                            |                   |                                                       |                |                                     |  |  |  |

|-------------------|------------------------------------------------------------|-------------------|--------------------------------------------|-------------------|-------------------------------------------------------|----------------|-------------------------------------|--|--|--|

| BRT DATA<br>(HEX) | % FULL-<br>SCALE<br>CURREN<br>T<br>(LINEAR)                | BRT DATA<br>(HEX) | % OF FULL-<br>SCALE<br>CURRENT<br>(LINEAR) | BRT DATA<br>(HEX) | % OF<br>FULL-<br>SCALE<br>CURRE<br>NT<br>(LINEA<br>R) | BRT DATA (HEX) | % OF FULL-SCALE<br>CURRENT (LINEAR) |  |  |  |

| 0x00              | 0.00%                                                      | 0x20              | 25.79%                                     | 0x40              | 50.78%                                                | 0x60           | 75.78%                              |  |  |  |

| 0x01              | 1.57%                                                      | 0x21              | 26.57%                                     | 0x41              | 51.57%                                                | 0x61           | 76.56%                              |  |  |  |

| 0x02              | 2.35%                                                      | 0x22              | 27.35%                                     | 0x42              | 52.35%                                                | 0x62           | 77.35%                              |  |  |  |

| 0x03              | 3.13%                                                      | 0x23              | 28.13%                                     | 0x43              | 53.13%                                                | 0x63           | 78.13%                              |  |  |  |

| 0x04              | 3.91%                                                      | 0x24              | 28.91%                                     | 0x44              | 53.91%                                                | 0x64           | 78.91%                              |  |  |  |

| 0x05              | 4.69%                                                      | 0x25              | 29.69%                                     | 0x45              | 54.69%                                                | 0x65           | 79.69%                              |  |  |  |

| 0x06              | 5.48%                                                      | 0x26              | 30.47%                                     | 0x46              | 55.47%                                                | 0x66           | 80.47%                              |  |  |  |

| 0x07              | 6.26%                                                      | 0x27              | 31.25%                                     | 0x47              | 56.25%                                                | 0x67           | 81.25%                              |  |  |  |

| 0x08              | 7.04%                                                      | 0x28              | 32.04%                                     | 0x48              | 57.03%                                                | 0x68           | 82.03%                              |  |  |  |

| 0x09              | 7.82%                                                      | 0x29              | 32.82%                                     | 0x49              | 57.82%                                                | 0x69           | 82.81%                              |  |  |  |

| 0x0A              | 8.60%                                                      | 0x2A              | 33.60%                                     | 0x4A              | 58.60%                                                | 0x6A           | 83.59%                              |  |  |  |

| 0x0B              | 9.38%                                                      | 0x2B              | 34.38%                                     | 0x4B              | 59.38%                                                | 0x6B           | 84.38%                              |  |  |  |

| 0x0C              | 10.16%                                                     | 0x2C              | 35.16%                                     | 0x4C              | 60.16%                                                | 0x6C           | 85.16%                              |  |  |  |

| 0x0D              | 10.94%                                                     | 0x2D              | 35.94%                                     | 0x4D              | 60.94%                                                | 0x6D           | 85.94%                              |  |  |  |

| 0x0E              | 11.72%                                                     | 0x2E              | 36.72%                                     | 0x4E              | 61.72%                                                | 0x6E           | 86.72%                              |  |  |  |

| 0x0F              | 12.51%                                                     | 0x2F              | 37.50%                                     | 0x4F              | 62.50%                                                | 0x6F           | 87.50%                              |  |  |  |

| 0x10              | 13.29%                                                     | 0x30              | 38.29%                                     | 0x50              | 63.28%                                                | 0x70           | 88.28%                              |  |  |  |

| 0x11              | 14.07%                                                     | 0x31              | 39.07%                                     | 0x51              | 64.06%                                                | 0x71           | 89.06%                              |  |  |  |

| 0x12              | 14.85%                                                     | 0x32              | 39.85%                                     | 0x52              | 64.85%                                                | 0x72           | 89.84%                              |  |  |  |

| 0x10<br>0x11      | 13.29%<br>14.07%                                           | 0x30<br>0x31      | 38.29%<br>39.07%                           | 0x50<br>0x51      | 63.28%<br>64.06%                                      | 0x70<br>0x71   | 88.28%<br>89.06%                    |  |  |  |

Table 3. ILED vs. Brightness Register Data (Linear Mapping)

| BRT DATA<br>(HEX) | % FULL-<br>SCALE<br>CURREN<br>T<br>(LINEAR) | BRT DATA<br>(HEX) | % OF FULL-<br>SCALE<br>CURRENT<br>(LINEAR) | BRT DATA<br>(HEX) | % OF<br>FULL-<br>SCALE<br>CURRE<br>NT<br>(LINEA<br>R) | BRT DATA (HEX) | % OF FULL-SCALE<br>CURRENT (LINEAR) |  |  |

|-------------------|---------------------------------------------|-------------------|--------------------------------------------|-------------------|-------------------------------------------------------|----------------|-------------------------------------|--|--|

| 0x13              | 15.63%                                      | 0x33              | 40.63%                                     | 0x53              | 65.63%                                                | 0x73           | 90.63%                              |  |  |

| 0x14              | 16.41%                                      | 0x34              | 41.41%                                     | 0x54              | 66.41%                                                | 0x74           | 91.41%                              |  |  |

| 0x15              | 17.19%                                      | 0x35              | 42.19%                                     | 0x55              | 67.19%                                                | 0x75           | 92.19%                              |  |  |

| 0x16              | 17.97%                                      | 0x36              | 42.97%                                     | 0x56              | 67.97%                                                | 0x76           | 92.97%                              |  |  |

| 0x17              | 18.76%                                      | 0x37              | 43.75%                                     | 0x57              | 68.75%                                                | 0x77           | 93.75%                              |  |  |

| 0x18              | 19.54%                                      | 0x38              | 44.53%                                     | 0x58              | 69.53%                                                | 0x78           | 94.53%                              |  |  |

| 0x19              | 20.32%                                      | 0x39              | 45.32%                                     | 0x59              | 70.39%                                                | 0x79           | 95.31%                              |  |  |

| 0x1A              | 21.10%                                      | 0x3A              | 46.10%                                     | 0x5A              | 71.10%                                                | 0x7A           | 96.09%                              |  |  |

| 0x1B              | 21.88%                                      | 0x3B              | 46.88%                                     | 0x5B              | 71.88%                                                | 0x7B           | 96.88%                              |  |  |

| 0x1C              | 22.66%                                      | 0x3C              | 47.66%                                     | 0x5C              | 72.66%                                                | 0x7C           | 97.66%                              |  |  |

| 0x1D              | 23.44%                                      | 0x3D              | 48.44%                                     | 0x5D              | 73.44%                                                | 0x7D           | 98.44%                              |  |  |

| 0x1E              | 24.22%                                      | 0x3E              | 49.22%                                     | 0x5E              | 74.22%                                                | 0x7E           | 99.22%                              |  |  |

| 0x1F              | 25.00%                                      | 0x3F              | 50.00%                                     | 0x5F              | 75.00%                                                | 0x7F           | 100.00%                             |  |  |

### Table 3. ILED vs. Brightness Register Data (Linear Mapping) (continued)

### NOTE

When determining the LED current from (Table 2 and Table 3) there is a typical offset of 113  $\mu$ A with a ±300- $\mu$ A variation that must be added to the calculated value for codes 0x0A and below. For example, in linear mode with I<sub>FULL\_SCALE</sub> = 19 mA and brightness code 0x09 chosen, the nominal current setting is 0.0782 × 19 mA = 1.4858 mA. Adding in the 113- $\mu$ A typical offset gives 1.4858 mA + 0.113 mA = 1.5988 mA. With the typical ±300- $\mu$ A range, the high and low currents can be I<sub>LOW</sub> = 1.2988 mA, I<sub>HIGH</sub> = 1.8988 mA. For exponential mode with codes 0x0A and below, this offset and variation error gets divided down by 10 (11.3  $\mu$ A offset with ±30- $\mu$ A typical range).

### 8.3.13 Simple Enable Disable With PWM Current Control

With bits [7 and 5] of the General Configuration Register set to '1' the PWM input is enabled as a simple enable/disable. The simple enable/disable feature operates as described in Figure 36. In this mode, when the PWM input is held high (PWM Polarity bit = 0) for > 2 ms the LM3530 will turn on the LED current at the programmed Full-Scale Current  $\times$  % of Full-Scale Current as set by the code in the Brightness Control Register. When the PWM input is held low for > 2 ms the device will shut down. With the PWM Polarity bit = 1 the PWM input is configured for active low operation. In this configuration holding PWM low for > 2 ms will turn on the device at the programmed Full-Scale Current  $\times$  % of Full-Scale Current as set by the code in the Brightness Control Register. Control Register. Likewise, holding PWM high for > 2 ms will put the device in shutdown.

Driving the PWM input with a pulsed waveform at a variable duty cycle is also possible in simple enable/Disable mode, so long as the low pulse width is < 2 ms. When a PWM signal is used in this mode the input duty cycle information is internally filtered, and an analog voltage is used to control the LED current. This type of PWM control (PWM to Analog current control) prevents large voltage excursions across the output capacitor that can result in audible noise. Simple Enable/Disable mode can be useful since the default bit setting for the General Configuration Register is 0xCC (Simple Enable bit = 1, PWM Enable = 1, and Full-Scale Current = 19mA). Additionally, the default Brightness Register setting is 0x7F (100% of Full-Scale current). This gives the LM3530 the ability to turn on after power up (or after reset) without having to do any writes to the  $l^2$ C-compatible bus.

(5)

(6)

INSTRUMENTS

Texas

Figure 36. Simple Enable/Disable Timing

Example: Simple Enable Disable with PWM Current Control):

As an example, assume that the HWEN input is toggled low then high. This resets the LM3530 and sets all the registers to their default value. When the PWM input is then pulled high for > 2 ms the LED current becomes:  $I_{LED} = I_{LED FS} \times BRT \times D = 19 \text{ mA} \times 1.00 \times 100\% \approx 19 \text{ mA}.$

where

• BRT is the % of I<sub>LED\_FS</sub> as set in the Brightness Control Register. (4)

If then the PWM input is fed with a 5-kHz pulsed waveform at 40% duty cycle the LED current becomes:

$I_{LED} = I_{LED_{FS}} \times BRT \times D = 19 \text{ mA} \times 1.00 \times 0.4 \approx 7.6 \text{ mA}.$

Then, if the Brightness Control Register is loaded with 0x55 (9.6% of Full-Scale Current) the LED current becomes:

$I_{LED} = I_{LED_{FS}} \times BRT \times D = 19 \text{ mA} \times 9.65 \times 0.4 \approx 0.73 \text{ mA}.$

### 8.3.14 Ambient Light Current Control

With bits [4:3] of the ALS Configuration Register both set to 1, the LM3530 is configured for Ambient Light Current Control. In this mode the ambient light sensing inputs (ALS1, and/or ALS2) monitor the outputs of analog output ambient light sensing photo diodes and adjust the LED current depending on the ambient light. The ambient light sensing circuit has 4 configurable Ambient Light Boundaries (ZB0 – ZB3) programmed through the four (8-bit) Zone Boundary Registers. These zone boundaries define 5 ambient brightness zones (Figure 27). Each zone corresponds to a programmable brightness setting which is programmable through the 5 Zone Target Registers (Z0T – Z4T). When the ALS1, and/or ALS2 input (depending on the bit settings of the ALS Input Select bits) detects that the ambient light has crossed to a new zone (as defined by one of the Zone Boundary Register which corresponds to the new ambient light brightness zone.

On start-up the 4 Zone Boundary Registers are pre-loaded with 0x33 (51d), 0x66 (102d), 0x99 (153d), and 0xCC (204d). Each ALS input has a 1-V active input voltage range with a 4mV offset voltage which makes the default Zone Boundaries set at:

Zone Boundary  $0 = 1V \times 51/255 + 4 \text{ mV} = 204 \text{ mV}$

Zone Boundary  $1 = 1V \times 102/255 + 4 \text{ mV} = 404 \text{ mV}$

Zone Boundary 2 = 1V × 153/255 + 4 mV = 604 mV

Zone Boundary  $3 = 1V \times 204/255 + 4 \text{ mV} = 804 \text{ mV}$

These Zone Boundary Registers are all 8-bit (readable and writable) registers. The first zone (Z0) is defined between 0 and 204 mV, the Z1 default is defined between 204 mV and 404 mV, the Z2 default is defined between 404 mV and 604 mV, the Z3 default is defined between 604 mV and 804 mV, and the Z4 default is defined between 804 mV and 1.004 V. The default settings for the 5 Zone Target Registers are 0x19, 0x33, 0x4C, 0x66, and 0x7F. This corresponds to LED brightness settings of 0.336%, 1.43%, 5.781%, 24.844%, and 100% of full-scale current respectively (assuming exponential backlight mapping).

Example: Ambient Light Control Current.

As an example, assume that the APDS-9005 is used as the ambient light sensing photo diode with its output connected to the ALS1 input. The ALS Resistor Select Register is loaded with 0x04 which configures the ALS1 input for a 2.27-k $\Omega$  internal pull-down resistor (see Table 9). The APDS-9005 has a typical 400nA/LUX response. With a 2.27-k $\Omega$  resistor the sensor output would see a 0-mV to 908-mV swing with a 0 to 1000 LUX change in ambient light. Next, the ALS Configuration Register is programmed with 0x3C. From Table 6, this configures the LM3530's ambient light sensing interface for:

ALS1 as the active ALS input (bits [6:5] = 01)

Ambient Light Current Control Enabled (bit 4 = 1)

ALS circuitry Enabled (bit 3 = 1)

Sets the ALS Averaging Time to 512 ms (bits [2:0] = 100)

Next, the General Configuration Register is programmed with 0x19 which sets the Full-Scale Current to 26 mA, selects Exponential Brightness Mapping, and enables the device via the I<sup>2</sup>C-compatible interface.

Now assume that the APDS-9005 ambient light sensor detects a 100 LUX ambient light at its input. This forces the ambient light sensors output (and the ALS1 input) to 87.5mV corresponding to Zone 0. Since Zone 0 points to the brightness code programmed in Zone Target Register 0 (loaded with code 0x19), the LED current becomes:

$I_{LED} = I_{LED_FS} \times ZoneTarget0 = 26 \text{ mA} \times 0.336\% \approx 87 \mu \text{A}.$

Where the code in Zone Target Register 0 points to the % of ILED\_FS as given by Table 2 or Table 3, depending on whether Exponential or Linear Mapping are selected.