LM5017 ZHCS812K - JANUARY 2012 - REVISED AUGUST 2021

# LM5017 100V、600mA 恒定导通时间同步降压/Fly-Buck™ 稳压器

### 1 特性

- 7.5V 至 100V 宽输入范围

- 集成式 100V 高侧和低侧开关

- 无需肖特基二极管

- 恒定导通时间控制

- 无需环路补偿

- 超快瞬态响应

- 接近恒定的运行频率

- 智能峰值电流限制

- 可调节输出电压(以 1.225V 为基准电压)

- 精度为 2% 的反馈基准电压

- 频率可调至 1MHz

- 可调欠压锁定 (UVLO)

- 远程关断

- 热关断

- 封装:

- WSON-8

- SO PowerPAD™-8

- 使用 WEBENCH® Power Designer 创建定制稳压器 设计方案

### 2 应用

- 工业可编程逻辑控制器 (PLC)

- 智能电表

- 电信初级侧和次级侧偏置

- 低功耗隔离式直流/直流 (Fly-Buck™)

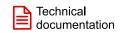

典型同步降压应用电路

### 3 描述

LM5017 是一款 100V、600mA 同步降压稳压器,集成 了高侧和低侧 MOSFET。LM5017 所采用的恒定导通 时间 (COT) 控制方案无需环路补偿,可提供出色的瞬 态响应,并且可实现超高降压比。导通时间与输入电压 成反比,因此在整个输入电压范围内,频率几乎保持恒 定。高压启动稳压器为 IC 的内部运行以及集成栅极驱 动器提供了偏置电源。

峰值电流限制电路可防止出现过载情况。欠压锁定 (UVLO) 电路支持对输入欠压阈值和迟滞进行单独编 程。其他的保护特性包括:热关断和偏置电源欠压锁定 (V<sub>CC</sub> UVLO)<sub>o</sub>

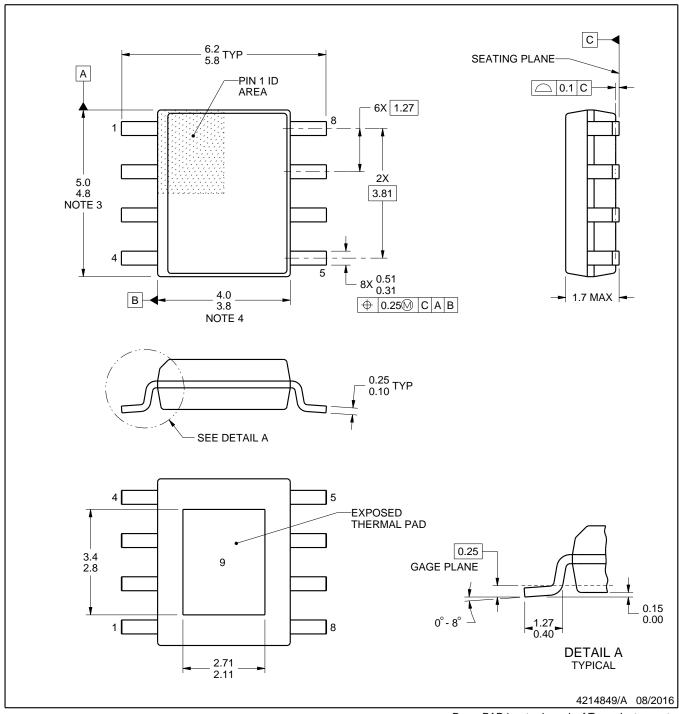

LM5017 器件采用 WSON-8 和 HSOP PowerPAD-8 塑 料封装。

#### 器件信息

|          | FF 11 1A -0-      |                 |  |  |  |  |  |

|----------|-------------------|-----------------|--|--|--|--|--|

| 器件型号     | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |  |  |  |  |  |

| LM5017   | SO PowerPAD (8)   | 4.89mm × 3.90mm |  |  |  |  |  |

| LIVISOTY | WSON (8)          | 4.00mm × 4.00mm |  |  |  |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附

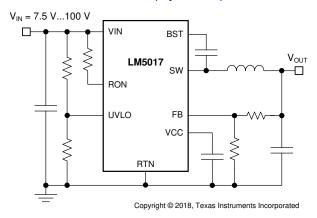

典型 Fly-Buck 应用电路

### **Table of Contents**

| 1 特性                                 | 1 | 8 Application and Implementation        | 15               |

|--------------------------------------|---|-----------------------------------------|------------------|

|                                      |   | 8.1 Application Information             |                  |

| - 二,7-<br>3 描述                       |   | 8.2 Typical Application                 |                  |

| 4 Revision History                   |   | 9 Power Supply Recommendations          | <mark>25</mark>  |

| 5 Pin Configuration and Functions    |   | 10 Layout                               | <mark>2</mark> 6 |

| 6 Specifications                     |   | 10.1 Layout Guidelines                  |                  |

| 6.1 Absolute Maximum Ratings         |   | 10.2 Layout Example                     |                  |

| 6.2 ESD Ratings                      |   | 11 Device and Documentation Support     | <mark>27</mark>  |

| 6.3 Recommended Operating Conditions |   | 11.1 Device Support                     | <mark>27</mark>  |

| 6.4 Thermal Information              |   | 11.2 Documentation Support              |                  |

| 6.5 Electrical Characteristics       |   | 11.3 接收文档更新通知                           |                  |

| 6.6 Timing Requirements              |   | 11.4 支持资源                               | 28               |

| 6.7 Typical Characteristics          |   | 11.5 Trademarks                         |                  |

| 7 Detailed Description               |   | 11.6 静电放电警告                             |                  |

| 7.1 Overview                         |   | 11.7 术语表                                |                  |

| 7.2 Functional Block Diagram         |   | 12 Mechanical, Packaging, and Orderable |                  |

| 7.3 Feature Description              |   | Information                             | 29               |

| 7.4 Device Functional Modes          |   |                                         |                  |

|                                      |   |                                         |                  |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| Ch | anges from Revision J (November 2017) to Revision K (August 2021)    | Page |

|----|----------------------------------------------------------------------|------|

| •  | 在标题中添加了"同步 Fly-Buck"                                                 | 1    |

|    | 更新了整个文档中的表格、图和交叉参考的编号格式。                                             |      |

| •  | 更新了应用要点并添加了超链接                                                       | 1    |

| •  | Changed Overview                                                     | 9    |

|    | Changed Functional Block Diagram                                     |      |

| •  | Changed Power Supply Recommendations                                 | 25   |

| •  | Updated Related Documentation                                        | 27   |

| Ch | anges from Revision I (October 2015) to Revision J (November 2017)   | Page |

| •  | Deleted the lead temperature from the Absolute Maximum Ratings table | 4    |

|    |                                                                      |      |

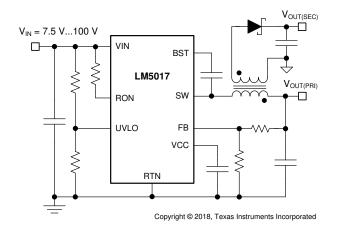

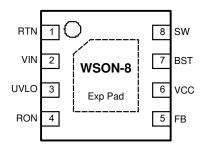

# **5 Pin Configuration and Functions**

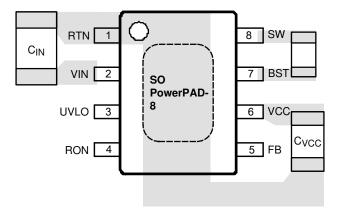

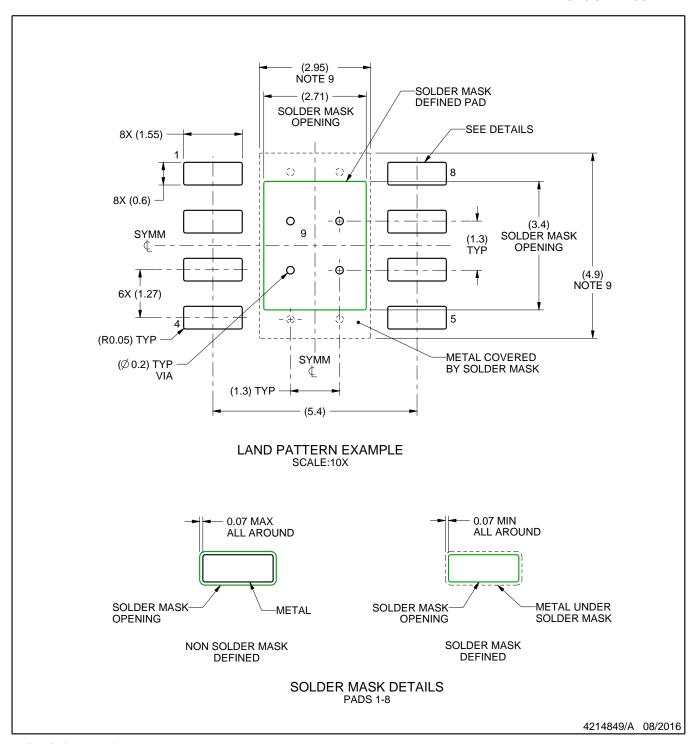

图 5-1. DDA Package 8-Pin SO PowerPAD Top View

图 5-2. NGU Package 8-Pin WSON With Exposed Thermal Pad Top View

表 5-1. Pin Functions

|     | DIN  |     | 7,011                                                                            | PIN FUNCTIONS                                                                                                                                                                                                                                                                   |

|-----|------|-----|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | PIN  | I/O | DESCRIPTION                                                                      | APPLICATION INFORMATION                                                                                                                                                                                                                                                         |

| NO. | NAME |     |                                                                                  |                                                                                                                                                                                                                                                                                 |

| 1   | RTN  | _   | Ground                                                                           | Ground connection of the integrated circuit.                                                                                                                                                                                                                                    |

| 2   | VIN  | Р   | Input voltage                                                                    | Operating input range is 7.5 V to 100 V.                                                                                                                                                                                                                                        |

| 3   | UVLO | I   | Undervoltage comparator input                                                    | Resistor divider from $V_{\text{IN}}$ to UVLO to GND programs the undervoltage detection threshold. An internal current source is enabled when UVLO is above 1.225 V to provide hysteresis. When UVLO pin is pulled below 0.66 V externally, the regulator is in shutdown mode. |

| 4   | RON  | I   | On-time control                                                                  | A resistor between this pin and $V_{\text{IN}}$ sets the buck switch on-time as a function of $V_{\text{IN}}$ . Minimum recommended on-time is 100 ns at maximum input voltage.                                                                                                 |

| 5   | FB   | I   | Feedback                                                                         | This pin is connected to the inverting input of the internal regulation comparator. The regulation level is 1.225 V.                                                                                                                                                            |

| 6   | VCC  | 0   | Output from the internal high-voltage series pass regulator. Regulated at 7.6 V. | The internal $V_{CC}$ regulator provides bias supply for the gate drivers and other internal circuitry. A 1- $\mu$ F decoupling capacitor is recommended.                                                                                                                       |

| 7   | BST  | ı   | Bootstrap capacitor                                                              | An external capacitor is required between the BST and SW pins (0.01- $\upmu$ F ceramic). The BST capacitor is charged by the $V_{CC}$ regulator through an internal diode when SW is low.                                                                                       |

| 8   | SW   | Р   | Switching node                                                                   | Power switching node. Connect to the output inductor and bootstrap capacitor.                                                                                                                                                                                                   |

|     | EP   | _   | Exposed Pad                                                                      | Exposed pad must be connected to the RTN pin. Solder to the system ground plane on application board for reduced thermal resistance.                                                                                                                                            |

### **6 Specifications**

### **6.1 Absolute Maximum Ratings**

See (1)

|                                             | MIN   | MAX                   | UNIT |

|---------------------------------------------|-------|-----------------------|------|

| VIN, UVLO to RTN                            | - 0.3 | 100                   | V    |

| SW to RTN                                   | - 1.5 | V <sub>IN</sub> + 0.3 | V    |

| SW to RTN (100-ns transient)                | - 5   | V <sub>IN</sub> + 0.3 | V    |

| BST to VCC                                  |       | 100                   | V    |

| BST to SW                                   |       | 13                    | V    |

| RON to RTN                                  | - 0.3 | 100                   | V    |

| VCC to RTN                                  | - 0.3 | 13                    | V    |

| FB to RTN                                   | - 0.3 | 5                     | V    |

| Maximum Junction Temperature <sup>(2)</sup> |       | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>       | - 55  | 150                   | °C   |

<sup>(1)</sup> Absolute Maximum Ratings are limits beyond which damage to the device may occur. # 6.3 are conditions under which operation of the device is intended to be functional. For ensured specifications and test conditions, see the # 6.5. The RTN pin is the GND reference electrically connected to the substrate.

### 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                               | MIN  | MAX | UNIT |

|-----------------------------------------------|------|-----|------|

| V <sub>IN</sub> Voltage <sup>(1)</sup>        | 7.5  | 100 | V    |

| Operating Junction Temperature <sup>(2)</sup> | - 40 | 125 | °C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under the device is intended to be functional. For specifications and test conditions, see #6.5.

#### 6.4 Thermal Information

|                      |                                                    | LM         |        |      |

|----------------------|----------------------------------------------------|------------|--------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                      | NGU (WSON) | UNIT   |      |

|                      |                                                    | 8 PINS     | 8 PINS |      |

| R <sub>0</sub> JA    | Junction-to-ambient thermal resistance             | 41.3       | 41.1   | °C/W |

| R <sub>0</sub> JCbot | Junction-to-case (bottom) thermal resistance       | 3.2        | 2.4    | °C/W |

| ΨЈВ                  | Junction-to-board thermal characteristic parameter | 19.2       | 24.4   | °C/W |

| R <sub>0</sub> JB    | Junction-to-board thermal resistance               | 19.1       | 30.6   | °C/W |

| R <sub>θ JCtop</sub> | Junction-to-case (top) thermal resistance          | 34.7       | 37.3   | °C/W |

| ΨЈТ                  | Junction-to-top thermal characteristic parameter   | 0.3        | 6.7    | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Submit Document Feedback

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

### 6.5 Electrical Characteristics

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over -40°C to 125°C junction temperature range, unless otherwise stated.  $V_{IN}$  = 48 V, unless otherwise stated. See<sup>(1)</sup>

|                        | PARAMETER                                                      | TEST CONDITIONS                                                      | MIN  | TYP   | MAX  | UNIT |

|------------------------|----------------------------------------------------------------|----------------------------------------------------------------------|------|-------|------|------|

| V <sub>CC</sub> SUPP   | _Y                                                             |                                                                      |      |       |      |      |

| V <sub>CC</sub>        | VCC regulator output                                           | V <sub>IN</sub> = 48 V, I <sub>CC</sub> = 20 mA                      | 6.25 | 7.6   | 8.55 | V    |

| I <sub>LIM-VCC</sub>   | VCC current limit                                              | V <sub>IN</sub> = 48 V <sup>(2)</sup>                                | 26   |       |      | mA   |

| V <sub>CC-UV</sub>     | VCC undervoltage lockout voltage (V <sub>VCC</sub> increasing) | $-40$ °C $\leq$ T <sub>J</sub> $\leq$ 125°C                          | 4.15 | 4.5   | 4.9  | V    |

| V <sub>CC-UV-HYS</sub> | VCC undervoltage hysteresis                                    |                                                                      |      | 300   |      | mV   |

| V <sub>CC-LDO</sub>    | VIN - VCC dropout voltage                                      | V <sub>IN</sub> = 9 V, I <sub>CC</sub> = 20 mA                       |      | 2.3   |      | V    |

| ОР                     | I <sub>IN</sub> operating current                              | Non-switching, V <sub>FB</sub> = 3 V                                 |      | 1.75  |      | mA   |

| I <sub>SHD</sub>       | I <sub>IN</sub> shutdown current                               | V <sub>UVLO</sub> = 0 V                                              |      | 50    | 225  | μΑ   |

| SWITCH C               | HARACTERISTICS                                                 |                                                                      |      |       |      |      |

| R <sub>DS(ON)1</sub>   | Buck switch R <sub>DS(on)</sub>                                | I <sub>TEST</sub> = 200 mA, V <sub>BST</sub> - V <sub>SW</sub> = 7 V |      | 0.8   | 1.8  | Ω    |

| R <sub>DS(ON)2</sub>   | Synchronous switch R <sub>DS(on)</sub>                         | I <sub>TEST</sub> = 200 mA                                           |      | 0.45  | 1    | Ω    |

| BST <sub>UV</sub>      | Gate drive UVLO                                                | V <sub>BST</sub> - V <sub>SW</sub> rising                            | 2.4  | 3     | 3.6  | V    |

| BST <sub>UV-HYS</sub>  | Gate drive UVLO hysteresis                                     |                                                                      |      | 260   |      | mV   |

| CURRENT                | LIMIT                                                          |                                                                      |      |       | 1    |      |

| I <sub>LIM -HS</sub>   | Current limit threshold                                        | - 40°C ≤ T <sub>J</sub> ≤ 125°C                                      | 0.7  | 1.02  | 1.3  | Α    |

| t <sub>RES</sub>       | Current limit response time                                    | Time to switch off                                                   |      | 150   |      | ns   |

| t <sub>OFF1</sub>      | OFF-time generator (test 1)                                    | V <sub>FB</sub> = 0.1 V, V <sub>IN</sub> = 48 V                      |      | 12    |      | μs   |

| t <sub>OFF2</sub>      | OFF-time generator (test 2)                                    | V <sub>FB</sub> = 1 V, V <sub>IN</sub> = 48 V                        |      | 2.5   |      | μs   |

| REGULAT                | ON AND OVERVOLTAGE COMP                                        | PARATORS                                                             |      | ,     | 1    |      |

| V <sub>FB</sub>        | FB regulation level                                            | Internal reference trip point for switch ON                          | 1.2  | 1.225 | 1.25 | V    |

| V <sub>FB-OV</sub>     | FB overvoltage threshold                                       | Trip point for switch OFF                                            |      | 1.62  |      | V    |

| FB-BIAS                | FB bias current                                                |                                                                      |      | 60    |      | nA   |

| JNDERVO                | LTAGE SENSING FUNCTION                                         |                                                                      |      |       |      |      |

| V <sub>UVLO-TH</sub>   | UVLO threshold                                                 | Voltage at UVLO rising                                               | 1.19 | 1.225 | 1.26 | V    |

| UVLO-HYS               | UVLO hysteresis input current                                  | V <sub>UVLO</sub> = 2.5 V                                            | - 10 | - 20  | - 29 | μA   |

| √ <sub>SD-TH</sub>     | Remote shutdown threshold                                      | Voltage at UVLO falling                                              | 0.32 | 0.66  |      | V    |

| V <sub>SD-HYS</sub>    | Remote shutdown hysteresis                                     |                                                                      |      | 110   |      | mV   |

| THERMAL                | SHUTDOWN                                                       | -                                                                    |      |       |      |      |

| Γ <sub>SD</sub>        | Thermal shutdown temperature                                   |                                                                      |      | 165   |      | °C   |

| T <sub>SD-HYS</sub>    | Thermal shutdown hysteresis                                    |                                                                      |      | 20    |      | °C   |

<sup>(1)</sup> All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

### 6.6 Timing Requirements

Typical values correspond to  $T_J = 25^{\circ}C$ . Minimum and maximum limits apply over  $-40^{\circ}C$  to  $125^{\circ}C$  junction temperature range unless otherwise stated.  $V_{IN} = 48$  V unless otherwise stated.

|                  |                        |                                                   | MIN | NOM | MAX | UNIT |

|------------------|------------------------|---------------------------------------------------|-----|-----|-----|------|

| ON-TIM           | ME GENERATOR           |                                                   |     |     |     |      |

| t <sub>ON1</sub> | t <sub>ON</sub> test 1 | V <sub>IN</sub> = 32 V, R <sub>ON</sub> = 100 k Ω | 270 | 350 | 460 | ns   |

| t <sub>ON2</sub> | t <sub>ON</sub> test 2 | V <sub>IN</sub> = 48 V, R <sub>ON</sub> = 100 k Ω | 188 | 250 | 336 | ns   |

| t <sub>ON3</sub> | t <sub>ON</sub> test 3 | V <sub>IN</sub> = 75 V, R <sub>ON</sub> = 250 k Ω | 250 | 370 | 500 | ns   |

<sup>(2)</sup> VCC provides self bias for the internal gate drive and control circuits. Device thermal limitations limit external loading.

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over -40°C to 125°C junction temperature range unless otherwise stated.  $V_{IN}$  = 48 V unless otherwise stated.

|                       |                        |                                                   | MIN  | NOM  | MAX  | UNIT |

|-----------------------|------------------------|---------------------------------------------------|------|------|------|------|

| t <sub>ON4</sub>      | t <sub>ON</sub> test 4 | V <sub>IN</sub> = 10 V, R <sub>ON</sub> = 250 k Ω | 1880 | 3200 | 4425 | ns   |

| MINIMUM               | MINIMUM OFF-TIME       |                                                   |      |      |      |      |

| t <sub>OFF(min)</sub> | Minimum off-timer      | V <sub>FB</sub> = 0 V                             |      | 144  |      | ns   |

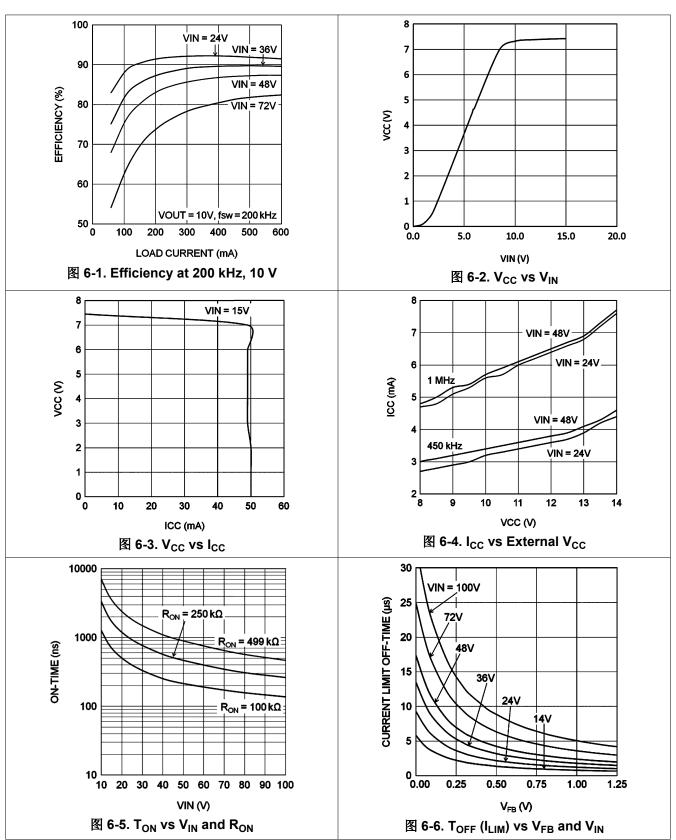

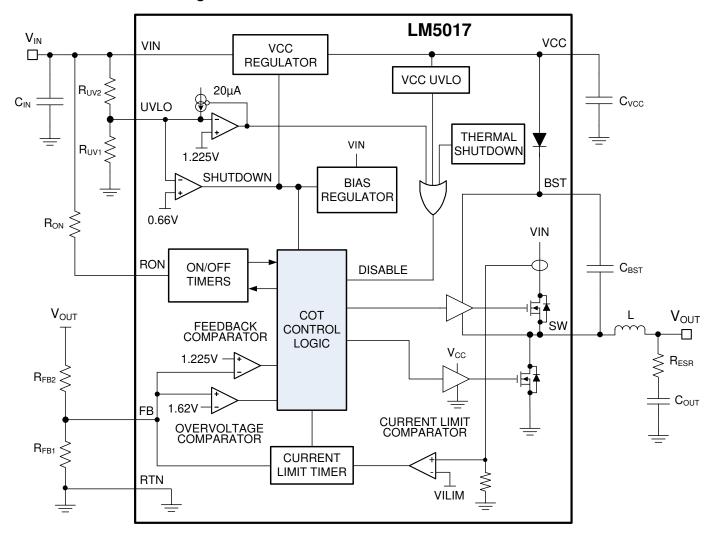

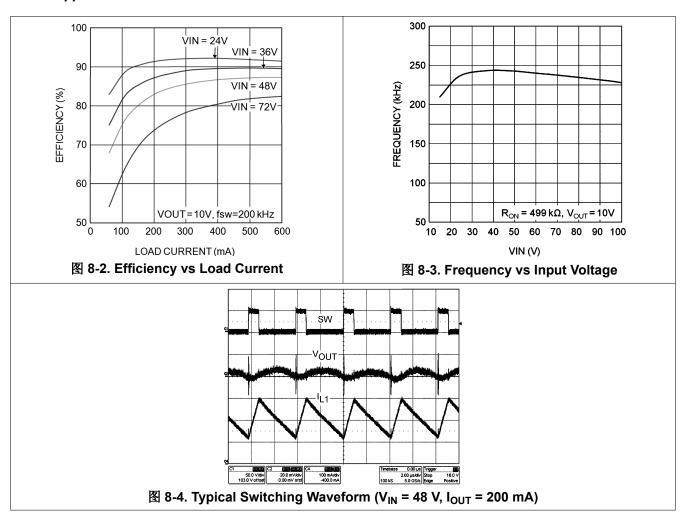

### **6.7 Typical Characteristics**

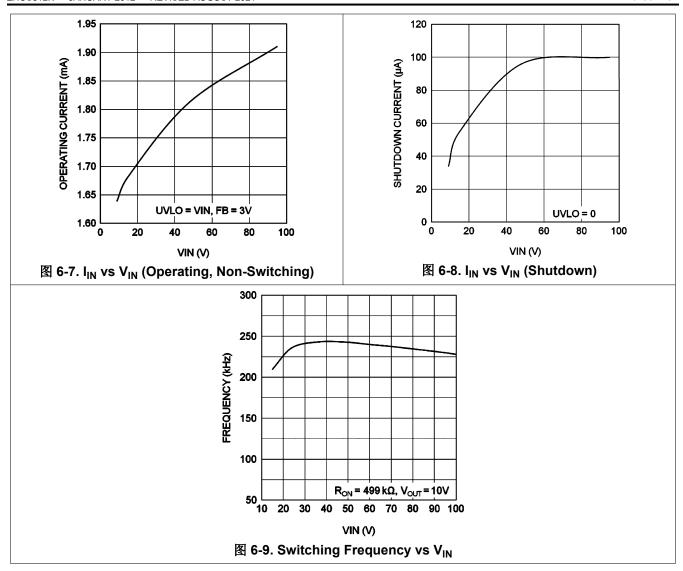

### 7 Detailed Description

### 7.1 Overview

The LM5017 step-down synchronous switching converter features all the functions needed to implement a low-cost, efficient buck regulator capable of supplying 600 mA to the load. This high-voltage regulator contains 100-V N-channel buck and synchronous rectifier switches and is available in 8-pin thermally-enhanced WSON and SO packages with pin pitches of 0.8 mm and 1.27 mm, respectively. The regulator operation is based on an adaptive constant on-time control architecture where the on-time is inversely proportional to input voltage V<sub>IN</sub>. This feature maintains a relatively constant operating frequency with load and input voltage variations. A constant on-time switching regulator requires no loop compensation resulting in fast load transient response.

The LM5017 can be applied in numerous end equipment systems requiring efficient step-down regulation from higher input voltages. This regulator is well-suited for 24-V industrial systems as well as 48-V communications and PoE voltage ranges. The LM5017 integrates an undervoltage lockout (UVLO) circuit to prevent faulty operation of the device at low input voltages and features intelligent current limit and thermal shutdown to protect the device during overload or short circuit. Peak current limit detection circuit is implemented with a forced off-time during current limiting that is inversely proportional to  $V_{OUT}$  and directly proportional to  $V_{IN}$ . Varying the current limit off-time with  $V_{OUT}$  and  $V_{IN}$  ensures short-circuit protection with minimal current limit foldback. Additional protection features include thermal shutdown with automatic recovery, VCC and gate drive UVLO, minimum forced off-time, and remote shutdown.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

#### 7.3.1 Control Overview

The LM5017 buck regulator employs a control principle based on a comparator and a one-shot on-timer, with the output voltage feedback (FB) compared to an internal reference (1.225 V). If the FB voltage is below the reference the internal buck switch is turned on for the one-shot timer period, which is a function of the input voltage and the programming resistor ( $R_{ON}$ ). Following the on-time the switch remains off until the FB voltage falls below the reference, but never before the minimum off-time forced by the minimum off-time one-shot timer. When the FB pin voltage falls below the reference and the minimum off-time one-shot period expires, the buck switch is turned on for another on-time one-shot period. This will continue until regulation is achieved and the FB voltage is approximately equal to 1.225 V (typ).

In a synchronous buck converter, the low-side (sync) FET is on when the high-side (buck) FET is off. The inductor current ramps up when the high-side switch is on and ramps down when the high-side switch is 'off'. There is no diode emulation feature in this IC, and therefore, the inductor current may ramp in the negative direction at light load. This causes the converter to operate in continuous conduction mode (CCM) regardless of the output loading. The operating frequency remains relatively constant with load and line variations. Calculate the operating frequency as shown in 方程式 1.

$$f_{SW} = \frac{V_{OUT}}{K \times R_{ON}}$$

(1)

where

•  $K = 9 \times 10^{-11}$

The output voltage ( $V_{OUT}$ ) is set by two external resistors ( $R_{FB1}$ ,  $R_{FB2}$ ). The regulated output voltage is calculated as shown in 方程式 2.

$$V_{OUT} = 1.225V \times \frac{R_{FB2} + R_{FB1}}{R_{FB1}}$$

(2)

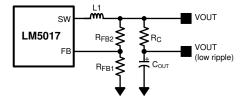

This regulator regulates the output voltage based on ripple voltage at the feedback input, requiring a minimum amount of ESR for the output capacitor ( $C_{OUT}$ ). A minimum of 25 mV of ripple voltage at the feedback pin (FB) is required for the LM5017. In cases where the capacitor ESR is too small, additional series resistance may be required ( $R_C$  in  $\mathbb{Z}$  7-1).

For applications where lower output voltage ripple is required the output can be taken directly from a low ESR output capacitor, as shown in  $\[mathbb{R}\]$  7-1. However,  $\[mathbb{R}\]$  C slightly degrades the load regulation.

图 7-1. Low Ripple Output Configuration

#### 7.3.2 V<sub>CC</sub> Regulator

The LM5017 device contains an internal high-voltage linear regulator with a nominal output of 7.6 V. The input pin ( $V_{IN}$ ) can be connected directly to the line voltages up to 100 V. The  $V_{CC}$  regulator is internally current limited to 30 mA. The regulator sources current into the external capacitor at  $V_{CC}$ . This regulator supplies current to internal circuit blocks including the synchronous MOSFET driver and the logic circuits. When the voltage on the  $V_{CC}$  pin reaches the undervoltage lockout ( $V_{CC}$  UVLO) threshold of 4.5 V, the IC is enabled.

An internal diode connected from  $V_{CC}$  to the BST pin replenishes the charge in the gate drive bootstrap capacitor when SW pin is low.

At high input voltages, the power dissipated in the high voltage regulator is significant and can limit the overall achievable output power. As an example, with the input at 48 V and switching at high frequency, the  $V_{CC}$  regulator may supply up to 7 mA of current resulting in 48 V × 7 mA = 336 mW of power dissipation. If the  $V_{CC}$  voltage is driven externally by an alternate voltage source between 8.55 V and 13 V, the internal regulator is disabled. This reduces the power dissipation in the IC.

### 7.3.3 Regulation Comparator

The feedback voltage at FB is compared to an internal 1.225 V reference. In normal operation, when the output voltage is in regulation, an on-time period is initiated when the voltage at FB falls below 1.225 V. The high side switch will stay on for the on-time, causing the FB voltage to rise above 1.225 V. After the on-time period, the high side switch will stay off until the FB voltage again falls below 1.225 V. During start-up, the FB voltage will be below 1.225 V at the end of each on-time, causing the high side switch to turn on immediately after the minimum forced off-time of 144 ns. The high side switch can be turned off before the on-time is over if the peak current in the inductor reaches the current limit threshold.

### 7.3.4 Overvoltage Comparator

The feedback voltage at FB is compared to an internal 1.62 V reference. If the voltage at FB rises above 1.62 V the on-time pulse is immediately terminated. This condition can occur if the input voltage and/or the output load changes suddenly. The high side switch will not turn on again until the voltage at FB falls below 1.225 V.

#### 7.3.5 On-Time Generator

The on-time for the LM5017 device is determined by the  $R_{ON}$  resistor and is inversely proportional to the input voltage ( $V_{IN}$ ), resulting in a nearly constant frequency as  $V_{IN}$  is varied over the operating range. The on-time for the LM5017 can be calculated using 方程式 3.

$$T_{ON} = \frac{10^{-10} \text{ x R}_{ON}}{V_{IN}} \tag{3}$$

See  $\boxtimes$  6-5. R<sub>ON</sub> should be selected for a minimum on-time (at maximum V<sub>IN</sub>) greater than 100 ns for proper operation. This requirement limits the maximum switching frequency for high V<sub>IN</sub>.

#### 7.3.6 Current Limit

The LM5017 device contains an intelligent current limit off-timer. If the current in the buck switch exceeds 1.02 A, the present cycle is immediately terminated, and a non-resetable off-timer is initiated. The length of the off-time is controlled by the FB voltage and the input voltage  $V_{IN}$ . As an example, when FB = 0 V and  $V_{IN}$  = 48 V, the off-time is set to 16  $\mu$ s. This condition occurs when the output is shorted and during the initial part of start-up. This  $V_{IN}$  dependent off-time ensures safe short circuit operation up to the maximum input voltage of 100 V.

In cases of overload where the FB voltage is above zero volts (not a short circuit) the current limit off-time is reduced. Reducing the off-time during less severe overloads reduces the amount of foldback, recovery time, and start-up time. The off-time is calculated from 方程式 4.

$$T_{OFF(ILIM)} = \frac{0.07 \times V_{IN}}{V_{FB} + 0.2 \text{ V}} \ \mu\text{s} \tag{4}$$

The current limit protection feature is peak limited. The maximum average output current will be less than the peak.

#### 7.3.7 N-Channel Buck Switch and Driver

The LM5017 device integrates an N-Channel Buck switch and associated floating high voltage gate driver. The gate driver circuit works in conjunction with an external bootstrap capacitor and an internal high voltage diode. A 0.01 uF ceramic capacitor connected between the BST pin and the SW pin provides the voltage to the driver during the on-time. During each off-time, the SW pin is at approximately 0 V, and the bootstrap capacitor charges from  $V_{CC}$  through the internal diode. The minimum off-timer, set to 144 ns, ensures a minimum time each cycle to recharge the bootstrap capacitor.

Copyright © 2021 Texas Instruments Incorporated

#### 7.3.8 Synchronous Rectifier

The LM5017 provides an internal synchronous N-Channel MOSFET rectifier. This MOSFET provides a path for the inductor current to flow when the high-side MOSFET is turned off.

The synchronous rectifier has no diode emulation mode, and is designed to keep the regulator in continuous conduction mode even with light loads which would otherwise result in discontinuous operation.

#### 7.3.9 Undervoltage Detector

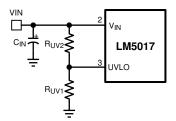

The LM5017 device contains a dual level undervoltage lockout (UVLO) circuit. A summary of threshold voltages and operational states is provided in #7.4. When the UVLO pin voltage is below 0.66 V, the regulator is in a low current shutdown mode. When the UVLO pin voltage is greater than 0.66V but less than 1.225 V, the regulator is in standby mode. In standby mode the  $V_{CC}$  bias regulator is active while the regulator output is disabled. When the  $V_{CC}$  pin exceeds the  $V_{CC}$  undervoltage threshold and the UVLO pin voltage is greater than 1.225 V, normal operation begins. An external set-point voltage divider from  $V_{IN}$  to GND can be used to set the minimum operating voltage of the regulator.

UVLO hysteresis is accomplished with an internal 20-  $\mu$ A current source that is switched on or off into the impedance of the set-point divider. When the UVLO threshold is exceeded, the current source is activated to quickly raise the voltage at the UVLO pin. The hysteresis is equal to the value of this current times the resistance  $R_{UV2}$ .

If the UVLO pin is connected directly to the  $V_{IN}$  pin, the regulator will begin operation once the  $V_{CC}$  undervoltage is satisfied.

图 7-2. UVLO Resistor Setting

#### 7.3.10 Thermal Protection

The LM5017 device should be operated so the junction temperature does not exceed 150°C during normal operation. An internal Thermal Shutdown circuit is provided to protect the LM5017 in the event of a higher than normal junction temperature. When activated, typically at 165°C, the regulator is forced into a low power reset state, disabling the buck switch and the  $V_{CC}$  regulator. This feature prevents catastrophic failures from accidental device overheating. When the junction temperature falls below 145°C (typical hysteresis = 20°C), the  $V_{CC}$  regulator is enabled, and normal operation is resumed.

#### 7.3.11 Ripple Configuration

LM5017 uses Constant-On-Time (COT) control in which the on-time is terminated by an on-timer and the off-time is terminated by the feedback voltage ( $V_{FB}$ ) falling below the reference voltage ( $V_{REF}$ ). Therefore, for stable operation, the feedback voltage must decrease monotonically, in phase with the inductor current during the off-time. Furthermore, this change in feedback voltage ( $V_{FB}$ ) during off-time must be larger than any noise component present at the feedback node.

表 7-1 shows three different methods for generating appropriate voltage ripple at the feedback node. Type 1 and Type 2 ripple circuits couple the ripple at the output of the converter to the feedback node (FB). The output voltage ripple has two components:

- 1. Capacitive ripple caused by the inductor current ripple charging/discharging the output capacitor.

- Resistive ripple caused by the inductor current ripple flowing through the ESR of the output capacitor.

The capacitive ripple is not in phase with the inductor current. As a result, the capacitive ripple does not decrease monotonically during the off-time. The resistive ripple is in phase with the inductor current and

decreases monotonically during the off-time. The resistive ripple must exceed the capacitive ripple at the output node ( $V_{OUT}$ ) for stable operation. If this condition is not satisfied unstable switching behavior is observed in COT converters, with multiple on-time bursts in close succession followed by a long off-time.

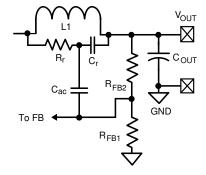

Type 3 ripple method uses  $R_r$  and  $C_r$  and the switch node (SW) voltage to generate a triangular ramp. This triangular ramp is ac coupled using  $C_{ac}$  to the feedback node (FB). Since this circuit does not use the output voltage ripple, it is ideally suited for applications where low output voltage ripple is required. For more information on each ripple generation method, refer to the *AN-1481 Controlling Output Ripple and Achieving ESR Independence in Constant On-Time (COT) Regulator Designs* application report.

表 7-1. Ripple Configuration

| TYPE 1<br>LOWEST COST CONFIGURATION                                                     | TYPE 2 REDUCED RIPPLE CONFIGURATION                                                              | TYPE 3 MINIMUM RIPPLE CONFIGURATION                                                                                                  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OUT</sub> R <sub>FB2</sub> R <sub>C</sub> To FB  R <sub>FB1</sub> GND            | Vout  Cac  R <sub>FB1</sub> R <sub>FB1</sub> Cout  GND                                           | To FB R <sub>FB1</sub>                                                                                                               |

| $R_{C} \ge \frac{25 \text{ mV}}{\Delta I_{L(MIN)}} \times \frac{V_{OUT}}{V_{REF}} $ (5) | $C \ge \frac{5}{f_{sw}(R_{FB2}  R_{FB1})}$ $R_C \ge \frac{25 \text{ mV}}{\Delta I_{L(MIN)}}$ (6) | $C_{r} = 3300 \text{ pF}$ $C_{ac} = 100 \text{ nF}$ $R_{r}C_{r} \le \frac{(V_{IN(MIN)} - V_{OUT}) \times T_{ON}}{25 \text{ mV}}$ (7) |

#### 7.3.12 Soft-Start

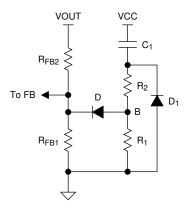

A soft-start feature can be implemented with the LM5017 using an external circuit. As shown in  $\boxtimes$  7-3, the soft-start circuit consists of one capacitor,  $C_1$ , two resistors,  $R_1$  and  $R_2$ , and a diode, D. During the initial start-up, the VCC voltage is established prior to the  $V_{OUT}$  voltage. Capacitor  $C_1$  is discharged and D is thereby forward biased to pull up the FB voltage. The FB voltage exceeds the reference voltage (1.225 V) and switching is therefore disabled. As capacitor  $C_1$  charges, the voltage at node B gradually decreases and switching commences.  $V_{OUT}$  will gradually rise to maintain the FB voltage at the reference voltage. Once the voltage at node B is less than a diode drop above FB voltage, the soft-start is finished and D is reverse biased.

During the initial part of the start-up, the FB voltage can be approximated as follows. Please note that the effect of  $R_1$  has been ignored to simplify the calculation shown in 52 8.

$$V_{FB} = (VCC - V_D) \times \frac{R_{FB1} \times R_{FB2}}{R_2 \times (R_{FB1} + R_{FB2}) + R_{FB1} \times R_{FB2}}$$

(8)

C1 is charged after the first start up. Diode D1 is optional and can be added to discharge C1 when the input voltage experiences a momentary drop to initialize the soft-start sequence.

To achieve the desired soft-start, the following design guidance is recommended:

- (1)  $R_2$  is selected so that  $V_{FB}$  is higher than 1.225 V for a  $V_{CC}$  of 4.5 V, but is lower than 5 V when  $V_{CC}$  is 8.55 V. If an external  $V_{CC}$  is used,  $V_{FB}$  should not exceed 5 V at maximum  $V_{CC}$ .

- (2)  $C_1$  is selected to achieve the desired start-up time that can be determined from 方程式 9.

$$t_{S} = C_{1} \times (R_{2} + \frac{R_{FB1} \times R_{FB2}}{R_{FB1} + R_{FB2}})$$

(9)

(3)  $R_1$  is used to maintain the node B voltage at zero after the soft-start is finished. A value larger than the feedback resistor divider is preferred. Note that the effect of  $R_1$  is ignored in the previous equations.

Based on the schematic shown in 8 - 1, selecting  $C_1 = 1$  uF,  $R_2 = 1$  k $\Omega$ ,  $R_1 = 30$  k $\Omega$  results in a soft-start time of about 2 ms.

图 7-3. Soft-Start Circuit

### 7.4 Device Functional Modes

表 7-2. UVLO Modes

| UVLO             | V <sub>CC</sub> Regulator | MODE      | DESCRIPTION                                                |  |  |

|------------------|---------------------------|-----------|------------------------------------------------------------|--|--|

| < 0.66 V         | Disabled                  | Shutdown  | V <sub>CC</sub> regulator disabled.<br>Switching disabled. |  |  |

| 0.66 V - 1.225 V | Enabled                   | Standby   | V <sub>CC</sub> regulator enabled<br>Switching disabled.   |  |  |

| > 1.225 V        | V <sub>CC</sub> < 4.5 V   | Standby   | V <sub>CC</sub> regulator enabled.<br>Switching disabled.  |  |  |

| > 1.225 V        | V <sub>CC</sub> > 4.5 V   | Operating | V <sub>CC</sub> enabled.<br>Switching enabled.             |  |  |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

### 8 Application and Implementation

#### Note

以下应用部分中的信息不属于 TI 器件规格的范围,TI 不担保其准确性和完整性。TI 的客 户应负责确定 器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

### 8.1 Application Information

The LM5017 device is step-down DC-DC converter. The device is typically used to convert a higher DC voltage to a lower DC voltage with a maximum available output current of 650 mA. Use the following design procedure to select component values for the LM5017 device. Alternately, use the WEBENCH® software to generate a complete design. The WEBENCH software uses an iterative design procedure and accesses a comprehensive database of components when generating a design. This section presents a simplified discussion of the design process.

### 8.2 Typical Application

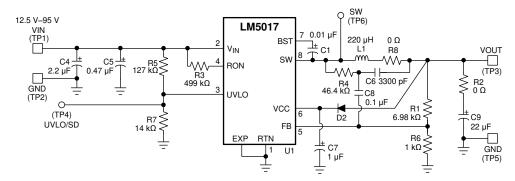

#### 8.2.1 Application Circuit: 12.5-V to 95-V Input and 10-V, 600-mA Output Buck Converter

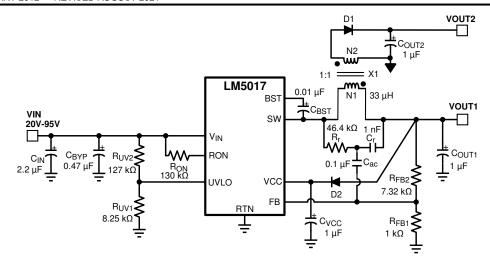

The application schematic of a buck supply is shown in 🗵 8-1. For output voltage (V<sub>OUT</sub>) more than one diode drop above the maximum regulation threshold of  $V_{CC}$  (8.55 V, see #6.5), the  $V_{CC}$  pin can be connected to  $V_{OUT}$ through a diode (D2), as shown in \( \begin{aligned} 8-1, for higher efficiency and lower power dissipation in the IC. \)

The design example below uses equations from the #7.3 with component names provided. Corresponding component designators from 8 8-1 are also provided for each selected value.

图 8-1. Final Schematic for 12.5-V to 95-V Input, and 10-V, 600-mA Output Buck Converter

#### 8.2.1.1 Design Requirements

Selection of external components is illustrated through a design example. The design example specifications are shown in 表 8-1.

| 表 8-1. Buck Converte | r Design Specificat | ions |

|----------------------|---------------------|------|

| METERS               |                     | ,    |

| • • •                | <b>O</b> 1     |

|----------------------|----------------|

| DESIGN PARAMETERS    | VALUE          |

| Input voltage range  | 12.5 V to 95 V |

| Output voltage       | 10 V           |

| Maximum Load current | 600 mA         |

| Switching Frequency  | ≈ 225 kHz      |

#### 8.2.1.2 Detailed Design Procedure

### 8.2.1.2.1 Custom Design with WEBENCH Tools

Click here to create a custom design using the WEBENCH® Power Designer.

1. Start by entering your V<sub>IN</sub>, V<sub>OUT</sub> and I<sub>OUT</sub> requirements.

- 2. Optimize your design for key parameters like efficiency, footprint and cost using the optimizer dial and compare this design with other possible solutions from Texas Instruments.

- 3. WEBENCH Power Designer provides you with a customized schematic along with a list of materials with real time pricing and component availability.

- 4. In most cases, you will also be able to:

- Run electrical simulations to see important waveforms and circuit performance,

- Run thermal simulations to understand the thermal performance of your board,

- · Export your customized schematic and layout into popular CAD formats,

- Print PDF reports for the design, and share your design with colleagues.

### 8.2.1.2.2 R<sub>FB1</sub>, R<sub>FB2</sub>

$V_{OUT}$  =  $V_{FB}$  x ( $R_{FB2}/R_{FB1}$  + 1), and because  $V_{FB}$  = 1.225 V, the ratio of  $R_{FB2}$  to  $R_{FB1}$  calculates as 7 : 1. Standard values are chosen with  $R_{FB2}$  = R1 = 6.98 k $\Omega$  and  $R_{FB1}$  = R6 = 1 k $\Omega$ . Other values could be used as long as the 7 : 1 ratio is maintained.

#### 8.2.1.2.3 Frequency Selection

At the minimum input voltage, the maximum switching frequency of LM5017 is restricted by the forced minimum off-time (T<sub>OFF(MIN)</sub>) as given by 方程式 10.

$$f_{\text{SW(MAX)}} = \frac{1 - D_{\text{MAX}}}{T_{\text{OFF(MIN)}}} = \frac{1 - 10/12.5}{200 \text{ ns}} = 1 \text{ MHz}$$

(10)

Similarly, at maximum input voltage, the maximum switching frequency of LM5017 is restricted by the minimum  $T_{ON}$  as given by 方程式 11.

$$f_{\text{SW(MAX)}} = \frac{D_{\text{MIN}}}{T_{\text{ON(MIN)}}} = \frac{10/95}{100 \text{ ns}} = 1.05 \text{ MHz}$$

(11)

Resistor  $R_{ON}$  sets the nominal switching frequency based on 方程式 12.

$$f_{SW} = \frac{V_{OUT}}{K \times R_{ON}}$$

(12)

where

•  $K = 9 \times 10^{-11}$

Operation at high switching frequency results in lower efficiency while providing the smallest solution. For this example a conservative 225 kHz was selected, resulting in  $R_{ON}$  = 493 k $\Omega$ . A standard value for  $R_{ON}$  = R3 = 499 k $\Omega$  is selected.

#### 8.2.1.2.4 Inductor Selection

The minimum inductance is selected to limit the output ripple to 15 to 40 percent of the maximum load current. In addition, the peak inductor current at maximum load should be smaller than the minimum current limit as given in # 6.5 table.

The inductor current ripple is given by 方程式 13.

$$\Delta I_{L} = \frac{V_{IN} - V_{OUT}}{L1 \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}}$$

(13)

$$I_{LI}(peak) = I_{OUT} + \frac{\Delta I_{L(MAX)}}{2} = 690 \text{ mA}$$

(14)

690 mA is less than the minimum current limit threshold of 0.7 A. The selected inductor should be able to withstand the maximum current limit of 1.3 A during startup and overload conditions without saturating.

#### 8.2.1.2.5 Output Capacitor

The output capacitor is selected to minimize the capacitive ripple across it. The maximum ripple is observed at maximum input voltage and is given by:

$$C_{OUT} = \frac{\Delta I_L}{8 \times f_{sw} \times \Delta V_{ripple}}$$

(15)

where

•  $\Delta V_{ripple}$  is the voltage ripple across the capacitor.

Assuming  $V_{IN}$  = 95 V and substituting  $\triangle V_{ripple}$  = 10 mV gives  $C_{OUT}$  = 10.1  $\mu$  F. A 22- $\mu$  F standard value is selected for  $C_{OUT}$  = C9. An X5R or X7R type capacitor with a voltage rating 16 V or higher should be selected.

#### 8.2.1.2.6 Type III Ripple Circuit

Type III ripple circuit as described in # 7.3.11 is chosen for this example. For a constant on-time converter to be stable, the injected in-phase ripple should be larger than the capacitive ripple on  $C_{OUT}$ .

Using the type III ripple circuit equation, the target ripple will be greater than the capacitive ripple generated at the primary-side output if the following condition is satisfied:

$$C_r = C6 = 3300 \text{ pF}$$

$$C_{ac} = C8 = 100 \text{ nF}$$

$$R_{r} \leq \frac{(V_{IN(MIN)} - V_{OUT}) \times T_{ON(VINMIN)}}{(25 \text{ mV} \times C_{r})}$$

(16)

For T<sub>ON</sub>, refer to 方程式 3.

Ripple resistor  $R_r$  is calculated to be 57.6 k $\Omega$ . This value provides the minimum ripple for stable operation. A smaller resistance should be selected to allow for variations in  $T_{ON}$ ,  $C_{OUT}$ , and other components.  $R_r$  = R4 = 46.4 k $\Omega$  is selected for this example application.

#### 8.2.1.2.7 V<sub>CC</sub> and Bootstrap Capacitors

The  $V_{CC}$  capacitor provides charge to bootstrap capacitor as well as internal circuitry and low side gate driver. The Bootstrap capacitor provides charge to high side gate driver. The recommended value for  $C_{VCC}$  = C7 = 1  $\mu$  F. A good value for  $C_{BST}$  = C1 = 0.01  $\mu$  F.

#### 8.2.1.2.8 Input Capacitor

Input capacitor should be large enough to limit the input voltage ripple as shown in 方程式 17.

$$C_{\text{IN}} \ge \frac{I_{\text{OUT(MAX)}}}{4 \text{ x } f_{\text{SW}} \text{ x } \Delta V_{\text{IN}}}$$

(17)

Choosing a  $\triangle$  V<sub>IN</sub> = 0.5 V gives a minimum C<sub>IN</sub> = 1.3  $\upmu$ F. A standard value of 2.2  $\upmu$ F is selected for C<sub>IN</sub> = C4. The input capacitor should be rated for the maximum input voltage under all conditions. A 100-V, X7R dielectric should be selected for this design.

The input capacitor should be placed directly across  $V_{IN}$  and RTN (pin 1 and 2) of the IC. If it is not possible to place all of the input capacitor close to the IC, a 0.47-  $\mu$  F capacitor should be placed near the IC to provide a bypass path for the high frequency component of the switching current.

#### 8.2.1.2.9 UVLO Resistors

The UVLO resistors  $R_{FB1}$  and  $R_{FB2}$  set the UVLO threshold and hysteresis according to the relationship shown in 方程式 18 and 方程式 19.

$$V_{IN}(HYS) = I_{HYS} X R_{UV2}$$

(18)

where

• I<sub>HYS</sub> = 20 μA

$$V_{IN} (UVLO, rising) = 1.225 V x \left( \frac{R_{UV2}}{R_{UV1}} + 1 \right)$$

(19)

Setting UVLO hysteresis of 2.5 V and UVLO rising threshold of 12 V results in  $R_{UV1}$  = 14.53 k $\Omega$  and  $R_{UV2}$  = 125 k $\Omega$ . Selecting standard values of  $R_{UV1}$  = R7 = 14 k $\Omega$  and  $R_{UV2}$  = R5 = 127 k $\Omega$  results in UVLO threshold and hysteresis of 12.4 V and 2.5 V respectively.

#### 8.2.1.3 Application Curves

### 8.2.2 Isolated DC/DC Converter Using LM5017

An isolated supply using the LM5017 is shown in  $\[ \mathbb{R} \]$  8-5. Inductor (L) in a typical buck circuit is replaced with a coupled inductor (X1). A diode (D1) is used to rectify the voltage on a secondary output. The nominal voltage at the secondary output ( $V_{OUT2}$ ) is given by 方程式 20.

$$V_{OUT2} = V_{OUT1} \times \frac{N_S}{N_P} - V_F$$

(20)

#### where

- V<sub>F</sub> is the forward voltage drop of D1

- N<sub>P</sub> and N<sub>S</sub> are the number of turns on the primary and secondary of coupled inductor X1.

For output voltage ( $V_{OUT1}$ ) more than one diode drop above the maximum  $V_{CC}$  (8.55 V), the  $V_{CC}$  pin can be diode connected to  $V_{OUT1}$  for higher efficiency and low dissipation in the IC. For a complete isolated bias design with LM5017, refer to the *AN-2204 LM5017 Isolated Supply Evaluation Board* application report.

Copyright © 2021 Texas Instruments Incorporated

图 8-5. Typical Isolated Application Schematic

#### 8.2.2.1 Design Requirements

| DESIGN PARAMETERS                          | VALUE        |

|--------------------------------------------|--------------|

| Input Voltage Range                        | 20 V - 100 V |

| Primary Output Voltage                     | 10 V         |

| Secondary (Isolated) Output Voltage        | 9.5 V        |

| Maximum Load Current (Primary + Secondary) | 300 mA       |

| Maximum Power Output                       | 3 W          |

| Nominal Switching Frequency                | 750 kHz      |

### 8.2.2.2 Detailed Design Procedure

#### 8.2.2.2.1 Transformer Turns Ratio

The transformer turns ratio is selected based on the ratio of the primary output voltage to the secondary (isolated) output voltage. In this design example, the two outputs are nearly equal and a 1:1 turns ratio transformer is selected. Therefore, N2/N1 = 1.

If the secondary (isolated) output voltage is significantly higher or lower than the primary output voltage, a turns ratio less than or greater than 1 is recommended. The primary output voltage is normally selected based on the input voltage range such that the duty cycle of the converter does not exceed 50% at the minimum input voltage. This condition is satisfied if VOUT1 <  $V_{IN\ MIN}$  / 2.

### 8.2.2.2.2 Total I<sub>OUT</sub>

Calculate the total primary-referred load current by multiplying the isolated output loads by the turns ratio of the transformer as shown in 方程式 21.

$$I_{OUT(MAX)} = I_{OUT1} + I_{OUT2} \times \frac{N2}{N1} = 0.3 \text{ A}$$

(21)

### 8.2.2.2.3 R<sub>FB1</sub>, R<sub>FB2</sub>

The feedback resistors are selected to set the primary output voltage. The selected value for  $R_{FB1}$  is 1 k $\Omega$ .  $R_{FB2}$  can be calculated using the following equations to set  $V_{OUT1}$  to the specified value of 10 V. A standard resistor value of 7.32 k $\Omega$  is selected for  $R_{FB2}$ .

$$V_{OUT1} = 1.225V \times (1 + \frac{R_{FB2}}{R_{FB1}})$$

(22)

$$\to R_{FB2} = \left(\frac{V_{OUT1}}{1.225} - 1\right) \times R_{FB1} = 7.16 \text{ k}\Omega$$

(23)

#### 8.2.2.2.4 Frequency Selection

Calculate the value of R<sub>ON</sub> to achieve the desired switching frequency using 方程式 24.

$$f_{SW} = \frac{V_{OUT1}}{K \times R_{ON}}$$

(24)

where

•  $K = 9 \times 10^{-11}$

For  $V_{OUT1}$  of 10 V and  $f_{SW}$  of 750 kHz, the calculated value of  $R_{ON}$  is 148 kΩ. A lower value of 130 kΩ is selected for this design to allow for second-order effects at high switching frequency that are not included in  $5\pi$   $\pm$  24.

#### 8.2.2.2.5 Transformer Selection

A coupled inductor or a flyback-type transformer is required for this topology. Energy is transferred from primary to secondary when the low-side synchronous switch of the buck converter is conducting.

The maximum inductor primary ripple current that can be tolerated without exceeding the buck switch peak current limit threshold (0.7 A minimum) is given by 方程式 25.

$$\Delta I_{L1} = \left(0.7 - I_{OUT1} - I_{OUT2} \times \frac{N2}{N1}\right) \times 2 = 0.8 \text{ A}$$

(25)

Using the maximum peak-to-peak inductor ripple current  $\Delta I_{L1}$  from 方程式 25, the minimum inductor value is given by 方程式 26.

$$L1 = \frac{V_{\text{IN}(\text{MAX})} - V_{\text{OUT}}}{\Delta I_{\text{L1}} \times f_{\text{SW}}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}(\text{MAX})}} = 14.9 \,\mu\text{H}$$

(26)

A higher value of 33  $\mu$ H is selected to insure the high-side switch current does not exceed the minimum peak current limit threshold. With this inductance, the inductor current ripple is  $\Delta$  I<sub>L1</sub>= 0.36 A at the maximum V<sub>IN</sub>.

### 8.2.2.2.6 Primary Output Capacitor

In a conventional buck converter the output ripple voltage is calculated as shown in 方程式 27.

$$\Delta V_{OUT} = \frac{\Delta I_{L1}}{8 \times f \times C_{OUT1}}$$

(27)

To limit the primary output ripple voltage  $\triangle$  V<sub>OUT1</sub> to approximately 50 mV, an output capacitor C<sub>OUT1</sub> of 1.2  $\mu$ F would be required for a conventional buck.

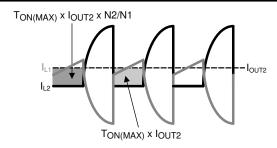

图 8-6 shows the primary winding current waveform (I<sub>L1</sub>) of a Fly-Buck™ converter. The reflected secondary winding current adds to the primary winding current during the buck switch off-time. Because of this increased current, the output voltage ripple is not the same as in conventional buck converter. The output capacitor value calculated in 方程式 27 should be used as the starting point. Optimization of output capacitance over the entire line and load range must be done experimentally. If the majority of the load current is drawn from the secondary isolated output, a better approximation of the primary output voltage ripple is given by 方程式 28.

$$\Delta V_{OUT1} = \frac{\left(I_{OUT2} \times \frac{N2}{N1}\right) \times T_{ON(MAX)}}{C_{OUT1}} \approx 67 \text{ mV}$$

(28)

图 8-6. Current Waveforms for C<sub>OUT1</sub> Ripple Calculation

A standard 1- $\mu$ F, 25 V capacitor is selected for this design. If lower output voltage ripple is required, a higher value should be selected for  $C_{OUT1}$  and/or  $C_{OUT2}$ .

#### 8.2.2.2.7 Secondary Output Capacitor

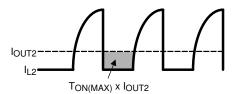

A simplified waveform for secondary output current ( $I_{OUT2}$ ) is shown in  $\boxtimes 8-7$ .

图 8-7. Secondary Current Waveforms for C<sub>OUT2</sub> Ripple Calculation

The secondary output current ( $I_{OUT2}$ ) is sourced by  $C_{OUT2}$  during on-time of the buck switch,  $T_{ON}$ . Ignoring the current transition times in the secondary winding, the secondary output capacitor ripple voltage can be calculated using 方程式 29.

$$\Delta V_{OUT2} = \frac{I_{OUT2} \times T_{ON \text{ (MAX)}}}{C_{OUT2}}$$

(29)

For a 1 : 1 transformer turns ratio, the primary and secondary voltage ripple equations are identical. Therefore,  $C_{OUT2}$  is chosen to be equal to  $C_{OUT1}$  (1  $\mu F$ ) to achieve comparable ripple voltages on primary and secondary outputs.

If lower output voltage ripple is required, a higher value should be selected for C<sub>OUT1</sub> and/or C<sub>OUT2</sub>.

#### 8.2.2.2.8 Type III Feedback Ripple Circuit

Type III ripple circuit as described in #7.3.11 is required for the Fly-Buck topology. Type I and Type II ripple circuits use series resistance and the triangular inductor ripple current to generate ripple at V<sub>OUT</sub> and the FB pin. The primary ripple current of a Fly-Buck is the combination or primary and reflected secondary currents as illustrated in 8.6. In the Fly-Buck topology, Type I and Type II ripple circuits suffer from large jitter as the reflected load current affects the feedback ripple.

图 8-8. Type III Ripple Circuit

Selecting the Type III ripple components using the equations from # 7.3.11 will ensure that the FB pin ripple is be greater than the capacitive ripple from the primary output capacitor  $C_{OUT1}$ . The feedback ripple component values are chosen as shown in  $\hbar$  23.

$$C_r = 1000 \text{ pF}$$

$C_{ac} = 0.1 \text{ }\mu\text{F}$

$$R_r C_r \le \frac{\left(V_{\text{IN }(M\text{IN})} - V_{\text{OUT}}\right) \times T_{\text{ON}}}{50 \text{ mV}}$$

(30)

The calculated value for  $R_r$  is 66 k $\Omega$ . This value provides the minimum ripple for stable operation. A smaller resistance should be selected to allow for variations in  $T_{ON}$ ,  $C_{OUT1}$  and other components. For this design,  $R_r$  value of 46.4 k $\Omega$  is selected.

#### 8.2.2.2.9 Secondary Diode

The reverse voltage across secondary-rectifier diode D1 when the high-side buck switch is off can be calculated using 方程式 31.

$$V_{D1} = \frac{N2}{N1} V_{IN} \tag{31}$$

For a V<sub>IN MAX</sub> of 95 V and the 1:1 turns ratio of this design, a 100 V Schottky is selected.

#### 8.2.2.2.10 V<sub>CC</sub> and Boostrap Capacitor

A 1- $\mu$ F capacitor of 16 V or higher rating is recommended for the V<sub>CC</sub> regulator bypass capacitor. A good value for the BST pin bootstrap capacitor is 0.01- $\mu$ F with a 16 V or higher rating.

#### 8.2.2.2.11 Input Capacitor

The input capacitor is typically a combination of a smaller bypass capacitor located near the regulator IC and a larger bulk capacitor. The total input capacitance should be large enough to limit the input voltage ripple to a desired amplitude. For input ripple voltage  $\triangle V_{IN}$ ,  $C_{IN}$  can be calculated using 方程式 32.

$$C_{IN} \ge \frac{I_{OUT(MAX)}}{4 \times f \times \Delta V_{IN}}$$

(32)

Choosing a  $\triangle$  V<sub>IN</sub> of 0.5 V gives a minimum C<sub>IN</sub> of 0.2  $\upmu$  F. A standard value of 0.47  $\upmu$  F is selected for C<sub>BYP</sub> in this design. A bulk capacitor of higher value reduces voltage spikes due to parasitic inductance between the power source to the converter. A standard value of 2.2  $\upmu$  F is selected for C<sub>IN</sub> in this design. The voltage ratings of the two input capacitors should be greater than the maximum input voltage under all conditions.

#### **8.2.2.2.12 UVLO Resistors**

UVLO resistors  $R_{UV1}$  and  $R_{UV2}$  set the undervoltage lockout threshold and hysteresis according to 方程式 33 and 方程式 34.

$$V_{\text{IN (HYS)}} = I_{\text{HYS}} \times R_{\text{UV2}}$$

(33)

where

I<sub>HYS</sub> = 20 μ A, typical.

$$V_{IN}(UVLO, rising) = 1.225V \times \left(\frac{R_{UV2}}{R_{UV1}} + 1\right)$$

(34)

For a UVLO hysteresis of 2.5 V and UVLO rising threshold of 20 V, 方程式 33 and 方程式 34 require  $R_{UV1}$  of 8.25 k $\Omega$  and  $R_{UV2}$  of 127 k $\Omega$  and these values are selected for this design example.

### 8.2.2.2.13 V<sub>CC</sub> Diode

Diode D2 is an optional diode connected between  $V_{OUT1}$  and the  $V_{CC}$  regulator output pin. When  $V_{OUT1}$  is more than one diode drop greater than the  $V_{CC}$  voltage, the  $V_{CC}$  bias current is supplied from  $V_{OUT1}$ . This results in reduced power losses in the internal  $V_{CC}$  regulator which improves converter efficiency.  $V_{OUT1}$  must be set to a voltage at least one diode drop higher than 8.55 V (the maximum  $V_{CC}$  voltage) if D2 is used to supply bias current.

#### 8.2.2.3 Application Curves

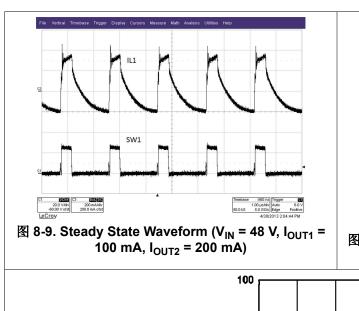

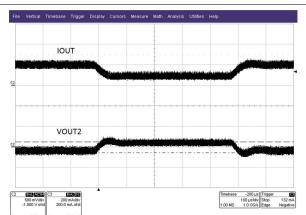

图 8-10. Step Load Response ( $V_{IN}$  = 48 V,  $I_{OUT1}$  = 0 A, Step Load on  $I_{OUT2}$  = 100 mA to 200 mA)

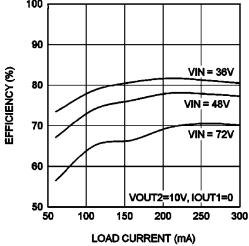

图 8-11. Efficiency at 750 kHz, V<sub>OUT1</sub> = 10 V

### 9 Power Supply Recommendations

$$I_{IN} = \frac{P_{OUT}}{V_{IN} \cdot \eta} \tag{35}$$

where

η is the efficiency

If the regulator is connected to an input supply through long wires or PCB traces with a large impedance, take special care to achieve stable performance. The parasitic inductance and resistance of the input cables may have an adverse affect on converter operation, particularly during operation at low input voltage. The parasitic inductance in combination with the low-ESR ceramic input capacitors form an underdamped resonant circuit. This circuit can cause overvoltage transients at VIN each time the input supply is cycled on and off. The parasitic resistance causes the input voltage to dip during a load transient. The best way to solve such issues is to reduce the distance from the input supply to the regulator and use an aluminum or tantalum input capacitor in parallel with the ceramics. The moderate ESR of the electrolytic capacitors helps to damp the input resonant circuit and reduce any voltage overshoots. A capacitance in the range of 4.7  $\mu$ F to 22  $\mu$ F is usually sufficient to provide input parallel damping and helps to hold the input voltage steady during large load transients.

An EMI input filter is often used in front of the regulator that, unless carefully designed, can lead to instability as well as some of the effects mentioned above. The application report Simple Success with Conducted EMI for DC-DC Converters (SNVA489) provides helpful suggestions when designing an input filter for any switching regulator.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

### 10 Layout

### 10.1 Layout Guidelines

A proper layout is essential for optimum performance of the circuit. In particular, the following guidelines should be observed:

- 1. C<sub>IN</sub>: The loop consisting of input capacitor (C<sub>IN</sub>), V<sub>IN</sub> pin, and RTN pin carries switching currents. Therefore, the input capacitor should be placed close to the IC, directly across V<sub>IN</sub> and RTN pins and the connections to these two pins should be direct to minimize the loop area. In general it is not possible to accommodate all of input capacitance near the IC. A good practice is to use a 0.1- μ F or 0.47- μ F capacitor directly across the V<sub>IN</sub> and RTN pins close to the IC, and the remaining bulk capacitor as close as possible (see 图 10-1).

- 2. C<sub>VCC</sub> and C<sub>BST</sub>: The V<sub>CC</sub> and bootstrap (BST) bypass capacitors supply switching currents to the high and low side gate drivers. These two capacitors should also be placed as close to the IC as possible, and the connecting trace length and loop area should be minimized (see

10-1).

- 3. The Feedback trace carries the output voltage information and a small ripple component that is necessary for proper operation of LM5017. Therefore, care should be taken while routing the feedback trace to avoid coupling any noise to this pin. In particular, feedback trace should not run close to magnetic components, or parallel to any other switching trace.

- 4. SW trace: The SW node switches rapidly between V<sub>IN</sub> and GND every cycle and is therefore a possible source of noise. The SW node area should be minimized. In particular, the SW node should not be inadvertently connected to a copper plane or pour.

### 10.2 Layout Example

图 10-1. Placement of Bypass Capacitors

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

### 11 Device and Documentation Support

### 11.1 Device Support

### 11.1.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

### 11.1.2 Development Support

For development support, see the following:

- LM5017 Buck Converter Quick-start Calculator

- Fly-Buck Converter Quick-start Calculator

- LM5017 PSPICE Transient Model

- LM5017 TINA-TI Transient Spice Model

- LM5017 TINA-TI Transient Reference Design

- For TI's reference design library, visit *TI Reference Designs*

- For TI's WEBENCH Design Environment, visit the WEBENCH® Design Center.

- To view a related device of this product, see the LM5018 100-V, 300-mA synchronous buck converter.

- Power House Blogs:

- Fly-Buck: Frequently Asked Questions (FAQs)

- Lower EMI and Quiet Switching With the Fly-Buck Topology

- Fly-Buck Converter PCB Layout Tips

- When is Fly-Buck the Right Choice for Your Isolated Power Needs?

- How to Design for EMC and Isolation With Fly-Buck Converters

- Create a Fly-Buck Converter in WEBENCH® Power Designer

#### 11.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM5017 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage  $(V_{IN})$ , output voltage  $(V_{OUT})$ , and output current  $(I_{OUT})$  requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 11.2 Documentation Support

### 11.2.1 Related Documentation

For related documentation, see the following:

- AN-2200 LM5017 Evaluation Board (SNVA612)

- AN-2204 LM5017 Isolated Supply Evaluation Board (SNVA611)

- AN-2292 Designing an Isolated Buck (Fly-Buck) Converter (SNVA674)

- AN-1481 Controlling Output Ripple & Achieving ESR Independence in Constant ON-Time Regulator Designs (SNVA166)

- · TI Reference Designs:

- Dual Channel-to-Channel Isolated Universal Analog Input Module for PLC Reference Design (TIDUBI1)

Copyright © 2021 Texas Instruments Incorporated

- High Voltage Stepper Driver Reference Design (TIDUCR6)

- Reference Design for Voltage, Current & Temp Monitoring for Solar Module Level Power Electronics (TIDUCM3)

- High Resolution, Fast Startup Analog Front End for Air Circuit Breaker Reference Design (TIDUB80)

- Signal Processing Front End for Electronic Trip Units Used in ACBs/MCCBs reference design (TIDUA09)

- Ultra-Small 1W, 12V-36V Iso Power Supply for Analog Prog Logic Controller Modules Reference Design (TIDU855)

- 16-Bit Analog Output Module Reference Design for Programmable Logic Controllers (PLCs) (TIDU189)

- 2.5W Bipolar Isolated Fly-Buck Ultra-Compact Reference Design (TIDUCA3)

- Class 3 Isolated Fly-Buck Power Module for PoE Application Reference Design (TIDU779)

- Wide-Input Isolated IGBT Gate-Drive Fly-Buck Power Supply for Three-Phase Inverters (TIDU670)

- Isolated RS-485 to Wi-Fi Bridge with 24 VAC Power Reference Design (TIDUA49)

- Dual-Output Isolated Fly-Buck Reference Design With an Ultra-Small Coupled Inductor (TIDUC31)

- Small Footprint Isolated DC/DC Converter for Analog Input Module Reference Design (TIDUBR7)

- Leakage Current Measurement Reference Design for Determining Insulation Resistance (TIDU873)

- Thermal Protection Reference Design of IGBT Modules for HEV/EV Traction Inverters (TIDUBJ2)

- White Papers:

- Designing Isolated Rails on the Fly With Fly-Buck Converters

- Valuing Wide V<sub>IN</sub>, Low-EMI Synchronous Buck Circuits for Cost-Effective, Demanding Applications

- An Overview of Conducted EMI Specifications for Power Supplies

- An Overview of Radiated EMI Specifications for Power Supplies

- AN-2162: Simple Success with Conducted EMI from DC-DC Converters (SNVA489)

- Using New Thermal Metrics (SBVA025)

- Semiconductor and IC Package Thermal Metrics (SPRA953)

### 11.3 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*订阅更新* 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 11.4 支持资源

TI E2E™ 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 11.5 Trademarks

PowerPAD™ and are trademarks of Texas Instruments.

Fly-Buck<sup>™</sup> and Tl E2E<sup>™</sup> are trademarks of Texas Instruments.

WEBENCH® are registered trademarks of Texas Instruments.

所有商标均为其各自所有者的财产。

### 11.6 静电放电警告

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 11.7 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

Submit Document Feedback

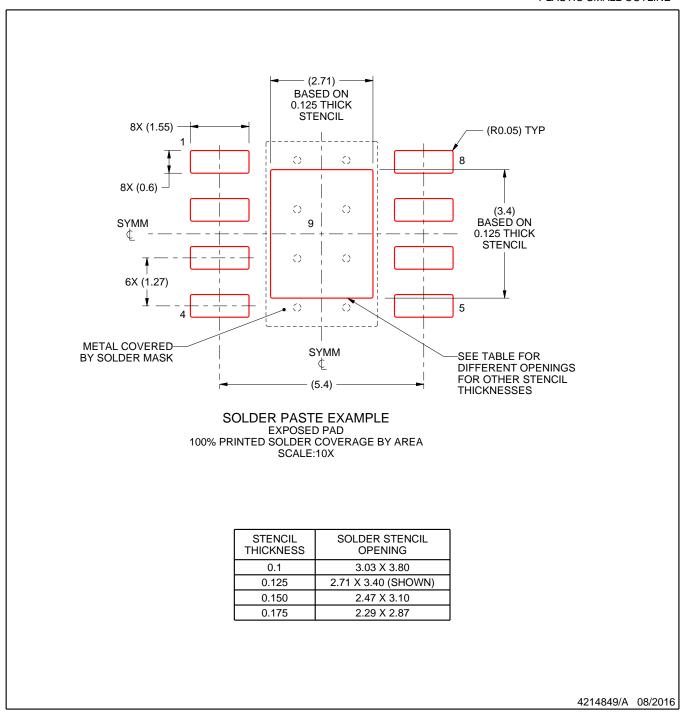

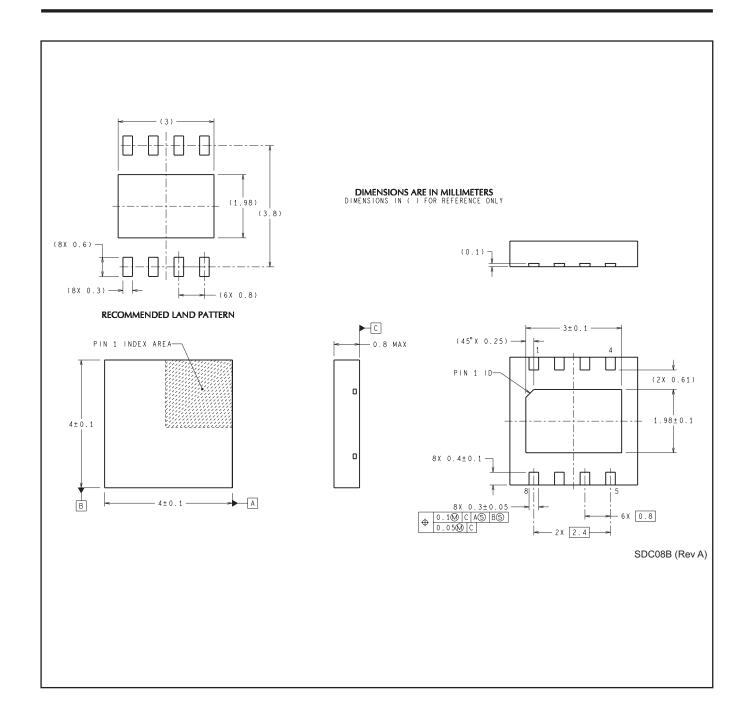

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https://www.ti.com/legal/termsofsale.html) 或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021,德州仪器 (TI) 公司 www.ti.com 2-Jun-2022

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp       | Op Temp (°C) | <b>Device Marking</b> (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|--------------------------------------|---------------------|--------------|-----------------------------|---------|

| LM5017MR/NOPB    | ACTIVE     | SO PowerPAD  | DDA                | 8    | 95             | RoHS & Green | NIPDAU   SN                          | Level-3-260C-168 HR | -40 to 125   | L5017<br>MR                 | Samples |

| LM5017MRE/NOPB   | ACTIVE     | SO PowerPAD  | DDA                | 8    | 250            | RoHS & Green | NIPDAU   SN                          | Level-3-260C-168 HR | -40 to 125   | L5017<br>MR                 | Samples |

| LM5017MRX/NOPB   | ACTIVE     | SO PowerPAD  | DDA                | 8    | 2500           | RoHS & Green | NIPDAU   SN                          | Level-3-260C-168 HR | -40 to 125   | L5017<br>MR                 | Samples |

| LM5017SD/NOPB    | ACTIVE     | WSON         | NGU                | 8    | 1000           | RoHS & Green | SN                                   | Level-1-260C-UNLIM  | -40 to 125   | L5017                       | Samples |

| LM5017SDE/NOPB   | ACTIVE     | WSON         | NGU                | 8    | 250            | RoHS & Green | SN                                   | Level-1-260C-UNLIM  | -40 to 125   | L5017                       | Samples |

| LM5017SDX/NOPB   | ACTIVE     | WSON         | NGU                | 8    | 4500           | RoHS & Green | SN                                   | Level-1-260C-UNLIM  | -40 to 125   | L5017                       | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 2-Jun-2022

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 21-Sep-2022

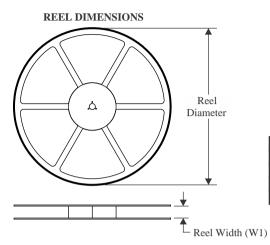

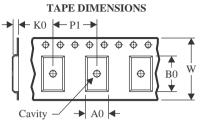

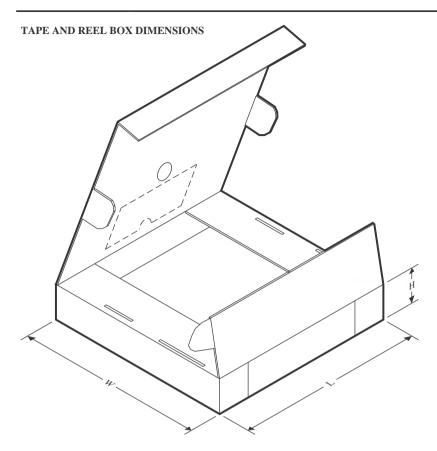

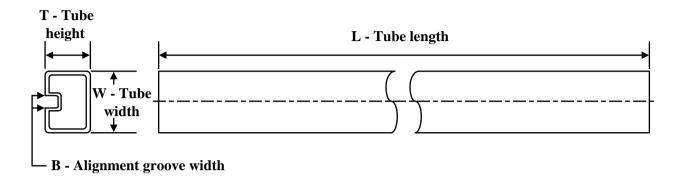

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

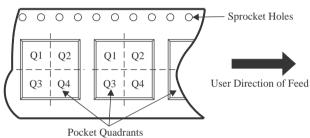

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM5017MRE/NOPB | SO<br>PowerPAD  | DDA                | 8 | 250  | 178.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM5017MRE/NOPB | SO<br>PowerPAD  | DDA                | 8 | 250  | 330.0                    | 12.5                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| LM5017MRX/NOPB | SO<br>PowerPAD  | DDA                | 8 | 2500 | 330.0                    | 12.5                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |