ZHCSBC9D – APRIL 2013 – REVISED JANUARY 2014

Tools &

Software

# 交流-直流准谐振电流模式脉宽调制 (PWM) 控制器

## 特性

www.ti.com.cn

- 临界传导模式

- 峰值电流模式控制模式

- 针对低待机功耗的跳周模式

- 针对持续过载保护的断续模式

- 逐周期过流保护可保持通用交流线路上的准确度

- 线路电流前馈

- 通过感测辅助绕组的 OVP 保护

- 集成 0.7A 峰值栅极驱动器

- 直接光耦合器件接口

- 电流感测信号的前缘消隐

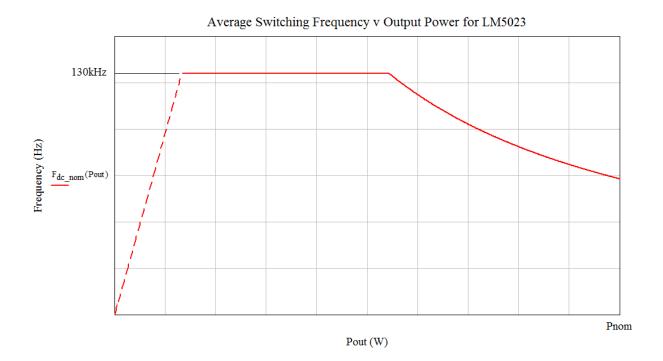

- 最高频率钳位 130kHz

- 可编程软启动

- 热关断

- 8 引脚表面贴装小外形尺寸 (MSOP) 封装

## 应用范围

- 通用输入交流-直流笔记本电脑适配器 10W 至 65W

- 高效辅助电路和辅助电源

- 电池充电器

- 消费类电子产品(**DVD**播放器、机顶盒、数字电视、游戏机、打印机等)

## 说明

LM5023 是一款准谐振脉宽调制 (PWM) 控制器,此控制器包含有实现一个高效离线电源所需的全部功能。 LM5023 使用变压器辅助绕组来实现消磁检测,从而确保了临界传导模式 (CCM) 运行。LM5023 特有一个用于过流保护的断续模式,它具有的自动重启功能可减少过载期间功率元件上的应力。针对节能应用(ENERGY STAR®, CEPCP等)的跳周模式可在轻负载时减少功耗。LM5023 还使用变压器辅助绕组来实现输出过压 (OVP) 保护,如果检测到 OVP 故障,LM5023 就锁存控制器。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ÆΑ

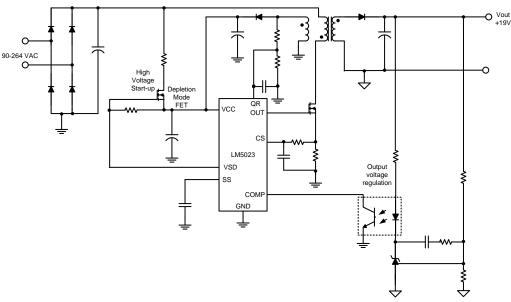

## 经简化电路原理图

## ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                         | VALUE | MIN MAX           |      |

|------------------|-------------------------------------------------------------------------|-------|-------------------|------|

|                  |                                                                         | MIN   | MAX               | UNIT |

| I <sub>QR</sub>  | Negative Injection Current When the QR Pin is Being Driven Below Ground | _     | 4                 | mA   |

| VSD              | Maximum Voltage                                                         | -0.3  | 45                | V    |

| I <sub>VSD</sub> | VSD Clamp Continuous Current                                            | -     | 500               | μA   |

| Voltage<br>Range | SS, COMP, QR                                                            | -0.3  | 7                 | V    |

| Voltage<br>Range | CS                                                                      | -0.3  | 1.25              | V    |

| OUT              | Gate-Drive Voltage at DRV                                               | -0.3  | Self-<br>limiting | V    |

| I <sub>OUT</sub> | Peak OUT Current, Source                                                | -     | 0.3               | А    |

| IOUT             | Peak OUT Current Sink                                                   | -     | 0.7               | А    |

| VCC              | Bias Supply Voltage                                                     | -0.3  | 16                | V    |

| TJ               | Operating Junction Temperature Range                                    | -40   | +125              | °C   |

| T <sub>STG</sub> | Storage Temperature                                                     | -55   | +150              | °C   |

| ESD              | Human Body Model (HBM) JESD22-A114                                      |       | 2                 | kV   |

|                  | Charged-Device Model (CDM) JESD22-C101                                  |       | 1                 | kV   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

### THERMAL CHARACTERISTICS

|               |                            |     | UNIT |

|---------------|----------------------------|-----|------|

| $\theta_{JA}$ | MSOP-8 Junction to Ambient | 107 | °C/W |

(1) The package thermal impedance is calculated in accordance with JESD 51-7.

### **RECOMMENDED OPERATING CONDITIONS**

|                  |                      | MIN | MAX | UNIT |

|------------------|----------------------|-----|-----|------|

| VCC              | Bias Supply Voltage  | 8   | 14  | V    |

| I <sub>VSD</sub> | Current Sense        | 2   | 10  | μA   |

| I <sub>QR</sub>  | QR Pin Current       | 1   | 4   | mA   |

| TJ               | Junction Temperature | -40 | 125 | °C   |

ZHCSBC9D - APRIL 2013-REVISED JANUARY 2014

www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS**

Minimum and Maximum apply over the junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $+25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise specified, the following conditions apply: VCC = 10 V,  $F_{SW} = 100 \text{ kHz} 50\%$  Duty Cycle, No Load on OUT.

|                      | PARAMETER                            | TEST CONDITIONS                                                                   | MIN  | TYP  | MAX  | UNIT |

|----------------------|--------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| BIAS SUPP            |                                      | · · · · ·                                                                         |      |      |      |      |

| VCC <sub>ON</sub>    | Controller enable threshold          |                                                                                   | 12   | 12.8 | 13.5 | V    |

| VCC <sub>OFF</sub>   | Minimum operating voltage            |                                                                                   | 7.0  | 7.5  | 8.0  | V    |

| V <sub>RST</sub>     | Internal logic reset (fault latch)   |                                                                                   | 4.5  | 5.0  | 5.5  | V    |

| ICC <sub>ST</sub>    | ICC current while in standby mode    | COMP = 0.5V, CS = 0 V, no switching                                               |      | 340  | 420  | μA   |

| ICC <sub>OP</sub>    | Operating supply current             | COMP = 2.25 V, OUT switching                                                      |      | 800  |      | μA   |

| SHUTDOW              | N CONTROL (VSD pin)                  |                                                                                   |      |      |      |      |

| IVSD OFF             | Off state leakage current            |                                                                                   |      | 0.1  |      | μA   |

| V <sub>VSD ON1</sub> | ON state pull-down voltage at 10 uA  | After VCC <sub>ON</sub> ( $I_{VSD}$ = 10 uA)                                      |      | 0.65 |      | V    |

| V <sub>VSD_ON2</sub> | ON state pull-down voltage at 100 uA | After VCC <sub>ON</sub> ( $I_{VSD}$ = 100 uA)                                     |      | 0.84 |      | V    |

| SKIP CYCL            | E MODE COMPARATOR                    |                                                                                   |      |      |      |      |

| V <sub>SKIP</sub>    | Skip cycle mode enable threshold     | CS Rising                                                                         | 70   | 120  | 170  | mV   |

| V <sub>SK-HYS</sub>  | Skip cycle mode hysteresis           |                                                                                   |      | 12   |      | mV   |

| QR DETEC             | т                                    |                                                                                   |      |      |      |      |

| V <sub>OVP</sub>     | Overvoltage comparator threshold     |                                                                                   | 2.85 | 3    | 3.17 | V    |

| T <sub>OVP</sub>     | Sample delay for OVP                 |                                                                                   | 870  | 1050 | 1270 | ns   |

| V <sub>DEM</sub>     | VDEM demagnetization threshold       |                                                                                   |      | 0.35 |      | V    |

| F <sub>MAX</sub>     | Maximum frequency                    |                                                                                   | 114  | 130  | 148  | kHz  |

| T <sub>RST</sub>     | T <sub>RESTART</sub>                 |                                                                                   | 9.4  | 12   | 15.7 | μs   |

| PWM COM              | PARATORS                             |                                                                                   |      |      |      |      |

| TP <sub>PWM</sub>    | COMP to OUT delay                    | COMP set to 2 V CS stepped 0 to 0.4 V, time to OUT transition low, $C_{LOAD} = 0$ |      | 20   |      | ns   |

| D <sub>MIN</sub>     | Minimum duty cycle                   | COMP = 0 V                                                                        |      |      | 0    | %    |

| G <sub>COMP</sub>    | COMP to PWM comparator gain          |                                                                                   |      | 0.33 |      |      |

| V <sub>COMP-O</sub>  | COMP open circuit voltage            | I(COMP)=20µa                                                                      | 4.3  | 4.9  | 5.8  | V    |

| V <sub>COMP-H</sub>  | COMP at maximum VCS                  |                                                                                   |      | 2.25 |      | V    |

| I <sub>COMP</sub>    | COMP short circuit current           | COMP = 0 V                                                                        |      | 132  |      | μA   |

| R <sub>COMP</sub>    | R pull-up                            |                                                                                   | 41   | 45   | 49   | kΩ   |

## **ELECTRICAL CHARACTERISTICS (continued)**

Minimum and Maximum apply over the junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $+25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise specified, the following conditions apply: VCC = 10 V,  $F_{SW} = 100 \text{ kHz} 50\%$  Duty Cycle, No Load on OUT.

| PARAMETER            |                                        | TEST CONDITIONS                                                             | MIN | TYP            | MAX | UNIT |

|----------------------|----------------------------------------|-----------------------------------------------------------------------------|-----|----------------|-----|------|

| CURRENT              | LIMIT                                  |                                                                             |     |                |     |      |

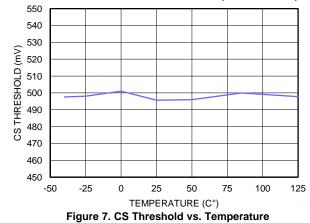

| V <sub>CS</sub>      | Cycle-by-cycle sense voltage threshold |                                                                             | 450 | 450 500<br>130 |     | mV   |

| T <sub>LEB</sub>     | Leading edge blanking time             |                                                                             |     | 130            |     | ns   |

| T <sub>PCS</sub>     | Current limit to OUT delay             | CS step from 0 to 0.6 V time to onset of OUT transition low, $C_{LOAD} = 0$ |     | 22             |     | ns   |

| R <sub>LEB</sub>     | CS blanking sinking impedance          |                                                                             |     | 15             | 35  | Ω    |

| G <sub>CM</sub>      | Current mirror gain                    | I <sub>QR</sub> = 2 ma                                                      |     | 100            |     | A/A  |

| C <sub>FF</sub>      | Current feed forward                   | I <sub>QR</sub> = 2 ma                                                      |     | 140            |     | mV   |

| HICCUP M             | ODE                                    |                                                                             |     |                |     |      |

| T <sub>OL</sub> _10  | Over load detection timer              | I <sub>VSD</sub> = 10 uA                                                    |     | 12             |     | ms   |

| T <sub>OL</sub> _100 | Over load detection timer              | I <sub>VSD</sub> = 100 uA                                                   |     | 1.2            |     | ms   |

| OUTPUT G             | GATE DRIVER                            |                                                                             |     |                |     |      |

| V <sub>OH</sub>      | OUT high saturated                     | I <sub>OUT</sub> = 50 mA, VCC-OUT                                           |     | 0.3            | 1.1 | V    |

| V <sub>OL</sub>      | OUT low saturated                      | I <sub>OUT</sub> = 100 mA                                                   |     | 0.3            | 1   | V    |

| I <sub>PH</sub>      | Peak OUT source current                | OUT = VCC/2                                                                 |     | 0.3            |     | А    |

| I <sub>PL</sub>      | Peak OUT sink current                  | OUT = VCC/2                                                                 |     | 0.7            |     | А    |

| t <sub>r</sub>       | Rise time                              | C <sub>LOAD</sub> = 1 nF                                                    |     | 25             |     | ns   |

| t <sub>f</sub>       | Fall time                              | C <sub>LOAD</sub> = 1 nF                                                    |     | 15             |     | ns   |

| SOFT-STA             | RT                                     |                                                                             |     |                |     |      |

| I <sub>SS</sub>      | Soft-start                             |                                                                             | 17  | 22             | 30  | μA   |

| THERMAL              |                                        |                                                                             |     |                |     |      |

| T <sub>SD</sub>      | Thermal shutdown temp                  |                                                                             |     | 165            |     | °C   |

ZHCSBC9D - APRIL 2013-REVISED JANUARY 2014

#### www.ti.com.cn

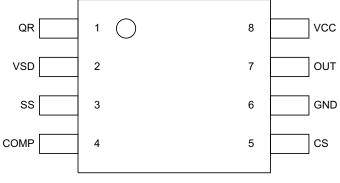

## **PIN FUNCTIONS**

| NAME | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| COMP | 4   | I    | Control input for the Pulse Width Modulator and Skip cycle comparators.<br>COMP pull-up is provided by an internal 42 K resistor which may be<br>used to bias an opto-coupler transistor.                                                                                                                                                                         |  |  |  |  |

| CS   | 5   | I    | Current sense input for current mode control and over-current protection.<br>Current limiting is accomplished using a dedicated current sense<br>comparator. If the CS comparator input exceeds 0.5 V, the OUT pin<br>switches low for cycle-by-cycle current limit. CS is held low for 90 ns<br>after OUT switches high to blank the leading edge current spike. |  |  |  |  |

| GND  | 6   | G    | Ground connection return for internal circuits.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| OUT  | 7   | 0    | High current output to the external MOSFET gate input with source/sir current capability of 0.3 A and 0.7 A respectively.                                                                                                                                                                                                                                         |  |  |  |  |

| QR   | 1   | I    | The auxiliary FLYBACK winding of the power transformer is monitored to detect the Quasi-Resonant operation. The peak auxiliary voltage is sensed to detect an output overvoltage (OVP) fault and shuts down the controller.                                                                                                                                       |  |  |  |  |

| SS   | 3   | 0    | An external capacitor and an internal 22 $\mu\text{A}$ current source sets the soft-start ramp.                                                                                                                                                                                                                                                                   |  |  |  |  |

| VSD  | 2   | 0    | Connect this pin to the Gate of the external start-up circuit FET; it will disable the start-up FET after VCC is valid.                                                                                                                                                                                                                                           |  |  |  |  |

| VCC  | 8   | Р    | VCC provides bias to controller and gate drive sections of the LM5023.<br>An external capacitor must be connected from this pin to ground.                                                                                                                                                                                                                        |  |  |  |  |

## **DEVICE INFORMATION**

LM5023 Pin Configuration

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

TEXAS INSTRUMENTS

www.ti.com.cn

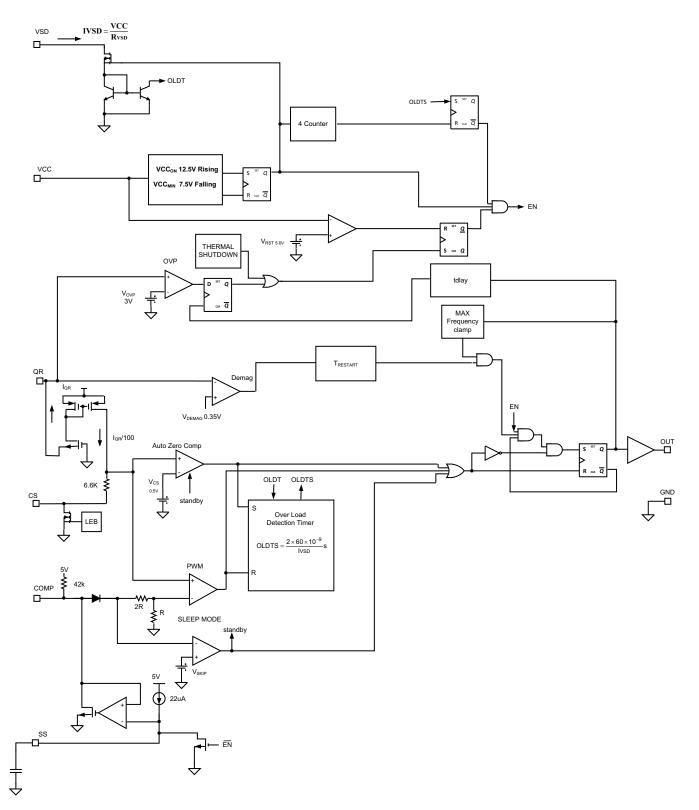

## FUNCTIONAL BLOCK DIAGRAM

#### ZHCSBC9D - APRIL 2013 - REVISED JANUARY 2014

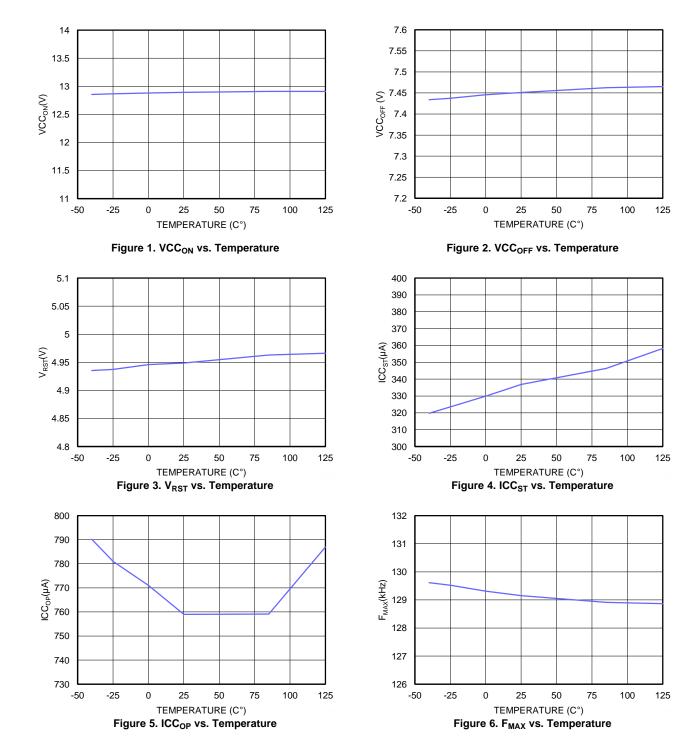

## **TYPICAL CHARACTERISTICS**

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

## **TYPICAL CHARACTERISTICS (continued)**

#### **FUNCTIONAL DESCRIPTION**

The LM5023 is a Quasi-Resonant controller which contains all of the features needed to implement a highly efficient off-line power supply. The LM5023 uses the transformer auxiliary winding for demagnetization detection to ensure Quasi-Resonant operation (Valley-Switching) to minimize switching losses. For application that need to meet the ENERGY STAR® low standby power requirements, the LM5023 features an extremely low lq current (346 µA) and skip cycle mode which reduces power consumption at light loads. The LM5023 uses a feedback signal from the output to provide a very accurate output voltage regulation <1%. To reduce overheating and stress during a sustained overload conditions the LM5023 offers a hiccup mode for over current protection and provides a current limit restart timer to disable the outputs and forcing a delayed restart (hiccup mode).

For offline start-up, an external Depletion Mode N Channel MOSFET can be used. This method is recommended for applications where a very low standby power (<50 mW) is required. For application where a low standby power is not as critical an enhancement mode, N Channel MOSFET can be used. If an OVP is detected on the auxiliary winding (QR pin), the IC permanently latches off, requiring recycling of power to restart Additional features include line-current-feed forward, pulse-by-pulse current limit, and a maximum frequency clamp of 130 kHz.

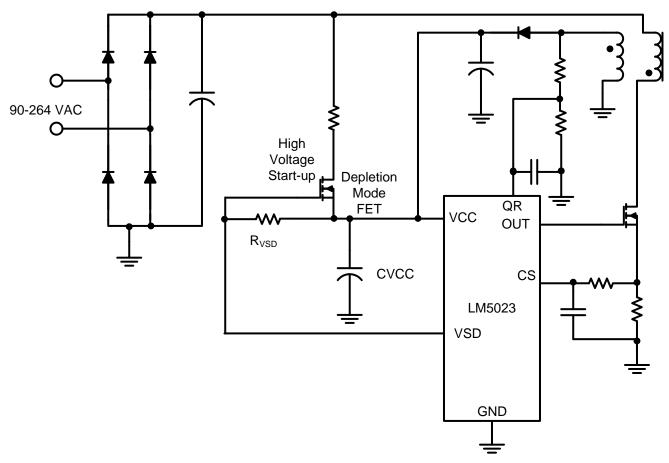

#### START-UP

Referring to Figure 8, when the AC rectified line voltage is applied to the bulk energy storage capacitor; the N Channel Depletion Mode MOSFET is turned on and supplies the charging current to the VCC capacitor. When the voltage on the VCC pin reaches 12.5 V typical, the PWM controller, soft-start circuit and gate driver are enabled.

When the LM5023 is enabled and the OUT drive signal starts switching the Flyback MOSFET, energy is being stored and then transferred from the transformer primary to the secondary windings. A bias winding, shown in Figure 8, delivers energy to the VCC capacitor to sustain the voltage on the VCC pin. The voltage supplied from the auxiliary winding should be within the range of 10 V to 14 V (where 16 V is the absolute maximum rating).

After reaching the VCC<sub>ON</sub> threshold the LM5023 VSD open Drain output, which is pulled up to VCC during startup, goes low. This applies a negative Gate to Source voltage on the Depletion Mode MOSFET turning it off. This disables the high voltage start-up circuit. The high voltage start-up circuit can be implemented in either of two ways; the first is shown in Figure 8, which uses an N Channel Depletion Mode FET, the second is shown in Figure 9, which uses an N Channel Enhancement Mode FET. The circuit using the Depletion Mode FET will have the lowest standby power. The standby power consumption of the FET is the voltage across the start-up FET multiplied by the Drain to Source Cutoff current with Gate negatively biased, this is typically 0.1  $\mu$ A.

Standby Power of the Start-up FET calculation:

- Vin = 230Vac

- VCC = 10V

- Vdcmax = 230Vac  $\sqrt{2}$  = 325Vdc

- $I_{DOFF}=0.1\mu A,\ I_{DOFF}$  is the Depletion MODE FETs leakage current

- $Pd = IDOFF \bullet Vdcmax = 0.1uA \bullet 325Vdc = 32.5\mu W$

When VCC < VCC(on) the current consumption of the  $I_C = I_{CC(st)}$ , nominally 340  $\mu$ A.

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

www.ti.com.cn

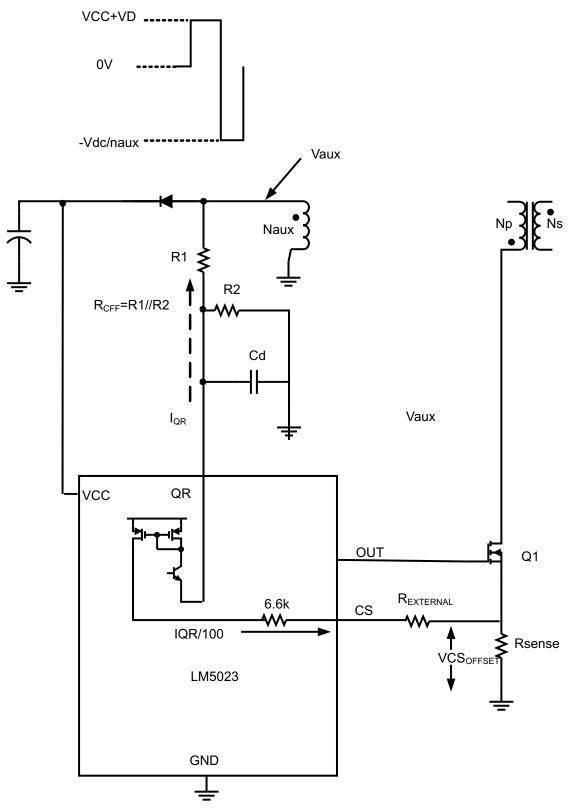

Figure 8. Start-Up With a Depletion Mode FET

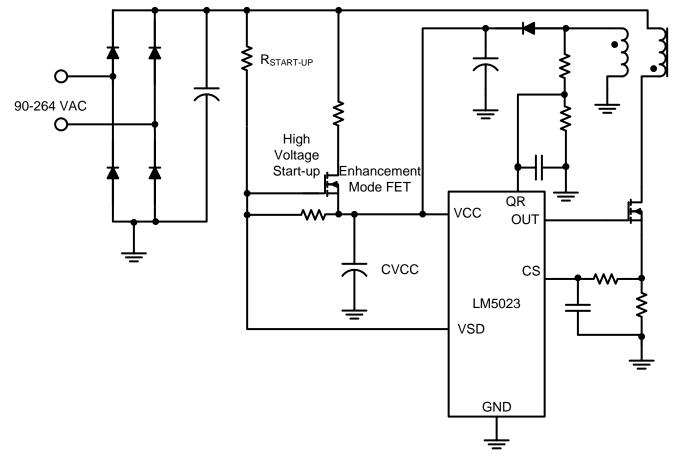

An alternative start-up circuit employs an Enhancement Mode FET with resistors connected from the rectified dc bus to the Gate of the FET, Figure 9. After the input AC power is applied the Enhancement Mode FET supplies the charging current to the VCC capacitor  $C_{VCC}$ . After reaching the VCC<sub>ON</sub> threshold the LM5023 VSD open Drain output, which is pulled up to VCC during start-up, goes low. This grounds the Gate of the start-up MOSFET turning it off. The start-up resistors are always in the circuit, therefore the standby power consumed will be higher than if a Depletion Mode FET were used.

• Vin = 230 Vac

- Vdcmax = 230Vac  $\sqrt{2}$  = 325Vdc

- Rstart up =  $10M\Omega$

$$P_{Re sistors} = \frac{Vdc^2}{D} = \frac{325^2}{1000} = 10.56 \text{mW}$$

• Resistors

$$-\frac{1}{R}$$

Restart  $-up -\frac{1}{10M\Omega} = 10.3$

Figure 9. Start-Up With an Enhancement Mode FET

### **Quasi Resonant Operation**

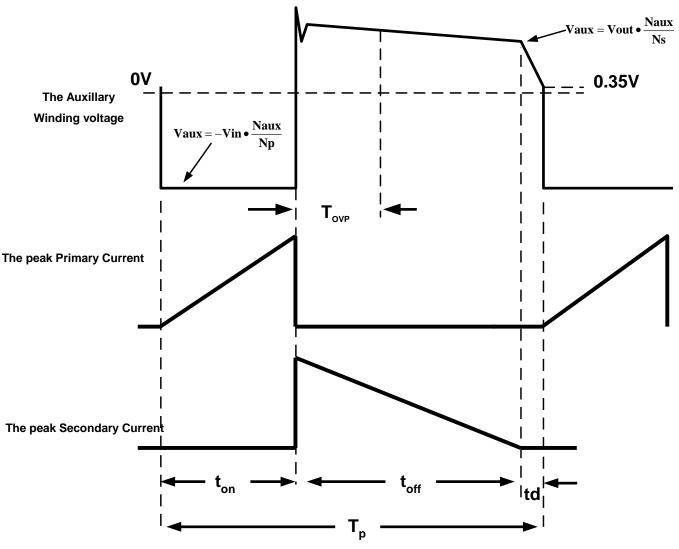

A Quasi-Resonant controlled Flyback converter operates by storing energy in the transformers primary during the MOSFETs on-time. During the on-time ( $T_{ON}$ ) VIN is applied across the primary of the transformer. The primary current starts out at zero and ramps towards a peak value ( $I_{PEAK}$ ). When the peak primary current reaches the feedback compensation error voltage the PWM comparator resets the output drive, turning off the MOSFET. Due to the phasing of the transformer, the output diode is reversed biased during the MOSFET on-time.

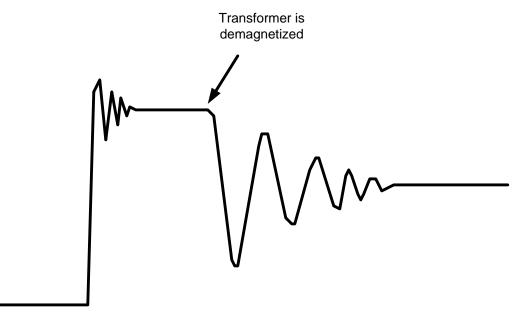

During the MOSFETs off time the output diode is forward biased and the stored energy in the transformer primary inductor is transferred to the output. The voltage seen on the secondary inductor is  $V_{OUT}$  plus the output diodes forward voltage drop, V<sub>F</sub>. The current in the output inductor linearly decreases from  $I_{PEAK} \bullet Ns/Np$  to zero, refer to Figure 11.

When the current in the secondary reaches zero, the transformer is demagnetized, and there is an open circuit on the secondary, and with the primary MOSFET also turned off, there is an open on the primary. A resonant circuit is formed between the transformers primary inductance and the MOSFET output capacitance. The resonant frequency is calculated by:

### Freq = $2 \cdot \pi \sqrt{Lp \cdot COSS}$

During the resonant period the Drain voltage of the MOSFET will ring down towards ground, refer to Figure 10. When the Drain voltage is at its minimum the Flyback MOSFET is turned back on. The point where the voltage is at its minimum is calculated by:

$td = \pi \bullet \sqrt{Lp \bullet COSS}$

Copyright © 2013–2014, Texas Instruments Incorporated

Figure 10. The Flyback Drain Voltage Waveform

Transformer demagnetization is detected by sensing the transformers auxiliary winding. When the transformer is demagnetized the auxiliary winding voltage follows the Drain of the MOSFET and changes from Vout•Naux/Ns to -Vin•Naux/Np. Internal to the LM5203 QR pin is a comparator with a 0.35 V reference. As the auxiliary winding voltage falls below 0.35 V, the voltage is sensed and the comparator sets the PWM Flip-Flop turning on the Flyback MOSFET. Figure 11 shows the QR Converter typical waveforms; the auxiliary winding voltage, primary, and secondary current waveforms. It is possible to adjustable the delay on the auxiliary winding with a resistor and external capacitor to ensures that the MOSFET switches when its Drain voltage is at its minimum, refer to the schematic in Figure 14 and the section on Valley Switching for details. The benefits of QR operation are reduced EMI, and turn-on switching losses.

ZHCSBC9D - APRIL 2013-REVISED JANUARY 2014

Figure 11. QR Converter Typical Waveforms

## **Quasi Resonant Operating Frequency**

When the primary side Flyback MOSFET turns on, the current ramps up until the peak primary current exceeds the feedback compensation error voltage. When this occurs the PWM comparator resets the output drive, turning off the MOSFET. The current ramps up with a slope of:

$\frac{\text{Vin}}{\text{Lp}} = \frac{\text{di}}{\text{dt}}$

The t<sub>ON</sub> time of the switch is calculated by:

$$\mathsf{ton} = \frac{\mathsf{Lp}}{\mathsf{Vin}} \bullet \mathsf{lpk}$$

When the primary side Flyback MOSFET is turned off, the energy stored in the primary inductance is transfer to the secondary inductance, the off time to transfer all of the energy is:

$$toff = Ipk \bullet \frac{n \bullet Lp}{Vo + Vf}$$

## LM5023

ZHCSBC9D - APRIL 2013 - REVISED JANUARY 2014

www.ti.com.cn

The total switching period is:

Tp = ton + toff + tdly

The resonant circuit created by the transformer primary inductance and the MOSFETs output capacitance is the tdly time, refer to Figure 11.

tdly =

$$\frac{\pi}{2} \bullet \sqrt{Lp \bullet COSS}$$

Pout =  $\frac{1}{2} \bullet Lp \bullet Ipk^2 \bullet Freq \bullet \eta$

Combining equations:

F

Freq :=

$$\frac{1}{\left[ Lp \cdot 2 \cdot Pout \cdot \left[ \frac{n \cdot (Vo + Vf + Vin)}{\eta \cdot [Vin \cdot [n \cdot (Vo + Vf)]]} \right]^2 \right] + tdly}$$

1

From inspection of the equations, it can be seen that the QR Flyback converter does not operate at a fixed frequency. The frequency varies with the output load, input line voltage, or a combination of the two. In order to keep LM5023 frequency below the EMI starting limit of 150 kHz per CISPR--22, the LM5023 has an internal timer which prevents the output drive from restarting within 7.69 µs of the previous driver output (OUT) high to low transition. This timer clamps the maximum switching frequency from exceeding 130 kHz (typical).

## **PWM Comparator**

The PWM comparator compares the current sense signal with the loop error voltage from the COMP pin. The COMP pin voltage is reduced by a fixed 0.75 V offset and then attenuated by a 3:1 resistor divider. The PWM comparator input offset voltage is designed such that less than 0.75 V at the COMP pin will result in a zero duty cycle at the controller output.

## Soft-Start

The soft-start feature allows the power converter to gradually reach the initial steady state operating point, thereby reducing start-up stresses and current surges. At power on, after the VCC reaches the VCC<sub>ON</sub> threshold an internal 22 µA current source charges an external capacitor connected to the SS pin. The capacitor voltage will ramp up slowly and will limit the COMP pin voltage and the duty cycle of the output pulses.

## **Gate Driver**

The LM5023 driver (OUT) was designed to drive the gate of an N Channel MOSFET and is capable of sourcing a peak current of 0.4 A and sinking 0.7 A.

## **Skip Cycle Operation**

During light load conditions, the efficiency of the switching power supply typically drops as the losses associated with switching and operating bias currents of the converter become a significant percentage of the power delivered to the load. The largest component of the power loss is the switching loss associated with the gate driver and external MOSFET gate charge. Each PWM cycle consumes a finite amount of energy as the MOSFET is turned on and then turned off. These switching losses are proportional to the frequency of operation.

To improve the light load efficiency the LM5023 enters a Skip Cycle mode during light load conditions. As the output load is decreased, the COMP pin voltage is reduced by the voltage feedback loop to reduce the Flyback converters peak primary current. Referring to the Block Diagram, the PWM comparator input tracks the COMP pin voltage through a 0.75 V level shift circuit and a 3:1 resistor divider. As the COMP pin voltage falls, the input to the PWM comparator falls proportionately. When the PWM comparator input falls to 125 mV, the Skip Cycle comparator detects the light load condition and disables output pulses from the controller. The LM5023 also reduces all internal bias currents, while in skip mode, to further reduce quiescent power. The controller continues to skip switching cycles until the power supply output falls and the COMP pin voltage increases to demand more output current. The number of cycles skipped will depend on the load and the response time of the frequency

voltage loop compensation network. Eventually the COMP voltage will increase when the voltage loop requires more current to sustain the regulated output voltage. When the PWM comparator input exceeds 135 mV (10 mV hysteresis), normal fixed frequency switching resumes. Typical light load operation power supply designs will produce a short burst of output pulses followed by a long skip cycle interval (no drive pulses). The result is a large reduction in the average input power.

Figure 12. LM5023 Modulation Curve

### **Current Limit/Current Sense**

The LM5023 provides a cycle-by-cycle over current protection feature. Current limit is triggered by an internal current sense comparator with a threshold of 500 mV. If the CS pin voltage plus the current limit feed forward signal voltage exceeds 500 mV, the MOSFET drive signal (OUT) will be terminated. An RC filter, located near the LM5023 CS pin is recommended to attenuate the noise coupled from the power FET's gate to source switching. The CS pin capacitance is discharged at the end of each PWM cycle by an internal switch. The discharge switch remains on for an additional 90 ns for Leading Edge Blanking (LEB). LEB prevents the LM5023 current sense comparator from being falsely triggered due to the noise generated by the switch currents initial spike. The LM5023 current sense comparator is very fast, and may respond to short duration noise pulses. Layout considerations are critical for the current sense filter and sense resistor. The capacitor associated with the CS filter must be placed very close to the device and connected directly to the pins of the IC (CS and GND). If a current sense transformer is used, both leads of the transformer secondary should be routed to the sense resistor, which should also be located close to the IC. If a current sense resistor located in the power FET's source is used for current sense, a low inductance resistor is required. In this case, all of the noise sensitive low current grounds should be connected in common near the IC and then a single connection should be made.

LM5023

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

www.ti.com.cn

## **APPLICATION INFORMATION**

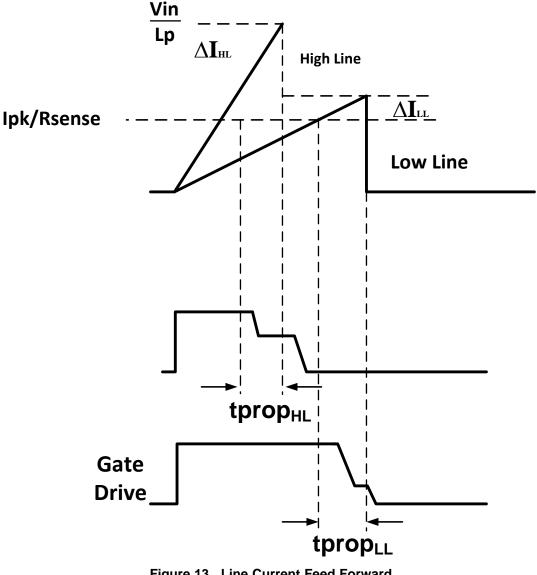

## Line Current Limit Feed Forward

In a peak current mode controlled when the power supply is in an overload, the peak current (measured across the current sense resistor VCS) is compared to a voltage reference for overload protection. If the peak current exceeds the reference the LM5023 controller will turn off the primary side Flyback MOSFET on a cycle-by-cycle basls. However, the primary switch can't be turned off instantly, as there are several unavoidable delays. The first delay is caused by the LEB circuit which provides leading-edge blanking. The second delay is caused by the propagation delay between the detecting point of VCS and the actual turn off of the power MOSFET. The total delay time (tprop) refer to Figure 13, includes the current limit comparator, the logic, the gate driver, and the power MOSFET turning off.

The propagation delay causes the peak primary current to overshoot, the overshoot increase the maximum peak current beyond the calculated value. The peak current overshoot increase as the AC line voltage increase because of the increase in the slope of the primary current:

$$\frac{\text{Vin}}{\text{Lp}} = \frac{\text{di}}{\text{tprop}}$$

This increase in the peak input current overshoot causes a wide variation of overpower limit in a Flyback converter. In Figure 4, it can be seen that the overpower limit increases with the input line voltage, because of lpkmax increase:

$$lpk max = \sqrt{\frac{Pout \bullet 2}{Lp \bullet Freq \bullet \eta}} + \frac{Vin}{Lp} \bullet tprop$$

$$Pin = \frac{1}{2} \bullet lpk max^{2} \bullet Lp \bullet Freq$$

$$Pout = \frac{Pin}{\eta}$$

Figure 13. Line Current Feed Forward

To improve the overpower limit accuracy over the full Universal Input Line; the LM5023 integrates Line Current Limit Feed Forward. Line Current Limit Feed Forward improve the overpower limit by summing a current proportional to the input rectified line into the current sense resistor R<sub>SENSE</sub>), refer to Figure 14. The current proportional to the input line biases up the current sense pin, this turns off the Flyback MOSFET earlier at high input line. This feature compensates for the propagation delays creating a overpower protection that is nearly constant over the Universal Input Line.

To implement Line Current Limit Feed Forward, the first step is to calculate the QR switching frequency at low line and then at high line when the power supply is operating in current limit.

For our example:

- $Lp = 400 \, \mu H$

- $R_{SENSE} = 0.15 \Omega$

- $Vdc_{min} = 127 V$

- $Vdc_{max} = 325 V$

- Tprop = 160 ns

- $V_{CS} = 0.5 V$

## LM5023

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

www.ti.com.cn

- naux = 10.9

- n = ns/np = .167

- tdly = 580 ns

$$Freq\_LL = \frac{1}{\left(\frac{V_{CS}}{Rsense}\right) \bullet Lp \bullet \left[\left(\frac{1}{Vdc_{min}}\right) + \frac{1}{(Vout + Vf) \bullet n}\right] + tdly}$$

$$Freq\_LL = \frac{1}{\left(\frac{0.5V}{0.15\Omega}\right) \bullet 400\mu H \bullet \left[\left(\frac{1}{127V}\right) + \frac{1}{(19V + 0.7V) \bullet 6}\right] + 580ns} = 49.6 \text{kHz}$$

$$Freq\_HL = \frac{1}{\left(\frac{V_{CS}}{Rsense}\right) \bullet Lp \bullet \left[\left(\frac{1}{Vdc_{max}}\right) + \frac{1}{(Vout + Vf) \bullet 6}\right] + tdly}$$

$$Freq\_HL = \frac{1}{\left(\frac{0.5V}{0.15\Omega}\right) \bullet 400\mu H \bullet \left[\left(\frac{1}{325V}\right) + \frac{1}{(19V + 0.7V) \bullet 6}\right] + 580ns} = 62.3 \text{kHz}$$

The next step is to calculate the uncompensated output power at the minimum and maximum input line voltage while in current limit.

Pout\_LL =

$$\frac{1}{2} \cdot Lp \cdot \left(\frac{VCS}{Rsense}\right)^2 \cdot Freq_LL \cdot \eta$$

Pout\_LL =  $\frac{1}{2} \cdot 400\mu H \cdot \left(\frac{0.5}{0.15}\right)^2 \cdot 49.6 \text{kHz} \cdot 0.86 = 94.9 \text{W}$

Pout\_HL =  $\frac{1}{2} \cdot Lp \cdot \left(\frac{VCS}{Rsense}\right)^2 \cdot Freq_HL \cdot \eta$

Pout\_HL =  $\frac{1}{2} \cdot 400\mu H \cdot \left(\frac{0.5}{0.15}\right)^2 \cdot 62.3 \text{kHz} \cdot 0.86 = 119.1 \text{W}$

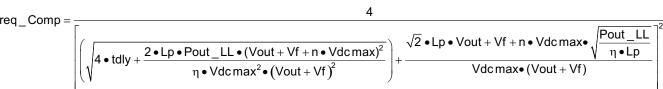

Step three is to calculate the peak current at high line so it does not deliver more power than while it is operating at low line (94.9 W). One thing that complicates the Line Current Limit Feed Forward calculation is that with Quasi Resonant operation the switching frequency changes with line and load. We have two equations and two unknowns, the peak primary current and the QR frequency. This requires use of the quadratic equation:

$$ax^2 + Bx + C = 0$$

The positive root is:

$$x = \frac{\left(B + \sqrt{B^2 + 4DT}\right)}{4}$$

Freq\_Comp =

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

$$Freq\_Comp = \frac{4}{\left[\left(\sqrt{4 \cdot 580ns + \frac{2 \cdot 400\mu H \cdot 94.9 \cdot (19 + 0.7 + 0.167 \cdot 325V)^2}{0.86 \cdot 325V^2 \cdot (19V + 0.7V)^2}}\right) + \frac{\sqrt{2} \cdot 400\mu H \cdot (19V + 0.7V + 0.167 \cdot 325V) \cdot \sqrt{\frac{94.9W}{0.86 \cdot 400\mu H}}}{325V \cdot (19V + 0.7V)}\right]^2} = 76.8kHz$$

Step four is to calculate the peak current.

$$IL max\_LL = \sqrt{\frac{2 \cdot Pout\_LL}{\eta \cdot Lp \cdot Freq\_Comp}}$$

$$IL max\_LL = \sqrt{\frac{2 \cdot 94.9W}{0.86 \cdot 400\mu H \cdot 76.8kHz}} = 2.679Apk$$

$$VCS\_CL = Rsense \cdot \left[IL max\_CL - \left(\frac{Vdc max}{Lp}\right) \cdot tprop\right]$$

$$VCS\_CL = 0.15\Omega \cdot \left[2.679Apk - \left(\frac{325V}{400\mu H}\right) \cdot 160ns\right] = 0.382V$$

For the power supply to go into pulse-by-pulse current limit the voltage across the current sense resistor must be 0.5 V, so:

$VCS_OFFSET := V_{CS} - VCS_CL$

VCS\_OFFSET is the required voltage offset that must be injected across the current sense resistor, R<sub>SENSE</sub>.

VCS\_OFFSET :=

$$V_{CS} - VCS_CL = 0.5V - 0.382V = 0.118V$$

After calculating the required offset voltage, use the following equations to calculate the required current feed forward:

While the main Flyback switch is on, Q1, the voltage on the Auxiliary winding will be negative and proportional to the rectified line.

$$-Vaux = \frac{Vdc}{Naux}$$

$$IQR = \frac{-Vaux}{-Vaux}$$

R1

IQR should be chosen in the range of 1 ma to 4 ma. The demagnetization circuit impedance should be calculated to limit the maximum current flowing through Pin 1 to less than 4 mA.

$R_{OFFSET} = 6.6 \text{ k}\Omega + R_{EXTERNAL}$  (the 6.6 k $\Omega$  resistance is internal to the LM5023).

Where: Naux is the number of turns on the Flyback primary (Np) divided by the number of turns on the transformer Auxiliary (Naux) winding. The current mirror in the QR pin input has a gain of 100; this will offset the voltage on the current sense pin by:

$$VCSOFFSET = \frac{IQR}{100} \bullet (6.6k\Omega + REXTERNAL)$$

Set IQR= 1.75 mA

Vdcmax

$$R_{1} = \frac{\boxed{naux}}{IQR} = \frac{325V}{10.9} = 17.0k\Omega$$

$$\frac{10.9}{1.75mA}$$

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

TEXAS INSTRUMENTS

www.ti.com.cn

$ROFFSET = \frac{VOFFSET}{IQR} \bullet 100 = \frac{0.118V}{1.75mA} \bullet 100 = 6742\Omega$

ROFFSET = RINTERNAL + REXTERNAL

$\text{REXTERNAL} = \text{ROFFSET} - 6.6 \text{k}\Omega = 6742 \Omega - 6.6 \text{k}\Omega = 142 \Omega$

No external resistor is required based on the applications describe above, so a 499  $\Omega$  resistor and 100 pF capacitor are installed in the CS pin input as a noise filter.

ZHCSBC9D - APRIL 2013-REVISED JANUARY 2014

www.ti.com.cn

Figure 14. Current Feed Forward

LM5023

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

#### **Overvoltage Protection**

Output overvoltage protection is implemented with the LM5023 by monitoring the QR pin during the time when the main Flyback MOSFET is off and the energy stored in the transformer primary is being transferred to the secondary. There is a delay prior to sampling the QR pin during the MOSFETs off time, TOVP. There are two reasons for the delay, the first is to blank the voltage spike which is a result of the transformers leakage inductance. The second is to improve the accuracy of the output voltage sensing, referring to the transformer auxiliary winding voltage shown in Figure 11. It is clear there is a down slope in the voltage which represents the decreasing VF of the output rectifier and resistance voltage drop (IS x RS) as the secondary current decreases to zero, so by delaying the sampling of the QR voltage a more accurate representation of the output voltage is achieved.

Connected to the QR pin is a comparator with a 3.0 V reference. The transformers auxiliary voltage is proportional to Vout by the transformers turns ratio:

(1)

To set the OVP, a voltage divider is connected to the transformers auxiliary winding, refer to Figure 13. In the section titled Line Current Limit Feed Forward, we developed equations to improve the power limit. Resistor R1 was calculated for Line Current Limit Feed Forward; to implement OVP we now need to calculate R2.

$$V_{OVP} = Vaux \_OVP \bullet \frac{R2}{R1 + R2}$$

$$R2 = 3.0V \bullet \frac{R1}{Vaux \ OVP - 3V}$$

When an OVP fault has been detected, the LM5023 OUT driver is latched-off. VCC will discharge to VCCMIN and the VSD pin will be asserted high, allowing the Depletion Mode FET to turn-on and charge up the VCC capacitor to  $VCC_{ON}$ . The VSD pin will be toggled on-off-on to maintain VCC to the controller. The only way to clear the fault is to removed the input power and allow the controllers VCC voltage to drop below V<sub>RST</sub>, 5.0 V.

### Valley Switching

For QR operation the Flyback MOSFET is turned on with the minimum Drain voltage. The delay on the auxiliary winding can be adjusted with an external resistor and capacitor to improve valley switching. The delay-time, tdly, must equal half of the natural oscillation period:

$$\mathsf{tdly} = \frac{\pi}{2} \bullet \sqrt{\mathsf{Lp} \bullet \mathsf{COSS}}$$

By substituting

$tdly = RFF \bullet Cd$

We can calculate the RC time constant to achieve the minimum Drain voltage when the LM5023 turns on the Flyback MOSFET.

$$\mathsf{Cd} := \frac{\left[ \left( \frac{\pi}{2} \right) \cdot \sqrt{\mathsf{Lp}_{\mathsf{used}} \cdot \mathsf{Coss}} \right]}{\mathsf{RFF}}$$

The LM5023 QR pin's capacitance is approximately 20 pF, so CdUSED = Cd -20 pF

$$\mathsf{RFF} \coloneqq \frac{(\mathsf{R1} \cdot \mathsf{R2})}{(\mathsf{R1} + \mathsf{R2})}$$

R1 and R2 were previously calculated to set the Line Current Limit Feed Forward and Overvoltage protection.

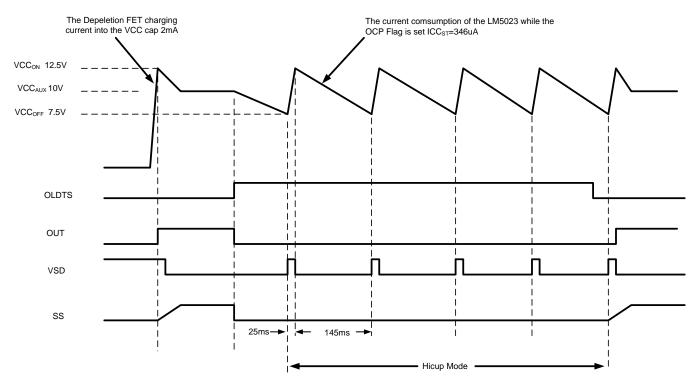

#### **Hiccup Mode**

Hiccup Mode is a method to prevent the power supply from over-heating during and extended overload condition. In an overload fault, the current limit comparator turns off the driver output on pulse-by-pulse basis. This starts the Over Load Detection Timer, after the Over Load Detection Timer (OLDT) times out, the current limit comparator is rechecked, if the power supply is still in an overload condition, the OUT drive is Latched-off and VCC is allowed to drop to VCC<sub>OFF</sub> (7.5 V).

When VCC reaches VCC<sub>OFF</sub>, the VSD open drain output is disabled allowing the Depletion Mode start-up FET to turn-on, charging up the VCC capacitor to VCC<sub>ON</sub> (12.5 V). When VCC reaches VCC<sub>ON</sub>, the VSD output goes low turning-off the Depletion Mode FET. The VCC capacitor is discharged from VCC<sub>ON</sub> to VCC<sub>OFF</sub> at a rate proportional to the VCC capacitor and the ICC<sub>ST</sub> current (346  $\mu$ A typical). The charging and discharging of the VCC capacitor is repeated four times (refer to Figure 15) so the total Hiccup time is:

tHICCUP = tCHARGE • 4 + tDISCHARGE • 4

After allowing VCC to charge and discharge four times, the LM5023 goes through an auto restart sequence, enabling the LM5023 soft-start and driver output. It is important to set the Over Load Detection Timer long enough so that under low input line and full load conditions that the power supply will have enough time to start-up.

The Over Load Detection Timer can be set with the resister in series with the VSD pin ®<sub>VSD</sub>), refer to Figure 8.

$$I_{VSD} = \frac{VCC}{R_{VSD}} = \frac{10V}{1M\Omega} = 10\mu A$$

OVER\_Load\_Detection\_Timer =  $\frac{2 \cdot 60 nA}{I_{VSD}} = \frac{2 \cdot 60 nA}{10 \mu A} = 12 m \sec A$

Normally it is recommended that  $R_{VSD}$ >1 M $\Omega$ , if a lower value is used then the standby power will be higher.

Assuming:

If the Depletion Mode FET charges the VCC capacitor with 2 mA, VCC Capacitor is 10 uF.

$t_{CHARGE} = \frac{\left(VCC_{ON} - VCC_{OFF}\right)}{I_{CHARGE}} \bullet C_{VCC} = \frac{12.5V - 7.5V}{2mA} \bullet 10vF = 25ms$

$t_{\text{DISCHARGE}} = \frac{\left(VCC_{\text{ON}} - VCC_{\text{OFF}}\right)}{ICC_{\text{ST}}} \bullet C_{\text{VCC}} = \frac{12.5 \text{V} - 7.5 \text{V}}{346 \mu \text{A}} \bullet 10 \mu \text{F} = 145 \text{ms}$

$t_{HICCUP} = 25ms \bullet 4 + 145ms \bullet 4 = 680ms$

TEXAS INSTRUMENTS

#### ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

ZHCSBC9D - APRIL 2013 - REVISED JANUARY 2014

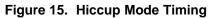

### **EVALUATION BOARD SCHEMATIC**

ZHCSBC9D-APRIL 2013-REVISED JANUARY 2014

## **REVISION HISTORY**

| C | hanges from Revision C (August, 2013) to Revision D                               | Page |

|---|-----------------------------------------------------------------------------------|------|

| • | Added LM5023 Pin Configuration                                                    | 5    |

| • | Changed FUNCTIONAL BLOCK DIAGRAM.                                                 | 6    |

| • | Added VCC < VCC(on) the current consumption.                                      | 9    |

| • | Changed IQR equation from R <sub>OFFSET</sub> to R1.                              | 19   |

|   | Changed Current Feed Forward resistor value from 1 k $\Omega$ to 6.6 k $\Omega$ . |      |

www.ti.com.cn

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LM5023MM-2/NOPB  | ACTIVE        | VSSOP        | DGK                | 8    | 1000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | SK9B                    | Samples |

| LM5023MMX-2/NOPB | ACTIVE        | VSSOP        | DGK                | 8    | 3500           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | SK9B                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW**: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

## PACKAGE OPTION ADDENDUM

10-Dec-2020

## PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

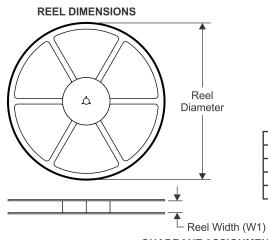

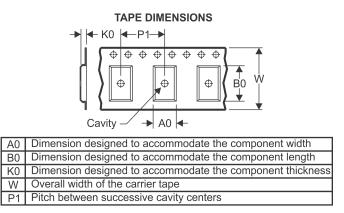

## TAPE AND REEL INFORMATION

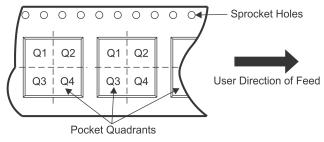

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM5023MM-2/NOPB             | VSSOP           | DGK                | 8 | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LM5023MMX-2/NOPB            | VSSOP           | DGK                | 8 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com

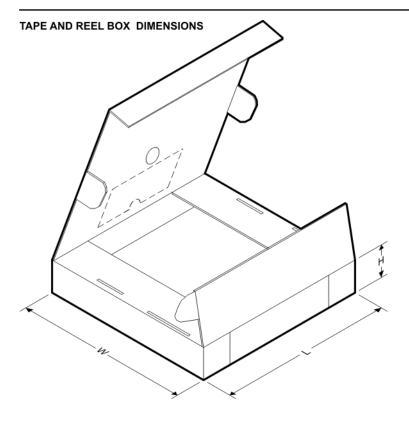

## PACKAGE MATERIALS INFORMATION

21-Oct-2021

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5023MM-2/NOPB  | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LM5023MMX-2/NOPB | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

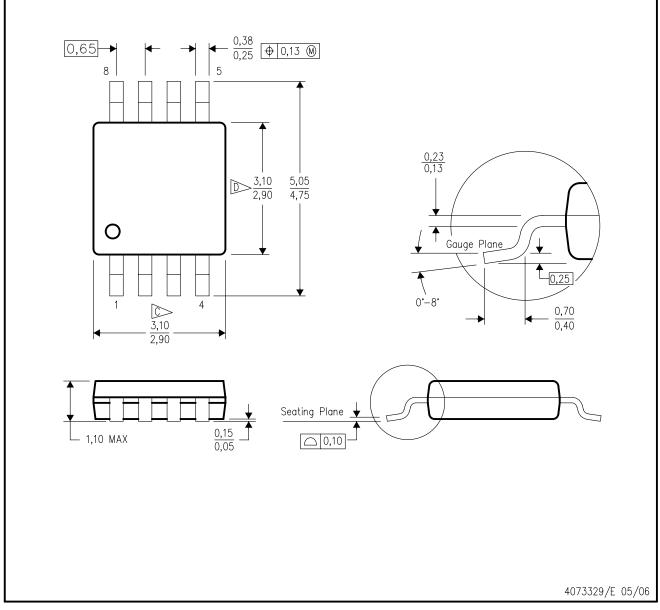

DGK (S-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- D Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

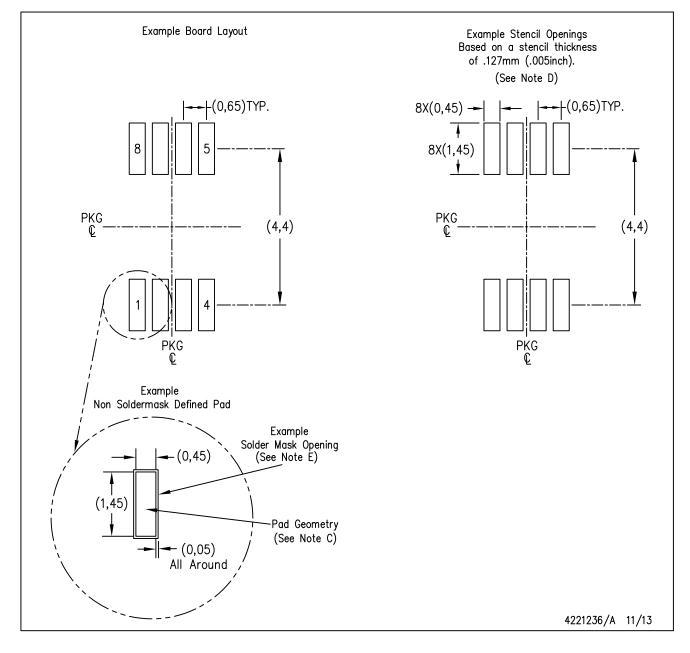

## DGK (S-PDSO-G8)

## PLASTIC SMALL OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021,德州仪器 (TI) 公司

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Texas Instruments manufacturer:

Other Similar products are found below :

NCP1218AD65R2G NCP1244BD065R2G NCP6153MNTWG NCP81101BMNTXG NCP81205MNTXG SJE6600 SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81206MNTXG MAX1653ESET NCP1240FD065R2G NCP1361BABAYSNT1G NCP1230P100G NX2124CSTR NCP1366BABAYDR2G NCP81174NMNTXG NCP4308DMTTWG NCP4308AMTTWG NCP1366AABAYDR2G NCP1251FSN65T1G NCP1246BLD065R2G NTE7233 ISL69122IRAZ MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G NCP1246ALD065R2G AZ494AP-E1 CR1510-10 NCP4205MNTXG XC9221C093MR-G XRP6141ELTR-F RY8017 LP6260SQVF LP6298QVF ISL6121LIB ISL6225CA ISL6244HRZ ISL6268CAZ ISL6315IRZ ISL6420AIAZ-TK ISL6420AIRZ ISL6420IAZ ISL6421ERZ ISL6440IA ISL6441IRZ-TK