LM5050-1, LM5050-1-Q1

ZHCSKM9F-MAY 2011-REVISED DECEMBER 2019

# LM5050-1、LM5050-1-Q1 高侧 OR-ing FET 控制器

# 1 特性

- 提供标准和符合 AEC-Q100 标准版本的 LM5050Q0MK-1(高达 150°C T<sub>J</sub>)和 LM5050Q1MK-1(高达 125°C T<sub>J</sub>)

- 提供功能安全

- 提供文档以帮助创建功能安全系统设计

- 宽工作输入电压范围 V<sub>IN</sub>: 1V 至 75V (V<sub>IN</sub> < 5V 时 需要 V<sub>BIAS</sub>)

- 100V 瞬态电压

- 适用于外部 N 沟道 MOSFET 的电荷泵栅极驱动器

- 针对电流反向 50ns 快速响应

- 2A 峰值栅极关断电流

- 超小 V<sub>DS</sub> 关断电压,可缩短关断时间

- 封装: SOT-6 (薄型 SOT-23-6)

# 2 应用

冗余 (N+1) 电源的有源 OR-ing

# 3 说明

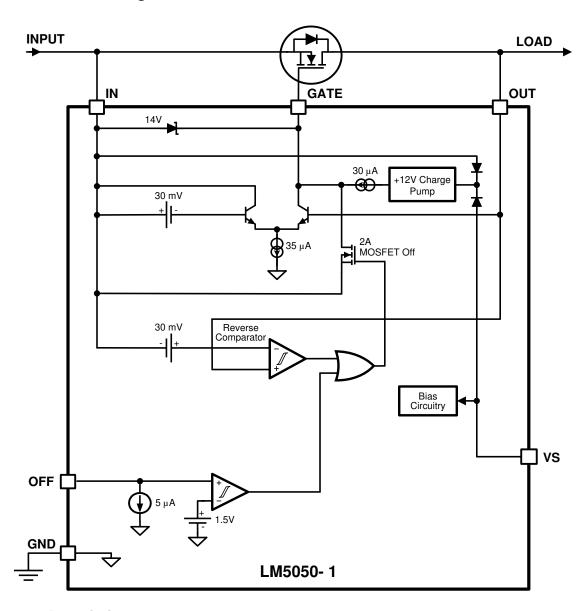

LM5050-1/-Q1 高侧 OR-ing FET 控制器与外部 MOSFET 配合工作,当与电源串联时则用作理想的二极管整流器。此 ORing 控制器可使 MOSFET 替换电源分配网络中的二极管整流器,从而降低功率损耗和压降。

LM5050-1/-Q1 控制器为外部 N 沟道 MOSFET 和快速响应比较器提供电荷泵栅极驱动,以在电流反向流动时关断 FET。LM5050-1/-Q1 可连接 5V 至 75V 的电源,可承受高达 100V 的瞬态电压。

#### 器件信息(1)

| 器件型号        | 封装      | 封装尺寸 (标称值)      |  |  |

|-------------|---------|-----------------|--|--|

| LM5050-1    | COT (C) | 2.00            |  |  |

| LM5050-1-Q1 | SOT (6) | 2.90mm × 1.60mm |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

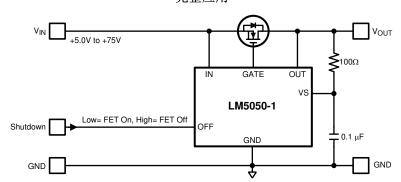

## 完整应用

# 典型冗余电源配置

|                            |                                                                                                                                                                                                                                                                                                                                                 | 目录                                                                                               |                    |                             |          |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------|-----------------------------|----------|

| 1<br>2<br>3<br>4<br>5<br>6 | 说明 修订历史记录  Pin Configuration and Functions Specifications 6.1 Absolute Maximum Ratings 6.2 ESD Ratings: LM5050-1 6.3 ESD Ratings: LM5050-1-Q1 6.4 Recommended Operating Conditions 6.5 Thermal Information 6.6 Electrical Characteristics 6.7 Typical Characteristics 8 Detailed Description 11 7.1 Overview 12 7.2 Functional Block Diagram 13 | 1<br>1<br>1<br>2<br>2<br>3<br>3<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>5<br>5<br>3<br>3<br>1<br>1 | 8<br>9<br>10<br>11 | 7.4 Device Functional Modes |          |

| 注:<br>Cha                  | 7.3 Feature Description                                                                                                                                                                                                                                                                                                                         | F                                                                                                |                    |                             | Page     |

| •                          | 向特性 部分添加了提供功能安全的链接                                                                                                                                                                                                                                                                                                                              |                                                                                                  |                    |                             | 1        |

| Cha                        | nges from Revision D (June 2013) to Revision E                                                                                                                                                                                                                                                                                                  |                                                                                                  |                    |                             | Page     |

| •                          | 已添加 添加了 <i>ESD</i> 额定值 表、特性 说明 部分、器件功                                                                                                                                                                                                                                                                                                           | 能模式、                                                                                             | 应月                 | 用和实施 部分、电源相关建议 部分、布局 音      | <u> </u> |

分、器件和文档支持部分以及机械、封装和可订购信息部分.......1

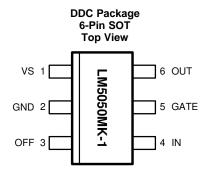

# **5 Pin Configuration and Functions**

**Pin Functions**

| PIN |      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                               |  |  |  |

|-----|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME | 1/0 | DESCRIPTION                                                                                                                                                                                                                                               |  |  |  |

| 1   | VS   | 1   | The main supply pin for all internal biasing and an auxiliary supply for the internal gate drive charge pump. Typically connected to either $V_{OUT}$ or $V_{IN}$ ; a separate supply can also be used.                                                   |  |  |  |

| 2   | GND  | PWR | Ground return for the controller                                                                                                                                                                                                                          |  |  |  |

| 3   | OFF  | I   | A logic high state at the OFF pin will pull the GATE pin low and turn off the external MOSFET. Note that when the MOSFET is off, current will still conduct through the FET's body diode. This pin should may be left open or connected to GND if unused. |  |  |  |

| 4   | IN   | I   | Voltage sense connection to the external MOSFET Source pin.                                                                                                                                                                                               |  |  |  |

| 5   | GATE | 0   | Connect to the Gate of the external MOSFET. Controls the MOSFET to emulate a low forward-voltage diode.                                                                                                                                                   |  |  |  |

| 6   | OUT  | 0   | Voltage sense connection to the external MOSFET Drain pin.                                                                                                                                                                                                |  |  |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                   | MIN  | MAX | UNIT |

|-----------------------------------|------|-----|------|

| IN, OUT Pins to Ground (2)        | -0.3 | 100 | V    |

| GATE Pin to Ground <sup>(2)</sup> | -0.3 | 100 | V    |

| VS Pin to Ground                  | -0.3 | 100 | V    |

| OFF Pin to Ground                 | -0.3 | 7   | V    |

| Storage Temperature               | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings: LM5050-1

|                    |                          |                                                                   | VALUE | UNIT |

|--------------------|--------------------------|-------------------------------------------------------------------|-------|------|

| .,                 | Clastrootatia dia aharaa | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Machine model (MM) <sup>(2)</sup>                                 | ±150  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 ESD Ratings: LM5050-1-Q1

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Machine model (MM) <sup>(2)</sup>                       | ±150  | V    |

<sup>1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                        |                  | MIN | MAX | UNIT |

|----------------------------------------|------------------|-----|-----|------|

| IN, OUT, VS Pins                       | IN, OUT, VS Pins |     | 75  | V    |

| OFF Pin                                |                  | 0   | 5.5 | V    |

|                                        | Standard Grade   | -40 | 125 | °C   |

| Junction Temperature (T <sub>J</sub> ) | LM5050Q0MK-1     | -40 | 150 | °C   |

|                                        | LM5050Q1MK-1     | -40 | 125 | °C   |

# 6.5 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | DDC (SOT) | UNIT |

|----------------------|----------------------------------------------|-----------|------|

|                      |                                              | 6 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 180.7     | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 41.3      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 28.2      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.7       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 27.8      | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> The GATE pin voltage is typically 12 V above the IN pin voltage when the LM5050-1 is enabled (that is, OFF Pin is Opén or Low, and VIN > VOUT). Therefore, the absolute maximum rating for the IN pin voltage applies only when the LM5050-1 is disabled (that is, OFF Pin is logic high), or for a momentary surge to that voltage because the Absolute Maximum Rating for the GATE pin is also 100 V

<sup>(2)</sup> The MM is a 200-pF capacitor discharged through a 0-Ω resistor (that is, directly) into each pin. Applicable test standard is JESD-A115-A.

The MM is a 200-pF capacitor discharged through a 0-Ω resistor (that is, directly) into each pin. Applicable test standard is JESD-A115-A.

# **Thermal Information (continued)**

|                       | THERMAL METRIC <sup>(1)</sup>                | DDC (SOT) | UNIT |

|-----------------------|----------------------------------------------|-----------|------|

|                       |                                              | 6 PINS    |      |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A       | °C/W |

# 6.6 Electrical Characteristics

Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 12 \text{ V}$ ,  $V_{VS} = V_{IN}$ ,  $V_{OUT} = V_{IN}$ ,  $V_{OFF} = 0 \text{ V}$ ,  $C_{GATE} = 47 \text{ nF}$ , and  $T_J = 25^{\circ}\text{C}$ .

| PARAMETER             |                                        | TEST CONDITIONS                                                                                 |                                                               |                             | MIN | TYP | MAX | UNIT   |  |

|-----------------------|----------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------|-----|-----|-----|--------|--|

| VS PIN                |                                        |                                                                                                 |                                                               |                             |     |     |     |        |  |

| V <sub>VS</sub>       | Operating<br>Supply Voltage<br>Range   | $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$                                           |                                                               |                             | 5   |     | 75  | ٧      |  |

|                       |                                        | V <sub>VS</sub> = 5 V, V <sub>IN</sub> = 5 V                                                    | T <sub>J</sub> = 25°C                                         |                             |     | 75  |     |        |  |

|                       |                                        | $V_{OUT} = V_{IN} - 100 \text{ mV}$                                                             | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ |                             |     |     | 105 |        |  |

| L                     | Operating                              | V <sub>VS</sub> = 12 V, V <sub>IN</sub> = 12 V                                                  | $T_J = 25^{\circ}C$                                           |                             |     | 100 |     | μА     |  |

| I <sub>VS</sub>       | Supply Current                         | $V_{OUT} = V_{IN} - 100 \text{ mV}$                                                             | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ |                             |     |     | 147 | μΑ     |  |

|                       |                                        | V <sub>VS</sub> = 75 V, V <sub>IN</sub> = 75 V                                                  | $T_J = 25^{\circ}C$                                           |                             |     | 130 |     |        |  |

|                       |                                        | $V_{OUT} = V_{IN} - 100 \text{ mV}$                                                             | $T_J = -40$ °C to 125°C                                       |                             |     |     | 288 |        |  |

| IN PIN                |                                        |                                                                                                 |                                                               |                             |     |     |     |        |  |

| V <sub>IN</sub>       | Operating Input Voltage Range          | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$                                             |                                                               |                             | 5   |     | 75  | ٧      |  |

|                       |                                        | V <sub>IN</sub> = 5 V                                                                           | $T_J = 25$ °C                                                 |                             |     | 190 |     |        |  |

|                       |                                        | $V_{VS} = V_{IN}$<br>$V_{OUT} = V_{IN} - 100 \text{ mV}$<br>GATE = Open                         | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ |                             | 32  |     | 305 | 5      |  |

| I <sub>IN</sub>       | IN Pin current                         | $V_{IN}$ = 12 V to 75 V $V_{VS}$ = $V_{IN}$ V to 75 V $V_{OUT}$ = $V_{IN}$ - 100 mV GATE = Open | T <sub>J</sub> = 25°C                                         |                             |     | 320 |     | μΑ     |  |

|                       |                                        |                                                                                                 | $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$         | LM5050MK-1,<br>LM5050Q1MK-1 | 233 |     | 400 |        |  |

|                       |                                        |                                                                                                 | $T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$   | LM5050Q0MK-1                | 233 |     | 475 |        |  |

| OUT PIN               |                                        |                                                                                                 |                                                               | -                           |     |     | *   |        |  |

| V <sub>OUT</sub>      | Operating<br>Output Voltage<br>Range   | $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$                                           |                                                               |                             | 5   |     | 75  | V      |  |

|                       |                                        | V <sub>IN</sub> = 5 V to 75 V                                                                   | T <sub>J</sub> = 25°C                                         |                             | 3.2 |     |     |        |  |

| I <sub>OUT</sub>      | OUT Pin Current                        | $V_{VS} = V_{IN}$<br>$V_{OUT} = V_{IN} - 100 \text{ mV}$                                        | $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$         |                             |     |     | 8   | μA     |  |

| GATE PIN              |                                        |                                                                                                 | I                                                             |                             |     |     |     |        |  |

|                       |                                        | V <sub>IN</sub> = 5 V                                                                           | T <sub>J</sub> = 25°C                                         |                             |     | 30  |     |        |  |

|                       | Gate Pin Source                        | $V_{VS} = V_{IN}$<br>$V_{GATE} = V_{IN}$<br>$V_{OUT} = V_{IN} - 175 \text{ mV}$                 | $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$         |                             | 12  |     | 41  |        |  |

| I <sub>GATE(ON)</sub> | Current                                | V <sub>IN</sub> = 12 V to 75 V                                                                  | T <sub>J</sub> = 25°C                                         |                             |     | 32  |     | μA     |  |

|                       |                                        | $V_{VS} = V_{IN}$ $V_{GATE} = V_{IN}$ $V_{OUT} = V_{IN} - 175 \text{ mV}$                       | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ |                             | 20  |     | 41  |        |  |

|                       |                                        | V <sub>IN</sub> = 5 V                                                                           | T <sub>J</sub> = 25°C                                         |                             |     | 7   |     |        |  |

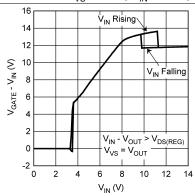

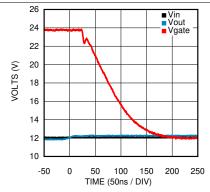

|                       | V <sub>GATE</sub> - V <sub>IN</sub> in | $V_{VS} = V_{IN}$<br>$V_{OUT} = V_{IN} - 175 \text{ mV}$                                        | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ |                             | 4   |     | 9   | )<br>V |  |

| $V_{GS}$              | Forward Operation <sup>(1)</sup>       | V <sub>IN</sub> = 12 V to 75 V                                                                  | T <sub>J</sub> = 25°C                                         |                             |     | 12  |     |        |  |

|                       | Operation                              | $V_{VS}^{II} = V_{IN}$                                                                          |                                                               |                             |     |     |     |        |  |

# **Electrical Characteristics (continued)**

Typical values represent the most likely parametric norm at  $T_J = 25$ °C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 12 \text{ V}$ ,  $V_{VS} = V_{IN}$ ,  $V_{OUT} = V_{IN}$ ,  $V_{OFF} = 0 \text{ V}$ ,  $C_{GATE} = 47 \text{ nF}$ , and  $T_J = 25^{\circ}\text{C}$ .

| PARAMETER               |                                                                               | TEST CONDITIONS                                                                           |                                                               |                             | MIN          | TYP  | MAX  | UNIT |  |

|-------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------|--------------|------|------|------|--|

|                         | Gate                                                                          | $C_{GATE} = 0^{(2)}$                                                                      | $T_J = 25^{\circ}C$                                           |                             |              | 25   |      |      |  |

|                         | Capacitance<br>Discharge Time                                                 |                                                                                           | $T_J = -40$ °C to 125°C                                       |                             |              |      | 85   |      |  |

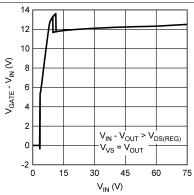

| t <sub>GATE(REV)</sub>  | at Forward to                                                                 | C <sub>GATE</sub> = 10 nF <sup>(2)</sup>                                                  | $T_J = 25^{\circ}C$                                           |                             |              | 60   |      | ns   |  |

|                         | Reverse<br>Transition                                                         | C <sub>GATE</sub> = 47 nF <sup>(2)</sup>                                                  | $T_J = 25^{\circ}C$                                           |                             |              | 180  |      | 1    |  |

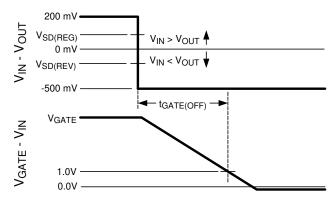

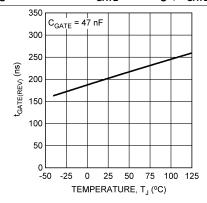

|                         | See Figure 1                                                                  | OGATE = 47 TIF V                                                                          | $T_J = -40$ °C to 125°C                                       |                             |              |      | 350  |      |  |

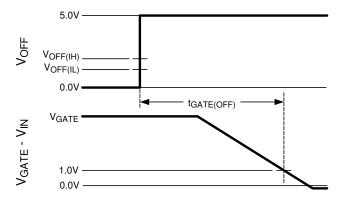

| t <sub>GATE</sub> (OFF) | Gate Capacitance DischargeTime at OFF pin Low to High Transition See Figure 2 | C <sub>GATE</sub> = 47 nF <sup>(3)</sup>                                                  | T <sub>J</sub> = 25°C                                         |                             |              | 486  |      | ns   |  |

|                         |                                                                               | ., ., .,                                                                                  | $T_J = 25^{\circ}C$                                           | ,                           |              | 2.8  |      |      |  |

| I <sub>GATE(OFF)</sub>  | Gate Pin Sink<br>Current                                                      | $V_{GATE} = V_{IN} + 3 V$<br>$V_{OUT} > V_{IN} + 100 \text{ mV}$<br>$t \le 10 \text{ ms}$ | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | LM5050MK-1,<br>LM5050Q1MK-1 | 1.8          |      |      | Α    |  |

|                         |                                                                               | . –                                                                                       | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | LM5050Q0MK-1                | 1.4          |      |      |      |  |

| .,                      | Reverse V <sub>SD</sub>                                                       |                                                                                           | $T_J = 25^{\circ}C$                                           |                             |              | -28  |      |      |  |

| $V_{SD(REV)}$           | Threshold<br>V <sub>IN</sub> < V <sub>OUT</sub>                               | V <sub>IN</sub> - V <sub>OUT</sub>                                                        | $T_J = -40$ °C to 125°C                                       |                             | -41          |      | -16  | mV   |  |

| $\Delta V_{SD(REV)}$    | Reverse V <sub>SD</sub><br>Hysteresis                                         |                                                                                           | T <sub>J</sub> = 25°C                                         |                             |              | 10   |      | mV   |  |

|                         | Regulated<br>Forward V <sub>SD</sub>                                          | orward V <sub>SD</sub>                                                                    | $T_J = 25^{\circ}C$                                           |                             |              | 19   |      |      |  |

|                         |                                                                               |                                                                                           | $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$         | LM5050MK-1,<br>LM5050Q1MK-1 | 1            |      | 37   | m\/  |  |

| V                       |                                                                               |                                                                                           | $T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$   | LM5050Q0MK-1                | 1            |      | 60   |      |  |

| $V_{SD(REG)}$           | Threshold                                                                     |                                                                                           | $T_J = 25^{\circ}C$                                           | ,                           |              | 22   |      | mV   |  |

|                         |                                                                               |                                                                                           | $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$         | LM5050MK-1,<br>LM5050Q1MK-1 | 4.4          |      | 37   |      |  |

|                         |                                                                               |                                                                                           | V <sub>IN</sub> - V <sub>OUT</sub>                            | $T_J = -40$ °C to 125°C     | LM5050Q0MK-1 | 4.4  |      | 60   |  |

| OFF PIN                 |                                                                               |                                                                                           |                                                               |                             |              |      |      |      |  |

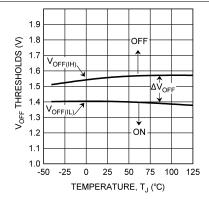

| .,                      | OFF Input High                                                                | $V_{OUT} = V_{IN}-500 \text{ mV}$                                                         | $T_J = 25^{\circ}C$                                           |                             |              | 1.56 |      |      |  |

| V <sub>OFF(IH)</sub>    | Threshold<br>Voltage                                                          | V <sub>OFF</sub> Rising                                                                   | $T_J = -40$ °C to 125°C                                       |                             |              |      | 1.75 | V    |  |

| V                       | OFF Input Low                                                                 | V <sub>OUT</sub> = V <sub>IN</sub> - 500 mV                                               | T <sub>J</sub> = 25°C                                         |                             |              | 1.4  |      | V    |  |

| $V_{OFF(IL)}$           | Threshold<br>Voltage                                                          | V <sub>OFF</sub> Falling                                                                  | $T_J = -40$ °C to 125°C                                       |                             | 1.1          |      |      |      |  |

| $\Delta V_{OFF}$        | OFF Threshold<br>Voltage<br>Hysteresis                                        | V <sub>OFF(IH)</sub> - V <sub>OFF(IL)</sub>                                               | T <sub>J</sub> = 25°C                                         |                             |              | 155  |      | mV   |  |

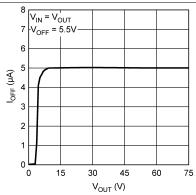

|                         | OFF Die leterrel                                                              | V <sub>OFF</sub> = 4.5 V                                                                  | $T_J = 25^{\circ}C$                                           |                             |              | 5    |      |      |  |

| $I_{OFF}$               | OFF Pin Internal Pulldown                                                     | VOFF - 4.5 V                                                                              | $T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$   |                             | 3            |      | 7    | μΑ   |  |

|                         |                                                                               | V <sub>OFF</sub> = 5 V                                                                    | $T_J = 25^{\circ}C$                                           |                             |              | 8    |      |      |  |

Time from  $V_{IN}$ - $V_{OUT}$  voltage transition from 200 mV to -500 mV until GATE pin voltage falls to  $V_{IN}$  + 1 V. See Figure 1. Time from  $V_{OFF}$  voltage transition from 0 V to 5 V until GATE pin voltage falls to  $V_{IN}$  + 1 V. See Figure 2

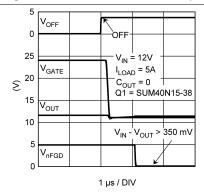

Figure 1. Gate OFF Timing for Forward to Reverse Transition

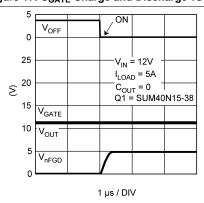

Figure 2. Gate OFF Timing for OFF Pin Low to High Transition

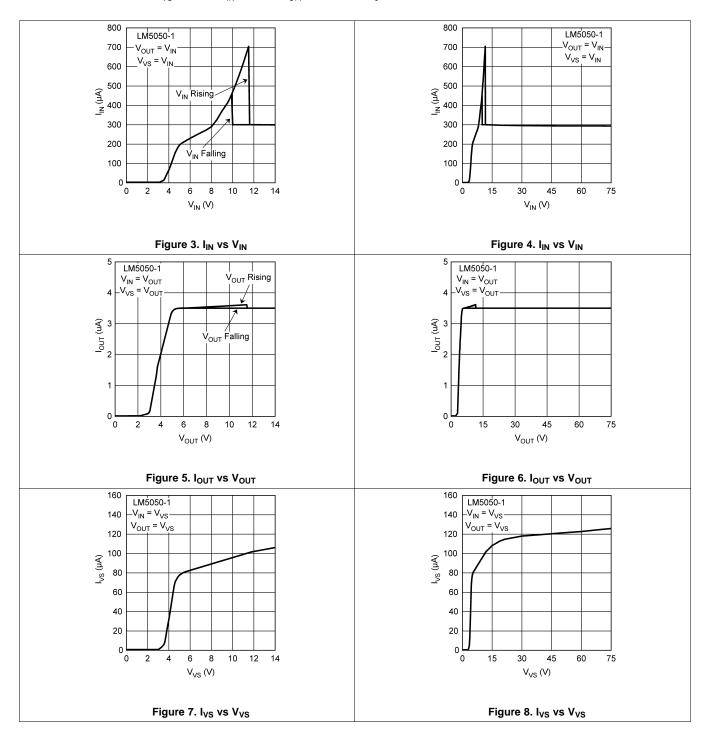

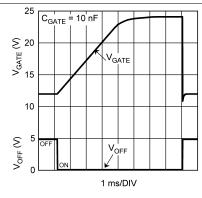

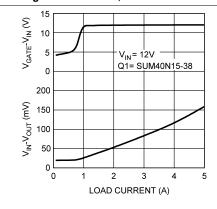

# 6.7 Typical Characteristics

Unless otherwise stated:  $V_{VS}$  = 12 V,  $V_{IN}$  = 12 V,  $V_{OFF}$  = 0 V, and  $T_J$  = 25°C

# **Typical Characteristics (continued)**

Unless otherwise stated:  $V_{VS}$  = 12 V,  $V_{IN}$  = 12 V,  $V_{OFF}$  = 0 V, and  $T_J$  = 25°C

Figure 9.  $(V_{GATE} - V_{IN})$  vs  $V_{IN}$ ,  $V_{VS} = V_{OUT}$

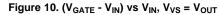

Figure 11. Forward  $C_{GATE}$  Charge Time,  $C_{GATE}$  = 47 nF

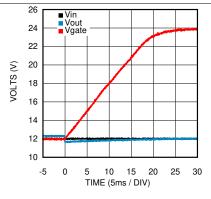

Figure 12. Reverse C<sub>GATE</sub> Discharge, C<sub>GATE</sub> = 47 nF

Figure 13. V<sub>GATE</sub> - V<sub>IN</sub> vs Temperature

Figure 14.  $t_{\text{GATE}(\text{REV})}$  vs Temperature

# **Typical Characteristics (continued)**

Unless otherwise stated:  $V_{VS}$  = 12 V,  $V_{IN}$  = 12 V,  $V_{OFF}$  = 0 V, and  $T_J$  = 25°C

Figure 15. OFF Pin Thresholds vs Temperature

Figure 17. C<sub>GATE</sub> Charge and Discharge vs OFF Pin

Figure 18. OFF Pin, ON to OFF Transition

Figure 19. OFF Pin, OFF to ON Transition

Figure 20. GATE Pin vs  $(R_{DS(ON)} \times I_{DS})$

# 7 Detailed Description

#### 7.1 Overview

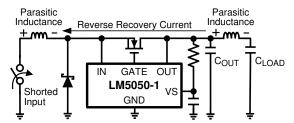

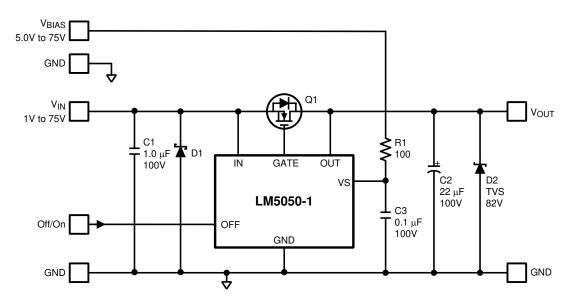

Blocking diodes are commonly placed in series with supply inputs for the purpose of ORing redundant power sources and protecting against supply reversal. The LM5050 replaces diodes in these applications with an N-MOSFET to reduce both the voltage drop and power loss associated with a passive solution. At low input voltages, the improvement in forward voltage loss is readily appreciated where headroom is tight, as shown in Figure 2. The LM5050 operates from 5 V to 75 V and it can withstand an absolute maximum of 100 V without damage. A 12-V or 15-A ideal diode application is shown in Figure 24. Several external components are included in addition to the MOSFET, Q1. Ideal diodes, like their non-ideal counterparts, exhibit a behavior known as reverse recovery. In combination with parasitic or intentionally introduced inductances, reverse recovery spikes may be generated by an ideal diode during an reverse current shutdown. D1, D2 and R1 protect against these spikes which might otherwise exceed the LM5050 100-V survival rating. COUT also plays a role in absorbing reverse recovery energy. Spikes and protection schemes are discussed in detail in the *Short Circuit Failure of an Input Supply* section.

#### NOTE

The OFF pin may be used to active the GATE pull down circuit and turn off the pass MOSFET, but it does not disconnect the load from the input because Q1's body diode is still present.

If Vs is powered while IN is floating or grounded, then about 0.5mA will leak from the Vs pin into the IC and about 3mA will leak from the OUT pin into the IC. From this leakage, about 50 uA will flow out of the IN pin and the rest will flow to ground. This does not affect long term reliability of the IC, but may influence circuit design. See *Reverse Input Voltage Protection With IQ Reduction* for details on how to avoid this leakage current.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 IN, GATE, and OUT Pins

When power is initially applied, the load current will flow from source to drain through the body diode of the MOSFET. Once the voltage across the body diode exceeds  $V_{SD(REG)}$  then the LM5050-1 begins charging the MOSFET gate through a 32  $\mu$ A (typical) charge pump current source . In forward operation, the gate of the MOSFET is charged until it reaches the clamping voltage of the 12-V GATE to IN pin Zener diode internal to the LM5050-1.

The LM5050-1 is designed to regulate the MOSFET gate-to-source voltage. If the MOSFET current decreases to the point that the voltage across the MOSFET falls below the  $V_{SD(REG)}$  voltage regulation point of 22 mV (typical), the GATE pin voltage will be decreased until the voltage across the MOSFET is regulated at 22 mV. If the source-to-drain voltage is greater than the  $V_{SD(REG)}$  voltage, the gate-to-source voltage will increase and eventually reach the 12-V GATE to IN pin Zener clamp level.

### **Feature Description (continued)**

If the MOSFET current reverses, possibly due to failure of the input supply, such that the voltage across the LM5050-1 IN and OUT pins is more negative than the  $V_{SD(REV)}$  voltage of -28 mV (typical), the LM5050-1 will quickly discharge the MOSFET gate through a strong GATE to IN pin discharge transistor.

If the input supply fails abruptly, as would occur if the supply was shorted directly to ground, a reverse current will temporarily flow through the MOSFET until the gate can be fully discharged. This reverse current is sourced from the load capacitance and from the parallel connected supplies. The LM5050-1 responds to a voltage reversal condition typically within 25 ns. The actual time required to turn off the MOSFET will depend on the charge held by the gate capacitance of the MOSFET being used. A MOSFET with 47 nF of effective gate capacitance can be turned off in typically 180 ns. This fast turnoff time minimizes voltage disturbances at the output, as well as the current transients from the redundant supplies.

#### 7.3.2 VS Pin

The LM5050-1 VS pin is the main supply pin for all internal biasing and an auxiliary supply for the internal gate drive charge pump.

For typical LM5050-1 applications, where the input voltage is above 5 V, the VS pin can be connected directly to the OUT pin. In situations where the input voltage is close to, but not less than, the 5 V minimum, it may be helpful to connect the VS pin to the OUT pin through an RC Low-Pass filter to reduce the possibility of erratic behavior due to spurious voltage spikes that may appear on the OUT and IN pins. The series resistor value should be low enough to keep the VS voltage drop at a minimum. A typical series resistor value is 100  $\Omega$ . The capacitor value should be the lowest value that produces acceptable filtering of the voltage noise.

If Vs is powered while IN is floating or grounded, then about 0.5 mA will leak from the Vs pin into the IC and about 3mA will leak from the OUT pin into the IC. From this leakage, about 50 uA will flow out of the IN pin and the rest will flow to ground. This does not affect long term reliability of the IC, but may influence circuit design. See *Reverse Input Voltage Protection With IQ Reduction* for details on how to avoid this leakage current.

Alternately, it is possible to operate the LM5050-1 with  $V_{IN}$  value as low as 1 V if the VS pin is powered from a separate supply. This separate VS supply must be from 5 V and 75 V. See Figure 27.

#### 7.3.3 OFF Pin

The OFF pin is a logic level input pin that is used to control the gate drive to the external MOSFET. The maximum operating voltage on this pin is 5.5 V.

When the OFF pin is high, the MOSFET is turned off (independent of the sensed IN and OUT voltages). In this mode, load current will flow through the body diode of the MOSFET. The voltage difference between the IN pin and OUT pins will be approximately 700 mV if the MOSFET is operating normally through the body diode.

The OFF pin has an internal pulldown of 5 µA (typical). If the OFF function is not required the pin may be left open or connected to ground.

#### 7.4 Device Functional Modes

#### 7.4.1 ON/OFF Control Mode

The MOSFET can be turned off by asserting the OFF pin high. This mode only disables the MOSFET, but V<sub>OUT</sub> is still available through the body diode of the MOSFET.

#### 7.4.2 External Power Supply Mode

The Vs pin of the LM5050 can be operated from 5 V to 75 V as the bias input supply. In this mode  $V_{IN}$  voltage can be as low as 1 V, as shown in Figure 27.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

Systems that require high availability often use multiple, parallel-connected redundant power supplies to improve reliability. Schottky OR-ing diodes are typically used to connect these redundant power supplies to a common point at the load. The disadvantage of using OR-ing diodes is the forward voltage drop, which reduces the available voltage and the associated power losses as load currents increase. Using an N-channel MOSFET to replace the OR-ing diode requires a small increase in the level of complexity, but reduces, or eliminates, the need for diode heat sinks or large thermal copper area in circuit board layouts for high power applications.

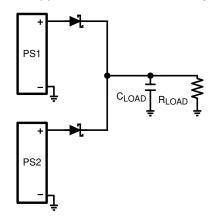

Figure 21. OR-ing with Diodes

The LM5050-1/-Q1 is a positive voltage (that is, high-side) OR-ing controller that will drive an external N-channel MOSFET to replace an OR-ing diode. The voltage across the MOSFET source and drain pins is monitored by the LM5050-1 at the IN and OUT pins, while the GATE pin drives the MOSFET to control its operation based on the monitored source-drain voltage. The resulting behavior is that of an ideal rectifier with source and drain pins of the MOSFET acting as the anode and cathode pins of a diode respectively.

Figure 22. OR-ing With MOSFETs

# **Application Information (continued)**

#### 8.1.1 MOSFET Selection

The important MOSFET electrical parameters are the maximum continuous Drain current  $I_D$ , the maximum Source current (that is, body diode)  $I_S$ , the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the gate-to-source threshold voltage  $V_{GS(TH)}$ , the drain-to-source reverse breakdown voltage  $V_{(BR)DSS}$ , and the drain-to-source On resistance  $R_{DS(ON)}$ .

The maximum continuous drain current,  $I_D$ , rating must exceed the maximum continuous load current. The rating for the maximum current through the body diode,  $I_S$ , is typically rated the same as, or slightly higher than the drain current, but body diode current only flows while the MOSFET gate is being charged to  $V_{GS(TH)}$ .

Gate Charge Time =  $Q_g / I_{GATE(ON)}$

- 1. The maximum drain-to-source voltage,  $V_{DS(MAX)}$ , must be high enough to withstand the highest differential voltage seen in the application. This would include any anticipated fault conditions.

- The drain-to-source reverse breakdown voltage, V<sub>(BR)DSS</sub>, may provide some transient protection to the OUT pin in low voltage applications by allowing conduction back to the IN pin during positive transients at the OUT pin.

- 3. The gate-to-source threshold voltage,  $V_{GS(TH)}$ , should be compatible with the LM5050-1 gate drive capabilities. Logic level MOSFETs, with  $R_{DS(ON)}$  rated at  $V_{GS(TH)}$  at 5 V, are recommended, but sub-Logic level MOSFETs having  $R_{DS(ON)}$  rated at  $V_{GS(TH)}$  at 2.5 V, can also be used.

- 4. The dominate MOSFET loss for the LM5050-1 active OR-ing controller is conduction loss due to source-to-drain current to the output load, and the  $R_{DS(ON)}$  of the MOSFET. This conduction loss could be reduced by using a MOSFET with the lowest possible  $R_{DS(ON)}$ . However, contrary to popular belief, arbitrarily selecting a MOSFET based solely on having low  $R_{DS(ON)}$  may not always give desirable results for several reasons:

- Reverse transition detection. Higher R<sub>DS(ON)</sub> will provide increased voltage information to the LM5050-1 Reverse Comparator at a lower reverse current level. This will give an earlier MOSFET turnoff condition should the input voltage become shorted to ground. This will minimize any disturbance of the redundant bus.

- Reverse current leakage. In cases where multiple input supplies are closely matched it may be possible

for some small current to flow continuously through the MOSFET drain to source (that is, reverse)

without activating the LM5050-1 Reverse Comparator. Higher R<sub>DS(ON)</sub> will reduce this reverse current

level.

- Cost. Generally, as the R<sub>DS(ON)</sub> rating goes lower, the cost of the MOSFET goes higher.

- 5. The dominate MOSFET loss for the LM5050-1 active OR-ing controller is conduction loss due to source-to-drain current to the output load, and the  $R_{DS(ON)}$  of the MOSFET. This conduction loss could be reduced by using a MOSFET with the lowest possible  $R_{DS(ON)}$ . However, contrary to popular belief, arbitrarily selecting a MOSFET based solely on having low  $R_{DS(ON)}$  may not always give desirable results for several reasons:

- a. Selecting a MOSFET with an R<sub>DS(ON)</sub> that is too large will result in excessive power dissipation. Additionally, the MOSFET gate will be charged to the full value that the LM5050-1 can provide as it attempts to drive the Drain to Source voltage down to the V<sub>SD(REG)</sub> of 22 mV typical. This increased Gate charge will require some finite amount of additional discharge time when the MOSFET needs to be turned off.

- b. As a guideline, it is suggest that R<sub>DS(ON)</sub> be selected to provide at least 22 mV, and no more than 100 mV, at the nominal load current.

- c.  $(22 \text{ mV} / I_D) \le R_{DS(ON)} \le (100 \text{ mV} / I_D)$

- d. The thermal resistance of the MOSFET package should also be considered against the anticipated dissipation in the MOSFET to ensure that the junction temperature (T<sub>J</sub>) is reasonably well controlled, because the R<sub>DS(ON)</sub> of the MOSFET increases as the junction temperature increases.

- 6.  $P_{DISS} = I_D^2 \times (R_{DS(ON)})$

- 7. Operating with a maximum ambient temperature ( $T_{A(MAX)}$ ) of 35°C, a load current of 10 A, and an  $R_{DS(ON)}$  of 10 m $\Omega$ , and desiring to keep the junction temperature under 100°C, the maximum junction-to-ambient thermal resistance rating ( $\theta_{JA}$ ) must be:

- a.  $R_{\theta JA} \le (T_{J(MAX)} T_{A(MAX)})/(I_D^2 \times R_{DS(ON)})$

- b.  $R_{\theta JA} \le (100^{\circ}C 35^{\circ}C)/(10 \text{ A} \times 10 \text{ A} \times 0.01 \Omega)$

### Application Information (continued)

c.  $R_{\theta JA} \le 65^{\circ}C/W$

# 8.1.2 Short Circuit Failure of an Input Supply

An abrupt  $0-\Omega$  short circuit across the input supply will cause the highest possible reverse current to flow while the internal LM5050-1 control circuitry discharges the gate of the MOSFET. During this time, the reverse current is limited only by the  $R_{DS(ON)}$  of the MOSFET, along with parasitic wiring resistances and inductances. Worst case instantaneous reverse current would be limited to:

$$I_{D(REV)} = (V_{OUT} - V_{IN}) / R_{DS(ON)}$$

$$\tag{1}$$

The internal Reverse Comparator will react, and will start the process of discharging the Gate, when the reverse current reaches:

$$I_{D(REV)} = V_{SD(REV)} / R_{DS(ON)}$$

(2)

When the MOSFET is finally switched off, the energy stored in the parasitic wiring inductances will be transferred to the rest of the circuit. As a result, the LM5050-1 IN pin will see a negative voltage spike while the OUT pin will see a positive voltage spike. The IN pin can be protected by diode clamping the pin to GND in the negative direction. The OUT pin can be protected with a TVS protection diode, a local bypass capacitor, or both. In low voltage applications, the MOSFET drainto- source breakdown voltage rating may be adequate to protect the OUT pin (that is,  $V_{\text{IN}} + V_{\text{(BR)DSS(MAX)}} < 75 \text{ V}$ ), but most MOSFET data sheets do not ensure the maximum breakdown rating, so this method should be used with caution.

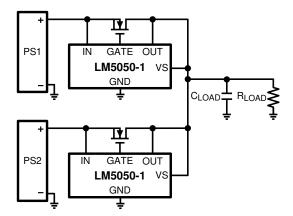

Figure 23. Reverse Recovery Current Generates Inductive Spikes at VIN and VOUT pins.

### 8.2 Typical Applications

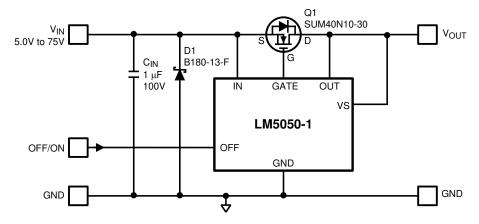

### 8.2.1 Typical Application With Input and Output Transient Protection

Figure 24. Typical Application With Input and Output Transient Protection Schematic

# **Typical Applications (continued)**

#### 8.2.1.1 Design Requirements

Table 1 shows the parameters for Figure 24

**Table 1. Design Parameters**

| DESIGN PARAMETER                          | EXAMPLE VALUE |

|-------------------------------------------|---------------|

| Minimum Input Voltage, VIN <sub>MIN</sub> | 6 V           |

| Maximum Input Voltage, VIN <sub>Max</sub> | 50 V          |

| Output Current Range, IOUT                | 0 to 15 A     |

| Ambient Temperature Range, T <sub>A</sub> | 0°C to 50°C   |

#### 8.2.1.2 Detailed Design Procedure

The following design procedure can be used to select component values for the LM5050-1.

#### 8.2.1.2.1 Power Supply Components (R1 C1,) Selection

The LM5050-1 VS pin is the main supply pin for all internal biasing and an auxiliary supply for the internal gate drive charge pump. The series resistor (R1) value should be low enough to keep the VS voltage drop at a minimum. A typical series resistor value is  $100 \Omega$ . The capacitor value (0.1 uF typical) should be the lowest value that produces acceptable filtering of the voltage noise.

### 8.2.1.2.2 MOSFET (Q1) Selection

The MOSFET (Q1) selection procedure is explained in detail in *MOSFET Selection*. The MOSFET used in the design example is SUM40N10-30-E3.

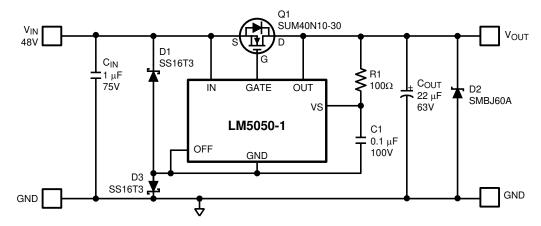

#### 8.2.1.2.3 D1 and D2 Selection for Inductive Kick-Back Protection

Diode D1 and capacitor C1 and diode D2 and capacitor C2 in the Figure 27 serve as inductive kick-back protection to limit negative transient voltage spikes generated on the input when the input supply voltage is abruptly shorted to zero volts. As a result, the LM5050-1 IN pin will see a negative voltage spike while the OUT pin will see a positive voltage spike. The IN pin can be protected by schottky diode (D1) clamping the pin to GND in the negative direction, similarly the OUT pin should be protected with a TVS protection diode (D1), or with a local bypass capacitor, or both. D1 is selected as 1-A, 60-V Schottky Barrier Rectifier (SS16T3G) and D2 is the 60 V, TVS (SMBJ60A-13-F).

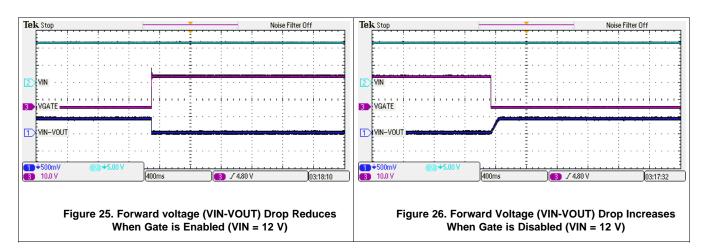

#### 8.2.1.3 Application Curves

## 8.2.2 Using a Separate VS Supply for Low Vin Operation

In some applications, it is desired to operate LM5050-1 from low supply voltage. The LM5050-1 can operate with a 1-V rail voltage, provided its VS pin is biased from 5 V to 75 V. The detail of such application is depicted in Figure 27.

Figure 27. Using a Separate vs Supply for Low Vin Operation Schematic

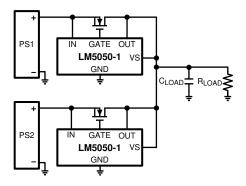

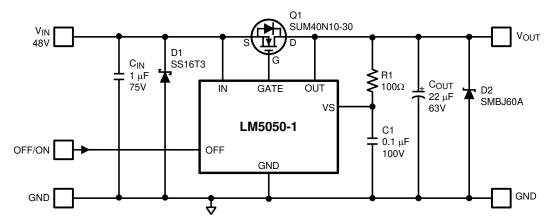

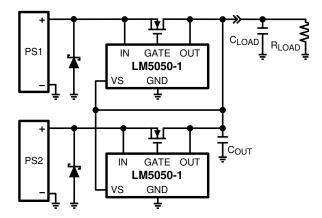

## 8.2.3 ORing of Two Power Sources

Figure 28. ORing of Two Power Sources

### 8.2.4 Reverse Input Voltage Protection With IQ Reduction

If Vs is powered while IN is floating or grounded, then about 0.5 mA will leak from the Vs pin into the IC and about 3 mA will leak from the OUT pin into the IC. From this leakage, about 50 uA will flow out of the IN pin and the rest will flow to ground. This does not affect long term reliability of the IC, but may influence circuit design.

In battery powered applications, whenever LM5050-1 functionality is not needed, the supply to the LM5050-1 can be disconnected by turning "OFF" Q2, as shown in Figure 29. This disconnects the ground path of the LM5050-1 and eliminates the current leakage from the battery.

The quiescent current of LM5050-1 can be also reduced by disconnecting the supply to VS pin, whenever LM5050-1 function is not need.

Figure 29. Reverse Input Voltage Protection With IQ Reduction Schematic

### 8.2.5 Basic Application With Input Transient Protection

Figure 30. Basic Application With Input Transient Protection Schematic

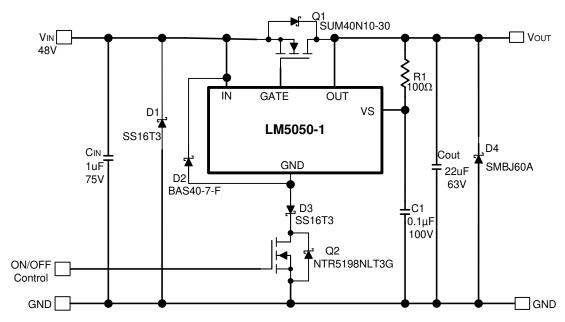

# 8.2.6 48-V Application With Reverse Input Voltage ( $V_{IN} = -48 \text{ V}$ ) Protection

Figure 31. 48-V Application With Reverse Input Voltage ( $V_{IN} = -48 \text{ V}$ ) Protection Schematic

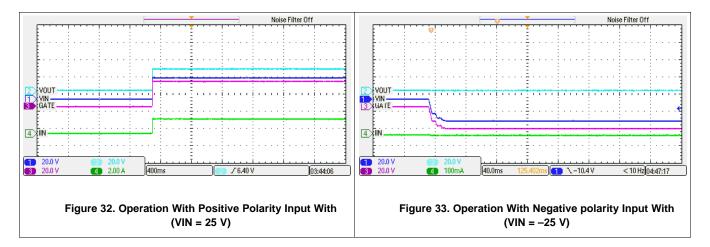

# 8.2.6.1 Application Curves

# 9 Power Supply Recommendations

When the LM5050-1/-Q1 shuts off the external MOSFET, transient voltages will appear on the input and output due to reverse recovery, as discussed in *Short Circuit Failure of an Input Supply*. To prevent LM5050-1 and surrounding components from damage under the conditions of a direct input short circuit, it is necessary to clamp the negative transient at IN, and OUT pins with TVS.

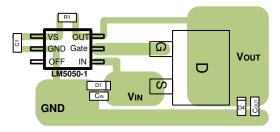

# 10 Layout

### 10.1 Layout Guidelines

The typical PCB layout for LM5050-1/-Q1 is shown in Figure 34. TI recommends connecting the IN, Gate and OUT pins close to the source and drain pins of the MOSFET. Keep the traces of the MOSFET drain wide and short to minimize resistive losses. Place surge suppressors (D1 and D4) components as shown in the example layout of LM5050-1 in *Layout Example*.

# 10.2 Layout Example

Figure 34. Typical Layout Example With D2PAK N-MOSFET

## 11 器件和文档支持

### 11.1 文档支持

#### 11.1.1 相关文档

《使用具有低电流和高噪声输入电源的 LM5050-1 实现稳定 VGS》, SLVA684

#### 11.2 相关链接

下表列出了快速访问链接。类别包括技术文档、支持与社区资源、工具和软件,以及申请样片或购买产品的快速链接。

表 2. 相关链接

| 器件          | 产品文件夹 | 样片与购买 | 技术文档 | 工具与软件 | 支持和社区 |

|-------------|-------|-------|------|-------|-------|

| LM5050-1    | 单击此处  | 单击此处  | 单击此处 | 单击此处  | 单击此处  |

| LM5050-1-Q1 | 单击此处  | 单击此处  | 单击此处 | 单击此处  | 单击此处  |

# 11.3 社区资源

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

### 11.4 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且不会对此文档进行修订。如需获取此数据表的浏览器版本,请查阅左侧的导航栏。

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device   | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|--------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

|                    | (-)    |              |                    |      |                | (=)          | (6)                           | (=)                |              | ( " - 7              |         |

| LM5050MK-1/NOPB    | ACTIVE | SOT-23-THIN  | DDC                | 6    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | SZHB                 | Samples |

| LM5050MKX-1/NOPB   | ACTIVE | SOT-23-THIN  | DDC                | 6    | 3000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | SZHB                 | Samples |

| LM5050Q0MK-1/NOPB  | ACTIVE | SOT-23-THIN  | DDC                | 6    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 150   | SL5B                 | Samples |

| LM5050Q0MKX-1/NOPB | ACTIVE | SOT-23-THIN  | DDC                | 6    | 3000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 150   | SL5B                 | Samples |

| LM5050Q1MK-1/NOPB  | ACTIVE | SOT-23-THIN  | DDC                | 6    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | SP3B                 | Samples |

| LM5050Q1MKX-1/NOPB | ACTIVE | SOT-23-THIN  | DDC                | 6    | 3000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | SP3B                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 9-Aug-2022

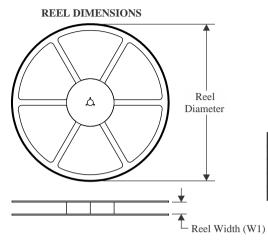

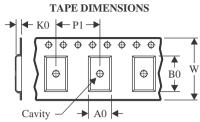

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

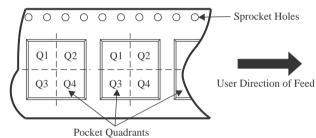

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM5050MK-1/NOPB    | SOT-23-<br>THIN | DDC                | 6 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM5050MKX-1/NOPB   | SOT-23-<br>THIN | DDC                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM5050Q0MK-1/NOPB  | SOT-23-<br>THIN | DDC                | 6 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM5050Q0MKX-1/NOPB | SOT-23-<br>THIN | DDC                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM5050Q1MK-1/NOPB  | SOT-23-<br>THIN | DDC                | 6 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM5050Q1MKX-1/NOPB | SOT-23-<br>THIN | DDC                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

www.ti.com 9-Aug-2022

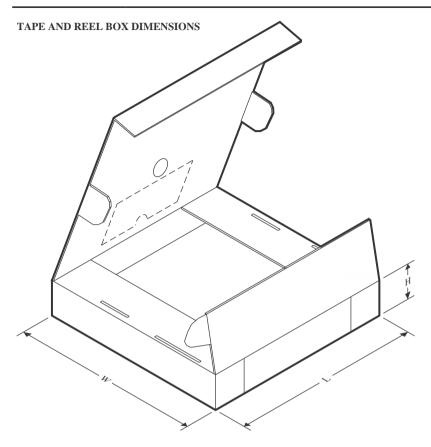

# \*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5050MK-1/NOPB    | SOT-23-THIN  | DDC             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM5050MKX-1/NOPB   | SOT-23-THIN  | DDC             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LM5050Q0MK-1/NOPB  | SOT-23-THIN  | DDC             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM5050Q0MKX-1/NOPB | SOT-23-THIN  | DDC             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LM5050Q1MK-1/NOPB  | SOT-23-THIN  | DDC             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM5050Q1MKX-1/NOPB | SOT-23-THIN  | DDC             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

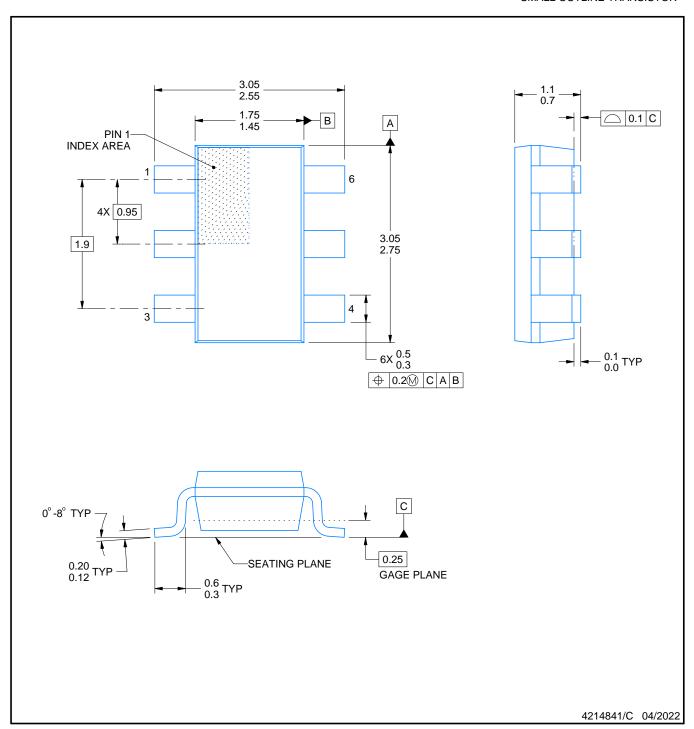

SMALL OUTLINE TRANSISTOR

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC MO-193.

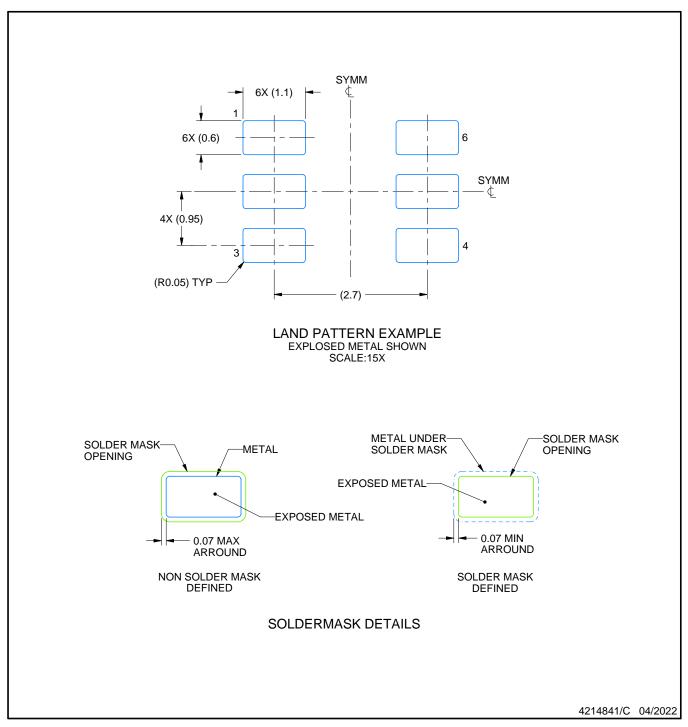

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 4. Publication IPC-7351 may have alternate designs.

- 5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

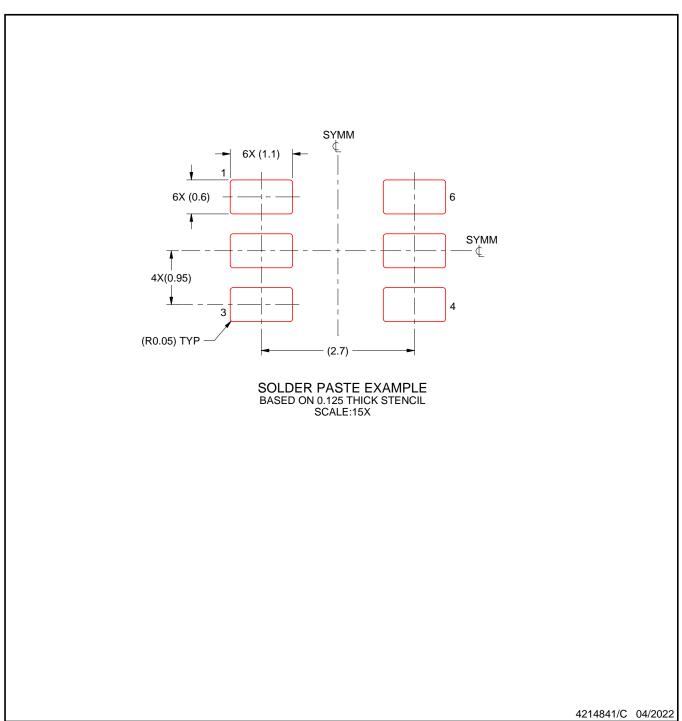

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Hot Swap Voltage Controllers category:

Click to view products by Texas Instruments manufacturer:

Other Similar products are found below:

LT4256-1CS8#TRPBF HIP1011BCBZA ISL6119HIBZA ISL6141IBZA ISL6151CBZA-T ISL61851ACBZ ISL61851BCBZ

ISL61851BIBZ-T ISL61851CCBZ ISL61851DCBZ ISL61851GCBZ ISL61851HCBZ ISL61851ICBZ ISL61851KCBZ TPS25961DRVR

TPS26612DDFR LM74700MDDFREP TPS23880RTQR MP5991GLU-Z MP5048GU-Z TPS259822LNRGER TPS259461ARPWR

TPS16530RGER LT4256-3IGN#TRPBF LT1641IS8#TRPBF LTC4218IGN#TRPBF LTC4210-1CS6#TRPBF LTC4211IMS8#TRPBF

RT1720GF TPS259827ONRGER LM74502HDDFR TPS259823ONRGER LM74502QDDFRQ1 LM5068MMX-2/NOPB

LM74502HQDDFRQ1 TPS25210LRPWR TPS26601RHFR TPS26611DDFR TPS259472ARPWR LM74500QDDFRQ1 TPS26610DDFR

TPS259460ARPWR LM5066IPMHX/NOPB TPS259824LNRGER TPS259823LNRGER NU6-II 60kA/385V 4P NU6-G 40kA/275V 4P

NU6-II 40kA/385V 2P TPS26635RGER AL6-NFNFBW-9