Sample &

Buy

### LM5105

SNVS349E -FEBRUARY 2005-REVISED AUGUST 2016

Support &

Community

# LM5105 100-V Half-Bridge Gate Driver With Programmable Dead Time

Technical

Documents

### 1 Features

- Drives Both a High-Side and Low-Side N-Channel MOSFET

- 1.8-A Peak Gate Drive Current

- Bootstrap Supply Voltage Range up to 118-V DC

- Integrated Bootstrap Diode

- Single TTL Compatible Input

- Programmable Turnon Delays (Dead Time)

- Enable Input Pin

- Fast Turnoff Propagation Delays (26 ns Typical)

- Drives 1000 pF With 15-ns Rise and Fall Time

- Supply Rail Undervoltage Lockout

- Low Power Consumption

- Package: Thermally Enhanced 10-Pin WSON (4 mm × 4 mm)

## 2 Applications

- Solid-State Motor Drives

- Half- and Full-Bridge Power Converters

## 3 Description

Tools &

Software

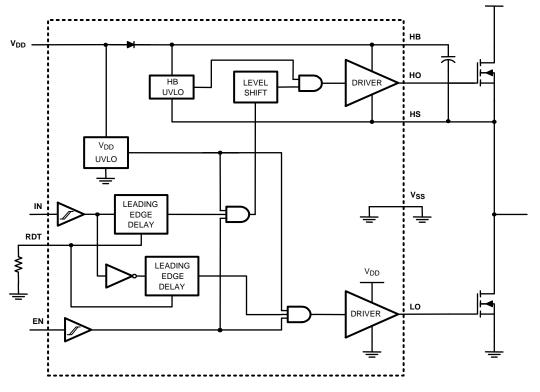

The LM5105 is a high-voltage gate driver designed to drive both the high-side and low-side N-Channel MOSFETs in a synchronous buck or half-bridge configuration. The floating high-side driver is capable of working with rail voltages up to 100 V. The single control input is compatible with TTL signal levels and a single external resistor programs the switching transition dead time through tightly matched turnon delay circuits. A high-voltage diode is provided to charge the high-side gate-drive bootstrap capacitor. The robust level shift technology operates at high speed while consuming low power and provides clean output transitions. Undervoltage lockout disables the gate driver when either the low-side or the bootstrapped high-side supply voltage is below the operating threshold. The LM5105 is offered in the thermally enhanced WSON plastic package.

### Device Information<sup>(1)</sup>

| Device information |           |                   |  |  |  |  |

|--------------------|-----------|-------------------|--|--|--|--|

| PART NUMBER        | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |

| LM5105             | WSON (10) | 4.00 mm × 4.00 mm |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

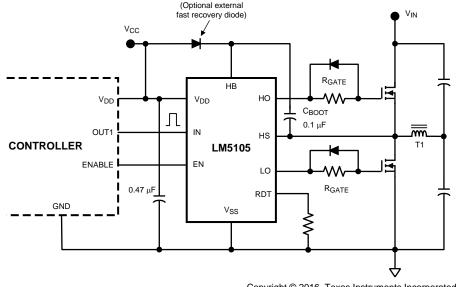

### Simplified Application Diagram

Copyright © 2016, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions        |

| 6 | Spe  | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 4                      |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 5              |

|   | 6.5  | Electrical Characteristics5        |

|   | 6.6  | Switching Characteristics 6        |

|   | 6.7  | Typical Characteristics8           |

| 7 | Deta | ailed Description 11               |

|   | 7.1  | Overview 11                        |

|   | 7.2  | Functional Block Diagram 11        |

|   | 7.3  | Feature Description 11             |

|   | 7.4  | Device Functional Modes 12         |

|   |      |                                    |

| 8  | Арр  | lication and Implementation 13                     |

|----|------|----------------------------------------------------|

|    | 8.1  | Application Information 13                         |

|    | 8.2  | Typical Application 13                             |

| 9  | Pow  | er Supply Recommendations 16                       |

|    | 9.1  | Power Dissipation Considerations 16                |

|    | 9.2  | HS Transient Voltages Below Ground 16              |

| 10 | Lay  | out 17                                             |

|    | 10.1 | Layout Guidelines 17                               |

|    | 10.2 | Layout Example 17                                  |

| 11 | Dev  | ice and Documentation Support 18                   |

|    | 11.1 | Documentation Support 18                           |

|    | 11.2 | Receiving Notification of Documentation Updates 18 |

|    | 11.3 |                                                    |

|    | 11.4 | Trademarks 18                                      |

|    | 11.5 | Electrostatic Discharge Caution 18                 |

|    | 11.6 | Glossary 18                                        |

| 12 |      | hanical, Packaging, and Orderable                  |

|    | Info | mation 18                                          |

|    |      |                                                    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision D (March 2016) to Revision E                                                                                                                                                                                    | Page    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Updated values in the <i>Thermal Information</i> table to align with JEDEC standards                                                                                                                                                  | 5       |

| Changes from Revision C (March 2013) to Revision D                                                                                                                                                                                    | Page    |

| • Added Device Information table, ESD Ratings, Detailed Description section, Application and Implementation section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Oro Information section | lerable |

| Changes from Revision B (March 2013) to Revision C                                                                                                                                                                                    | Page    |

| Changed layout of National Semiconductor Data Sheet to TI format                                                                                                                                                                      | 13      |

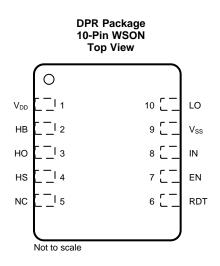

# 5 Pin Configuration and Functions

### Pin Functions

|     |                 |       | DESCRIPTION                                                                                                                                                                                                             |  |  |

|-----|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME            | ITPE" | DESCRIPTION                                                                                                                                                                                                             |  |  |

| 1   | V <sub>DD</sub> | Р     | Positive gate drive supply. Decouple VDD to VSS using a low ESR/ESL capacitor, placed as close to the IC as possible.                                                                                                   |  |  |

| 2   | НВ              | Р     | High-side gate driver bootstrap rail. Connect the positive terminal of bootstrap capacitor to the HB pin and connect negative terminal to HS. The Bootstrap capacitor must be placed as close to IC as possible.        |  |  |

| 3   | НО              | 0     | High-side gate driver output. Connect to the gate of high side N-MOS device through a short, low inductance path.                                                                                                       |  |  |

| 4   | HS              | Р     | High-side MOSFET source connection. Connect to the negative terminal of the bootstrap capacitor and to the source of the high side N-MOS device.                                                                        |  |  |

| 5   | NC              | _     | Not connected.                                                                                                                                                                                                          |  |  |

| 6   | RDT             | I     | Dead-time programming pin. A resistor from RDT to VSS programs the turnon delay of both the high and low side MOSFETs. The resistor must be placed close to the IC to minimize noise coupling from adjacent PCB traces. |  |  |

| 7   | EN              | I     | Logic input for driver disable or enable. TTL compatible threshold with hysteresis. LO and HO are held in the low state when EN is low.                                                                                 |  |  |

| 8   | IN              | I     | Logic input for gate driver. TTL compatible threshold with hysteresis. The high side MOSFET is turned on and the low side MOSFET turned off when IN is high.                                                            |  |  |

| 9   | V <sub>SS</sub> | G     | Ground return. All signals are referenced to this ground.                                                                                                                                                               |  |  |

| 10  | LO              | 0     | Low-side gate driver output. Connect to the gate of the low side N-MOS device with a short, low inductance path.                                                                                                        |  |  |

| _   | Exposed Pad     | _     | It is recommended that the exposed pad on the bottom of the package be soldered to ground plane on the PCB to aid thermal dissipation.                                                                                  |  |  |

(1) G = Ground, I = Input, O = Output, P = Power

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                       | MIN      | МАХ                   | UNIT |

|---------------------------------------|----------|-----------------------|------|

| V <sub>DD</sub> to V <sub>SS</sub>    | -0.3     | 18                    | V    |

| HB to HS                              | -0.3     | 18                    | V    |

| IN and EN to V <sub>SS</sub>          | -0.3     | V <sub>DD</sub> + 0.3 | V    |

| LO to V <sub>SS</sub>                 | -0.3     | V <sub>DD</sub> + 0.3 | V    |

| HO to V <sub>SS</sub>                 | HS – 0.3 | HB + 0.3              | V    |

| HS to $V_{SS}^{(3)}$                  | -5       | 100                   | V    |

| HB to V <sub>SS</sub>                 |          | 118                   | V    |

| RDT to V <sub>SS</sub>                | -0.3     | 5                     | V    |

| Junction temperature, T <sub>J</sub>  |          | 150                   | °C   |

| Storage temperature, T <sub>stg</sub> | -55      | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) In the application the HS node is clamped by the body diode of the external lower N-MOSFET, therefore the HS voltage generally does not exceed –1 V. However, in some applications, board resistance and inductance may result in the HS node exceeding this stated voltage transiently. If negative transients occur on HS, the HS voltage must never be more negative than V<sub>DD</sub> – 15 V. For example, if V<sub>DD</sub> = 10 V, the negative transients at HS must not exceed –5 V.

## 6.2 ESD Ratings

|                    |                         |                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM) <sup>(1)(2)</sup> | ±2000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) The human-body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin. Pin 2, Pin 3 and Pin 4 are rated at 500 V.

### 6.3 Recommended Operating Conditions

|                   |                      | MIN    | NOM | MAX     | UNIT |

|-------------------|----------------------|--------|-----|---------|------|

| V <sub>DD</sub>   |                      | 8      |     | 14      | V    |

| HS <sup>(1)</sup> |                      | -1     |     | 100     | V    |

| HB                |                      | HS + 8 |     | HS + 14 | V    |

| HS                | Slew rate            |        |     | <50     | V/ns |

| TJ                | Junction temperature | -40    |     | 125     | °C   |

(1) In the application the HS node is clamped by the body diode of the external lower N-MOSFET; therefore, the HS voltage generally does not exceed –1 V. However in some applications, board resistance and inductance may result in the HS node exceeding this stated voltage transiently. If negative transients occur on HS, the HS voltage must never be more negative than V<sub>DD</sub> – 15 V. For example, if V<sub>DD</sub> = 10 V, the negative transients at HS must not exceed –5 V.

### 6.4 Thermal Information

|                       |                                              | LM5105     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DPR (WSON) | UNIT |

|                       |                                              | 10 PINS    |      |

| $R_{	heta JA}$        | Junction-to-ambient thermal resistance       | 37.8       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 36.2       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 14.9       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 15.2       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.4        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

Unless otherwise noted,  $V_{DD} = HB = 12 \text{ V}$ ,  $V_{SS} = HS = 0 \text{ V}$ , EN = 5 V, no load on LO or HO, RDT= 100 k $\Omega^{(1)}$ . Typical limits are for  $T_J = 25^{\circ}$ C, and minimum and maximum limits apply over the operating junction temperature range (-40°C to 125°C).

|                   | PARAMETER                                | TEST CONDITIONS                                            | MIN  | ТҮР  | MAX  | UNIT |

|-------------------|------------------------------------------|------------------------------------------------------------|------|------|------|------|

| SUPPLY            | CURRENTS                                 | L                                                          |      |      |      |      |

| I <sub>DD</sub>   | V <sub>DD</sub> quiescent current        | IN = EN = 0 V                                              |      | 0.34 | 0.6  | mA   |

| I <sub>DDO</sub>  | V <sub>DD</sub> operating current        | f = 500 kHz                                                |      | 1.65 | 3    | mA   |

| I <sub>HB</sub>   | Total HB quiescent current               | IN = EN = 0 V                                              |      | 0.06 | 0.2  | mA   |

| I <sub>HBO</sub>  | Total HB operating current               | f = 500 kHz                                                |      | 1.3  | 3    | mA   |

| I <sub>HBS</sub>  | HB to V <sub>SS</sub> current, quiescent | HS = HB = 100 V                                            |      | 0.05 | 10   | μΑ   |

| I <sub>HBSO</sub> | HB to V <sub>SS</sub> current, operating | f = 500 kHz                                                |      | 0.1  |      | mA   |

| INPUT IN          | AND EN                                   |                                                            |      |      |      |      |

| V <sub>IL</sub>   | Low-level input voltage threshold        |                                                            | 0.8  | 1.8  |      | V    |

| VIH               | High-level input voltage threshold       |                                                            |      | 1.8  | 2.2  | V    |

| R <sub>pd</sub>   | Input pulldown resistance pin IN and EN  |                                                            | 100  | 200  | 500  | kΩ   |

| DEAD-TIN          | IE CONTROLS                              | L                                                          |      |      |      |      |

| VRDT              | Nominal voltage at RDT                   |                                                            | 2.7  | 3    | 3.3  | V    |

| IRDT              | RDT pin current limit                    | RDT = 0 V                                                  | 0.75 | 1.5  | 2.25 | mA   |

| UNDER V           | OLTAGE PROTECTION                        |                                                            | į    |      |      |      |

| V <sub>DDR</sub>  | V <sub>DD</sub> rising threshold         |                                                            | 6    | 6.9  | 7.4  | V    |

| V <sub>DDH</sub>  | V <sub>DD</sub> threshold hysteresis     |                                                            |      | 0.5  |      | V    |

| V <sub>HBR</sub>  | HB rising threshold                      |                                                            | 5.7  | 6.6  | 7.1  | V    |

| V <sub>HBH</sub>  | HB threshold hysteresis                  |                                                            |      | 0.4  |      | V    |

| BOOT ST           | RAP DIODE                                |                                                            | į    |      |      |      |

| V <sub>DL</sub>   | Low-current forward voltage              | I <sub>VDD-HB</sub> = 100 μA                               |      | 0.6  | 0.9  | V    |

| V <sub>DH</sub>   | High-current forward voltage             | $I_{VDD-HB} = 100 \text{ mA}$                              |      | 0.85 | 1.1  | V    |

| R <sub>D</sub>    | Dynamic resistance                       | $I_{VDD-HB} = 100 \text{ mA}$                              |      | 0.8  | 1.5  | Ω    |

| LO GATE           | DRIVER                                   |                                                            |      |      |      |      |

| V <sub>OLL</sub>  | Low-level output voltage                 | I <sub>LO</sub> = 100 mA                                   |      | 0.25 | 0.4  | V    |

| V <sub>OHL</sub>  | High-level output voltage                | $I_{LO} = -100 \text{ mA},$<br>$V_{OHL} = V_{DD} - V_{LO}$ |      | 0.35 | 0.55 | V    |

| I <sub>OHL</sub>  | Peak pullup current                      | LO = 0 V                                                   |      | 1.8  |      | А    |

| I <sub>OLL</sub>  | Peak pulldown current                    | LO = 12 V                                                  |      | 1.6  |      | А    |

(1) Minimum and maximum limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

### **Electrical Characteristics (continued)**

Unless otherwise noted,  $V_{DD} = HB = 12 \text{ V}$ ,  $V_{SS} = HS = 0 \text{ V}$ , EN = 5 V, no load on LO or HO, RDT= 100 k $\Omega^{(1)}$ . Typical limits are for  $T_J = 25^{\circ}$ C, and minimum and maximum limits apply over the operating junction temperature range (-40°C to 125°C).

|                  | PARAMETER                 | TEST CONDITIONS                                          | MIN | TYP  | MAX  | UNIT |  |

|------------------|---------------------------|----------------------------------------------------------|-----|------|------|------|--|

| HO GATE DRIVER   |                           |                                                          |     |      |      |      |  |

| V <sub>OLH</sub> | Low-level output voltage  | I <sub>HO</sub> = 100 mA                                 |     | 0.25 | 0.4  | V    |  |

| V <sub>OHH</sub> | High-level output voltage | I <sub>HO</sub> = -100 mA,<br>V <sub>OHH</sub> = HB - HO |     | 0.35 | 0.55 | V    |  |

| I <sub>OHH</sub> | Peak pullup current       | HO = 0 V                                                 |     | 1.8  |      | А    |  |

| I <sub>OLH</sub> | Peak pulldown current     | HO = 12 V                                                |     | 1.6  |      | A    |  |

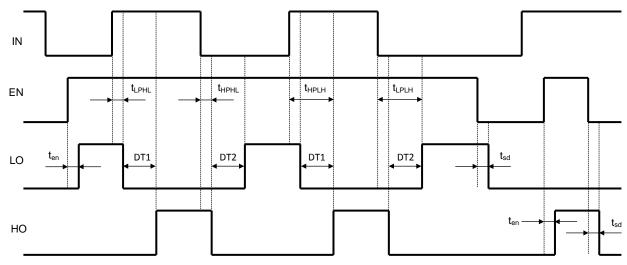

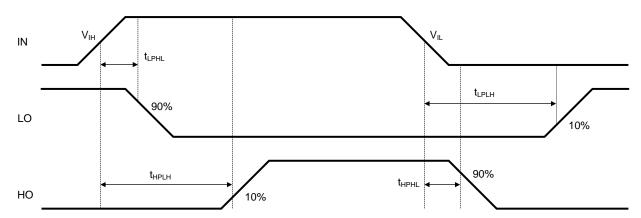

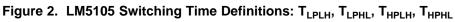

## 6.6 Switching Characteristics

Unless otherwise noted,  $V_{DD} = HB = 12$ ,  $V_{SS} = HS = 0$  V, no Load on LO or  $HO^{(1)}$ . Typical limits are for  $T_J = 25^{\circ}C$ , and minimum and maximum limits apply over the operating junction temperature range (-40°C to 125°C).

|                                   | PARAMETER                              | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|-----------------------------------|----------------------------------------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>LPHL</sub>                 | Lower turnoff propagation delay        |                                                 |     | 26  | 56  | ns   |

| t <sub>HPHL</sub>                 | Upper turnoff propagation delay        |                                                 |     | 26  | 56  | ns   |

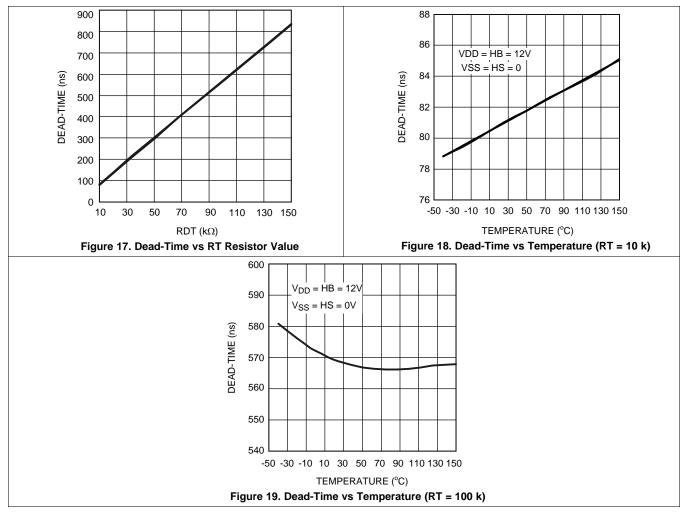

| t <sub>LPLH</sub>                 | Lower turnon propagation delay         | RDT = 100 k                                     | 485 | 595 | 705 | ns   |

| t <sub>HPLH</sub>                 | Upper turnon propagation delay         | RDT = 100 k                                     | 485 | 595 | 705 | ns   |

| t <sub>LPLH</sub>                 | Lower turnon propagation delay         | RDT = 10 k                                      | 75  | 105 | 150 | ns   |

| t <sub>HPLH</sub>                 | Upper turnon propagation delay         | RDT = 10 k                                      | 75  | 105 | 150 | ns   |

| t <sub>en</sub> , t <sub>sd</sub> | Enable and shutdown propagation delay  |                                                 |     | 28  |     | ns   |

|                                   | Dead-time LO OFF to HO ON              | RDT = 100 k                                     |     | 570 |     | ns   |

| DT1, DT2                          | and HO OFF to LO ON                    | RDT = 10 k                                      |     | 80  |     | ns   |

| MDT                               | Dead-time matching                     | RDT = 100 k                                     |     | 50  |     | ns   |

| t <sub>R</sub> , t <sub>F</sub>   | Either output rise or fall time        | C <sub>L</sub> = 1000 pF                        |     | 15  |     | ns   |

| t <sub>BS</sub>                   | Bootstrap diode turnon or turnoff time | I <sub>F</sub> = 20 mA, I <sub>R</sub> = 200 mA |     | 50  |     | ns   |

(1) Minimum and maximum limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

Figure 1. LM5105 Input - Output Waveforms

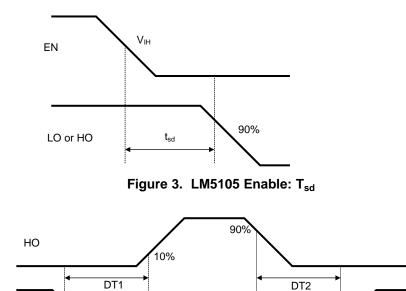

Figure 4. LM5105 Dead-Time: DT

MDT + |DT1-DT2|

90%

LO

, 10%

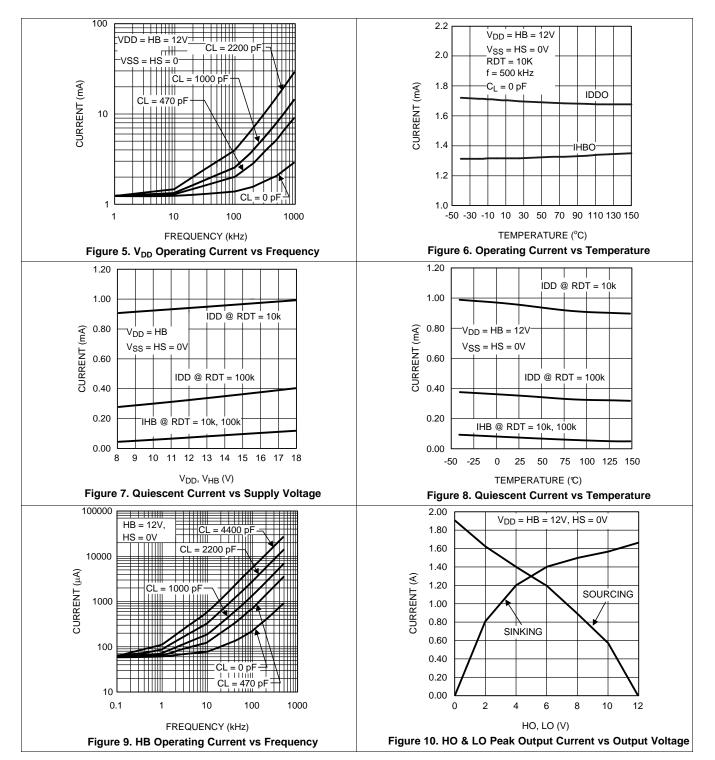

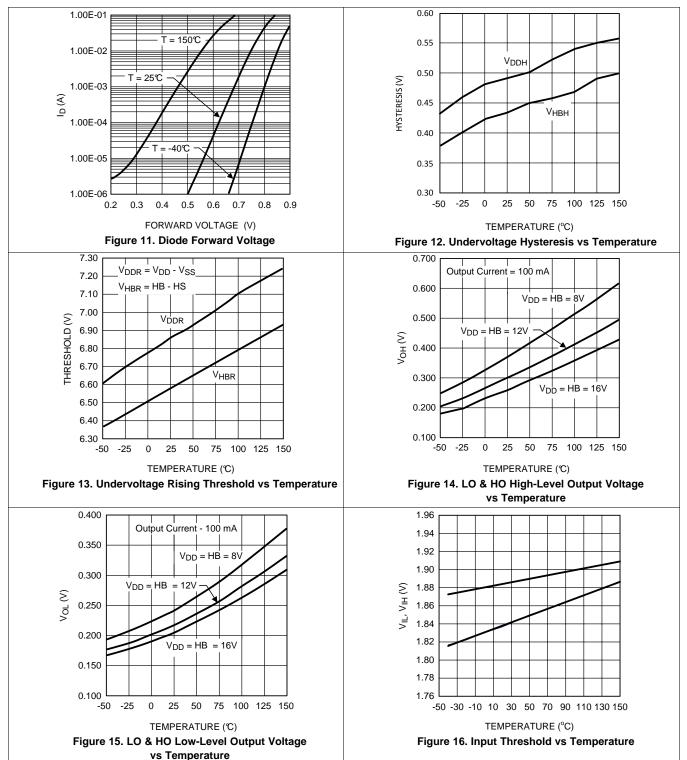

## 6.7 Typical Characteristics

### **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

## 7 Detailed Description

### 7.1 Overview

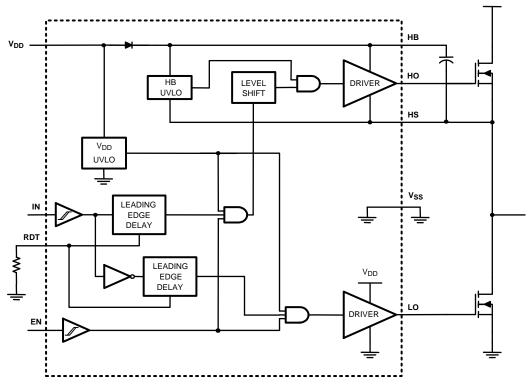

The LM5105 is a single PWM input Gate Driver with Enable that offers a programmable dead time. The dead time is set with a resistor at the RDT pin and can be adjusted from 100 ns to 600 ns. The wide dead-time programming range provides the flexibility to optimize drive signal timing for a wide range of MOSFETS and applications.

The RDT pin is biased at 3 V and current-limited to 1-mA maximum programming current. The time delay generator accommodates resistor values from 5 k to 100 k with a dead time that is proportional to the RDT resistance. Grounding the RDT pin programs the LM5105 to drive both outputs with minimum dead time.

### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

### 7.3 Feature Description

### 7.3.1 Start-Up and UVLO

Both top and bottom drivers include undervoltage lockout (UVLO) protection circuitry, which monitors the supply voltage ( $V_{DD}$ ) and bootstrap capacitor voltage (HB – HS) independently. The UVLO circuit inhibits each driver until sufficient supply voltage is available to turn on the external MOSFETs, and the UVLO hysteresis prevents chattering during supply voltage transitions. When the supply voltage is applied to the  $V_{DD}$  pin of LM5105, the top and bottom gates are held low until  $V_{DD}$  exceeds the UVLO threshold, typically about 6.9 V. Any UVLO condition on the bootstrap capacitor disables only the high-side output (HO).

### 7.4 Device Functional Modes

Table 1 lists the functional modes for LM5105.

### Table 1. Function Table

| EN | IN PIN | LO PIN | HO PIN |  |  |

|----|--------|--------|--------|--|--|

| L  | Any    | L      | L      |  |  |

| Н  | Н      | L      | Н      |  |  |

| Н  | L      | Н      | L      |  |  |

### 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The LM5105 is one of the latest generation of high-voltage gate drivers which are designed to drive both the high-side and low-side N-channel MOSFETs in a half-bridge or full-bridge configuration or in a synchronous buck circuit. The floating high-side driver can operate with supply voltages up to 110 V. This allows for N-channel MOSFET control in half-bridge, full-bridge, push-pull, two-switch forward, and active clamp topologies.

The outputs of the LM5105 are controlled from a single input. The rising edge of each output can be delayed with a programming resistor.

### 8.2 Typical Application

### 8.2.1 Design Requirements

Table 2 lists the design parameters for this application example.

| Table 2. Design Falanciers |             |  |  |  |  |  |  |

|----------------------------|-------------|--|--|--|--|--|--|

| PARAMETER                  | VALUE       |  |  |  |  |  |  |

| Gate Drive IC              | LM5105      |  |  |  |  |  |  |

| Mosfet                     | CSD18531Q5A |  |  |  |  |  |  |

| V <sub>DD</sub>            | 10 V        |  |  |  |  |  |  |

| Q <sub>gmax</sub>          | 43 nC       |  |  |  |  |  |  |

| F <sub>sw</sub>            | 100 kHz     |  |  |  |  |  |  |

| D <sub>Max</sub>           | 95%         |  |  |  |  |  |  |

| I <sub>HBS</sub>           | 10 µA       |  |  |  |  |  |  |

| V <sub>DH</sub>            | 1.1 V       |  |  |  |  |  |  |

### Table 2. Design Parameters

| Table 2. Design Parameters (continued) |

|----------------------------------------|

|----------------------------------------|

| PARAMETER        | VALUE |

|------------------|-------|

| V <sub>HBR</sub> | 7.1 V |

| V <sub>HBH</sub> | 0.4 V |

### 8.2.2 Detailed Design Procedure

$\Delta V_{HB} = V_{DD} - V_{DH} - V_{HBL}$

where

- $V_{DD}$  = Supply voltage of the gate drive IC

- V<sub>DH</sub> = Bootstrap diode forward voltage drop

- V<sub>asmin</sub> = Minimum gate source threshold voltage

$C_{BOOT} = \frac{\Delta V}{\Delta V_{HB}}$

$$Q_{\text{TOTAL}} = Q_{\text{gmax}} + I_{\text{HBS}} \times \frac{D_{\text{Max}}}{F_{\text{SW}}}$$

(3)

The quiescent current of the bootstrap circuit is 10  $\mu$ A, which is negligible compared to the Qgs of the MOSFET.

$$Q_{\text{TOTAL}} = 43nC + 10\mu A \times \frac{0.95}{100 \text{kHz}}$$

(4)

$$Q_{\text{TOTAL}} = 43.01 \text{ nC}$$

(5)

In practice the value for the C<sub>BOOT</sub> capacitor should be greater than that calculated to allow for situations where the power stage may skip pulse due to load transients. In this circumstance the boot capacitor must maintain the HB pin voltage above the UVLO voltage for the HB circuit.

As a general rule the local  $V_{DD}$  bypass capacitor should be 10 times greater than the calculated value of  $C_{BOOT}$ .

| V <sub>HBL</sub> = V <sub>HBR</sub> - V <sub>HBH</sub>         | (6)  |

|----------------------------------------------------------------|------|

| $V_{HBL} = 6.7 V$                                              | (7)  |

| $\Delta V_{HB} = 10 \text{ V} - 1.1 \text{ V} - 6.7 \text{ V}$ | (8)  |

| $\Delta V_{HB} = 2.2 V$                                        | (9)  |

| C <sub>BOOT</sub> = 43.01nc / 2.2 V                            | (10) |

| C <sub>BOOT</sub> = 19.6 nF                                    | (11) |

In practice, the value of C<sub>Boot</sub> is greater than the calculated value. This allows for the capacitance shift caused by the DC bias voltage and for situations where the power stage would otherwise skip pulses due to load transients. Therefore, it is recommended to include a safety-related margin in the C<sub>Boot</sub> value and place it as close to the VDD and VSS pins as possible. A 50-V, 0.1-µF capacitor is chosen in this example.

The bootstrap and bias capacitors should be ceramic types with X7R dielectric. The voltage rating should be twice that of the maximum VDD to allow for loss of capacitance once the devices have a DC bias voltage across them and to ensure long-term reliability of the devices.

The resistor values, RT, for setting turnon delay can be found in Figure 17.

(1)

(2)

### 8.2.3 Application Curves

16 Submit Documentation Feedback

Copyright © 2005–2016, Texas Instruments Incorporated

# 9 Power Supply Recommendations

## 9.1 Power Dissipation Considerations

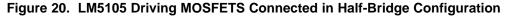

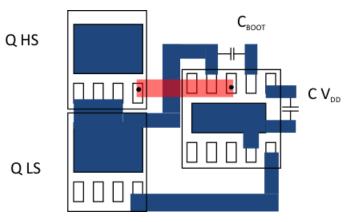

The total IC power dissipation is the sum of the gate driver losses and the bootstrap diode losses. The gate driver losses are related to the switching frequency (f), output load capacitance on LO and HO ( $C_L$ ), and supply voltage ( $V_{DD}$ ) and can be roughly calculated with Equation 12.

$$P_{DGATES} = 2 \times f \times C_{L} \times V_{DD}^{2}$$

There are some additional losses in the gate drivers due to the internal CMOS stages used to buffer the LO and HO outputs. Figure 23 shows the measured gate driver power dissipation versus frequency and load capacitance. At higher frequencies and load capacitance values, the power dissipation is dominated by the power losses driving the output loads and agrees well with the previous equation. Figure 23 can be used to approximate the power losses due to the gate drivers.

### 9.2 HS Transient Voltages Below Ground

The HS node is always clamped by the body diode of the lower external FET. In some situations, board resistances and inductances can cause the HS node to transiently swing several volts below ground. The HS node can swing below ground provided:

- 1. HS must always be at a lower potential than HO. Pulling HO more than -0.3 V below HS can activate parasitic transistors resulting in excessive current flow from the HB supply, possibly resulting in damage to the IC. The same relationship is true with LO and VSS. If necessary, a Schottky diode can be placed externally between HO and HS or LO and GND to protect the IC from this type of transient. The diode must be placed as close to the IC pins as possible in order to be effective.

- 2. HB to HS operating voltage should be 14 V or less. Hence, if the HS pin transient voltage is -5 V, VDD should be ideally limited to 9 V to keep HB to HS below 14 V.

- 3. Low ESR bypass capacitors from HB to HS and from VCC to VSS are essential for proper operation. The capacitor should be located at the leads of the IC to minimize series inductance. The peak currents from LO and HO can be quite large. Any inductances in series with the bypass capacitor will cause voltage ringing at the leads of the IC which must be avoided for reliable operation.

### 10 Layout

### **10.1 Layout Guidelines**

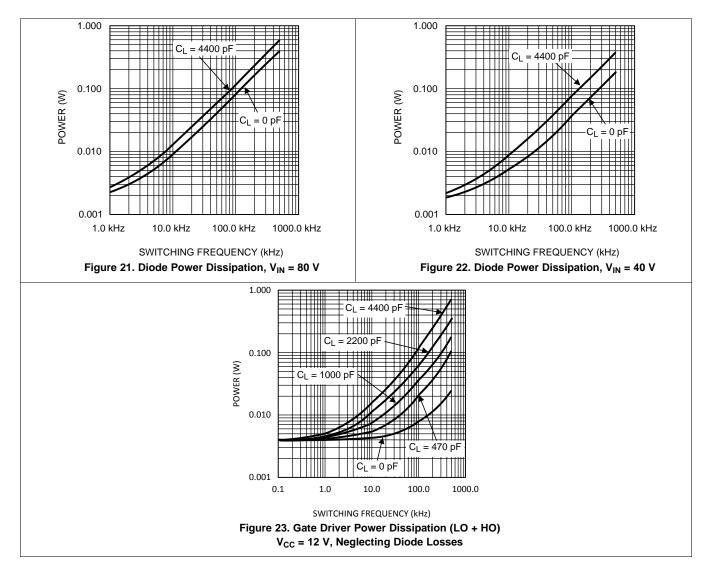

The optimum performance of high- and low-side gate drivers cannot be achieved without taking due considerations during circuit board layout. Following points are emphasized.

- 1. A low ESR or ESL capacitor must be connected close to the IC, and between  $V_{DD}$  and  $V_{SS}$  pins and between HB and HS pins to support high peak currents being drawn from  $V_{DD}$  during turnon of the external MOSFET.

- 2. To prevent large voltage transients at the drain of the top MOSFET, a low ESR electrolytic capacitor must be connected between MOSFET drain and ground (V<sub>SS</sub>).

- 3. To avoid large negative transients on the switch node (HS) pin, the parasitic inductances in the source of top MOSFET and in the drain of the bottom MOSFET (synchronous rectifier) must be minimized.

- 4. Grounding considerations:

- The first priority in designing grounding connections is to confine the high peak currents from charging and discharging the MOSFET gate in a minimal physical area. This decreases the loop inductance and minimize noise issues on the gate terminal of the MOSFET. The MOSFETs must be placed as close as possible to the gate driver.

- The second high current path includes the bootstrap capacitor, the bootstrap diode, the local ground referenced bypass capacitor and low side MOSFET body diode. The bootstrap capacitor is recharged on the cycle-by-cycle basis through the bootstrap diode from the ground referenced V<sub>DD</sub> bypass capacitor. The recharging occurs in a short time interval and involves high peak current. Minimizing this loop length and area on the circuit board is important to ensure reliable operation.

- 5. The resistor on the RDT pin must be placed very close to the IC and separated from high current paths to avoid noise coupling to the time delay generator which could disrupt timer operation.

### 10.2 Layout Example

Figure 24. Component Placement

TEXAS INSTRUMENTS

www.ti.com

### **11** Device and Documentation Support

### **11.1 Documentation Support**

### 11.1.1 Related Documentation

For related documentation see the following:

AN-1187 Leadless Leadframe Package (LLP) (SNOA401)

### 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### **11.3 Community Resource**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 11.4 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 11.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LM5105SD/NOPB    | ACTIVE        | WSON         | DPR                | 10   | 1000           | RoHS & Green    | NIPDAU   SN                          | Level-1-260C-UNLIM   | -40 to 125   | L5105SD                 | Samples |

| LM5105SDX/NOPB   | ACTIVE        | WSON         | DPR                | 10   | 4500           | RoHS & Green    | NIPDAU   SN                          | Level-1-260C-UNLIM   | -40 to 125   | L5105SD                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

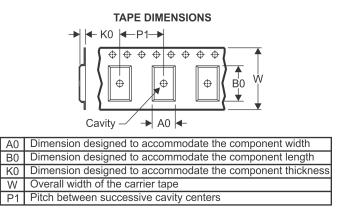

## TAPE AND REEL INFORMATION

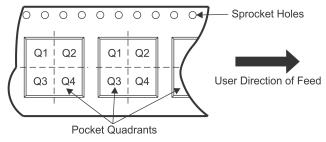

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM5105SD/NOPB               | WSON            | DPR                | 10 | 1000 | 180.0                    | 12.4                     | 4.3        | 4.3        | 1.1        | 8.0        | 12.0      | Q1               |

| LM5105SD/NOPB               | WSON            | DPR                | 10 | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5105SDX/NOPB              | WSON            | DPR                | 10 | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

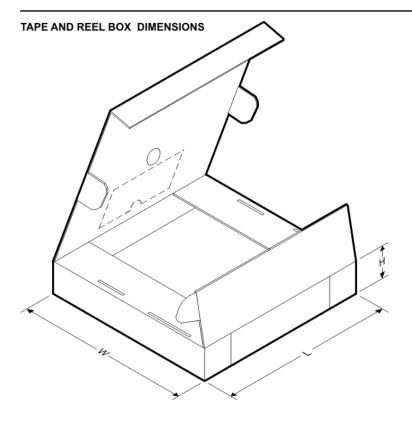

# PACKAGE MATERIALS INFORMATION

21-Oct-2021

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5105SD/NOPB  | WSON         | DPR             | 10   | 1000 | 200.0       | 183.0      | 25.0        |

| LM5105SD/NOPB  | WSON         | DPR             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

| LM5105SDX/NOPB | WSON         | DPR             | 10   | 4500 | 367.0       | 367.0      | 35.0        |

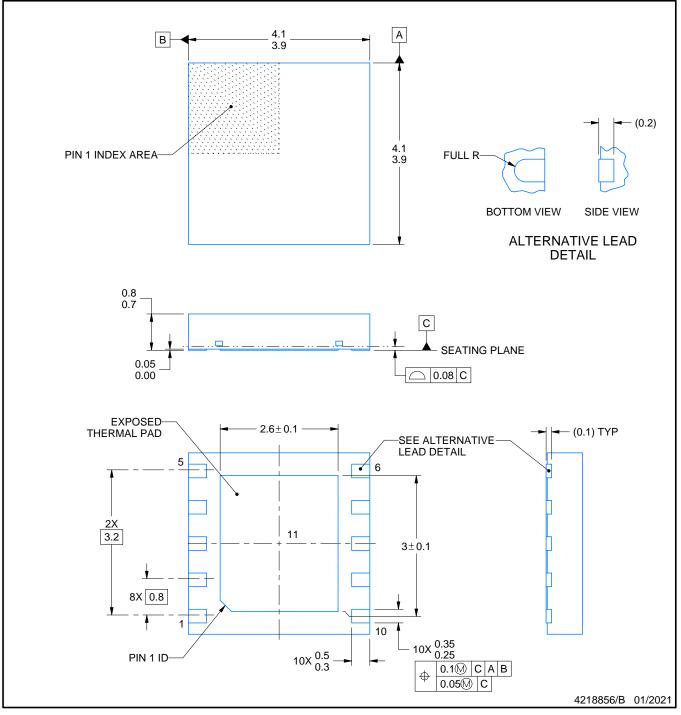

# **DPR0010A**

# **PACKAGE OUTLINE**

## WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.2. This drawing is subject to change without notice.3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

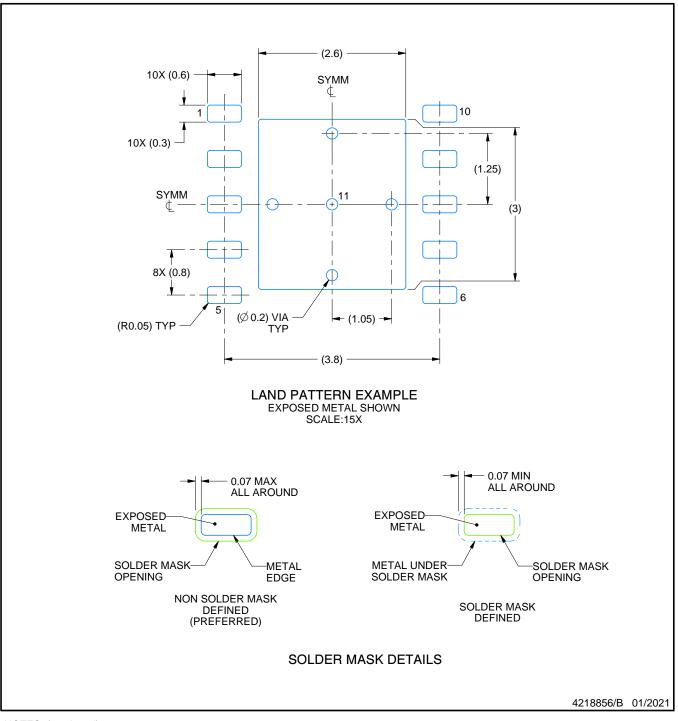

# **DPR0010A**

# **EXAMPLE BOARD LAYOUT**

## WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

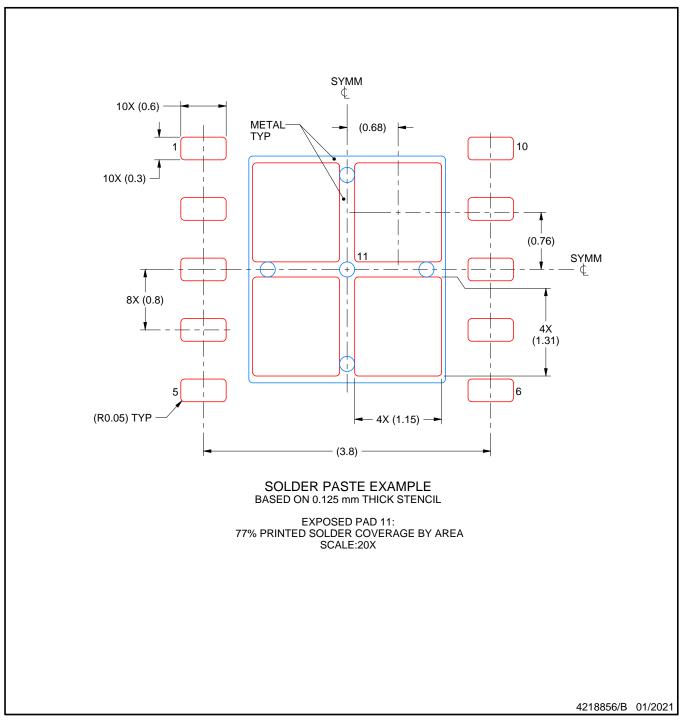

# **DPR0010A**

# **EXAMPLE STENCIL DESIGN**

## WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by Texas Instruments manufacturer:

Other Similar products are found below :

56956

57.404.7355.5

LT4936

57.904.0755.0

5811-0902

0131700000

LTP70N06

LVP640

5J0-1000LG-SIL

LY2-US-AC240

LY3-UA

DC24

LZNQ2-US-DC12

LZP40N10

60100564

60249-1-CUT-TAPE

0134220000

6035

60713816

61161-90

6131-204-23149P

6131-205

17149P

6131-209-15149P

6131-218-17149P

6131-220-21149P

6131-260-2358P

6131-265-11149P

CS1HCPU63

6150-5001

CSB4

CSK

38-60006

CSK-38-60008

621A

622-4053LF

6273

M40N08MA-H

M55155/29XH06

64-807

65-1930-6

CV500ISB02

M83723/88Y1407N

CWD012-2

CWD03-3

CX3225SB16934D0PPSC2

CX5032GB10000D0PPS02

687-772NF1

70.140.1653

70.200.0653.0

703001B01F060

70-3601

706006D02F0601

601

687-772NF1

70.140.1653

70.200.0653.0

703001B01F060