Sample &

Buy

LM98620

SNAS426C - FEBRUARY 2008 - REVISED MAY 2014

# LM98620 10-Bit 70 MSPS 6 Channel Imaging Signal Processor with LVDS Output

#### Features 1

Texas

- 3.3 V Single Supply Operation

- CDS or S/H Processing

**INSTRUMENTS**

- 35 MHz Channel Rate

- Enhanced ESD Protection on Timing, Control and LVDS Pins

- Low Power CMOS Design

- 12 Terminal to 16 Terminal (Selectable) LVDS Serialized Data Output

- 4-Wire Serial Interface

- 2 Channel Symmetrical Architecture

- Independent Gain and Offset Correction for Each Channel

- Digital Black Level Calibration for Each Channel

- Digital White Level Calibration for Each Channel

- Programmable Input Clamp

- **Key Specifications**

- Maximum Input Level:

- 1.2 Vp-p (CDS Gain = 1.0)

- 0.58 Vp-p (CDS Gain = 2.1)

- Input Sample Rate:

- 5 to 35 MSPS 6ch mode

- 10 to 35 MSPS 3ch mode

- PGA Gain Range: 1x to 10x (0 to 20 dB)

- CDS/SH Gain Settings: 1x or 2.1x

- Total Channel Gain: 1x to 21x (0 to 26 dB)

- PGA Gain Resolution: 8 bits Analog

- ADC Resolution: 10 bits

- ADC Sampling Rate: 10 to 70 MSPS

- SNR: 68.5 dB (Gain = 1x)

- Offset DAC Range:

- ±111 mV or ±59.5 mV FDAC

- ±281 mV CDAC

- Offset DAC Resolution:

- ±10 bits FDAC

- ±4 bits CDAC

- Supply Voltage: 3.0 V to 3.6 V

- Power Dissipation: 1.02 W (typical)

# 2 Applications

- High Performance Digital Color Copiers

- Scanners

- Other Image Processing Applications

#### Description 3

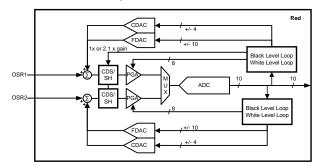

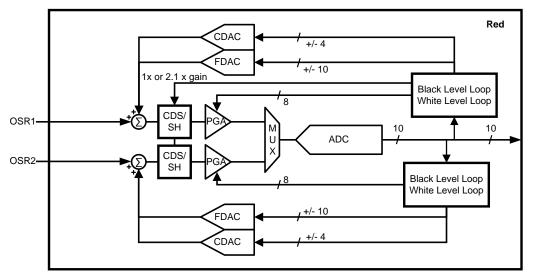

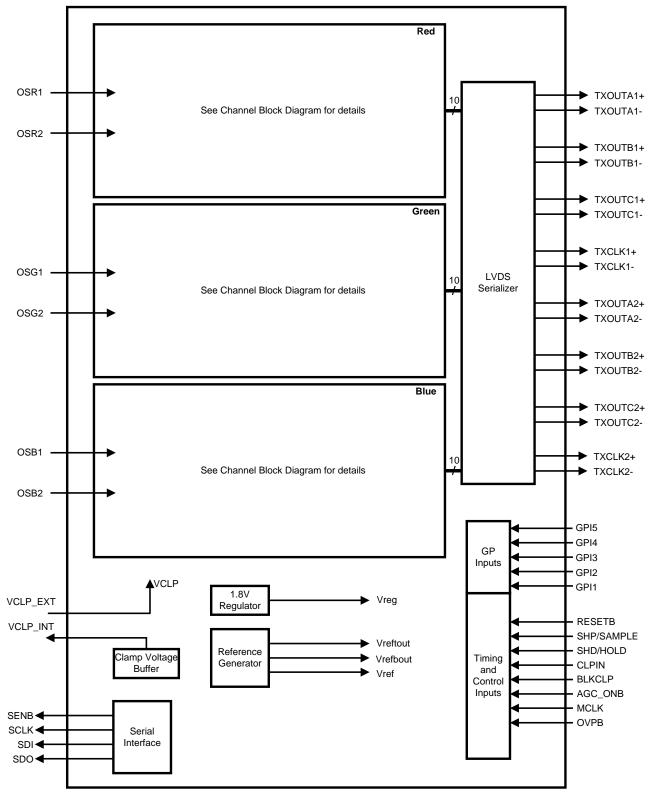

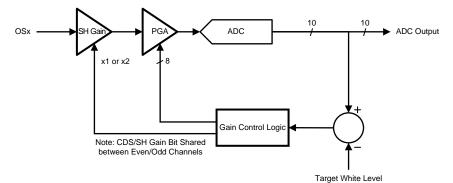

The LM98620 is a fully integrated, 10-Bit, 70 MSPS signal processing solution for high performance digital color copiers, scanners, and other image processing applications. High-speed signal throughput is achieved with an innovative six channel architecture utilizing Correlated Double Sampling (CDS), or Sample and Hold (SH) type sampling. Gain settings of 1x or 2x are available in the CDS/SH input stage. Each channel has a dedicated 1x to 10x (8 bit) PGA that allows accurate gain adjustment. The Digital White Level auto calibration loop can automatically set the PGA value to achieve a selected white target level. Each channel also has a ±4 bit coarse and ±10bit fine analog offset correction DAC that allows offset correction before the sample-and-hold amplifier. These correction values can be controlled by an automated Digital Black Level correction loop. The PGA and offset DACs for each channel are programmed independently allowing unique values of gain and offset for each of the six channels. A 2-to-1 multiplexing scheme routes the signals to three 70 MHz high performance ADCs. The fully differential processing channels achieve exceptional noise immunity, having a very low noise floor of -68.5dB. The 10-bit analog-to-digital converters have excellent performance, making dvnamic the LM98620 transparent in the image reproduction chain.

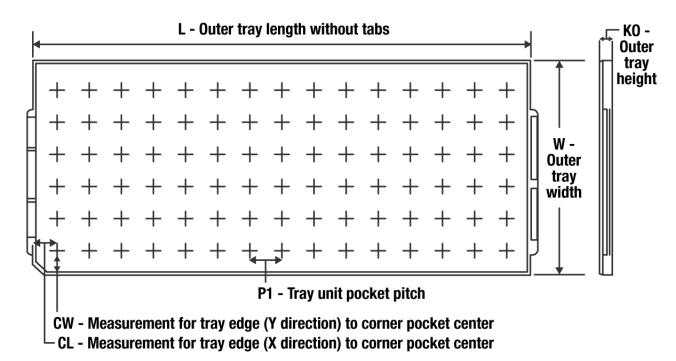

#### Device Information<sup>(1)</sup>

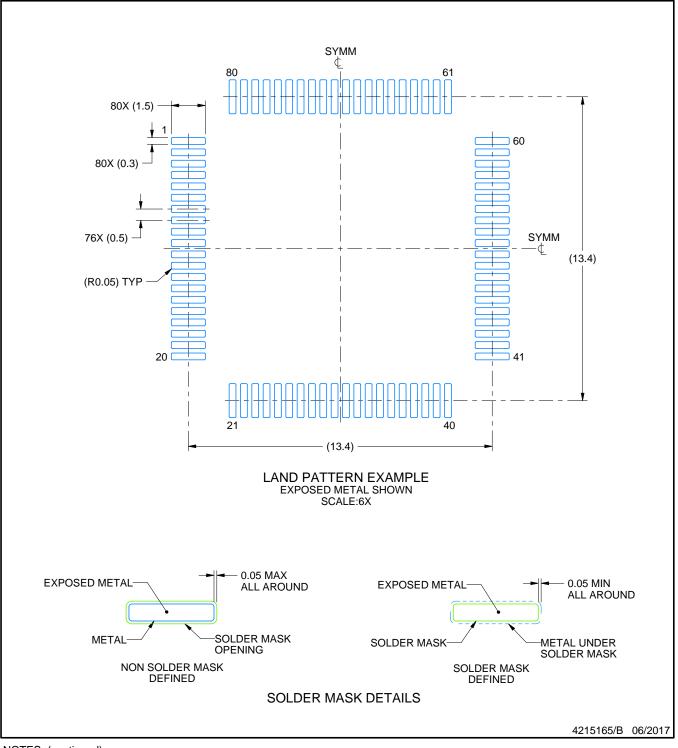

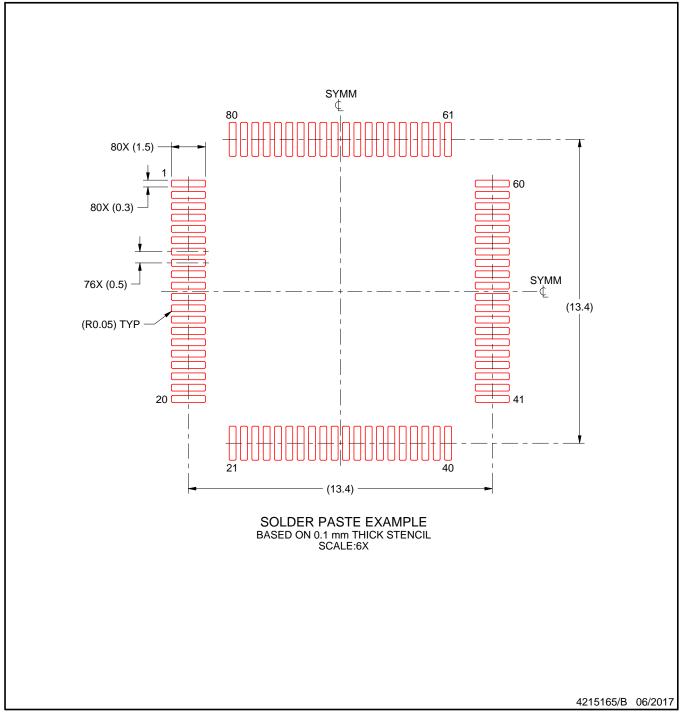

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |  |  |

|-------------|-----------|---------------------|--|--|

| LM98620     | TQFP (80) | 12.00 mm × 12.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

#### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                          |    | 7.2   |

|---|-----------------------------------------------------|----|-------|

| 2 | Applications 1                                      |    | 7.3   |

| 3 | Description 1                                       |    | 7.4   |

| 4 | Revision History                                    |    | 7.5   |

| 5 | Pin Configuration and Functions                     |    | 7.6   |

| 6 | Specifications                                      | 8  | Appli |

|   | 6.1 Absolute Maximum Ratings 5                      |    | 8.1   |

|   | 6.2 Handling Ratings 6                              | -  | 8.2   |

|   | 6.3 Recommended Operating Conditions                | 9  | Powe  |

|   | 6.4 Thermal Information7                            |    | 9.1   |

|   | 6.5 Electrical Characteristics                      | 10 | Layo  |

|   | 6.6 Timing Requirements, AFE/ADC Timing             |    | 10.1  |

|   | 6.7 Timing Requirements, Serial Interface Timing 10 |    | 10.2  |

|   | 6.8 Timing Requirements, LVDS Output Timing 11      | 11 | Devi  |

|   | 6.9 LVDS TIming 15                                  |    | 11.1  |

|   | 6.10 User Input Based Timing 17                     |    | 11.2  |

| 7 | Detailed Description                                |    | 11.3  |

|   | 7.1 Overview                                        | 12 | Mech  |

| 7.2  | Functional Block Diagram                                                                                                                                     | 19                                          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 7.3  | Feature Description                                                                                                                                          | 21                                          |

| 7.4  | Device Functional Modes                                                                                                                                      | 31                                          |

| 7.5  | Programming                                                                                                                                                  | 35                                          |

| 7.6  | Register Maps                                                                                                                                                | 46                                          |

| App  | lications and Implementation                                                                                                                                 | . 58                                        |

| 8.1  | Application Information                                                                                                                                      | 58                                          |

| 8.2  | Typical Applications                                                                                                                                         | 59                                          |

| Pow  | er Supply Recommendations                                                                                                                                    | . 62                                        |

| 9.1  | Over Voltage Protection on OS Inputs                                                                                                                         | 62                                          |

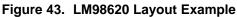

| Laye | out                                                                                                                                                          | . 63                                        |

| -    |                                                                                                                                                              |                                             |

| 10.2 | Layout Examples                                                                                                                                              | 64                                          |

| Dev  | ice and Documentation Support                                                                                                                                | . 65                                        |

| 11.1 | Trademarks                                                                                                                                                   | 65                                          |

| 11.2 | Electrostatic Discharge Caution                                                                                                                              | 65                                          |

| 11.3 | Glossary                                                                                                                                                     | 65                                          |

| Мес  | hanical, Packaging, and Orderable                                                                                                                            |                                             |

|      |                                                                                                                                                              | . 65                                        |

|      | 7.3<br>7.4<br>7.5<br>7.6<br><b>App</b><br>8.1<br>8.2<br><b>Pow</b><br>9.1<br><b>Layo</b><br>10.1<br>10.2<br><b>Dev</b><br>11.1<br>11.2<br>11.3<br><b>Mec</b> | <ul> <li>8.2 Typical Applications</li></ul> |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C  | hanges from Revision B (January 2014) to Revision C Page                                                                                                                                                                                                        |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | Added data sheet flow and layout to conform with new TI standards. Added the following sections: Applications and<br>Implementation; Power Supply Recommendations; Layout; Device and Documentation Support; Mechanical,<br>Packaging, and Ordering Information |

| •  | Added footnote "When the input voltage" to Absolute Maximum Ratings table                                                                                                                                                                                       |

| CI | hanges from Revision A (December 2013) to Revision B Page                                                                                                                                                                                                       |

| •  | Changed format of data sheet to conform with TI standards 1                                                                                                                                                                                                     |

| C  | hanges from Original (February 2008) to Revision A Page                                                                                                                                                                                                         |

| •  | Added sections to make full data sheet from template 1                                                                                                                                                                                                          |

www.ti.com

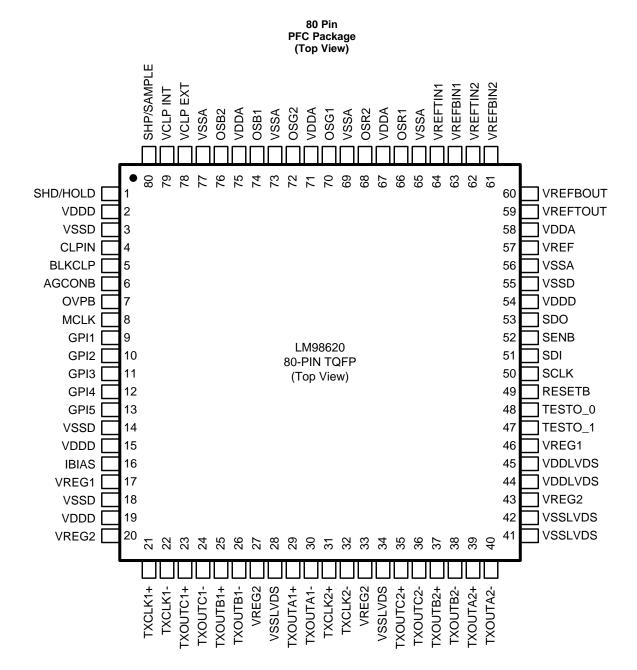

# 5 Pin Configuration and Functions

LM98620 SNAS426C-FEBRUARY 2008-REVISED MAY 2014 Texas NSTRUMENTS

www.ti.com

|          |                       |                     | Pin       | Functions                                                                                                                                                                                                                                                            |

|----------|-----------------------|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | PIN                   | TYPE <sup>(1)</sup> | PULLUP    | DESCRIPTION                                                                                                                                                                                                                                                          |

| NAME     | NUMBER                | ITFE''              | PULLDOWN  | DESCRIPTION                                                                                                                                                                                                                                                          |

| SHD/HOLD | 1                     | DI                  |           | Data Clamp Pulse/Hold Input                                                                                                                                                                                                                                          |

| VDDD     | 2, 15, 19, 54         | PI                  |           | Digital Power Supply                                                                                                                                                                                                                                                 |

| VSSD     | 3, 14, 18, 55         | PI                  |           | Digital Power Supply Ground                                                                                                                                                                                                                                          |

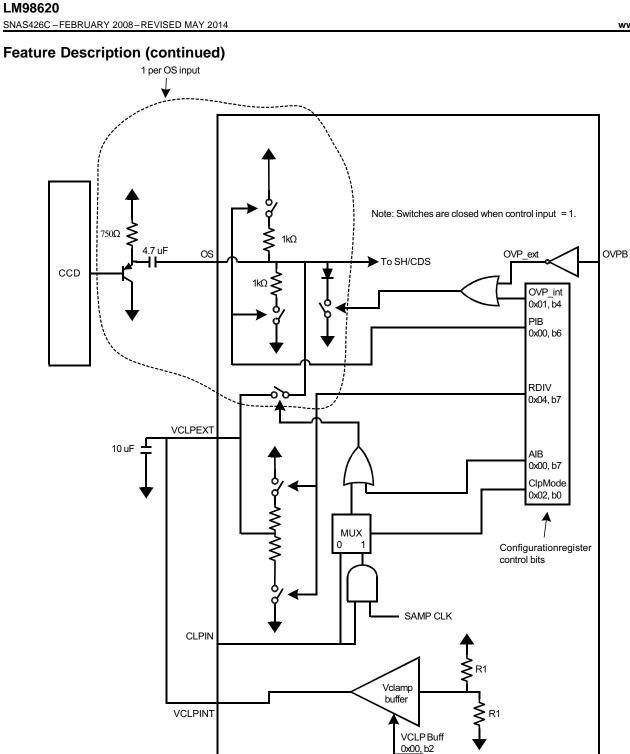

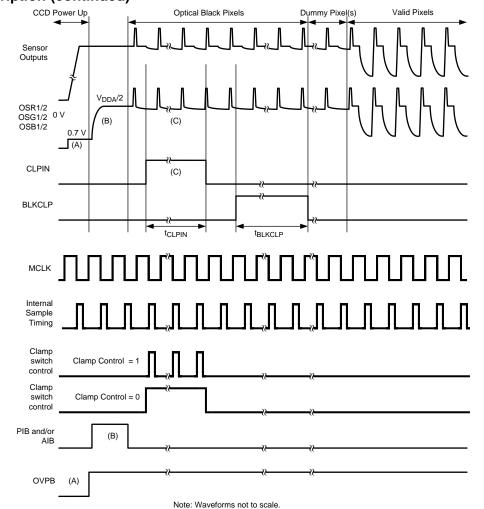

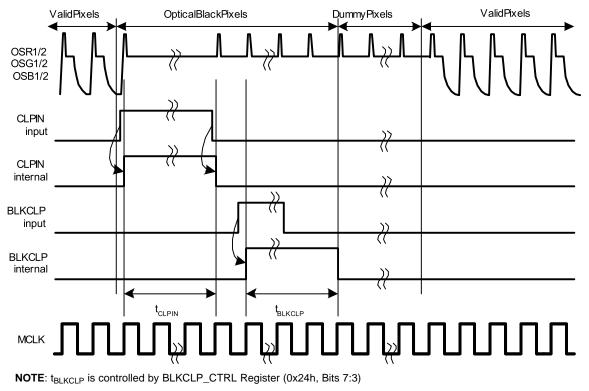

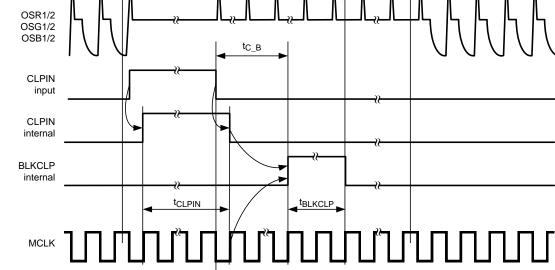

| CLPIN    | 4                     | DI                  |           | Input Pulse that Invokes the Input Clamp Switch                                                                                                                                                                                                                      |

| BLKCLP   | 5                     | DI                  | PD 108 kΩ | Input Pulse that Invokes the Black Calibration Loop                                                                                                                                                                                                                  |

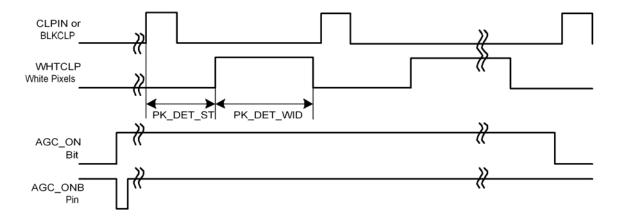

| AGC_ONB  | 6                     | DI                  | PU 108 kΩ | Input Pulse that Invokes the White Calibration Loop. Tie high to disable White Clamp. Pulse Low to initiate White Clamp. (Active Low)                                                                                                                                |

| OVPB     | 7                     | DI                  |           | Over Voltage Protection Enable (Active Low). Enables OS input protections switches to ground during system power up. Should be tied high after AFE and CCD voltages have stabilized.                                                                                 |

| MCLK     | 8                     | DI                  |           | Master Clock Input                                                                                                                                                                                                                                                   |

| GPI1-5   | 9 to 13               | DI                  |           | General Purpose Inputs 1 – 5, mapped into LVDS output data                                                                                                                                                                                                           |

| IBIAS    | 16                    | AO                  |           | Optional IBIAS resistor connection. To minimize device to device power consumption variation, connect an 11k $\Omega$ 1% resistor to VSSA. If no resistor is used, the internal bias and power supply currents will be subject to normal device to device variation. |

| VREG1    | 17, 46                | PO                  |           | Decoupling connection for VREG1 – Approx. 1.8 V output <sup>(2)</sup>                                                                                                                                                                                                |

|          |                       |                     |           | Decoupling connection for VREG2 – Approx. 1.8 V output <sup>(2)</sup>                                                                                                                                                                                                |

| VREG2    | 20, 27, 33, 43        | PO                  |           |                                                                                                                                                                                                                                                                      |

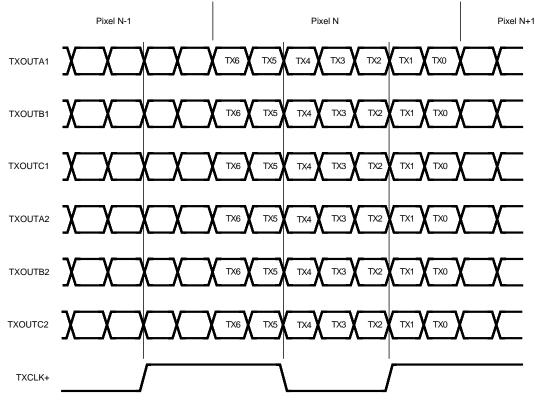

| TXCLK1   | 21, 22                | DO                  |           | Differential LVDS Output Clock 1                                                                                                                                                                                                                                     |

| TXOUTC1  | 23, 24                | DO                  |           | Differential LVDS Output Data C1                                                                                                                                                                                                                                     |

| TXOUTB1  | 25, 26                | DO                  |           | Differential LVDS Output Data B1                                                                                                                                                                                                                                     |

| VSSLVDS  | 28, 34, 41, 42        | PI                  |           | LVDS Power Supply Ground                                                                                                                                                                                                                                             |

| TXOUTA1  | 29, 30                | DO                  |           | Differential LVDS Output Data A1                                                                                                                                                                                                                                     |

| TXCLK2   | 31, 32                | DO                  |           | Differential LVDS Output Clock 2                                                                                                                                                                                                                                     |

| TXOUTC2  | 35, 36                | DO                  |           | Differential LVDS Output Data C2                                                                                                                                                                                                                                     |

| TXOUTB2  | 37, 38                | DO                  |           | Differential LVDS Output Data B2                                                                                                                                                                                                                                     |

| TXOUTA2  | 39, 40                | DO                  |           | Differential LVDS Output Data A2                                                                                                                                                                                                                                     |

| VDDLVDS  | 44, 45                | PI                  |           | LVDS Power Supply                                                                                                                                                                                                                                                    |

| TESTO_1  | 47                    | DO                  |           | Digital Test Output                                                                                                                                                                                                                                                  |

| TESTO_0  | 48                    | DO                  |           | Digital Test Output                                                                                                                                                                                                                                                  |

| RESETB   | 49                    | DI                  | PU 108 kΩ | Master Reset Input(Active Low)                                                                                                                                                                                                                                       |

| SCLK     | 50                    | DI                  |           | Serial Clock for the 4-wire Serial Interface                                                                                                                                                                                                                         |

| SDI      | 51                    | DI                  |           | Serial Data for the 4-wire Serial Interface                                                                                                                                                                                                                          |

| SENB     | 52                    | DI                  | PU 108 kΩ | Serial Enable (Active Low) for the 4-wire Serial Interface                                                                                                                                                                                                           |

| SDO      | 53                    | DO                  |           | Serial Output Data for the 4-wire Serial Interface                                                                                                                                                                                                                   |

| VSSA     | 56, 65, 69, 73,<br>77 | PI                  |           | Analog Power Supply Ground                                                                                                                                                                                                                                           |

| VREF     | 57                    | AO                  |           | Reference Voltage Bypass – Approx. 1.2 V output <sup>(2)</sup>                                                                                                                                                                                                       |

| VDDA     | 58, 67, 71, 75        | PI                  |           | Analog Power Supply                                                                                                                                                                                                                                                  |

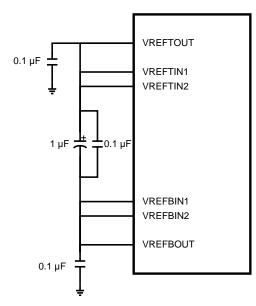

| VREFTOUT | 59                    | AO                  |           | Top Reference Bypass. Connect to bypass capacitors (see <i>Applications and Implementation</i> ) and VREFTINx. – Approx. 2.23 V output. <sup>(2)</sup>                                                                                                               |

(1) KEY: A – Analog, D – Digital, P – Power, I – Input, O – Output, PD – Pull-down resistor to VSSD. PU – Pull-up resistor to VDDD.

(2) Voltages provided for debugging only. Not a guaranteed specification.

## **Pin Functions (continued)**

| P          | IN     | TYPE <sup>(1)</sup> | PULLUP   | DESCRIPTION                                                                                                                                                     |  |

|------------|--------|---------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NUMBER | ITPE                | PULLDOWN | DESCRIPTION                                                                                                                                                     |  |

| VREFBOUT   | 60     | AO                  |          | Bottom Reference Bypass. Connect to bypass capacitors (see<br><i>Applications and Implementation</i> ) and VREFBINx. – Approx. 0.98 V<br>output. <sup>(3)</sup> |  |

| VREFBIN2   | 61     | AI                  |          | Bottom Reference Input Voltage for the ADC. Connect to VREFBOUT.                                                                                                |  |

| VREFTIN2   | 62     | AI                  |          | Top Reference Input Voltage for the ADC. Connect to VREFTOUT.                                                                                                   |  |

| VREFBIN1   | 63     | AI                  |          | Bottom Reference Input Voltage for the AFE. Connect to VREFBOUT.                                                                                                |  |

| VREFTIN1   | 64     | AI                  |          | Top Reference Input Voltage for the AFE. Connect to VREFTOUT.                                                                                                   |  |

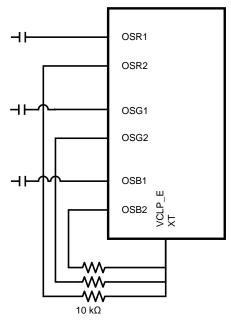

| OSR1       | 66     | AI                  |          | Input Voltage 1 for the Red Channel                                                                                                                             |  |

| OSR2       | 68     | AI                  |          | Input Voltage 2 for the Red Channel                                                                                                                             |  |

| OSG1       | 70     | AI                  |          | Input Voltage 1 for the Green Channel                                                                                                                           |  |

| OSG2       | 72     | AI                  |          | Input Voltage 2 for the Green Channel                                                                                                                           |  |

| OSB1       | 74     | AI                  |          | Input Voltage 1 for the Blue Channel                                                                                                                            |  |

| OSB2       | 76     | AI                  |          | Input Voltage 2 for the Blue Channel                                                                                                                            |  |

| VCLP_EXT   | 78     | AI                  |          | External Clamp Voltage (Connect to VCLP_INT or customer supplied reference voltage                                                                              |  |

| VCLP_INT   | 79     | AO                  |          | Internally Generated V-Clamp Voltage. Connect to bypass capacitors and VCLK_EXT. – Approx. 1.65 V output <sup>(3)</sup>                                         |  |

| SHP/SAMPLE | 80     | DI                  |          | Pedestal Clamp Pulse/Sample Input.                                                                                                                              |  |

(3) Voltages provided for debugging only. Not a guaranteed specification.

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)

|                                                    | MIN                   | MAX                    | UNIT |

|----------------------------------------------------|-----------------------|------------------------|------|

| Supply Voltage                                     | -0.3                  | 4.2                    | V    |

| Voltage at any Pin (except VREG1, VREG2)           | -0.3                  | VDDA + 0.3             | V    |

| Voltage at VREG1, VREG2                            | -0.3                  | 2.1                    | V    |

| Continuous Input Current at any Pin <sup>(2)</sup> |                       | ±25                    | mA   |

| Continuous Input Package Current <sup>(2)</sup>    |                       | ±50                    | mA   |

| Maximum Junction Temperature (Powered)             | T <sub>J_ABS_MA</sub> | <sub>X</sub> = +135    | °C   |

| Specified Ambient Temperature Range                | 0 ≤ T A               | ≤ +70                  | °C   |

| Maximum Junction Temperature                       | T <sub>J_OP_MA</sub>  | <sub>&lt;</sub> = +110 | °C   |

(1) Absolute maximum ratings are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the device should be operated at these limits.

(2) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < (GND - 0.3 V) or V<sub>IN</sub> > (V<sub>DDA</sub> + 0.3 V)), the DC current at that pin should be limited to ±25 mA. The 50 mA DC maximum package input current means that a maximum of two pins can simultaneously have input currents that equal 25 mA.

# 6.2 Handling Ratings

|                                      |                         |                                                                                   | MIN | MAX  | UNIT |

|--------------------------------------|-------------------------|-----------------------------------------------------------------------------------|-----|------|------|

| T <sub>stg</sub>                     | Storage temperature ran |                                                                                   |     | 150  | °C   |

|                                      |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins $^{\rm (3)}$         |     | 2500 |      |

| V <sub>(ESD)</sub> <sup>(1)(2)</sup> | Electrostatic discharge | Machine Model (MM)                                                                |     | 250  | V    |

|                                      |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all $pins^{(4)}$ |     | 1000 |      |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

(2) Human body model, 100 pF discharged through a 1.5 kΩ resistor. Machine model, 200 pF discharged directly into each pin. Charged device model (CDM) simulates a pin slowly acquiring charge (such as from a device sliding down the feeder in an automated assembler) then rapidly being discharged.

(a) Higher 7500V human body model rating and 750V machine model rating for the following pins: SHP, SHD, CLPIN, BLKCLP, AGC\_ONB, OVPB, MCLK, RESETB, SENB, SCLK, SDI, SDO, TXCLK1, TXCLK2, TXOUTA1, TXOUTB1, TXOUTC1, TXOUTA2, TXOUTB2, TXOUTC2.

(3) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(4) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                                                      | MIN  | NOM MAX                        | UNIT |

|------------------------------------------------------|------|--------------------------------|------|

| Analog Supply Voltage Range                          | +3.0 | +3.6                           | V    |

| Digital Supply Voltage Range                         | +3.0 | +3.6                           | V    |

| LVDS Supply Voltage Range                            | +3.0 | +3.6                           | V    |

| DC Power Supply Voltage Relationships <sup>(1)</sup> |      | VDDD ≥ VDDA,<br>VDDD ≥ VDDLVDS |      |

| Voltage at any Digital I/O pin                       | 0    | VDDD                           | V    |

| Voltage at any Analog Input pin                      | 0    | VDDA                           | V    |

| Voltage at any LVDS I/O pin                          | 0    | VDDLV<br>DS                    | V    |

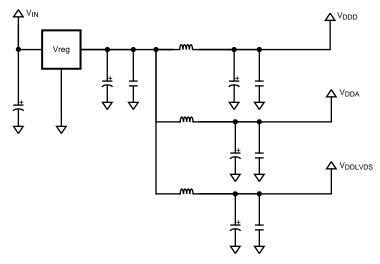

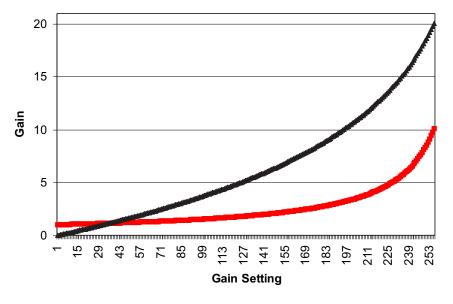

(1) Static voltage levels on VDDD must be at the same voltage or slightly higher than VDDLVDS or VDDA. Therefore, driving all three power supplies from a common linear voltage regulator is recommended. Please see Figure 1.

Figure 1. Recommended Setup

# 6.4 Thermal Information

|                                                         | LM98620VHB |      |

|---------------------------------------------------------|------------|------|

| THERMAL METRIC <sup>(1)</sup>                           | TQFP       | UNIT |

|                                                         | 80 PINS    |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance | 32         | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

Over operating free-air temperature range (unless otherwise noted).

The following specifications apply for VDDA = VDDD = VDDLVDS = 3.3 V;  $F_{MCLK} = F_{ADCCLK} = 70$  Ms/s; 6 Channel Mode unless otherwise noted.

|                    |                                                      | TEST CONDITIONS                                                                                                 | $T_A = T_{MIN}$ to $T_{MAX}$ |     | TA   | = +25°C | ;                   | UNIT |        |

|--------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------|-----|------|---------|---------------------|------|--------|

|                    | PARAMETER                                            | TEST CONDITIONS                                                                                                 | MIN                          | TYP | MAX  | MIN     | TYP                 | MAX  | UNIT   |

| ADC/AFE            |                                                      |                                                                                                                 |                              |     |      |         |                     |      |        |

|                    | Resolution                                           | No missing codes                                                                                                |                              |     | 10   |         |                     |      | bits   |

| INL                | Integral Neg Lincovity                               | Gain = 1x                                                                                                       | -1.5%                        |     | 1.8% |         | -0.6%<br>to<br>0.8% |      |        |

| INL                | Integral Non-Linearity                               | Gain = 6x                                                                                                       |                              |     |      |         | -1.4%<br>to<br>1.4% |      |        |

| DNL                | Differential Nen Linearity                           | Gain = 1x                                                                                                       | -0.99                        |     | 1.6  |         | -0.4 to<br>0.4      |      | lsb    |

|                    | Differential Non-Linearity                           | Gain = 6x                                                                                                       |                              |     |      |         | -0.6 to<br>0.7      |      | 150    |

| SNR                | Signal-to-Noise Ratio <sup>(1)</sup>                 | Gain = 1x                                                                                                       |                              |     |      |         | 68.5                |      | dB     |

| ONIX               |                                                      | Gain = 6x                                                                                                       |                              |     |      |         | 58.5                |      | uВ     |

|                    |                                                      | Negative Polarity:                                                                                              |                              |     |      |         |                     |      |        |

|                    | Analog Input Range (OSx<br>Inputs)                   | • Peak-to-peak, CDS gain = 1x                                                                                   | 1.12                         |     | 1.28 |         | 1.2                 |      | V      |

|                    |                                                      | • Peak-to-peak, CDS gain = 2.1x                                                                                 | 0.54                         |     | 0.62 |         | 0.58                |      |        |

|                    |                                                      | Positive Polarity:                                                                                              |                              |     |      |         |                     |      |        |

|                    |                                                      | • Peak-to-peak, CDS gain = 1x                                                                                   |                              |     |      |         | 1.2                 |      | V      |

|                    | Analog Input Leakage<br>(Osx inputs)                 | GND < Vin < VDDA<br>Source Follower Enabled – OVP<br>off                                                        | -250                         |     | 200  |         | ±25                 |      | nA     |

| R <sub>CLAMP</sub> | Input Clamp Impedance                                | (See <sup>(2)</sup> )                                                                                           |                              |     |      |         | 43                  |      | Ω      |

|                    | Conversion Ratio                                     | CDS/SH Gain Setting = 1x<br>PGA gain setting = Min                                                              | 0.79                         |     | 0.91 |         | 0.85                |      | lsb/mV |

|                    | Conversion Ratio Color to Color <sup>(3)</sup> Error |                                                                                                                 |                              |     |      |         | 0.24%               |      |        |

|                    | Conversion Ratio Ch1 to<br>Ch2 Error                 |                                                                                                                 |                              |     |      |         | 0.13%               |      |        |

|                    | Crosstalk – Color to Color                           | R1,B1 to G1; R1,G1 to B1, and<br>so forth. R2, B2, to G2; R2, G2,<br>to B2, and so forth.<br>Gain = 20x setting |                              |     |      |         | 0.07%               |      |        |

|                    | Crosstalk – Ch1 to Ch1                               | R1 to R2, R2 to R1, G1 to G2, G2 to G1, B1 to B2, B2 to B1 Gain = $20x$ setting                                 |                              |     |      |         | 0.2%                |      |        |

(1) SNR = 20log(1024/Output Noise(lsb rms)) with input = DC.

(2) This parameter specified by simulation and/or bench evaluation and not production tested.

(3) For conversion ratio min/max, variation and error, Conversion ratio is: (Digital Max – Digital Min)/(Vin Max – Vin Min). Measured at gain setting of 1x

SNAS426C-FEBRUARY 2008-REVISED MAY 2014

www.ti.com

### **Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted).

The following specifications apply for VDDA = VDDD = VDDLVDS = 3.3 V;  $F_{MCLK} = F_{ADCCLK} = 70$  Ms/s; 6 Channel Mode unless otherwise noted.

|                 | PARAMETER                               | TEST CONDITIONS                                                           | $T_A = T$ | MIN to T <sub>MAX</sub> | T <sub>A</sub> = +25° | UNIT |             |

|-----------------|-----------------------------------------|---------------------------------------------------------------------------|-----------|-------------------------|-----------------------|------|-------------|

|                 | PARAMETER                               | TEST CONDITIONS                                                           | MIN       | TYP MAX                 | MIN TYP               | MAX  | UNIT        |

|                 |                                         | Active Mode:                                                              |           |                         |                       |      |             |

|                 |                                         | Total Power                                                               |           | 1119                    | 1020                  |      | mW          |

|                 | Power Consumption                       | • IDDA                                                                    |           | 240                     |                       |      | mA          |

|                 |                                         | • IDDD                                                                    |           | 58                      |                       |      | mA          |

|                 |                                         | • IDDLVDS                                                                 |           | 41                      |                       |      | mA          |

|                 |                                         | Power-Down Mode:                                                          |           |                         |                       |      |             |

|                 | Power Consumption                       | MCLK Active                                                               |           | 191                     | 159                   |      | mW          |

|                 |                                         | MCLK Stopped                                                              |           | 47                      | 23                    |      | mW          |

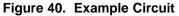

| PGA (8 bit      | ts) Gain = 283/(283-M)                  |                                                                           |           |                         |                       |      |             |

|                 | PGA Gain Range <sup>(4)</sup>           | Gain at max setting/<br>Gain at min setting                               | 19.5      | 20.9                    | 20                    |      | dB          |

|                 | PGA Stepsize                            |                                                                           |           |                         | 0.3                   |      | dB          |

|                 | PGA Monotonicity                        |                                                                           |           | Mono-<br>tonic          |                       |      |             |

|                 | PGA Error (Difference from ideal curve) |                                                                           |           |                         | <0.6%                 |      |             |

| CDS/SH          |                                         |                                                                           |           |                         |                       |      |             |

|                 |                                         |                                                                           |           |                         | 6.4                   |      | dB          |

|                 | CDS/SH Gain                             | Gain at 2.1x / Gain at 1x                                                 | 2         | 2.13                    | 2.1                   |      | V/V         |

| Offset FD       | AC (±10 bits)                           |                                                                           |           |                         |                       |      |             |

|                 | DAC Full Scale (input referred)         | Large FDAC range                                                          | 103       | 120                     | 111                   |      | ±mV         |

|                 |                                         | Small FDAC range                                                          | 54        | 66                      | 59.5                  |      |             |

|                 | DAC Monotonicity                        |                                                                           |           | Mono-<br>tonic          |                       |      |             |

| Offset CD       | AC (± 4 bits)                           |                                                                           |           |                         |                       |      |             |

|                 | DAC Full Scale (input referred)         |                                                                           | 259       | 302                     | 281                   |      | ±mV         |

|                 | DAC Monotonicity                        |                                                                           |           | Mono-<br>tonic          |                       |      |             |

| BLACK C         | ALIBRATION LOOP                         |                                                                           |           |                         |                       |      |             |

|                 | Target Output Level                     |                                                                           |           | 127                     | 0                     |      | lsb         |

| WHITE CA        | LIBRATION LOOP                          |                                                                           |           |                         |                       |      |             |

|                 | Target Output Level                     |                                                                           | 512       | 1023                    |                       |      | lsb         |

|                 | Window Size                             |                                                                           |           | 2,4,8,<br>16,32         |                       |      | #<br>Pixels |

| LOGIC I/O       | DC PARAMETERS                           | · · · · · ·                                                               |           |                         |                       |      |             |

| V <sub>IH</sub> | Logic Input High Threshold              | SHP, SHD, CLPIN, BLKCLP,<br>AGC_ONB, OVPB, MCLK, GPIn,<br>SCLK, SDI, SENB | 2.0       |                         |                       |      | V           |

| V <sub>IL</sub> | Logic Input Low Threshold               | SHP, SHD, CLPIN, BLKCLP,<br>AGC_ONB, OVPB, MCLK, GPIn,<br>SCLK, SDI, SENB |           | 0.8                     |                       |      | V           |

| I <sub>IN</sub> | Logic Input Leakage                     |                                                                           | -100      | 100                     | ±25                   |      | nA          |

|                 | Logio Quinut Valtere L'et               | VDDD = 3.6 V, lout = -0.5 mA                                              | 3.3       |                         | 3.5                   |      |             |

| V <sub>OH</sub> | Logic Output Voltage High               | VDDD = 3.0 V, lout = -0.5 mA                                              | 2.7       |                         | 2.9                   |      | V           |

(4) PGA gain range is: [(ADC\_OUT(PGA @ 111111111)) / (ADC\_OUT(PGA @ 000000000))]

### **Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted).

The following specifications apply for VDDA = VDDD = VDDLVDS = 3.3 V;  $F_{MCLK} = F_{ADCCLK} = 70$  Ms/s; 6 Channel Mode unless otherwise noted.

|                  | DADAMETED                         | TEST CONDITIONS             | T <sub>A</sub> = T | <sub>MIN</sub> to T <sub>I</sub> | MAX  | T <sub>A</sub> | = +25°C | ;   |      |

|------------------|-----------------------------------|-----------------------------|--------------------|----------------------------------|------|----------------|---------|-----|------|

|                  | PARAMETER                         | TEST CONDITIONS             |                    | TYP                              | MAX  | MIN            | TYP     | MAX | UNIT |

| V                | Lagia Output Valtaga Law          | VDDD = 3.6 V, lout = 1.6 mA |                    |                                  | 0.3  |                | 0.15    |     | V    |

| V <sub>OL</sub>  | Logic Output Voltage Low          | VDDD = 3.0 V, lout = 1.6 mA |                    |                                  | 0.3  |                | 0.15    |     | v    |

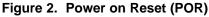

| V <sub>REB</sub> | Power On Reset Threshold          |                             |                    |                                  |      |                | 1.4     |     | V    |

| LVDS DC          | PARAMETERS                        |                             |                    |                                  |      |                |         |     |      |

| V <sub>OD</sub>  | Differential Output Voltage       |                             | 210                |                                  | 420  |                | 300     |     | mV   |

| $\Delta V_{OD}$  | Change in Diff. Output<br>Voltage |                             |                    |                                  | 17   |                | 2.5     |     | mV   |

| V <sub>OS</sub>  | Offset Voltage                    |                             | 1.17               |                                  | 1.28 |                | 1.2     |     | V    |

| $\Delta V_{OS}$  | Change in Offset Voltage          |                             |                    |                                  | 13   |                | 2.5     |     | mV   |

| 1                | Output Short Circuit Current      | TXCLKx                      |                    |                                  | 6.7  |                | 5       |     |      |

| IOS              | Output Short Circuit Current      | TXOUTxx                     |                    |                                  | 8.9  |                | 7       |     | mA   |

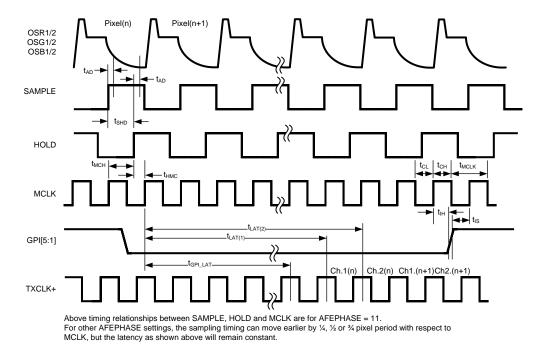

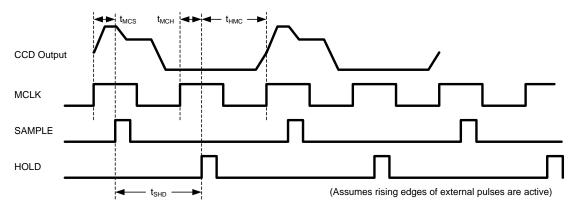

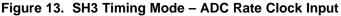

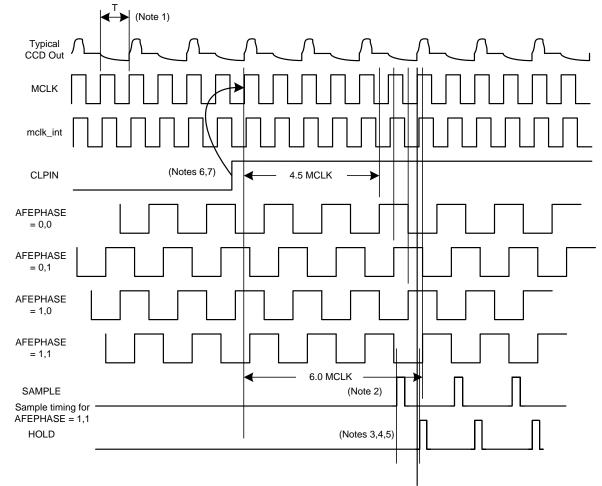

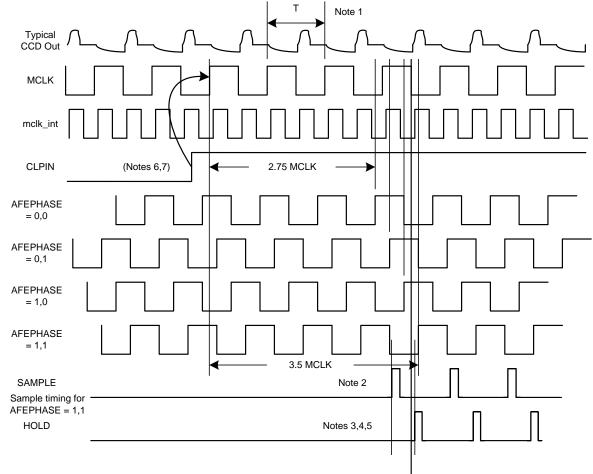

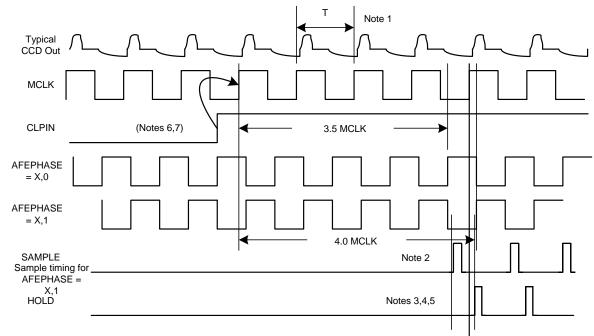

# 6.6 Timing Requirements, AFE/ADC Timing

|                    |                                        | TEST CONDITIONS                             | TA       | = T <sub>MIN</sub> to T <sub>MA</sub> | x   | Τ,  | ( = +25       | °C    |                   |

|--------------------|----------------------------------------|---------------------------------------------|----------|---------------------------------------|-----|-----|---------------|-------|-------------------|

|                    |                                        | TEST CONDITIONS                             | MIN      | TYP N                                 | IAX | MIN | TYP           | MAX   | UNIT              |

| f <sub>MCLK</sub>  | MCLK frequency                         | 6 channel mode                              | 10       |                                       | 70  |     |               |       | MHz               |

|                    |                                        | 3 channel mode                              | 10       |                                       | 35  |     |               |       | IVIEZ             |

| DC                 | MCLK Duty Cycle                        |                                             |          |                                       |     | 40% |               | 60%   |                   |

| S <sub>MAX</sub>   | Input Sampling Rate – maximum          |                                             |          |                                       | 35  |     |               |       | MS/s              |

| S <sub>MIN</sub>   | Input Sampling Rate –                  |                                             | 5        |                                       |     |     |               |       | MS/s              |

|                    | minimum                                |                                             | 10       |                                       |     |     |               |       | 1015/5            |

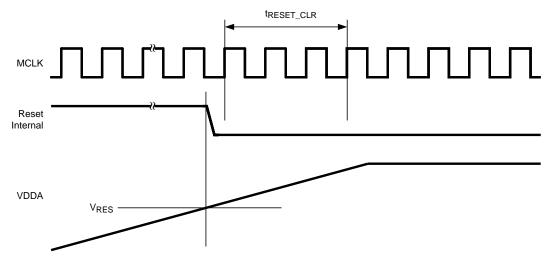

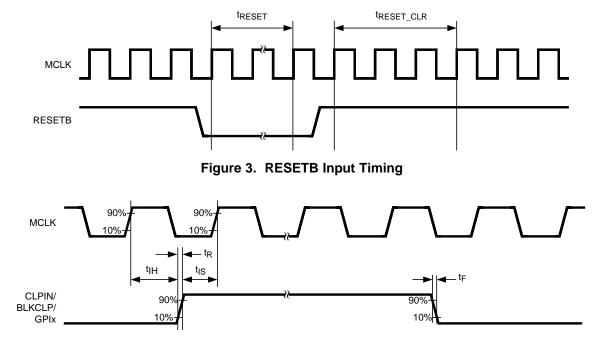

| t <sub>RESET</sub> | RESETB Pulse Width                     |                                             | 2        |                                       |     |     |               |       | t <sub>MCLK</sub> |

| t<br>RESET_CLR     | RESETB Clear Time <sup>(1)</sup>       |                                             |          |                                       | 3   |     |               |       | t <sub>MCLK</sub> |

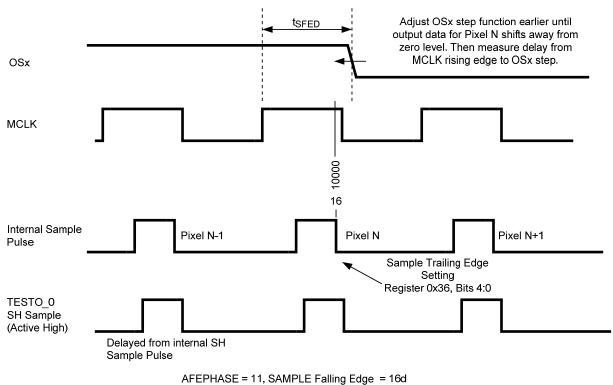

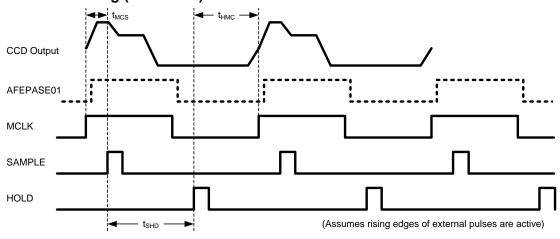

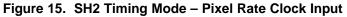

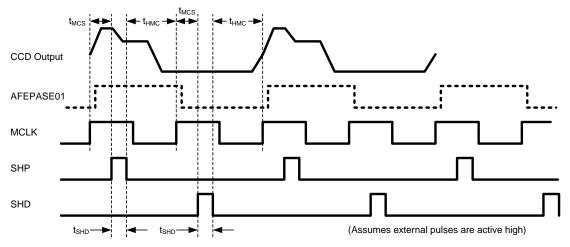

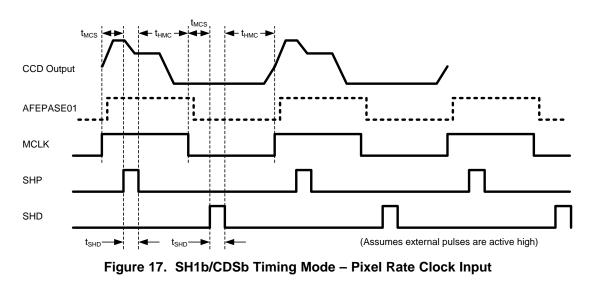

| t <sub>MNS</sub>   | Min Sample Falling Edge                | SH2b (t <sub>SHD</sub> = 8.2 ns), MCLK= ADC | CLK/2):  |                                       |     |     |               |       |                   |

|                    | Setting                                | • ADCCLK = 20 MHz                           |          |                                       | 5   |     | 4             |       | Decimal           |

|                    |                                        | • ADCCLK = 70 MHz                           |          |                                       |     |     | 12            | 14    | Setting           |

| t <sub>MXS</sub>   | Max Sample Falling Edge                | SH2b ( $t_{SHD}$ = 8.2 ns), MCLK = AD       | CCLK/2:  |                                       |     |     |               |       |                   |

|                    | Setting                                | • ADCCLK = 20 MHz                           | 27       |                                       |     |     | 29            |       | Decimal           |

|                    |                                        | • ADCCLK = 70 MHz                           | 23       |                                       |     |     | 25            |       | Setting           |

| t <sub>MXE</sub>   | Sample Falling Edge Max                | SH2b, Register 0x36 = Min to Max            | (MCLK =  | = ADCCLK/2):                          |     |     |               |       |                   |

|                    | Error                                  | • ADCCLK = 20 MHz                           |          |                                       |     |     | +0.2/<br>-0.3 |       | ns                |

|                    |                                        | • ADCCLK = 70 MHz                           |          |                                       |     |     | +0.2/<br>-0.4 |       | ns                |

| t <sub>SFED</sub>  | Sample Falling Edge Delay              | SH2b, Register 0x36 = 16d (MCLk             | K = ADCC | :LK/2):                               |     |     |               |       |                   |

|                    | (MCLK rising edge to OSx voltage step) | ADCCLK = 70 MHz                             |          |                                       |     |     | 13            | 13 ns |                   |

| t <sub>SHD</sub>   | SHP/SHD high period                    | (See <sup>(1)</sup> )                       |          |                                       |     |     | 8.2           |       | ns                |

(1) This parameter specified by simulation and/or bench evaluation and not production tested.

# Timing Requirements, AFE/ADC Timing (continued)

| -                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

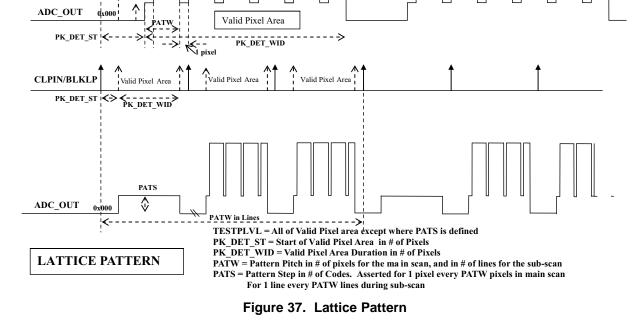

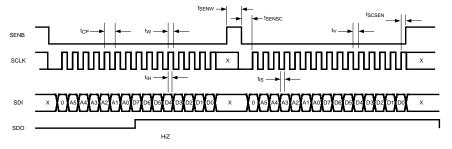

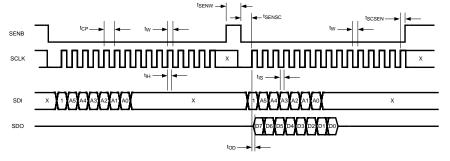

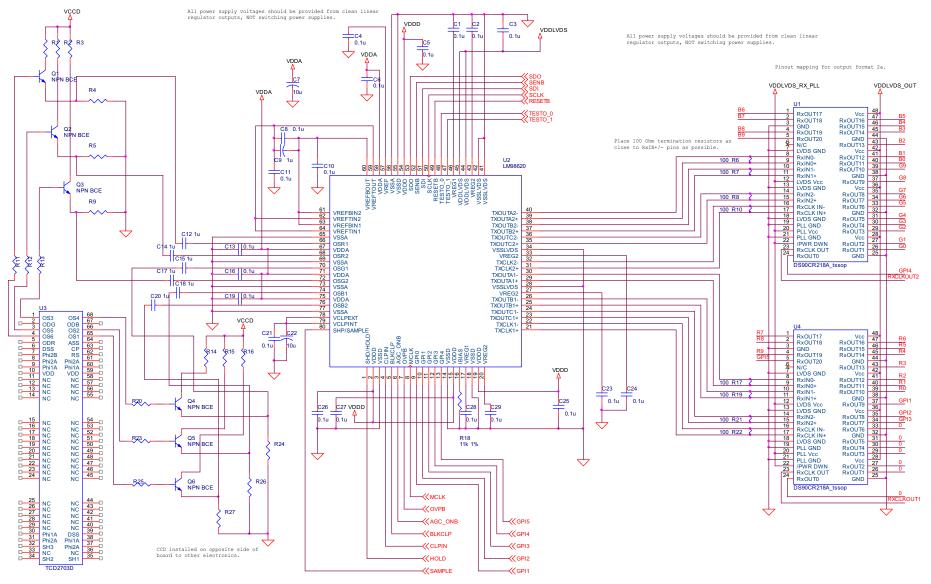

|                                    | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                            | TA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | = T <sub>MIN</sub> te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | o T <sub>MAX</sub>                                                                              | T <sub>A</sub> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | = +25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | °C                                                                                                                                                                                                           | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |