🕳 Sample &

Buy

ZHCSDQ5A - APRIL 2015 - REVISED MAY 2015

# LMH6401 直流至 4.5GHz、全差分数字可变增益放大器

Technical

Documents

## 1 特性

- 3dB 带宽: 4.5GHz(26dB 增益时)

- 增益范围: -6dB 至 26dB(步长为 1dB)

- 差分输入阻抗: 100Ω

- 支持共模控制的差分输出

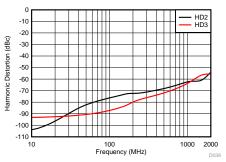

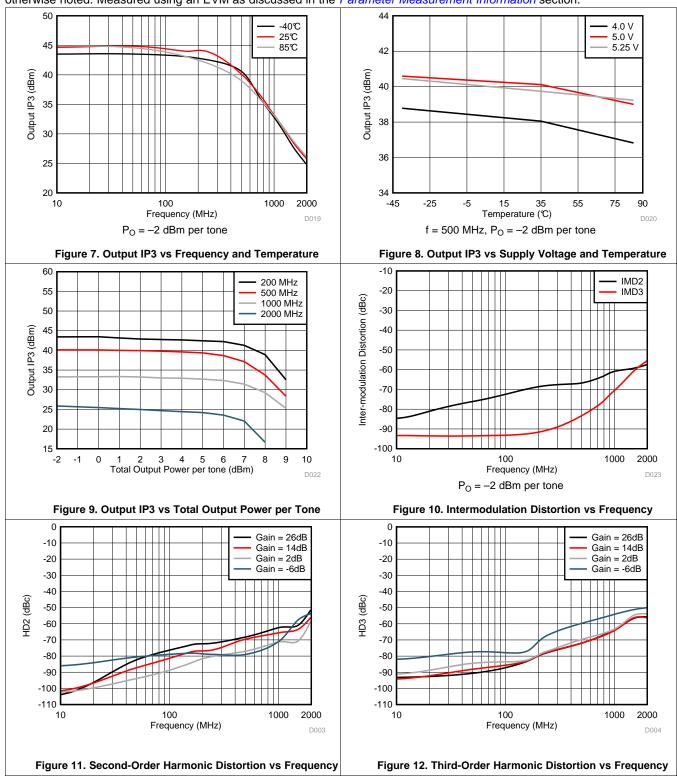

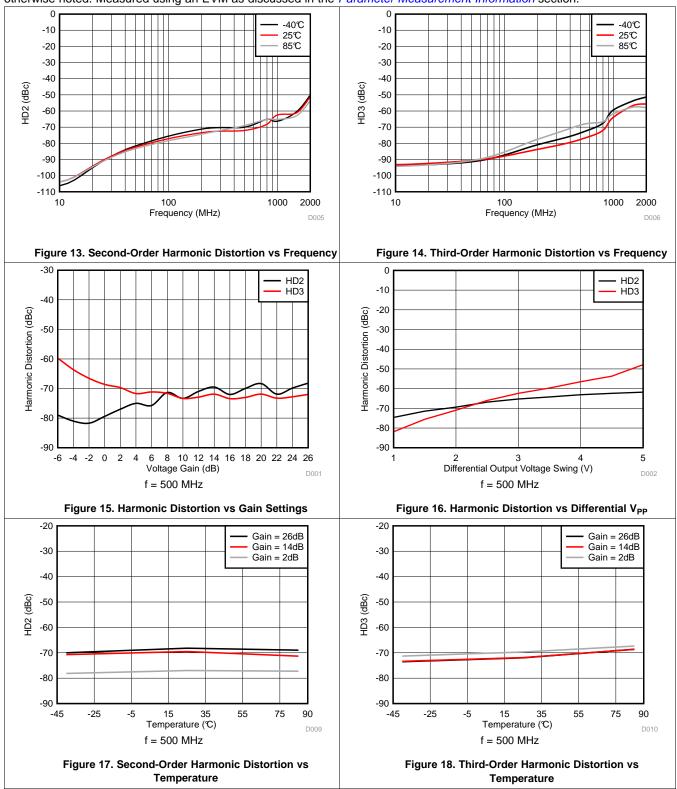

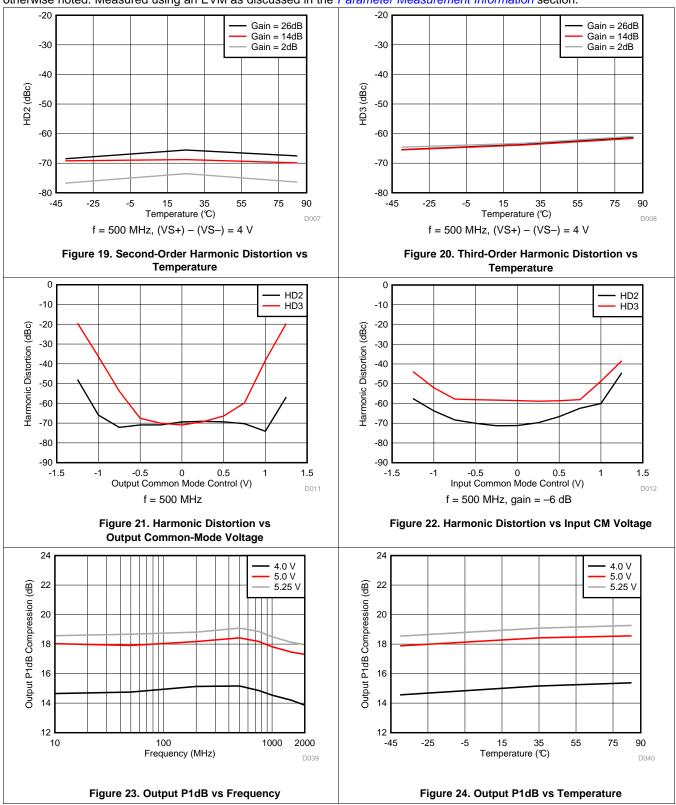

- 最大增益条件下的失真(V<sub>O</sub> = 2 V<sub>PPD</sub>, R<sub>L</sub> = 200Ω):

- 200MHz: HD2 为 -73dBc, HD3 为 -80dBc

- 500 MHz: HD2 为 -68dBc, HD3 为 -72dBc

- 1 GHz: HD2 为 -63dBc, HD3 为 -63dBc

- 2 GHz: HD2 为 -58dBc, HD3 为 -54dBc

- 输出 IP3:

- 200MHz 时为 43dBm

- 1GHz 时为 33dBm

- 2GHz 时为 27dBm

- 输出 IP2:

- 200MHz 时为 67dBm

- 1GHz 时为 60dBm

- 2GHz 时为 52dBm

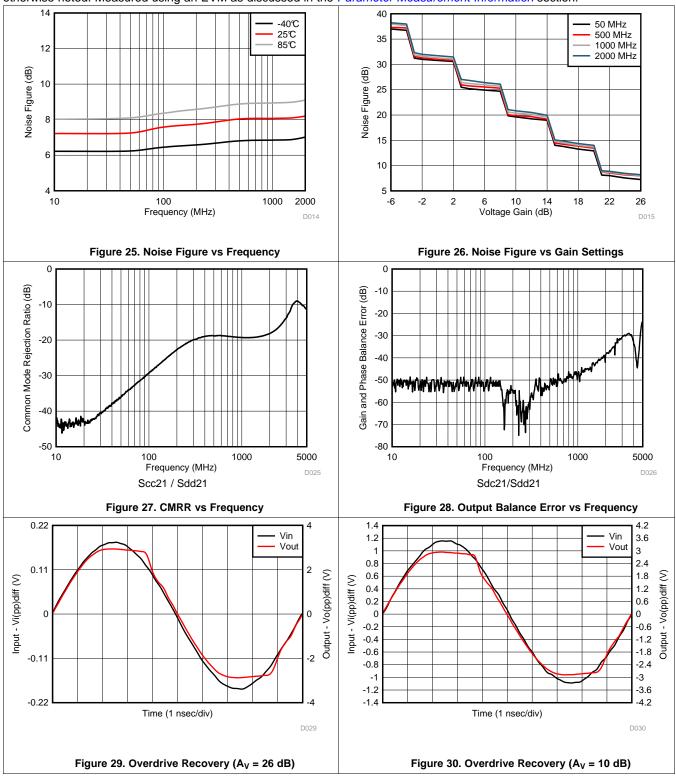

- 1GHz、R<sub>S</sub> = 100Ω 时的噪声系数为 8dB

- 82ps 上升/下降时间脉冲响应

- 供电电源: 5.0V/69mA

- 支持单电源和 (±) 分离电源供电:

直流和交流耦合应用

- 采用先进的互补 BiCMOS 工艺制成

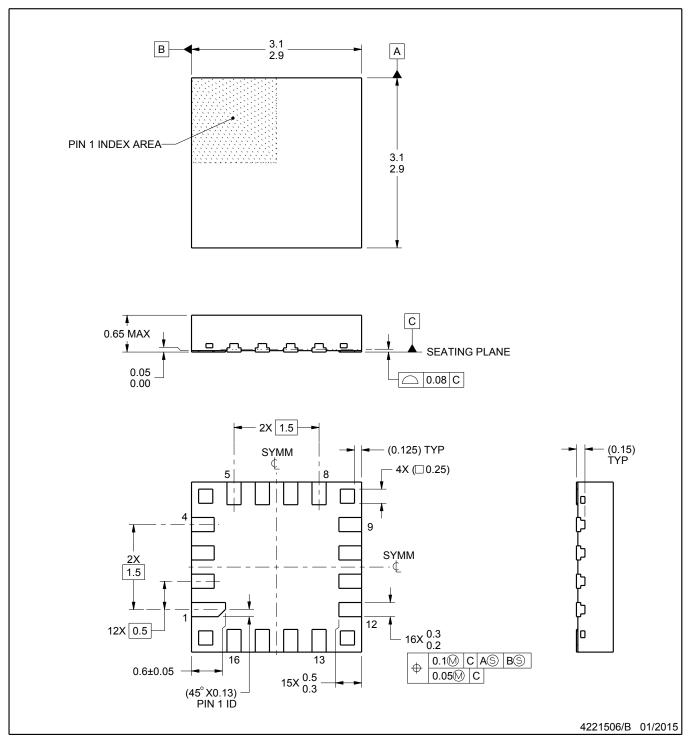

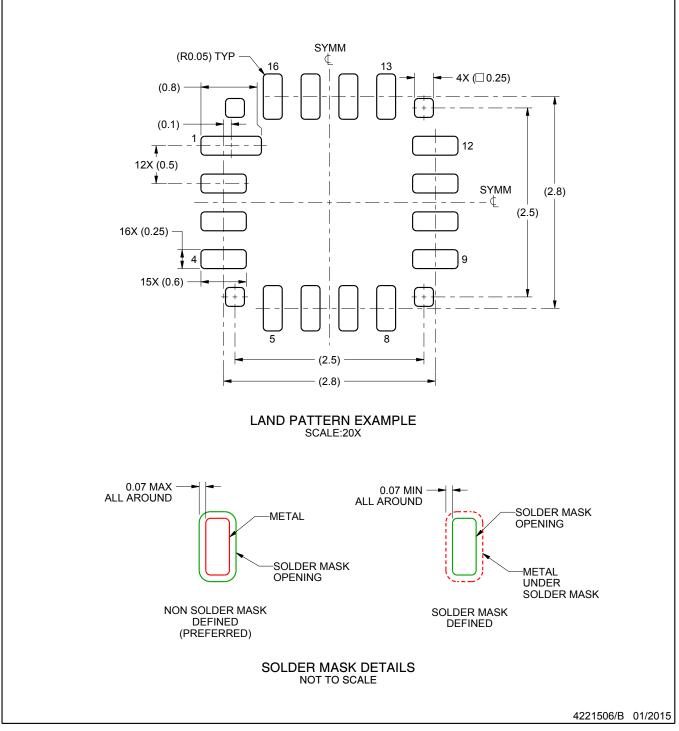

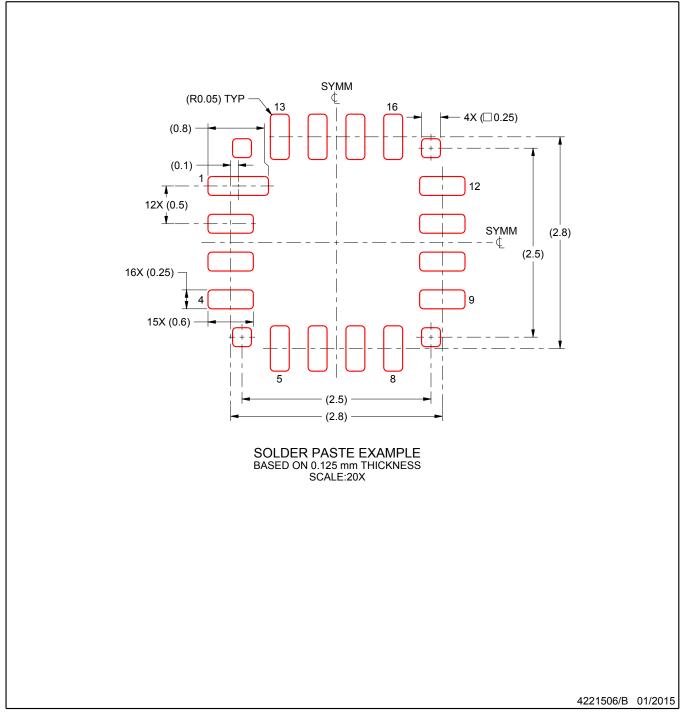

- 3mm × 3mm 超薄四方扁平无引线 (UQFN)-16 封装

## 2 应用

- 测试和测量

- 超宽带模数转换器 (ADC) 驱动器

- 通信接收器

- 射频 (RF) 采样子系统

- 表面声波 (SAW) 滤波缓冲器和驱动器

- 国防设备和雷达

## 3 说明

Tools &

Software

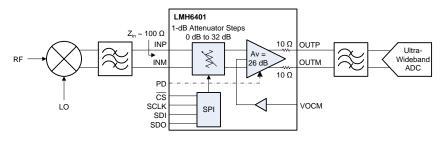

LMH6401 是一款面向直流到射频 (RF)、中频 (IF) 和 高速时域应用的宽带、数控可变增益放大器 (DVGA)。 对于需要自动增益控制 (AGC) 的直流或交流耦合应用 而言,该器件是一款理想的 ADC 驱动器。

Support &

Community

20

该器件对噪声和失真性能进行了优化,以便驱动超宽带 ADC。 放大器在最大增益条件下的噪声系数为 8dB, 在 1GHz 满量程信号电平条件下的谐波失真为 -63dBc。 该器件支持单电源和分离电源供电,以驱动 ADC。 该器件提供了共模参考输入引脚,以便使放大 器输出共模符合 ADC 输入要求。

该器件通过 SPI™ 接口执行增益控制,并且支持 32dB 的增益范围(-6dB 至 26dB,步长为 1dB)。此外,还可以通过外部 PD 引脚或串行外设接口 (SPI) 控制提供掉电功能。

这一性能水平在 345mW 的低功耗下才能实现。 器件 工作的环境温度范围为 -40℃ 至 85℃。

器件信息<sup>(1)</sup>

| 器件型号    | 封装        | 封装尺寸(标称值)       |

|---------|-----------|-----------------|

| LMH6401 | UQFN (16) | 3.00mm x 3.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

## 谐波失真与频率间的关系 (Vo = 2 VPPD)

#### IF 采样接收器应用

# 目录

| 1 | 特性   |                                                   |

|---|------|---------------------------------------------------|

| 2 | 应用   |                                                   |

| 3 | 说明   |                                                   |

| 4 | 修订   | 历史记录 2                                            |

| 5 |      | ice Options3                                      |

| 6 | Pin  | Configuration and Functions 4                     |

| 7 | Spe  | cifications5                                      |

|   | 7.1  | Absolute Maximum Ratings 5                        |

|   | 7.2  | ESD Ratings5                                      |

|   | 7.3  | Recommended Operating Conditions 5                |

|   | 7.4  | Thermal Information 5                             |

|   | 7.5  | Electrical Characteristics 6                      |

|   | 7.6  | SPI Timing Requirements 8                         |

|   | 7.7  | Typical Characteristics 9                         |

| 8 | Para | ameter Measurement Information 16                 |

|   | 8.1  | Setup Diagrams 16                                 |

|   | 8.2  | Output Measurement Reference Points 17            |

|   | 8.3  | ATE Testing and DC Measurements 17                |

|   | 8.4  | Frequency Response 17                             |

|   | 8.5  | Distortion 17                                     |

|   | 8.6  | Noise Figure 18                                   |

|   | 8.7  | Pulse Response, Slew Rate, and Overdrive Recovery |

|   |      |                                                   |

|   | 8.8  | Power Down                                        |

|   | 8.9  | VOCM Frequency Response 18                        |

| 9  | Deta | iled Description 19            |

|----|------|--------------------------------|

|    | 9.1  | Overview 19                    |

|    | 9.2  | Functional Block Diagram 19    |

|    | 9.3  | Feature Description 20         |

|    | 9.4  | Device Functional Modes 20     |

|    | 9.5  | Programming 20                 |

|    | 9.6  | Register Maps 23               |

| 10 | Арр  | lication and Implementation 26 |

|    | 10.1 | Application Information 26     |

|    | 10.2 | Typical Application 30         |

|    | 10.3 | Do's and Don'ts 35             |

| 11 | Pow  | ver-Supply Recommendations     |

|    | 11.1 | Single-Supply Operation 36     |

|    | 11.2 | Split-Supply Operation 36      |

| 12 | Lay  | out                            |

|    | 12.1 | Layout Guidelines              |

|    | 12.2 | Layout Examples                |

| 13 | 器件   | 和文档支持 39                       |

|    | 13.1 | 文档支持 39                        |

|    | 13.2 | 社区资源                           |

|    | 13.3 | 商标                             |

|    | 13.4 | 静电放电警告 39                      |

|    | 13.5 | 术语表 39                         |

| 14 | 机械   | 、封装和可订购信息4C                    |

|    |      |                                |

# 4 修订历史记录

## Changes from Original (April 2015) to Revision A

| • | 布为量产数据 | . 1 |

|---|--------|-----|

|---|--------|-----|

www.ti.com.cn

Page

# 5 Device Options

| DEVICE  | BW (A <sub>V</sub> = 12 dB) | DISTORTION                          | NOISE                   |  |  |

|---------|-----------------------------|-------------------------------------|-------------------------|--|--|

| LMH5401 | 6.2 GHz                     | –75-dBc HD2, –75-dBc HD3 at 500 MHz | 1.25 nV/√ <del>Hz</del> |  |  |

| LMH3401 | 7 GHz, G = 16 dB            | –79-dBc HD2, –77-dBc HD3 at 500 MHz | 1.4 nV/√Hz              |  |  |

| LMH6554 | 1.6 GHz                     | –79-dBc HD2, –70-dBc HD3 at 250 MHz | 0.9 nV/√Hz              |  |  |

## Table 1. FDA Device Companion

## Table 2. DVGA Device Comparison

| DEVICE  | MAX GAIN, BW   | DISTORTION                                     | NOISE FIGURE |

|---------|----------------|------------------------------------------------|--------------|

| LMH6517 | 22 dB, 1.2 GHz | 43-dBm OIP3 at 200 MHz, -74-dBc HD3 at 200 MHz | 5.5 dB       |

| LMH6521 | 26 dB, 1.2 GHz | 49-dBm OIP3 at 200 MHz, -84-dBc HD3 at 200 MHz | 7.3 dB       |

| LMH6881 | 26 dB, 2.4 GHz | 42-dBm OIP3 at 200 MHz, -76-dBc HD3 at 200 MHz | 9.7 dB       |

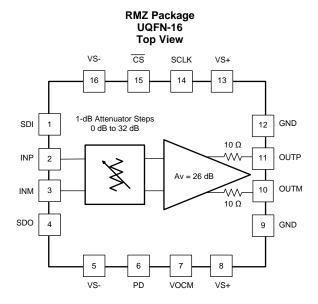

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN |      | FUNCTION | DESCRIPTION                                                   |  |  |

|-----|------|----------|---------------------------------------------------------------|--|--|

| NO. | NAME | FUNCTION | DESCRIPTION                                                   |  |  |

| 1   | SDI  | Input    | Serial interface input data                                   |  |  |

| 2   | INP  | Input    | Positive input pin                                            |  |  |

| 3   | INM  | Input    | Negative input pin                                            |  |  |

| 4   | SDO  | Output   | Serial interface output data                                  |  |  |

| 5   | VS-  | Power    | Negative supply voltage                                       |  |  |

| 6   | PD   | Input    | ower-down pin.<br>= amplifier enabled, 1 = amplifier disabled |  |  |

| 7   | VOCM | Input    | Input pin to set amplifier output common-mode voltage         |  |  |

| 8   | VS+  | Power    | Positive supply voltage                                       |  |  |

| 9   | GND  | Power    | Ground                                                        |  |  |

| 10  | OUTM | Output   | Negative output pin                                           |  |  |

| 11  | OUTP | Output   | Positive output pin                                           |  |  |

| 12  | GND  | Power    | Ground                                                        |  |  |

| 13  | VS+  | Power    | Positive supply voltage                                       |  |  |

| 14  | SCLK | Input    | Serial interface clock                                        |  |  |

| 15  | CS   | Input    | Chip select                                                   |  |  |

| 16  | VS-  | Power    | Negative supply voltage                                       |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                  |                                                               | MIN | MAX | UNIT |

|----------------------------------|---------------------------------------------------------------|-----|-----|------|

| Supply voltage                   | V = (VS+) - (VS-)                                             |     | 5.5 | V    |

| Digital input pins               | Digital input pins                                            |     | VS+ | V    |

| Maximum input difference voltage |                                                               |     | 2.1 | V    |

| Maximum input voltage            |                                                               | VS- | VS+ | V    |

|                                  | Maximum junction, T <sub>J</sub>                              |     | 150 | °C   |

| Tomporatura                      | Maximum junction, continuous operation, long-term reliability |     | 125 | °C   |

| Temperature                      | Operating free-air, T <sub>A</sub>                            | -40 | 85  | °C   |

|                                  | Storage, T <sub>stg</sub>                                     | -65 | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                   | MIN | NOM | MAX  | UNIT |

|---------------------------------------------------|-----|-----|------|------|

| Supply voltage                                    | 4.0 | 5.0 | 5.25 | V    |

| Minimum operating positive (VS+) supply voltage   | 2.0 |     |      | V    |

| Ambient operating air temperature, T <sub>A</sub> | -40 | 25  | 85   | °C   |

| Operating junction temperature, T <sub>J</sub>    | -40 |     | 125  | °C   |

## 7.4 Thermal Information

|                       |                                              | LMH6401    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RMZ (UQFN) | UNIT |

|                       |                                              | 16 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 78         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 43         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 24         | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 2.3        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 24         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a        | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

ZHCSDQ5A - APRIL 2015-REVISED MAY 2015

www.ti.com.cn

## 7.5 Electrical Characteristics

At  $T_A = 25^{\circ}$ C, VS- = -2.5 V, VS+ = 2.5 V, VOCM = 0 V,  $R_{LOAD} = 200 \cdot \Omega$  differential ( $R_{o(internal, diff)} = 20 \Omega$ ),  $V_O = 2 V_{PPD}$ , and  $A_V = 26$  dB, unless otherwise noted.

|                                 | PARAMETER                               | TEST COND                                                           | ITIONS             | MIN  | ТҮР   | МАХ  | UNIT   | TEST<br>LEVEL <sup>(1)</sup> |

|---------------------------------|-----------------------------------------|---------------------------------------------------------------------|--------------------|------|-------|------|--------|------------------------------|

| DYNAM                           |                                         |                                                                     |                    |      |       |      |        |                              |

| SSBW                            | Small-signal, –3-dB bandwidth           | $A_V = 26 \text{ dB}, V_O = 200 \text{ mV}_{PPD}$                   |                    |      | 4.5   |      | GHz    | С                            |

| LSBW                            | Large-signal, –3-dB bandwidth           | $A_V = 26 \text{ dB}, V_O = 2.0 \text{ V}_{PP}$                     | PD                 |      | 4.5   |      | GHz    | С                            |

|                                 | Bandwidth for 0.1-dB flatness           | $A_V = 26 \text{ dB}, V_O = 2.0 \text{ V}_{PP}$                     |                    |      | 500   |      | MHz    | С                            |

| SR                              | Slew rate                               | V <sub>O</sub> = 2-V step                                           |                    |      | 18200 |      | V/µs   | С                            |

| t <sub>R</sub> , t <sub>F</sub> | Rise and fall time                      | V <sub>O</sub> = 2-V step, 10% to 90                                | )%                 |      | 82    |      | ps     | С                            |

|                                 | Overdrive recovery                      | Overdrive = $\pm 0.5$ V                                             | · · ·              |      |       |      | ps     | С                            |

|                                 | Output balance error                    | f = 1 GHz                                                           |                    |      | -47   |      | dB     | С                            |

| ts                              | Settling time to 1%                     | $V_0 = 2$ -V step, R <sub>L</sub> = 200 0                           | 2                  |      | 700   |      | ps     | С                            |

|                                 |                                         | f = 200 MHz, V <sub>O</sub> = 2.0 V                                 | PPD                |      | -73   |      | dBc    | С                            |

|                                 |                                         | f = 500 MHz, V <sub>O</sub> = 2.0 V                                 |                    |      | -68   |      | dBc    | С                            |

| HD2                             | Second-harmonic distortion              | f = 1 GHz, V <sub>O</sub> = 2.0 V <sub>PPD</sub>                    |                    |      | -63   |      | dBc    | С                            |

|                                 |                                         | f = 2 GHz, V <sub>O</sub> = 2.0 V <sub>PPD</sub>                    |                    |      | -58   |      | dBc    | С                            |

|                                 |                                         | f = 200 MHz, V <sub>O</sub> = 2.0 V                                 |                    |      | -80   |      | dBc    | С                            |

| I                               |                                         | f = 500 MHz, V <sub>O</sub> = 2.0 V                                 |                    |      | -72   |      | dBc    | С                            |

| HD3                             | Third-harmonic distortion               | f = 1 GHz, V <sub>O</sub> = 2.0 V <sub>PPD</sub>                    | )                  |      | -63   |      | dBc    | С                            |

|                                 |                                         | f = 2 GHz, V <sub>O</sub> = 2.0 V <sub>PPD</sub>                    |                    |      | -54   |      | dBc    | С                            |

|                                 |                                         | f = 200 MHz, P <sub>O</sub> = -2 dB                                 | m per tone         |      | 67    |      | dBm    | С                            |

| OIP2                            | Output second-order intercept point     | f = 500 MHz, $P_0 = -2$ dBm per tone                                |                    |      | 65    |      | dBm    | С                            |

|                                 |                                         | $f = 1 \text{ GHz}, P_0 = -2 \text{ dBm per tone}$                  |                    |      | 60    |      | dBm    | С                            |

|                                 |                                         | $f = 2 \text{ GHz}, P_0 = -2 \text{ dBm per tone}$                  |                    |      | 52    |      | dBm    | С                            |

|                                 |                                         | f = 200 MHz, $P_0 = -2$ dBm per tone                                |                    |      | 43    |      | dBm    | С                            |

| 0.00                            | Output third-order intercept point      | $f = 500 \text{ MHz}, P_0 = -2 \text{ dBm per tone}$                |                    |      | 40    |      | dBm    | С                            |

| OIP3                            |                                         | $f = 1 \text{ GHz}, P_0 = -2 \text{ dBm per tone}$                  |                    |      | 33    |      | dBm    | С                            |

|                                 |                                         | $f = 2 \text{ GHz}, P_0 = -2 \text{ dBm per tone}$                  |                    |      | 27    |      | dBm    | С                            |

| IMD2                            | Second-order intermodulation distortion | f = 500 MHz, V <sub>O</sub> = 1.0 V                                 | PP per tone        |      | -68   |      | dBc    | С                            |

| IMD3                            | Third-order intermodulation distortion  | f = 500 MHz, V <sub>O</sub> = 1.0 V <sub>I</sub>                    | PP per tone        |      | -83   |      | dBc    | С                            |

| P1dB                            | 1-dB compression point                  | f = 500 MHz, power mea<br>output                                    | sured at amplifier |      | 18.3  |      | dBm    | С                            |

| NF                              | Noise figure                            | R <sub>S</sub> = 100 Ω                                              | f = 200 MHz        |      | 7.7   |      | dB     | С                            |

| INI                             | Noise ligure                            | $N_{\rm S} = 100.02$                                                | f = 1 GHz          |      | 8     |      | dB     | С                            |

|                                 | Output-referred noise voltage           | $A_V = 26 \text{ dB}, \text{ f} > 1 \text{ MHz}$                    |                    |      | 30.4  |      | nV/√Hz | С                            |

| S12                             | Reverse transmission (S12)              | f = 1 GHz                                                           |                    |      | -65   |      | dB     | С                            |

| S11                             | Input return loss (S11)                 | 100-Ω system, f = 2 GHz                                             |                    |      | -15   |      | dB     | С                            |

| GAIN PA                         | ARAMETERS                               | ·                                                                   |                    |      |       |      |        |                              |

|                                 | Maximum voltage gain                    |                                                                     |                    | 25.5 | 26.0  | 26.5 | dB     | А                            |

|                                 | Minimum voltage gain                    |                                                                     |                    | -7.5 | -6.0  | -4.5 | dB     | А                            |

|                                 | Gain range                              |                                                                     |                    |      | 32    |      | dB     | С                            |

|                                 | Gain step size                          |                                                                     |                    | 0.9  | 1     | 1.1  | dB     | А                            |

|                                 |                                         | A <sub>V</sub> = 26 dB to 10 dB<br>(referenced to 26-dB gai         | n)                 | -0.5 |       | 0.5  | dB     | А                            |

|                                 | Cumulative gain error                   | $A_V = 26 \text{ dB to } -6 \text{ dB}$<br>(referenced to 26-dB gai | n)                 | -1   |       | 1    | dB     | А                            |

|                                 | Gain step transition time               |                                                                     |                    |      | 1     |      | ns     | С                            |

Test levels: (A) 100% DC tested at 25°C unless otherwise specified. Over-temperature limits by characterization and simulation. (B) Limits set by bench verification and simulation. (C) Typical value only for information.

# **Electrical Characteristics (continued)**

At  $T_A = 25^{\circ}$ C, VS- = -2.5 V, VS+ = 2.5 V, VOCM = 0 V,  $R_{LOAD} = 200 \cdot \Omega$  differential ( $R_{o(internal, diff)} = 20 \Omega$ ),  $V_O = 2 V_{PPD}$ , and  $A_V = 26 \text{ dB}$ , unless otherwise noted.

|                   | PARAMETER                                  | TEST CONDITIONS                        | MIN         | ТҮР         | МАХ         | UNIT             | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------|--------------------------------------------|----------------------------------------|-------------|-------------|-------------|------------------|------------------------------|

| ANALO             | G INPUT CHARACTERISTICS                    |                                        |             |             |             |                  |                              |

| R <sub>i</sub>    | Input resistance                           | Differential                           | 85          | 100         | 112         | Ω                | А                            |

| Ci                | Input capacitance                          | Differential                           |             | 0.8         |             | pF               | С                            |

| VICM              | Input common-mode voltage                  | Self-biased to mid-supply              | -0.3        |             | 0.3         | V                | А                            |

| VICLR             | Low-level input common-mode voltage range  | Differential gain shift < 1 dB         |             | (VS–) + 1.5 |             | V                | С                            |

| V <sub>ICHR</sub> | High-level input common-mode voltage range | Differential gain shift < 1 dB         |             | (VS+) – 1.5 |             | V                | С                            |

| ANALO             | G OUTPUT CHARACTERISTICS                   |                                        |             |             |             |                  |                              |

| R <sub>o</sub>    | Output resistance                          | Differential                           | 18          | 20          | 25          | Ω                | А                            |

| V <sub>OL</sub>   | Low-level output voltage range             | Low-level clipping level               |             | (VS–) + 1   | (VS–) + 1.1 | V                | А                            |

| V <sub>OH</sub>   | High-level output voltage range            | High-level clipping level              | (VS+) – 1.1 | (VS+) – 1   |             | V                | А                            |

| V <sub>OM</sub>   | Maximum output voltage swing               | Differential                           |             | 6.0         |             | V <sub>PPD</sub> | С                            |

| CMRR              | Common-mode rejection ratio                | ±0.3-V input common-mode shift         | 38.4        | 45          |             | dB               | А                            |

| POWER             | R SUPPLY                                   |                                        |             |             |             |                  |                              |

| Vs                | Supply voltage $[V = (VS+) - (VS-)]$       |                                        | 4.0         | 5.0         | 5.25        | V                | А                            |

|                   | Minimum positive (VS+) supply voltage      |                                        | 2.0         |             |             | V                | А                            |

|                   |                                            | VS-, measured at 1-kHz sine-wave       | 66          | 70          |             | dB               | А                            |

| PSRR              | Power-supply rejection ratio               | VS+, measured at 1-kHz sine-wave       | 66          | 70          |             | dB               | А                            |

|                   |                                            | PD = 0 (device enabled)                | 60          | 69          | 78          | mA               | А                            |

| Ι <sub>Q</sub>    | Quiescent current                          | PD = 1 (device disabled)               | 1           | 7           | 12          | mA               | А                            |

| OUTPU             | T COMMON-MODE CONTROL (VOCM                | / Pin)                                 |             |             |             |                  |                              |

| SSBW              | Small-signal bandwidth                     | VOCM = 200 mV <sub>PP</sub>            |             | 160         |             | MHz              | С                            |

|                   | VOCM voltage range low                     | VOCM gain < 2%                         | -0.5        |             |             | V                | А                            |

|                   | VOCM voltage range high                    | VOCM gain < 2%                         |             |             | 0.5         | V                | А                            |

| V <sub>oo</sub>   | Output offset voltage                      | All gain settings                      | -40         |             | 40          | mV               | А                            |

|                   | VOCM gain                                  |                                        |             | 1.0         |             | V                | С                            |

| V <sub>OCM</sub>  | Common-mode offset voltage                 | VOCM pin driven to GND                 | -10         |             | 10          | mV               | А                            |

| POWER             | R DOWN (PD Pin)                            |                                        |             |             | 4           |                  |                              |

|                   | Power-down quiescent current               |                                        | 1           | 7           | 12          | mA               | A                            |

|                   | PD bias current                            | PD = 2.5 V                             |             | 80          | 100         | μA               | А                            |

|                   | Turn-on time delay                         | Time to $V_0 = 90\%$ of final value    |             | 70          |             | ns               | С                            |

|                   | Turn-off time delay                        | Time to $V_0 = 10\%$ of original value |             | 10          |             | ns               | С                            |

| DIGITA            | L INPUT/OUTPUT                             | •                                      | +           |             |             |                  | +                            |

| VIH               | High-level input voltage                   | Referred to GND                        | 1.2         |             | VS+         | V                | А                            |

| V <sub>IL</sub>   | Low-level input voltage                    | Referred to GND                        |             |             | 0.8         | V                | A                            |

| V <sub>OH</sub>   | High-level output voltage                  | 1 kΩ to GND                            | 1.4         |             |             | V                | А                            |

| V <sub>OL</sub>   | Low-level output voltage                   | 1 kΩ to GND                            |             |             | 0.4         | V                | A                            |

#### LMH6401

ZHCSDQ5A-APRIL 2015-REVISED MAY 2015

www.ti.com.cn

# 7.6 SPI Timing Requirements<sup>(1)</sup>

At  $T_A = 25^{\circ}$ C, VS- = -2.5 V, VS+ = 2.5 V, VOCM = 0 V,  $R_{LOAD} = 200 \cdot \Omega$  differential ( $R_{o(internal, diff)} = 20 \Omega$ ),  $V_O = 2 V_{PPD}$ , and  $A_V = 26 \text{ dB}$ , unless otherwise noted. Limits set by bench verification and simulation.

|                  |                                        | MIN | NOM N | IAX | UNIT |

|------------------|----------------------------------------|-----|-------|-----|------|

| f <sub>s_c</sub> | SCLK frequency                         |     |       | 50  | MHz  |

| t <sub>PH</sub>  | SCLK pulse duration, high              | 10  |       |     | ns   |

| t <sub>PL</sub>  | SCLK pulse duration, low               | 10  |       |     | ns   |

| t <sub>SU</sub>  | SDI setup                              | 3   |       |     | ns   |

| t <sub>H</sub>   | SDO hold                               | 3   |       |     | ns   |

| t <sub>IZ</sub>  | SDO tri-state                          |     |       | 3   | ns   |

| t <sub>ODZ</sub> | SDO driven to tri-state <sup>(2)</sup> |     |       | 5   | ns   |

| t <sub>OZD</sub> | SDO tri-state to driven                |     |       | 3   | ns   |

| t <sub>OD</sub>  | SDO output delay <sup>(2)</sup>        |     |       | 3   | ns   |

| t <sub>CSS</sub> | CS setup <sup>(3)</sup>                | 3   |       |     | ns   |

| t <sub>CSH</sub> | CS hold                                | 3   |       |     | ns   |

| t <sub>IAG</sub> | Inter-access gap                       | 20  |       |     | ns   |

Ensured by design.

Reference to negative edge of SCLK.

Reference to positive edge of SCLK.

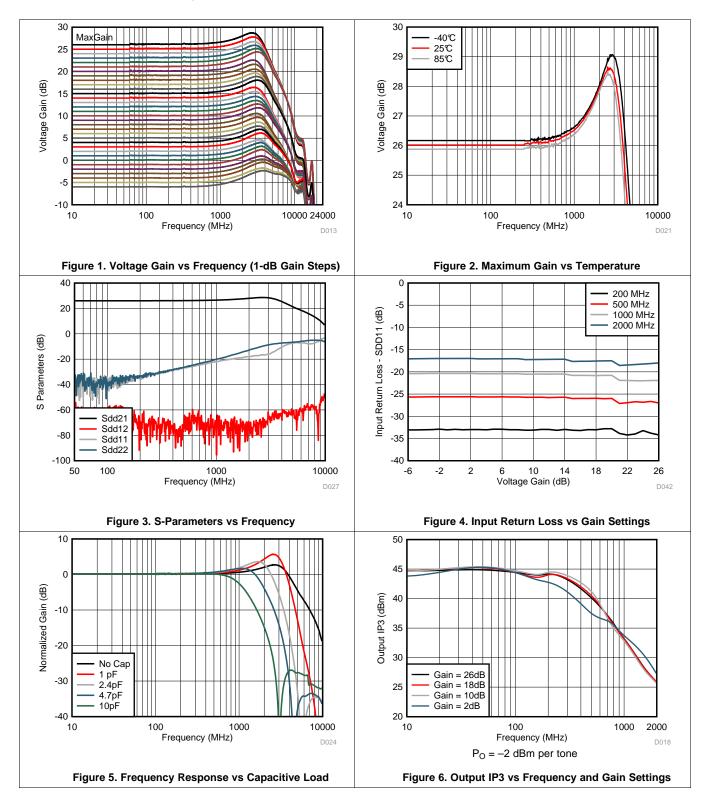

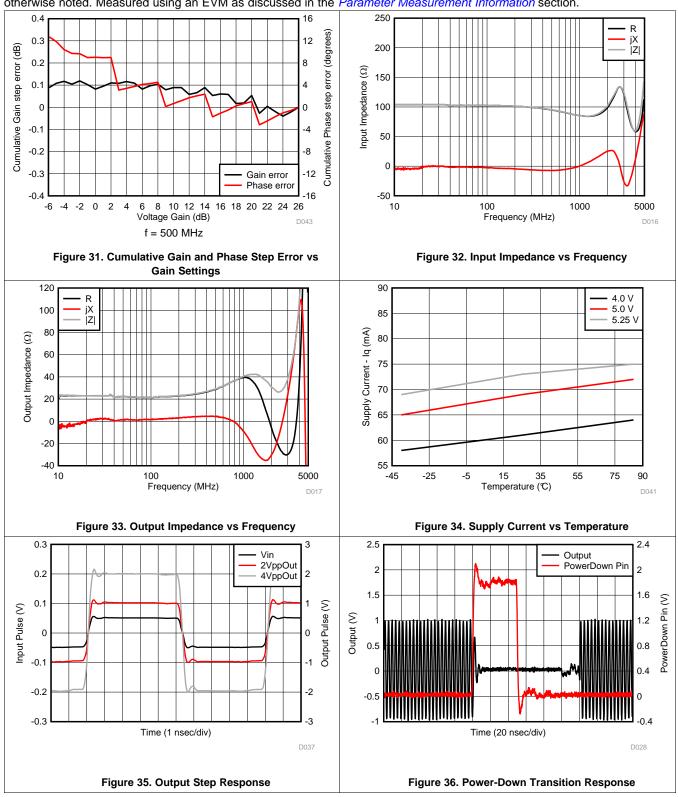

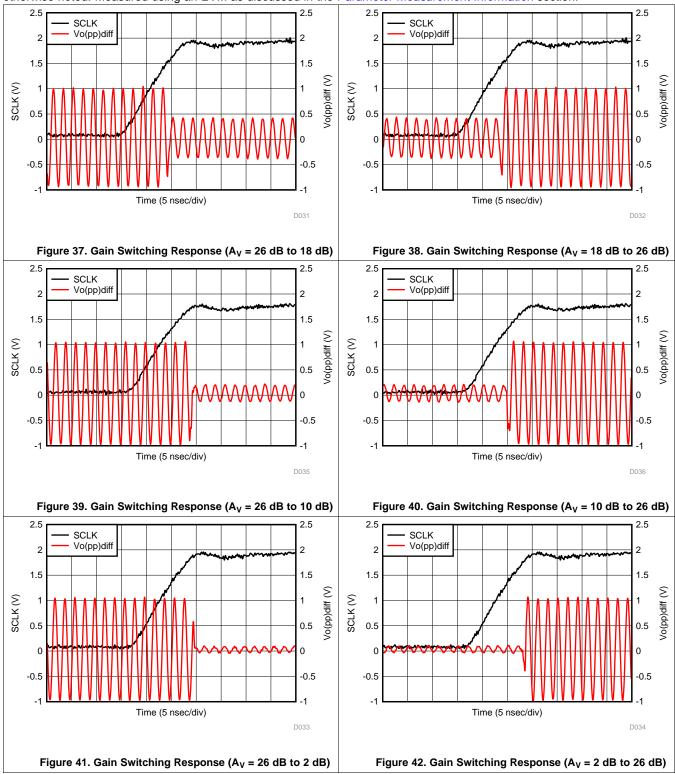

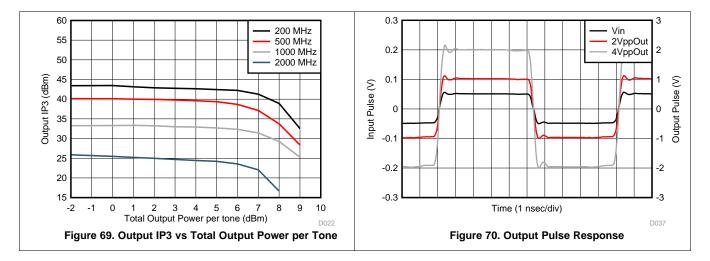

## 7.7 Typical Characteristics

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

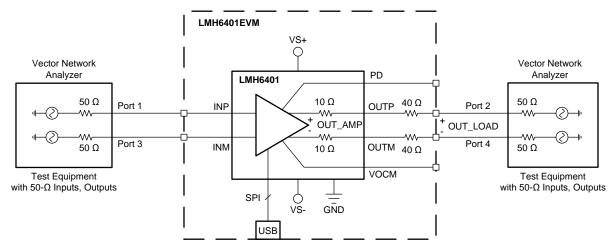

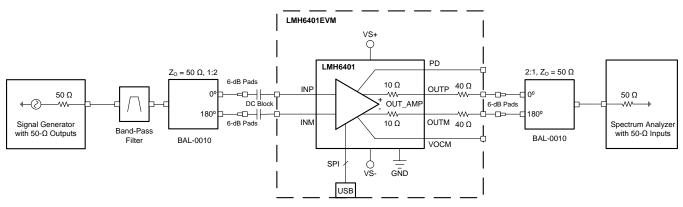

## 8 Parameter Measurement Information

## 8.1 Setup Diagrams

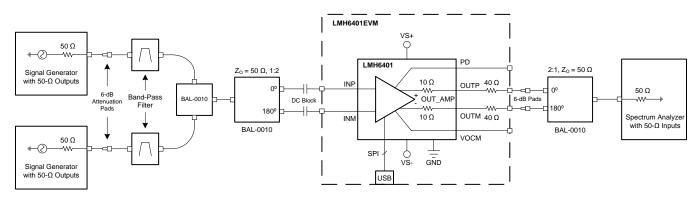

Figure 43. Frequency Response Differential Test Setup

Figure 44. Single-Tone Harmonic Distortion Test Setup

Figure 45. Two-Tone Linearity Test Setup (OIP3, OIP2)

LMH6401 ZHCSDQ5A – APRIL 2015 – REVISED MAY 2015

www.ti.com.cn

## Setup Diagrams (continued)

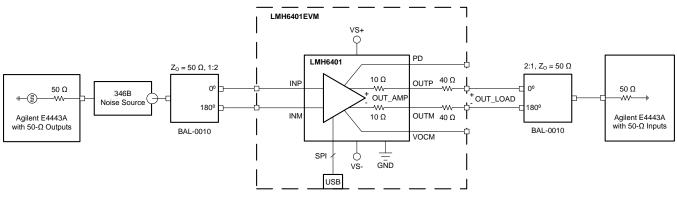

Figure 46. Noise Figure Test Setup

## 8.2 Output Measurement Reference Points

The LMH6401 has two on-chip,  $10-\Omega$  output resistors. When matching the output to a  $100-\Omega$  load, the evaluation module (EVM) uses an external  $40-\Omega$  resistor on each output leg to complete the output matching. Having onchip output resistors creates two potential reference points for measuring the output voltage. The first reference point is at the internal amplifier output (OUT\_AMP), and the second reference point is at the externally-matched  $100-\Omega$  load (OUT\_LOAD). The measurements in the *Electrical Characteristics* table and in the *Typical Characteristics* section are referred to the (OUT\_AMP) reference point unless otherwise specified. The conversion between reference points is a straightforward correction of 3 dB for power and 6 dB for voltage, as shown in Equation 1 and Equation 2. The measurements are referenced to OUT\_AMP when not specified.

VOUT\_LOAD = (VOUT\_AMP - 6 dB) POUT\_LOAD = (POUT\_AMP - 3 dB)

(1) (2)

## 8.3 ATE Testing and DC Measurements

All production testing and dc parameters are measured on automated test equipment capable of dc measurements only. Some measurements (such as voltage gain) are referenced to the output of the internal amplifier and do not include losses attributed to the on-chip output resistors. The *Electrical Characteristics* values specify these conditions. When the measurement is referred to the amplifier output, the output resistors are not included in the measurement. If the measurement is referred to the device pins, then the output resistor loss is included in the measurement.

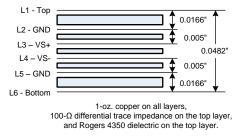

#### 8.4 Frequency Response

This test is done by running an S-parameter sweep on a 4-port differential network analyzer using the standard EVM with no baluns; see Figure 43. The inputs and outputs of the EVM are connected to the network analyzer using  $50-\Omega$  coaxial cables with all the ports set to a characteristic impedance (Z<sub>0</sub>) of  $50 \Omega$ .

The frequency response test with capacitive load is done by soldering the capacitor across the LMH6401 output pins. In this configuration, the on-chip,  $10-\Omega$  resistors on each output leg isolate the capacitive load from the amplifier output pins.

#### 8.5 Distortion

The standard EVM is used for measuring both the single-tone harmonic distortion and two-tone intermodulation distortion; see Figure 44 and Figure 45, respectively. The distortion is measured with differential input signals to the LMH6401. In order to interface with single-ended test equipment, external baluns (1:2,  $Z_0 = 50 \Omega$ ) are required between the EVM output ports and the test equipment. The *Typical Characteristics* plots are created with Marki<sup>TM</sup> baluns, model number BAL-0010. These baluns are used to combine two single tones in the two-tone test plots as well as convert the single-ended input to differential output for harmonic distortion tests. The use of 6-dB attenuator pads on both the inputs and outputs is recommended to provide a balanced match between the external balun and the EVM.

## 8.6 Noise Figure

This test is done by matching the input of the LMH6401 to a 50- $\Omega$  noise source using a 1:2 balun (see Figure 46), with the noise figure being referred to the input impedance (R<sub>S</sub> = 100  $\Omega$ ). As noted in Figure 46, an Agilent E4443A with NF features is used for the testing.

## 8.7 Pulse Response, Slew Rate, and Overdrive Recovery

For time-domain measurements, the standard EVM is driven through a balun again to convert a single-ended output from the test equipment to the differential inputs of the LMH6401. The differential outputs are directly connected to the oscilloscope inputs, with the differential signal response calculated using trace math from the two separate oscilloscope inputs.

## 8.8 Power Down

The standard EVM is used for this test by completely removing the shorting block on jumper JPD. A high-speed,  $50-\Omega$  pulse generator is used to drive the PD pin, which toggles the output signal on or off depending upon the PD pin voltage.

## 8.9 VOCM Frequency Response

The standard EVM is used for this test. A network analyzer is connected to the VOCM input of the EVM and the EVM outputs are connected to the network analyzer with  $50-\Omega$  coaxial cables. The network analyzer analysis mode is set to single-ended input and differential output, and the output common-mode response is measured with respect to the single-ended input (Scs21). The input signal frequency is swept with the signal level set for 100 mV (–16 dBm). Note that the common-mode control circuit gain is approximately one.

## 9 Detailed Description

## 9.1 Overview

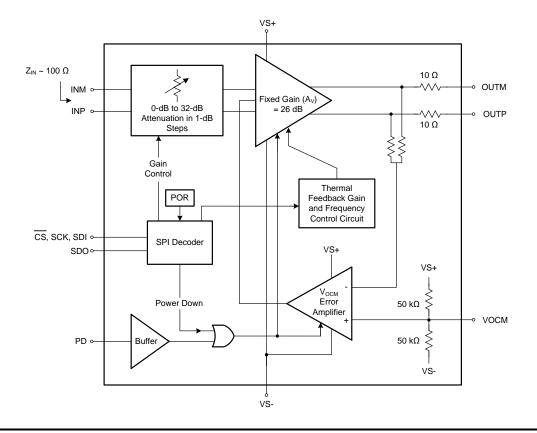

The LMH6401 is a very high-performance, differential I/O, digitally-controlled variable gain amplifier (DVGA). The device is optimized for radio frequency (RF), intermediate frequency (IF), or high-speed time-domain applications with 3-dB bandwidths up to 4.5 GHz. The device is ideal for dc- or ac-coupled applications requiring a variable gain stage when driving an analog-to-digital converter (ADC).

The LMH6401 is best suited to optimize system linearity and noise performance over the entire gain range in the RF and IF bands. Operating on a nominal 5-V supply or ±2.5-V split supplies, the device consists of an attenuator stage followed by a fixed-gain amplifier to provide voltage gain control from –6 dB to 26 dB in 1-dB steps (as shown in the *Functional Block Diagram* section) with an overall 32-dB gain range. The variable gain control for the device is offered through the digital serial peripheral interface (SPI) register. The device has a unique attenuator ladder architecture providing dynamic range improvements where the overall noise figure (NF) remains relatively constant for the first 5-dB attenuator steps, with NF degrading proportional to the attenuator steps on the sixth step. This behavior repeats over the entire gain range; see Figure 26.

The device has a differential input impedance of  $100-\Omega$  and is intended to be driven differentially by a matched  $100-\Omega$  differential source impedance for the best linearity and noise performance. The LMH6401 has two on-chip,  $10-\Omega$  resistors, one on each output (as shown in the *Functional Block Diagram* section). For most load conditions, the  $10-\Omega$  resistors are only a partial termination. Consequently, external termination resistors are required in most applications. See Table 11 for common load values and the matching resistors.

The LMH6401 supports a common-mode reference input (VOCM) pin to align the amplifier output common-mode with the subsequent stage (ADC) input requirements. The output common-mode of the LMH6401 is self-biased to mid-supply when the VOCM pin is not driven externally. The device can be operated on a power-supply voltage range of 4.0 V to 5.25 V and supports both single- and split-supply operation. For correct digital operation, the positive supply must not be below 2 V for ground reference logic. A power-down feature is also available through the SPI register and the external PD pin.

## 9.2 Functional Block Diagram

## 9.3 Feature Description

The LMH6401 includes the following features:

- Fully-differential amplifier

- Digitally-controlled variable gain: -6 dB to 26 dB in 1-dB steps

- Output common-mode control

- Single- or split-supply operation

- Large-signal bandwidth of 4.5 GHz

- Usable bandwidth up to 2 GHz

- Power-down control

## 9.4 Device Functional Modes

## 9.4.1 Power-On Reset (POR)

The LMH6401 has a built-in, power-on reset (POR) that sets the device registers to their default state (see Table 3) on power-up. Note that the LMH6401 register information is lost each time power is removed. When power is reapplied, the POR ensures the device enters a default state. Power glitches (of sufficient duration) can also initiate the POR and return the device to a default state.

## 9.4.2 Power-Down (PD)

The device supports power-down control using an external power-down (PD) pin or by writing a logic high to bit 6 of SPI register 2h (see the *Register Maps* section). The external PD is an active high pin. When left floating, the device defaults to an *on* condition when the PD pin defaults to logic low as a result of the internal pulldown resistor. The device PD thresholds are noted in the *Electrical Characteristics* table. The device consumes approximately 7 mA in power-down mode. Note that the SPI register contents are preserved in power-down mode.

#### 9.4.3 Thermal Feedback Control

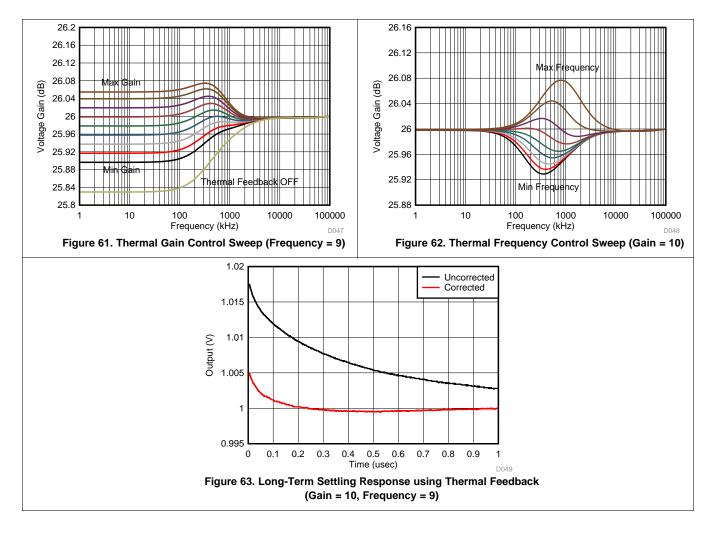

The LMH6401 has a thermal feedback gain and frequency control feature that allows for improved low-frequency settling performance. The Thermal Feedback Gain Control and Thermal Feedback Frequency Control registers set through the SPI control this feature. The default setting is described in Table 3. Graphs are Included in the *Application and Implementation* section that illustrate how the thermal feedback gain and frequency control allows for enhanced performance.

#### 9.4.4 Gain Control

The LMH6401 gain can be controlled from 26-dB gain (0-dB attenuation) to –6-dB gain in 1-dB steps by digitally programming the SPI register 2h. See the *Register Maps* section for more details.

## 9.5 Programming

#### 9.5.1 Details of the Serial Interface

The LMH6401 has a set of internal registers that can be accessed by the serial interface controlled by the  $\overline{CS}$  (chip select), SCLK (serial interface clock), SDI (serial interface input data), and SDO (serial interface readback data) pins. Serial input to the device is enabled when  $\overline{CS}$  is low. SDI serial data are latched at every SCLK rising edge when  $\overline{CS}$  is active (low). Serial data are loaded into the register at every 16th SCLK rising edge when  $\overline{CS}$  is low. When the word length exceeds a multiple of 16 bits, the excess bits are ignored. Data can be loaded in multiples of 16-bit words within a single active  $\overline{CS}$  pulse. The first eight bits form the register address and the remaining eight bits form the register data. The interface can function with SCLK frequencies from 50 MHz down to very low speeds (of a few Hertz) and also with a non-50% SCLK duty cycle. A summary of the LMH6401 SPI protocol follows:

- SPI-1.1 compliant interface

- SPI register contents protected in power-down

- SPI-controlled power-down

- Powered from the main VS+ power supply

- 1.8-V logic compliant

#### **Programming (continued)**

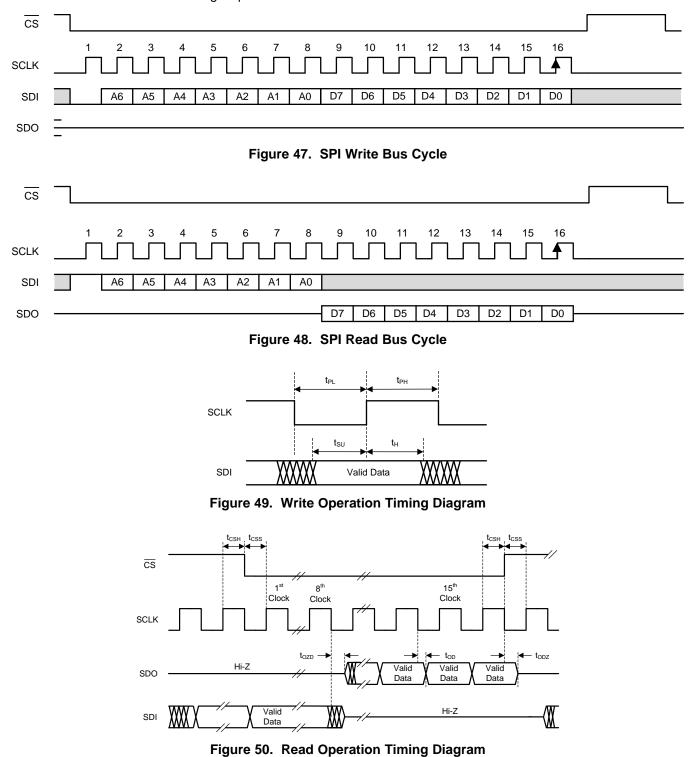

### 9.5.2 Timing Diagrams

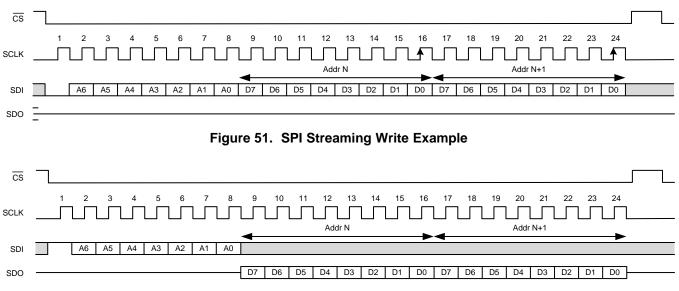

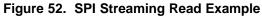

Figure 47 and Figure 48 show timing diagrams for the SPI write and read bus cycles, respectively. Figure 49 and Figure 50 show timing diagrams for the write and read operations, respectively, of the LMH6401. Figure 51 and Figure 52 illustrate example SPI stream write and read timing diagrams, respectively. Refer to the *Electrical Characteristics* table for SPI timing requirements.

LMH6401 ZHCSDQ5A-APRIL 2015-REVISED MAY 2015

www.ti.com.cn

## **Programming (continued)**

## 9.6 Register Maps

Table 3 lists the SPI register map.

## Table 3. SPI Register Map

| ADDRESS<br>(A[6:0]) | R/W | REGISTER                           | DEFAULT (Hex)      |

|---------------------|-----|------------------------------------|--------------------|

| 0                   | R   | Revision ID                        | 03h                |

| 1                   | R   | Product ID                         | 00h                |

| 2                   | R/W | Gain Control                       | 20h (minimum gain) |

| 3                   | R/W | Reserved                           | 8Ch                |

| 4                   | R/W | Thermal feedback gain control      | 27h                |

| 5                   | R/W | Thermal feedback frequency control | 45h                |

| 6-127               | R   | Reserved                           | 00h                |

## 9.6.1 Revision ID (address = 0h, Read-Only) [default = 03h]

#### Figure 53. Revision ID

| 7    | 6    | 5    | 4     | 3      | 2    | 1    | 0    |

|------|------|------|-------|--------|------|------|------|

|      |      |      | Revis | ion ID |      |      |      |

| R-0b | R-0b | R-0b | R-0b  | R-0b   | R-0b | R-1b | R-1b |

|      |      |      |       |        |      |      |      |

LEGEND: R = Read only; -n = value after reset

#### **Table 4. Revision ID Field Descriptions**

| Bit | Field       | Туре | Default  | Description                   |

|-----|-------------|------|----------|-------------------------------|

| 7-0 | Revision ID | R    | 00000011 | Revision identification bits. |

## 9.6.2 Product ID (address = 1h, Read-Only) [default = 00h]

#### Figure 54. Product ID

| 7    | 6           | 5    | 4    | 3    | 2    | 1    | 0    |  |

|------|-------------|------|------|------|------|------|------|--|

|      | Product ID  |      |      |      |      |      |      |  |

| R-0b | R-0b        | R-0b | R-0b | R-0b | R-0b | R-0b | R-0b |  |

|      | Deed anks a |      |      |      |      |      |      |  |

LEGEND: R = Read only; -n = value after reset

## Table 5. Product ID Field Descriptions

| Bit | Field      | Туре | Default  | Description                  |

|-----|------------|------|----------|------------------------------|

| 7-0 | Product ID | R    | 00000000 | Product identification bits. |

## 9.6.3 Gain Control (address = 2h) [default = 20h]

| Figure | 55. | Gain | Control |

|--------|-----|------|---------|

|--------|-----|------|---------|

| 7        | 6          | 5      | 4      | 3      | 2       | 1      | 0      |

|----------|------------|--------|--------|--------|---------|--------|--------|

| Reserved | Power Down |        |        | Gain C | Control |        |        |

| R/W-0b   | R/W-0b     | R/W-1b | R/W-0b | R/W-0b | R/W-0b  | R/W-0b | R/W-0b |

LEGEND: R/W = Read/Write; -n = value after reset

## Table 6. Gain Control Field Description

| Bit | Field        | Туре | Default | Description                                   |

|-----|--------------|------|---------|-----------------------------------------------|

| 7   | Reserved     | R/W  | 0       | Reserved, always program to 0                 |

| 6   | Power Down   | R/W  | 0       | 0 = Active<br>1 = Power down                  |

| 5-0 | Gain Control | R/W  | 100000  | Gain control (see Table 10 for gain settings) |

## 9.6.4 Reserved (address = 3h) [default = 8Ch]

### Figure 56. Reserved

| 7      | 6        | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|--------|----------|--------|--------|--------|--------|--------|--------|--|--|

|        | Reserved |        |        |        |        |        |        |  |  |

| R/W-1b | R/W-0b   | R/W-0b | R/W-0b | R/W-1b | R/W-1b | R/W-0b | R/W-0b |  |  |

|        | -        |        |        |        |        |        |        |  |  |

LEGEND: R/W = Read/Write; -n = value after reset

## **Table 7. Reserved Field Descriptions**

| Bit | Field    | Туре | Default  | Description |

|-----|----------|------|----------|-------------|

| 7-0 | Reserved | R/W  | 10001100 | Reserved    |

## 9.6.5 Thermal Feedback Gain Control (address = 4h) [default = 27h]

## Figure 57. Thermal Feedback Gain Control

| 7        | 6        | 5          | 4      | 3      | 2                | 1       | 0      |

|----------|----------|------------|--------|--------|------------------|---------|--------|

| Reserved | Reserved | Thermal SD |        | Therma | al Feedback Gain | Control |        |

| R/W-0b   | R/W-0b   | R/W-1b     | R/W-0b | R/W-0b | R/W-1b           | R/W-1b  | R/W-1b |

LEGEND: R/W = Read/Write; -n = value after reset

## Table 8. Thermal Feedback Gain Control Field Descriptions

| Bit | Field                         | Туре | Default | Description                                                                                                    |

|-----|-------------------------------|------|---------|----------------------------------------------------------------------------------------------------------------|

| 7-6 | Reserved                      | R/W  | 00      | Reserved, always program to 00                                                                                 |

| 5   | Thermal SD                    | R/W  | 1       | 0 = Thermal feedback control enabled<br>1 = Thermal feedback control disabled                                  |

| 4-0 | Thermal Feedback Gain Control | R/W  | 00111   | 00000 = Minimum thermal feedback gain (see Figure 61)<br>11111 = Maximum thermal feedback gain (see Figure 61) |

## 9.6.6 Thermal Feedback Frequency Control (address = 5h) [default = 45h]

## Figure 58. Thermal Feedback Frequency Control

| 7        | 6        | 5        | 4      | 3         | 2               | 1          | 0      |

|----------|----------|----------|--------|-----------|-----------------|------------|--------|

| Reserved | Reserved | Reserved |        | Thermal F | eedback Frequen | cy Control |        |

| R/W-0b   | R/W-1b   | R/W-0b   | R/W-0b | R/W-0b    | R/W-1b          | R/W-0b     | R/W-1b |

LEGEND: R/W = Read/Write; -n = value after reset

## Table 9. Thermal Feedback Frequency Control Field Descriptions

| Bit | Field                                 | Туре | Default | Description                                                                                                              |

|-----|---------------------------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------|

| 7-5 | Reserved                              | R/W  | 010     | Reserved, always program to 010                                                                                          |

| 4-0 | Thermal Feedback Frequency<br>Control | R/W  | 00101   | 00000 = Minimum thermal feedback frequency (see Figure 62)<br>11111 = Maximum thermal feedback frequency (see Figure 62) |

### Table 10. Gain Control Register Controls

| ATTENUATION (dB) | GAIN (dB) | REGISTER SETTING (Address = 02h) |

|------------------|-----------|----------------------------------|

| 0                | 26        | 00h                              |

| 1                | 25        | 01h                              |

| 2                | 24        | 02h                              |

| 3                | 23        | 03h                              |

| 4                | 22        | 04h                              |

| 5                | 21        | 05h                              |

| 6                | 20        | 06h                              |

| 7                | 19        | 07h                              |

| 8                | 18        | 08h                              |

| 9                | 17        | 09h                              |

| 10               | 16        | 0Ah                              |

| 11               | 15        | 0Bh                              |

| 12               | 14        | 0Ch                              |

| 13               | 13        | 0Dh                              |

| 14               | 12        | 0Eh                              |

| 15               | 11        | 0Fh                              |

| 16               | 10        | 10h                              |

| 17               | 9         | 11h                              |

| 18               | 8         | 12h                              |

| 19               | 7         | 13h                              |

| 20               | 6         | 14h                              |

| 21               | 5         | 15h                              |

| 22               | 4         | 16h                              |

| 23               | 3         | 17h                              |

| 24               | 2         | 18h                              |

| 25               | 1         | 19h                              |

| 26               | 0         | 1Ah                              |

| 27               | -1        | 1Bh                              |

| 28               | -2        | 1Ch                              |

| 29               | -3        | 1Dh                              |

| 30               | -4        | 1Eh                              |

| 31               | -5        | 1Fh                              |

| 32               | -6        | 20h-3Fh                          |

TEXAS INSTRUMENTS

www.ti.com.cn

## **10** Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## **10.1** Application Information

## **10.1.1 Analog Input Characteristics**

The LMH6401 is a single-channel device with analog input signal pins (INP and INM) that denote the positive and negative input pins, respectively. The device inputs can be either ac- or dc-coupled. In order to dc-couple the inputs, care must be taken to ensure the common-mode voltage is set within the input common-mode range of the device, as described in the *Electrical Characteristics* table. For optimal linearity and noise performance, TI recommends setting the inputs using input capacitors that allow the inputs to self-bias close to mid-supply and isolates the common-mode voltage of the driving circuitry. The LMH6401 inputs must be driven differentially. For single-ended input source applications, care must be taken to select an appropriate balun or fully-differential amplifier (such as the LMH3401 or LMH5401) that can convert single-ended signals into differential signals with minimal distortion.

At maximum gain, the digital attenuator is set to 0-dB attenuation, the input signal is much smaller than the output, and the maximum output voltage swing is limited by the output stage of the device. At minimum gain, however, the maximum output voltage swing is limited by the input stage because the output is 6 dB lower than the inputs. In the minimum gain configuration, the input signal begins to clip against the electrostatic discharge (ESD) protection diodes before the output reaches maximum swing limits. This clipping is a result of the input signal being unable to swing below the negative supply voltage and being unable to exceed the positive supply voltage because of the protection diodes. For linear operation, care must be taken to ensure that the input is kept within the maximum input voltage ratings, as described in the *Absolute Maximum Ratings* table. The supply voltage imposes the limit for the input voltage swing because the input stage self-biases to approximately mid-rail.

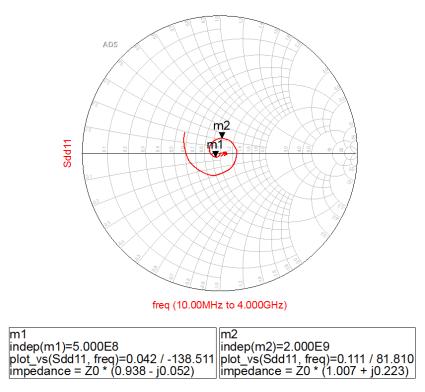

The device input impedance is set by the internal input termination resistors to a nominal value of 100  $\Omega$ . Process variations result in a range of values, as described in the *Electrical Characteristics* table. The input impedance is also affected by device parasitic reactance at higher frequencies, thus shifting the impedance away from a nominal 100  $\Omega$ . The LMH6401 exhibits a well-matched, 100- $\Omega$  differential input impedance in the usable bandwidth, achieving a –15-dB input return loss at 2 GHz across the gain settings; see Figure 3. Figure 59 illustrates a Smith chart plot of the LMH6401 differential input impedance referenced to a 100- $\Omega$  characteristic impedance.

## **Application Information (continued)**

Figure 59. Smith Chart Showing Differential Input Impedance ( $z_0 = 100 \Omega$ )

#### 10.1.2 Analog Output Characteristics

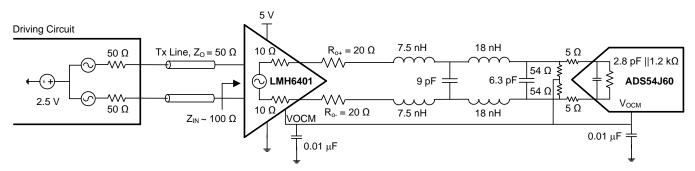

The LMH6401, as with most RF amplifiers, has two 10- $\Omega$ , on-chip resistors on each output leg to provide isolation from board parasitics at the output pins; see the *Functional Block Diagram* section. When designing a filter between the LMH6401 and the interfacing circuitry (ADC), the filter source impedance must be calculated by taking into account the two 10- $\Omega$ , on-chip resistors. Table 11 shows the calculated external source impedance values ( $R_{O+}$  and  $R_{O-}$ ) required for various matched filter loads ( $R_L$ ). An important note is that the filter design between the LMH6401 and the ADC is not limited to a matched filter, and source impedance values ( $R_{O+}$  and  $R_{O-}$ ) can be reduced to achieve higher swing at the filter outputs. Achieving lower loss in the filter source impedance resistors or higher swing at the filter outputs is often desirable because the amplifier must output reduced swing to maintain the same full-scale input at the ADC and, thus, better linearity performance. An example 370-MHz, un-matched, low-pass filter between the LMH6401 and ADS54J60 is illustrated in Figure 64, with ( $R_{O+}$  and  $R_{O-}$ ) set to 20  $\Omega$  and  $R_L$  set to 100  $\Omega$ .

| Table 11. Load Component Values <sup>(1</sup> | ) |

|-----------------------------------------------|---|

|-----------------------------------------------|---|

...

| LOAD (R <sub>L</sub> ) | R <sub>0+</sub> AND R <sub>0-</sub> FOR A MATCHED<br>TERMINATION | TOTAL LOAD RESISTANCE AT<br>AMPLIFIER OUTPUT | TERMINATION LOSS |

|------------------------|------------------------------------------------------------------|----------------------------------------------|------------------|

| 50 Ω                   | 15 Ω                                                             | 100 Ω                                        | 6 dB             |

| 100 Ω                  | 40 Ω                                                             | 200 Ω                                        | 6 dB             |

| 200 Ω                  | 90 Ω                                                             | 400 Ω                                        | 6 dB             |

| 400 Ω                  | 190 Ω                                                            | 800 Ω                                        | 6 dB             |

| 1 kΩ                   | 490 Ω                                                            | 2000 Ω                                       | 6 dB             |

(1) The total load includes termination resistors.

LMH6401 ZHCSDQ5A – APRIL 2015–REVISED MAY 2015

The LMH6401 can be either dc- or ac-coupled at the outputs. For dc-coupled applications, the device provides an option to control the output common-mode voltage using the VOCM pin. Device performance is optimal when the output common-mode voltage is within  $\pm 0.5$  V of mid-supply (see Figure 21) and performance degrades outside the range when the output swing approaches clipping levels. The LMH6401 can achieve a maximum output swing of 6 V<sub>PPD</sub> with the output common-mode voltage centered at mid-supply.

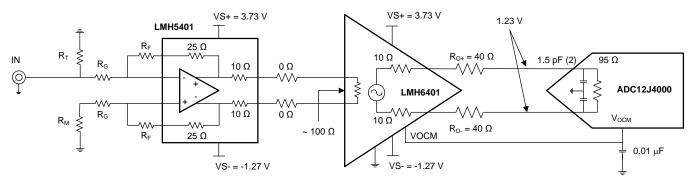

Note that by default, the output common-mode voltage is set to mid-supply before the two  $10-\Omega$ , on-chip resistors; see the *Functional Block Diagram* section. On a single-supply operation when dc-coupling the device outputs to an ADC using common-mode, level-shifting resistors, the output common-mode voltage and resistor values being calculated must include the two internal  $10-\Omega$  resistors in the equation. When operating the LMH6401 on split supplies and dc-coupling the outputs, TI recommends matching the output common-mode voltage of the LMH6401 with the input common-mode voltage of the ADC. A simple design procedure is to select the supply voltages (VS+ and VS-) such that the default output common-mode voltage being set is equal to the input common-mode voltage of the ADC. As illustrated in Figure 66, the supplies of the LMH6401 are selected such that the default output common-mode voltage is set to mid-supply or 1.23 V, which is within the input common-mode voltage range of the ADC (1.185 V to 1.265 V).

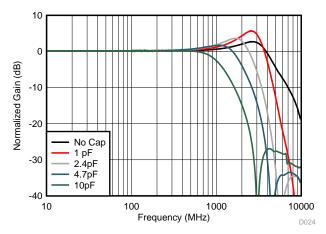

#### 10.1.2.1 Driving Capacitive Loads

With high-speed signal paths, capacitive loading at the output is highly detrimental to the signal path, as shown in Figure 60. The device on-chip resistors are included in order to isolate the parasitic capacitance associated with the package and the printed circuit board (PCB) pads that the device is soldered to. However, designers must make every effort to reduce parasitic loading on the amplifier output pins. The LMH6401 is stable with most capacitive loads up to 10 pF; however, bandwidth suffers with capacitive loading on the output.

Figure 60. Frequency Response vs Capacitive Load

#### 10.1.3 Thermal Feedback Control

The LMH6401 can be used to optimize long-term settling responses using thermal feedback gain and frequency control registers. These registers are disabled on power-up and can be enabled by clearing the thermal SD bit; see the Thermal Feedback Gain Control register. The thermal feedback gain control bits increase the low-frequency gain and the thermal feedback frequency control bits shift the boost frequency. The thermal feedback gain offset to optimize the control range. The thermal feedback off condition is illustrated in the gain control plot (Figure 61), along with a sweep of gain settings of 0, 4, 8...28, and 31 with a 0 register value representing the minimum gain setting from the gain sweep over the values of 0, 4, 8...28, and 31 with a 0 register value representing the minimum frequency boost setting.

#### 10.1.3.1 Step Response Optimization using Thermal Feedback Control

The LMH6401 has an adjustable frequency compensation scheme that is designed to dramatically improve the step response for long-term settling. The structure of the LMH6401 gives the best distortion performance for signals ranging from dc to 2 GHz over a wide range of gain settings. Thermal heating causes a small change in gain at low frequencies close to 500 kHz. This change in gain is shown in Figure 61 in the ac response for the trace labeled *Thermal Feedback OFF*. The amount of gain change is approximately 0.18 dB at maximum gain. This gain change resulting from thermal heating leads to approximately 1.7% overshoot that settles over a relatively long time period. A patent pending technique is added that allows for the reduction of this overshoot to approximately 0.35%, thus eliminating the long-term settling and still retaining the wide dynamic performance range. The circuit also corrects for small systematic changes that occur at different gain settings and tracks temperature changes as well. This low-frequency gain correction is accomplished by the addition of a circuit that alters the gain at low frequencies to nearly eliminate the variation from low to high frequencies.

The step response optimization circuit is disabled on power-up and can be enabled by clearing bit 5 in the Thermal Feedback Gain Control register (register 4h). The power-on default setting for thermal gain and frequency are adjusted for the evaluation board for typical silicon performance. These registers are made available for customization in the final system because board layout characteristics or other components in the system can change the required correction needed.

Figure 63 demonstrates the initial step response and the corrected response that corresponds to the default register values for a typical device on the evaluation board displaying long-term settling correction.

LMH6401 ZHCSDQ5A – APRIL 2015–REVISED MAY 2015

#### 10.1.4 Thermal Considerations

The LMH6401 is packaged in a space-saving UQFN package that has a thermal coefficient ( $R_{\theta JA}$ ) of 78°C/W. Limit the total power dissipation in order to keep the device junction temperature below 150°C for instantaneous power and below 125°C for continuous power.

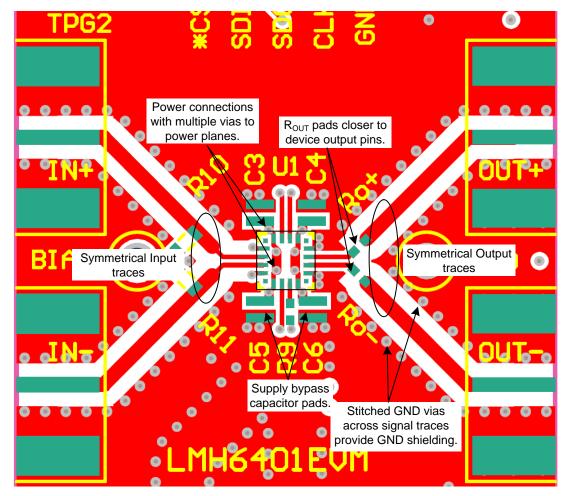

## **10.2 Typical Application**

The LMH6401 is designed and optimized for the highest performance when driving differential input ADCs. Figure 64 shows a block diagram of the LMH6401 driving an ADC with a fourth-order, low-pass filter. The primary interface circuit between the amplifier and the ADC is usually an antialiasing filter to suppress high-frequency harmonics aliasing into the ADC FFT spectrum. The interface circuit also provides a means to bias the signal to the input common-mode voltage required by the ADC. Filters range from single-order real RC poles to higher-order RLC filters, depending on the application requirements. Output resistors ( $R_0$ ) in series with the amplifier outputs isolate the amplifier from any capacitive load presented by the filter.

Figure 64. The LMH6401 Driving an ADS54J60 with a 370 MHz Fourth-Order Chebyshev Low-Pass Filter

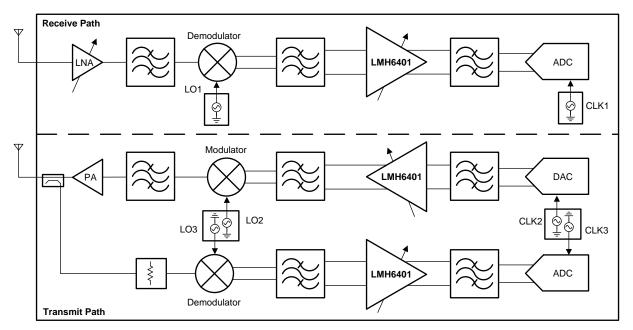

Low distortion and low noise figure, along-with low power dissipation make the LMH6401 an ideal device for use in front-end radio applications. Figure 65 shows a block diagram of a one-transmit and one-receive (1T/1R) radio architecture with a digital pre-distortion path, where the LMH6401 can be used as a variable-gain IF amplifier on both the transmit and receive signal chain.

Figure 65. 1T/1R with Digital Pre-Distortion Front-End Radio Application

## **Typical Application (continued)**

#### 10.2.1 Design Requirements

Table 12 shows example design requirements for an amplifier in an oscilloscope front-end application; the LMH6401 meets these requirements.

| SPECIFICATION                                                                                                                      | DESIGN REQUIREMENTS                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Supply voltage and current                                                                                                         | 4.0 V to 5.25 V with typically less than a 100-mA current and<br>split-supply operation supported |

| Usable input frequency range                                                                                                       | DC to 2 GHz                                                                                       |

| Voltage gain and gain range                                                                                                        | 26-dB to 10-dB voltage gain with x2 attenuation supported<br>(ideal 32-dB gain range)             |

| OIP3 (P <sub>0</sub> = –2 dBm per tone, R <sub>L</sub> = 200 $\Omega$ ) and noise figure (R <sub>S</sub> = 100 $\Omega$ ) at 1 GHz | > 30 dBm and less than 10 dB, respectively.                                                       |

| Rise and fall time ( $V_0$ = 2-V step) from 10% to 90%                                                                             | Less than 100 ps                                                                                  |

| Settling time to 1% of $V_0 = 2$ -V step                                                                                           | Less than 1 ns with long-term settling correction required                                        |

#### Table 12. Example Design Requirements for an Oscilloscope Front-End application

#### 10.2.2 Detailed Design Procedure

#### 10.2.2.1 Driving ADCs

When the amplifier is driving an ADC, the key points to consider for implementation are the signal-to-noise ratio (SNR), spurious-free dynamic range (SFDR), and ADC input considerations, as described in this section.

A typical application of the LMH6401 involves driving an ultra-wideband, 12-bit ADC (such as the ADC12J4000), as shown in Figure 66. The LMH6401 can drive the full Nyquist bandwidth of ADCs with sampling rates up to 4 GSPS. If the front-end bandwidth of the ADC is more than 2 GHz, use a simple noise filter to improve SNR. Otherwise, the ADC can be connected directly to the amplifier output pins with appropriate matching resistors to limit the full-scale input of the ADC. Note that the LMH6401 inputs must be driven differentially using a balun or fully-differential amplifiers (FDAs). For dc-coupled applications, an FDA (such as the LMH3401 or LMH5401) that can convert a single-ended input to a differential output with low distortion is preferred.

LMH6401 ZHCSDQ5A – APRIL 2015–REVISED MAY 2015

Copyright © 2015, Texas Instruments Incorporated

#### 10.2.2.1.1 SNR Considerations

The signal-to-noise ratio (SNR) of the amplifier and filter can be calculated from the amplitude of the signal and the bandwidth of the filter. The noise from the amplifier is band-limited by the filter with the equivalent brick-wall filter bandwidth. The amplifier and filter noise can be calculated using Equation 3:

$$SNR_{AMP+FILTER} = 10 \cdot \log \left( \frac{V_{O}^{2}}{e^{2}_{FILTEROUT}} \right) = 20 \cdot \log \left( \frac{V_{O}}{e_{FILTEROUT}} \right)$$

where:

- $e_{\text{FILTEROUT}} = e_{\text{NAMPOUT}} \bullet \sqrt{\text{ENB}},$

- $e_{NAMPOUT}$  = the output noise density of the LMH6401 (30.4 nV/ $\sqrt{Hz}$ ) at A<sub>V</sub> = 26 dB,

- ENB = the brick-wall equivalent noise bandwidth of the filter, and

• V<sub>O</sub> = the amplifier output signal.

For example, with a first-order (N = 1) band-pass or low-pass filter with a 1000-MHz cutoff, ENB is 1.57 •  $f_{-3dB} = 1.57 • 1000$  MHz = 1570 MHz. For second-order (N = 2) filters, ENB is  $1.22 • f_{-3dB}$ . When the filter order increases, ENB approaches  $f_{-3dB}$  (N = 3  $\rightarrow$  ENB = 1.15 •  $f_{-3dB}$ ; N = 4  $\rightarrow$  ENB = 1.13 •  $f_{-3dB}$ ). Both V<sub>0</sub> and  $e_{\text{FILTEROUT}}$  are in RMS voltages. For example, with a 2-V<sub>PP</sub> (0.707 V<sub>RMS</sub>) output signal and a 1000-MHz first-order, low-pass filter, the SNR of the amplifier and filter is 55.4 dB with  $e_{\text{FILTEROUT}} = 30.4 \text{ nV}/\sqrt{\text{Hz}} • \sqrt{1570 \text{ MHz}} = 1204.5 \ \mu\text{V}_{\text{RMS}}$ .

The SNR of the amplifier, filter, and ADC sum in RMS fashion, as shown in Equation 4 (SNR values in dB):

$$SNR_{SYSTEM} = -20 \cdot \log \left[ \sqrt{10^{\frac{-SNR_{AMP-FILTER}}{10}} + 10^{\frac{-SNR_{ADC}}{10}}} \right]$$

(4)

This formula shows that if the SNR of the amplifier and filter equals the SNR of the ADC, the combined SNR is 3 dB lower (worse). Thus, for minimal degradation (< 1 dB) on the ADC SNR, the SNR of the amplifier and filter must be  $\geq$  10 dB greater than the ADC SNR. The combined SNR calculated in this manner is usually accurate to within ±1 dB of the actual implementation.

#### 10.2.2.1.2 SFDR Considerations

The SFDR of the amplifier is usually set by the second- or third-harmonic distortion for single-tone inputs, and by the second-order or third-order intermodulation distortion for two-tone inputs. Harmonics and second-order intermodulation distortion can be filtered to some degree, but third-order intermodulation spurs cannot be filtered. The ADC generates the same distortion products as the amplifier, but also generates additional spurs (not harmonically related to the input signal) as a result of sampling and clock feed through.

When the spurs from the amplifier and filter are known, each individual spur can be directly added to the same spur from the ADC, as shown in Equation 5, to estimate the combined spur (spur amplitudes in dBc):

$$HDx_{\text{SYSTEM}} = -20 \cdot \log \left[ 10^{\frac{-HDx_{\text{AMP}+\text{FILTER}}}{20}} + 10^{\frac{-HDx_{\text{ADC}}}{20}} \right]$$

This calculation assumes the spurs are in phase, but usually provides a good estimate of the final combined distortion.

For example, if the spur of the amplifier and filter equals the spur of the ADC, then the combined spur is 6 dB higher. To minimize the amplifier contribution (< 1 dB) to the overall system distortion, the spur from the amplifier and filter must be approximately 15 dB lower in amplitude than that of the converter. The combined spur calculated in this manner is usually accurate to within  $\pm 6$  dB of the actual implementation; however, higher variations can be detected as a result of phase shift in the filter, especially in second-order harmonic performance.

This worst-case spur calculation assumes that the amplifier and filter spur of interest is in phase with the corresponding spur in the ADC, such that the two spur amplitudes can be added linearly. There are two phase-shift mechanisms that cause the measured distortion performance of the amplifier-ADC chain to deviate from the expected performance calculated using Equation 5; one is the common-mode phase shift and other is the differential phase shift.

(3)

(5)

*Common-mode phase shift* is the phase shift detected equally in both branches of the differential signal path including the filter. Common-mode phase shift nullifies the basic assumption that the amplifier, filter, and ADC spur sources are in phase. This phase shift can lead to better performance than predicted when the spurs become phase shifted, and there is the potential for cancellation when the phase shift reaches 180°. However, there is a significant challenge in designing an amplifier-ADC interface circuit to take advantage of a common-mode phase shift for cancellation: the phase characteristics of the ADC spur sources are unknown, thus the necessary phase shift in the filter and signal path for cancellation is also unknown.

Differential phase shift is the difference in the phase response between the two branches of the differential filter signal path. Differential phase shift in the filter is a result of mismatched components caused by nominal tolerances and can severely degrade the even harmonic distortion of the amplifier-ADC chain. This effect has the same result as mismatched path lengths for the two differential traces, and causes more phase shift in one path than the other. Ideally, the phase responses over frequency through the two sides of a differential signal path are identical, such that even harmonics remain optimally out of phase and cancel when the signal is taken differentially. However, if one side has more phase shift than the other, then the even harmonic cancellation is not as effective.

Single-order RC filters cause very little differential phase shift with nominal tolerances of 5% or less, but higherorder LC filters are very sensitive to component mismatch. For instance, a third-order Butterworth band-pass filter with a 100-MHz center frequency and a 20-MHz bandwidth shows as much as 20° of differential phase imbalance in a SPICE Monte Carlo analysis with 2% component tolerances. Therefore, although a prototype may work, production variance is unacceptable. For ac-coupled or dc-coupled applications where a transformer or balun cannot be used, using first- or second-order filters is recommended to minimize the effect of differential phase shift.

#### 10.2.2.1.3 ADC Input Common-Mode Voltage Considerations—AC-Coupled Input

When interfacing to an ADC, the input common-mode voltage range of the ADC must be taken into account for proper operation. In an ac-coupled application between the amplifier and the ADC, the input common-mode voltage bias of the ADC can be accomplished in different ways. Some ADCs use internal bias networks such that the analog inputs are automatically biased to the required input common-mode voltage if the inputs are accoupled with capacitors (or if the filter between the amplifier and ADC is a band-pass filter). Other ADCs supply their required input common-mode voltage from a reference voltage output pin (often termed CM or  $V_{CM}$ ). With these ADCs, the ac-coupled input signal can be re-biased to the input common-mode voltage by connecting resistors from each input to the CM output of the ADC, as shown in Figure 67. AC coupling provides dc common-mode isolation between the amplifier and the ADC; thus, the output common-mode voltage of the amplifier is a *don't care* for the ADC.

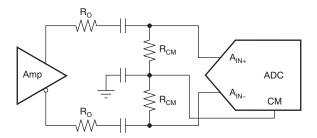

Figure 67. Biasing AC-Coupled ADC Inputs Using the ADC CM Output

#### 10.2.2.1.4 ADC Input Common-Mode Voltage Considerations—DC-Coupled Input