LP8860-Q1

ZHCSCK8G-MAY 2014-REVISED OCTOBER 2017

# LP8860-Q1 具有四个 150mA 通道的低 EMI 汽车 LED 驱动器

## 特性

- 符合汽车应用 应用

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1: -40°C 至 +125°C 环境工作温 度

- 输入电压工作范围: 3V 至 48V

- 四路高精度电流阱

- 电流匹配度为 0.5%(典型值)

- LED 灯串电流高达 150mA/通道

- 采用外部 PWM 亮度控制,调光比大于 13 000:1

- 通过 SPI 或 I<sup>2</sup>C 进行 16 位调光控制

- 支持显示模式(全局调光)和群集模式(独立调

- 针对更高 LED 驱动光效率的混合 PWM 和电流调 光

- 针对 LED PWM 频率的同步

- 具有介于 100kHz 到 2.2Mhz 之间的可编程开关频 率和用于降低电磁干扰 (EMI) 的扩频选项的升压控 制器

- 升压同步输入

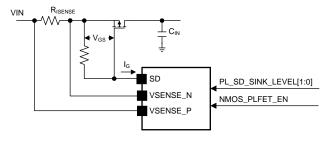

- 电力线场效应晶体管 (FET) 控制,可实现浪涌电流 保护和待机节能

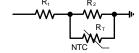

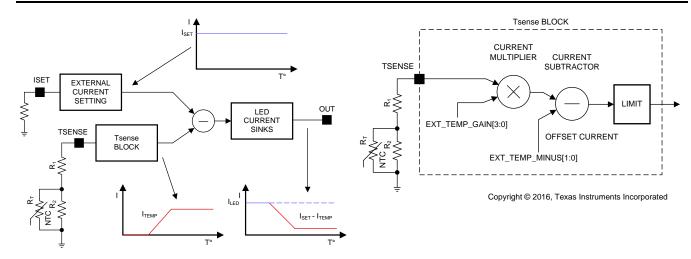

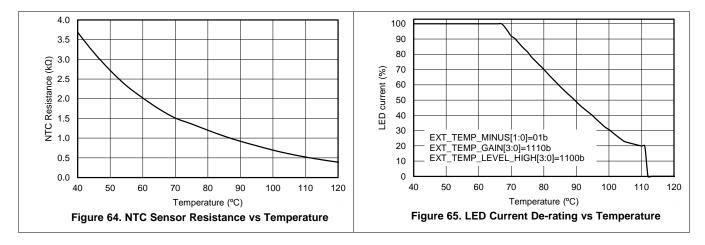

- 使用外部温度传感器自动降低 LED 电流

- 丰富的故障诊断"

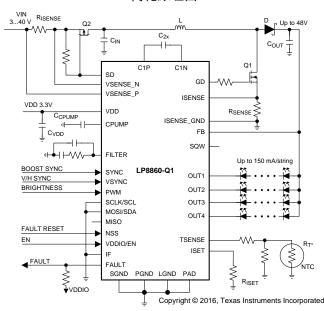

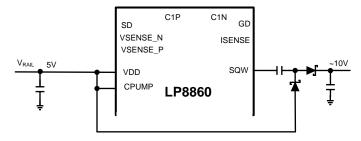

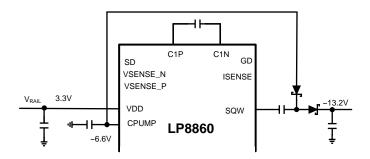

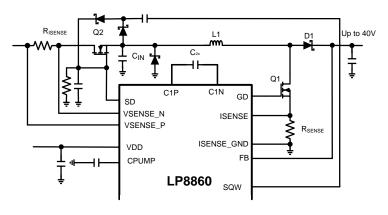

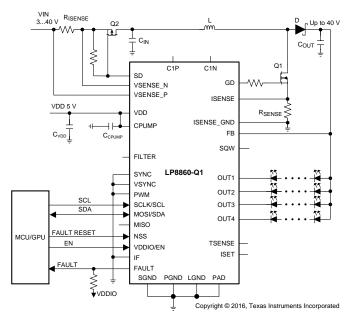

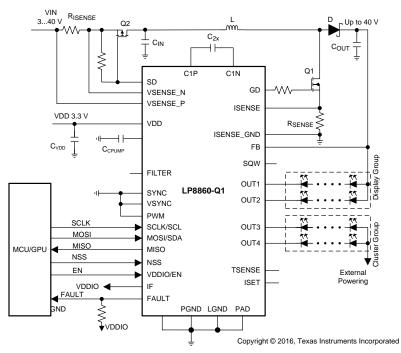

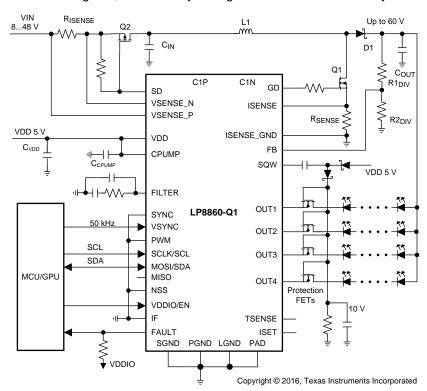

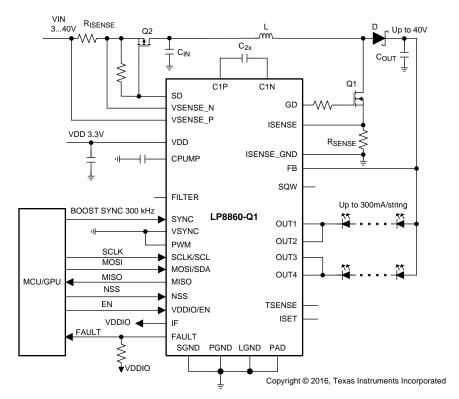

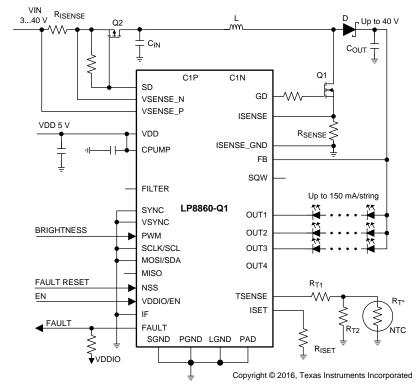

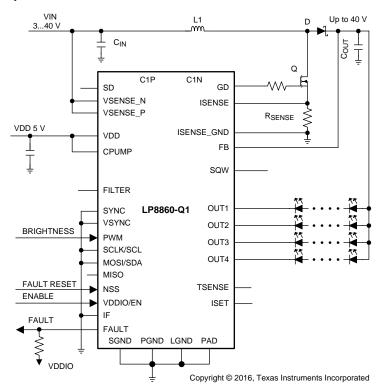

#### 简化原理图

### 2 应用

- 为以下应用提供背光:

- 汽车信息娱乐系统

- 汽车仪表盘

- 智能车镜

- 抬头显示屏 (HUD)

- 中央信息显示屏 (CID)

- 音视频导航 (AVN)

## 3 说明

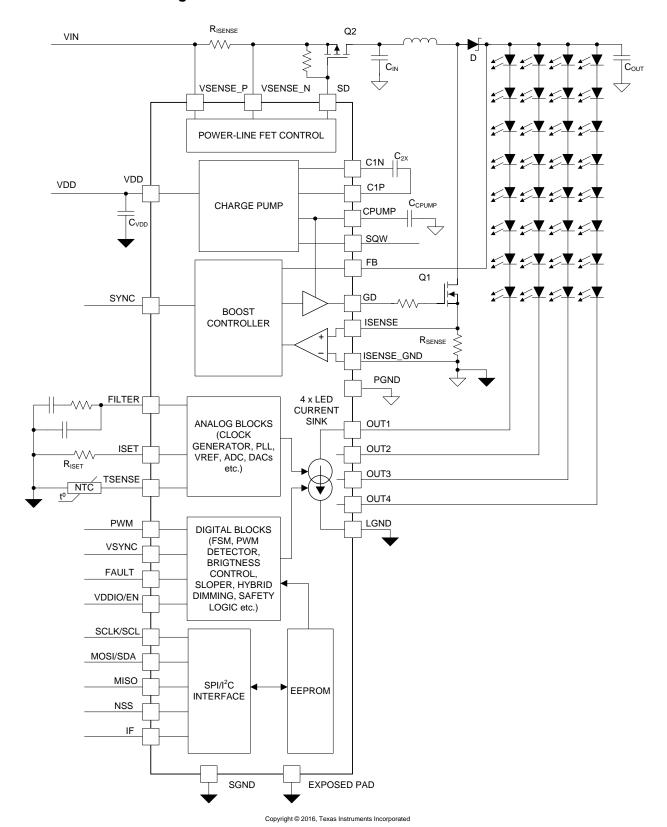

LP8860-Q1 是具有升压控制器的汽车用高效 LED 驱动 器。该器件具有可通过 PWM 输入信号、SPI 和/或 I2C 主机控制的 4 路高精度电流阱。

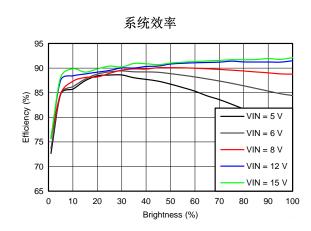

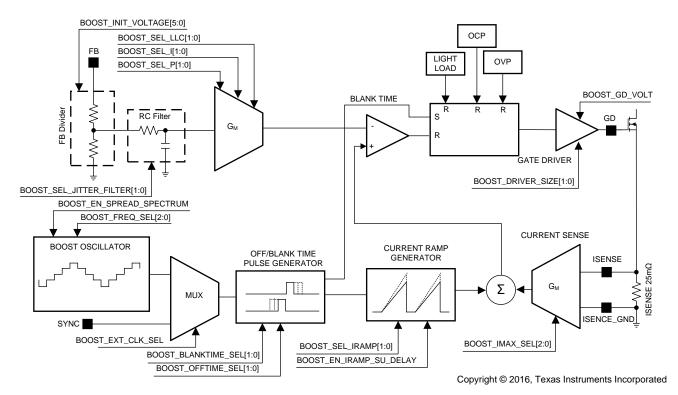

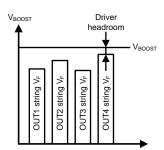

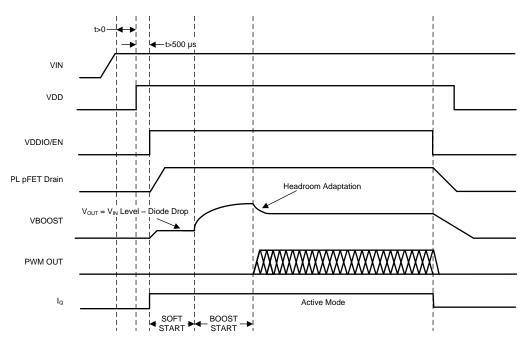

升压转换器具有基于 LED 电流阱余量电压的自适应输 出电压控制。该特性可在所有条件下将电压调节到能够 满足需要的最低水平, 从而最大限度降低功耗。凭借宽 范围可调频率, LP8860-Q1 能够避免调幅 (AM) 射频 波段的干扰。

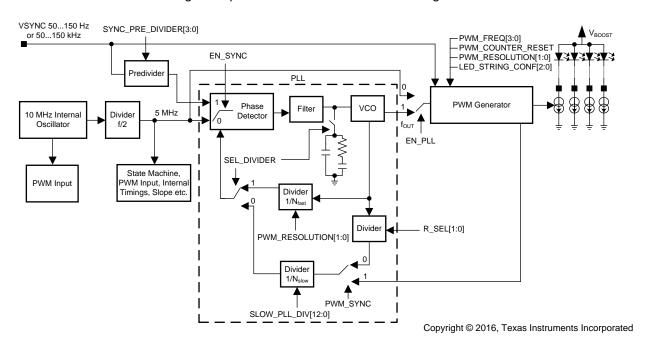

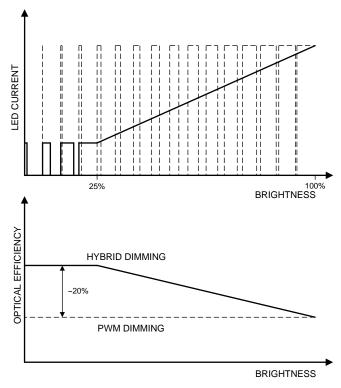

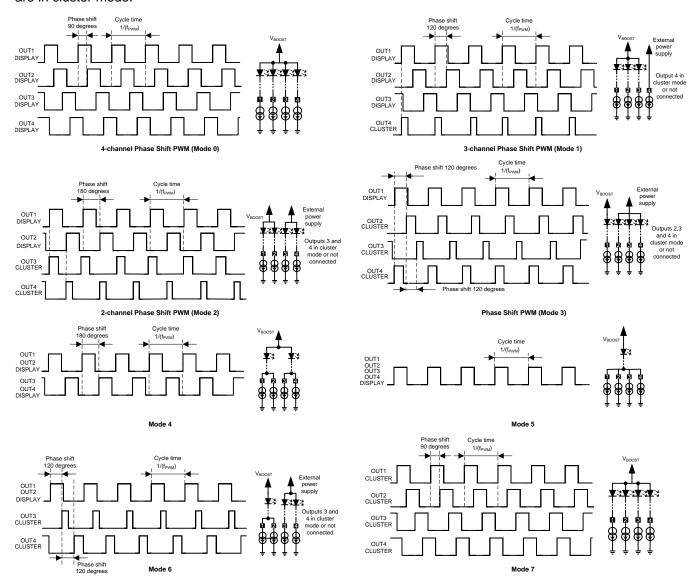

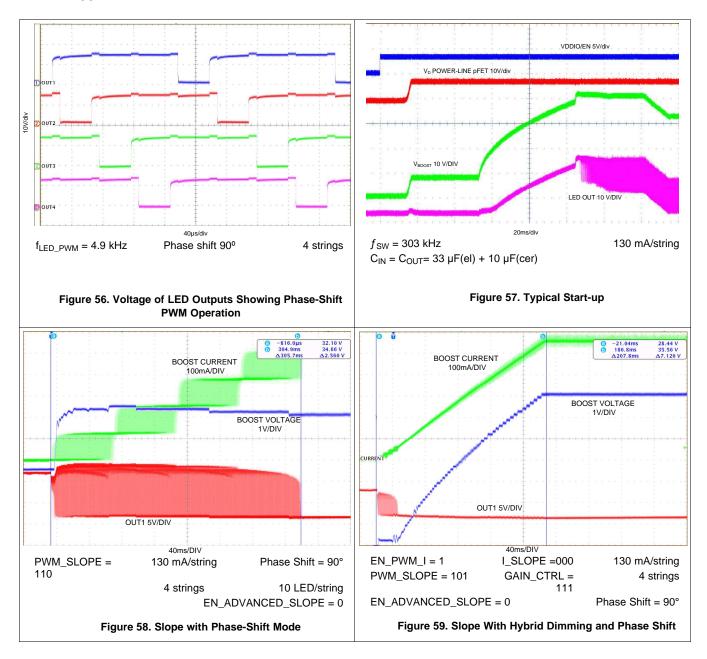

LP8860-Q1 支持内置混合 PWM 和电流调光,从而降 低了 EMI、延长了 LED 使用寿命且提高了总光学效 率。相移 PWM 可减少人耳噪声和输出纹波。

### 器件信息(1)

|           | HH I I I HI ICI             |                 |

|-----------|-----------------------------|-----------------|

| 器件型号      | 封装                          | 封装尺寸 (标称值)      |

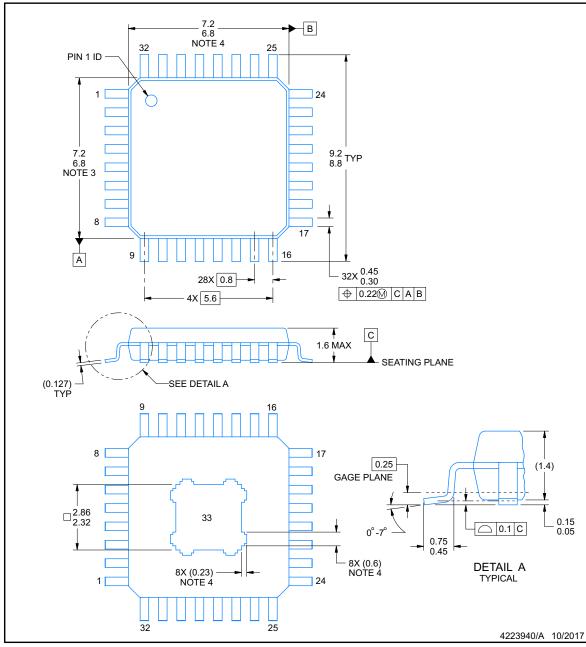

| LP8860-Q1 | 散热薄型四方扁平<br>封装 (HLQFP) (32) | 7.00mm × 7.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

| $\rightarrow$ | $\rightarrow$ |

|---------------|---------------|

| ы             |               |

| —             | ` N           |

|               |               |

| 1                              | 特性                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              | 7.17 Typical Characteristics   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                              | 应用1                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                            | Detailed Description           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •                                            | 8.1 Overview                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4                              | 修订历史记录                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              | 8.2 Functional Block Diagram   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5                              | 器件比较表                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              | 8.3 Feature Description        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

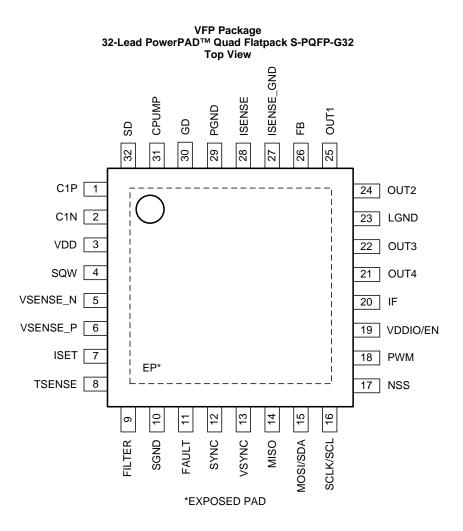

| _                              | Pin Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              | 8.4 Device Functional Modes    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | 8.5 Programming                | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7                              | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              | 8.6 Register Maps              | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                | 7.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                                            | Application and Implementation | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                | 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              | 9.1 Application Information    | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                | 7.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              | 9.2 Typical Applications       | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                | 7.5 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                                           | Power Supply Recommendations   | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                | 7.6 Current Sinks Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11                                           | Layout                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

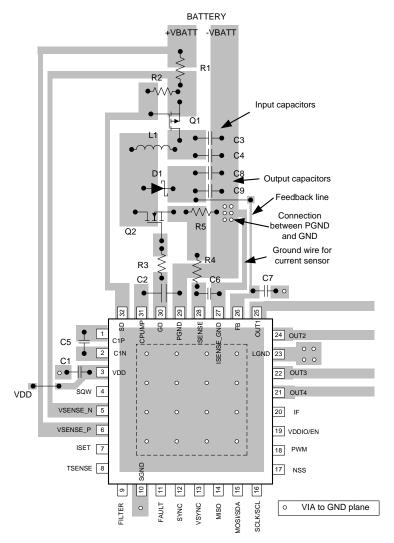

|                                | 7.7 Boost Converter Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              | 11.1 Layout Guidelines         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | 7.8 Logic Interface Characteristics 9                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              | 11.2 Layout Example            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

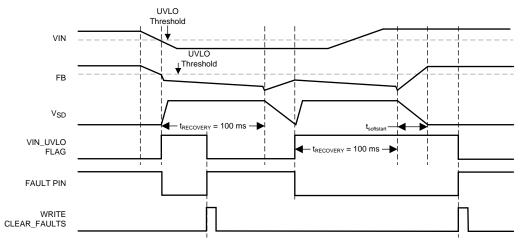

|                                | 7.9 V <sub>IN</sub> Undervoltage Protection (VIN_UVLO)                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                           | 器件和文档支持                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | 7.10 V <sub>DD</sub> Undervoltage Protection (VDD_UVLO) 10                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              | 12.1 器件支持                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

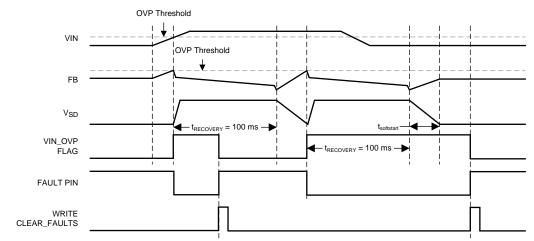

|                                | 7.11 V <sub>IN</sub> Overvoltage Protection (VIN_OVP)                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              | 12.2 文档支持                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | 7.12 V <sub>IN</sub> Overcurrent Protection (VIN_OCP)                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              | 12.3 接收文档更新通知                  | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | 7.13 Power-Line FET Control Electrical                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              | 12.4 社区资源                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              | 12.5 商标                        | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | 7.14 External Temp Sensor Control Electrical                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              | 12.6 静电放电警告                    | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | Characteristics 10                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              | 12.7 Glossary                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

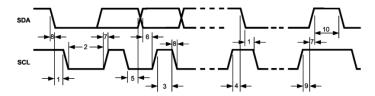

|                                | 7.15 I <sup>2</sup> C Serial Bus Timing Parameters (SDA, SCLK) . 12                                                                                                                                                                                                                                                                                                                                                                                                              | 13                                           | 机械、封装和可订购信息                    | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

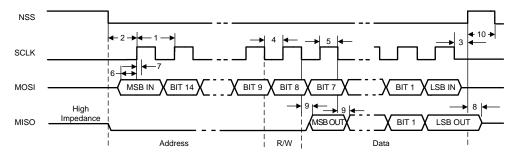

|                                | 7.16 SPI Timing Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | 多订历史记录<br>ges from Revision F (July 2017) to Revision G                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |                                | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| han                            | 多订历史记录                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |