MSP430FG6626, MSP430FG6625 MSP430FG6426, MSP430FG6425

- MAY 2015 - REVISED SEPTEMBER 2020

# MSP430FG662x、MSP430FG642x 混合信号微控制器

## 1 特性

- 低电源电压范围: 3.6V 低至 1.8V

- 高性能集成信号链

- 连续时间  $\Sigma$   $\Delta$  16 位模数转换器 (ADC), 具有 内部基准电压和 10 个外部模拟输入,其中 6 个 单端输入和 4 个可选差分或单端输入

- 双路运算放大器

- 四通道低阻抗接地开关

- 电压比较器

- 具有同步功能的双 12 位数模转换器 (DAC)

- 具有高达 160 段对比度控制的集成 LCD 驱动器

- MSP430FG662x: 全速通用串行总线 (USB)

- 集成 USB-PHY

- 集成 3.3V 和 1.8V USB 电源系统

- 集成 USB-PLL

- 八输入和八输出端点

- 超低功耗

- 激活模式 (AM),

所有系统时钟激活:

8MHz 时为 250µA/MHz、3.0V、闪存程序执行

- 待机模式 (LPM3): 含晶体的 看门狗、电源监控器可用、完全 RAM 保持、快 速唤醒:

2.2V 时为 3.2µA, 3.0V 时为 3.4µA (典型值)

- 关断 RTC 模式 (LPM3.5): 关断模式、带有晶振的有源 RTC: 3.0V 时为 0.9µA ( 典型值 )

- 关断模式 (LPM4.5): 3.0V 时为 0.2µA ( 典型值 )

- 智能数字外设

- 两个 16 位计时器,每个计时器具有 3 个捕捉/比 较寄存器

- 一个具有 5 个捕捉/比较寄存器的 16 位计时器

- 一个 16 位计时器,具有 7 个捕捉/比较寄存器

- 6 通道内部 DMA

- 硬件乘法器支持 32 位运算

- 四个通用串行通信接口 (USCI)

- USCI A0 和 USCI A1

- 具有自动波特率检测功能的增强型通用异步 收发器 (UART)

- 红外数据通讯 (IrDA) 编码器和解码器

- 同步 SPI

- USCI\_B0 和 USCI\_B1

- I<sup>2</sup>C

- 同步 SPI

- 具有用于时间偏移校正的校准逻辑的 RTC,在 LPM 3.5 下运行

- 16 位 RISC 架构,扩展存储器,高达 20MHz 的系 统时钟

- 灵活的电源管理系统

- 具有可编程稳压内核电源电压的完全集成 LDO

- 电源电压监控、监视和欠压保护

- 单一时钟系统

- 针对频率稳定的锁相环 (FLL) 控制环路

- 低功耗低频内部时钟源 (VLO)

- 低频修整内部基准源 (REFO)

- 32kHz 晶振 (XT1)

- 高达 32MHz 的高频晶振 (XT2)

- 用于备用子系统的独立电压电源

- 32kHz 低频振荡器 (XT1)

- RTC

- 各用存储器(8字节)

- 开发工具与软件 ( 另请参阅工具与软件 )

- MSP-TS430PZ100AUSB 100 引脚目标开发板

- MSP430Ware™ 代码示例

- 在 3 μs (典型值 ) 内从待机模式唤醒

- 串行板上编程,无需外部编程电压

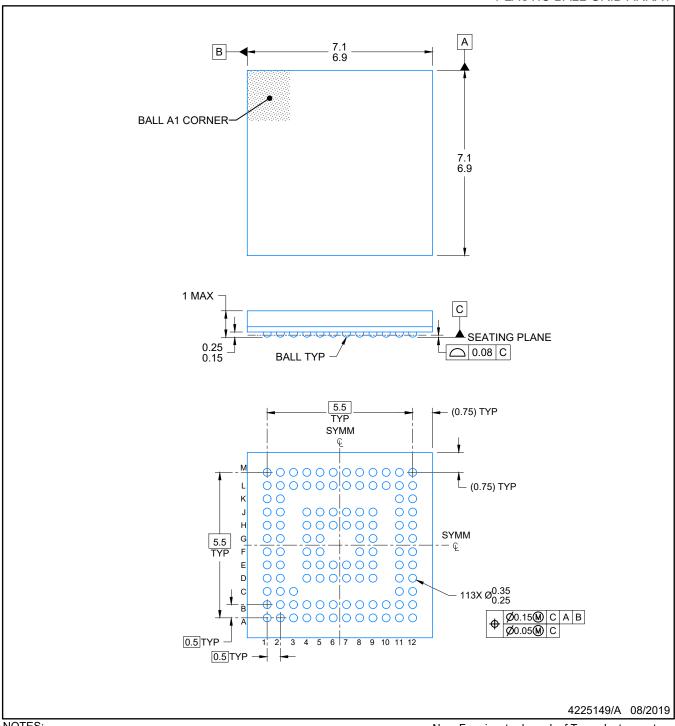

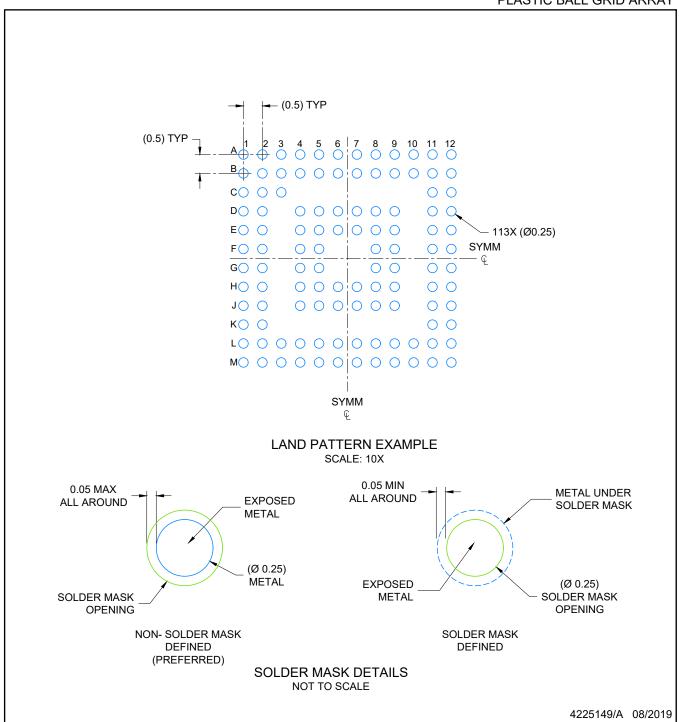

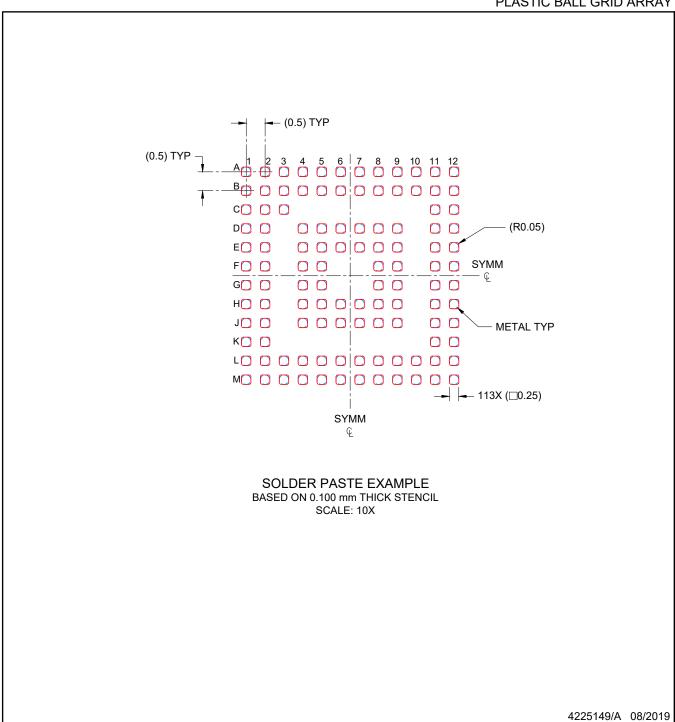

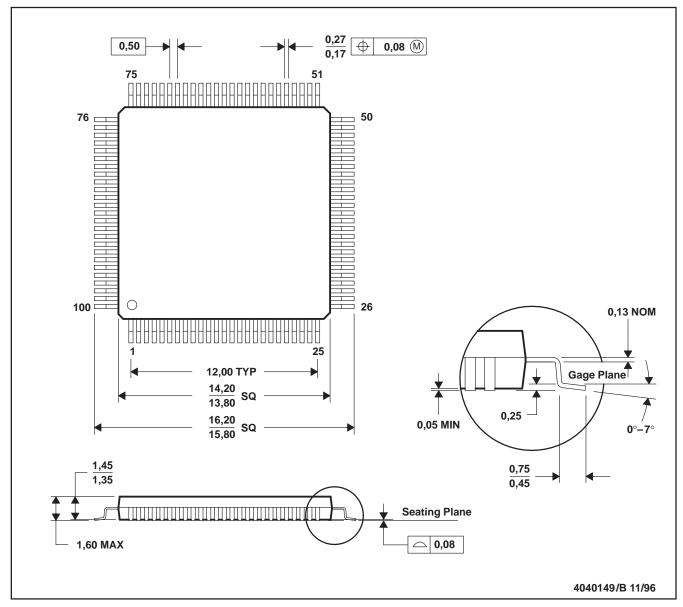

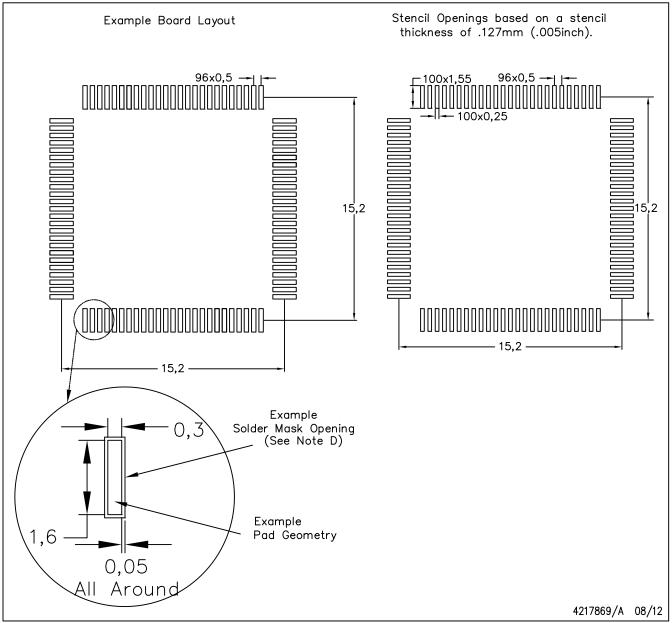

- 可采用 100 引脚 LQFP 和 113 引脚 Microstar Junior™ BGA 封装

- 器件比较汇总了可用的产品系列成员

### 2 应用

- 模拟传感器系统

- 数字传感器系统

- 手持式仪表

- 医疗诊断仪表

- 手持式工业测试仪

- 测量设备

## 3 说明

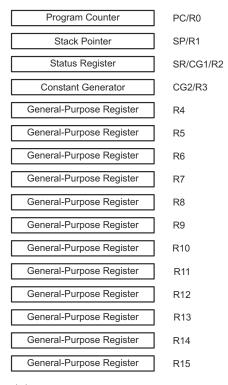

德州仪器 (TI) MSP430FG662x 和 MSP430FG642x 微控制器 (MCU) 属于 MSP430 计量和监控产品系列。该架构和集成外设与五种低功耗模式相结合并经过优化,可在便携式和电池供电测量应用中延长电池寿命。该器件具有一个强大的 16 位 RISC CPU、16 位寄存器和有助于实现出色编码效率的常数发生器。数控振荡器 (DCO) 可以让器件在不到 5µs 的时间内从低功耗模式唤醒至激活模式。

MSP430FG662x MCU 面向小型信号监控应用、包括一个 16 位  $\Sigma$ -  $\Delta$  ADC、双低功耗运算放大器、双 12 位 DAC、电压比较器、四个 USCI (两个 USCI\_A 模块和两个 USCI\_B 模块 )、四个 16 位计时器、一个硬件乘法器、一个 DMA 模块、一个 RTC 模块、一个 LCD 驱动器 (此驱动器在 100 引脚器件和 113 引脚器件中具有高达 160 段的集成对比度控制、集成式全速 USB、辅助电源系统、高达 128KB 闪存、10KB SRAM 和 73 个 I/O 引脚 )。

MSP430FG642x MCU 面向小型信号监控应用、包括一个 16 位  $\Sigma$ -  $\Delta$  ADC、双低功耗运算放大器、双 12 位 DAC、电压比较器、四个 USCI (两个 USCI\_A 模块和两个 USCI\_B 模块 )、四个 16 位计时器、一个硬件乘法器、一个 DMA 模块、一个 RTC 模块、一个 LCD 驱动器 (此驱动器在 100 引脚器件和 113 引脚器件中具有高达 160 段的集成对比度控制、辅助电源系统、高达 128KB 闪存、10KB SRAM 和 73 个 I/O 引脚 )。

这些微控制器的典型应用包括小信号监控应用,例如手持式测试和测量设备、现场变送器和血糖仪。这些微控制器可通过高模拟集成降低总体系统成本,并通过低功耗运行实现较长的电池寿命。

MSP430FG662x 和 MSP430FG642x MCU 由一款广泛的硬件和软件生态系统提供支持,随附参考设计和代码示例,以便用户快速开展设计。开发套件包括 MSP-TS430PZ100AUSB 100 引脚目标开发板。TI 还提供免费的 MSP430Ware™ 软件,该软件以 Code Composer Studio™ IDE 桌面和云版本组件的形式提供(位于 TI Resource Explorer 中)。TI E2E™ 支持论坛还为 MSP430 MCU 提供广泛的在线配套资料、培训和在线支持。

有关完整的模块说明,请参阅《MSP430F5xx 和 MSP430F6xx 系列用户指南》。

#### 器件信息

| 器件型号 <sup>(1)</sup>             | 封装                          | 封装尺寸 <sup>(2)</sup> |

|---------------------------------|-----------------------------|---------------------|

| MSP430FG6626IPZ                 | PZ (100)                    | 14mm x 14mm         |

| MSP430FG6626IZCA                | nFBGA (113)                 | 7mm × 7mm           |

| MSP430FG6626IZQW <sup>(3)</sup> | MicroStar Junior™ BGA (113) | 7mm × 7mm           |

- (1) 如需获得所有可用器件的全新器件、封装和订购信息,请参阅*封装选项附录*(节 12)或浏览 TI 网站www.ti.com。

- (2) 这里显示的尺寸为近似值。若要获得包含误差值的封装尺寸,请参阅节 12 中的机械数据。

- (3) 采用 ZQW (MicroStar Junior BGA) 封装的所有可订购器件型号均已更改为最后可采购期限的状态。 有关此状态的详细信息,请访问产品生命周期页面。

## 4 功能方框图

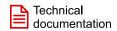

图 4-1 展示了 MSP430FG6626 和 MSP430FG6625 器件的功能方框图。

图 4-1. 功能方框图 - MSP430FG6626 和 MSP430FG6625

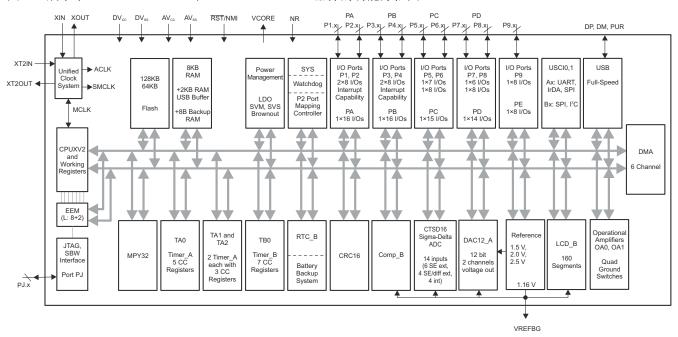

图 4-2 展示了 MSP430FG6426 和 MSP430FG6425 器件的功能方框图。

图 4-2. 功能方框图 - MSP430FG6426 和 MSP430FG6425

## **Table of Contents**

| 1 特性                                                          | 9.5 Interrupt               |

|---------------------------------------------------------------|-----------------------------|

| 2 应用                                                          |                             |

| 3 说明                                                          | 0 7 LIA DT D0               |

| 4 功能方框图                                                       | 0 0 IT4 0 0                 |

| 5 Revision History                                            |                             |

| 6 Device Comparison                                           | 9.10 RAM                    |

| 6.1 Related Products                                          | <sub>7</sub> 9.11 Backup    |

| 7 Terminal Configuration and Functions                        | 9.12 Periphe                |

| 7.1 Pin Diagrams                                              | 9.13 Input/O                |

| 7.2 Pin Attributes1                                           | 9.14 Device I               |

| 7.3 Signal Descriptions1                                      | 9.15 Memory                 |

| 7.4 Pin Multiplexing2                                         | <sub>7</sub> 9.16 Identific |

| 7.5 Buffer Type2                                              | 7 10 Application            |

| 7.6 Connection of Unused Pins2                                | 3 10.1 Device               |

| 8 Specifications2                                             | 10.2 Periphe                |

| 8.1 Absolute Maximum Ratings2                                 | Information                 |

| 8.2 ESD Ratings2                                              | 11 Device and               |

| 8.3 Recommended Operating Conditions2                         | 11.1 Getting                |

| 8.4 Active Mode Supply Current Into V <sub>CC</sub> Excluding | 11.2 Device I               |

| External Current3                                             | 1 11.3 Tools an             |

| 8.5 Low-Power Mode Supply Currents (Into V <sub>CC</sub> )    | 11.4 Docume                 |

| Excluding External Current3                                   | 2 11.5 Related              |

| 8.6 Low-Power Mode With LCD Supply Currents                   | 11.6 支持资源                   |

| (Into V <sub>CC</sub> ) Excluding External Current3           | 3 11.7 Tradema              |

| 8.7 Thermal Resistance Characteristics3                       |                             |

| 8.8 Timing and Switching Characteristics3                     |                             |

| 9 Detailed Description7                                       |                             |

| 9.1 Overview7                                                 |                             |

| 9.2 CPU                                                       |                             |

| 9.3 Instruction Set7                                          | -                           |

| 9.4 Operating Modes8                                          | )                           |

| 9.5 Interrupt vector Addresses                  | 81  |

|-------------------------------------------------|-----|

| 9.6 USB BSL                                     | 82  |

| 9.7 UART BSL                                    | 82  |

| 9.8 JTAG Operation                              |     |

| 9.9 Flash Memory                                | 83  |

| 9.10 RAM                                        |     |

| 9.11 Backup RAM                                 | 84  |

| 9.12 Peripherals                                | 84  |

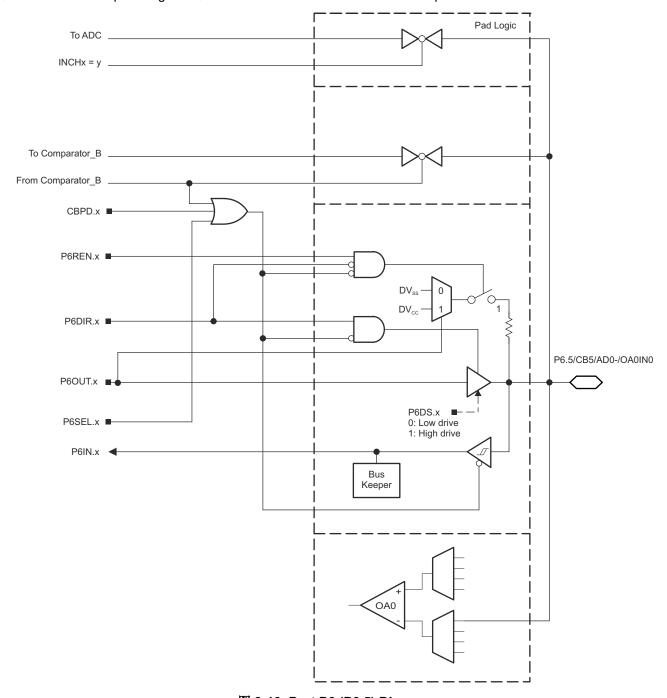

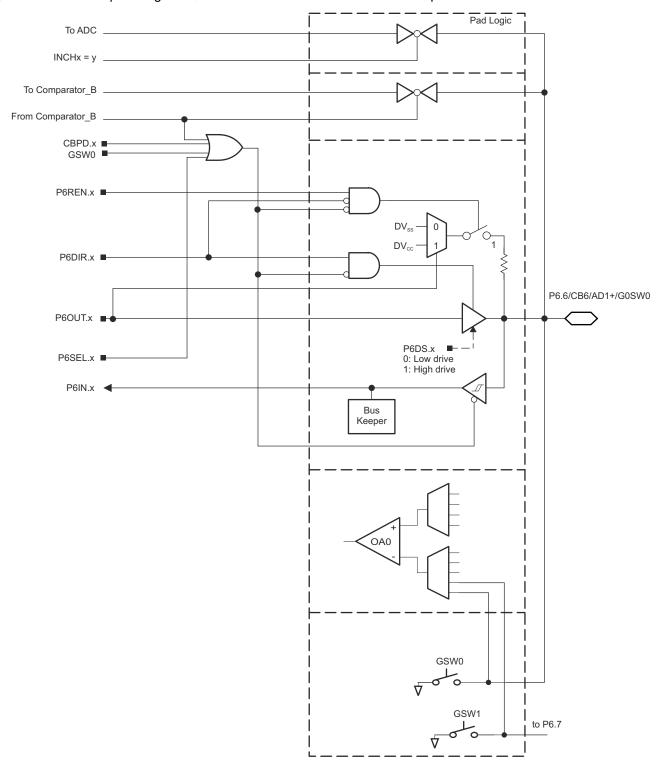

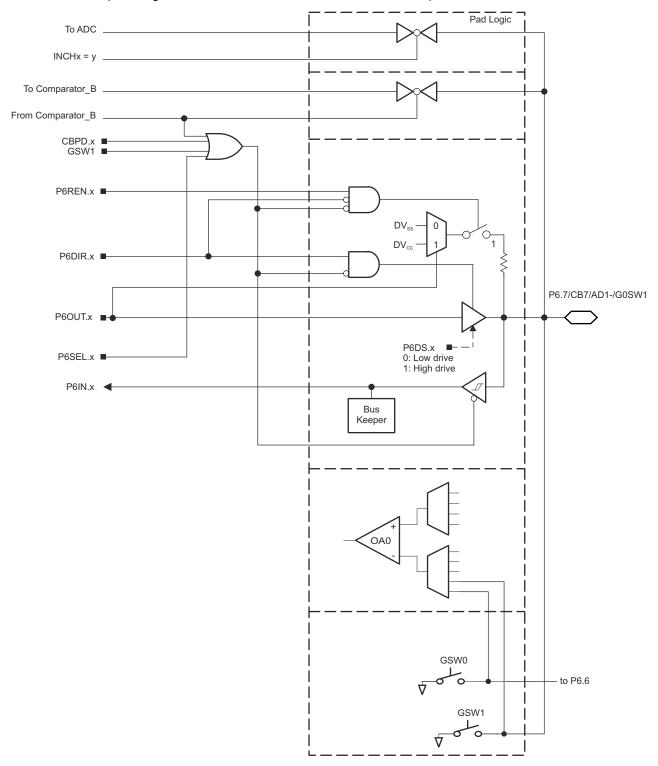

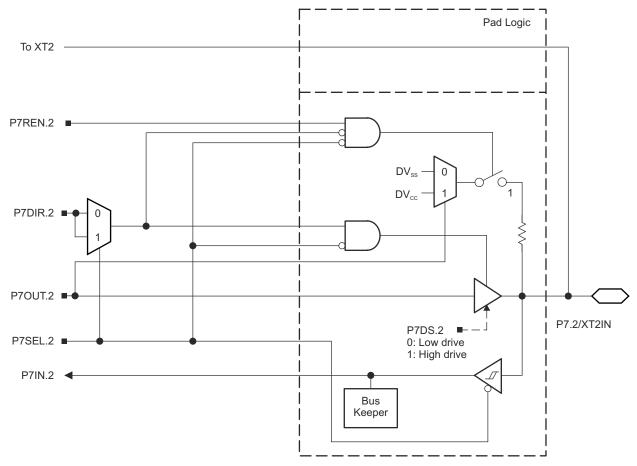

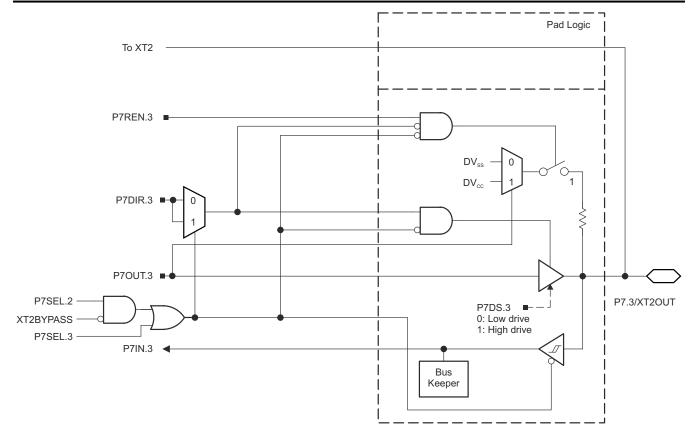

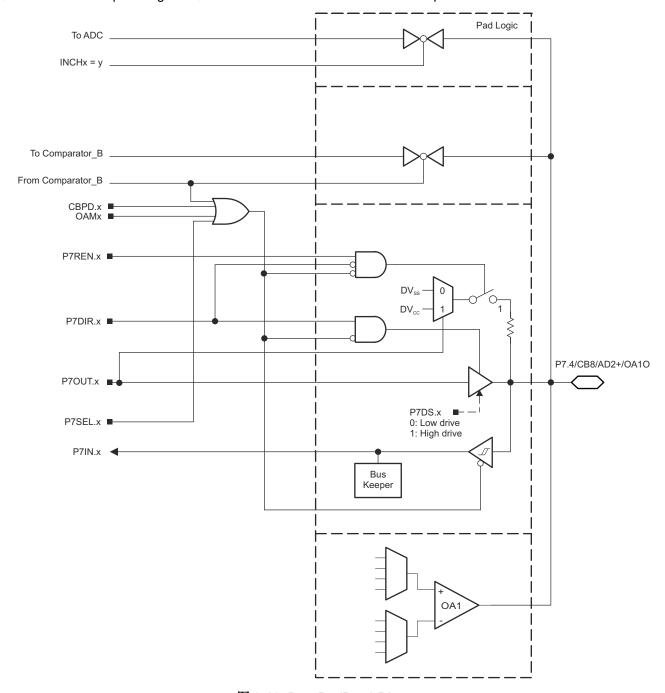

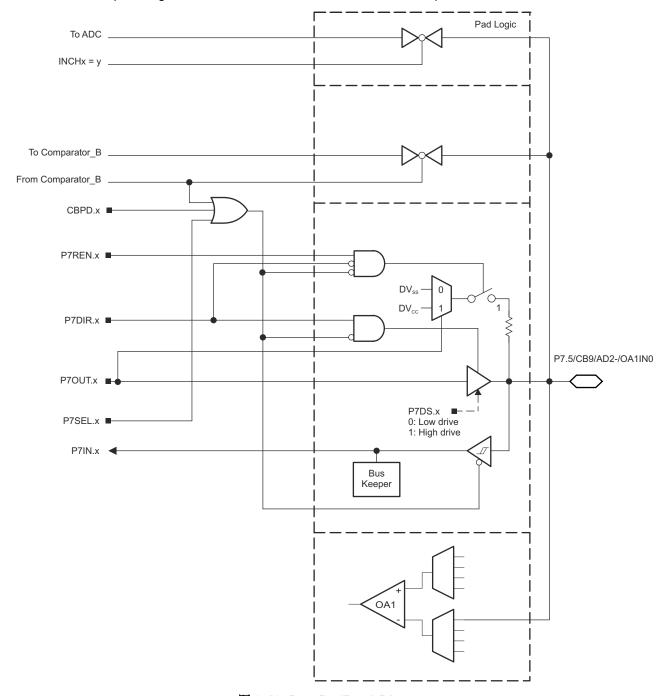

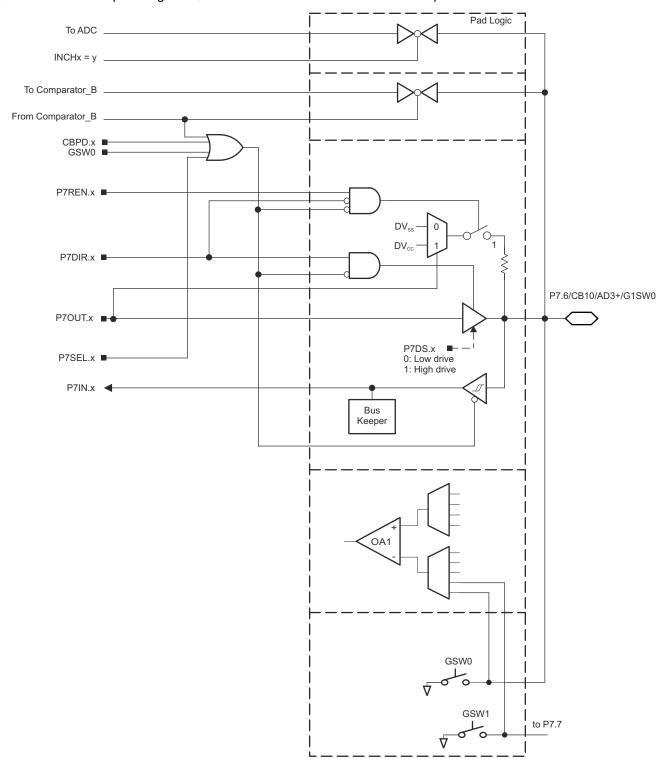

| 9.13 Input/Output Diagrams                      | 98  |

| 9.14 Device Descriptors                         | 138 |

| 9.15 Memory                                     | 138 |

| 9.16 Identification                             |     |

| 0 Applications, Implementation, and Layout      |     |

| 10.1 Device Connection and Layout Fundamentals. | 157 |

| 10.2 Peripheral- and Interface-Specific Design  |     |

| Information                                     |     |

| 1 Device and Documentation Support              | 171 |

| 11.1 Getting Started                            |     |

| 11.2 Device Nomenclature                        |     |

| 11.3 Tools and Software                         |     |

| 11.4 Documentation Support                      |     |

| 11.5 Related Links                              |     |

| 11.6 支持资源                                       |     |

| 11.7 Trademarks                                 |     |

| 11.8 静电放电警告                                     | 176 |

| 11.9 Export Control Notice                      | 176 |

| 11.10 术语表                                       | 177 |

| 2 Mechanical, Packaging, and Orderable          |     |

| Information                                     | 178 |

| 12.1 Packaging Information                      | 178 |

| 2 <del>-</del>                                  |     |

# **5 Revision History**

注:以前版本的页码可能与当前版本的页码不同

Changes from revision A to revision B

| C | hanges from September 27, 2018 to September 11, 2020                                                                                                                                                                          | Page           |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| • | 更新了整个文档中的章节、表格、图和交叉参考的编号                                                                                                                                                                                                      | 1              |

| • | 更新了 节 <b>1</b> <i>特性</i>                                                                                                                                                                                                      | 1              |

| • | 通篇增加了 nFBGA 封装 (ZCA) 信息                                                                                                                                                                                                       | 2              |

| • | 在器件信息中添加了有关采用 ZQW 封装的所有可订购器件型号状态变化的注意事项                                                                                                                                                                                       | 2              |

| • | 更新了 节 <b>3</b> <i>说明</i>                                                                                                                                                                                                      | 2              |

| • | Corrected the signal name and description (changed DVCC to AVCC) on pin 16 (or H1, G2) in 表 7-2, S Descriptions                                                                                                               | _              |

| • | Changed the MAX value of the I <sub>ERASE</sub> and I <sub>MERASE</sub> , I <sub>BANK</sub> parameters in 节 8.8.19.1, <i>Flash Memory</i>                                                                                     |                |

| C | hanges from initial release to revision A                                                                                                                                                                                     |                |

| C | hanges from May 22, 2015 to September 26, 2018                                                                                                                                                                                | Page           |

| • | Added 节 6.1, Related Products                                                                                                                                                                                                 | <mark>7</mark> |

| • | Added typical conditions statements at the beginning of † 8, Specifications                                                                                                                                                   | 29             |

| • | Updated notes (1) and (2) and added note (3) in 节 8.8.4.1, Wake-up Times From Low-Power Modes at Reset                                                                                                                        |                |

|   | Removed duplicate symbol and removed note (5) on Ri <sub>(VREFBG)</sub> , Ri <sub>(VeREF+)</sub> parameter in † 8.8.13.4, <i>12</i>                                                                                           |                |

|   | DAC, Reference Input Specifications                                                                                                                                                                                           | 66             |

| • | Added "CBPWRMD = 00 or 01" to Test Conditions of the first row of the $t_{EN\_CMP}$ parameter; Added second row for $t_{EN\_CMP}$ with Test Conditions of "CBPWRMD = 10" and MAX value of 100 $\mu$ s in $\ddagger$ 8.8.16.1, |                |

|   | Comparator_B                                                                                                                                                                                                                  | 72             |

| • | Added 节 8.8.18, LDO-PWR (LDO Power System)                                                                                                                                                                                    |                |

| • | Throughout document, changed all instances of "bootstrap loader" to "bootloader"                                                                                                                                              |                |

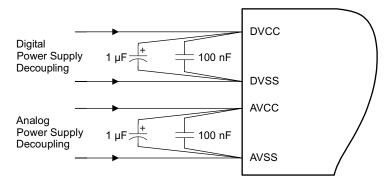

| • | Changed decoupling capacitor recommendation from "one 10 $\mu$ F and one 100 nF" to "one 1 $\mu$ F and one                                                                                                                    |                |

|   | 100 nF" for consistency with 节 10.1.1                                                                                                                                                                                         |                |

| • | Changed decoupling capacitor recommendation from "one 10 μF and one 100 nF" to "one 1 μF and one                                                                                                                              |                |

|   | 100 nF" for consistency with 节 10.1.1                                                                                                                                                                                         |                |

| • | Changed decoupling capacitor recommendation from "one 10 µF and one 100 nF" to "one 1 µF and one                                                                                                                              |                |

|   | 100 nF" for consistency with 节 10.1.1                                                                                                                                                                                         |                |

| • | Added 节 10.2.5, DAC12 Peripheral                                                                                                                                                                                              |                |

| • | Added 节 10.2.6, USB Module                                                                                                                                                                                                    |                |

| • | Added 节 10.2.7, LDO Module                                                                                                                                                                                                    |                |

| • | Replaced former section Development Tools Support with † 11.3, Tools and Software                                                                                                                                             | 173            |

| • | Changed format and added content to † 11.4, Documentation Support                                                                                                                                                             |                |

## **6 Device Comparison**

表 6-1 summarizes the available family members.

### 表 6-1. Device Comparison

| <b>DEVICE</b> <sup>(1)</sup> (2) | FLASH<br>(KB) | SRAM<br>(KB) <sup>(3)</sup> | Timer_A <sup>(4)</sup> | Timer_B <sup>(5)</sup> | USCI_A:<br>UART, IrDA,<br>SPI | USCI_B:<br>SPI, I <sup>2</sup> C | CTSD16<br>(Ch) <sup>(6)</sup> | DAC12_A<br>(Ch) | OA | Comp_B<br>(channels) | USB | I/Os | PACKAGE                       |

|----------------------------------|---------------|-----------------------------|------------------------|------------------------|-------------------------------|----------------------------------|-------------------------------|-----------------|----|----------------------|-----|------|-------------------------------|

| MSP430FG6626                     | 128           | 8 + 2                       | 5, 3, 3                | 7                      | 2                             | 2                                | 10 ext,<br>5 int              | 2               | 2  | 12                   | 1   | 73   | 100 PZ,<br>113 ZCA<br>113 ZQW |

| MSP430FG6625                     | 64            | 8 + 2                       | 5, 3, 3                | 7                      | 2                             | 2                                | 10 ext,<br>5 int              | 2               | 2  | 12                   | 1   | 73   | 100 PZ,<br>113 ZCA<br>113 ZQW |

| MSP430FG6426                     | 128           | 10                          | 5, 3, 3                | 7                      | 2                             | 2                                | 10 ext,<br>5 int              | 2               | 2  | 12                   | 0   | 73   | 100 PZ,<br>113 ZCA<br>113 ZQW |

| MSP430FG6425                     | 64            | 10                          | 5, 3, 3                | 7                      | 2                             | 2                                | 10 ext,<br>5 int              | 2               | 2  | 12                   | 0   | 73   | 100 PZ,<br>113 ZCA<br>113 ZQW |

- (1) For the most current package and ordering information, see the Package Option Addendum in † 12, or see the TI website at www.ti.com.

- (2) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/packaging.

- (3) The additional 2KB of USB SRAM that is listed can be used as general-purpose SRAM when USB is not in use.

- (4) Each number in the sequence represents an instantiation of Timer\_A with its associated number of capture compare registers and PWM output generators available. For example, a number sequence of 3, 5 would represent two instantiations of Timer\_A, the first instantiation having 3 and the second instantiation having 5 capture compare registers and PWM output generators, respectively.

- (5) Each number in the sequence represents an instantiation of Timer\_B with its associated number of capture compare registers and PWM output generators available. For example, a number sequence of 3, 5 would represent two instantiations of Timer\_B, the first instantiation having 3 and the second instantiation having 5 capture compare registers and PWM output generators, respectively.

- (6) ADC inputs consist of a mix of single ended and differential. See the pinning for available input pairs and types.

#### **6.1 Related Products**

For information about other devices in this family of products or related products, see the following links.

#### Products for TI microcontrollers

TI's low-power and high-performance MCUs, with wired and wireless connectivity options, are optimized for a broad range of applications.

### Products for MSP430 ultra-low-power microcontrollers

One platform. One ecosystem. Endless possibilities. Enabling the connected world with innovations in ultra-low-power microcontrollers with advanced peripherals for precise sensing and measurement.

### Companion products for MSP430FG6626

Review products that are frequently purchased or used with this product.

### Reference designs for MSP430FG6626

Find reference designs that leverage the best in TI technology to solve your system-level challenges.

# 7 Terminal Configuration and Functions

## 7.1 Pin Diagrams

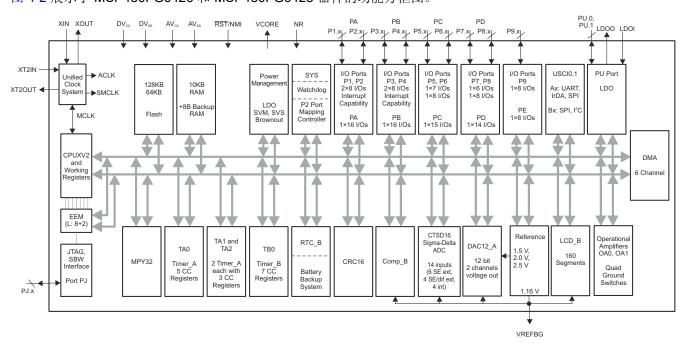

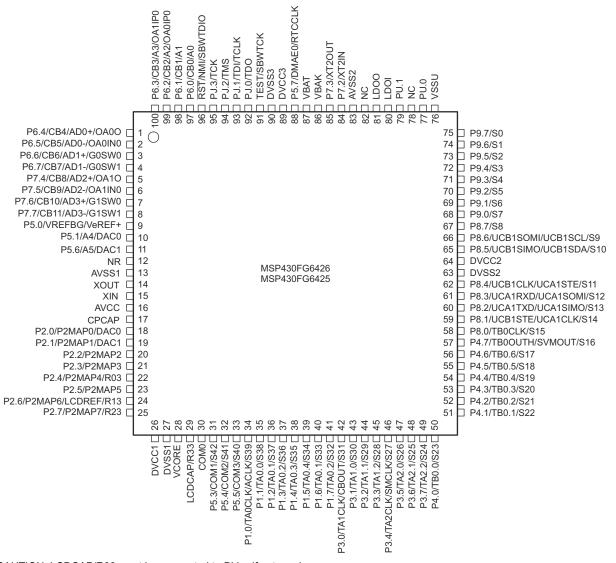

7-1 shows the pinout for the MSP430FG6626 and MSP430FG6625 devices in the 100-pin PZ package.

CAUTION: LCDCAP/R33 must be connected to DV<sub>SS</sub> if not used.

图 7-1. 100-Pin PZ Package (Top View), MSP430FG6626IPZ, MSP430FG6625IPZ

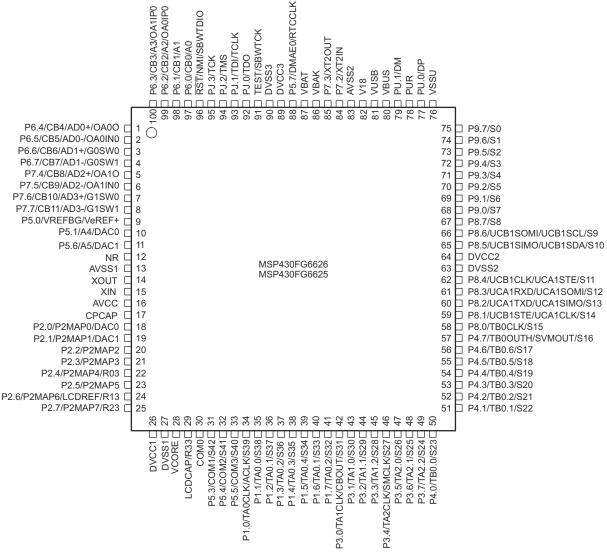

☑ 7-2 shows the pinout for the MSP430FG6426 and MSP430FG6425 devices in the 100-pin PZ package.

A. CAUTION: LCDCAP/R33 must be connected to DV<sub>SS</sub> if not used.

图 7-2. 100-Pin PZ Package (Top View), MSP430FG6426IPZ, MSP430FG6425IPZ

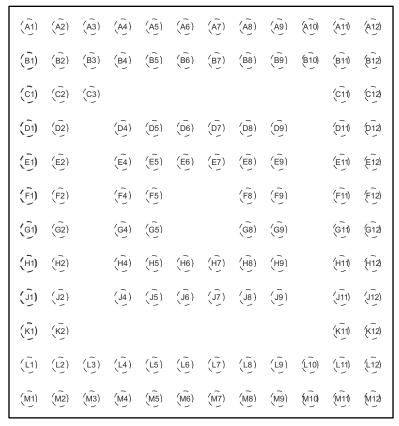

图 7-3 shows the pinout for the 113-pin ZCA or ZQW package.

NOTE: For terminal assignments, see 节 7.3.

图 7-3. 113-Pin ZCA or ZQW Package (Top View), MSP430FG6626IZCA, MSP430FG6625IZCA, MSP430FG6426IZCA, MSP430FG6625IZCA, MSP430FG6626IZQW, MSP430FG6625IZQW, MSP430FG6425IZQW, MSP430FG6425IZQW

### 7.2 Pin Attributes

表 7-1 describes the attributes of the pins.

表 7-1. Pin Attributes

| PIN NO. |          |                     | 7-1. PIII Attribu |                 | POWER                 | RESET STATE      |

|---------|----------|---------------------|-------------------|-----------------|-----------------------|------------------|

| PZ      | ZCA, ZQW | SIGNAL NAME (1) (2) | SIGNAL TYPE (3)   | BUFFER TYPE (4) | SOURCE <sup>(5)</sup> | AFTER BOR (6) (7 |

|         |          | P6.4                | I/O               | LVCMOS          | DVCC                  | OFF              |

| 1       | A1       | CB4                 | I                 | Analog          | DVCC                  | N/A              |

| '       | Δ'       | AD0+                | I                 | Analog          | DVCC                  | N/A              |

|         |          | OA0O                | 0                 | Analog          | DVCC                  | N/A              |

|         |          | P6.5                | I/O               | LVCMOS          | DVCC                  | OFF              |

| 2       | B2       | CB5                 | I                 | Analog          | DVCC                  | N/A              |

| 2       | DZ       | AD0-                | I                 | Analog          | DVCC                  | N/A              |

|         |          | OA0IN0              | I                 | Analog          | DVCC                  | N/A              |

|         |          | P6.6                | I/O               | LVCMOS          | DVCC                  | OFF              |

| 2       | D4       | CB6                 | I                 | Analog          | DVCC                  | N/A              |

| 3       | B1       | AD1+                | I                 | Analog          | DVCC                  | N/A              |

|         |          | G0SW0               | I                 | Analog          | DVCC                  | N/A              |

|         |          | P6.7                | I/O               | LVCMOS          | DVCC                  | OFF              |

|         | 00       | CB7                 | I                 | Analog          | DVCC                  | N/A              |

| 4       | C3       | AD1-                | I                 | Analog          | DVCC                  | N/A              |

|         |          | G0SW1               | I                 | Analog          | DVCC                  | N/A              |

|         |          | P7.4                | I/O               | LVCMOS          | DVCC                  | OFF              |

| _       | C2       | CB8                 | I                 | Analog          | DVCC                  | N/A              |

| 5       |          | AD2+                | I                 | Analog          | DVCC                  | N/A              |

|         |          | OA10                | 0                 | Analog          | DVCC                  | N/A              |

|         | C1       | P7.5                | I/O               | LVCMOS          | DVCC                  | OFF              |

| _       |          | СВ9                 | I                 | Analog          | DVCC                  | N/A              |

| 6       |          | AD2-                | I                 | Analog          | DVCC                  | N/A              |

|         |          | OA1IN0              | I                 | Analog          | DVCC                  | N/A              |

|         |          | P7.6                | I/O               | LVCMOS          | DVCC                  | OFF              |

|         |          | CB10                | I                 | Analog          | DVCC                  | N/A              |

| 7       | D4       | AD3+                | I                 | Analog          | DVCC                  | N/A              |

|         |          | G1SW0               | I                 | Analog          | DVCC                  | N/A              |

|         |          | P7.7                | I/O               | LVCMOS          | DVCC                  | OFF              |

|         |          | CB11                | I                 | Analog          | DVCC                  | N/A              |

| 8       | D2       | AD3-                | I                 | Analog          | DVCC                  | N/A              |

|         |          | G1SW1               | I                 | Analog          | DVCC                  | N/A              |

|         |          | P5.0                | I/O               | LVCMOS          | DVCC                  | OFF              |

| 9       | D1       | VREFBG              | 0                 | Analog          | DVCC                  | N/A              |

|         |          | VeREF+              | I                 | Analog          | N/A                   | N/A              |

|         |          | P5.1                | I/O               | LVCMOS          | DVCC                  | OFF              |

| 10      | E4       | A4                  | I                 | Analog          | DVCC                  | N/A              |

| -       |          | DAC0                | 0                 | Analog          | DVCC                  | N/A              |

|         |          | P5.6                | I/O               | LVCMOS          | DVCC                  | OFF              |

| 11      | E2       | A5                  | I                 | Analog          | DVCC                  | N/A              |

|         | EZ       |                     |                   |                 |                       |                  |

| PIN NO. |          | SIGNAL NAME (1) (2) | SIGNAL TYPE (3) | BUFFER TYPE (4) | POWER                 | RESET STATE   |

|---------|----------|---------------------|-----------------|-----------------|-----------------------|---------------|

| PZ      | ZCA, ZQW | SIGNAL NAME (7)     | SIGNAL TIPE (7  | BOTTERTIFE      | SOURCE <sup>(5)</sup> | AFTER BOR (6) |

| 12      | E1       | NR                  | I               | Analog          | N/A                   | N/A           |

| 13      | F2       | AVSS1               | Р               | Power           | N/A                   | N/A           |

| 14      | F1       | XOUT                | 0               | Analog          | N/A                   | N/A           |

| 15      | G1       | XIN                 | I               | Analog          | N/A                   | N/A           |

| 16      | H1, G2   | AVCC                | Р               | Power           | N/A                   | N/A           |

| 17      | G4       | CPCAP               | I/O             | Analog          | DVCC                  | N/A           |

|         |          | P2.0                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 18      | H2       | P2MAP0              | I/O             | LVCMOS          | DVCC                  | N/A           |

|         |          | DAC0                | 0               | Analog          | DVCC                  | N/A           |

|         |          | P2.1                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 19      | J1       | P2MAP1              | I/O             | LVCMOS          | DVCC                  | N/A           |

|         |          | DAC1                | 0               | Analog          | DVCC                  | N/A           |

| 20      | 114      | P2.2                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 20      | H4       | P2MAP2              | I/O             | LVCMOS          | DVCC                  | N/A           |

| 04      | 10       | P2.3                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 21      | J2       | P2MAP3              | I/O             | LVCMOS          | DVCC                  | N/A           |

|         |          | P2.4                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 22      | K1       | P2MAP4              | I/O             | LVCMOS          | DVCC                  | N/A           |

|         |          | R03                 | I/O             | Analog          | DVCC                  | N/A           |

| 00      | K2       | P2.5                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 23      |          | P2MAP5              | I/O             | LVCMOS          | DVCC                  | N/A           |

|         | 1.0      | P2.6                | I/O             | LVCMOS          | DVCC                  | OFF           |

| •       |          | P2MAP6              | I/O             | LVCMOS          | DVCC                  | N/A           |

| 24      | L2       | LCDREF              | I               | Analog          | N/A                   | N/A           |

|         |          | R13                 | I/O             | Analog          | DVCC                  | N/A           |

|         |          | P2.7                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 25      | L3       | P2MAP7              | I/O             | LVCMOS          | DVCC                  | N/A           |

|         |          | R23                 | I/O             | Analog          | DVCC                  | N/A           |

| 26      | L1       | DVCC1               | Р               | Power           | N/A                   | N/A           |

| 27      | M1       | DVSS1               | Р               | Power           | N/A                   | N/A           |

| 28      | M2       | VCORE               | Р               | Power           | DVCC                  | N/A           |

|         |          | LCDCAP              | I/O             | Analog          | DVCC                  | N/A           |

| 29      | M3       | R33                 | I/O             | Analog          | DVCC                  | N/A           |

| 30      | J4       | COM0                | 0               | Analog          | DVCC                  | N/A           |

|         |          | P5.3                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 31      | L4       | COM1                | 0               | Analog          | DVCC                  | N/A           |

|         |          | S42                 | 0               | Analog          | DVCC                  | N/A           |

|         |          | P5.4                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 32      | M4       | COM2                | 0               | LVCMOS          | DVCC                  | N/A           |

|         |          | S41                 | 0               | Analog          | DVCC                  | N/A           |

|         |          | P5.5                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 33      | J5       | COM3                | I/O             | LVCMOS          | DVCC                  | N/A           |

|         |          | S40                 | 0               | Analog          | DVCC                  | N/A           |

| PIN NO. |          | 010NAL NAME (1) (2) | CIONAL TYPE (3) |                 | POWER                 | RESET STATE      |

|---------|----------|---------------------|-----------------|-----------------|-----------------------|------------------|

| PZ      | ZCA, ZQW | SIGNAL NAME (1) (2) | SIGNAL TYPE     | BUFFER TYPE (4) | SOURCE <sup>(5)</sup> | AFTER BOR (6) (7 |

|         |          | P1.0                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 34      | L5       | TA0CLK              | I               | LVCMOS          | DVCC                  | N/A              |

| 34      |          | ACLK                | 0               | LVCMOS          | DVCC                  | N/A              |

|         |          | S39                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P1.1                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 25      | M5       | TA0.0               | I/O             | LVCMOS          | DVCC                  | N/A              |

| 35      | CIVI     | BSLTX               | 0               | LVCMOS          | DVCC                  | N/A              |

|         |          | S38                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P1.2                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 20      | 10       | TA0.1               | I/O             | LVCMOS          | DVCC                  | N/A              |

| 36      | J6       | BSLRX               | I               | LVCMOS          | DVCC                  | N/A              |

|         |          | S37                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P1.3                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 37      | H6       | TA0.2               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S36                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P1.4                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 38      | M6       | TA0.3               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S35                 | 0               | Analog          | DVCC                  | N/A              |

|         | L6       | P1.5                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 39      |          | TA0.4               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S34                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P1.6                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 40      | J7       | TA0.1               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S33                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P1.7                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 41      | M7       | TA0.2               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S32                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P3.0                | I/O             | LVCMOS          | DVCC                  | OFF              |

|         |          | TA1CLK              | I               | LVCMOS          | DVCC                  | N/A              |

| 42      | L7       | CBOUT               | 0               | LVCMOS          | DVCC                  | N/A              |

|         |          | S31                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P3.1                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 43      | H7       | TA1.0               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S30                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P3.2                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 44      | M8       | TA1.1               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S29                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P3.3                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 45      | L8       | TA1.2               | I/O             | LVCMOS          | DVCC                  | N/A              |

|         |          | S28                 | 0               | Analog          | DVCC                  | N/A              |

|         |          | P3.4                | I/O             | LVCMOS          | DVCC                  | OFF              |

|         |          | TA2CLK              | I               | LVCMOS          | DVCC                  | N/A              |

| 46      | J8       | SMCLK               | 0               | LVCMOS          | DVCC                  | N/A              |

|         |          | S27                 | 0               | Analog          | DVCC                  | N/A              |

| PII | N NO.    |                     | CIONAL TYPE (3) |                 | POWER                 | RESET STATE      |

|-----|----------|---------------------|-----------------|-----------------|-----------------------|------------------|

| PZ  | ZCA, ZQW | SIGNAL NAME (1) (2) | SIGNAL TYPE     | BUFFER TYPE (4) | SOURCE <sup>(5)</sup> | AFTER BOR (6) (7 |

|     |          | P3.5                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 47  | M9       | TA2.0               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S26                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P3.6                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 48  | L9       | TA2.1               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S25                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P3.7                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 49  | M10      | TA2.2               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S24                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P4.0                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 50  | J9       | TB0.0               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S23                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P4.1                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 51  | M11      | TB0.1               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S22                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P4.2                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 52  | L10      | TB0.2               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S21                 | 0               | Analog          | DVCC                  | N/A              |

|     | M12      | P4.3                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 53  |          | TB0.3               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S20                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P4.4                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 54  | L12      | TB0.4               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S19                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P4.5                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 55  | L11      | TB0.5               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S18                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P4.6                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 56  | K11      | TB0.6               | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S17                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P4.7                | I/O             | LVCMOS          | DVCC                  | OFF              |

|     | 1440     | TB0OUTH             | I               | LVCMOS          | DVCC                  | N/A              |

| 57  | K12      | SVMOUT              | 0               | LVCMOS          | DVCC                  | N/A              |

|     |          | S16                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P8.0                | I/O             | LVCMOS          | DVCC                  | OFF              |

| 58  | J11      | TB0CLK              | I               | LVCMOS          | DVCC                  | N/A              |

|     |          | S15                 | 0               | Analog          | DVCC                  | N/A              |

|     |          | P8.1                | I/O             | LVCMOS          | DVCC                  | OFF              |

|     |          | UCB1STE             | I/O             | LVCMOS          | DVCC                  | N/A              |

| 59  | J12      | UCA1CLK             | I/O             | LVCMOS          | DVCC                  | N/A              |

|     |          | S14                 | 0               | Analog          | DVCC                  | N/A              |

| PII  | NO.      | SIGNAL NAME (1) (2) | SIGNAL TYPE (3) | BUFFER TYPE (4) | POWER                 | RESET STATE   |

|------|----------|---------------------|-----------------|-----------------|-----------------------|---------------|

| PZ   | ZCA, ZQW | SIGNAL NAME (*/ (=/ | SIGNAL TIPE (9) | BUFFER TIPE (1) | SOURCE <sup>(5)</sup> | AFTER BOR (6) |

|      |          | P8.2                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 60   | H11      | UCA1TXD             | 0               | LVCMOS          | DVCC                  | N/A           |

| 00   | 1111     | UCA1SIMO            | I/O             | LVCMOS          | DVCC                  | N/A           |

|      |          | S13                 | 0               | Analog          | DVCC                  | N/A           |

|      |          | P8.3                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 61   | H12      | UCA1RXD             | 1               | LVCMOS          | DVCC                  | N/A           |

| 01   | 1112     | UCA1SOMI            | I/O             | LVCMOS          | DVCC                  | N/A           |

|      |          | S12                 | 0               | Analog          | DVCC                  | N/A           |

|      |          | P8.4                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 62   | G11      | UCB1CLK             | I/O             | LVCMOS          | DVCC                  | N/A           |

| 02   | GII      | UCA1STE             | I/O             | LVCMOS          | DVCC                  | N/A           |

|      |          | S11                 | 0               | Analog          | DVCC                  | N/A           |

| 63   | G12      | DVSS2               | Р               | Power           | N/A                   | N/A           |

| 64   | F12      | DVCC2               | Р               | Power           | N/A                   | N/A           |

|      |          | P8.5                | I/O             | LVCMOS          | DVCC                  | OFF           |

| G.E. | F14      | UCB1SIMO            | I/O             | LVCMOS          | DVCC                  | N/A           |

| 65   | F11      | UCB1SDA             | I/O             | LVCMOS          | DVCC                  | N/A           |

|      |          | S10                 | 0               | Analog          | DVCC                  | N/A           |

|      | G9       | P8.6                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 00   |          | UCB1SOMI            | I/O             | LVCMOS          | DVCC                  | N/A           |

| 66   |          | UCB1SCL             | I/O             | LVCMOS          | DVCC                  | N/A           |

|      |          | S9                  | 0               | Analog          | DVCC                  | N/A           |

|      | E12      | P8.7                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 67   |          | S8                  | 0               | Analog          | DVCC                  | N/A           |

|      |          | P9.0                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 68   | E11      | S7                  | 0               | Analog          | DVCC                  | N/A           |

|      |          | P9.1                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 69   | F9       | S6                  | 0               | Analog          | DVCC                  | N/A           |

|      |          | P9.2                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 70   | D12      | S5                  | 0               | Analog          | DVCC                  | N/A           |

|      |          | P9.3                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 71   | D11      | S4                  | 0               | Analog          | DVCC                  | N/A           |

|      |          | P9.4                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 72   | E9       | S3                  | 0               | Analog          | DVCC                  | N/A           |

|      |          | P9.5                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 73   | C12      | S2                  | 0               | Analog          | DVCC                  | N/A           |

|      | + -      | P9.6                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 74   | C11      | S1                  | 0               | Analog          | DVCC                  | N/A           |

|      |          | P9.7                | I/O             | LVCMOS          | DVCC                  | OFF           |

| 75   | D9       | S0                  | 0               | Analog          | DVCC                  | N/A           |

| 76   | B11, B12 | VSSU                | P               | Power           | N/A                   | N/A           |

|      |          | PU.0                | I/O             | HVCMOS          | VBUS                  | HiZ           |

| 77   | A12      | DP                  | I/O             | HVCMOS          | VBUS                  | N/A           |

| PIN NO. |          | SIGNAL NAME (1) (2)  | SIGNAL TYPE (3) | BUFFER TYPE (4)       | POWER                 | RESET STATE                |

|---------|----------|----------------------|-----------------|-----------------------|-----------------------|----------------------------|

| PZ      | ZCA, ZQW | SIGNAL NAME (** (=*) | SIGNAL TIPE     | BUFFER TIPE (1)       | SOURCE <sup>(5)</sup> | AFTER BOR (6) (7)          |

| 78      | B10      | PUR (FG662x only)    | I/O             | HVCMOS/open-<br>drain | VBUS                  | HiZ                        |

|         |          | NC (FG642x only)     | I/O             | N/A                   | N/A                   | N/A                        |

| 79      | A11      | PU.1                 | I/O             | HVCMOS                | VBUS                  | HiZ                        |

| 19      | All      | DM                   | I/O             | HVCMOS                | VBUS                  | N/A                        |

| 80      | A10      | VBUS                 | ı               | Power                 | N/A                   | N/A                        |

| 60      | Alu      | LDOI                 | ı               | Analog                | External              | N/A                        |

| 81      | A9       | VUSB                 | 0               | Power                 | N/A                   | N/A                        |

| 01      | As       | LDOO                 | 0               | Analog                | VBUS                  | N/A                        |

| 82      | В9       | V18 (FG662x only)    | 0               | Power                 | N/A                   | N/A                        |

| 02      | B9       | NC (FG642x only)     | -               | N/A                   | N/A                   | N/A                        |

| 83      | A8       | AVSS2                | Р               | Power                 | N/A                   | N/A                        |

| 0.1     | DO       | P7.2                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 84      | B8       | XT2IN                | ı               | Analog                | DVCC                  | N/A                        |

| 85      | B7       | P7.3                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 65      | D/       | XT2OUT               | 0               | Analog                | DVCC                  | N/A                        |

| 86      | A7       | VBAK                 | I/O             | Analog                | N/A                   | N/A                        |

| 87      | D8       | VBAT                 | Р               | Power                 | N/A                   | N/A                        |

|         |          | P5.7                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 88      | D7       | DMAE0                | ı               | LVCMOS                | DVCC                  | N/A                        |

|         |          | RTCCLK               | 0               | LVCMOS                | DVCC                  | N/A                        |

| 89      | A6       | DVCC3                | Р               | Power                 | N/A                   | N/A                        |

| 90      | A5       | DVSS3                | Р               | Power                 | N/A                   | N/A                        |

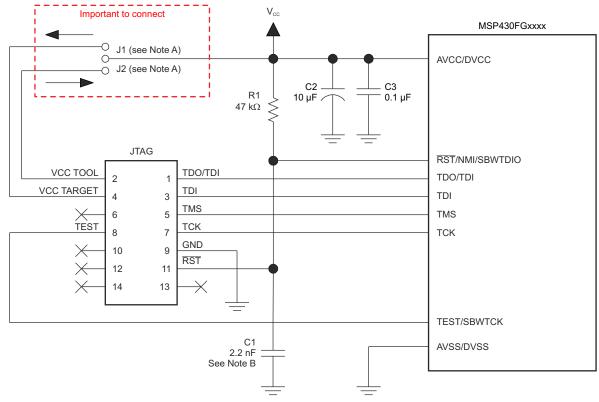

| 91      | B6       | TEST                 | 1               | LVCMOS                | DVCC                  | No Emu: PD<br>Emu: PD      |

|         |          | SBWTCK               | I               | LVCMOS                | DVCC                  | N/A                        |

|         |          | PJ.0                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 92      | B5       | TDO                  | 0               | LVCMOS                | DVCC                  | No Emu: OFF<br>Emu: DRIVE0 |

|         |          | PJ.1                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 93      | A4       | TDI                  | 1               | LVCMOS                | DVCC                  | No Emu: OFF<br>Emu: PU     |

|         |          | TCLK                 | 1               | LVCMOS                | DVCC                  | No Emu: OFF<br>Emu: OFF    |

|         |          | PJ.2                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 94      | E7       | TMS                  | I               | LVCMOS                | DVCC                  | No Emu: OFF<br>Emu: PU     |

|         |          | PJ.3                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 95      | D6       | тск                  | I               | LVCMOS                | DVCC                  | No Emu: OFF<br>Emu: PU     |

|         |          | RST                  | I/O             | LVCMOS                | DVCC                  | PU                         |

| 96      | A3       | NMI                  | I               | LVCMOS                | DVCC                  | N/A                        |

|         |          | SBWTDIO              | I/O             | LVCMOS                | DVCC                  | PU                         |

|         |          | P6.0                 | I/O             | LVCMOS                | DVCC                  | OFF                        |

| 97      | B4       | CB0                  | ı               | Analog                | DVCC                  | N/A                        |

|         |          | A0                   | I               | Analog                | DVCC                  | N/A                        |

| PIN | NO.                                                 | SIGNAL NAME (1) (2) | SIGNAL TYPE (3)                                     | BUFFER TYPE (4) | POWER                 | RESET STATE       |  |

|-----|-----------------------------------------------------|---------------------|-----------------------------------------------------|-----------------|-----------------------|-------------------|--|

| PZ  | ZCA, ZQW                                            | SIGNAL NAME (17 (2) | SIGNAL NAME (1) (2) SIGNAL TYPE (4) BUFFER TYPE (4) |                 | SOURCE <sup>(5)</sup> | AFTER BOR (6) (7) |  |

|     |                                                     | P6.1                | I/O                                                 | LVCMOS          | DVCC                  | OFF               |  |

| 98  | В3                                                  | CB1                 | I                                                   | Analog          | DVCC                  | N/A               |  |

|     |                                                     | A1                  | I                                                   | Analog          | DVCC                  | N/A               |  |

|     |                                                     | P6.2                | I/O                                                 | LVCMOS          | DVCC                  | OFF               |  |

| 99  | A2                                                  | CB2                 | I                                                   | Analog          | DVCC                  | N/A               |  |

| 99  |                                                     | A2                  | I                                                   | Analog          | DVCC                  | N/A               |  |

|     |                                                     | OA0IP0              | I                                                   | Analog          | DVCC                  | N/A               |  |

|     |                                                     | P6.3                | I/O                                                 | LVCMOS          | DVCC                  | OFF               |  |

| 100 | D5                                                  | CB3                 | I                                                   | Analog          | DVCC                  | N/A               |  |

| 100 | D3                                                  | A3                  | I                                                   | Analog          | DVCC                  | N/A               |  |

|     |                                                     | OA1IP0              | I                                                   | Analog          | DVCC                  | N/A               |  |

| N/A | E5, E6, E8,<br>F4, F5, F8,<br>G5, G8, H5,<br>H8, H9 | Reserved            | -                                                   | -               | -                     | -                 |  |

- (1) For each multiplexed pin, the signal that is listed first in this table is the reset default.

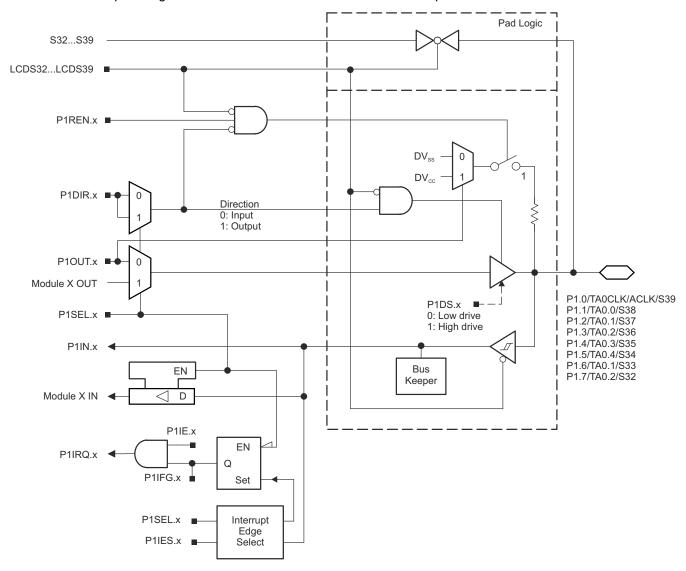

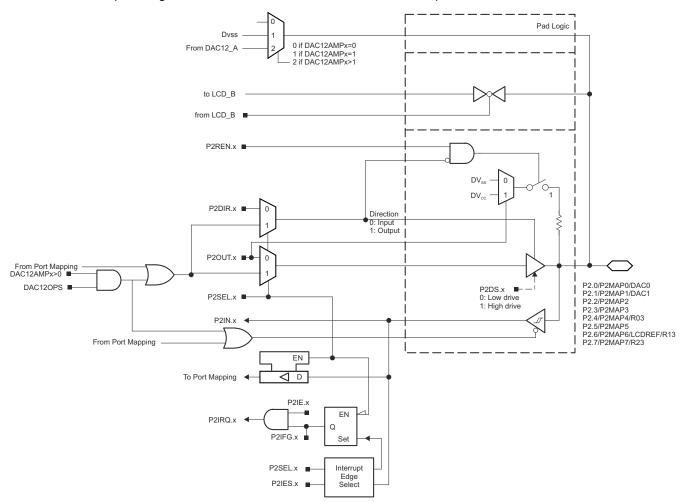

- (2) To determine the pin mux encodings for each pin, refer to  $\ddagger$  9.13.

- (3) Signal Types: I = Input, O = Output, I/O = Input or Output, P = power

- (4) Buffer Types: LVCMOS, HVCMOS, Analog, or Power (see 表 7-3 for details).

- (5) The power source shown in this table is the I/O power source, which may differ from the module power source.

- (6) Reset States:

- OFF = High-impedance input with pullup or pulldown disabled (if available)

- HiZ = High-impedance (neither input nor output)

- PD = High-impedance input with pulldown enabled

- PU = High-impedance input with pullup enabled

- DRIVE0 = Drive output low

- DRIVE1 = Drive output high

- N/A = Not applicable

- (7) For Debug pins: Emu = with emulator attached at reset, No Emu = without emulator attached at reset

# 7.3 Signal Descriptions

表 7-2 describes the signals for all device variants and package options.

## 表 7-2. Signal Descriptions

|             | SIGNAL     | PIN | NO.         | PIN<br>TYPE <sup>(1)</sup>                                                                                             |                                                                                                    |  |  |

|-------------|------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| FUNCTION    | NAME       | PZ  | ZCA,<br>ZQW |                                                                                                                        | DESCRIPTION                                                                                        |  |  |

|             | A0         | 97  | B4          | I                                                                                                                      | ADC analog single ended input A0                                                                   |  |  |

|             | A1         | 98  | В3          | I                                                                                                                      | ADC analog single ended input A1                                                                   |  |  |

|             | A2         | 99  | A2          | I                                                                                                                      | ADC analog single ended input A2                                                                   |  |  |

|             | A3         | 100 | D5          | I                                                                                                                      | ADC analog single ended input A3                                                                   |  |  |

|             | A4         | 10  | E4          | I                                                                                                                      | ADC analog single ended input A4                                                                   |  |  |

|             | A5         | 11  | E2          | I                                                                                                                      | ADC analog single ended input A5                                                                   |  |  |

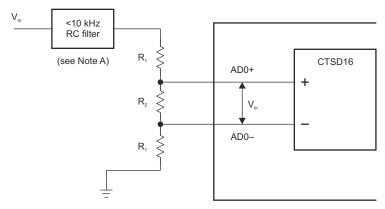

|             | AD0+       | 1   | A1          | I                                                                                                                      | ADC positive analog differential input AD0+                                                        |  |  |

| ADC         | AD0-       | 2   | B2          | I                                                                                                                      | ADC negative analog differential input AD0-                                                        |  |  |

|             | AD1+       | 3   | B1          | I                                                                                                                      | ADC positive analog differential input AD1+                                                        |  |  |

|             | AD1-       | 4   | C3          | I                                                                                                                      | ADC negative analog differential input AD1-                                                        |  |  |

|             | AD2+       | 5   | C2          | I                                                                                                                      | ADC positive analog differential input AD2+                                                        |  |  |

|             | AD2-       | 6   | C1          | I                                                                                                                      | ADC negative analog differential input AD2-                                                        |  |  |

|             | AD3+       | 7   | D4          | 1                                                                                                                      | ADC positive analog differential input AD3+                                                        |  |  |

|             | AD3-       | 8   | D2          | 1                                                                                                                      | ADC negative analog differential input AD3-                                                        |  |  |

|             | VeREF+     | 9   | D1          | I                                                                                                                      | Input for an external reference voltage to the ADC and DAC                                         |  |  |

| BSL         | BSLRX      | 36  | J6          | I                                                                                                                      | BSL receive input                                                                                  |  |  |

| BSL         | BSLTX      | 35  | M5          | 0                                                                                                                      | BSL transmit output                                                                                |  |  |

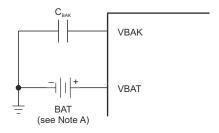

| Dookun      | VBAK 86 A7 |     | I/O         | Capacitor for backup subsystem. Do not load this pin externally. For capacitor values, see $C_{BAK}$ in $\dagger$ 8.3. |                                                                                                    |  |  |

| Backup      | VBAT       | 87  | D8          | Р                                                                                                                      | Backup or secondary supply voltage. If backup voltage is not supplied, connect to DVCC externally. |  |  |

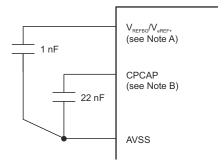

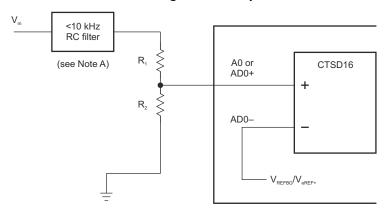

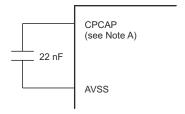

| Charge Pump | CPCAP      | 17  | G4          | I/O                                                                                                                    | Capacitor for op amp and CTSD16 rail-to-rail charge pump                                           |  |  |

|             | ACLK       | 34  | L5          | 0                                                                                                                      | ACLK output (divided by 1, 2, 4, 8, 16, or 32)                                                     |  |  |

|             | RTCCLK     | 88  | D7          | 0                                                                                                                      | RTCCLK output                                                                                      |  |  |

|             | SMCLK      | 46  | J8          | 0                                                                                                                      | SMCLK output                                                                                       |  |  |

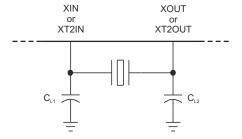

| Clock       | XIN        | 15  | G1          | I                                                                                                                      | Input terminal for crystal oscillator XT1                                                          |  |  |

|             | XOUT       | 14  | F1          | 0                                                                                                                      | Output terminal of crystal oscillator XT1                                                          |  |  |

|             | XT2IN      | 84  | B8          | I                                                                                                                      | Input terminal for crystal oscillator XT2                                                          |  |  |

|             | XT2OUT     | 85  | B7          | 0                                                                                                                      | Output terminal of crystal oscillator XT2                                                          |  |  |

|            | SIGNAL       |          | PIN NO.     |                            | escriptions (continued)                         |  |  |  |

|------------|--------------|----------|-------------|----------------------------|-------------------------------------------------|--|--|--|

| FUNCTION   | NAME         | PZ       | ZCA,<br>ZQW | PIN<br>TYPE <sup>(1)</sup> | DESCRIPTION                                     |  |  |  |

|            | CB0          | 97       | B4          | I                          | Comparator_B input CB0                          |  |  |  |

|            | CB1          | 98       | В3          | I                          | Comparator_B input CB1                          |  |  |  |

|            | CB2          | 99       | A2          | I                          | Comparator_B input CB2                          |  |  |  |

|            | CB3          | 100      | D5          | I                          | Comparator_B input CB3                          |  |  |  |

|            | CB4          | 1        | A1          | I                          | Comparator_B input CB4                          |  |  |  |

|            | CB5          | 2        | B2          | I                          | Comparator_B input CB5                          |  |  |  |

| Comparator | CB6          | 3        | B1          | I                          | Comparator_B input CB6                          |  |  |  |

|            | CB7          | 4        | C3          | I                          | Comparator_B input CB7                          |  |  |  |

|            | CB8          | 5        | C2          | I                          | Comparator_B input CB8                          |  |  |  |

|            | CB9          | 6        | C1          | I                          | Comparator_B input CB9                          |  |  |  |

|            | CB10         | 7        | D4          | I                          | Comparator_B input CB10                         |  |  |  |

|            | CB11         | 8        | D2          | I                          | Comparator_B input CB11                         |  |  |  |

|            | CBOUT        | 42       | L7          | 0                          | Comparator_B output                             |  |  |  |

| DAG        | DAC0 10 E4 O |          | 0           | DAC output channel 0       |                                                 |  |  |  |

| DAC        | DAC1         | 11<br>19 | E2<br>J1    | 0                          | DAC output channel 1                            |  |  |  |

| DMA        | DMAE0        | 88       | D7          | I                          | DMA external trigger input                      |  |  |  |

|            | SBWTCK       | 91       | В6          | I                          | Spy-Bi-Wire input clock                         |  |  |  |

|            | TCK          | 95       | D6          | I                          | Test clock                                      |  |  |  |

|            | TCLK         | 93       | A4          | I                          | Test clock input                                |  |  |  |

| Datasa     | TDI          | 93       | A4          | I                          | Test data input                                 |  |  |  |

| Debug      | TDO          | 92       | B5          | 0                          | Test data output                                |  |  |  |

|            | TEST         | 91       | В6          | I                          | Test mode pin; selects digital I/O on JTAG pins |  |  |  |

|            | TMS          | 94       | E7          | I                          | Test mode select                                |  |  |  |

|            | SBWTDIO      | 96       | A3          | I/O                        | Spy-Bi-Wire data input/output                   |  |  |  |

|          | CICNIAI        | PIN | NO.         | PIN<br>TYPE <sup>(1)</sup> | escriptions (continued)                                                         |  |  |

|----------|----------------|-----|-------------|----------------------------|---------------------------------------------------------------------------------|--|--|

| FUNCTION | SIGNAL<br>NAME | PZ  | ZCA,<br>ZQW |                            | DESCRIPTION                                                                     |  |  |

|          | P1.0           | 34  | L5          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P1.1           | 35  | M5          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P1.2           | 36  | J6          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P1.3           | 37  | H6          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P1.4           | 38  | M6          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P1.5           | 39  | L6          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P1.6           | 40  | J7          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P1.7           | 41  | M7          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P2.0           | 18  | H2          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondary function |  |  |

|          | P2.1           | 19  | J1          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondary function |  |  |

|          | P2.2           | 20  | H4          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondal function  |  |  |

| GPIO     | P2.3           | 21  | J2          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondar function  |  |  |

| GFIO     | P2.4           | 22  | K1          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondary function |  |  |

|          | P2.5           | 23  | K2          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondary function |  |  |

|          | P2.6           | 24  | L2          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondary function |  |  |

|          | P2.7           | 25  | L3          | I/O                        | General-purpose digital I/O with port interrupt and mappable secondary function |  |  |

|          | P3.0           | 42  | L7          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P3.1           | 43  | H7          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P3.2           | 44  | M8          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P3.3           | 45  | L8          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P3.4           | 46  | J8          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P3.5           | 47  | М9          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P3.6           | 48  | L9          | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

|          | P3.7           | 49  | M10         | I/O                        | General-purpose digital I/O with port interrupt                                 |  |  |

| 表 7-2. Signal Descriptions (continued) |        |         |             |                     |                                                 |  |  |  |  |

|----------------------------------------|--------|---------|-------------|---------------------|-------------------------------------------------|--|--|--|--|

| ELINIOTIC::                            | SIGNAL | PIN NO. |             | PIN                 | PEOPLETION                                      |  |  |  |  |

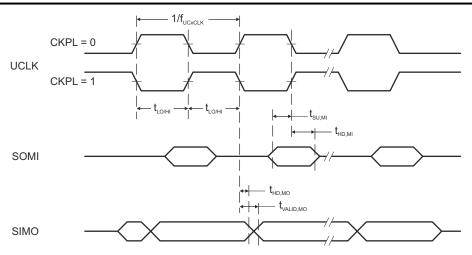

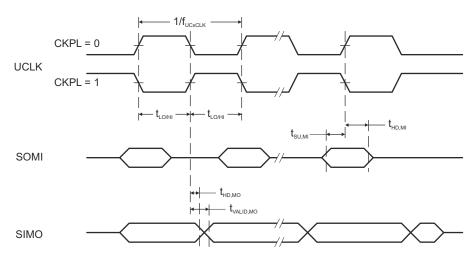

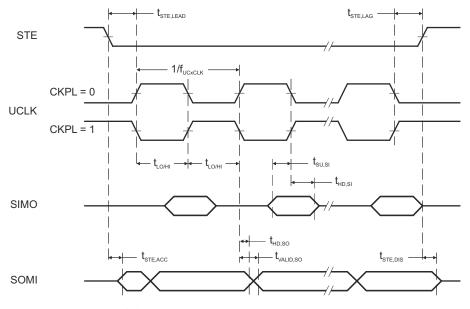

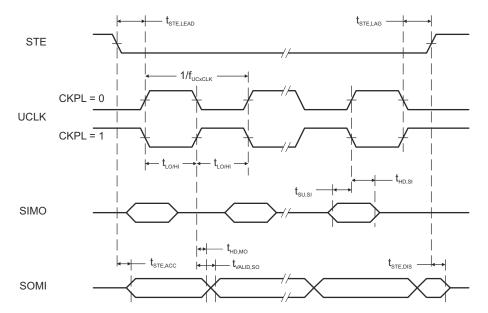

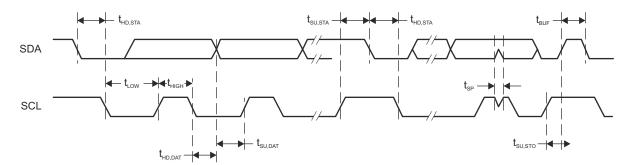

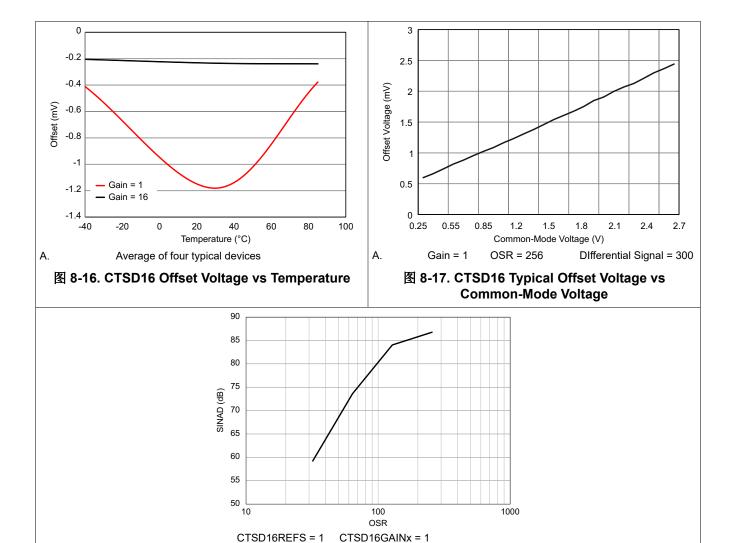

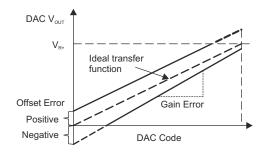

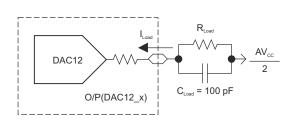

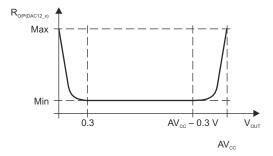

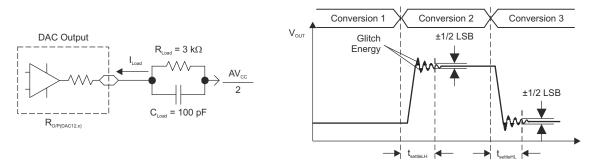

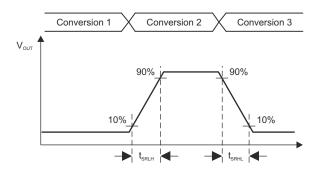

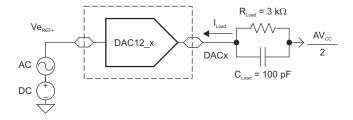

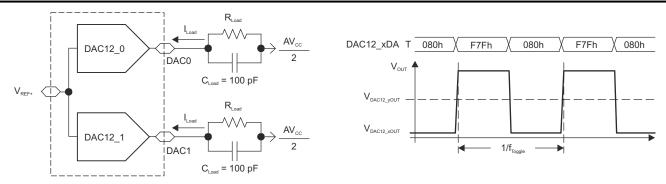

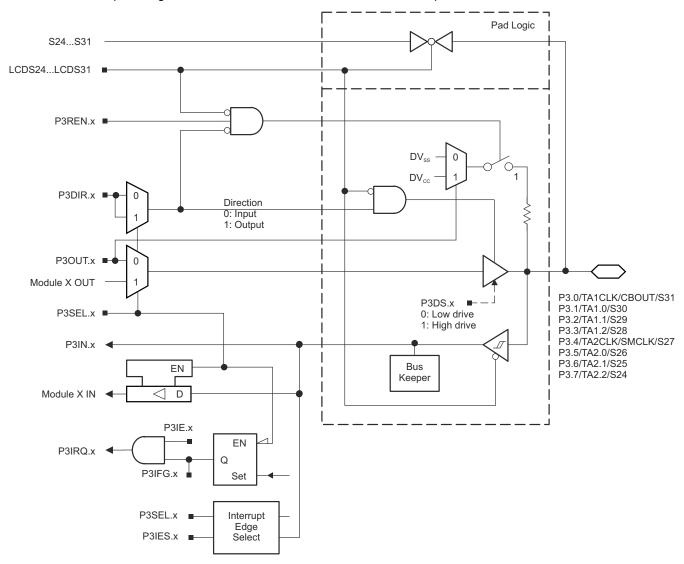

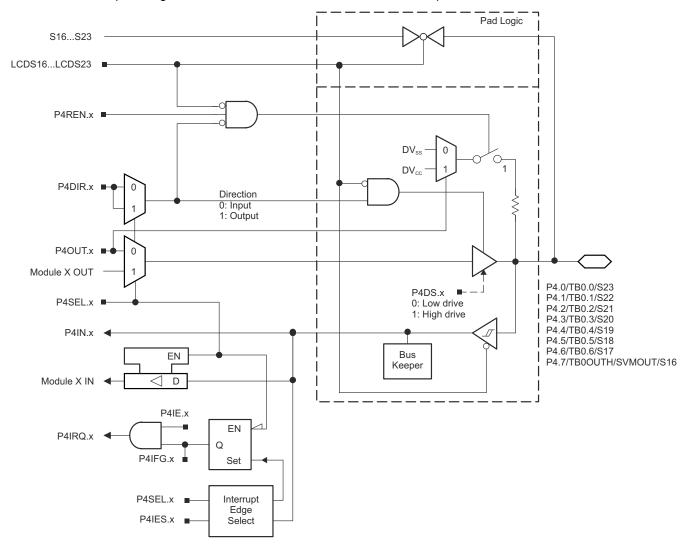

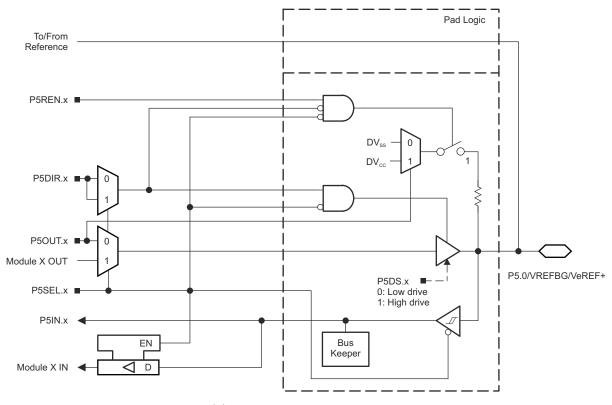

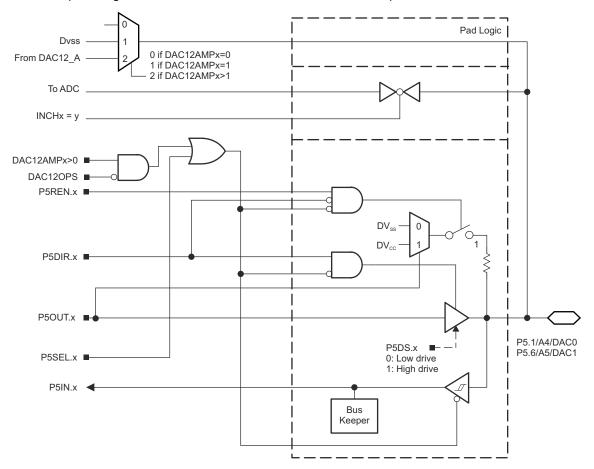

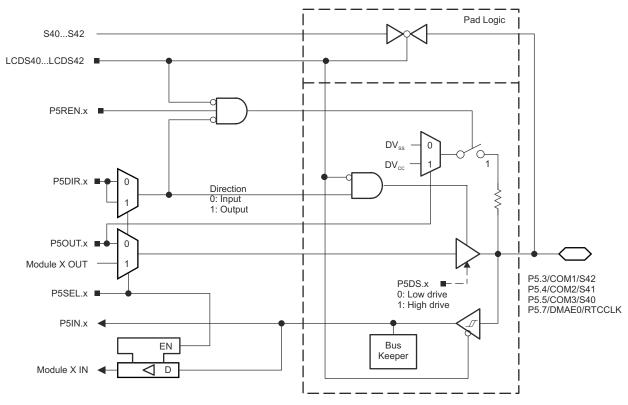

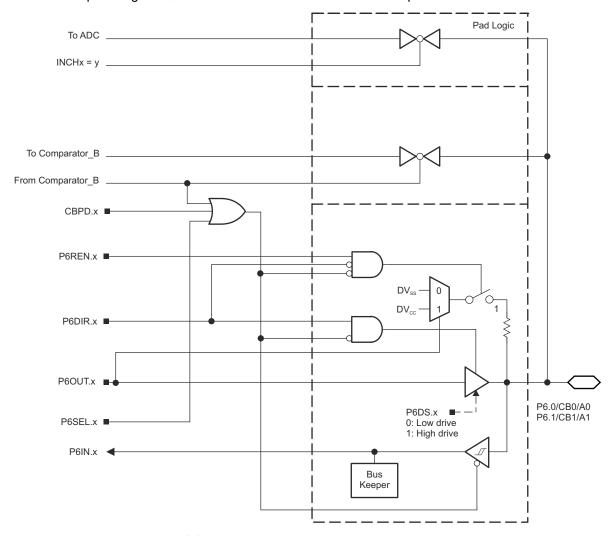

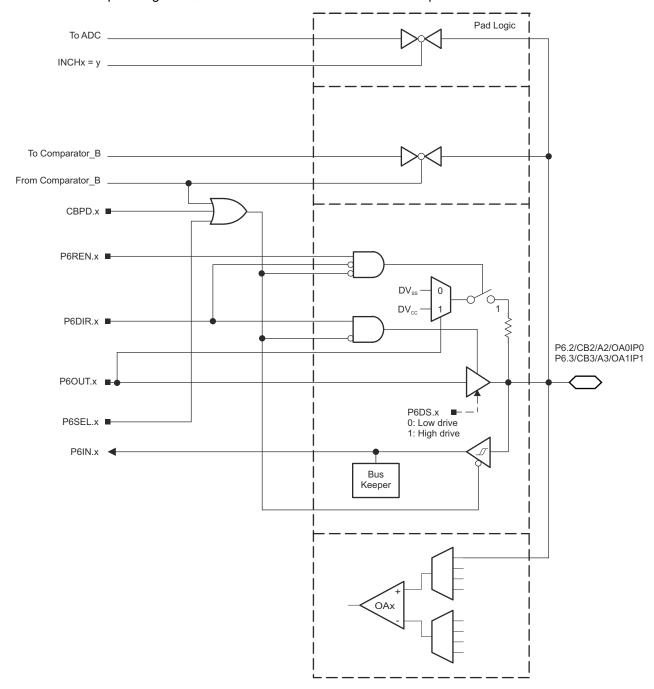

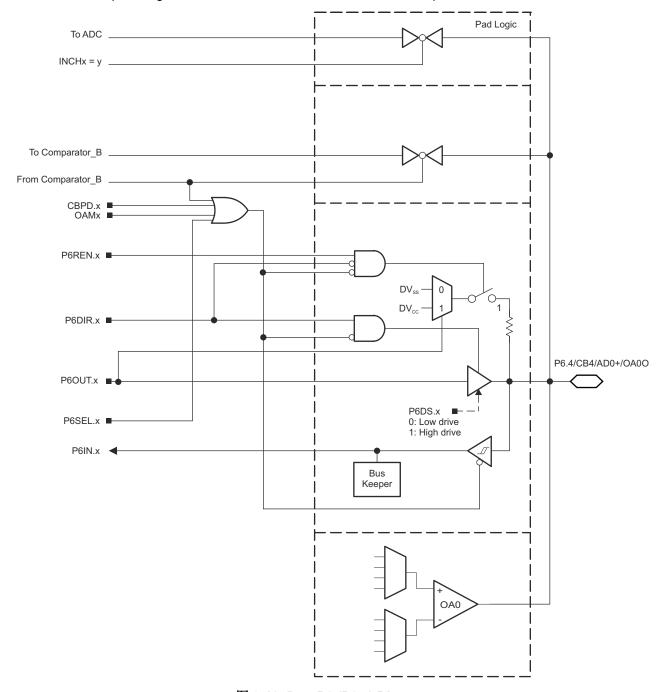

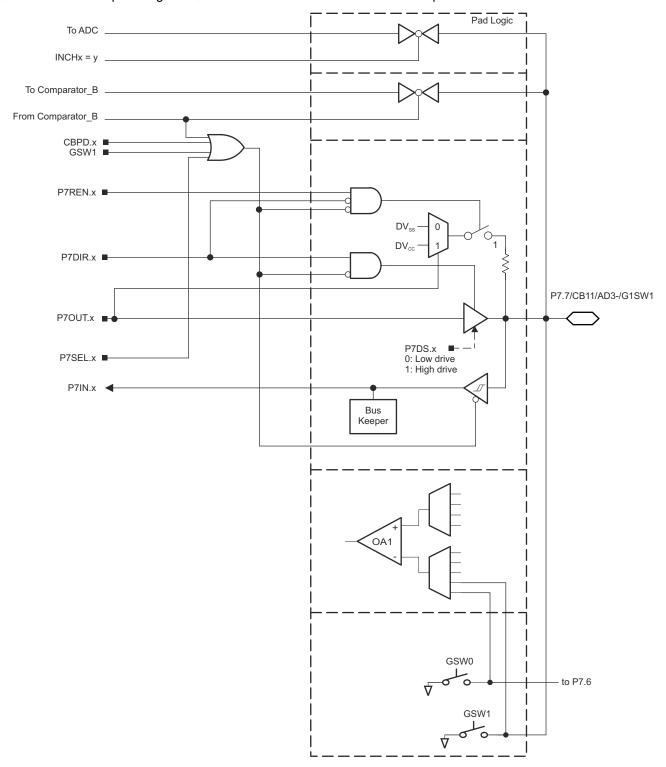

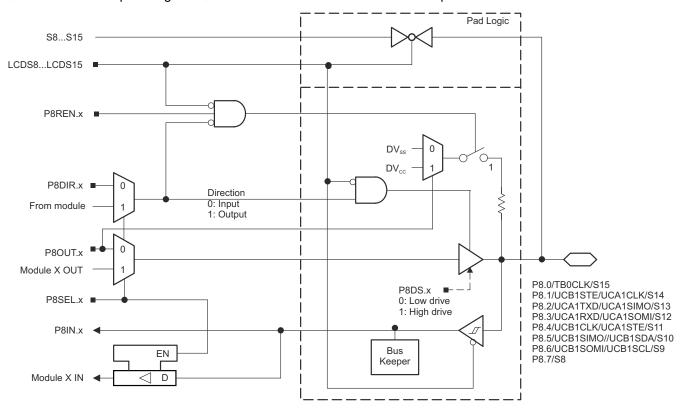

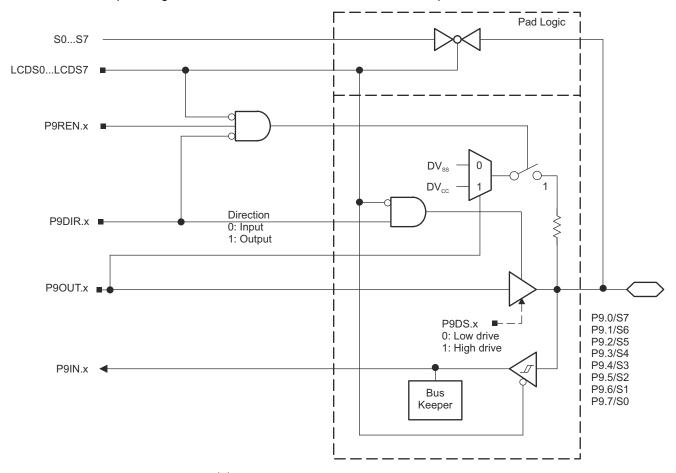

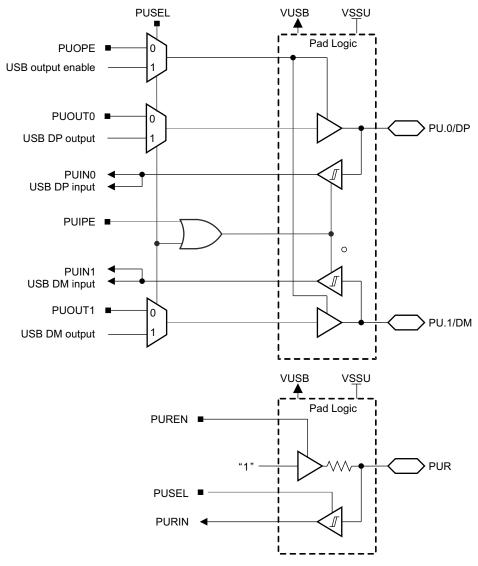

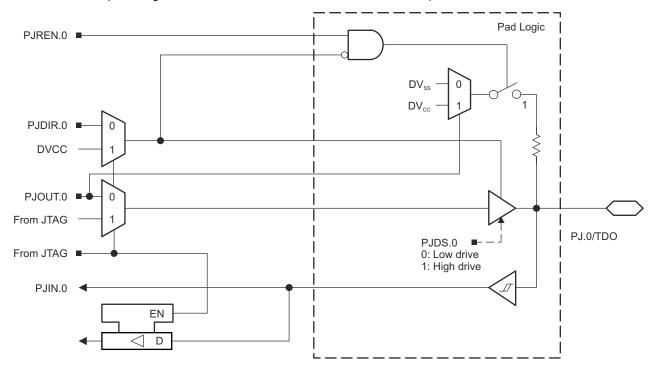

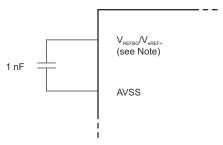

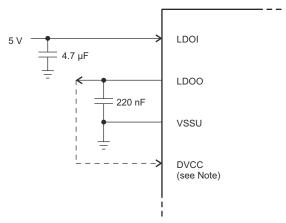

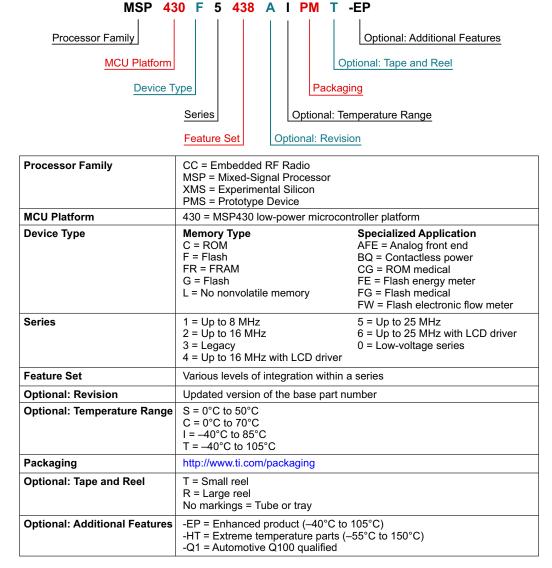

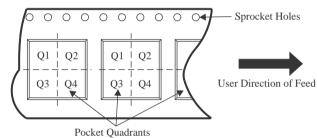

| FUNCTION                               | NAME   | PZ      | ZCA,<br>ZQW | TYPE <sup>(1)</sup> | DESCRIPTION                                     |  |  |  |  |