**THS4561** ZHCSGR2D - AUGUST 2017 - REVISED FEBRUARY 2021

# THS4561 低功耗、高电源电压范围、60MHz、全差分放大器

# 1 特性

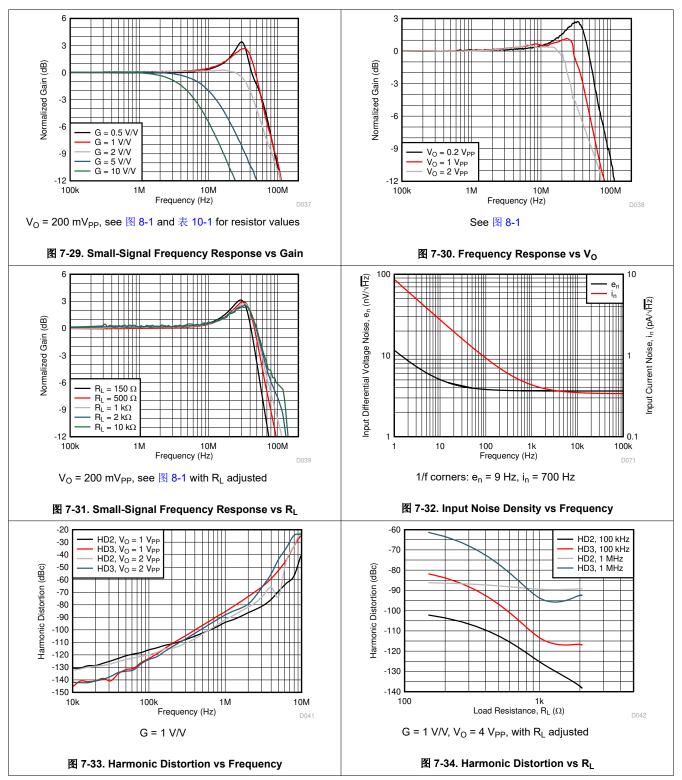

带宽:60MHz(G=1V/V)

压摆率: 230V/µs 增益带宽积:68MHz

• 电压噪声:

- 1/f 电压噪声拐角频率:8Hz - 宽带噪声 (≥ 500Hz): 4nV/ √ Hz 输入失调电压:±250µV(最大值)

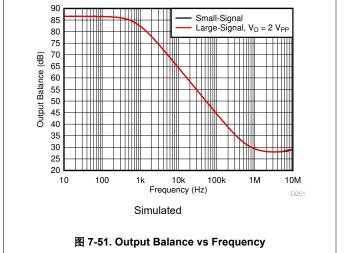

- 温漂: ±4µV/°C(最大值) • 电源工作范围: 2.85V 至 12.6V

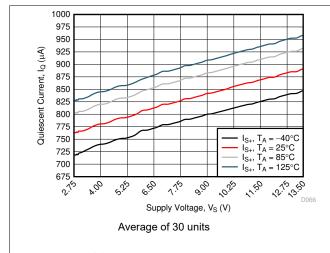

电源电流:775µA 负轨输入 (NRI)

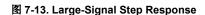

• 轨至轨输出 (RRO)

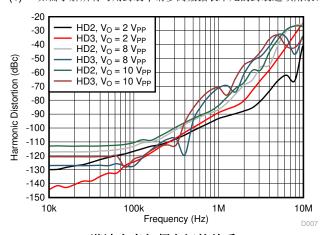

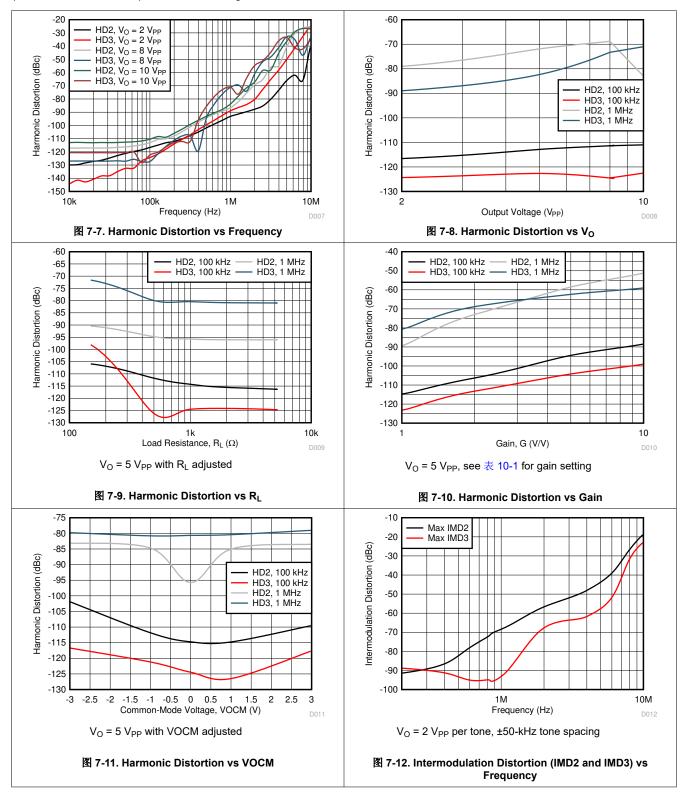

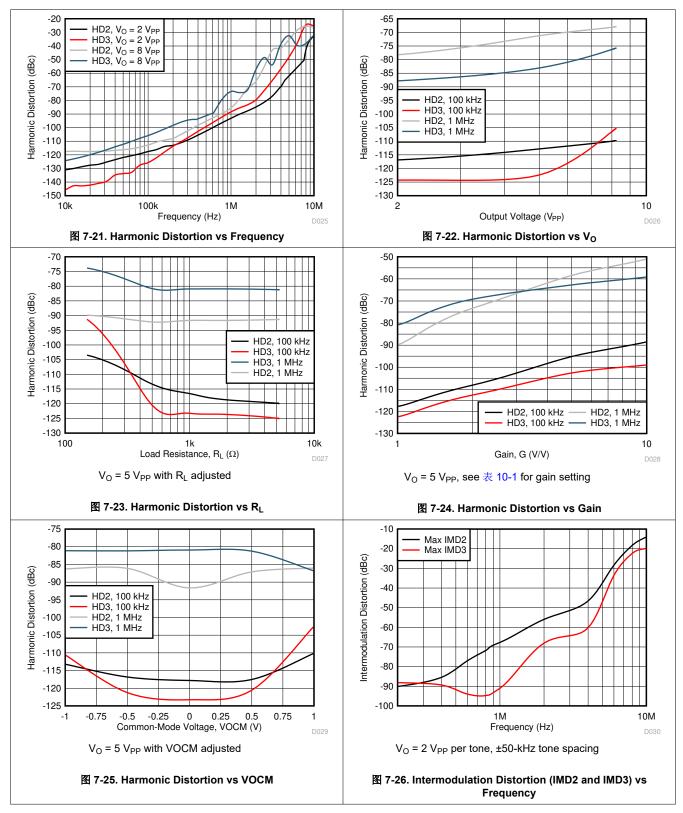

超低的谐波失真:

- HD2: -117dBc(2V<sub>PP</sub>、100kHz 时) - HD3: - 124dBc ( 2V<sub>PP</sub>、100kHz 时 )

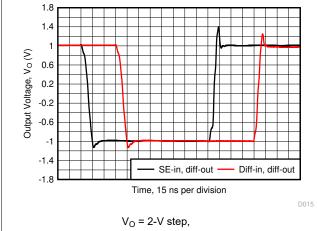

• 0.01% 稳定时间(2V 阶跃):90ns

## 2 应用

16 位至 20 位、差分 SAR 和 Δ-Σ 驱动器

差分有源滤波器

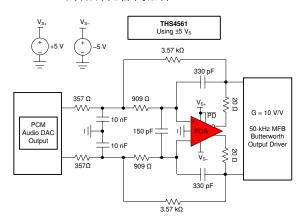

高输出摆幅 PCM 音频 DAC 输出

• 医疗超声波

电池测试仪

功率分析仪

THS4551 的低功耗替代器件

增益为 10V/V 且具有 50kHz 二阶 MFB 滤波器的 PCM 音频 DAC 输出

# 3 说明

THS4561 全差分放大器 (FDA) 可在单端源至差分输出 之间提供一个简单接口,从而满足精密模数转换器 (ADC) 的需求。THS4561 具有 8Hz 的超低 1/f 电压噪 声拐角频率和 130dB 的低总谐波失真 (THD),同时仅 消耗 775µA 的静态电流,非常适用于功率敏感的数据 采集 (DAQ) 系统,该系统需要使用放大器和 ADC 组 合来改善信噪比 (SNR) 及无杂散动态范围 (SFDR),从 而提供高性能。

THS4561 具有所需的负电源轨输入,可用于将直流耦 合、以接地为中心的源信号连接到单电源差分输入 ADC。低直流误差和温漂项可满足新兴的高速和高分 辨率逐次逼近寄存器 (SAR) 和  $\Delta - \Sigma$  ADC 输入要求。 2.85V 至 12.6V 电源电压范围、灵活的输出共模设置 以及电源余量低等特性,有助于符合多种 ADC 输入和 数模转换器 (DAC) 输出的要求。

THS4561 器件的额定工作温度范围是 - 40°C 至 +125°C。

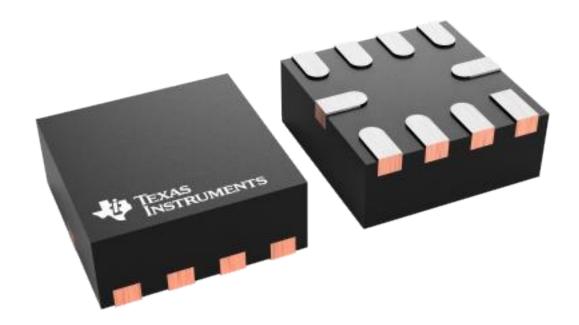

#### 器件信息

| 器件型号    | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |

|---------|-------------------|-----------------|

|         | VSSOP (8)         | 3.00mm × 3.00mm |

| THS4561 | WQFN (10)         | 2.00mm x 2.00mm |

|         | VQFN (16)         | 3.00mm × 3.00mm |

如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

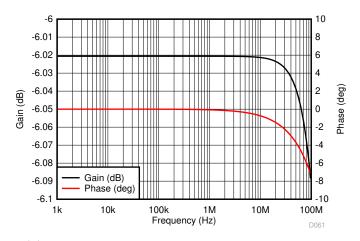

谐波失真与频率间的关系

# **Table of Contents**

| 2 应用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------|

| 3 说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 Characterization                                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1 8.6 Simulated Characterization Curves             |                           |

| 4 Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8.7 Terminology and Application Assumptions         |                           |

| 5 Device Comparison Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 9 Detailed Description                            |                           |

| 6 Pin Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4 9.1 Overview                                      |                           |

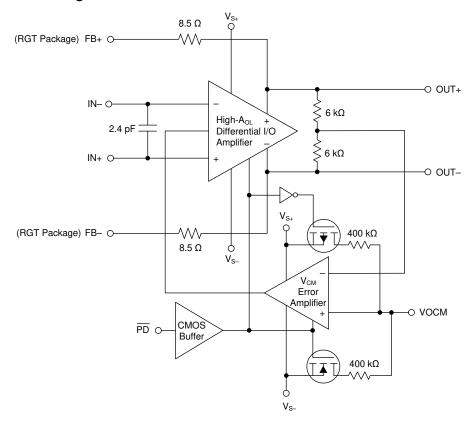

| 7 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>5</u> 9.2 Functional Block Diagram               |                           |

| 7.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5 9.3 Feature Description                           |                           |

| 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 9.4 Device Functional Modes                       |                           |

| 7.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                           |

| 7.4 Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5 10.1 Application Information                      |                           |

| 7.5 Electrical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V}$ to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.2 Typical Application                            |                           |

| 12 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7 11 Power Supply Recommendations                   |                           |

| 7.6 Typical Characteristics: $(V_{S+}) - (V_{S-}) = 12 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12 Layout                                           |                           |

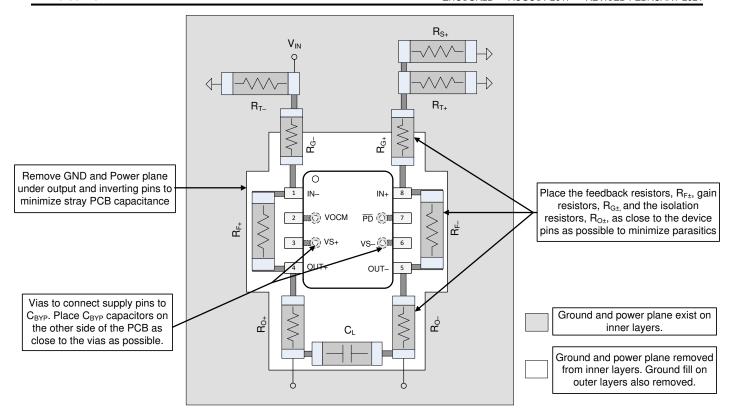

| 7.7 Typical Characteristics: $(V_{S+}) - (V_{S-}) = 5 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.1 Layout Guidelines                              |                           |

| 7.8 Typical Characteristics: $(V_{S+}) - (V_{S-}) = 3 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12.2 Layout Examples                                |                           |

| 7.9 Typical Characteristics: $(V_{S+}) - (V_{S-}) = 3-V$ to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13 Device and Documentation Support                 |                           |

| 12-V Supply Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18.1 接收文档更新通知                                       |                           |

| 8 Parameter Measurement Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22 13.2 文持贠源                                        |                           |

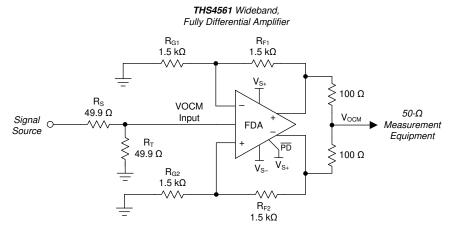

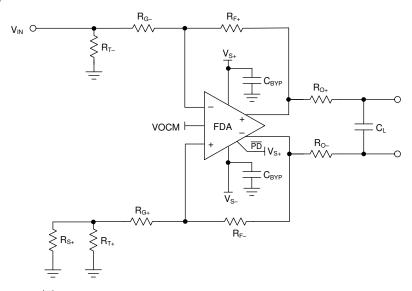

| 8.1 Example Characterization Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22 13.3 Trademarks                                  |                           |

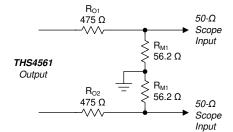

| 8.2 Output Interface Circuit for DC-Coupled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13.4 静电放电警告                                         | 40                        |

| Differential Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24 13.5 术语表                                         | 40                        |

| 8.3 Output Common-Mode Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |                           |

| 8.4 Differential Amplifier Noise Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     | 40                        |

| <ul> <li>Changes from Revision C (December 2020) to</li> <li>Changed the status of the RGT package from the changes f</li></ul>        |                                                     |                           |

| Changed the status of the RGT package from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | preview to production                               | 4                         |

| Changed the status of the RGT package from Package f               | preview to productionvision C (December 2020)       | Page                      |

| Changed the status of the RGT package from Package f               | preview to production                               | Page                      |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to productionvision C (December 2020)       | Page                      |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page                      |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page11                    |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page11                    |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page111                   |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page11145 value           |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page11145 value           |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page1115 value            |

| <ul> <li>Changed the status of the RGT package from // Changes from Revision B (August 2020) to Revision B (Augus</li></ul> | preview to production                               | Page1145 value5           |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page1145 value55          |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page115 value5 igure in   |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page115 value5 igure in18 |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production                               | Page115 value5 igure in18 |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production  vision C (December 2020)  µs | Page115 value5 igure in18 |

| <ul> <li>Changes from Revision B (August 2020) to Reversion Revision B (August 2020) to Reversion B (A</li></ul> | preview to production  vision C (December 2020)  µs | Page                      |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production  vision C (December 2020)  µs | Page                      |

| <ul> <li>Changed the status of the RGT package from pack</li></ul> | preview to production  vision C (December 2020)  µs | Page                      |

| <ul> <li>Changes from Revision B (August 2020) to Reversion Revision B (August 2020) to Reversion B (A</li></ul> | preview to production  wision C (December 2020)  ps | Page                      |

| <ul> <li>Changes from Revision B (August 2020) to Reversion Revision B (August 2020) to Reversion B (August 2017) to Reversion B (A</li></ul> | preview to production  wision C (December 2020)  ps | Page                      |

# **5 Device Comparison Table**

| DEVICE   | BW, G = 1 (MHz) | I <sub>Q</sub> , 5 V<br>(mA) | INPUT NOISE<br>(nV/√ Hz) | THD (dBc) 2 V <sub>PP</sub><br>AT 10 kHz | RAIL-TO-RAIL        | DUAL VERSIONS |

|----------|-----------------|------------------------------|--------------------------|------------------------------------------|---------------------|---------------|

| THS4561  | 60              | 0.78                         | 4                        | - 130                                    | Negative in and out | _             |

| THS4551  | 150             | 1.37                         | 3.3                      | - 138                                    | Negative in and out | THS4552       |

| THS4521  | 145             | 1.14                         | 5.6                      | - 120                                    | Negative in and out | THS4522       |

| THS4531A | 36              | 0.25                         | 10                       | - 118                                    | Negative in and out | THS4532       |

| THS4541  | 620             | 10.1                         | 2.2                      | - 140                                    | Negative in and out | _             |

# **6 Pin Configuration and Functions**

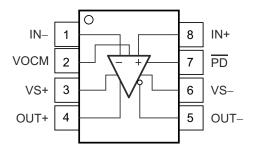

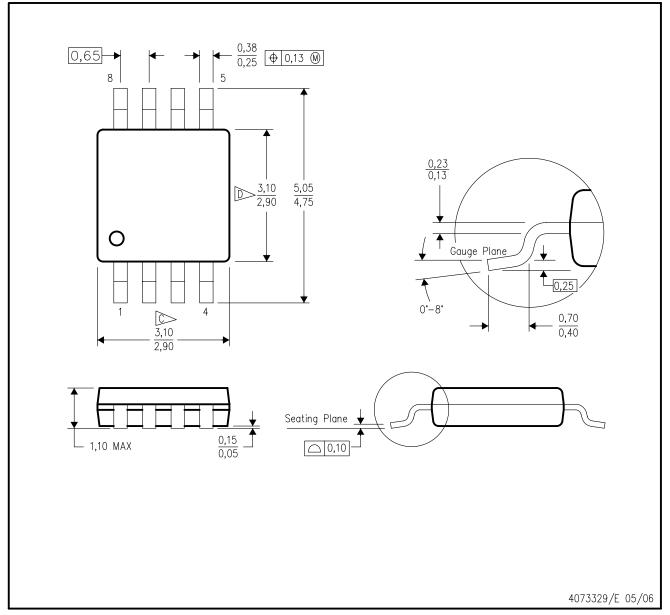

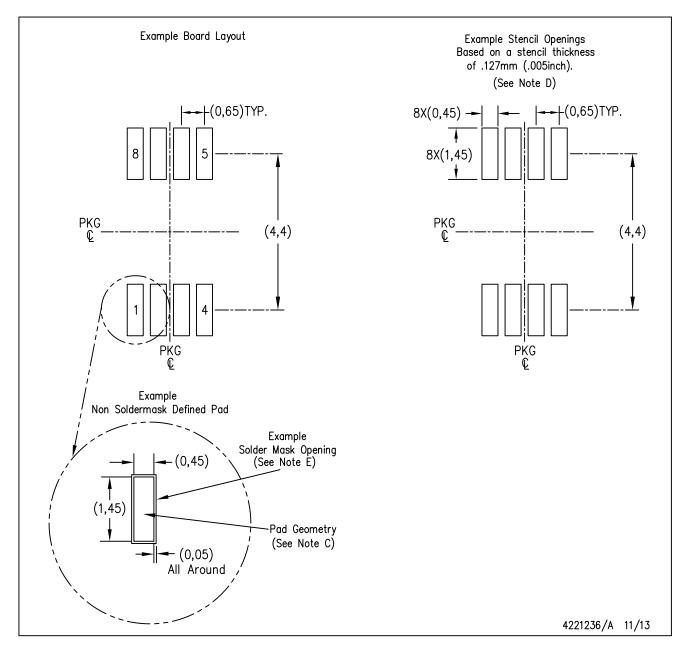

图 6-1. DGK Package 8-Pin VSSOP Top View

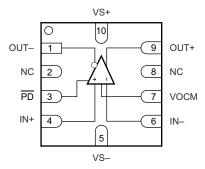

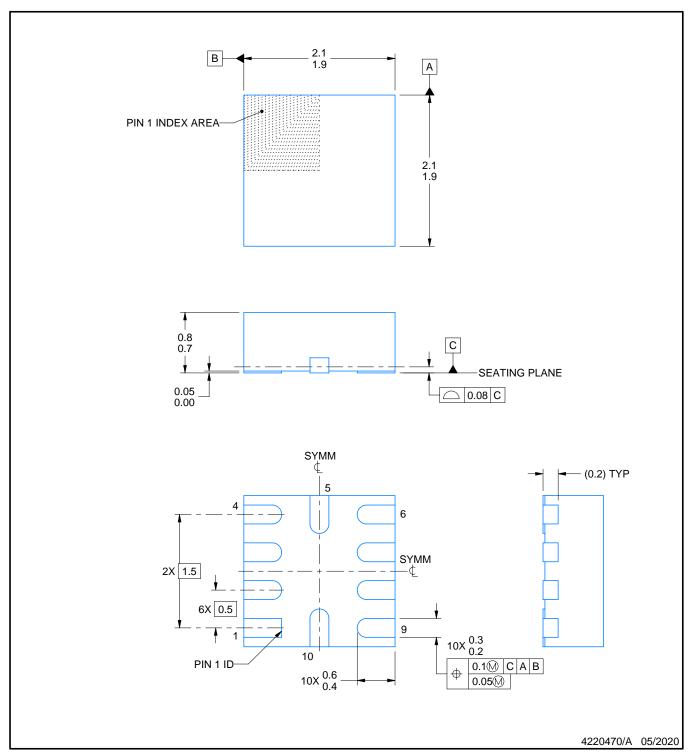

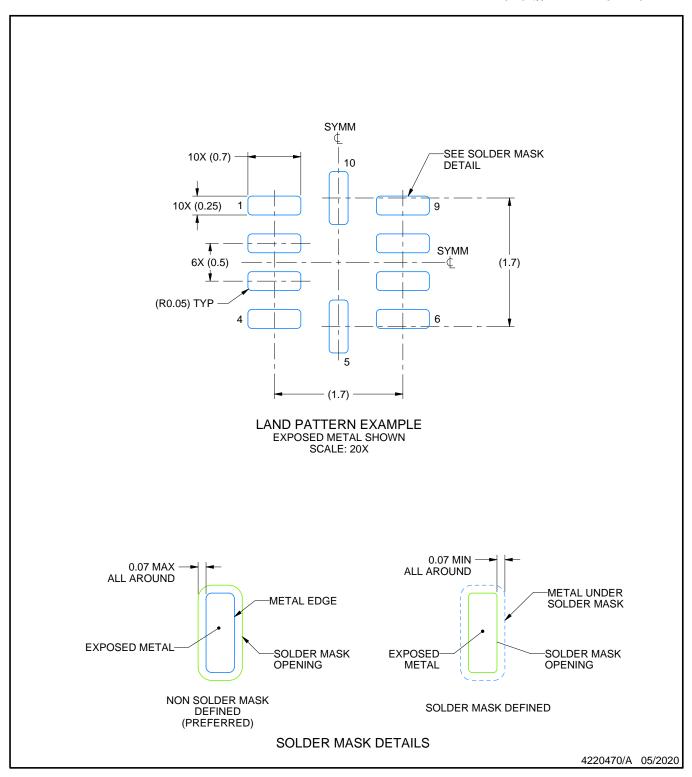

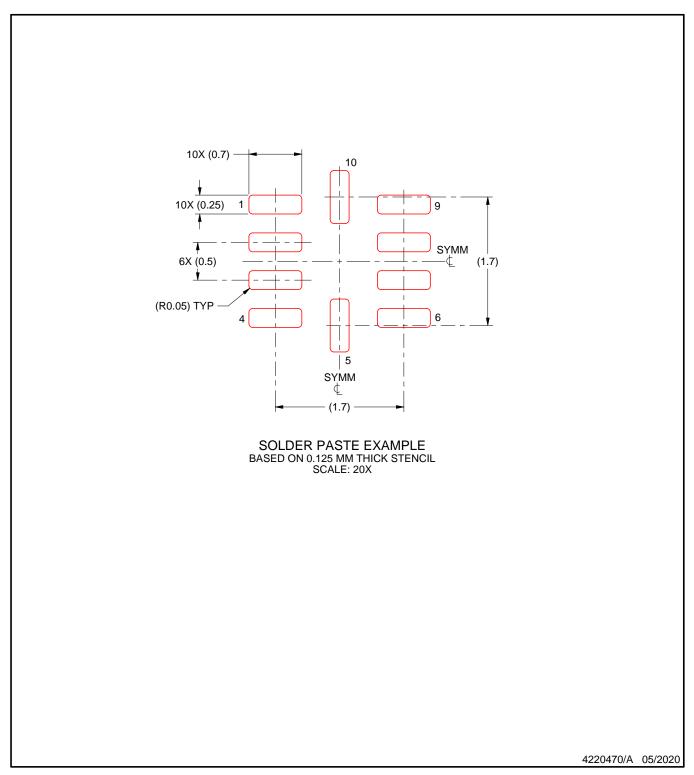

图 6-2. RUN Package 10-Pin WQFN Top View

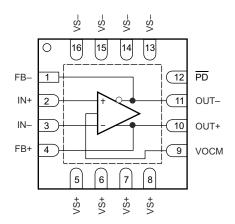

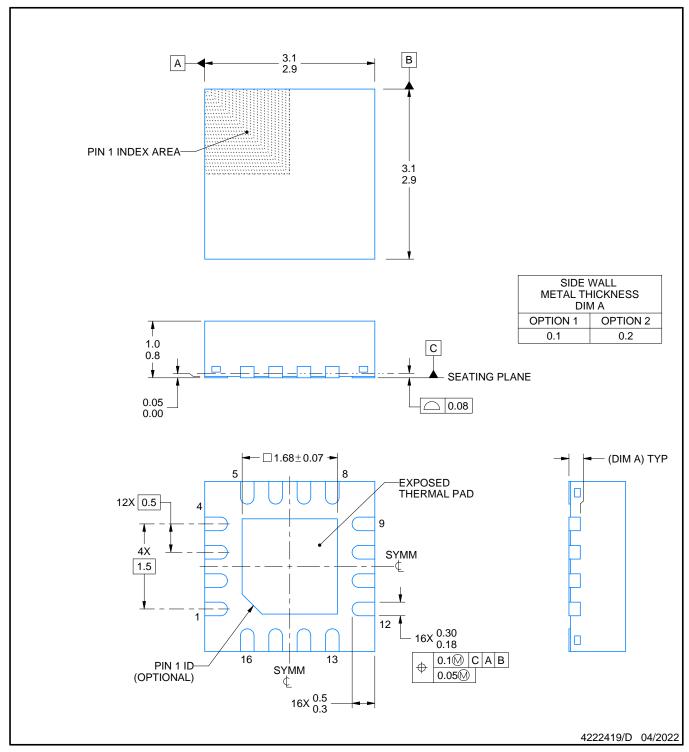

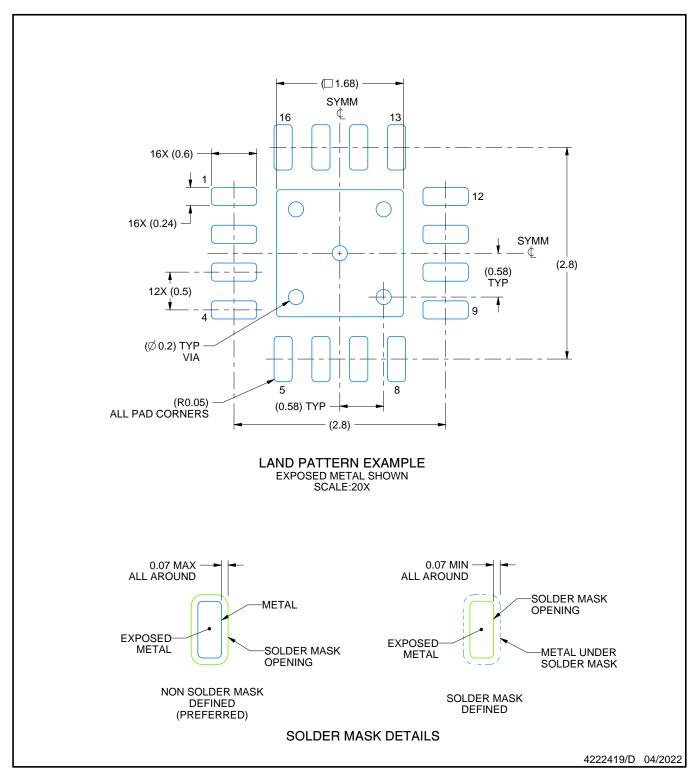

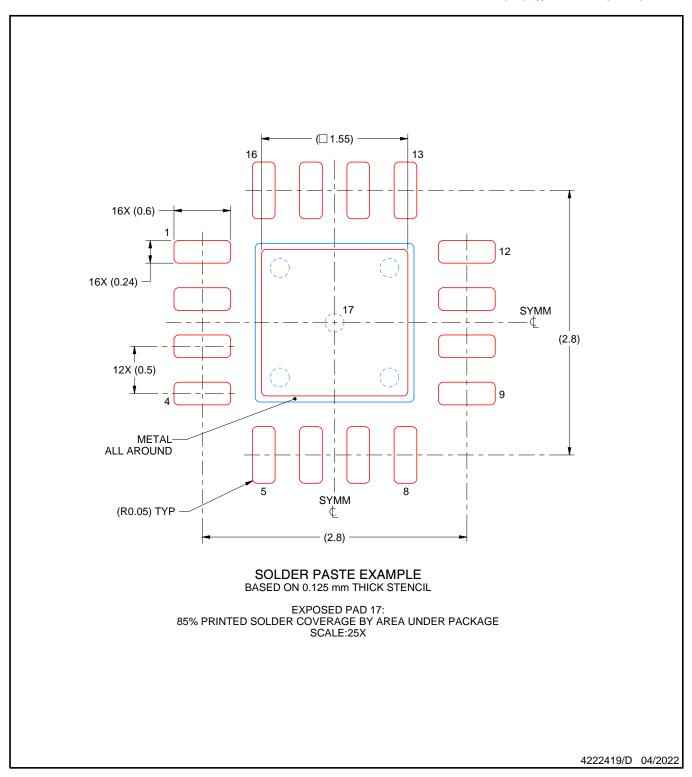

图 6-3. RGT Package 16-Pin VQFN With Exposed Thermal Pad Top View

|       | Р   | IN   |                    | TYPE <sup>(2)</sup> | DESCRIPTION                                                                      |

|-------|-----|------|--------------------|---------------------|----------------------------------------------------------------------------------|

| NAME  | DGK | RUN  | RGT <sup>(1)</sup> | TYPE(=)             | DESCRIPTION                                                                      |

| FB -  | _   | _    | 1                  | 0                   | Inverting (negative) output feedback                                             |

| FB+   | _   | _    | 4                  | 0                   | Noninverting (positive) output feedback                                          |

| IN -  | 1   | 6    | 3                  | I                   | Inverting (negative) amplifier input                                             |

| IN+   | 8   | 4    | 2                  | I                   | Noninverting (positive) amplifier input                                          |

| NC    | _   | 2, 8 | _                  | _                   | No internal connection                                                           |

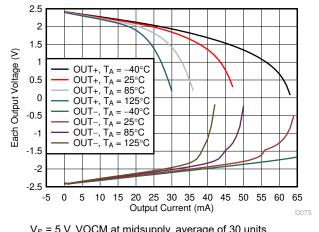

| OUT - | 5   | 1    | 11                 | 0                   | Inverting (negative) amplifier output                                            |

| OUT+  | 4   | 9    | 10                 | 0                   | Noninverting (positive) amplifier output                                         |

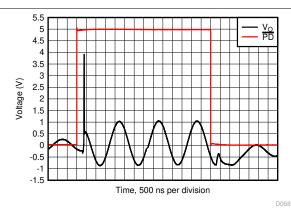

| PD    | 7   | 3    | 12                 | I                   | Power down. PD = logic low = power off mode; PD = logic high = normal operation. |

| VOCM  | 2   | 7    | 9                  | I                   | Common-mode voltage input                                                        |

| VS -  | 6   | 5    | 13, 14, 15,<br>16  | Р                   | Negative power-supply input                                                      |

| VS+   | 3   | 10   | 5, 6, 7, 8         | Р                   | Positive power-supply input                                                      |

表 6-1. Pin Functions

(2) I = input, O = output, P = power.

<sup>(1)</sup> Solder the exposed RGT package thermal pad to a heat-spreading power or ground plane. This pad is electrically isolated from the die, but must be connected to a power or ground plane and not floated.

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|             |                                                             | MIN                      | MAX              | UNIT |

|-------------|-------------------------------------------------------------|--------------------------|------------------|------|

|             | Total supply voltage, $V_S = (V_{S+} - V_{S-})$             |                          | 13.5             | V    |

| Voltage     | Supply turn-on/off dV/dT <sup>(2)</sup>                     |                          | ±0.35            | V/µs |

| Voltage     | Input, output, power down and common-mode pin voltage range | (V <sub>S</sub> -) - 0.5 | $(V_{S+}) + 0.5$ | V    |

|             | Differential input voltage                                  |                          | ±1               | V    |

| Current     | Continuous input current                                    |                          | ±10              | mA   |

| Current     | Continuous output current <sup>(3)</sup>                    |                          | ±20              | mA   |

|             | Junction temperature, T <sub>J</sub>                        |                          | 150              | °C   |

| Temperature | Operating free-air temperature, T <sub>A</sub>              | - 40                     | 125              | °C   |

|             | Storage temperature, T <sub>stg</sub>                       | - 65                     | 150              | °C   |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These stress-only ratings do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Staying below this specification ensures that the edge-triggered ESD absorption devices across the supply pins remains off.

- (3) Long-term continuous output current for electromigration limits.

## 7.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±3500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1250 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | NOM | MAX  | UNIT |

|----------------|--------------------------------|------|-----|------|------|

| Vs             | Total supply voltage           | 2.85 |     | 12.6 | V    |

| T <sub>A</sub> | Operating free-air temperature | - 40 | 25  | 125  | °C   |

#### 7.4 Thermal Information

|                        |                                              | THS4561     |            |            |      |  |

|------------------------|----------------------------------------------|-------------|------------|------------|------|--|

|                        | THERMAL METRIC <sup>(1)</sup>                | DGK (VSSOP) | RUN (WQFN) | RGT (VQFN) | UNIT |  |

|                        |                                              | 8 PINS      | 10 PINS    | 16 PINS    |      |  |

| R <sub> θ JA</sub>     | Junction-to-ambient thermal resistance       | 183.1       | 134.6      | 55.9       | °C/W |  |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 70.3        | 83.6       | 64.5       | °C/W |  |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 104.9       | 67.7       | 30.5       | °C/W |  |

| ΨЈТ                    | Junction-to-top characterization parameter   | 10.8        | 7.2        | 3.5        | °C/W |  |

| ΨЈВ                    | Junction-to-board characterization parameter | 103.2       | 67.5       | 30.5       | °C/W |  |

Copyright © 2021 Texas Instruments Incorporated

# 7.4 Thermal Information (continued)

|                        |                                              |             | THS4561    |         |      |

|------------------------|----------------------------------------------|-------------|------------|---------|------|

| THERMAL METRIC(1)      |                                              | DGK (VSSOP) | RGT (VQFN) | UNIT    |      |

|                        |                                              | 8 PINS      | 10 PINS    | 16 PINS |      |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | N/A        | 15.6    | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: THS4561

# 7.5 Electrical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V}$ to 12 V

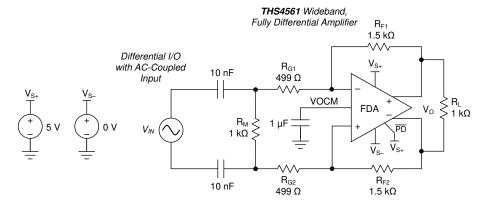

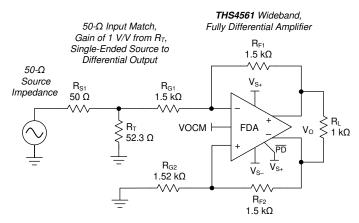

at  $T_A \approx 25^{\circ}\text{C}$ , VOCM<sup>(1)</sup> = midsupply, differential output (V<sub>O</sub>) = V<sub>OUT+</sub> - V<sub>OUT-</sub> = 2 V<sub>PP</sub>, R<sub>F</sub> = 1.5 k $^{\Omega}$ , R<sub>L</sub> = 1 k $^{\Omega}$ , 50- $^{\Omega}$  input match, differential closed-loop gain (G) = 1 V/V, single-ended input (SE-in), differential output (diff-out), and input and output referenced to midsupply for AC-coupled tests (unless otherwise noted)

|                                    | PARAMETER                           | TEST CONDIT                                                           | IONS                               | MIN                    | TYP                   | MAX              | UNIT     |

|------------------------------------|-------------------------------------|-----------------------------------------------------------------------|------------------------------------|------------------------|-----------------------|------------------|----------|

| AC PER                             | FORMANCE                            |                                                                       |                                    |                        |                       |                  |          |

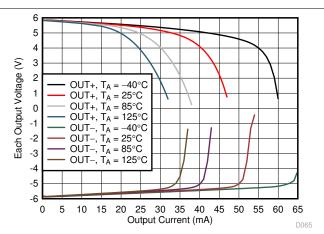

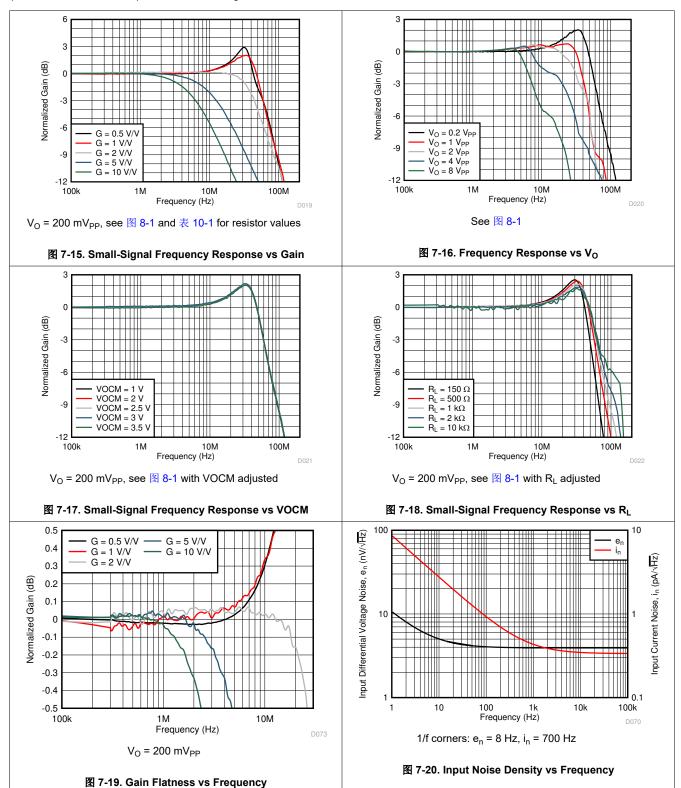

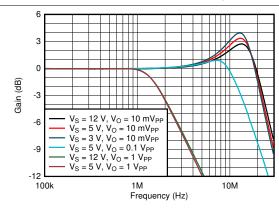

|                                    |                                     | $V_S = 5 \text{ V}, V_O = 200 \text{ mV}_{PP},$                       | 2-dB peaking                       |                        | 60                    |                  |          |

| 00014                              | Small-signal bandwidth              | -                                                                     | G = 2 V/V                          |                        | 45                    |                  |          |

| SSBW                               |                                     | $V_S = 5 \text{ V}, V_O = 200 \text{ mV}_{PP}$                        | G = 5 V/V                          |                        | 12.5                  |                  | MHz      |

|                                    |                                     |                                                                       | G = 10 V/V                         |                        | 6.3                   |                  |          |

| GBWP                               | Gain-bandwidth product              | V <sub>O</sub> = 200 mV <sub>PP</sub> , G = 20 V/                     | $V$ , $R_F = 10 \text{ k}\Omega$   |                        | 68                    |                  | MHz      |

| LSBW                               | Large-signal bandwidth              | V <sub>O</sub> = 4 V <sub>PP</sub>                                    |                                    |                        | 20                    |                  | MHz      |

|                                    | Bandwidth for 0.1-dB flatness       |                                                                       |                                    |                        | 5                     |                  | MHz      |

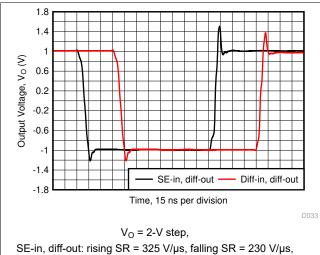

| CD                                 | Olasson 4 (000) (000)               | \\ - \( \) \\ \ - \( \) \\ \ - \( \) \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Rising                             |                        | 325                   |                  | V/µs     |

| SR                                 | Slew rate (20% - 80%)               | $V_S = 5 \text{ V}, V_O = 2\text{-V step}$                            | Falling                            |                        | 230                   |                  | V/µs     |

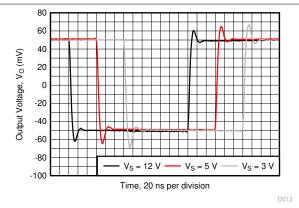

|                                    | 0.12 = 24 = 24 = 24 = 24 = 24 = 24  | V <sub>O</sub> = 2-V step,                                            | V <sub>S</sub> = 12 V              |                        | 5%                    |                  |          |

|                                    | Overshoot and undershoot            | input t <sub>r</sub> = 10 ns                                          | V <sub>S</sub> = 5 V               |                        | 11%                   |                  |          |

|                                    | 0.1% settling time                  | $V_O = 2-V$ step, input $t_r = 10$                                    | ) ns                               |                        | 40                    |                  | ns       |

|                                    | 0.01% settling time                 | $V_O = 2-V$ step, input $t_r = 10$                                    | ) ns                               |                        | 90                    |                  | ns       |

|                                    | Rise and fall time (10% - 90%)      | V <sub>O</sub> = 100-mV step, input t <sub>r</sub>                    | = 2 ns                             |                        | 5.7                   |                  | ns       |

|                                    | 0 1 1 1 1 1 1 1 1                   | .,                                                                    | V <sub>o</sub> = 2 V <sub>PP</sub> |                        | - 117                 |                  |          |

| HD2                                | Second-order harmonic distortion    | $V_S = 5 \text{ V, } f = 100 \text{ kHz}$                             | V <sub>o</sub> = 8 V <sub>PP</sub> |                        | - 110                 |                  |          |

|                                    |                                     |                                                                       | V <sub>o</sub> = 2 V <sub>PP</sub> |                        | - 124                 |                  | dBc      |

| HD3                                | Third-order harmonic distortion     | $V_S = 5 \text{ V, f} = 100 \text{ kHz}$                              | V <sub>o</sub> = 8 V <sub>PP</sub> |                        | - 106                 |                  |          |

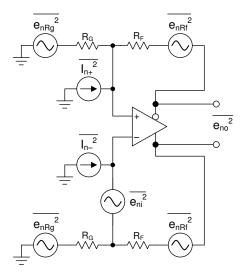

|                                    |                                     | f ≥ 500 Hz                                                            |                                    |                        | 4                     |                  | nV/ √ Hz |

| e <sub>n</sub>                     | Input differential voltage noise    | 1/f corner                                                            |                                    |                        | 8                     |                  | Hz       |

| i <sub>n</sub>                     | Input current noise, each input     | f ≥ 50 kHz                                                            |                                    |                        | 0.35                  |                  | pA/ √ Hz |

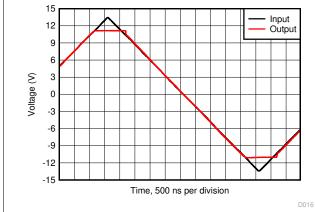

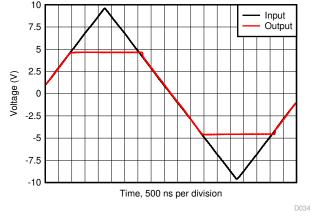

|                                    | Overdrive recovery time             | V <sub>S</sub> = 5 V, G = 2 V/V,<br>2x output overdrive, dc-co        | upled                              |                        | 210                   |                  | ns       |

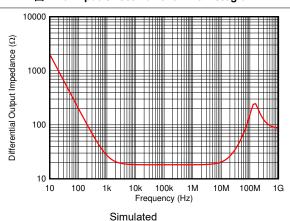

| Z <sub>OUT</sub>                   | Closed-loop output impedance        | f = 100 kHz (differential)                                            |                                    |                        | 0.06                  |                  | Ω        |

|                                    | FORMANCE                            | <u> </u>                                                              |                                    | I                      |                       |                  | I        |

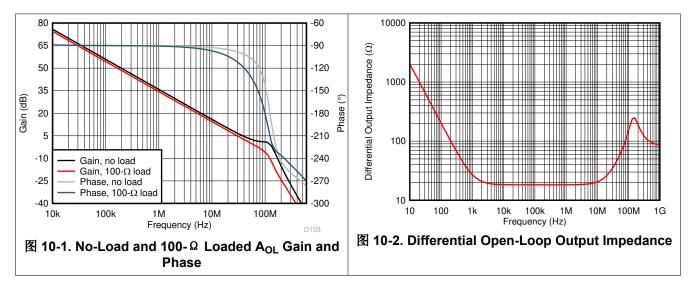

| A <sub>OL</sub>                    | Open-loop voltage gain              | V <sub>o</sub> = ±2 V                                                 |                                    | 104                    | 115                   |                  | dB       |

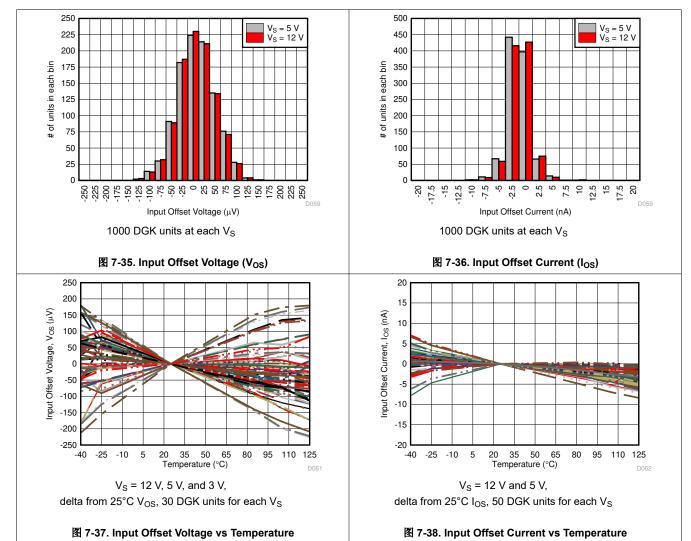

| V <sub>OS</sub>                    | Input offset voltage                | T <sub>A</sub> = 25°C                                                 |                                    | - 250                  | ±50                   | 250              | μV       |

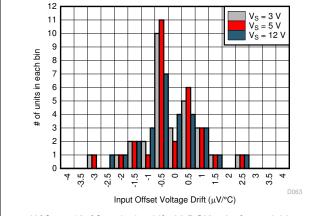

|                                    | Input offset voltage drift          | $T_A = 0$ °C to 85°C,<br>$T_A = -40$ °C to 125°C                      |                                    | - 4                    | ±0.5                  | 4                | μV/°C    |

| I <sub>B+</sub> , I <sub>B -</sub> | Input bias current <sup>(3)</sup>   | T <sub>A</sub> = 25°C                                                 |                                    |                        | 370                   | 600              | nA       |

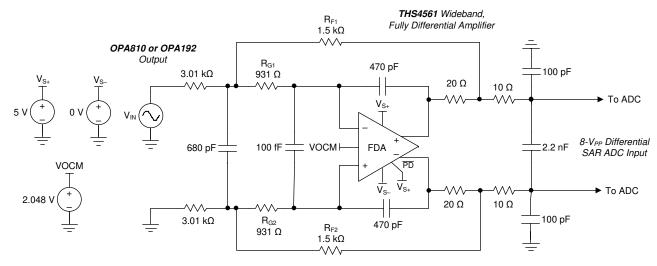

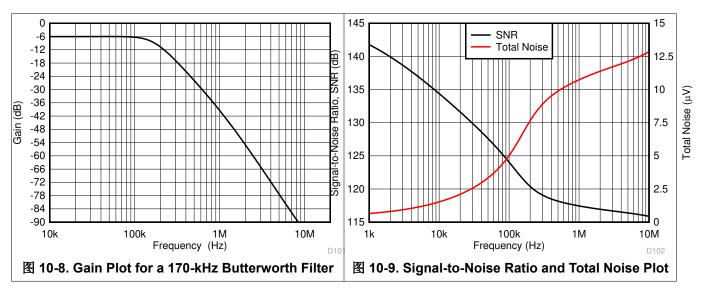

|                                    | Input bias current drift            | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                         |                                    |                        | 4.1                   | 8                | nA/°C    |