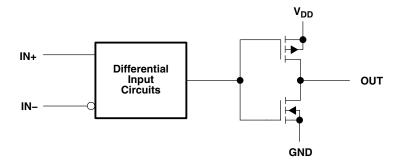

- Push-Pull CMOS Output Drives Capacitive Loads Without Pullup Resistor, I<sub>O</sub> = ± 8 mA

- Very Low Power ... 200 μW Typ at 5 V

- Fast Response Time . . . t<sub>PLH</sub> = 2.7 μs Typ With 5-mV Overdrive

- Single Supply Operation . . . 3 V to 16 V TLC3704M . . . 4 V to 16 V

- On-Chip ESD Protection

#### description

The TLC3704 consists of four independent micropower voltage comparators designed to operate from a single supply and be compatible with modern HCMOS logic systems. They are functionally similar to the LM339 but use 1/20th the power for similar response times. The push-pull CMOS output stage drives capacitive loads directly without a power-consuming pullup resistor to achieve the stated response time. Eliminating the pullup resistor not only reduces power dissipation, but also saves board space and component cost. The output stage is also fully compatible with TTL requirements.

Texas Instruments LinCMOS<sup>™</sup> process offers superior analog performance to standard CMOS processes. Along with the standard CMOS advantages of low power without sacrificing speed, high input impedance, and low bias currents, the LinCMOS process offers extremely stable input offset voltages with large differential input voltages. This characteristic makes it possible to build reliable CMOS comparators.

The TLC3704C is characterized for operation over the commercial temperature range of 0°C to 70°C. The TLC3704I is characterized for operation over the extended industrial temperature range of – 40°C to 85°C. The TLC3704M is characterized for operation over the full military temperature range of – 55°C to 125°C. The TLC3704Q is characterized for operation from – 40°C to 125°C. SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

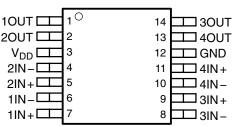

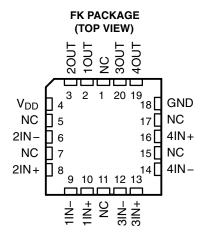

| D, J, OR N PACKAGE<br>(TOP VIEW)                     |                                 |   |                                      |                                                                       |  |  |  |  |

|------------------------------------------------------|---------------------------------|---|--------------------------------------|-----------------------------------------------------------------------|--|--|--|--|

| 10UT [<br>20UT [<br>2IN-[<br>2IN+[<br>1IN-[<br>1IN+[ | 1<br>2<br>3<br>4<br>5<br>6<br>7 | υ | 14<br>13<br>12<br>11<br>10<br>9<br>8 | ] 3OUT<br>] 4OUT<br>] GND<br>] 4IN +<br>] 4IN -<br>] 3IN +<br>] 3IN - |  |  |  |  |

NC - No internal connection

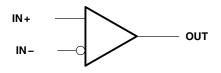

#### symbol (each comparator)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LinCMOS is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2009, Texas Instruments Incorporated

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

|                | AVAILABLE OPTIONS              |                      |                 |                    |                    |               |  |  |  |

|----------------|--------------------------------|----------------------|-----------------|--------------------|--------------------|---------------|--|--|--|

|                | M may                          |                      |                 | PACKAGE            |                    |               |  |  |  |

| T <sub>A</sub> | V <sub>IO</sub> max<br>at 25°C | SMALL OUTLINE<br>(D) | CERAMIC<br>(FK) | CERAMIC DIP<br>(J) | PLASTIC DIP<br>(N) | TSSOP<br>(PW) |  |  |  |

| 0°C to 70°C    | 5 mV                           | TLC3704CD            | —               | —                  | TLC3704CN          | TLC3704CPW    |  |  |  |

| –40°C to 85°C  | 5 mV                           | TLC3704ID            | -               | —                  | TLC3704IN          | TLC3704IPW    |  |  |  |

| –55°C to 125°C | 5 mV                           | TLC3704MD            | TLC3704MFK      | TLC3704MJ          | _                  | —             |  |  |  |

| –40°C to 125°C | 5 mV                           | _                    |                 | TLC3704QJ          |                    | _             |  |  |  |

The D and PW packages are available taped and reeled. Add R suffix to the device type (e.g., TLC3704CDR).

### functional block diagram (each comparator)

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, $V_{DD}$ (see Note 1)<br>Differential input voltage, $V_{ID}$ (see Note 2)<br>Input voltage range, $V_1$<br>Output voltage range, $V_0$<br>Input current, $I_1$<br>Output current, $I_0$ (each output)<br>Total supply current into $V_{DD}$<br>Total current out of GND<br>Continuous total power dissipation<br>Operating free-air temperature range, $T_A$<br>Storage temperature for 60 seconds: FK pa<br>Lead temperature 1,6 mm (1/16 inch) fro | 2)<br>: TLC3704C<br>TLC3704I<br>TLC3704M<br>TLC3704Q<br>ackage | $\begin{array}{c} \pm 18 \ V \\0.3 \ to \ V_{DD} \\ -0.3 \ to \ V_{DD} \\ \pm 5 \ mA \\ \pm 20 \ mA \\0.3 \ to \ V_{DD} \\ \pm 5 \ mA \\0.3 \ to \ V_{DD} \ to \ V_{DD} \\0.3 \ to \ V_{DD} \ to \ V_{DD} \\0.3 \ to \ V_{DD} \ to \ V_$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | om case for 10 seconds: D or N packa                           | ge 260°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | om case for 60 seconds: J package .                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to network ground.

2. Differential voltages are at IN+ with respect to IN-.

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

| DISSIPATION RATING TABLE |                                       |                                                |                                       |                                       |                                        |  |  |  |  |

|--------------------------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|--|--|--|--|

| PACKAGE                  | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |  |  |  |  |

| D                        | 950 mW                                | 7.6 mW/°C                                      | 608 mW                                | 494 mW                                | N/A                                    |  |  |  |  |

| FK                       | 1375 mW                               | 11.0 mW/°C                                     | 880 mW                                | 715 mW                                | 275 mW                                 |  |  |  |  |

| J                        | 1375 mW                               | 11.0 mW/°C                                     | 880 mW                                | 715 mW                                | 275 mW                                 |  |  |  |  |

| Ν                        | 1150 mW                               | 9.2 mW/°C                                      | 736 mW                                | 598 mW                                | N/A                                    |  |  |  |  |

| PW                       | 675 mW                                | 5.4 mW/°C                                      | 432 mW                                | 351 mW                                | N/A                                    |  |  |  |  |

## recommended operating conditions

|                                                |       | TLC370 | 4C                    |      |

|------------------------------------------------|-------|--------|-----------------------|------|

|                                                | MIN   | NOM    | MAX                   | UNIT |

| Supply voltage, V <sub>DD</sub>                | 3     | 5      | 16                    | V    |

| Common-mode input voltage, VIC                 | - 0.2 |        | V <sub>DD</sub> – 1.5 | V    |

| High-level output current, I <sub>OH</sub>     |       |        | - 20                  | mA   |

| Low-level output current, I <sub>OL</sub>      |       |        | 20                    | mA   |

| Operating free-air temperature, T <sub>A</sub> | 0     |        | 70                    | °C   |

# electrical characteristics at specified operating free-air temperature, $V_{DD} = 5 V$ (unless otherwise noted)

|                  |                                                     |                                                                                         | New                    | _           | TLC                           | C3704C |     |            |  |

|------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------|-------------|-------------------------------|--------|-----|------------|--|

|                  | PARAMETER                                           | TEST CO                                                                                 | NDITIONS               | TA          | MIN                           | TYP    | MAX | UNIT       |  |

| V                | Input offset voltage                                | $V_{DD} = 5 V \text{ to } 10$                                                           | ) V,                   | 25°C        |                               | 1.2    | 5   | mV         |  |

| V <sub>IO</sub>  | Input onset voltage                                 | $V_{IC} = 2.5 V$ $V_{IC} = 2.5 V$ $V_{IC} = V_{ICR}min$ $V_{DD} = 5 V \text{ to 10 } V$ | See Note 3             | 0°C to 70°C |                               |        | 6.5 | mv         |  |

|                  |                                                     | <u>м о с м</u>                                                                          |                        | 25°C        |                               | 1      |     | pА         |  |

| l <sub>IO</sub>  | Input offset current                                | $V_{IC} = 2.5 V$                                                                        |                        | 70°C        |                               |        | 0.3 | nA         |  |

|                  | Leaved bits a second state                          | N 05V                                                                                   |                        | 25°C        |                               | 5      |     | pА         |  |

| I <sub>IB</sub>  | Input bias current                                  | $V_{IC} = 2.5 V$                                                                        |                        | 70°C        |                               |        | 0.6 | nA         |  |

| .,               |                                                     |                                                                                         |                        | 25°C        | 0 to<br>V <sub>DD</sub> – 1   |        |     |            |  |

| V <sub>ICR</sub> | Common-mode input voltage range                     |                                                                                         |                        | 0°C to 70°C | 0 to<br>V <sub>DD</sub> – 1.5 |        |     | V          |  |

|                  |                                                     |                                                                                         |                        | 25°C        |                               | 84     |     |            |  |

| CMRR             | Common-mode rejection ratio                         | $V_{IC} = V_{ICR}min$                                                                   |                        | 70°C        |                               | 84     | dB  | dB         |  |

|                  |                                                     |                                                                                         |                        | 0°C         |                               | 84     |     |            |  |

|                  |                                                     |                                                                                         |                        | 25°C        |                               | 85     |     |            |  |

| k <sub>SVR</sub> | Supply-voltage rejection ratio                      | $V_{DD} = 5 V \text{ to } 10^{\circ}$                                                   | V                      | 70°C        |                               | 85     |     | dB         |  |

|                  |                                                     |                                                                                         |                        | 0°C         |                               | 85     |     |            |  |

|                  |                                                     | <u> </u>                                                                                |                        | 25°C        | 4.5                           | 4.7    |     |            |  |

| V <sub>OH</sub>  | High-level output voltage $V_{ID} = 1 V$ , $I_{OH}$ | $I_{OH} = -4 \text{ mA}$                                                                | 70°C                   | 4.3         |                               |        | V   |            |  |

|                  |                                                     | <u> </u>                                                                                | 1 4 4                  | 25°C        |                               | 210    | 300 |            |  |

| V <sub>OL</sub>  | Low-level output voltage                            | $V_{ID} = -1 V,$                                                                        | I <sub>OH</sub> = 4 mA | 70°C        |                               |        | 375 | mV         |  |

| I                | Supply surrent (all faux compositors)               | O to the local                                                                          |                        | No load     | 25°C                          |        | 35  | 80         |  |

| IDD              | Supply current (all four comparators)               | Outputs low,                                                                            | NU IUAU                | 0°C to 70°C |                               |        | 100 | μ <b>A</b> |  |

<sup>†</sup> All characteristics are measured with zero common-mode voltage unless otherwise noted.

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

#### recommended operating conditions

|                                                |       | TLC370 | )41                   |      |

|------------------------------------------------|-------|--------|-----------------------|------|

|                                                | MIN   | NOM    | MAX                   | UNIT |

| Supply voltage, V <sub>DD</sub>                | 3     | 5      | 16                    | V    |

| Common-mode input voltage, VIC                 | - 0.2 |        | V <sub>DD</sub> – 1.5 | V    |

| High-level output current, I <sub>OH</sub>     |       |        | - 20                  | mA   |

| Low-level output current, I <sub>OL</sub>      |       |        | 20                    | mA   |

| Operating free-air temperature, T <sub>A</sub> | - 40  |        | 85                    | °C   |

# electrical characteristics at specified operating free-air temperature, $V_{DD}$ = 5 V, $V_{IC}$ = 0 (unless otherwise noted)

|                  |                                       |                                        |                          | т <sub>А</sub> | TLC3704I                      |     |     |      |

|------------------|---------------------------------------|----------------------------------------|--------------------------|----------------|-------------------------------|-----|-----|------|

|                  | PARAMETER                             | TEST CO                                | TEST CONDITIONS          |                | MIN                           | TYP | MAX | UNIT |

| v                | Input offect veltere                  | $V_{DD} = 5 V \text{ to } 10$          | V,                       | 25°C           |                               | 1.2 | 5   | mV   |

| V <sub>IO</sub>  | Input offset voltage                  | $V_{IC} = V_{ICR}min$ ,                | See Note 3               | -40°C to 85°C  |                               |     | 7   | шv   |

|                  | lowest offerst surrout                |                                        |                          | 25°C           |                               | 1   |     | pА   |

| I <sub>IO</sub>  | Input offset current                  | V <sub>IC</sub> = 2.5 V                |                          | 85°C           |                               |     | 1   | nA   |

|                  | land bie environt                     |                                        |                          | 25°C           |                               | 5   |     | pА   |

| I <sub>IB</sub>  | Input bias current                    | V <sub>IC</sub> = 2.5 V                |                          | 85°C           |                               |     | 2   | nA   |

| .,               | <b>6</b>                              |                                        |                          | 25°C           | 0 to<br>V <sub>DD</sub> – 1   |     |     |      |

| V <sub>ICR</sub> | Common-mode input voltage range       |                                        |                          | -40°C to 85°C  | 0 to<br>V <sub>DD</sub> – 1.5 |     |     | V    |

|                  |                                       |                                        |                          | 25°C           |                               | 84  |     |      |

| CMRR             | Common-mode rejection ratio           | V <sub>IC</sub> = V <sub>ICR</sub> min |                          | 85°C           |                               | 84  |     | dB   |

|                  |                                       |                                        |                          | -40°C          |                               | 83  |     |      |

|                  |                                       |                                        |                          | 25°C           |                               | 85  |     |      |

| k <sub>SVR</sub> | Supply-voltage rejection ratio        | $V_{DD} = 5 V \text{ to } 10$          | V                        | 85°C           |                               | 85  |     | dB   |

|                  |                                       |                                        |                          | -40°C          |                               | 83  |     |      |

|                  |                                       | V 4.V                                  | 1 4 0                    | 25°C           | 4.5                           | 4.7 |     | v    |

| V <sub>OH</sub>  | High-level output voltage             | $V_{ID} = 1 V,$                        | $I_{OH} = -4 \text{ mA}$ | 85°C           | 4.3                           |     |     | V    |

| V                |                                       | V _ 1V                                 |                          | 25°C           |                               | 210 | 300 | mV   |

| V <sub>OL</sub>  | Low-level output voltage              | $V_{ID} = -1 V,$                       | I <sub>OH</sub> = 4 mA   | 85°C           |                               |     | 400 | IIIV |

| 100              | Supply current (all four comparators) | Outputs low,                           | No load                  | 25°C           |                               | 35  | 80  | μA   |

| DD               | Supply current (an four comparators)  |                                        | No load                  | -40°C to 85°C  |                               |     | 125 | μΑ   |

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

#### recommended operating conditions

|                                                |      | TLC370 | 4M                    |      |

|------------------------------------------------|------|--------|-----------------------|------|

|                                                | MIN  | NOM    | MAX                   | UNIT |

| Supply voltage, V <sub>DD</sub>                | 4    | 5      | 16                    | V    |

| Common-mode input voltage, VIC                 | 0    |        | V <sub>DD</sub> – 1.5 | V    |

| High-level output current, I <sub>OH</sub>     |      |        | - 20                  | mA   |

| Low-level output current, I <sub>OL</sub>      |      |        | 20                    | mA   |

| Operating free-air temperature, T <sub>A</sub> | - 55 |        | 125                   | °C   |

## electrical characteristics at specified operating free-air temperature, $V_{DD}$ = 5 V, $V_{IC}$ = 0 (unless otherwise noted)

|                  |                                       |                               |                          | _              | TLC                           | 3704M |                |            |

|------------------|---------------------------------------|-------------------------------|--------------------------|----------------|-------------------------------|-------|----------------|------------|

|                  | PARAMETER                             | TEST CONDITIONS               |                          | T <sub>A</sub> | MIN                           | TYP   | MAX 5 10 15 30 | UNIT       |

| v                | Input offect veltere                  | V <sub>DD</sub> = 5 V to 10   | V,                       | 25°C           |                               | 1.2   | 5              | mV         |

| V <sub>IO</sub>  | Input offset voltage                  | $V_{IC} = V_{ICR}min$ ,       | See Note 3               | -55°C to 125°C |                               |       | 10             | mv         |

|                  | Input offect current                  | V 05V                         |                          | 25°C           |                               | 1     |                | pА         |

| l <sub>IO</sub>  | Input offset current                  | V <sub>IC</sub> = 2.5 V       |                          | 125°C          |                               |       | 15             | nA         |

|                  | land big a summer                     |                               |                          |                |                               | 5     |                | pА         |

| I <sub>IB</sub>  | Input bias current                    | V <sub>IC</sub> = 2.5 V       |                          | 125°C          |                               |       | 30             | nA         |

| .,               | <b>6</b>                              |                               |                          | 25°C           | 0 to<br>V <sub>DD</sub> – 1   |       |                |            |

| V <sub>ICR</sub> | Common-mode input voltage range       |                               |                          | –55°C to 125°C | 0 to<br>V <sub>DD</sub> – 1.5 |       |                | V          |

|                  |                                       |                               |                          | 25°C           |                               | 84    |                |            |

| CMRR             | Common-mode rejection ratio           | $V_{IC} = V_{ICR}min$         |                          | 125°C          |                               | 83    |                | dB         |

|                  |                                       |                               |                          | −55°C          |                               | 82    |                |            |

|                  |                                       |                               |                          | 25°C           |                               | 85    |                |            |

| k <sub>SVR</sub> | Supply-voltage rejection ratio        | $V_{DD} = 5 V \text{ to } 10$ | V                        | 125°C          |                               | 85    |                | dB         |

|                  |                                       |                               |                          | −55°C          |                               | 82    |                |            |

| v                |                                       | V 4.V                         | 1 1                      | 25°C           | 4.5                           | 4.7   |                |            |

| V <sub>OH</sub>  | High-level output voltage             | $V_{ID} = 1 V,$               | $I_{OH} = -4 \text{ mA}$ | 125°C          | 4.2                           |       |                | V          |

| V                |                                       | V 1V                          | 1 1 m 1                  | 25°C           |                               | 210   | 300            |            |

| V <sub>OL</sub>  | Low-level output voltage              | $V_{ID} = -1 V,$              | I <sub>OH</sub> = 4 mA   | 125°C          |                               |       | 500            | mV         |

|                  | Supply current (all four comparators) | Outputs low,                  | No load                  | 25°C           |                               | 35    | 80             |            |

| DD               | Supply current (an iour comparators)  | Sulpuis low,                  | INO IDAU                 | –55°C to 125°C |                               |       | 175            | μ <b>A</b> |

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

#### recommended operating conditions

|                                                |      | TLC370 | 4Q                    |      |

|------------------------------------------------|------|--------|-----------------------|------|

|                                                | MIN  | NOM    | MAX                   | UNIT |

| Supply voltage, V <sub>DD</sub>                | 3    | 5      | 16                    | V    |

| Common-mode input voltage, VIC                 | -0.2 |        | V <sub>DD</sub> – 1.5 | V    |

| High-level output current, I <sub>OH</sub>     |      |        | - 20                  | mA   |

| Low-level output current, I <sub>OL</sub>      |      |        | 20                    | mA   |

| Operating free-air temperature, T <sub>A</sub> | - 40 |        | 125                   | °C   |

# electrical characteristics at specified operating free-air temperature, $V_{DD}$ = 5 V, $V_{IC}$ = 0 (unless otherwise noted)

|                  |                                |                             |                          | _              | TLC3                       | 704Q |                                                                                                                                                                                                                                                             |      |

|------------------|--------------------------------|-----------------------------|--------------------------|----------------|----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                  | PARAMETER                      | TEST CO                     | NDITIONS                 | TA             | MIN                        | TYP  | P         MAX           .2         5           7         1           15         5           30         30           33         33           35         33           35         33           37         1           10         300           500         500 | UNIT |

| v                | Input offect veltage           | V <sub>DD</sub> = 5 V to 10 | ) V,                     | 25°C           |                            | 1.2  | 5                                                                                                                                                                                                                                                           | mV   |

| V <sub>IO</sub>  | Input offset voltage           | $V_{IC} = V_{ICR}min$ ,     | See Note 3               | -40°C to 125°C |                            |      | 7                                                                                                                                                                                                                                                           | mv   |

|                  | land affect an uncert          | N 05V                       |                          | 25°C           |                            | 1    |                                                                                                                                                                                                                                                             | pА   |

| IIO              | Input offset current           | V <sub>IC</sub> = 2.5 V     |                          | 125°C          |                            |      | 15                                                                                                                                                                                                                                                          | nA   |

|                  |                                | N 05V                       |                          | 25°C           |                            | 5    |                                                                                                                                                                                                                                                             | pА   |

| I <sub>IB</sub>  | Input bias current             | V <sub>IC</sub> = 2.5 V     |                          | 125°C          |                            |      | 30                                                                                                                                                                                                                                                          | nA   |

|                  | Common-mode input voltage      |                             |                          | 25°C           | 0 to V <sub>DD</sub> – 1   |      |                                                                                                                                                                                                                                                             | Ň    |

| VICR             | range                          | -                           |                          | -40°C to 125°C | 0 to V <sub>DD</sub> – 1.5 |      |                                                                                                                                                                                                                                                             | V    |

|                  |                                |                             |                          | 25°C           |                            | 84   |                                                                                                                                                                                                                                                             |      |

| CMRR             | Common-mode rejection ratio    | $V_{IC} = V_{ICR}min$       |                          | 125°C          |                            | 83   | dB                                                                                                                                                                                                                                                          | dB   |

|                  |                                |                             |                          | -40°C          |                            | 83   |                                                                                                                                                                                                                                                             |      |

|                  |                                |                             |                          | 25°C           |                            | 85   |                                                                                                                                                                                                                                                             |      |

| k <sub>SVR</sub> | Supply-voltage rejection ratio | V <sub>DD</sub> = 5 V to 10 | V                        | 125°C          |                            | 85   |                                                                                                                                                                                                                                                             | dB   |

|                  |                                |                             |                          | -40°C          |                            | 83   |                                                                                                                                                                                                                                                             |      |

|                  |                                |                             |                          | 25°C           | 4.5                        | 4.7  |                                                                                                                                                                                                                                                             |      |

| V <sub>OH</sub>  | High-level output voltage      | V <sub>ID</sub> = 1 V,      | $I_{OH} = -4 \text{ mA}$ | 125°C          | 4.2                        |      |                                                                                                                                                                                                                                                             | V    |

| .,               |                                |                             |                          | 25°C           |                            | 210  | 300                                                                                                                                                                                                                                                         |      |

| V <sub>OL</sub>  | Low-level output voltage       | $V_{ID} = -1 V,$            | I <sub>OH</sub> = 4 mA   | 125°C          |                            |      | 500                                                                                                                                                                                                                                                         | mV   |

|                  | Supply current (all four       | Outroute Leve               | No. lood                 | 25°C           |                            | 35   | 80                                                                                                                                                                                                                                                          |      |

| I <sub>DD</sub>  | comparators)                   | Outputs low,                | No load                  | -40°C to 125°C |                            |      | 175                                                                                                                                                                                                                                                         | μA   |

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## switching characteristics, $V_{DD}$ = 5 V, $T_A$ = 25°C

|                  | PARAMETER                                                     | TES                                   | T CONDITIONS      | TLC3704C, TLC3704I<br>TLC3704M, TLC3704Q |      |      | UNIT |    |

|------------------|---------------------------------------------------------------|---------------------------------------|-------------------|------------------------------------------|------|------|------|----|

|                  |                                                               |                                       |                   | MIN TYP MAX                              |      |      |      |    |

|                  |                                                               |                                       | Overdrive = 2 mV  |                                          | 4.5  |      |      |    |

|                  |                                                               |                                       | Overdrive = 5 mV  |                                          | 2.7  |      |      |    |

|                  | Descention defending the black back and the                   | f = 10 kHz,<br>C <sub>1</sub> = 50 pF | Overdrive = 10 mV |                                          | 1.9  |      | _    |    |

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output <sup>†</sup> | 0 <u>[</u> = 30 pi                    | Overdrive = 20 mV |                                          | 1.4  |      | μs   |    |

|                  |                                                               |                                       | Overdrive = 40 mV |                                          |      |      |      |    |

|                  |                                                               | V <sub>I</sub> = 1.4-V ste            | o at IN+          |                                          |      |      |      |    |

|                  | Propagation delay time, high-to-low-level output <sup>†</sup> |                                       | Overdrive = 2 mV  |                                          | 4    |      |      |    |

|                  |                                                               |                                       | Overdrive = 5 mV  | 2.3                                      |      |      |      |    |

|                  |                                                               | f = 10 kHz,<br>C <sub>L</sub> = 50 pF | Overdrive = 10 mV |                                          | 1.5  |      |      |    |

| t <sub>PHL</sub> |                                                               |                                       | Overdrive = 20 mV |                                          |      | 0.95 |      | μs |

|                  |                                                               |                                       | Overdrive = 40 mV | 0.65                                     |      |      |      |    |

|                  |                                                               | V <sub>I</sub> = 1.4-V ste            | o at IN+          |                                          | 0.15 |      |      |    |

| t <sub>f</sub>   | Fall time                                                     | f = 10 kHz,<br>C <sub>L</sub> = 50 pF | Overdrive = 50 mV |                                          | 50   |      | ns   |    |

| t <sub>r</sub>   | Rise time                                                     | f = 10 kHz,<br>C <sub>L</sub> = 50 pF | Overdrive = 50 mV |                                          | 125  |      | ns   |    |

<sup>†</sup> Simultaneous switching of inputs causes degradation in output response.

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## PRINCIPLES OF OPERATION

#### LinCMOS process

The LinCMOS process is a linear polysilicon-gate CMOS process. Primarily designed for single-supply applications, LinCMOS products facilitate the design of a wide range of high-performance analog functions from operational amplifiers to complex mixed-mode converters.

This short guide is intended to answer the most frequently asked questions related to the quality and reliability of LinCMOS products. Direct further questions to the nearest TI field sales office.

#### electrostatic discharge

CMOS circuits are prone to gate oxide breakdown when exposed to high voltages even if the exposure is only for very short periods of time. Electrostatic discharge (ESD) is one of the most common causes of damage to CMOS devices. It can occur when a device is handled without proper consideration for environmental electrostatic charges, e.g., during board assembly. If a circuit in which one amplifier from a dual op amp is being used and the unused pins are left open, high voltages tends to develop. If there is no provision for ESD protection, these voltages may eventually punch through the gate oxide and cause the device to fail. To prevent voltage buildup, each pin is protected by internal circuitry.

Standard ESD-protection circuits safely shunt the ESD current by providing a mechanism whereby one or more transistors break down at voltages higher than the normal operating voltages but lower than the breakdown voltage of the input gate. This type of protection scheme is limited by leakage currents which flow through the shunting transistors during normal operation after an ESD voltage has occurred. Although these currents are small, on the order of tens of nanoamps, CMOS amplifiers are often specified to draw input currents as low as tens of picoamps.

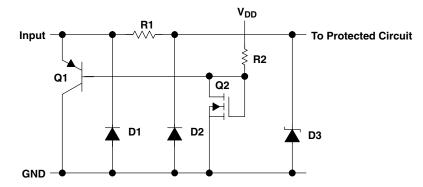

To overcome this limitation, TI design engineers developed the patented ESD-protection circuit shown in Figure 1. This circuit can withstand several successive 2-kV ESD pulses, while reducing or eliminating leakage currents that may be drawn through the input pins. A more detailed discussion of the operation of the TI ESD-protection circuit is presented on the next page.

All input and output pins on LinCMOS and Advanced LinCMOS products have associated ESD-protection circuitry that undergoes qualification testing to withstand 2000 V discharged from a 100-pF capacitor through a 1500- $\Omega$  resistor (human body model) and 200 V from a 100-pF capacitor with no current-limiting resistor (charged device model). These tests simulate both operator and machine handling of devices during normal test and assembly operations.

Figure 1. LinCMOS ESD-Protection Schematic

## PRINCIPLES OF OPERATION

#### input protection circuit operation

Texas Instruments patented protection circuitry allows for both positive- and negative-going ESD transients. These transients are characterized by extremely fast rise times and usually low energies, and can occur both when the device has all pins open and when it is installed in a circuit.

#### positive ESD transients

Initial positive charged energy is shunted through Q1 to V<sub>SS</sub>. Q1 turns on when the voltage at the input rises above the voltage on the V<sub>DD</sub> pin by a value equal to the V<sub>BE</sub> of Q1. The base current increases through R2 with input current as Q1 saturates. The base current through R2 forces the voltage at the drain and gate of Q2 to exceed its threshold level (V<sub>T</sub> ~ 22 to 26 V) and turn Q2 on. The shunted input current through Q1 to V<sub>SS</sub> is now shunted through the n-channel enhancement-type MOSFET Q2 to V<sub>SS</sub>. If the voltage on the input pin continues to rise, the breakdown voltage of the zener diode D3 is exceeded, and all remaining energy is dissipated in R1 and D3. The breakdown voltage of D3 is designed to be 24 to 27 V, which is well below the gate-oxide voltage of the circuit to be protected.

#### negative ESD transients

The negative charged ESD transients are shunted directly through D1. Additional energy is dissipated in R1 and D2 as D2 becomes forward biased. The voltage seen by the protected circuit is -0.3 V to -1 V (the forward voltage of D1 and D2).

#### circuit-design considerations

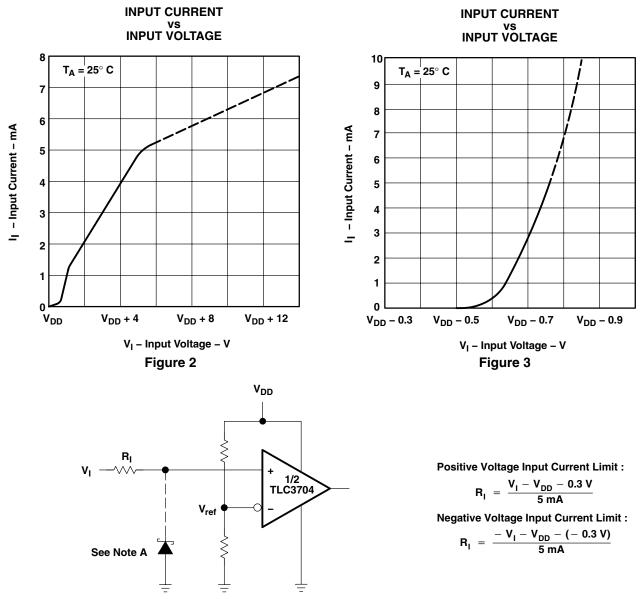

LinCMOS products are being used in actual circuit environments that have input voltages that exceed the recommended common-mode input voltage range and activate the input protection circuit. Even under normal operation, these conditions occur during circuit power up or power down, and in many cases, when the device is being used for a signal conditioning function. The input voltages can exceed  $V_{ICR}$  and not damage the device only if the inputs are current limited. The recommended current limit shown on most product data sheets is  $\pm 5$  mA. Figures 2 and 3 show typical characteristics for input voltage versus input current.

Normal operation and correct output state can be expected even when the input voltage exceeds the positive supply voltage. Again, the input current should be externally limited even though internal positive current limiting is achieved in the input protection circuit by the action of Q1. When Q1 is on, it saturates and limits the current to approximately 5-mA collector current by design. When saturated, Q1 base current increases with input current. This base current is forced into the V<sub>DD</sub> pin and into the device I<sub>DD</sub> or the V<sub>DD</sub> supply through R2 producing the current limiting effects shown in Figure 2. This internal limiting lasts only as long as the input voltage is below the V<sub>T</sub> of Q2.

When the input voltage exceeds the negative supply voltage, normal operation is affected and output voltage states may not be correct. Also, the isolation between channels of multiple devices (duals and quads) can be severely affected. External current limiting must be used since this current is directly shunted by D1 and D2 and no internal limiting is achieved. If normal output voltage states are required, an external input voltage clamp is required (see Figure 4).

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## **PRINCIPLES OF OPERATION**

### circuit-design considerations (continued)

NOTE A: If the correct input state is required when the negative input exceeds GND, a Schottky clamp is required.

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## PARAMETER MEASUREMENT INFORMATION

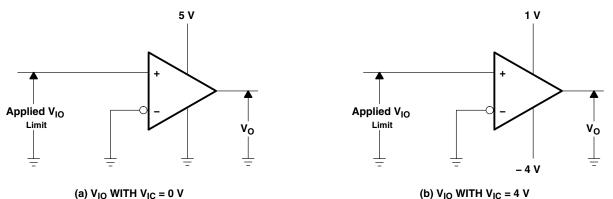

The TLC3704 contains a digital output stage which, if held in the linear region of the transfer curve, can cause damage to the device. Conventional operational amplifier/comparator testing incorporates the use of a servo loop which is designed to force the device output to a level within this linear region. Since the servo-loop method of testing cannot be used, we offer the following alternatives for measuring parameters such as input offset voltage, common-mode rejection, etc.

To verify that the input offset voltage falls within the limits specified, the limit value is applied to the input as shown in Figure 5(a). With the noninverting input positive with respect to the inverting input, the output should be high. With the input polarity reversed, the output should be low.

A similar test can be made to verify the input offset voltage at the common-mode extremes. The supply voltages can be slewed as shown in Figure 5(b) for the V<sub>ICR</sub> test, rather than changing the input voltages, to provide greater accuracy.

A close approximation of the input offset voltage can be obtained by using a binary search method to vary the differential input voltage while monitoring the output state. When the applied input voltage differential is equal, but opposite in polarity, to the input offset voltage, the output changes states.

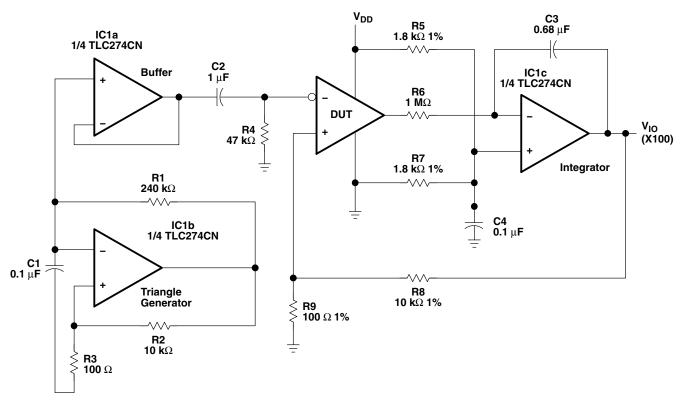

Figure 6 illustrates a practical circuit for direct dc measurement of input offset voltage that does not bias the comparator in the linear region. The circuit consists of a switching mode servo loop in which IC1a generates a triangular waveform of approximately 20-mV amplitude. IC1b acts as a buffer, with C2 and R4 removing any residual d.c. offset. The signal is then applied to the inverting input of the comparator under test, while the noninverting input is driven by the output of the integrator formed by IC1c through the voltage divider formed by R8 and R9. The loop reaches a stable operating point when the output of the comparator under test has a duty cycle of exactly 50%, which can only occur when the incoming triangle wave is sliced symmetrically or when the voltage at the noninverting input exactly equals the input offset voltage.

Voltage divider R8 and R9 provides an increase in the input offset voltage by a factor of 100 to make measurement easier. The values of R5, R7, R8, and R9 can significantly influence the accuracy of the reading; therefore, it is suggested that their tolerance level be one percent or lower.

Measuring the extremely low values of input current requires isolation from all other sources of leakage current and compensation for the leakage of the test socket and board. With a good picoammeter, the socket and board leakage can be measured with no device in the socket. Subsequently, this open socket leakage value can be subtracted from the measurement obtained with a device in the socket to obtain the actual input current of the device.

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

### PARAMETER MEASUREMENT INFORMATION

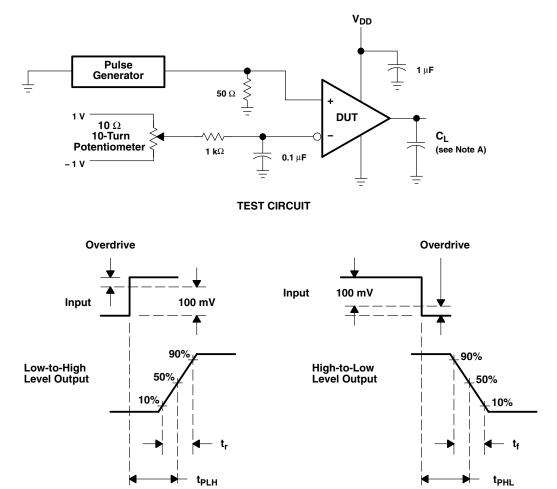

Response time is defined as the interval between the application of an input step function and the instant when the output reaches 50% of its maximum value. Response time for the low-to-high-level output is measured from the leading edge of the input pulse, while response time for the high-to-low-level output is measured from the trailing edge of the input pulse. Response time measurement at low input signal levels can be greatly affected by the input offset voltage. The offset voltage should be balanced by the adjustment at the inverting input as shown in Figure 7, so that the circuit is just at the transition point. A low signal, for example 105-mV or 5-mV overdrive, causes the output to change state.

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## PARAMETER MEASUREMENT INFORMATION

VOLTAGE WAVEFORMS

NOTE A:  $C_L$  includes probe and jig capacitance.

#### Figure 7. Response, Rise, and Fall Times Circuit and Voltage Waveforms

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## **TYPICAL CHARACTERISTICS**

#### **Table of Graphs**

|                  |                                                                |                                                              | FIGURE         |

|------------------|----------------------------------------------------------------|--------------------------------------------------------------|----------------|

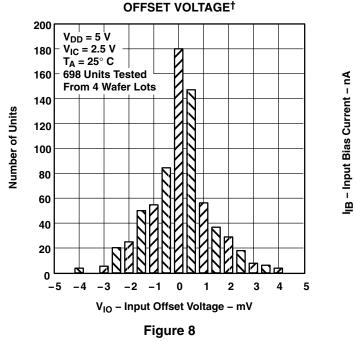

| V <sub>IO</sub>  | Input offset voltage                                           | Distribution                                                 | 8              |

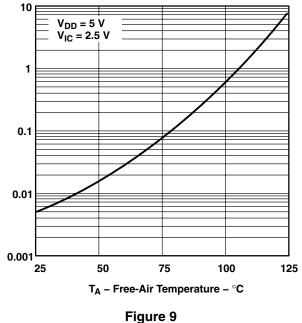

| I <sub>IB</sub>  | Input bias current                                             | vs Free-air temperature                                      | 9              |

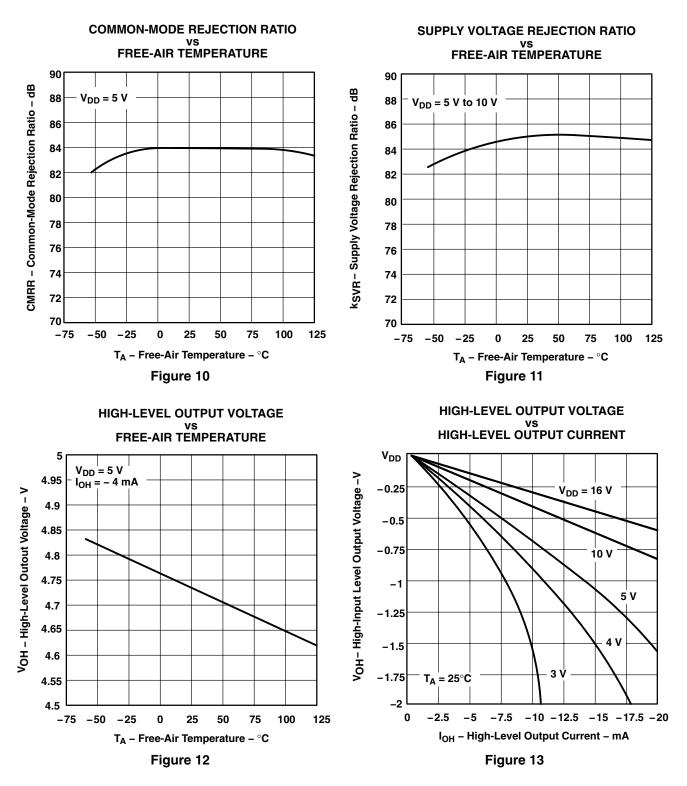

| CMRR             | Common-mode rejection ratio                                    | vs Free-air temperature                                      | 10             |

| k <sub>SVR</sub> | Supply-voltage rejection ratio                                 | vs Free-air temperature                                      | 11             |

| V <sub>OH</sub>  | High-level output current                                      | vs Free-air temperature<br>vs High-level output current      | 12<br>13       |

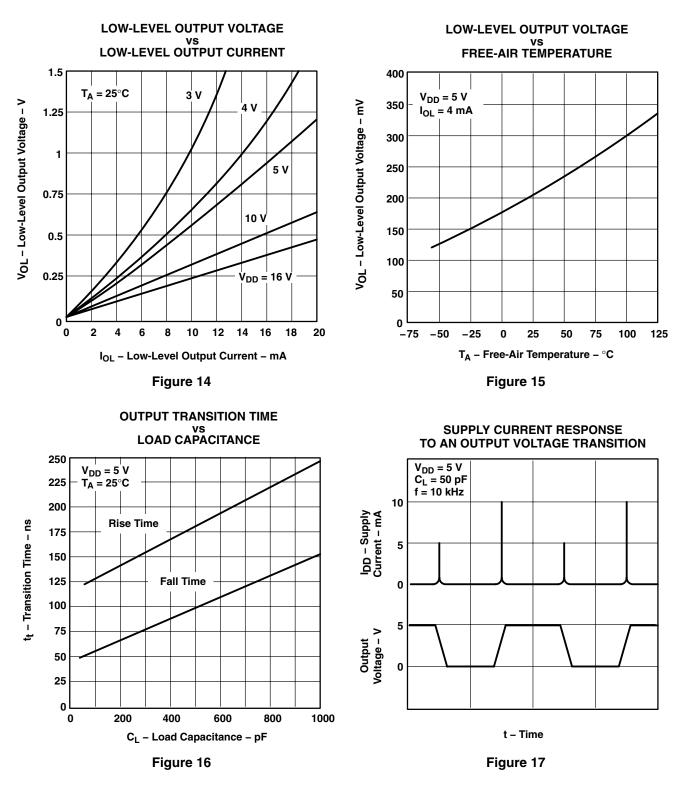

| V <sub>OL</sub>  | Low-level output voltage                                       | vs Low-level output current<br>vs Free-air temperature       | 14<br>15       |

| tt               | Output transition time                                         | vs Load capacitance                                          | 16             |

|                  | Supply current response to an output voltage transition        |                                                              | 17             |

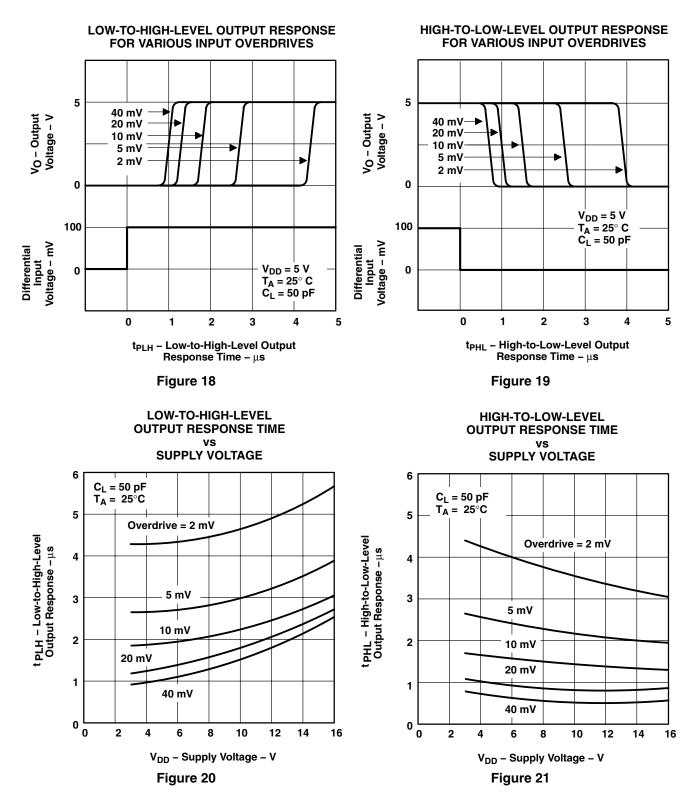

|                  | Low-to-high-level output response for various input overdrives |                                                              | 18             |

|                  | High-to-low-level output response for various input overdrives |                                                              | 19             |

| t <sub>PLH</sub> | Low-to-high-level output response time                         | vs Supply voltage                                            | 20             |

| t <sub>PHL</sub> | High-to-low-level output response time                         | vs Supply voltage                                            | 21             |

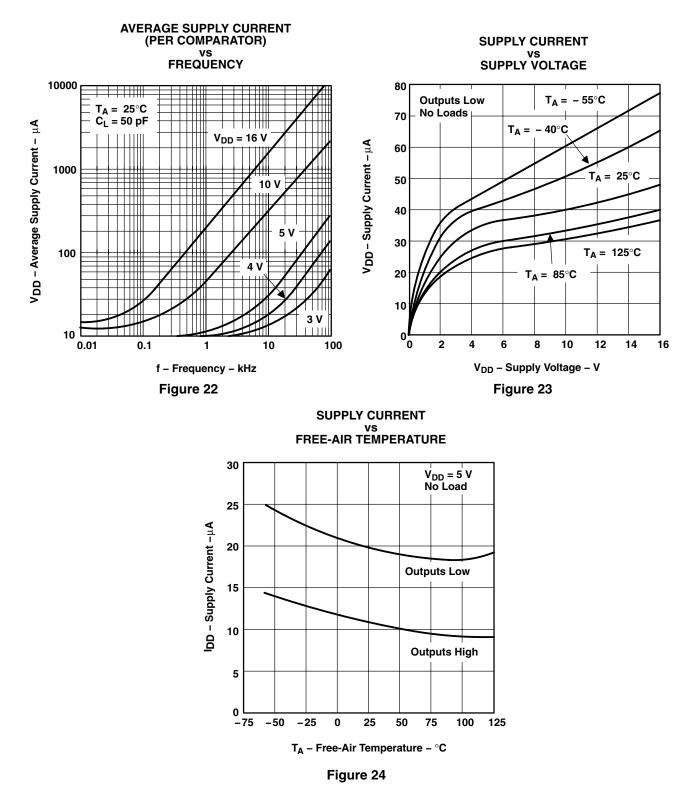

| I <sub>DD</sub>  | Supply current                                                 | vs Frequency<br>vs Supply voltage<br>vs Free-air temperature | 22<br>23<br>24 |

##

#### INPUT BIAS CURRENT vs FREE-AIR TEMPERATURE<sup>†</sup>

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

**TYPICAL CHARACTERISTICS<sup>†</sup>**

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## **TYPICAL CHARACTERISTICS<sup>†</sup>**

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

#### **TYPICAL CHARACTERISTICS**

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## **TYPICAL CHARACTERISTICS<sup>†</sup>**

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

### **APPLICATION INFORMATION**

The inputs should always remain within the supply rails in order to avoid forward biasing the diodes in the electrostatic discharge (ESD) protection structure. If either input exceeds this range, the device is not damaged as long as the input is limited to less than 5 mA. To maintain the expected output state, the inputs must remain within the common-mode range. For example, at  $25^{\circ}$ C with  $V_{DD} = 5$  V, both inputs must remain between – 0.2 V and 4 V to ensure proper device operation. To ensure reliable operation, the supply should be decoupled with a capacitor (0.1  $\mu$ F) that is positioned as close to the device as possible.

Output and supply current limitations should be watched carefully since the TLC3704 does not provide current protection. For example, each output can source or sink a maximum of 20 mA; however, the total current to ground can only be an absolute maximum of 60 mA. This prohibits sinking 20 mA from each of the four outputs simultaneously since the total current to ground would be 80 mA.

The TLC3704 has internal ESD-protection circuits that prevents functional failures at voltages up to 2000 V as tested under MIL-STD-883C, Method 3015.2; however, care should be exercised in handling these devices as exposure to ESD may result in the degradation of the device parametric performance.

|                                              | FIGURE |

|----------------------------------------------|--------|

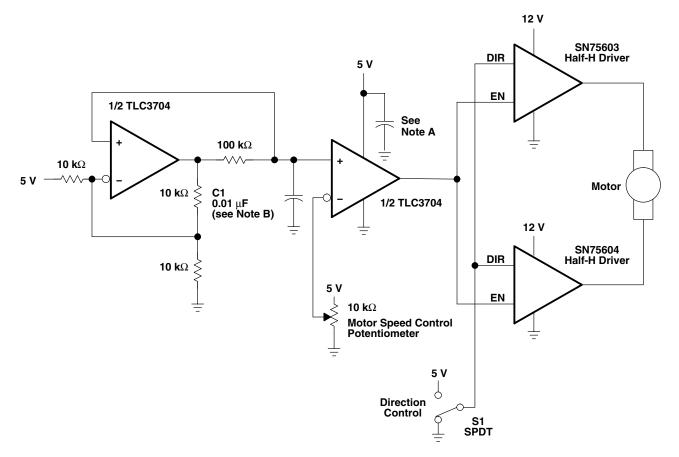

| Pulse-width-modulated motor speed controller | 25     |

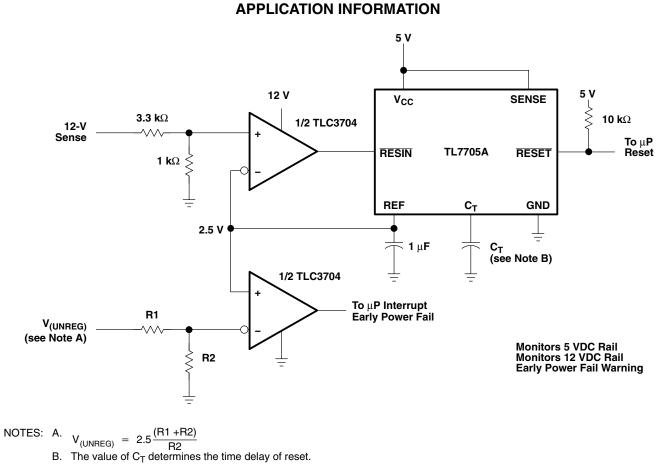

| Enhanced supply supervisor                   | 26     |

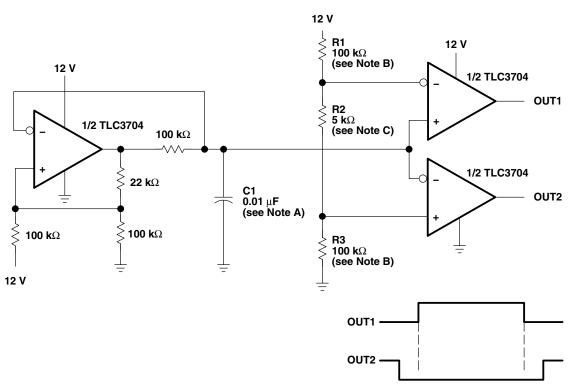

| Two-phase nonoverlapping clock generator     | 27     |

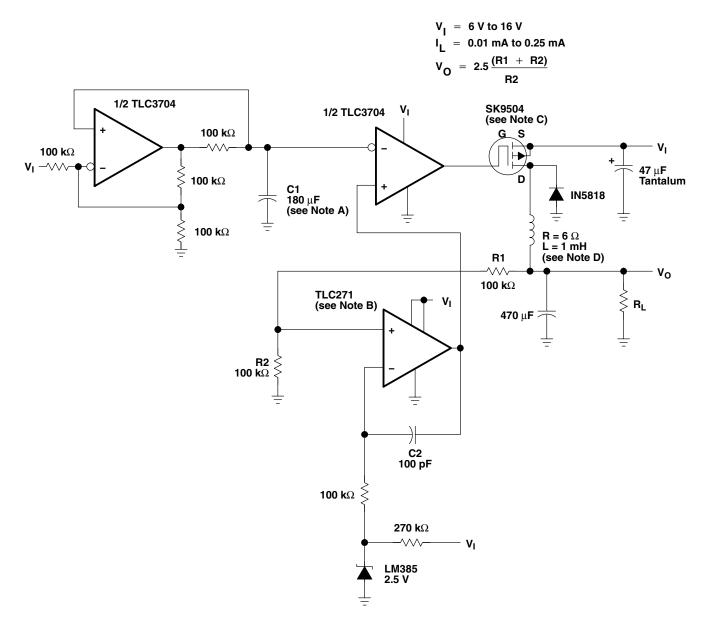

| Micropower switching regulator               | 28     |

#### **Table of Applications**

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

**APPLICATION INFORMATION**

NOTES: A. The recommended minimum capacitance is 10  $\mu$ F to eliminate common ground switching noise. B. Adjust C1 for change in oscillator frequency

Figure 25. Pulse-Width-Modulated Motor Speed Controller

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

Figure 26. Enhanced Supply Supervisor

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

## **APPLICATION INFORMATION**

- NOTES: A. Adjust C1 for a change in oscillator frequency where:  $1/f = 1.85(100 \text{ k}\Omega)C1$

- B. Adjust R1 and R3 to change duty cycle

- C. Adjust R2 to change deadtime

#### Figure 27. Two-Phase Nonoverlapping Clock Generator

SLCS117C - NOVEMBER 1986 - REVISED NOVEMBER 2009

#### **APPLICATION INFORMATION**

NOTES: A. Adjust C1 for a change in oscillator frequency

- B. TLC271 Tie pin 8 to pin 7 for low bias operation C. SK9504 VDS = 40 V

- - IDS = 1 Awill

- D. To achieve microampere current drive, the inductance of the circuit must be increased.

Figure 28. Micropower Switching Regulator

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)     | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5)                | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|---------------------|--------------------------------------|----------------------|--------------|----------------------------------------|---------|

| 5962-9096901M2A  | ACTIVE        | LCCC         | FK                 | 20   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-<br>9096901M2A<br>TLC3704<br>MFKB | Samples |

| 5962-9096901MCA  | ACTIVE        | CDIP         | J                  | 14   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-9096901MC<br>A<br>TLC3704MJB      | Samples |

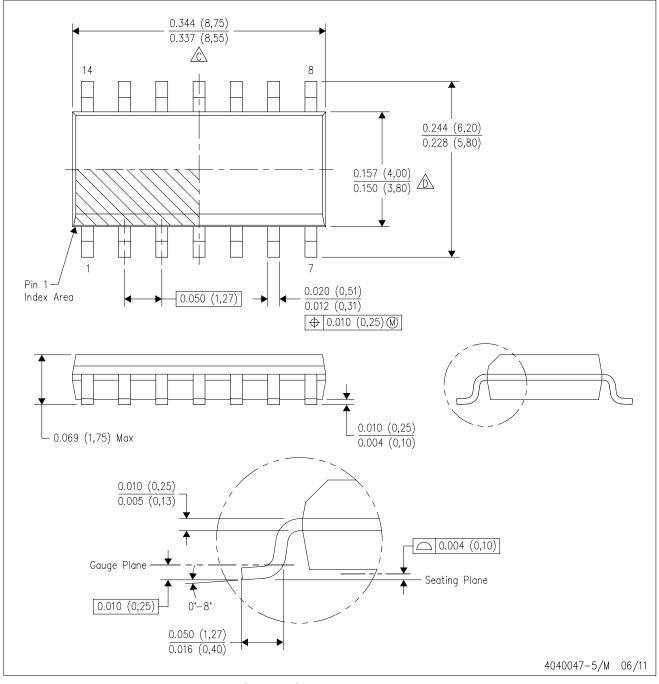

| TLC3704CD        | ACTIVE        | SOIC         | D                  | 14   | 50             | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | 0 to 70      | TLC3704C                               | Samples |

| TLC3704CDR       | ACTIVE        | SOIC         | D                  | 14   | 2500           | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | 0 to 70      | TLC3704C                               | Samples |

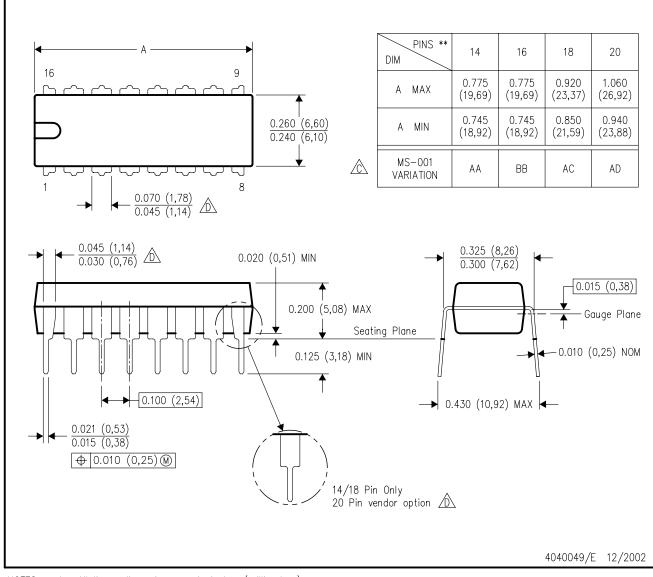

| TLC3704CN        | ACTIVE        | PDIP         | N                  | 14   | 25             | RoHS & Green        | NIPDAU                               | N / A for Pkg Type   | 0 to 70      | TLC3704CN                              | Samples |

| TLC3704CNSR      | ACTIVE        | SO           | NS                 | 14   | 2000           | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | 0 to 70      | TLC3704                                | Samples |

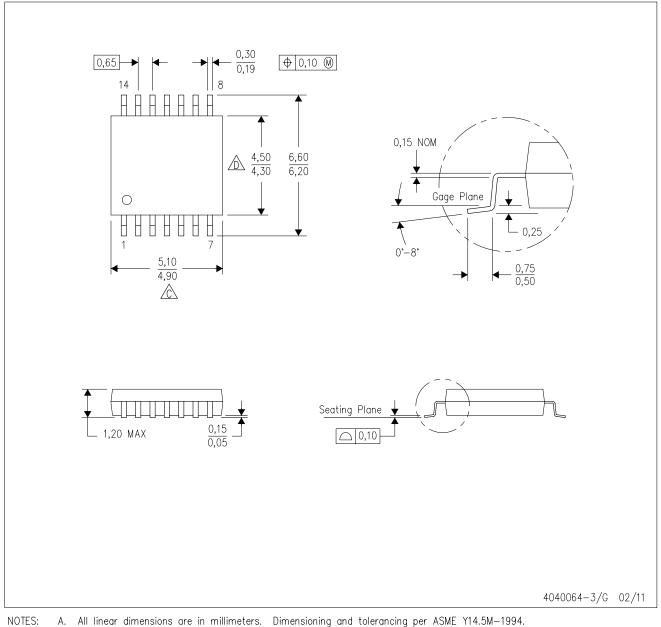

| TLC3704CPW       | ACTIVE        | TSSOP        | PW                 | 14   | 90             | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | 0 to 70      | P3704                                  | Samples |

| TLC3704CPWR      | ACTIVE        | TSSOP        | PW                 | 14   | 2000           | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | 0 to 70      | P3704                                  | Samples |

| TLC3704ID        | ACTIVE        | SOIC         | D                  | 14   | 50             | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | TLC3704I                               | Samples |

| TLC3704IDG4      | ACTIVE        | SOIC         | D                  | 14   | 50             | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | TLC3704I                               | Samples |

| TLC3704IDR       | ACTIVE        | SOIC         | D                  | 14   | 2500           | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | TLC3704I                               | Samples |

| TLC3704IN        | ACTIVE        | PDIP         | N                  | 14   | 25             | RoHS & Green        | NIPDAU                               | N / A for Pkg Type   | -40 to 85    | TLC3704IN                              | Samples |

| TLC3704IPW       | ACTIVE        | TSSOP        | PW                 | 14   | 90             | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | P3704I                                 | Samples |

| TLC3704IPWR      | ACTIVE        | TSSOP        | PW                 | 14   | 2000           | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | P3704I                                 | Samples |

| TLC3704MD        | ACTIVE        | SOIC         | D                  | 14   | 50             | RoHS & Green        | NIPDAU                               | Level-1-260C-UNLIM   | -55 to 125   | TLC3704MD                              | Samples |

| TLC3704MFKB      | ACTIVE        | LCCC         | FK                 | 20   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-<br>9096901M2A<br>TLC3704<br>MFKB | Samples |

| TLC3704MJB       | ACTIVE        | CDIP         | J                  | 14   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | 5962-9096901MC<br>A                    | Samples |

14-Oct-2022

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins Pack<br>Qt | • | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|-----------------|---|-----------------|-------------------------------|---------------|--------------|-------------------------|---------|

|                  |               |              |                    |                 |   |                 | (6)                           |               |              |                         |         |

|                  |               |              |                    |                 |   |                 |                               |               |              | TLC3704MJB              |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TLC3704, TLC3704M :

Catalog : TLC3704

#### • Automotive : TLC3704-Q1, TLC3704-Q1

Military : TLC3704M

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Automotive Q100 devices qualified for high-reliability automotive applications targeting zero defects

- Military QML certified for Military and Defense Applications

Texas

\*All dimensions are nominal

STRUMENTS

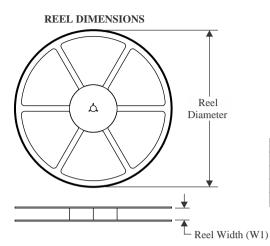

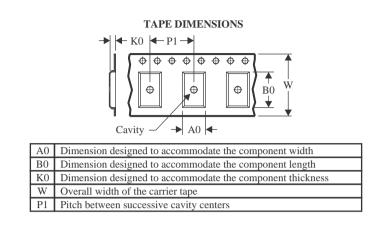

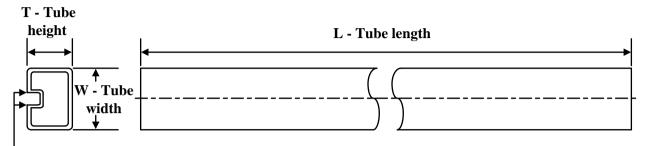

## TAPE AND REEL INFORMATION

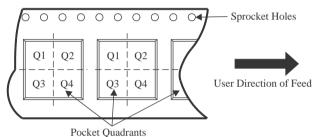

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLC3704CDR  | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| TLC3704CNSR | SO              | NS                 | 14 | 2000 | 330.0                    | 16.4                     | 8.2        | 10.5       | 2.5        | 12.0       | 16.0      | Q1               |

| TLC3704CPWR | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TLC3704IDR  | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| TLC3704IPWR | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com

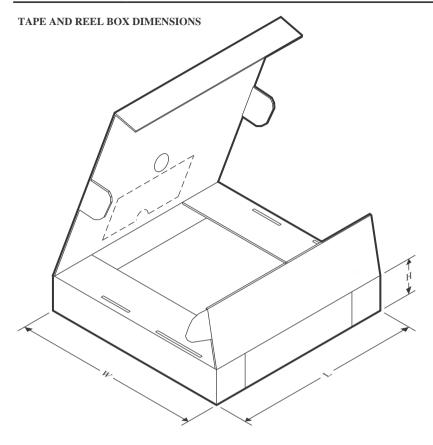

## PACKAGE MATERIALS INFORMATION

3-Jun-2022

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLC3704CDR  | SOIC         | D               | 14   | 2500 | 350.0       | 350.0      | 43.0        |

| TLC3704CNSR | SO           | NS              | 14   | 2000 | 356.0       | 356.0      | 35.0        |

| TLC3704CPWR | TSSOP        | PW              | 14   | 2000 | 356.0       | 356.0      | 35.0        |

| TLC3704IDR  | SOIC         | D               | 14   | 2500 | 350.0       | 350.0      | 43.0        |

| TLC3704IPWR | TSSOP        | PW              | 14   | 2000 | 356.0       | 356.0      | 35.0        |

## TEXAS INSTRUMENTS

www.ti.com

3-Jun-2022

## TUBE

## - B - Alignment groove width

| *All dimensions are r | nominal |

|-----------------------|---------|

|-----------------------|---------|

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| 5962-9096901M2A | FK           | LCCC         | 20   | 1   | 506.98 | 12.06  | 2030   | NA     |

| TLC3704CD       | D            | SOIC         | 14   | 50  | 505.46 | 6.76   | 3810   | 4      |

| TLC3704CN       | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230  | 4.32   |

| TLC3704CPW      | PW           | TSSOP        | 14   | 90  | 530    | 10.2   | 3600   | 3.5    |

| TLC3704ID       | D            | SOIC         | 14   | 50  | 505.46 | 6.76   | 3810   | 4      |

| TLC3704IDG4     | D            | SOIC         | 14   | 50  | 505.46 | 6.76   | 3810   | 4      |

| TLC3704IN       | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230  | 4.32   |

| TLC3704IPW      | PW           | TSSOP        | 14   | 90  | 530    | 10.2   | 3600   | 3.5    |

| TLC3704MD       | D            | SOIC         | 14   | 50  | 505.46 | 6.76   | 3810   | 4      |

| TLC3704MFKB     | FK           | LCCC         | 20   | 1   | 506.98 | 12.06  | 2030   | NA     |

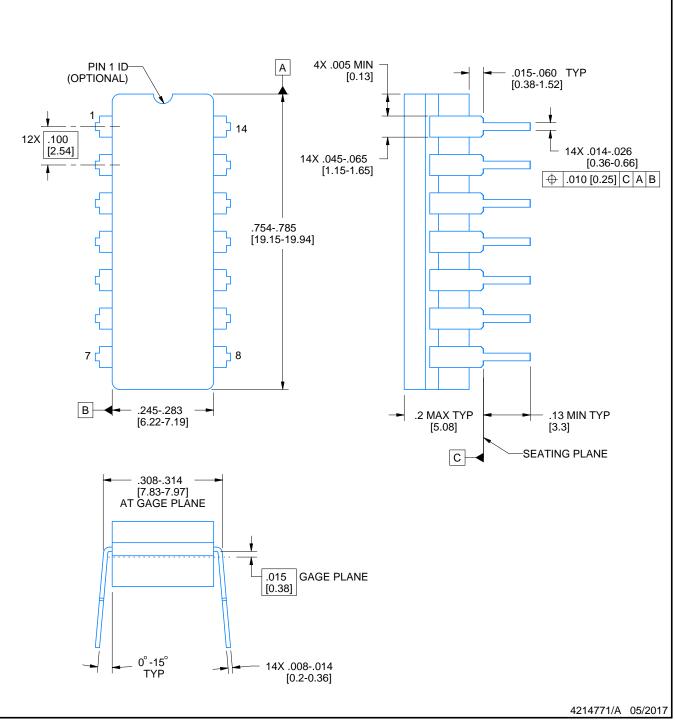

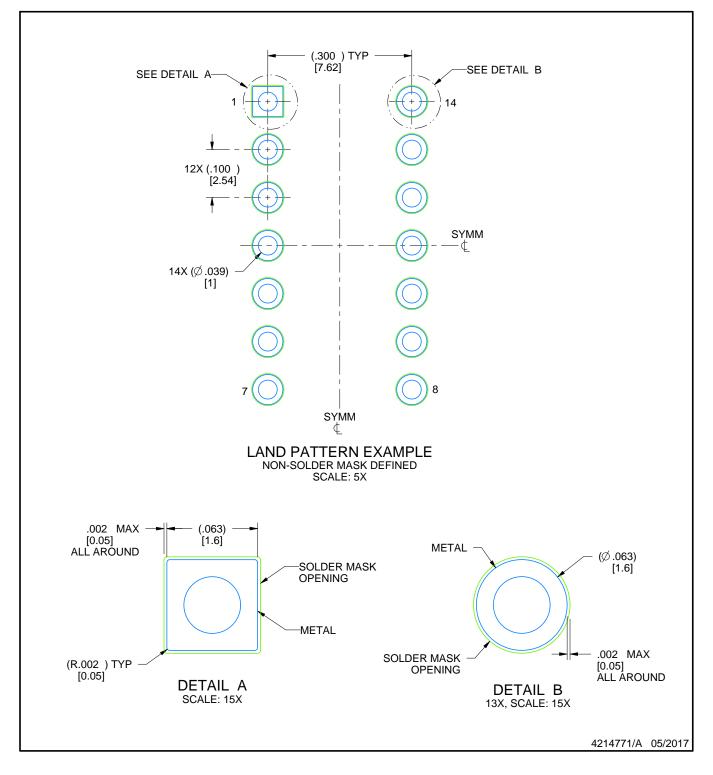

## **GENERIC PACKAGE VIEW**

## CDIP - 5.08 mm max height

CERAMIC DUAL IN LINE PACKAGE