## 用于

# 7 位 DC 和 7 位全局 BC LED 灯的 16 通道、16 位、ES-PWM, 完全自我 诊断 LED 驱动器

查询样品: TLC5948A

### 特性

- 16 个恒定流入电流源输出通道

- 支持最大 DC 和 BC 数据的灌电流能力:

- 2mA 至 45 mA (V<sub>CC</sub> ≤ 3.6V)

- 2 mA  $\Xi$  60 mA ( $V_{CC}$  > 3.6 V)

- 点校正 (DC):

- 0% 至 100% 范围的 7-位 (128 步)

- 全局亮度控制 (BC):

- 25% 至 100% 范围的 7-位 (128 步)

- 增强型光谱或传统 PWM灰度控制 (GS):

- 16-位 (65,536 步)

- LED 电源电压: 高达 10V

- VCC: 3.0V 至 5.5V

- 恒定电流精度:

- 通道间: ±0.6% (典型值), ±2% (最大值)

- 设备间: ±1% (典型值), ±4% (最大值)

- 数据传输速率: 33MHz

- 灰度控制时钟: 33MHz

- 自动显示重复和自动数据刷新

- 显示计时复位

- 用来大大减少 VCC 电流的省电模式

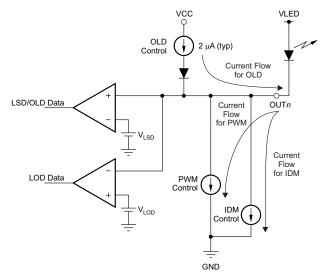

- 支持无形检测

模式 (IDM) 的开路检测 (LOD) 和短路检测 (LSD)

• 输出泄露侦测 (OLD)

- 电流基准端短路标记 (ISF)

- 热关断 (TSD) 和错误标记 (TEF)

- 预热报警 (PTW)

- 防止涌入电流的四通道成组延迟交换

- 工作温度范围: -40°C 至 +85°C

### 应用范围

- LED 视频显示屏

- LED 标识牌

## 说明

TLC5948 是一款 16 通道、恒定流入电流吸收 LED 驱动器。每个通道具有一个独立可调节,脉宽调制 (PWM) 灰度 (GS) 亮度控制,此控制有 65,536 步长 和128 步长的恒定电流点校正 (DC)。 DC 调节通道间的亮度偏差。 所有通道都有一个 128-步全局亮度控制(BC)。 BC 调节与其它 LED 驱动器的亮度偏差。 可通过一个串行接口端口来访问 GS,DC 和 BC 数据。

TLC5948 有 6 个错误信号: LED 打开侦测 (LOD), LED 短路侦测 (LSD), 输出泄露侦测 (OLD), 基准电流终端短路标志侦测 (ISF), 预热警告 (PTW), 和热错误标记 (TEF)。 可使用一个串行接口端口来读取错误检测结果。

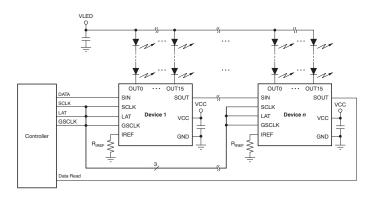

典型应用电路(多菊花链 TLC5948As)

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

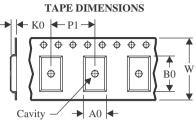

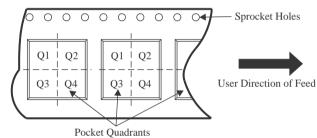

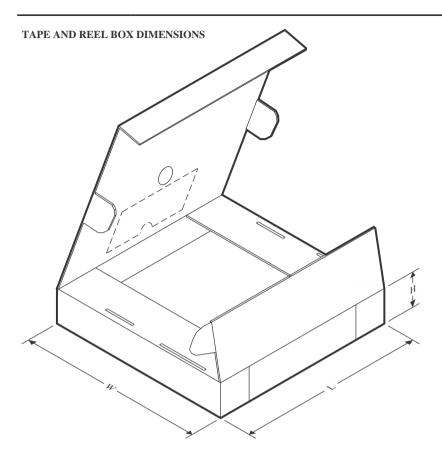

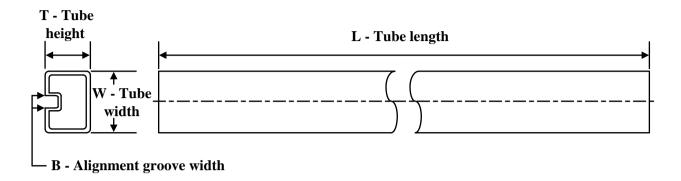

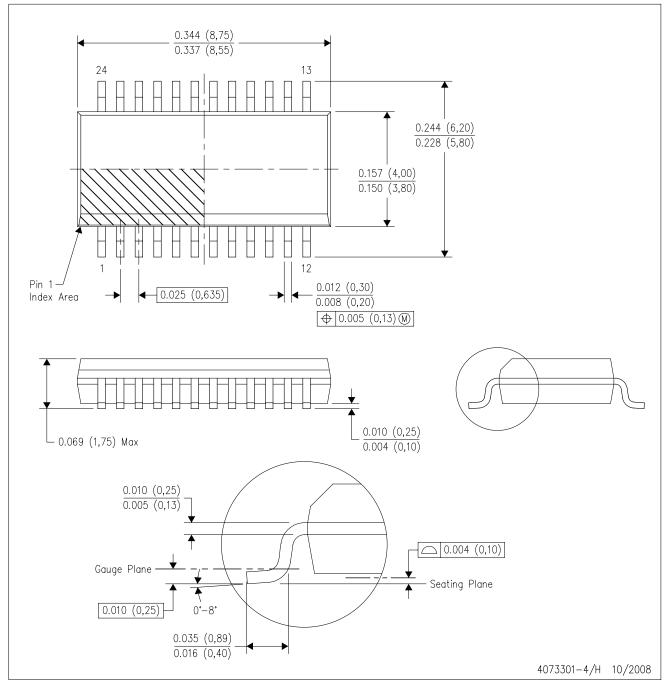

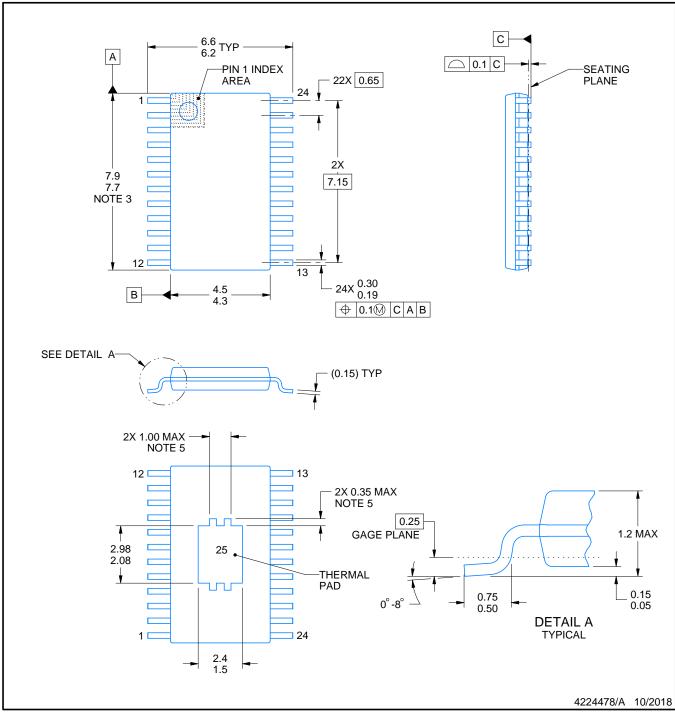

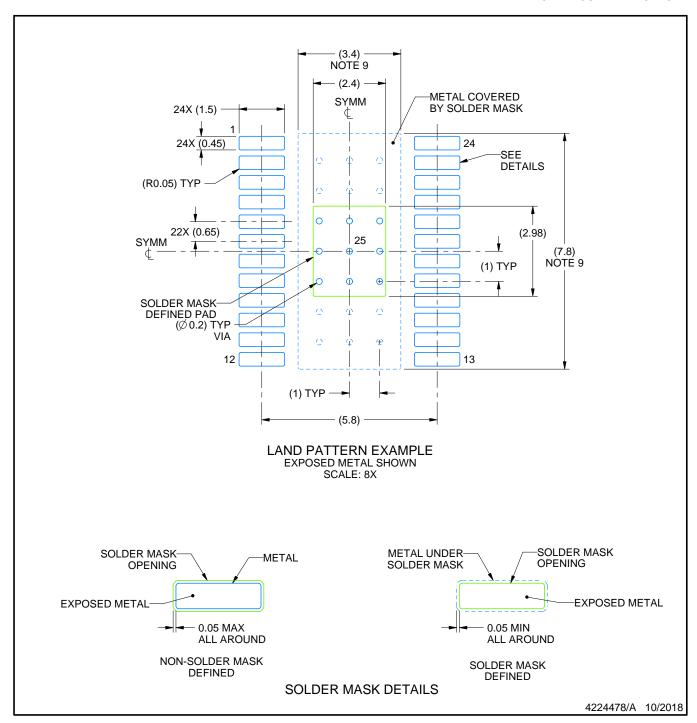

### PACKAGE AND ORDERING INFORMATION(1)

| PRODUCT   | PACKAGE-LEAD        | PACKAGE<br>DESIGNATOR | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|-----------|---------------------|-----------------------|--------------------|------------------------------|

|           | CCOD 24 OCOD 24     | DDO                   | TLC5948ADBQR       | Tape and Reel, 2500          |

| TI 05049A | SSOP-24, QSOP-24    | DBQ                   | TLC5948ADBQ        | Tube, 50                     |

| TLC5948A  | LITOCOD OLD DADTH   | DWD                   | TLC5948APWPR       | Tape and Reel, 2000          |

|           | HTSSOP-24 PowerPAD™ | PWP                   | TLC5948APWP        | Tube, 60                     |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at <a href="https://www.ti.com">www.ti.com</a>.

#### ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range, unless otherwise noted.

|                                        |                                          | VALU | VALUE                 |      |

|----------------------------------------|------------------------------------------|------|-----------------------|------|

|                                        |                                          | MIN  | MAX                   | UNIT |

|                                        | VCC                                      | -0.3 | +6.0                  | V    |

| Value == (2)                           | SIN, SCLK, LAT, GSCLK, IREF              | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| Voltage (2)                            | SOUT                                     | -0.3 | V <sub>CC</sub> + 0.3 | V    |

|                                        | OUT0 to OUT15                            | -0.3 | +11                   | V    |

| Current                                | OUT0 to OUT15                            |      | +70                   | mA   |

| Tomporatura                            | Operating junction, T <sub>J</sub> (max) |      | +150                  | °C   |

| Temperature                            | Storage, T <sub>stg</sub>                | -55  | +150                  | °C   |

| Electrostatic discharge (ESD) ratings: | Human body model (HBM)                   |      | 4000                  | V    |

|                                        | Charged device model (CDM)               |      | 2000                  | V    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

#### THERMAL INFORMATION

|                         |                                              | TLC59               | TLC5948A        |        |  |

|-------------------------|----------------------------------------------|---------------------|-----------------|--------|--|

|                         | THERMAL METRIC <sup>(1)</sup>                | DBQ<br>(SSOP, QSOP) | PWP<br>(HTSSOP) | UNITS  |  |

|                         |                                              | 24 PINS             | 24 PINS         |        |  |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 80.4                | 39.9            |        |  |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 44.2                | 23.2            |        |  |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 33.5                | 21.5            | 00/14/ |  |

| Ψ <sub>JT</sub>         | Junction-to-top characterization parameter   | 8.8                 | 0.6             | °C/W   |  |

| ΨЈВ                     | Junction-to-board characterization parameter | 33.2                | 21.3            |        |  |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | N/A                 | 3.8             |        |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> All voltages are with respect to device ground terminal.

## **RECOMMENDED OPERATING CONDITIONS**

At  $T_A = -40$ °C to +85°C and  $V_{CC} = 3$  V to 5.5 V, unless otherwise noted.

|                          |                                      |                                                                            | TLC5948A              |                     |      |

|--------------------------|--------------------------------------|----------------------------------------------------------------------------|-----------------------|---------------------|------|

|                          | PARAMETER                            | TEST CONDITIONS                                                            | MIN                   | NOM MAX             | UNIT |

| DC CHARAC                | TERISTICS                            | •                                                                          | •                     |                     |      |

| V <sub>CC</sub>          | Supply voltage                       |                                                                            | 3.0                   | 5.5                 | V    |

| Vo                       | Voltage applied to output            | OUT0 to OUT15                                                              |                       | 10                  | V    |

| V <sub>IH</sub>          | High-level input voltage             | SIN, SCLK, LAT, GSCLK                                                      | 0.7 × V <sub>CC</sub> | V <sub>CC</sub>     | V    |

| V <sub>IL</sub>          | Low-level input voltage              | SIN, SCLK, LAT, GSCLK                                                      | GND                   | $0.3 \times V_{CC}$ | V    |

| I <sub>OH</sub>          | High-level output current            | SOUT                                                                       |                       | -2                  | mA   |

| I <sub>OL</sub>          | Low-level output current             | SOUT                                                                       |                       | 2                   | mA   |

| 1                        | Constant output sink ourrent         | OUT0 to OUT15,<br>3 V ≤ V <sub>CC</sub> ≤ 3.6 V                            |                       | 45                  | mA   |

| l <sub>OLC</sub>         | Constant output sink current         | OUT0 to OUT15,<br>3.6 V < V <sub>CC</sub> ≤ 5.5 V                          |                       | 60                  | mA   |

| T <sub>A</sub>           | Operating free-air temperature range |                                                                            | -40                   | +85                 | °C   |

| T <sub>J</sub>           | Operating junction temperature range |                                                                            | -40                   | +125                | °C   |

| AC CHARAC                | TERISTICS                            |                                                                            |                       |                     |      |

| f <sub>CLK</sub> (SCLK)  | Data shift clock frequency           | SCLK                                                                       |                       | 33                  | MHz  |

| f <sub>CLK (GSCLK)</sub> | Grayscale control clock frequency    | GSCLK                                                                      |                       | 33                  | MHz  |

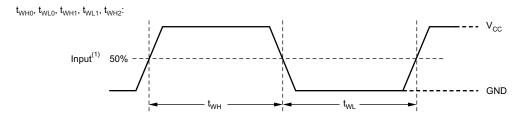

| t <sub>WH0</sub>         |                                      | SCLK                                                                       | 10                    |                     | ns   |

| t <sub>WL0</sub>         |                                      | SCLK                                                                       | 10                    |                     | ns   |

| t <sub>WH1</sub>         | Pulse duration                       | GSCLK                                                                      | 10                    |                     | ns   |

| t <sub>WL1</sub>         |                                      | GSCLK                                                                      | 10                    |                     | ns   |

| t <sub>WH2</sub>         |                                      | LAT                                                                        | 30                    |                     | ns   |

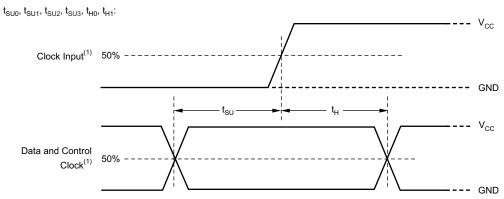

| t <sub>SU0</sub>         |                                      | SIN↑↓ to SCLK↑                                                             | 5                     |                     | ns   |

| t <sub>SU1</sub>         |                                      | LAT↑ to SCLK↑                                                              | 120                   |                     | ns   |

| t <sub>SU2</sub>         | Setup time                           | LAT↑ for BLANK bit '0' set to GSCLK↑                                       | 50                    |                     | ns   |

| t <sub>su3</sub>         |                                      | LAT↑ for GS data written to GSCLK↑ when display time reset mode is enabled | 100                   |                     | ns   |

| t <sub>H0</sub>          | Hold time                            | SCLK↑ to SIN↑↓                                                             | 5                     |                     | ns   |

| t <sub>H1</sub>          | Hold tille                           | SCLK↑ to LAT↑                                                              | 5                     |                     | ns   |

## **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40$ °C to +85°C and  $V_{CC} = 3$  V to 5.5 V. Typical values at  $T_A = +25$ °C and  $V_{CC} = 3.3$  V, unless otherwise noted.

|                    |                                          |                                                                                                                                                                                                                                    |                                          |                        | TLC5948A               |                        |      |

|--------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------|------------------------|------------------------|------|

|                    | PARAMETER                                | TEST CONDIT                                                                                                                                                                                                                        | TIONS                                    | MIN                    | TYP                    | MAX                    | UNIT |

| $V_{OH}$           | High-level output voltage (SOUT)         | I <sub>OH</sub> = -2 mA                                                                                                                                                                                                            |                                          | V <sub>CC</sub> - 0.4  |                        | V <sub>CC</sub>        | V    |

| $V_{OL}$           | Low-level output voltage (SOUT)          | I <sub>OL</sub> = 2 mA                                                                                                                                                                                                             |                                          |                        |                        | 0.4                    | V    |

| $V_{LOD0}$         |                                          | All OUT <i>n</i> = on, detection voltage                                                                                                                                                                                           | code = 0h                                | 0.25                   | 0.30                   | 0.35                   | V    |

| V <sub>LOD1</sub>  | 15D d-tti thh-ld                         | All OUT <i>n</i> = on, detection voltage                                                                                                                                                                                           | code = 1h                                | 0.55                   | 0.6                    | 0.65                   | V    |

| $V_{LOD2}$         | LED open-detection threshold             | All OUTn = on, detection voltage                                                                                                                                                                                                   | code = 2h                                | 0.85                   | 0.9                    | 0.95                   | V    |

| $V_{LOD3}$         |                                          | All OUT <i>n</i> = on, detection voltage                                                                                                                                                                                           | code = 3h                                | 1.15                   | 1.2                    | 1.25                   | V    |

| V <sub>LSD0</sub>  |                                          | All OUTn = on, detection voltage                                                                                                                                                                                                   | code = 0h                                | 0.30 × V <sub>CC</sub> | 0.35 × V <sub>CC</sub> | 0.40 × V <sub>CC</sub> | V    |

| V <sub>LSD1</sub>  |                                          | All OUT <i>n</i> = on, detection voltage                                                                                                                                                                                           | code = 1h                                | 0.40 × V <sub>CC</sub> | 0.45 × V <sub>CC</sub> | 0.50 × V <sub>CC</sub> | V    |

| V <sub>LSD2</sub>  | LED short-detection threshold            | All OUTn = on, detection voltage                                                                                                                                                                                                   | code = 2h                                | 0.50 × V <sub>CC</sub> | 0.55 × V <sub>CC</sub> | 0.60 × V <sub>CC</sub> | V    |

| $V_{LSD3}$         |                                          | All OUTn = on, detection voltage                                                                                                                                                                                                   | code = 3h                                | 0.60 × V <sub>CC</sub> | 0.65 × V <sub>CC</sub> | 0.70 × V <sub>CC</sub> | V    |

| V <sub>IREF</sub>  | Reference voltage output                 | $R_{IREF} = 1.1 \text{ k}\Omega$                                                                                                                                                                                                   |                                          | 1.17                   | 1.20                   | 1.23                   | V    |

| I <sub>IN</sub>    | Input current<br>(SIN, SCLK, LAT, GSCLK) | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                                                                                                                                                           |                                          | -1                     |                        | 1                      | μA   |

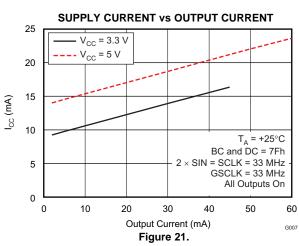

| I <sub>CC0</sub>   |                                          | SIN, SCLK, LAT, and GSCLK = GSn = FFFFh, DCn and BC = 7f R <sub>IREF</sub> = open (all outputs off)                                                                                                                                |                                          |                        | 1.5                    | 3                      | mA   |

| I <sub>CC1</sub>   |                                          | SIN, SCLK, LAT, and GSCLK = GS $n$ = FFFFh, DC $n$ and BC = 7 $t$ V <sub>OUTn</sub> = 0.8 V, R <sub>IREF</sub> = 2.2 k $\Omega$ (all outputs off, I <sub>OUTn</sub> = 23.1 mA                                                      | Fh,                                      |                        | 5                      | 7                      | mA   |

| I <sub>CC2</sub>   |                                          | SIN, SCLK, and LAT = GND, BLANK = 0, auto display repeat enabled, GSCLK = 33 MHz, GS $n$ = FFFFh, DC $n$ and BC = 7Fh, V <sub>OUTn</sub> = 0.8 V, R <sub>IREF</sub> = 2.2 k $\Omega$ (I <sub>OUT</sub> = 23.1 mA target)           |                                          |                        | 7                      | 9                      | mA   |

| I <sub>CC3</sub>   | Supply current (V <sub>CC</sub> )        | SIN, SCLK, and LAT = GND, BL repeat enabled, GSCLK = 33 Mt DCn and BC = 7Fh, V <sub>OUTn</sub> = 0.8 (I <sub>OUT</sub> = 46.1 mA target)                                                                                           | Hz, GS <i>n</i> = FFFFh,                 |                        | 11                     | 14                     | mA   |

| I <sub>CC4</sub>   |                                          | $V_{CC}$ = 5.0 V, SIN, SCLK, and LA auto display repeat enabled, GS GSn = FFFFh, DCn and BC = 7t R <sub>IREF</sub> = 0.91 kΩ (I <sub>OUT</sub> = 55.8 mA                                                                           | CLK = 33 MHz,<br>Fh, $V_{OUTn} = 0.8 V,$ |                        | 13                     | 18                     | mA   |

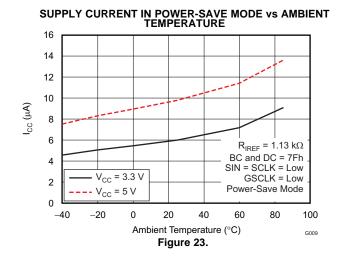

| I <sub>CC5</sub>   |                                          | $V_{CC}$ = 5.0 V, SIN, SCLK, LAT, and GSCLK = GND, BLANK = 0, auto display repeat enabled, GS $n$ = 0000h, DC $n$ and BC = 7Fh, in power-save mode, $V_{OUTn}$ = 0.8 V, $R_{IREF}$ = 0.91 k $\Omega$ ( $I_{OUT}$ = 55.8 mA target) |                                          |                        | 10                     | 40                     | μА   |

| I <sub>OLC0</sub>  | Constant output sink current             | All OUT $n$ = on, DC $n$ and BC = 7Fh, V <sub>OUTn</sub> = V <sub>OUTfix</sub> = 0.8 V, R <sub>IREF</sub> = 1.1 k $\Omega$ , T <sub>A</sub> = +25°C (I <sub>OLCn</sub> = 46.1 mA target)                                           |                                          | 43.4                   | 46.1                   | 48.8                   | mA   |

| I <sub>OLC1</sub>  | (OUT0 to OUT15)                          | $V_{\rm CC}$ = 5.0 V, All OUT $n$ = on, DC $n$ and BC = 7Fh, $V_{\rm OUTh}$ = $V_{\rm OUThx}$ = 0.8 V, R <sub>IREF</sub> = 0.91 k $\Omega$ , T <sub>A</sub> = +25°C ( $I_{\rm OLCn}$ = 55.8 mA target)                             |                                          | 52.5                   | 55.8                   | 59.1                   | mA   |

| I <sub>OLKG0</sub> |                                          | All $OUTn = off$ , $BLANK = 1$ ,                                                                                                                                                                                                   | $T_J = +25^{\circ}C$                     |                        |                        | 0.1                    | μA   |

| I <sub>OLKG1</sub> | Output leakage current (OUT0 to OUT15)   | $V_{OUTn} = V_{OUTfix} = 10 \text{ V},$                                                                                                                                                                                            | $T_J = +85^{\circ}C^{(1)}$               |                        |                        | 0.2                    | μA   |

| I <sub>OLKG2</sub> | (20.0.0.00.10)                           | $R_{IREF} = 1.1 \text{ k}\Omega$                                                                                                                                                                                                   | $T_J = +125^{\circ}C^{(1)}$              |                        | 0.3                    | 0.8                    | μA   |

<sup>(1)</sup> Not tested; specified by design.

## **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_A = -40$ °C to +85°C and  $V_{CC} = 3$  V to 5.5 V. Typical values at  $T_A = +25$ °C and  $V_{CC} = 3.3$  V, unless otherwise noted.

|                    |                                                                           | TLC5948A                                                                                                                                                                        |     |      |     |      |

|--------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                    | PARAMETER                                                                 | TEST CONDITIONS                                                                                                                                                                 | MIN | TYP  | MAX | UNIT |

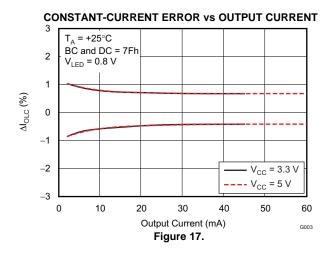

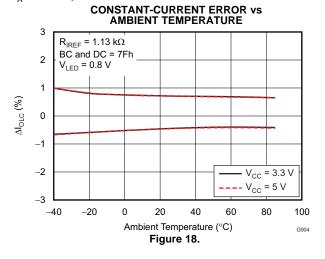

| ΔI <sub>OLC0</sub> | Constant-current error (channel-to-channel, OUT0 to OUT15) <sup>(2)</sup> | All OUT $n$ = on, DC $n$ and BC = 7Fh, $V_{OUTn}$ = $V_{OUTfix}$ = 0.8 V, $R_{IREF}$ = 1.1 k $\Omega$ , $T_A$ = +25°C ( $I_{OUTn}$ = 46.1 mA target)                            |     | ±0.6 | ±2  | %    |

| ΔI <sub>OLC1</sub> | Constant-current error (device-to-device, OUT0 to OUT15) <sup>(3)</sup>   | All OUT $n$ = on, DC $n$ and BC = 7Fh, $V_{OUTn}$ = $V_{OUTfix}$ = 0.8 V, $R_{IREF}$ = 1.1 k $\Omega$ , $T_A$ = +25°C ( $I_{OUTn}$ = 46.1 mA target)                            |     | ±1   | ±4  | %    |

| ΔI <sub>OLC2</sub> | Line regulation<br>(OUT0 to OUT15) <sup>(4)</sup>                         | $V_{CC}$ = 3.0 V to 5.5 V, all OUT $n$ = on, DC $n$ and BC = 7Fh, $V_{OUTn}$ = $V_{OUTfix}$ = 0.8 V, $R_{IREF}$ = 1.1 kΩ ( $I_{OUTn}$ = 46.1 mA target)                         |     | ±0.1 | ±1  | %/V  |

| ΔI <sub>OLC3</sub> | Load regulation<br>(OUT0 to OUT15) <sup>(5)</sup>                         | All OUT $n$ = on, DC $n$ and BC = 7Fh, V <sub>OUTn</sub> = 0.8 V to 3.0 V, V <sub>OUTfix</sub> = 0.8 V, R <sub>IREF</sub> = 1.1 k $\Omega$ (I <sub>OUTn</sub> = 46.1 mA target) |     | ±0.1 | ±1  | %/V  |

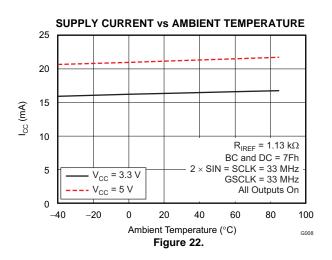

| T <sub>TEF</sub>   | Thermal error flag threshold                                              | Junction temperature (6)                                                                                                                                                        | 150 | 165  | 180 | °C   |

| T <sub>HYS</sub>   | Thermal error flag hysteresis                                             | Junction temperature (6)                                                                                                                                                        | 5   | 10   | 20  | °C   |

| T <sub>PTW</sub>   | Pre-thermal warning threshold                                             | Junction temperature <sup>(6)</sup>                                                                                                                                             | 125 | 138  | 150 | °C   |

(2) The deviation of each output from the OUT0 to OUT15 constant-current average. Deviation is calculated by the formula:

$$\Delta \text{ (\%)} = 100 \times \left[ \frac{I_{OLC(n)}}{\left[ \frac{(I_{OLC(0)} + I_{OLC(1)} + \dots + I_{OLC(14)} + I_{OLC(15)})}{16} \right]} - 1 \right]$$

Deviation of the OUT0 to OUT15 constant-current average from the ideal constant-current value. Deviation is calculated by the formula:

$$\Delta \text{ (\%)} = 100 \times \left[ \frac{\left( I_{\text{OLC(0)}} + I_{\text{OLC(1)}} + \dots I_{\text{OLC(14)}} + I_{\text{OLC(15)}} \right)}{16} \right] - \text{(Ideal Output Current)}$$

$$Ideal Output Current$$

Ideal current is calculated by the formula:

$$I_{OLCn(IDEAL)}$$

(mA) =  $42.3 \times \left[ \frac{1.20}{R_{IREF}} \right]$

(4) Line regulation is calculated by the formula:

$$\Delta \ (\%/V) = \left[ \frac{(I_{OLC(n)} \text{ at } V_{CC} = 5.5 \text{ V}) - (I_{OLC(n)} \text{ at } V_{CC} = 3.0 \text{ V})}{(I_{OLC(n)} \text{ at } V_{CC} = 3.0 \text{ V})} \right] \times \frac{100}{5.5 \text{ V} - 3.0 \text{ V}}$$

where n = 0 to 15.

where n = 0 to 15. Load regulation is calculated by the equation:

$$\Delta \ (\%/V) = \times \left[ \frac{(I_{OLC(n)} \ at \ V_{OUT,n} = 3 \ V) - (I_{OLC(n)} \ at \ V_{OUT,n} = 0.8 \ V)}{(I_{OLC(n)} \ at \ V_{OUT,n} = 0.8 \ V)} \right] \times \frac{100}{3 \ V - 0.8 \ V}$$

where n = 0 to 15.

Not tested; specified by design.

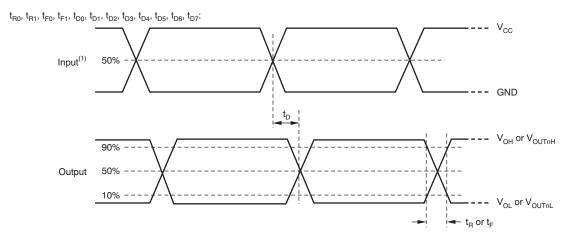

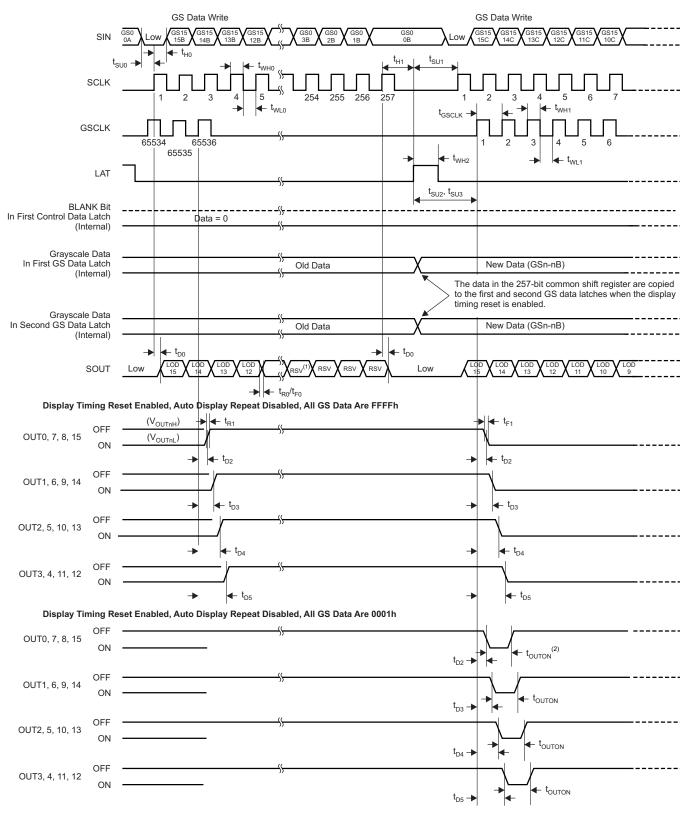

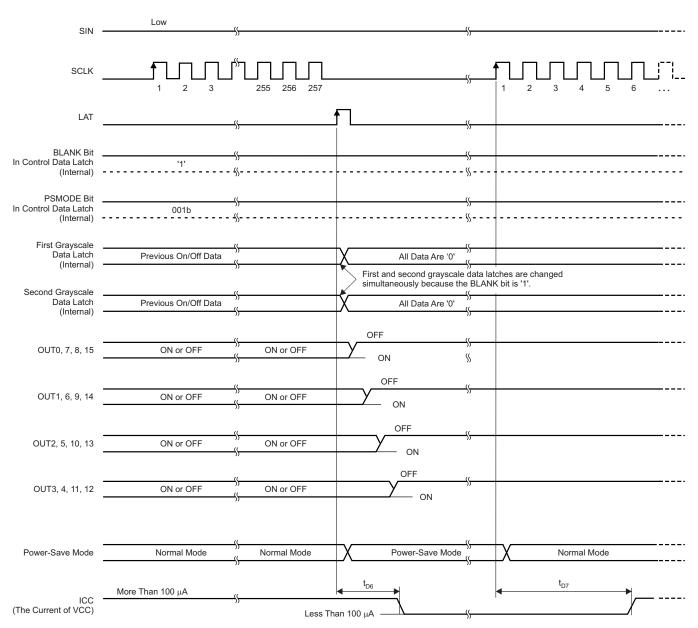

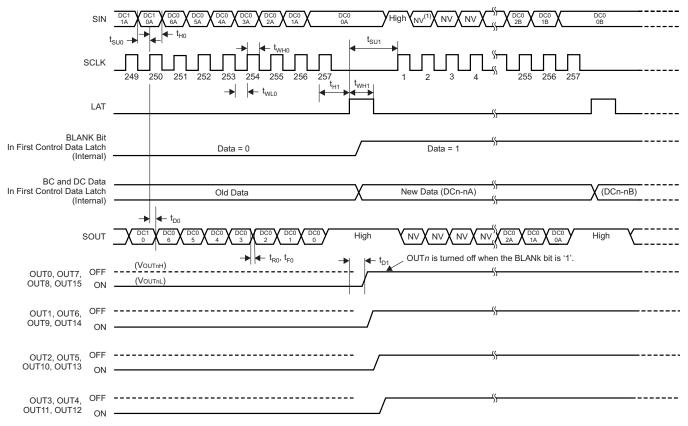

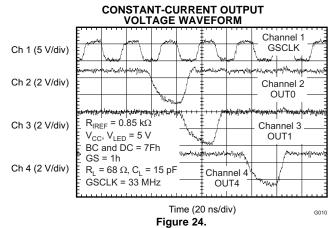

## SWITCHING CHARACTERISTICS (See Figure 4, Figure 5, and Figure 8 through Figure 11)

At  $T_A = -40$ °C to +85°C,  $V_{CC} = 3$  V to 5.5 V,  $C_L = 15$  pF,  $R_L = 82$   $\Omega$ ,  $R_{IREF} = 1.1$  k $\Omega$ , and  $V_{LED} = 5.0$  V. Typical values at  $V_{CC} = 3.3$  V and  $T_A = +25$ °C, unless otherwise noted.

|                     |                                     |                                                                                                                                       | TL  | .C5948A |     |      |

|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

|                     | PARAMETER                           | TEST CONDITIONS                                                                                                                       | MIN | TYP     | MAX | UNIT |

| t <sub>R0</sub>     | Rise time                           | SOUT                                                                                                                                  |     |         | 5   | ns   |

| t <sub>R1</sub>     | Rise time                           | OUTn, $DCn$ and $BC = 7Fh$                                                                                                            |     | 13      |     | ns   |

| t <sub>F0</sub>     | E-II dina                           | SOUT                                                                                                                                  |     |         | 5   | ns   |

| t <sub>F1</sub>     | Fall time                           | OUTn, $DCn$ and $BC = 7Fh$                                                                                                            |     | 23      |     | ns   |

| t <sub>D0</sub>     |                                     | SCLK↑ to SOUT↑↓                                                                                                                       |     | 15      | 25  | ns   |

| t <sub>D1</sub>     |                                     | LAT↑ for BLANK = 1 set to OUT0, 7, 8, and 15 off                                                                                      |     | 40      | 75  | ns   |

| t <sub>D2</sub>     |                                     | GSCLK↑ to OUT0, 7, 8, and 15 on/off with DCn and BC = 7Fh                                                                             | 5   | 36      | 65  | ns   |

| t <sub>D3</sub>     |                                     | GSCLK↑ to OUT1, 6, 9, and 14 on/off with DCn and BC = 7Fh                                                                             | 20  | 62      | 97  | ns   |

| t <sub>D4</sub>     | Dranagation dalay                   | GSCLK↑ to OUT2, 5, 10, and 13 on/off with DCn and BC = 7Fh                                                                            | 35  | 88      | 129 | ns   |

| t <sub>D5</sub>     | Propagation delay                   | GSCLK↑ to OUT3, 4, 11, and 12 on/off with DCn and BC = 7Fh                                                                            | 50  | 114     | 161 | ns   |

| t <sub>D6</sub>     |                                     | LAT↑ to power-save mode by writing data for OUT <i>n</i> off with BLANK = 1 and PSMODE = 110                                          |     |         | 200 | ns   |

| t <sub>D7</sub>     |                                     | SCLK↑ to normal mode with PSMODE = 101 or LAT ↑ to normal mode by writing GS data for OUT <i>n</i> on with BLANK = 1 and PSMODE = 110 |     |         | 50  | μs   |

| t <sub>ON_ERR</sub> | Output on-time error <sup>(1)</sup> | $t_{\rm OUTON}-t_{\rm GSCLK},$ GS $n$ = 0001h, GSCLK = 33 MHz, DC $n$ and BC = 7Fh, T <sub>A</sub> = +25°C                            | -20 |         | 10  | ns   |

<sup>(1)</sup> Output on-time error  $(t_{ON\_ERR})$  is calculated by the formula:  $t_{ON\_ERR} = t_{OUT\_ON} - t_{GSCLK}$ .  $t_{OUTON}$  is the actual on-time of the constant-current driver.  $t_{GSCLK}$  is the GSCLK period.

### PARAMETER MEASUREMENT INFORMATION

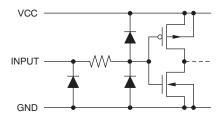

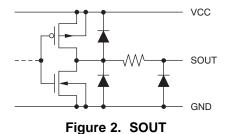

### PIN-EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

Figure 1. SIN, SCLK, LAT, GSCLK

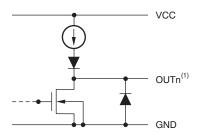

(1) n = 0 to 15.

Figure 3. OUT0 Through OUT15

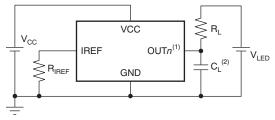

## **TEST CIRCUITS**

- (1) n = 0 to 15.

- (2)  $C_L$  includes measurement probe and jig capacitance.

VCC SOUT CL<sup>(1)</sup>

Figure 5. Rise Time and Fall Time Test Circuit for

SOUT

(1)  $C_L$  includes measurement probe and jig capacitance.

Figure 4. Rise Time and Fall Time Test Circuit for OUT*n*

V<sub>CC</sub>

VCC OUTO

IREF OUTn<sup>(1)</sup>

GND OUT15

V<sub>OUTfix</sub>

V<sub>OUTfix</sub>

(1) n = 0 to 15.

Figure 6. Constant-Current Test Circuit for OUTn

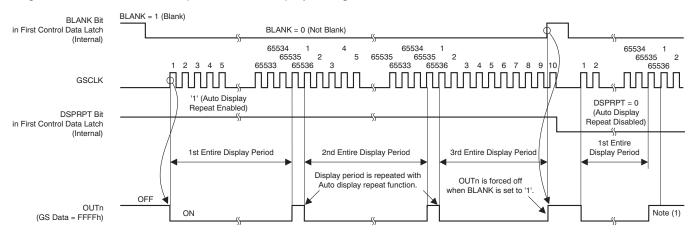

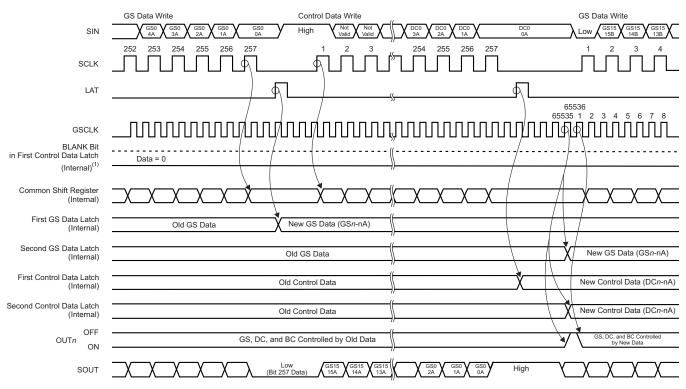

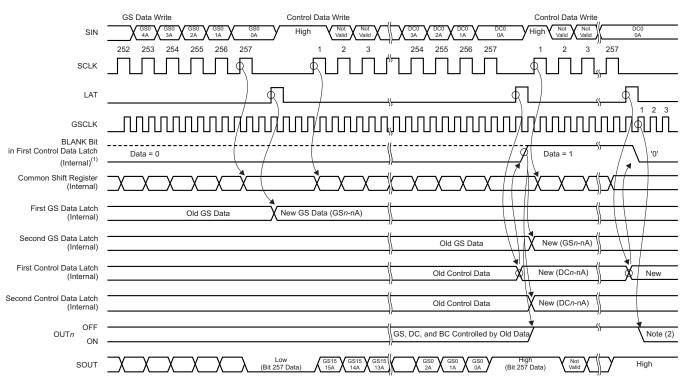

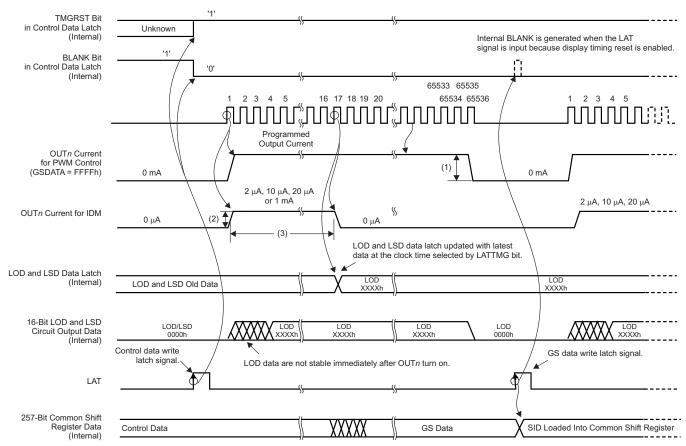

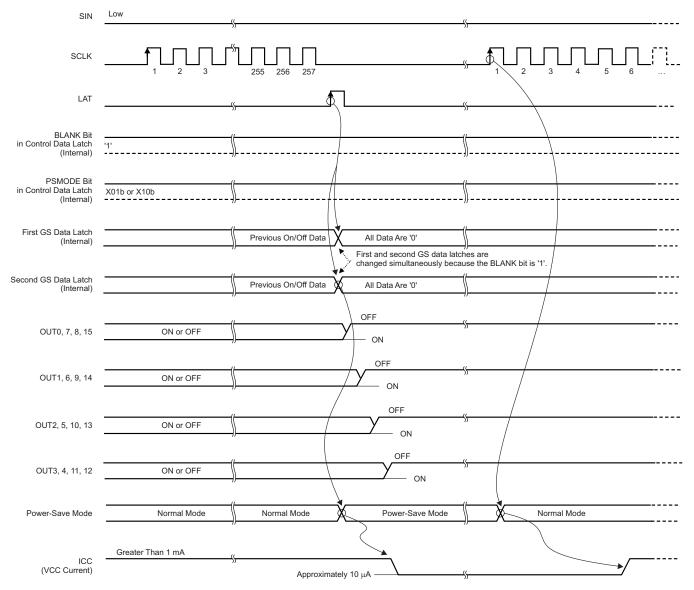

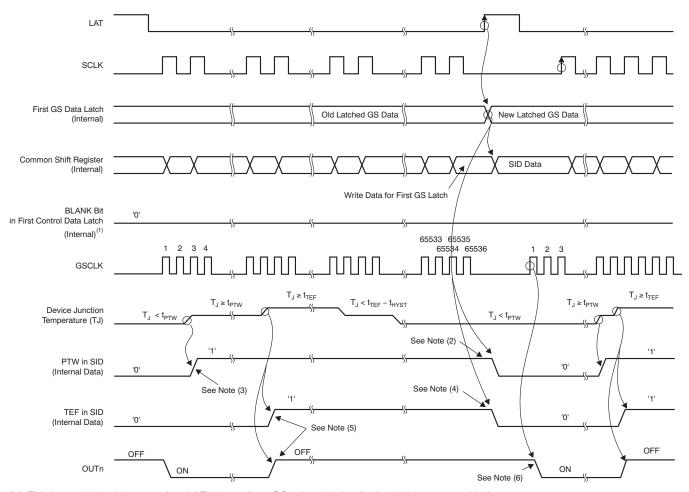

#### **TIMING DIAGRAMS**

(1) Input pulse rise and fall time is 1 ns to 3 ns.

Figure 7. Input Timing

(1) Input pulse rise and fall time is 1 ns to 3 ns.

Figure 8. Output Timing

- (1) RSV = reserved.

- (2)  $t_{OUTON}$  refers to  $t_{ON\_ERR} = t_{OUTON} t_{GSCLK}$ .

Figure 9. Grayscale Data Write Timing

Figure 10. Power-Save Mode Timing

(1) NV = Not valid; these data are not used for any function.

Figure 11. Control Data Write Timing

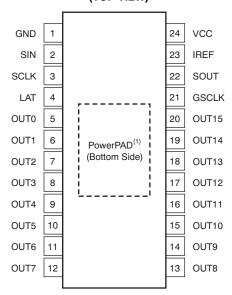

#### **PIN CONFIGURATION**

## DBQ AND PWP PACKAGES SSOP-24, QSOP-24, HTSSOP-24 (TOP VIEW)

NOTE: The PowerPAD only applies to the PWP package.

www.ti.com.cn

## **PIN DESCRIPTIONS**

| PI    | N   |     | PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GND   | 1   | _   | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GSCLK | 21  | I   | Grayscale (GS) pulse width modulation (PWM) reference clock control for OUT <i>n</i> .  When BLANK = 0, each GSCLK rising edge increments the GS counter for PWM control.  When BLANK = 1, all constant-current outputs (OUT0 to OUT15) are forced off, the GS counter is reset to '0', and the GS PWM timing controller is initialized.                                                                                                                                                                                                                                                                                                            |

| IREF  | 23  | I/O | Reference current terminal.  A resistor connected between IREF to GND sets the maximum current for all constant-current outputs.  When IREF is shorted to GND with low resistance, all constant-current outputs are forced off and the IREF short flag (ISF) bit in the status information data (SID) is set to '1'.                                                                                                                                                                                                                                                                                                                                |

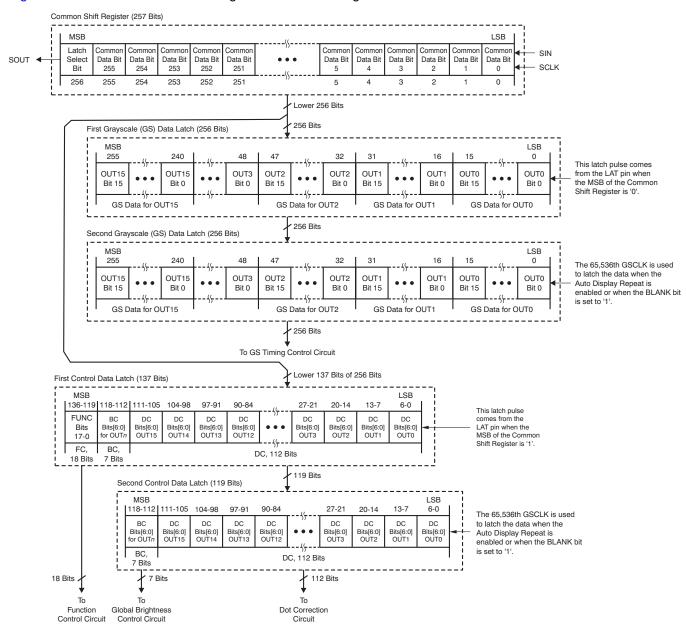

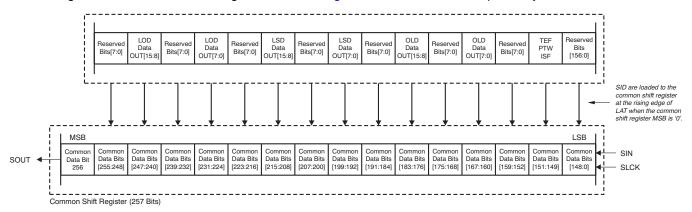

| LAT   | 4   | I   | The LAT rising edge either latches the data from the 257-bit common shift register into the first GS data latch when the common shift register MSB is '0' or it latches the data into the first control data latch when the common shift register MSB is '1'.  When the display timing reset bit (TMGRST) in the first control data latch is '1', the GS counter is initialized at the LAT signal for GS data writes. At the same time, the data in the 257-bit common shift register are copied to the first and second GS data latches simultaneously and the DC and BC data in the first control data latch are copied to the second data latch. |

| OUT0  | 5   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT1  | 6   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT2  | 7   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT3  | 8   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT4  | 9   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT5  | 10  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT6  | 11  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT7  | 12  | 0   | Constant-current outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OUT8  | 13  | 0   | Multiple outputs can be configured in parallel to increase the constant-current capability.  Different voltages can be applied to each output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT9  | 14  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT10 | 15  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT11 | 16  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT12 | 17  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT13 | 18  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT14 | 19  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OUT15 | 20  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SCLK  | 3   | I   | Serial data shift clock. Data present on SIN are shifted to the 257-bit common shift register LSB with the SCLK rising edge. Data in the shift register are shifted towards the MSB at each SCLK rising edge. The common shift register MSB appears on SOUT.                                                                                                                                                                                                                                                                                                                                                                                        |

| SIN   | 2   | I   | 257-bit common shift register serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SOUT  | 22  | 0   | 257-bit common shift register serial data output. LED open detection (LOD), LED short detection (LSD), output leak detection (OLD), thermal error flag (TEF), and the IREF pin short flag (ISF) bit can be read out with SOUT as SID after the LAT rising edge. SOUT is connected to the 257-bit common shift register MSB. Data are clocked out at the SCLK rising edge.                                                                                                                                                                                                                                                                           |

| VCC   | 24  | _   | Power-supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

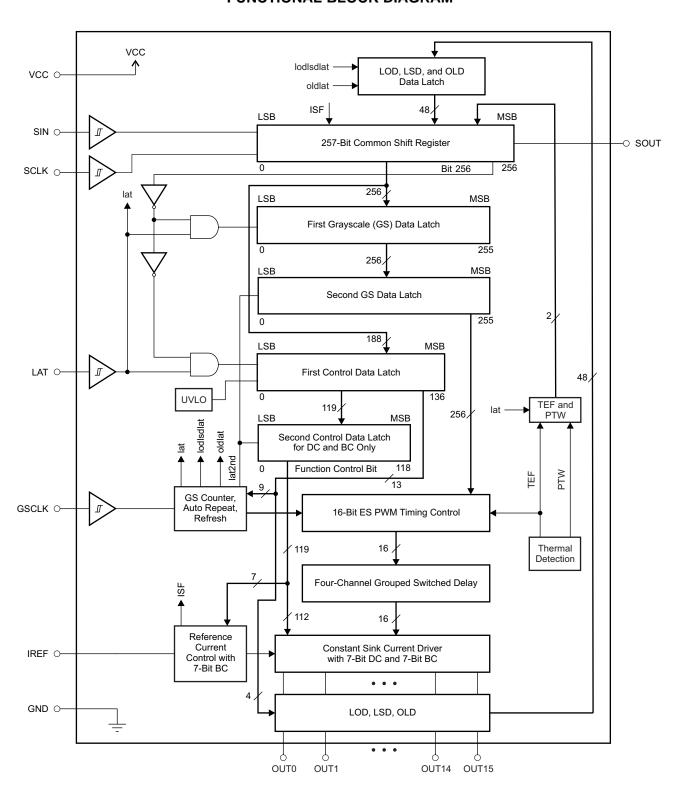

## **FUNCTIONAL BLOCK DIAGRAM**

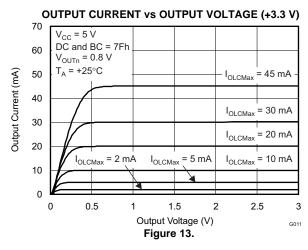

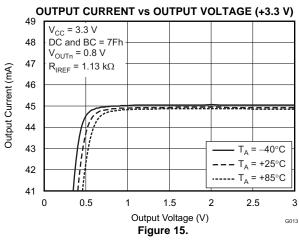

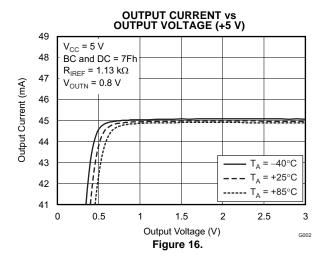

#### TYPICAL CHARACTERISTICS

At  $T_A = +25$ °C, unless otherwise noted.

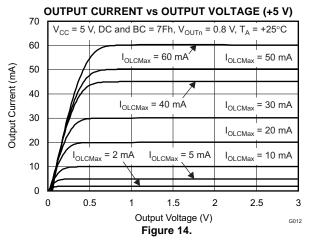

## TYPICAL CHARACTERISTICS (continued)

At  $T_A = +25$ °C, unless otherwise noted.

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C, unless otherwise noted.

Copyright © 2012, Texas Instruments Incorporated

#### DETAILED DESCRIPTION

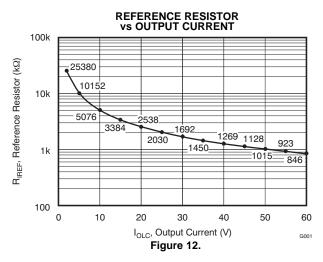

#### MAXIMUM CONSTANT SINK CURRENT VALUE

The maximum output current value of each channel (I<sub>OLCMax</sub>) is programmed by a single resistor (R<sub>IREF</sub>) that is placed between the IREF and GND pins. The current value can be calculated by Equation 1:

$$R_{IREF} = \frac{V_{IREF}}{I_{OLCMax}} \times 42.3$$

#### Where:

$V_{IREF}$  = the internal reference voltage on IREF (typically 1.20 V when the global brightness control data are at maximum)

$$I_{OLCMax} = 2 \text{ mA to } 60 \text{ mA with DC} n \text{ and BC} = 7\text{Fh}$$

(1)

$I_{OLCMax}$  is the highest current for each output. Each output sinks  $I_{OLCMax}$  current when it is turned on, and the dot correction (DC) data and the global brightness control (BC) data are set to the maximum value of 7Fh (127). Each output sink current can be reduced by lowering the DC and BC value.

$R_{IREF}$  must be between 0.846 k $\Omega$  and 25.4 k $\Omega$  in order to hold  $I_{OLCMax}$  between 60 mA (typ) and 2 mA (typ). Otherwise, the output may be unstable. Output currents lower than 2 mA can be achieved by setting  $I_{OLCMax}$  to 2 mA or higher and then using DC or global BC to lower the output current.

Table 1 shows the characteristics of the constant-current sink versus the external resistor, R<sub>IRFF</sub>.

Table 1. Maximum Constant-Current Output versus External Resistor Value

| I <sub>OLCMax</sub> (mA)          | R <sub>IREF</sub> (kΩ, typ) |

|-----------------------------------|-----------------------------|

| 60 (V <sub>CC</sub> > 3.6 V only) | 0.846                       |

| 55 (V <sub>CC</sub> > 3.6 V only) | 0.923                       |

| 50 (V <sub>CC</sub> > 3.6 V only) | 1.02                        |

| 45                                | 1.13                        |

| 40                                | 1.27                        |

| 35                                | 1.45                        |

| 30                                | 1.70                        |

| 25                                | 2.03                        |

| 20                                | 2.53                        |

| 15                                | 3.38                        |

| 10                                | 5.08                        |

| 5                                 | 10.2                        |

| 2                                 | 25.4                        |

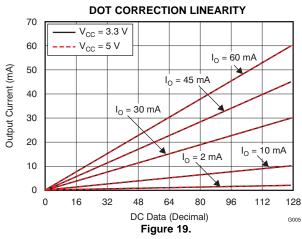

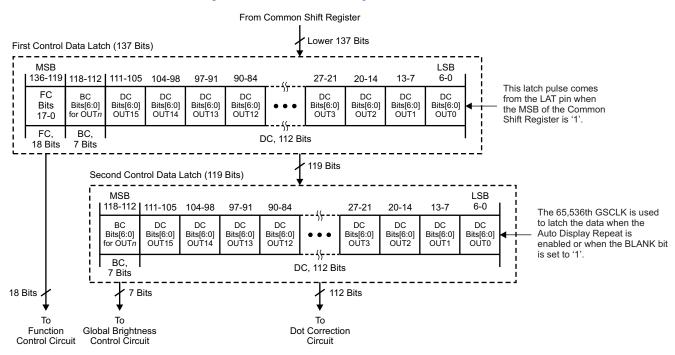

### **DOT CORRECTION (DC) FUNCTION**

The TLC5948A can individually adjust the output current of each channel (OUT0 to OUT15) by using DC. The DC function allows the brightness deviations of the LEDs connected to each output to be individually adjusted. Each output DC is programmed with a 7-bit word, so the value is adjusted with 128 steps within the range of 0% to 100% of I<sub>OLCMax</sub>. Equation 2 calculates the actual output current value as a function of R<sub>IREF</sub>, DC value, and global BC value. DC data are programmed into the TLC5948A with the serial interface. When the device is powered on, the DC data in the first and second control data latches contain random data. Therefore, DC data must be written to the DC data latch before turning the constant-current outputs on. Table 2 summarizes the DC data value versus the set current value.

Table 2. DC Data versus Current Ratio and Set Current Value

|          | DC DATA |     |               | RATIO OF                                        |                                                                    |                                                                   |

|----------|---------|-----|---------------|-------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|

| BINARY   | DECIMAL | HEX | BC DATA (Hex) | OUTPUT<br>CURRENT TO<br>I <sub>OLCMax</sub> (%) | I <sub>OUT</sub> (mA)<br>(I <sub>OLCMax</sub> = 45 mA,<br>typical) | I <sub>OUT</sub> (mA)<br>(I <sub>OLCMax</sub> = 2 mA,<br>typical) |

| 000 0000 | 0       | 00  | 7F            | 0                                               | 0                                                                  | 0                                                                 |

| 000 0001 | 1       | 01  | 7F            | 0.8                                             | 0.35                                                               | 0.02                                                              |

| 000 0010 | 2       | 02  | 7F            | 1.6                                             | 0.71                                                               | 0.03                                                              |

| _        | _       | _   | _             | _                                               | _                                                                  | _                                                                 |

| 111 1101 | 125     | 7D  | 7F            | 98.4                                            | 44.29                                                              | 1.97                                                              |

| 111 1110 | 126     | 7E  | 7F            | 99.2                                            | 44.65                                                              | 1.98                                                              |

| 111 1111 | 127     | 7F  | 7F            | 100.0                                           | 45.00                                                              | 2.00                                                              |

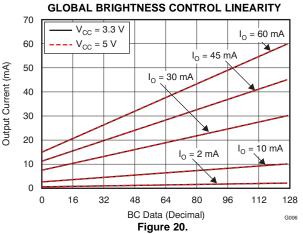

### **GLOBAL BRIGHTNESS CONTROL (BC) FUNCTION**

The TLC5948A has the ability to adjust the output current of all constant-current outputs simultaneously. This function is called *global brightness control* (BC). The global BC for all outputs (OUT0 to OUT15) is programmed with a 7-bit word. The global BC adjusts all output currents in 128 steps from 25% to 100%, where 100% corresponds to the maximum output current set by  $R_{IREF}$ . Equation 2 calculates the actual output current as a function of  $R_{IREF}$ , DC value, and global BC value. BC data can be set via the serial interface. When the device is powered on, the BC data in the first and second control data latches contain random data. Therefore, BC data must be written to the BC data latch before turning the constant-current output on.

The output current value controlled by DC and BC can be calculated by Equation 2.

$$I_{OUTn} = \left(\frac{1}{4} + \frac{3/4 \times BC}{127}\right) \times \frac{DCn}{127} \times I_{OLCMax}$$

#### Where:

$I_{OLCMax}$  = the maximum constant-current value for each output determined by  $R_{IREF}$

DCn = the dot correction value for each OUTn in the second control data latch (0h to 7Fh)

BC = the global brightness control value in the second control data latch (0h to 7Fh)

(2)

Table 3 and Table 4 summarize the BC data versus the set current value.

Table 3. BC Data versus Constant-Current Ratio and Set Current Value

|          | BC DATA |     | RATIO OF      |                                                 |                                                                |                                                               |

|----------|---------|-----|---------------|-------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------|

| BINARY   | DECIMAL | HEX | DC DATA (Hex) | OUTPUT<br>CURRENT TO<br>I <sub>OLCMax</sub> (%) | I <sub>OUT</sub> (mA)<br>(I <sub>OLCMax</sub> = 45 mA,<br>typ) | I <sub>OUT</sub> (mA)<br>(I <sub>OLCMax</sub> = 2 mA,<br>typ) |

| 000 0000 | 0       | 00  | 7F            | 25.0                                            | 11.25                                                          | 0.50                                                          |

| 000 0001 | 1       | 01  | 7F            | 25.6                                            | 11.52                                                          | 0.51                                                          |

| 000 0010 | 2       | 02  | 7F            | 26.2                                            | 11.78                                                          | 0.52                                                          |

| _        | _       | _   | _             | _                                               | _                                                              | _                                                             |

| 111 1101 | 125     | 7D  | 7F            | 98.8                                            | 44.47                                                          | 1.98                                                          |

| 111 1110 | 126     | 7E  | 7F            | 99.4                                            | 44.73                                                          | 1.99                                                          |

| 111 1111 | 127     | 7F  | 7F            | 100.0                                           | 45.00                                                          | 2.00                                                          |

Table 4. DC and BC Data versus Current Ratio and Set Current Value

| BC DATA (Hex) | DC DATA (Hex) | RATIO OF OUTPUT<br>CURRENT TO I <sub>OLCMax</sub><br>(%) | I <sub>OUT</sub> (mA)<br>(I <sub>OLCMax</sub> = 45 mA,<br>typical) | I <sub>OUT</sub> (mA)<br>(I <sub>OLCMax</sub> = 2 mA, typical) |

|---------------|---------------|----------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------|

| 00            | 3F            | 12.4                                                     | 5.58                                                               | 0.25                                                           |

| 01            | 3F            | 12.7                                                     | 5.71                                                               | 0.25                                                           |

| 02            | 3F            | 13.0                                                     | 5.84                                                               | 0.26                                                           |

| _             | _             | _                                                        | _                                                                  | _                                                              |

| 7D            | 3F            | 49.0                                                     | 22.06                                                              | 0.98                                                           |

| 7E            | 3F            | 49.3                                                     | 22.19                                                              | 0.99                                                           |

| 7F            | 3F            | 49.6                                                     | 22.32                                                              | 0.99                                                           |

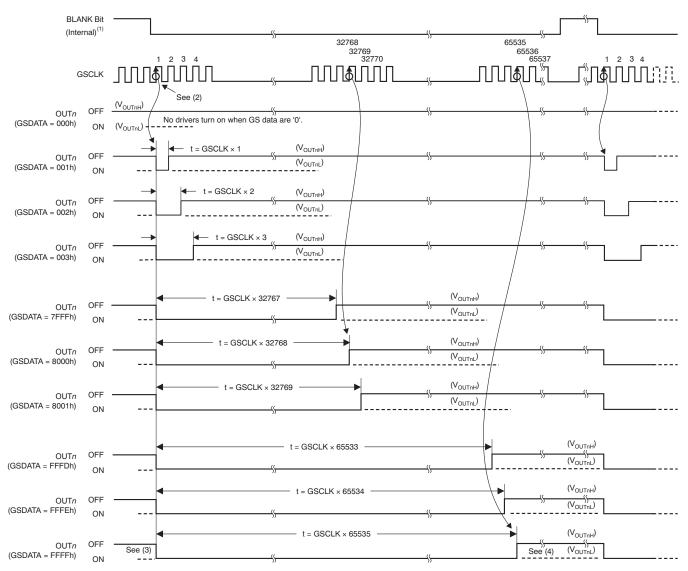

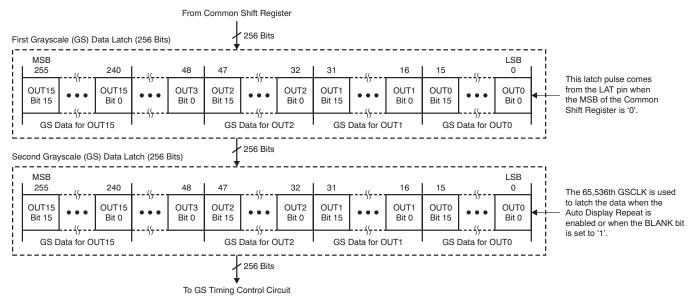

## **GRAYSCALE (GS) FUNCTION (PWM CONTROL)**

The TLC5948A can adjust the brightness of each output channel using a pulse width modulation (PWM) control scheme. The architecture of 16 bits per channel results in 65,536 brightness steps, from 0% up to 100% brightness.

The PWM operation for OUT*n* is controlled by a 16-bit grayscale (GS) counter. The GS counter increments on each GS reference clock (GSCLK) rising edge. The GS counter resets to 0000h when the BLANK bit in the first control data latch is set to '1'; the counter value is held at 0000h while the BLANK bit is '1', even if the GS clock input is toggled high and low.

The TLC5948A has two types of PWM control: conventional PWM control and enhanced spectrum (ES) PWM control. The conventional PWM control can be selected when the ESPWM bit in the first control data latch is '0'. The ES PWM control is selected when the ESPWM bit is '1'.

The on-time  $(t_{OUT\ ON})$  of each output (OUTn) can be calculated by Equation 3.

$$t_{OUT\ ON} = t_{GSCLK} \times GSn$$

(3)

Table 5 summarizes the GS data values versus the output on-time duty cycle. When the device powers up, the BLANK bit in the first control data latch is set to '1'. The 257-bit common shift register and the first and second GS data latches contain random data. Therefore, GS data must be written to the GS latches before the BLANK bit is set to '0'. All constant-current outputs are off when the BLANK bit is '1'.

Table 5. Output Duty Cycle and On-Time versus GS Data

| GS D    | GS DATA |                  | GS I    |      |                  |

|---------|---------|------------------|---------|------|------------------|

| DECIMAL | HEX     | ON-TIME DUTY (%) | DECIMAL | HEX  | ON-TIME DUTY (%) |

| 0       | 0       | 0                | 32768   | 8000 | 50.001           |

| 1       | 1       | 0.002            | 32769   | 8001 | 50.002           |

| 2       | 2       | 0.003            | 32770   | 8002 | 50.004           |

| 3       | 3       | 0.005            | 32771   | 8003 | 50.005           |

| _       | _       | _                | _       | _    | _                |

| 8191    | 1FFF    | 12.499           | 40959   | 9FFF | 62.499           |

| 8192    | 2000    | 12.500           | 40960   | A000 | 62.501           |

| 8193    | 2001    | 12.502           | 40961   | A001 | 62.502           |

| _       | _       | _                | _       | _    | _                |

| 16381   | 3FFD    | 24.996           | 49149   | BFFD | 74.997           |

| 16382   | 3FFE    | 24.997           | 49150   | BFFE | 74.998           |

| 16383   | 3FFF    | 24.999           | 49151   | BFFF | 75.000           |

| 16384   | 4000    | 25.000           | 49152   | C000 | 75.001           |

| 16385   | 4001    | 25.002           | 49153   | C001 | 75.003           |

| 16386   | 4002    | 25.003           | 49154   | C002 | 75.004           |

| 16387   | 4003    | 25.005           | 49155   | C003 | 75.006           |

| _       | _       | _                | _       | _    | _                |

| 24575   | 5FFF    | 37.499           | 57343   | DFFF | 87.500           |

| 24576   | 6000    | 37.501           | 57344   | E000 | 87.501           |

| 24577   | 6001    | 37.502           | 57345   | E001 | 87.503           |

| _       | _       | _                | _       | _    | _                |

| 32765   | 7FFD    | 49.996           | 65533   | FFFD | 99.997           |

| 32766   | 7FFE    | 49.998           | 65534   | FFFE | 99.998           |

| 32767   | 7FFF    | 49.999           | 65535   | FFFF | 100.000          |

### **Conventional PWM Control**

In this PWM control, the GS clock is enabled when the BLANK bit is set to '0'. The first GS clock rising edge after the BLANK bit is set to '0' increments the GS counter by one and switches on all outputs with a non-zero GS value programmed into the second GS data latch. Each additional GS clock rising edge increases the corresponding GS counter by one.

The GS counter keeps track of the number of clock pulses from the GS clock inputs. Each output stays on while the counter is less than or equal to the programmed GS value. Each output turns off at the GS counter value rising edge when the counter becomes greater than the output GS latch value. Figure 25 illustrates the conventional PWM operation.

- (1) The internal signal is generated when LAT inputs GS data with the display timing reset bit (TMGRST) set to '1'. This signal has the same function as a BLANK = 1 pulse. Furthermore, the signal is generated at the 65,536th GSCLK when the auto display repeat bit (DSPRPT) is set to '1'.

- (2) The GS counter begins to count GSCLK pulses after the BLANK bit is set to '0' or when the LAT signal for a GS data write is input with the display time reset mode enabled.

- (3) OUT*n* turns on at the first GSCLK rising edge except when GS data are '0' after the BLANK bit is set to '0' or when the LAT signal for a GS data write is input with the display time reset mode enabled.

- (4) OUTn does not turn on again until BLANK is set to '1' once, except when the TMGRST or DSPRPT bits are '1'.

## Figure 25. Conventional PWM Operation

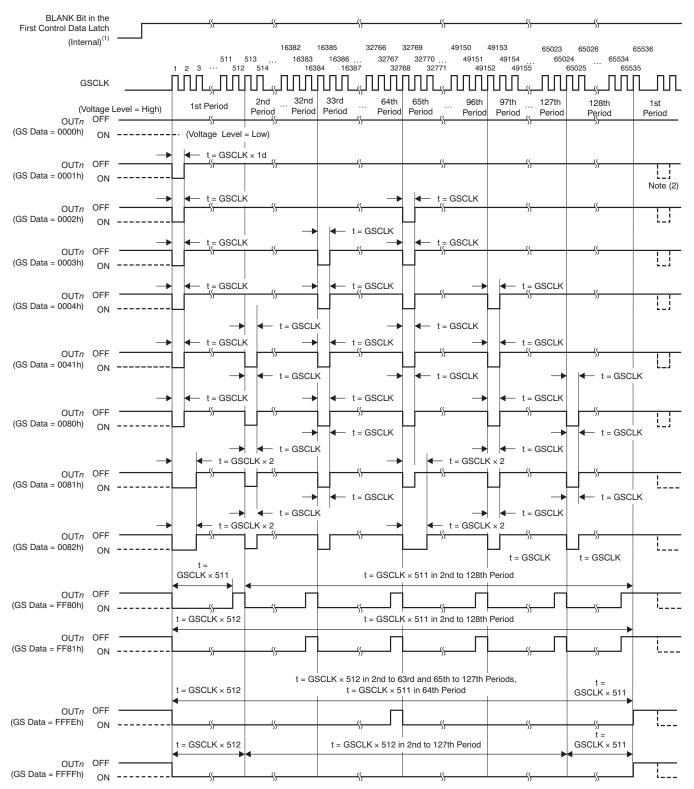

## **Enhanced Spectrum (ES) PWM Control**

In this PWM control, the total display period is divided into 128 display segments. The total display period is the time from the first GS clock (GSCLK) to the 65,536th GSCLK input after the BLANK bit is set to '0'. Each display segment has a maximum of 512 GSCLKs. The OUT*n* on-time changes, depending on the 16-bit GS data. Refer to Table 6 for the sequence of information and to Figure 26 for the timing information.

## Table 6. ES PWM Drive Turn On-Time Length

| GS DATA |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DECIMAL | HEX   | OUT n DRIVER OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 0       | 0000h | Does not turn on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 1       | 0001h | Turns on for one GSCLK period in the first display segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 2       | 0002h | Turns on for one GSCLK period in the first and 65th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 3       | 0003h | Turns on for one GSCLK period in the first, 65th, and 33th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 4       | 0004h | Turns on for one GSCLK period in the first, 65th, 33th, and 97th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 5       | 0005h | Turns on for one GSCLK period in the first, 65th, 33th, 97th, and 17th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 6       | 0006h | Turns on for one GSCLK period in the first, 65th, 33th, 97th, 17th, and 81th display segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |