# TLV840 Nano-Power Ultra-Low Voltage Supervisor with Adjustable Reset Time Delay

#### 1 Features

- Operating voltage range: 0.7 V to 6 V

- Nano supply current: 120 nA (Typical)

- Fixed threshold voltage (V<sub>IT-</sub>): 0.8 V to 5.4 V

- Threshold voltages available in 100mV steps

- High accuracy: ±0.5% (Typical)

- Built-in hysteresis (V<sub>HYS</sub>): 5% (Typical)

- Reset time delay (t<sub>D</sub>): capacitor-based programmable (TLV840C, TLV840M)

- Minimum time delay: 40 µs (typical) without capacitor

- Active-low manual reset (MR) (TLV840M)

- Four output topologies:

- TLV840xxDL: open-drain, active-low (RESET)

- TLV840xxPL: push-pull, active-low (RESET)

- TLV840xxDH: open-drain, active-high (RESET)

- TLV840xxPH: push-pull, active-high (RESET)

- Wide temperature range: -40°C to +125°C

- Package: SOT23-5 (DBV)

## 2 Applications

- **Motor Drives**

- **Factory Automation and Control**

- Home Theater and Entertainment

- **Electronic Point of Sale**

- **Grid Infrastructure**

- **Data Center and Enterprise Computing**

- **Multifunction Printer**

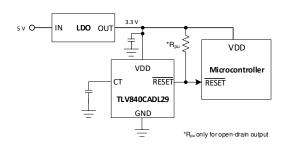

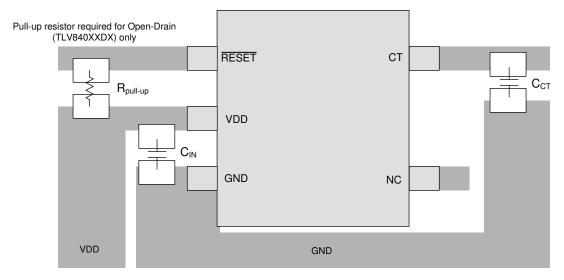

**Typical Application Circuit**

## 3 Description

The TLV840 family of voltage supervisors or reset ICs can operate at high voltage levels while maintaining very low quiescent current across the whole VDD and temperature range. TLV840 offers best combination of low power consumption, high accuracy and low propagation delay ( $t_p$  HL = 30  $\mu$ s typical).

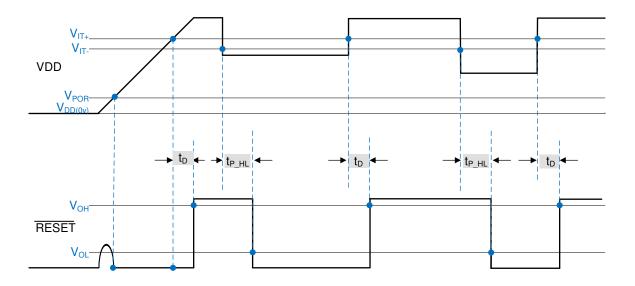

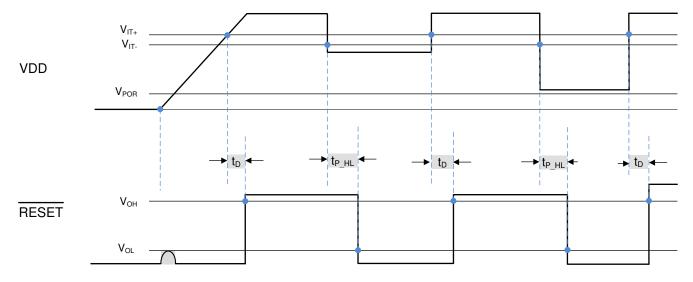

Reset output signal is asserted when the voltage at VDD drops below the negative voltage threshold (V<sub>IT-</sub>). Reset signal is cleared when VDD rise above V<sub>IT-</sub> plus hysteresis (V<sub>HYS</sub>) and the reset time delay (t<sub>D</sub>) expires. Reset time delay can be programmed by connecting a capacitor between the CT pin and ground for TLV840C and TLV840M. For a minimum reset delay time the CT pin can be left floating. TLV840N does not offer a programmable delay and offers fixed reset delay timing options: 40 µs, 2 ms, 10 ms, 30 ms, 50 ms, 80 ms, 100 ms, 150 ms, 200 ms.

Additional features: Low power-on reset voltage (V<sub>POR</sub>), built-in glitch immunity protection for VDD, built-in hysteresis, low open-drain output leakage current (I<sub>lkg(OD)</sub>). TLV840 is a perfect voltage monitoring solution for industrial applications and battery-powered / low-power applications.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| TLV840      | SOT-23 (5) (DBV)       | 2.90 mm × 1.60 mm |

For package details, see the mechanical drawing addendum at the end of the data sheet.

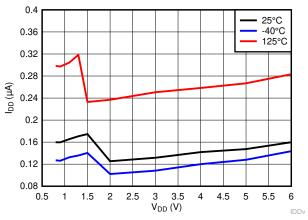

**Typical Supply Current**

## **Table of Contents**

| 1 Features                           | 1              | 8.2 Functional Block Diagram                      | 10                   |

|--------------------------------------|----------------|---------------------------------------------------|----------------------|

| 2 Applications                       | 1              | 8.3 Feature Description                           | 10                   |

| 3 Description                        | 1              | 8.4 Device Functional Modes                       | 14                   |

| 4 Revision History                   |                | 9 Application and Implementation                  | 15                   |

| 5 Device Comparison                  |                | 9.1 Application Information                       |                      |

| 6 Pin Configuration and Functions    | 4              | 9.2 Typical Application                           |                      |

| Pin Functions                        | 4              | 10 Power Supply Recommendations                   | 18                   |

| 7 Specifications                     | <u>5</u>       | 11 Layout                                         | 19                   |

| 7.1 Absolute Maximum Ratings         | <u>5</u>       | 11.1 Layout Guidelines                            | 19                   |

| 7.2 ESD Ratings                      | <u>5</u>       | 11.2 Layout Example                               | 19                   |

| 7.3 Recommended Operating Conditions | 5              | 12 Device and Documentation Support               | 20                   |

| 7.4 Thermal Information              | <mark>5</mark> | 12.1 Device Nomenclature                          | 20                   |

| 7.5 Electrical Characteristics       | 6              | 12.2 Receiving Notification of Documentation Upda | ates <mark>21</mark> |

| 7.6 Timing Requirements              | 7              | 12.3 Support Resources                            | 21                   |

| 7.7 Timing Diagrams                  | 8              | 12.4 Trademarks                                   | 21                   |

| 7.8 Typical Characteristics          | 9              | 13 Mechanical, Packaging, and Orderable           |                      |

| 8 Detailed Description               |                | Information                                       | 21                   |

| 8.1 Overview                         | 10             |                                                   |                      |

|                                      |                |                                                   |                      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cl | nanges from Revision B (July 2020) to Revision C (September 2020)                              | Page |

|----|------------------------------------------------------------------------------------------------|------|

| •  | Updated the numbering format for tables, figures, and cross-references throughout the document | 1    |

| •  | Updated Pin Connections                                                                        | 4    |

| •  | Added Timing Diagram                                                                           | 8    |

| •  | New Typical Characteristics                                                                    | 9    |

| _  |                                                                                                |      |

| Cl | nanges from Revision A (February 2020) to Revision B (July 2020)                               | Page |

|    | APL to RTM release                                                                             | 4    |

## **5 Device Comparison**

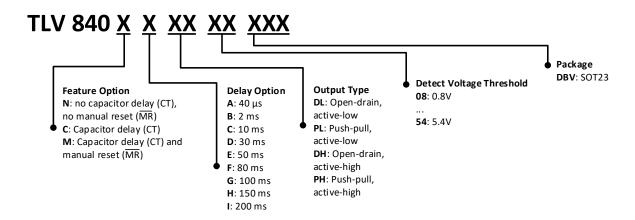

*Figure 5-1* shows the device naming nomenclature to compare the different device variants. See Table 12-1 for a more detailed explanation.

Figure 5-1. Device Naming Nomenclature

Orderable part numbers starting with TLV840C and TLV840M are only available with the delay option A. However, longer delays can be achieved through an external capacitor on the CT pin. Leaving the CT pin floating will result in typical 40us delay for these 2 feature options.

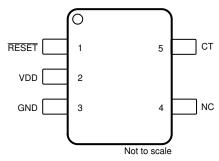

# **6 Pin Configuration and Functions**

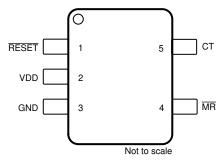

Figure 6-1. Pin Configuration TLV840C, DBV Package, 5-Pin SOT-23, TLV840C Top View

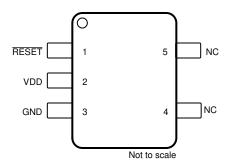

Figure 6-2. Pin Configuration TLV840M, DBV Package, 5-Pin SOT-23, TLV840M Top View

Figure 6-3. Pin Configuration TLV840N, DBV Package, 5-Pin SOT-23, TLV840N Top View

#### **Pin Functions**

|               |           | PIN       |           |     |                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------|-----------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN<br>NUMBER | TLV840CxL | TLV840MxL | TLV840NxL | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

| 1             | RESET     | RESET     | RESET     | 0   | <b>Active-Low Output Reset Signal:</b> This pin is driven logic low when VDD voltage falls below the negative voltage threshold $(V_{IT-})$ . RESET remains low (asserted) for the delay time period $(t_D)$ after VDD voltage rises above $V_{IT+}=V_{IT-}+V_{HYS}$ .                                                                           |

| 2             | VDD       | VDD       | VDD       | I   | Input Supply Voltage TLV840 monitors VDD voltage                                                                                                                                                                                                                                                                                                 |

| 3             | GND       | GND       | GND       | _   | Ground                                                                                                                                                                                                                                                                                                                                           |

| 4             | NC        | MR        | NC        | I   | Manual Reset Pull this pin to a logic low to assert a reset signal in the RESET output pin. After MRpin is left floating or pulls to logic high, the RESET output deasserts to the nominal state after the reset delay time (t <sub>D</sub> )expires.  NC stands for "No Connect". The pin can be left floating.  Recommended connection to GND. |

| 5             | СТ        | СТ        | NC        | -   | Capacitor Time Delay Pin. The CT pin offers a user-programmable delay time. Connect an external capacitor on this pin to adjust time delay. When not in use leave pin floating for the smallest fixed time delay.  NC stands for "No Connect". The pin can be left floating.  Recommended connection to GND.                                     |

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range, unless otherwise noted<sup>(1)</sup>

|                 |                                               | MIN  | MAX                      | UNIT |

|-----------------|-----------------------------------------------|------|--------------------------|------|

| Voltage         | VDD                                           | -0.3 | 6.5                      | V    |

| Voltage         | CT, MR (2), RESET (TLV840xxPL)                | -0.3 | V <sub>DD</sub> +0.3 (3) | \/   |

| voltage         | RESET (TLV840xxDL)                            | -0.3 | 6.5                      | V    |

| Current         | RESET, RESET pin                              | -20  | 20                       | mA   |

| Temperature (4) | Operating ambient temperature, T <sub>A</sub> | -40  | 125                      | °C   |

| Temperature (4) | Storage, T <sub>stg</sub>                     | -65  | 150                      | C    |

- (1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) If the logic signal driving  $\overline{MR}$  is less than  $V_{DD}$ , then additional current flows into  $V_{DD}$  and out of  $\overline{MR}$ .

- (3) The absolute maximum rating is (VDD + 0.3) V or 6.5 V, whichever is smaller

- (4) As a result of the low dissipated power in this device, it is assumed that  $T_J = T_A$ .

### 7.2 ESD Ratings

|                                            |                                                                   |                                                                                | VALUE | UNIT |

|--------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ± 2000                                                                         | V     |      |

| V <sub>(ESD)</sub>                         | Liectiostatic discharge                                           | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ± 750 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                               | MIN | NOM MAX | UNIT |

|----------------|-------------------------------|-----|---------|------|

| Voltage        | VDD (TLV840xxxL)              | 0.7 | 6       | V    |

| Voltage        | CT, RESET (TLV840xxxL), MR    | 0   | 6       | V    |

| Current        | RESET pin current             | -5  | 5       | mA   |

| T <sub>A</sub> | Operating ambient temperature | -40 | 125     | °C   |

#### 7.4 Thermal Information

| THERMAL METRIC(1)     |                                              | DBV (SOT23-5) | UNIT |

|-----------------------|----------------------------------------------|---------------|------|

|                       |                                              | 5 PINS        |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 193.5         | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 117.9         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 98.5          | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 43.4          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 97.8          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

At  $0.7~V \le V_{DD} \le 6~V$ ,  $CT = \overline{MR} = Open$ ,  $\overline{RESET}$  pull-up resistor ( $R_{pull-up}$ ) = 100 k $\Omega$  to VDD, output reset load ( $C_{LOAD}$ ) = 10 pF and over operating free-air temperature range  $-40^{\circ}C$  to 125 $^{\circ}C$ , unless otherwise noted. VDD ramp rate  $\le 100~\text{mV/µs}$ . Typical values are at  $T_A = 25^{\circ}C$

|                      | PARAMETER TEST CONDITIONS                |                                                                                                            | IDITIONS                                   | MIN                | TYP  | MAX                | UNIT   |  |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|------|--------------------|--------|--|

| соммо                | ON PARAMETERS                            |                                                                                                            |                                            |                    |      |                    |        |  |

| V <sub>DD</sub>      | Input supply voltage                     | TLV840xxxL                                                                                                 |                                            | 0.7                |      | 6                  | V      |  |

|                      | Negative-going input threshold accuracy  | V <sub>IT-</sub> = 0.8 V to 1.7 V                                                                          |                                            | -2.5               | ±0.5 | 2.5                |        |  |

| $V_{IT-}$            | (1)                                      | V <sub>IT-</sub> = 1.8 V to 5.4 V                                                                          |                                            | -2                 | ±0.5 | 2                  | %      |  |

| V <sub>HYS</sub>     | Hysteresis on V <sub>IT</sub> pin        |                                                                                                            |                                            | 2.5                | 5    | 7                  | %      |  |

|                      |                                          | V <sub>DD</sub> = 2 V<br>V <sub>IT</sub> = 0.8 V to 1.8 V                                                  | T <sub>A</sub> = -40°C to<br>85°C          |                    | 0.12 | 0.3                |        |  |

| I                    | Supply current into VDD pin (2)          | V <sub>11</sub> = 0.0 V to 1.0 V                                                                           |                                            |                    | 0.12 | 1.0                | μΑ     |  |

| I <sub>DD</sub>      | Supply current into VDD pili V           | V <sub>DD</sub> = 6 V<br>V <sub>IT</sub> = 0.8 V to 5.5 V                                                  | T <sub>A</sub> = -40°C to<br>85°C          |                    | 0.15 | 0.4                | μΑ     |  |

|                      | (2)                                      |                                                                                                            |                                            |                    | 0.15 | 1.2                |        |  |

| V <sub>MR_L</sub>    | Manual reset logic low input (2)         |                                                                                                            |                                            |                    |      | 0.3V <sub>DD</sub> | V      |  |

| V <sub>MR_H</sub>    | Manual reset logic high input (2)        |                                                                                                            |                                            | 0.7V <sub>DD</sub> |      |                    | V      |  |

| R <sub>MR</sub>      | Manual reset internal pull-up resistance |                                                                                                            |                                            |                    | 100  |                    | kΩ     |  |

| R <sub>CT</sub>      | CT pin internal resistance               |                                                                                                            |                                            |                    | 500  |                    | kΩ     |  |

| TLV840               | xxDL (Open-drain active-low)             |                                                                                                            |                                            |                    |      |                    |        |  |

| V <sub>POR</sub>     | Power on Reset Voltage (3)               | $V_{OL(max)}$ = 300 mV<br>$I_{OUT(Sink)}$ = 15 $\mu$ A                                                     |                                            |                    |      | 700                | mV     |  |

|                      |                                          | $V_{DD} = 0.7 \text{ V}, 0.8 \text{ V} \le V_{IT-} \le 1.5 \text{ V}$<br>$I_{OUT(Sink)} = 15  \mu\text{A}$ |                                            |                    |      | 300                | mV     |  |

| V <sub>OL</sub>      | Low level output voltage                 | $V_{DD}$ =1.5 V, 1.6 V $\leq$ V <sub>IT</sub> $\leq$ 3.3 V $I_{OUT(Sink)}$ = 500 $\mu$ A                   |                                            |                    |      | 300                |        |  |

|                      |                                          | $V_{DD} = 3.3 \text{ V}, 3.4 \text{ V} \le V_{IT-} \le 5.5 \text{ V}$<br>$I_{OUT(Sink)} = 2 \text{ mA}$    |                                            |                    |      | 300                | )      |  |

| I <sub>lkg(OD)</sub> | Open-Drain output leakage current        | $V_{DD} = V_{PULLUP} = 6V$<br>$T_A = -40^{\circ}C$ to 85°C                                                 | V <sub>DD</sub> = V <sub>PULLUP</sub> = 6V |                    | 10   | 100                | nA     |  |

| ing(OD)              |                                          | V <sub>DD</sub> = V <sub>PULLUP</sub> = 6V                                                                 |                                            |                    | 10   | 350                | nA     |  |

| TLV840x              | xxPL (Push-pull active-low)              |                                                                                                            |                                            |                    |      |                    |        |  |

| V <sub>POR</sub>     | Power on Reset Voltage (3)               | $V_{OL(max)} = 300 \text{ mV}$<br>$I_{OUT(Sink)} = 15 \mu\text{A}$                                         |                                            |                    |      | 700                | mV     |  |

|                      |                                          | $V_{DD} = 0.7 \text{ V}, 0.8 \text{ V} \le V_{OUT(Sink)} = 15  \mu\text{A}$                                | ′ <sub>IT</sub> ≤ 1.5 V                    |                    |      | 300                |        |  |

| $V_{OL}$             | Low level output voltage                 | $V_{DD} = 1.5 \text{ V}, 1.6 \text{ V} \le V_{OUT(Sink)} = 500  \mu\text{A}$                               | <sub>IT</sub> ≤ 3.3 V                      |                    |      | 300                | 300 mV |  |

|                      |                                          | $V_{DD} = 3.3 \text{ V}, 3.4 \text{ V} \le \text{V}$<br>$I_{OUT(Sink)} = 2 \text{ mA}$                     | ′ <sub>IT</sub> ≤ 5.5 V                    |                    |      | 300                | 300    |  |

|                      |                                          | $V_{DD} = 1.8 \text{ V}, 0.8 \text{ V} \le \text{V}$<br>$I_{OUT(Source)} = 500 \mu\text{A}$                | ′ <sub>IT</sub> ≤ 1.4 V                    | 0.8V <sub>DD</sub> |      |                    |        |  |

| V <sub>OH</sub>      | High level output voltage                | V <sub>DD</sub> = 3.3 V, 1.5 V ≤ V<br>I <sub>OUT(Source)</sub> = 500 μA                                    | <sub>IT</sub> _ ≤ 3.0 V                    | 0.8V <sub>DD</sub> |      |                    | ٧      |  |

|                      |                                          | $V_{DD} = 6 \text{ V, } 3.1 \text{ V} \le V_{IT-} \le 5.5 \text{ V}$<br>$I_{OUT(Source)} = 2 \text{ mA}$   |                                            | 0.8V <sub>DD</sub> |      |                    |        |  |

- (1)  $V_{IT-}$  threshold voltage range from 0.8 V to 5.4 V (for DL, PL versions) in 100 mV steps

- (2) If the logic signal driving MRis less than VDD, then I<sub>DD</sub> current increases based on voltage differential

- (3)  $V_{POR}$  is the minimum  $V_{DD}$  voltage level for a controlled output state

# 7.6 Timing Requirements

At  $0.7~V \le V_{DD} \le 6~V$ ,  $CT = \overline{MR} = Open$ ,  $\overline{RESET}$  pull-up resistor ( $R_{pull-up}$ ) = 100 k $\Omega$  to VDD, output reset load ( $C_{LOAD}$ ) = 10 pF and over operating free-air temperature range  $-40^{\circ}C$  to 125°C, unless otherwise noted. VDD ramp rate  $\le 100~mV/\mu s$ . Typical values are at  $T_A = 25^{\circ}C$

|                     | PARAMETER                                        |                                   | TEST CONDITIONS                                                                                                                          | MIN | TYP            | MAX | UNIT |

|---------------------|--------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|-----|------|

| t <sub>P_HL</sub>   | Propagation detect of below V <sub>IT</sub> _    | delay for VDD falling             | V <sub>DD</sub> : (V <sub>IT+</sub> + 10%) to (V <sub>IT-</sub> – 10%)                                                                   |     | 30             | 50  | μs   |

|                     |                                                  | TLV840xA                          | CT pin = Open or NC<br>(V <sub>IT-</sub> - 10%) to (V <sub>IT+</sub> + 10%)                                                              |     | 40             | 80  | μs   |

| $t_D$               | Reset time delay                                 | TLV840CA,                         | CT pin = 10 nF                                                                                                                           |     | 6.2            |     | ms   |

|                     |                                                  | TLV840MA                          | CT pin = 1 µF                                                                                                                            |     | 619            |     | ms   |

| t <sub>GI_VIT</sub> | Glitch immunity V <sub>IT</sub>                  |                                   | 5% V <sub>IT</sub> overdrive <sup>(2)</sup>                                                                                              |     | 10             |     | μs   |

| t MR_PW             | MR pin pulse duration                            | on to assert reset <sup>(3)</sup> |                                                                                                                                          |     | 500            |     | ns   |

| t MR_RES            | Propagation delay from MR low to reset assertion |                                   | $V_{DD} = 3.3 \text{ V},$ $\overline{\text{MR}} = V_{\overline{\text{MR}}_{-}\text{H}} \text{ to } V_{\overline{\text{MR}}_{-}\text{L}}$ |     | 1              |     | μs   |

| t mR_tD             | Delay from MR rele                               | ase to reset deassert             | $V_{DD}$ = 3.3 V,<br>$\overline{MR}$ = V $\overline{MR}_{L}$ to V $\overline{MR}_{H}$                                                    |     | t <sub>D</sub> |     | ms   |

<sup>(1)</sup>  $t_{P\_HL}$  measured from threshold trip point (V<sub>IT</sub>-) to RESET assert.  $V_{IT+}$  =  $V_{IT-}$  +  $V_{HYS}$

<sup>2)</sup> Overdrive % =  $[(V_{DD}/V_{IT-}) - 1] \times 100\%$

<sup>(3)</sup> Refer section on Manual Reset Input for min pulse width needed on MR pin

## 7.7 Timing Diagrams

- (1) Open-Drain timing diagram where RESET is pulled up to VDD via a pull-up resistor

- (2)  $\overline{\text{RESET}}$  output is undefined when  $V_{DD}$  is  $< V_{POR}$

Figure 7-1. Timing Diagram TLV840DL (Open-Drain Active-Low)

(3)  $\overline{RESET}$  output is undefined when  $V_{DD}$  is <  $V_{POR}$  and limited to  $V_{OL}$  for  $V_{DD}$  slew rate = 100mV /  $\mu S$

Figure 7-2. Timing Diagram TLV840PL (Push-Pull Active-Low)

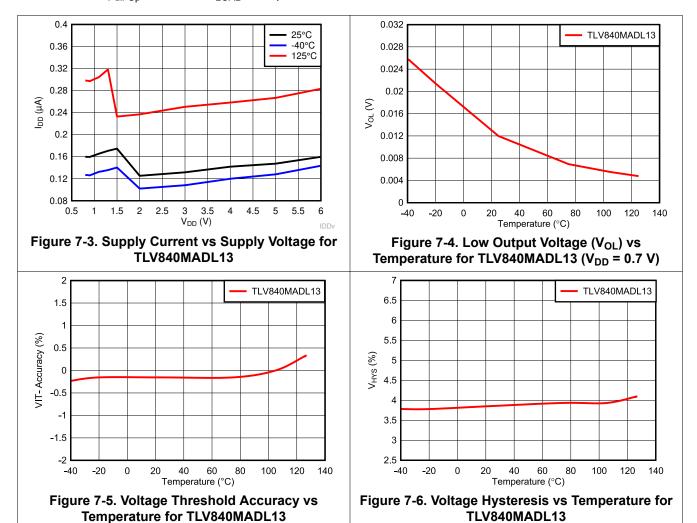

## 7.8 Typical Characteristics

Typical characteristics show the typical performance of the TLV840 device. Test conditions are  $T_A$  = 25°C, VDD = 3.3 V,  $R_{Pull-Up}$  = 100 k $\Omega$ ,  $C_{LOAD}$  = 50 pF, unless otherwise noted.

## **8 Detailed Description**

#### 8.1 Overview

The TLV840 is a family of nano-quiescent current voltage detectors with fixed threshold voltage. TLV840 features include programable reset time delay using external capacitor, active-low manual reset, 0.5% typical monitor threshold accuracy with hysteresis and glitch immunity.

Fixed negative threshold voltages ( $V_{IT}$ ) can be factory set from 0.8 V to 5.4 V. TLV840 is available in SOT-23 5-pin industry standard package.

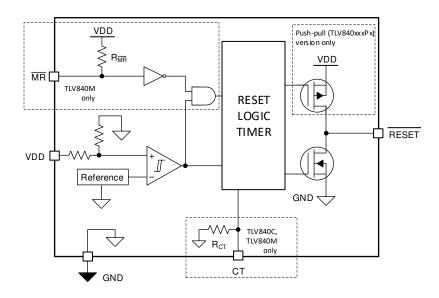

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Input Voltage (VDD)

VDD pin is monitored by the internal comparator to indicate when VDD falls below the fixed threshold voltage. VDD also functions as the supply for the internal bandgap, internal regulator, state machine, buffers and other control logic blocks. Good design practice involve placing a 0.1  $\mu$ F to 1  $\mu$ F bypass capacitor at VDD input for noisy applications to ensure enough charge is available for the device to power up correctly.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

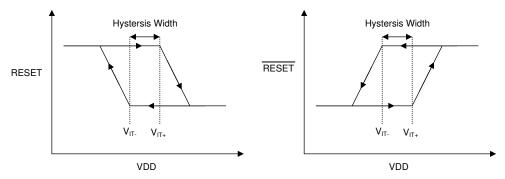

#### 8.3.1.1 VDD Hysteresis

The internal comparator has built-in hysteresis to avoid erroneous output reset release. If the voltage at the VDD pin falls below  $V_{IT}$  the output reset is asserted. When the voltage at the VDD pin goes above  $V_{IT}$  plus hysteresis  $(V_{HYS})$  the output reset is deasserted after  $t_D$  delay.

Figure 8-1. Hysteresis Diagram

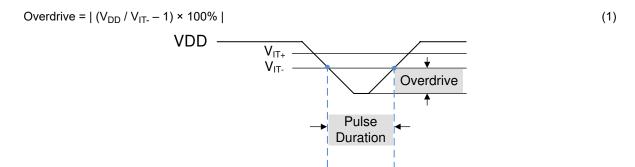

## 8.3.1.2 VDD Transient Immunity

The TLV840 is immune to quick voltage transients or excursion on VDD. Sensitivity to transients depends on both pulse duration ( $t_{Gl\_VIT}$ ) found in Section 7.6 and overdrive. Overdrive is defined by how much VDD deviates from the specified threshold. Threshold overdrive is calculated as a percent of the threshold in question, as shown in Equation 1.

Figure 8-2. Overdrive vs Pulse Duration

#### 8.3.2 User-Programmable Reset Time Delay

The reset time delay can be set to a minimum value of 80  $\mu$ s by leaving the CT pin floating, or a maximum value of approximately 6.2 seconds by connecting 10  $\mu$ F delay capacitor. The reset time delay (t<sub>D</sub>) can be programmed by connecting a capacitor no larger than 10  $\mu$ F between CT pin and GND.

The relationship between external capacitor ( $C_{CT}$ ) in  $\mu F$  at CT pin and the time delay ( $t_D$ ) in seconds is given by Equation 2.

$$t_D = -\ln (0.29) \times R_{CT} \times C_{CT} + t_D (CT pin = Open)$$

(2)

Equation 2 is simplified to Equation 3 by plugging  $R_{CT}$  and  $t_D$  (CT pin = Open) given in Section 7.5 section:

$$t_D = 618937 \times C_{CT} + 80\mu s$$

(3)

Equation 4 solves for external capacitor value (C<sub>CT</sub>) in units of µF where t<sub>D</sub> is in units of seconds

$$C_{CT} = (t_D - 80\mu s) \div 618937$$

(4)

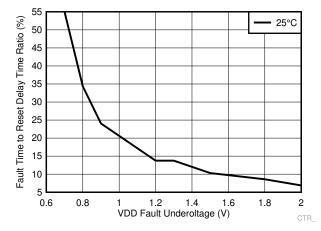

The recommended maximum delay capacitor for the TLV840 is limited to 10  $\mu$ F as this ensures there is enough time for the capacitor to fully discharge when the reset condition occurs. When a voltage fault occurs, the previously charged up capacitor discharges, and if the monitored voltage returns from the fault condition before the delay capacitor discharges completely, the reset delay will be shorter than expected because the delay capacitor will begin charging from a voltage above zero. Larger delay capacitors can be used so long as the capacitor has enough time to fully discharge during the duration of the voltage fault. The amount of time required to discharge the delay capacitor relative to the reset delay increases as VDD overdrive increases as shown in Figure 8-3.

Figure 8-3.  $C_{CT}$  Discharge Time During Fault Condition ( $V_{IT}$  = 2.1 V,  $C_{CT}$  = 1  $\mu$ F)

## 8.3.3 Manual Reset (MR) Input for TLV840M Only

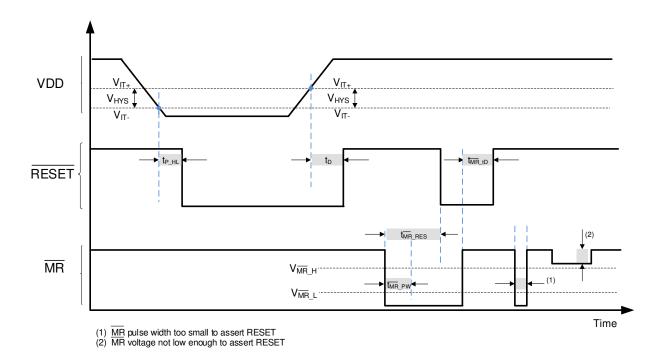

The manual reset ( $\overline{MR}$ ) input allows a processor GPIO or other logic circuits to initiate a reset. A logic low on  $\overline{MR}$  with pulse duration longer than t $_{\overline{MR}\_{PW}}$  will cause the reset output to assert. After  $\overline{MR}$  returns to a logic high ( $V_{\overline{MR}\_{H}}$ ) and VDD is above  $V_{\overline{IT}+}$ , reset is deasserted after the user programmed reset time delay ( $t_D$ ) expires.

The minimum duration for which  $\overline{MR}$  is held under V  $_{\overline{MR}\_L}$  must be at least 1% of t  $_{\overline{MR}\_tD}$ . Otherwise, the effective reset delay will be shorter roughly by the difference between 1% of t  $_{\overline{MR}\_tD}$  and the actual  $\overline{MR}$  pulse width. For large capacitor based delays this difference could be noticeable unless care is taken to lengthen the  $\overline{MR}$  pulse width.

$\overline{MR}$  is internally connected to VDD through a pull-up resistor R  $_{\overline{MR}}$  shown in Section 8.2. If the logic signal controlling  $\overline{MR}$  is less than VDD, then additional current flows from VDD into  $\overline{MR}$  internally. For minimum current consumption, drive  $\overline{MR}$  to either VDD or GND. V  $_{\overline{MR}}$  should not be higher than VDD voltage.

Figure 8-4. Timing Diagram MR and RESET (TLV840M)

#### 8.3.4 Output Logic

## 8.3.4.1 RESET Output, Active-Low

RESET (Active-Low) applies to TLV840DL (Open-Drain) and TLV840PL (Push-Pull) hence the "L" in the device name. RESET remains high (deasserted) as long as VDD is above the negative threshold ( $V_{IT-}$ ) and the  $\overline{MR}$  pin is floating or above V  $\overline{MR}_H$ . If VDD falls below the negative threshold ( $V_{IT-}$ ) or if  $\overline{MR}$  is driven low, then  $\overline{RESET}$  is asserted.

When  $\overline{MR}$  is again logic high or floating and VDD rise above  $V_{IT+}$ , the delay circuit will hold  $\overline{RESET}$  low for the specified reset time delay ( $t_D$ ). When the reset time delay has elapsed, the  $\overline{RESET}$  pin goes back to logic high voltage ( $V_{OH}$ ).

The TLV840DL (Open-Drain) version, denoted with "D" in the device name, requires a pull-up resistor to hold RESET pin high. Connect the pull-up resistor to the desired pull-up voltage source and RESET can be pulled up to any voltage up to 6.5 V independent of the VDD voltage. To ensure proper voltage levels, give some consideration when choosing the pull-up resistor values. The pull-up resistor value determines the actual  $V_{OL}$ , the output capacitive loading, and the output leakage current ( $I_{lkg(OD)}$ ).

The Push-Pull variants (TLV840PL and TLV840PH), denoted with "P" in the device name, does not require an external pull-up resistor.

#### 8.4 Device Functional Modes

Table 8-1 summarizes the various functional modes of the device. Logic high is represented by "H" and logic low is represented by "L".

| VDD                                                    | MR       | RESET     | RESET     |  |  |  |

|--------------------------------------------------------|----------|-----------|-----------|--|--|--|

| VDD < V <sub>POR</sub>                                 | Ignored  | Undefined | Undefined |  |  |  |

| V <sub>POR</sub> < V <sub>DD</sub> < V <sub>IT</sub> - | Ignored  | Н         | L         |  |  |  |

| VDD ≥ V <sub>IT-</sub>                                 | L        | Н         | L         |  |  |  |

| VDD ≥ V <sub>IT-</sub>                                 | Н        | L         | Н         |  |  |  |

| VDD ≥ V <sub>IT-</sub>                                 | Floating | L         | Н         |  |  |  |

Table 8-1. Truth Table

#### 8.4.1 Normal Operation (V<sub>DD</sub> > VPOR)

When VDD is greater than VPOR, the reset signal is determined by the voltage on the VDD pin with respect to the trip point  $(V_{IT})$

- MR high: the reset signal corresponds to VDD with respect to the threshold voltage.

- MR low: in this mode, the reset is asserted regardless of the threshold voltage.

#### 8.4.2 Below Power-On-Reset ( $V_{DD} < V_{POR}$ )

When the voltage on VDD is lower than  $V_{POR}$ , the device does not have enough bias voltage to internally pull the asserted output low or high and reset voltage level is undefined.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

# 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The following sections describe in detail how to properly use this device, depending on the requirements of the final application.

## 9.2 Typical Application

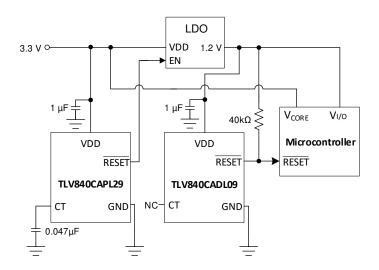

#### 9.2.1 Design 1: Dual Rail Monitoring with Power-up Sequencing

A typical application for the TLV840 is voltage rail monitoring and power-up sequencing as shown in Figure 9-1. The TLV840 can be used to monitor any rail above 0.9 V. In this design application, two TLV840 devices monitor two separate voltage rails and sequences the rails upon power-up. The TLV840CAPL29 is used to monitor the 3.3-V main power rail and the TLV840CADL09 is used to monitor the 1.2-V rail provided by the LDO for other system peripherals. The RESET output of the TLV840CAPL29 is connected to the ENABLE input of the LDO. A reset event is initiated on either voltage supervisor when the VDD voltage is less than V<sub>IT</sub>.

Figure 9-1. TLV840 Voltage Rail Monitor and Power-Up Sequencer Design Block Diagram

#### 9.2.1.1 Design Requirements

This design requires voltage supervision on two separate rails: 3.3-V and 1.2-V rails. The voltage rail needs to sequence upon power up with the 3.3-V rail coming up first followed by the 1.2-V rail at least 25 ms after.

| PARAMETER                          | DESIGN REQUIREMENT                                               | DESIGN RESULT                                                                                                    |

|------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Two Rail Voltage Supervision       | Monitor 3.3-V and 1.2-V rails                                    | Two TLV840 devices provide voltage monitoring with 1% accuracy with device options available in 0.1 V variations |

| Voltage Rail Sequencing            | Power up the 3.3-V rail first followed by 1.2-V rail 25 ms after | The CT capacitor on TLV840CAPL29 is set to 0.047 µF for a reset time delay of 29 ms typical                      |

| Maximum device current consumption | 1 μΑ                                                             | Each TLV840 requires 350 nA typical                                                                              |

#### 9.2.1.2 Detailed Design Procedure

The primary constraint for this application is choosing the correct device to monitor the supply voltage of the microprocessor. The TLV840 can monitor any voltage between 0.8 V and 5.4 V. Depending on how far away from the nominal voltage rail the user wants the voltage supervisor to trigger determines the correct voltage supervisor variant to choose. In this example, the first TLV840 triggers when the 3.3-V rail falls to 2.9 V. The second TLV840 triggers a reset when the 1.2-V rail falls to 0.9 V. The secondary constraint for this application is the reset time delay that must be at least 25 ms to allow the microprocessor, and all other devices using the 3.3-V rail, enough time to startup correctly before the 1.2-V rail is enabled via the LDO. Because a minimum time is required, the user must account for capacitor tolerance. For applications with ambient temperatures ranging from  $-40^{\circ}$ C to  $+125^{\circ}$ C,  $C_{CT}$  can be calculated using  $R_{CT}$  and solving for  $C_{CT}$  in Equation 2. Solving Equation 2 for 25 ms gives a minimum capacitor value of 0.04  $\mu$ F which is rounded up to a standard value 0.047  $\mu$ F to account for capacitor tolerance.

A 1  $\mu F$  decoupling capacitor is connected to the VDD pin as a good analog design practice. The pull-up resistor is only required for the Open-Drain device variants and is calculated to ensure that  $V_{OL}$  does not exceed max limit given the Isink possible at the expected supply voltage. In this design example nominal VDD is 1.2 V but dropping to 0.9 V. The *Recommended Operating Conditions* table provides 15  $\mu A$  I sink for 0.7 V VDD, which is the closest voltage to this design example. Using 15  $\mu A$  of Isink and 300 mV max  $V_{OL}$ , gives us 40 k $\Omega$  for the pull-up resistor. Any value higher than 40 k $\Omega$  would ensure that  $V_{OL}$  will not exceed 300 mV max specification.

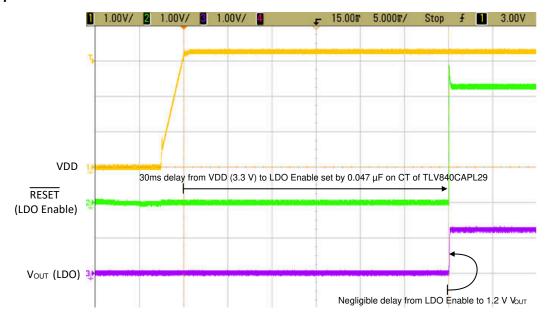

#### 9.2.1.3 Application Curves

Figure 9-2. Startup Sequence Highlighting the Delay Between 3.3V and 1.2V Rails

Submit Document Feedback

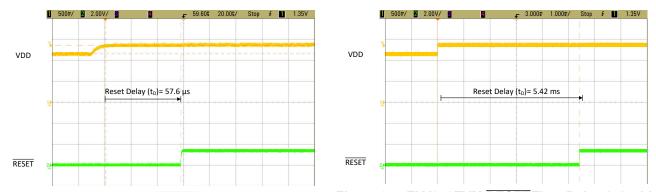

#### 9.2.2 Application Curve: TLV840EVM

These application curves are taken with the TLV840EVM. Please see the *TLV840EVM User Guide* for more information.

Figure 9-3. TLV840EVM RESET Time Delay (t<sub>D</sub>) with Figure 9-4. TLV840EVM RESET Time Delay (t<sub>D</sub>) with No Capacitor 0.01-µF Capacitor

Figure 9-5. TLV840EVM RESET Time Delay (t<sub>D</sub>) with 0.1-μF Capacitor

## 10 Power Supply Recommendations

These devices are designed to operate from an input supply with a voltage range between 0.7 V and 6 V. TI recommends an input supply capacitor between the VDD pin and GND pin. This device has a 6.5 V absolute maximum rating on the VDD pin. If the voltage supply providing power to VDD is susceptible to any large voltage transient that can exceed 6.5 V, additional precautions must be taken.

## 11 Layout

#### 11.1 Layout Guidelines

Make sure that the connection to the VDD pin is low impedance. Good analog design practice recommends placing a minimum  $0.1~\mu F$  ceramic capacitor as near as possible to the VDD pin. If a capacitor is not connected to the CT pin, then minimize parasitic capacitance on this pin so the rest time delay is not adversely affected.

- Make sure that the connection to the VDD pin is low impedance. Good analog design practice is to place a >0.1 µF ceramic capacitor as near as possible to the VDD pin.

- If a C<sub>CT</sub> capacitor is used, place these components as close as possible to the CT pin. If the CT pin is left unconnected, make sure to minimize the amount of parasitic capacitance on the pin to <5 pF.

- Place the pull-up resistors on RESET pin as close to the pin as possible.

## 11.2 Layout Example

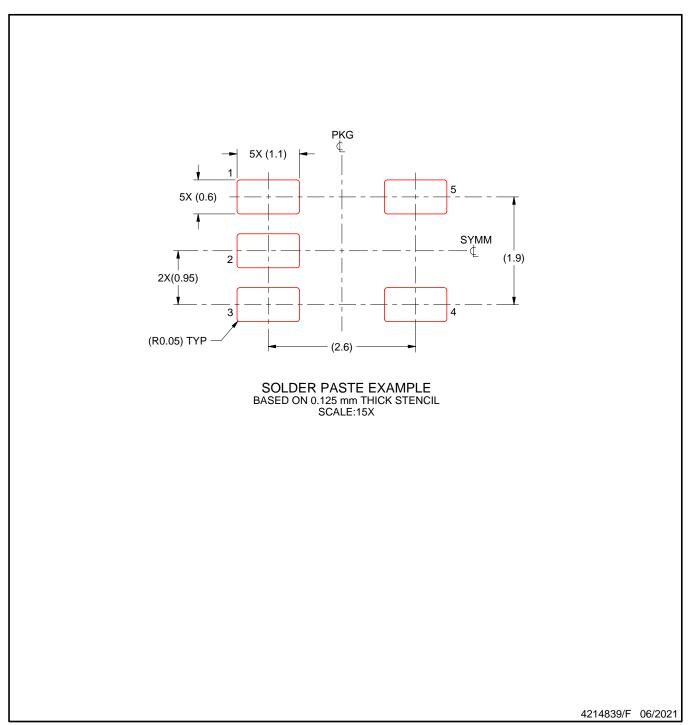

The layout example in shows how the TLV840 is laid out on a printed circuit board (PCB) with a user-defined delay.

Figure 11-1. TLV840C Recommended Layout

# 12 Device and Documentation Support

## 12.1 Device Nomenclature

Table 12-1 shows how to decode the function of the device based on its part number

**Table 12-1. Device Naming Convention**

| DESCRIPTION                    | NOMENCLATURE        | VALUE                                                  |  |  |  |  |

|--------------------------------|---------------------|--------------------------------------------------------|--|--|--|--|

| Generic Part number            | TLV840              | TLV840                                                 |  |  |  |  |

| Feature Option                 | N                   | No capacitor adjustable delay or manual reset options  |  |  |  |  |

|                                | C <sup>1</sup>      | CT pin for programmable delay using external capacitor |  |  |  |  |

|                                | M <sup>1</sup>      | Manual Reset option in addition to CT pin              |  |  |  |  |

| Delay Option                   | A                   | 40 μs (No internal reset time delay)                   |  |  |  |  |

|                                | В                   | 2 ms reset time delay                                  |  |  |  |  |

|                                | С                   | 10 ms reset time delay                                 |  |  |  |  |

|                                | D                   | 30 ms reset time delay                                 |  |  |  |  |

|                                | E                   | 50 ms reset time delay                                 |  |  |  |  |

|                                | F                   | 80 ms reset time delay                                 |  |  |  |  |

|                                | G                   | 100 ms reset time delay                                |  |  |  |  |

|                                | Н                   | 150 ms reset time delay                                |  |  |  |  |

|                                | I                   | 200 ms reset time delay                                |  |  |  |  |

| Variant code (Output Topology) | DL                  | Open-Drain, Active-Low                                 |  |  |  |  |

|                                | PL                  | Push-Pull, Active-Low                                  |  |  |  |  |

|                                | DH                  | Open-Drain, Active-High                                |  |  |  |  |

|                                | PH                  | Push-Pull, Active-High                                 |  |  |  |  |

| Detect Voltage Option          | ## (two characters) | Example: 12 stands for 1.2 V threshold                 |  |  |  |  |

| Package                        | DBV                 | SOT23-5                                                |  |  |  |  |

| Reel                           | R                   | Large Reel                                             |  |  |  |  |

1. Orderable part numbers starting with TLV840C and TLV840M are only available with the delay option A. However, longer delays can be achieved through an external capacitor on the CT pin. Leaving the CT pin floating will result in typical 40us delay for these 2 feature options

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

# 12.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 12.3 Support Resources

#### 12.4 Trademarks

All other trademarks are the property of their respective owners.

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

28-Oct-2022 www.ti.com

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| TLV840CADL11DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2CLF                 | Samples |

| TLV840CADL14DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2G1F                 | Samples |

| TLV840CADL28DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2CKF                 | Samples |

| TLV840CADL29DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2CNF                 | Samples |

| TLV840CADL40DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 2ILF                 | Samples |

| TLV840MADL08DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2H6F                 | Samples |

| TLV840MADL10DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2G2F                 | Samples |

| TLV840MADL13DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2CMF                 | Samples |

| TLV840MADL29DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2G3F                 | Samples |

| TLV840MADL30DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2G4F                 | Samples |

| TLV840MADL52DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2G5F                 | Samples |

| TLV840NADH29DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 2H5F                 | Samples |

| TLV840NADL20DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2G6F                 | Samples |

| TLV840NADL33DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2CIF                 | Samples |

| TLV840NADL35DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2CJF                 | Samples |

| TLV840NADL46DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2G7F                 | Samples |

| TLV840NAPL50DBVR | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | 2GOF                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**PACKAGE OPTION ADDENDUM**

www.ti.com 28-Oct-2022

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: Til defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TLV840:

Automotive : TLV840-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 18-Feb-2023

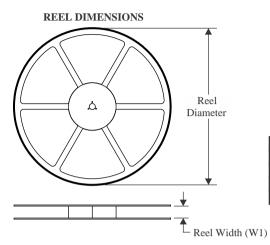

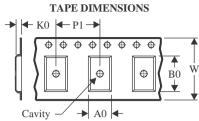

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

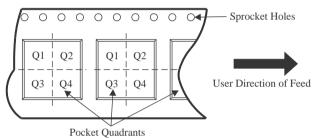

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLV840CADL11DBVR | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 9.0                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL11DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL14DBVR | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 9.0                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL14DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL28DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL28DBVR | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 9.0                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL29DBVR | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 9.0                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL29DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL40DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840CADL40DBVR | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 9.0                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL08DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL08DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL10DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL10DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL13DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL13DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

# PACKAGE MATERIALS INFORMATION

www.ti.com 18-Feb-2023

| Device           | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLV840MADL29DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL29DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL30DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL30DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL52DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840MADL52DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADH29DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL20DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL20DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL33DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL33DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL35DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL35DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL46DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NADL46DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NAPL50DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV840NAPL50DBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

www.ti.com 18-Feb-2023

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV840CADL11DBVR | SOT-23       | DBV             | 5    | 3000 | 180.0       | 180.0      | 18.0        |

| TLV840CADL11DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840CADL14DBVR | SOT-23       | DBV             | 5    | 3000 | 180.0       | 180.0      | 18.0        |

| TLV840CADL14DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840CADL28DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840CADL28DBVR | SOT-23       | DBV             | 5    | 3000 | 180.0       | 180.0      | 18.0        |

| TLV840CADL29DBVR | SOT-23       | DBV             | 5    | 3000 | 180.0       | 180.0      | 18.0        |

| TLV840CADL29DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840CADL40DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840CADL40DBVR | SOT-23       | DBV             | 5    | 3000 | 180.0       | 180.0      | 18.0        |

| TLV840MADL08DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL08DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL10DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL10DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL13DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL13DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL29DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL29DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

# PACKAGE MATERIALS INFORMATION

www.ti.com 18-Feb-2023

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV840MADL30DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL30DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL52DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840MADL52DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADH29DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL20DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL20DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL33DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL33DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL35DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL35DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL46DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NADL46DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NAPL50DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV840NAPL50DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

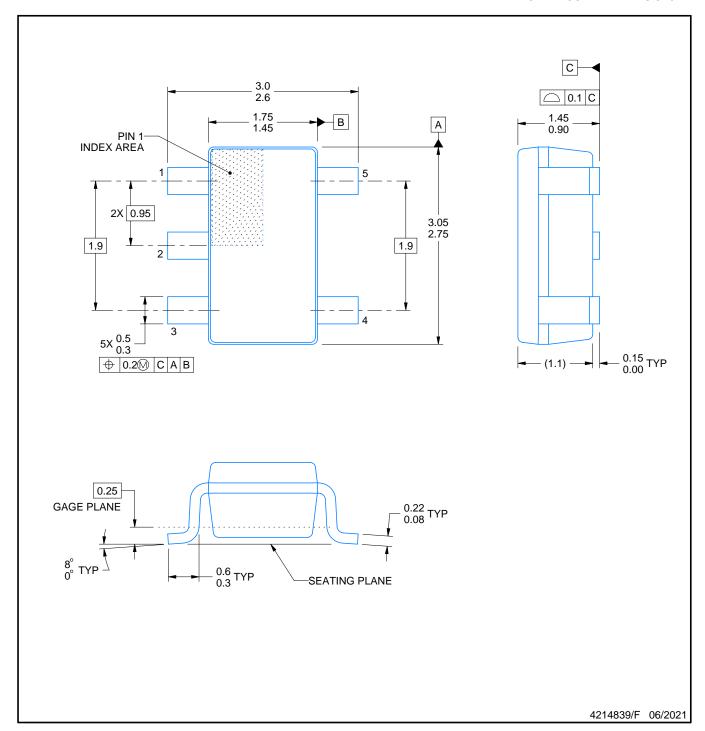

SMALL OUTLINE TRANSISTOR

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

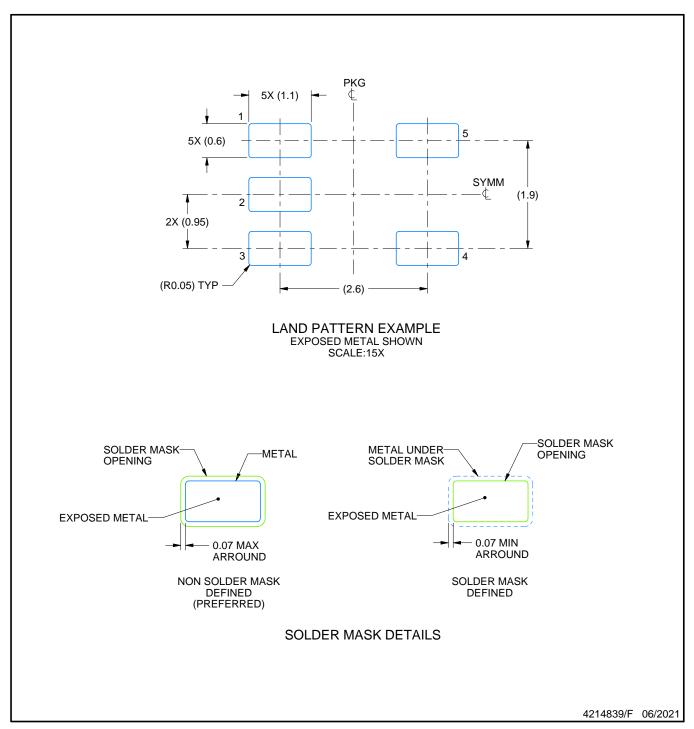

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 5. Publication IPC-7351 may have alternate designs.

- 6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

<sup>7.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

<sup>8.</sup> Board assembly site may have different recommendations for stencil design.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Supervisory Circuits category:

Click to view products by Texas Instruments manufacturer:

Other Similar products are found below:

CAT853STBI-T3 RT9818C-27GU3 DS1232L NCV302HSN45T1G STM6710FWB7F PT7M6127NLTA3EX XC6118C25AGR-G

ISL88011IH526Z-TK ISL88013IH529Z-TK ISL88705IP846Z ISL88706IP831Z ISL88708IB844Z ISL88708IP831Z TCM811MERCTR

X40420S14-A X40421S14-C X40430S14-A X40430S14I-A X40430S14I-B X40431S14-A X40431S14-B X40431S14-C X40431S14I-A

X40431S14I-B X40431S14I-C X4043P-2.7 X4043PI-2.7 X4043S8-2.7T1 X4043S8IZ-2.7 X4043S8IZT1 X4043S8T1 X4045P X4045PI

X4045PI-2.7 X4045S8-2.7T1 X4045S8IZ X4045S8T1 X4163P X4163P-2.7 X4163PI X4163PI-2.7 X4163S8 X4165P X4165P-2.7

X4165PI X4165PI-2.7 X4165S8I-2.7 X4283S8I X4323S8-2.7 X4323S8I-2.7