#### TMS320C5535, TMS320C5534, TMS320C5533, TMS320C5532

ZHCS277C - AUGUST 2011 - REVISED APRIL 2014

# TMS320C5535、C5534、C5533、C5532 定点数字信号处理器

#### 1 器件概述

# 1.1 特性

- 内核:

- 高性能、低功耗 TMS320C55x 定点数字信号处理器

- 20ns, 10ns 指令周期时间

- 50MHz, 100MHz 时钟速率

- 每个周期执行一条或两条指令

- 两个乘积累积单元(每秒高达2亿次乘积累加运算[MMACS])

- 两个算术和逻辑单元 (ALU)

- 三个内部数据和操作数读取总线以及两个内部 数据和操作数写入总线

- 与 C55x 器件软件兼容

- 提供工业温度器件

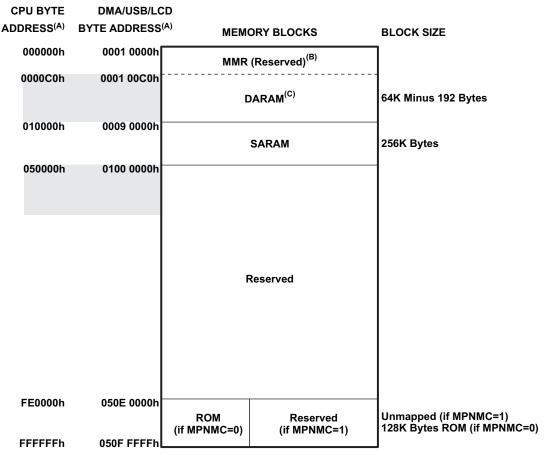

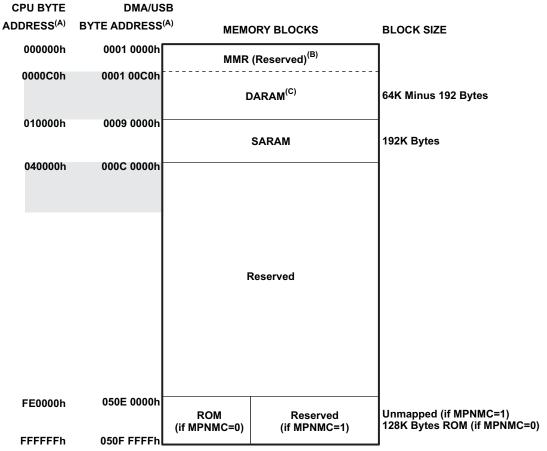

- 320KB 零等待状态片上 RAM,包括:

- 64KB 双访问 RAM (DARAM), 8 块 4K x 16 位.

- 256KB 单访问 RAM (SARAM), 32 块 4K x 16 位

- 128KB 零等待状态片上 ROM (4 块 16K x 16 位)

- 紧密耦合快速傅里叶变换 (FFT) 硬件加速器

- 外设:

- 直接存储器存取 (DMA) 控制器

- 四个 DMA,各配有四条通道(共 16 条通道)

- 三个 32 位通用 (GP) 定时器

- 一个可选用为看门狗或 GP

- 两个嵌入式多媒体卡 (eMMC) 和安全数字 (SD) 接口

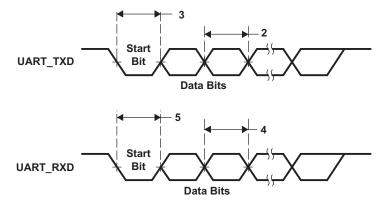

- 通用异步收发器 (UART)

- 具有四芯片选择的串行端口接口 (SPI)

- 主控和受控内部集成电路(I<sup>2</sup>C 总线)

- 四个针对数据传输的内部集成电路 (IC) 声音 (I<sup>2</sup>S 总统)

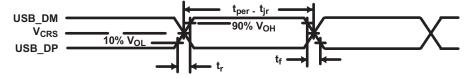

- 带有集成型 2.0 高速物理层 (PHY) 的器件 USB 端口,支持:

- USB 2.0 全速和高速器件

- 具有异步接口的 LCD 桥

- 10 位 4 输入逐次逼近 (SAR) ADC

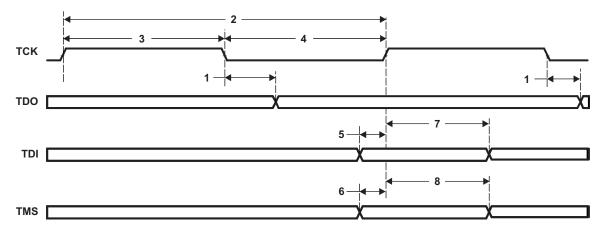

- IEEE-1149.1 (JTAG) 边界扫描兼容

- 32 个通用 I/O (GPIO) 引脚 (与其它器件功能复用)

- 可同时配置最多 20 个 GPIO 引脚

- 电源:

- 四个内核隔离的电源域:模拟,RTC,CPU和外设,以及USB

- 三个 I/O 隔离电源域: RTC I/O, USB 物理层 (PHY) 和 DV<sub>DDIO</sub>

- 提供三个集成低压降稳压器 (LDO)(DSP\_LDO、ANA\_LDO 和 USB\_LDO) 分别为以下隔离域供电: DSP 内核、模拟和 USB 内核

- 1.05V 内核 (50 MHz),1.8V、2.5V、2.75V 或 3.3V I/O

- 1.3V 内核 (100 MHz), 1.8V、2.5V、2.75V 或 3.3V I/O

- 时钟:

- 具有晶振输入、独立时钟域和独立电源的实时时 钟 (RTC)

- 低功耗软件可编程锁相环 (PLL) 时钟发生器

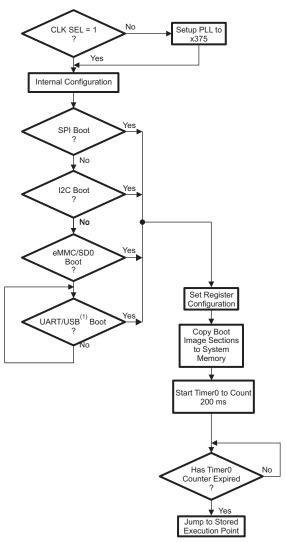

- 引导加载程序:

- 片上 ROM 引导加载程序 (RBL),可从 SPI EEPROM、SPI 串行闪存或 I<sup>2</sup>C EEPROM eMMC、SD、SDHC、UART 和 USB 启动

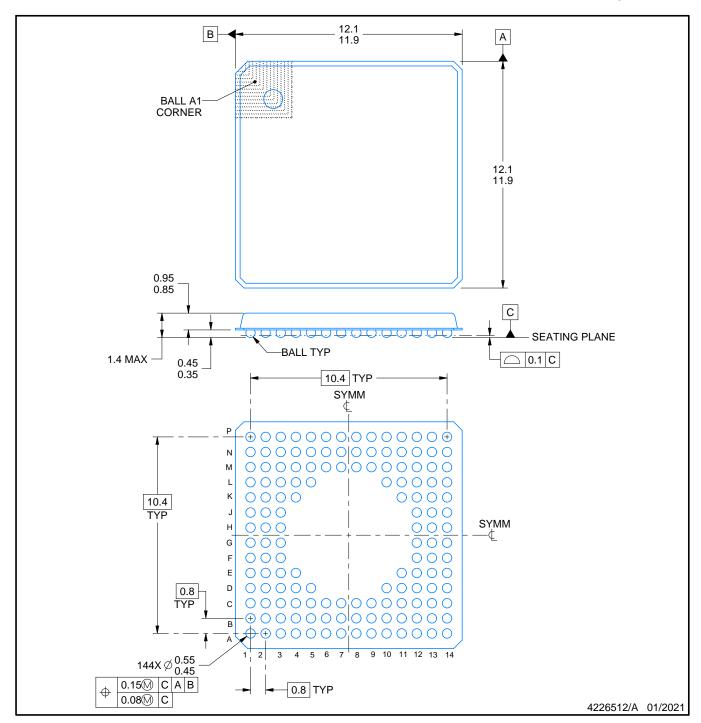

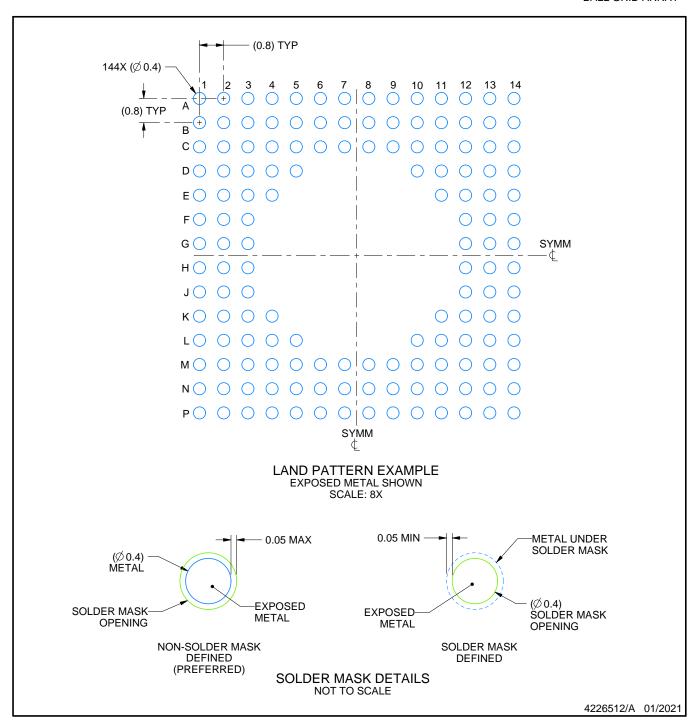

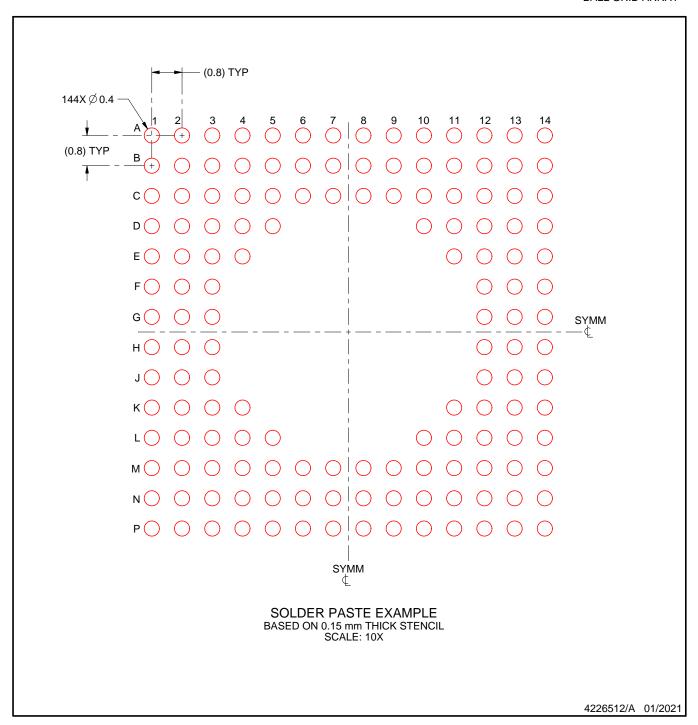

- 封装:

- 144 端子无铅塑料 BGA(球栅阵列)封装(后缀 ZHH)

#### 1.2 应用

- 无线音频器件(例如:头戴式耳机、麦克风、免提电话)

- 回声消除耳机

- 便携式医疗设备

- 语音应用

- 工业控制

- 指纹识别

- 软件定义的无线电

# 1.3 说明

这些器件是 TI C5000™ 定点数字信号处理器 (DSP) 产品系列的成员之一,适用于低功耗应用。

定点 DSP 基于 TMS320C55x DSP 系列 CPU 处理器内核。 C55x DSP 架构通过增加的并行性和重视节能来实现高性能和低功耗。 CPU 支持一个内部总线结构,此结构包含一条程序总线,一条 32 位读取总线和两条 16 位数据读取总线,两条数据写入总线和专门用于外设和 DMA 操作的附加总线。 这些总线可实现在一个单周期内执行高达四次 16 位数据读取和两次 16 位数据写入的功能。 此器件还包含四个 DMA 控制器,每个控制器具有 4 条通道,从而在无需 CPU 干预的情况下提供 16 条独立通道环境的数据移动。 每个DMA 控制器在每周期可执行一个 32 位数据传输,此数据传输与 CPU 的运行并行并且不受 CPU 运行的影响。

C55x CPU 提供两个乘积累积 (MAC) 单元,每个单元在一个单周期内能够进行 17 位乘以 17 位乘法以及 32 位加法。一个中央 40 位算术和逻辑单元 (ALU) 由一个附加 16 位 ALU 提供支持。 ALU 的使用受指令集控制,从而提供优化并行运行和功耗的能力。 C55x CPU 内的地址单元 (AU) 和数据单元 (DU) 对这些资源进行管理。

C55x CPU 支持一个可变字节宽度指令集以改进代码密度。 指令单元 (IU) 执行从内部或外部存储器中的 32 位程序取指令并且进行针对程序单元 (PU) 的指令排队。 PU 对指令进行解码,将任务指向地址单元和数据单元资源,并管理受到完全保护的管线。 跳转预测功能避免了条件指令执行时的管线冲刷。

TMS320C5535 上的通用输入和输出功能与 10 位 SAR ADC 一起为状态、中断以及用于键盘和媒体接口的位 I/O 提供足够的引脚。 通过以下器件为串行媒体提供支持: 两个安全数字 (SD) 外设、四个内部 IC 声音(I2S 总线)模块、一个具有多达四芯片选择的串行端口接口 (SPI)、一个 I<sup>2</sup>C 主控和受控接口和一个通用异步收发器 (UART) 接口。

其它外设包括: 一条仅支持器件模式的高速通用串行总线 (USB2.0) (TMS320C5532 上不提供)、一个实时时钟 (RTC)、三个通用定时器(其中一个可配置为看门狗定时器)和一个模拟锁相环 (APLL) 时钟发生器。

此外,TMS320C5535 还包括紧密耦合 FFT 硬件加速器。 紧密耦合 FFT 硬件加速器支持 8 至 1024 点(2 的幂)实值和复值 FFT。

器件中还包括以下三个集成 LDO, 用于为器件的各个部分供电。

ANA\_LDO (所有器件) 为 DSP PLL (VDDA PLL)、SAR 和电源管理电路 (VDDA ANA) 提供 1.3V 电压。

DSP\_LDO(TMS320C5535 和 C5534)为 DSP 内核 ( $CV_{DD}$ )(一旦检测到工作频率范围,便可由软件实时进行选择)提供 1.3V 或 1.05V 电压。 在最低功耗运行状态下,编程人员可以关断内部 DSP\_LDO,切断 DSP 内核 ( $CV_{DD}$ ) 电源,由外部电源为 RTC ( $CV_{DDRTC}$  和  $DV_{DDRTC}$ ) 供电。 可通过 RTC 报警中断或 WAKEUP 引脚重新使能内部 DSP\_LDO,然后重新对 DSP 内核加电。 DSP\_LDO 复位后,可针对引导加载程序提供 1.3V 工作电压。 对于 50MHz 器件,复位 DSP\_LDO 后必须将其设定为 1.05V,使其与内核电压  $CV_{DD}$  匹配,从而确保正常运行

USB\_LDO (TMS320C5535、C5534 和 C5533) 为 USB 内核数字电路 (USB\_V<sub>DD1P3</sub>) 和物理层电路 (USB\_V<sub>DD1P3</sub>) 提供 1.3 V 电压。

这些器件由业界备受赞誉的 eXpressDSP™、Code Composer Studio™ 集成开发环境 (IDE)、DSP/BIOS™、德州仪器 (TI) 的算法标准和业界最大的第三方网络提供支持。 Code Composer Studio IDE 提供的代码生成工具包括一个 C 语言编译器和连接器、RTDX™、XDS100、 XDS510™、 XDS560™ 仿 真器件驱动程序和评估模块。 这些器件也受 C55x DSP 库以及芯片支持库的支持,此库特有 50 多个基础软件内核(FIR 滤波器、IIR 滤波器、FFT 和多种数学函数)。

# 表 1-1. 器件信息

| 部件号                | 封装                  | 封装尺寸            |

|--------------------|---------------------|-----------------|

| TMS320C5535AZHH10  | BGA MICROSTAR (144) | 12.0mm x 12.0mm |

| TMS320C5535AZHHA10 | BGA MICROSTAR (144) | 12.0mm x 12.0mm |

| TMS320C5534AZHH10  | BGA MICROSTAR (144) | 12.0mm x 12.0mm |

| TMS320C5534AZHHA10 | BGA MICROSTAR (144) | 12.0mm x 12.0mm |

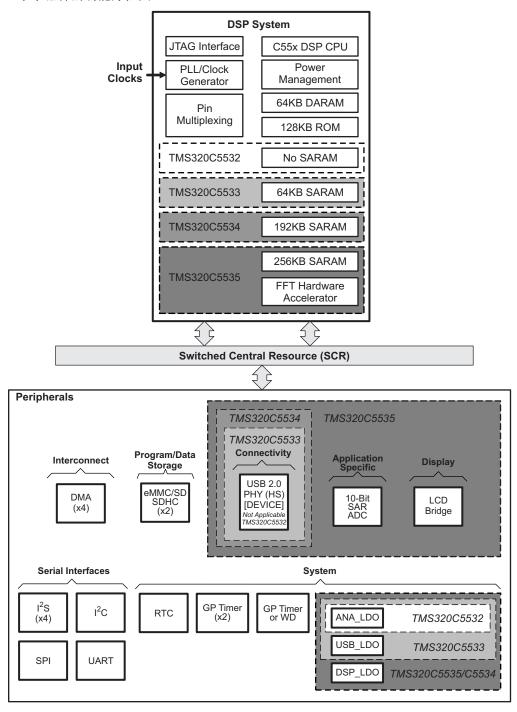

# 1.4 功能方框图

图 1-1 显示了器件的功能方框图。

图 1-1. 功能方框图

| ىك | - |

|----|---|

| ᇧ  | 2 |

|    |   |

| 1 | 器件   | 概述 <u>1</u>                          |   | 5.5  | Thermal Characteristics                 | 54          |

|---|------|--------------------------------------|---|------|-----------------------------------------|-------------|

|   | 1.1  | 特性1                                  |   | 5.6  | Power-On Hours                          | 54          |

|   | 1.2  | 应用                                   |   | 5.7  | Timing and Switching Characteristics    | 55          |

|   | 1.3  | 说明 <u>2</u>                          | 6 | Deta | ailed Description                       | 118         |

|   | 1.4  | 功能方框图4                               |   | 6.1  | CPU                                     | 118         |

| 2 | 修订   | 历史记录                                 |   | 6.2  | Memory                                  | 118         |

| 3 | Devi | ice Comparison 7                     |   | 6.3  | Identification                          | 144         |

|   | 3.1  | Device Characteristics 7             |   | 6.4  | Boot Modes                              | 145         |

| 4 | Tern | ninal Configuration and Functions 13 | 7 | Devi | ice and Documentation Support           | 149         |

|   | 4.1  | Pin Diagram <u>13</u>                |   | 7.1  | Device Support                          | 149         |

|   | 4.2  | Signal Descriptions 17               |   | 7.2  | Documentation Support                   | 150         |

|   | 4.3  | Pin Multiplexing46                   |   | 7.3  | Related Links                           | <u>151</u>  |

| 5 | Spec | cifications 49                       |   | 7.4  | 社区资源                                    | 151         |

|   | 5.1  | Absolute Maximum Ratings 49          |   | 7.5  | Trademarks                              | <u>151</u>  |

|   | 5.2  | Recommended Operating Conditions     |   | 7.6  | 静电放电警告                                  | <u>15</u> 1 |

|   | 5.3  | Electrical Characteristics           |   | 7.7  | Glossary                                | <u>151</u>  |

|   | 5.4  | Handling Ratings54                   | 8 |      | hanical Packaging and Orderable rmation | 152         |

# 2 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Char | ges from Revision B (February, 2012) to Revision C                                                                                               | Page       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| •    | Added power-on information for USB_VBUS, USB_V <sub>DDA3P3</sub> , USB_V <sub>DDA1P3</sub> , and USB_V <sub>DD1P3</sub> (LitBug SDOCM00101620)   | <u>28</u>  |

| •    | Changed description for RSV6 to tie directly to $V_{ss}$ (LitBug SDOCM00101619)                                                                  |            |

| •    | Added note that CV <sub>DDRTC</sub> must always be powered by an external power source and cannot be powered by on-<br>chip LDOs (Bugzilla 2151) |            |

| •    | Changed WU_DOUT reset value to 1 (LitBug SDOCM00096670)                                                                                          | 58         |

| •    | Deleted unsupported EMIF pins (LitBug SDOCM00095615)                                                                                             | 68         |

| •    | Changed SYSCLK maximum to 50 (Bugzilla 2145)                                                                                                     | 76         |

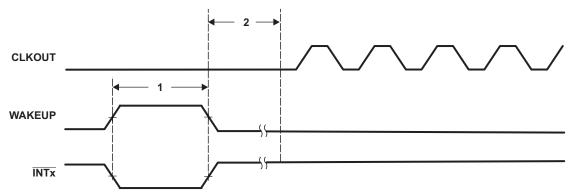

| •    | Changed minimum value for timing requirement for Wake-Up From IDLE (LitBug SDOCM00096476)                                                        | 82         |

| •    | Changed timing diagram for Wake-Up From IDLE (LitBug SDOCM00096480)                                                                              |            |

| •    | SDOCM00097368)                                                                                                                                   | 104<br>121 |

| •    | Added step to copy boot image sections to system memory (TIS Doc Feedback ID 5979)                                                               |            |

# 3 Device Comparison

Table 3-1 lists the important differences between the devices.

Table 3-1. Differences Between Devices

| Device         | Digital Core Supply<br>Voltage (CV <sub>DD</sub> ) |           | On-chip<br>DARAM | On-chip<br>SARAM | USB      | LCD<br>Interface | Tightly-<br>Coupled | SAR<br>ADC | LDO                  |

|----------------|----------------------------------------------------|-----------|------------------|------------------|----------|------------------|---------------------|------------|----------------------|

|                | 1.05 V                                             | 1.3 V     |                  |                  |          |                  | FFT                 |            |                      |

|                | Maximum                                            | CPU Speed |                  |                  |          |                  |                     |            |                      |

| TMS320C5535A05 | 50 MHz                                             | -         | CAICD            | OFCIAD           | √(1)     | <b>V</b>         | V                   | √          | ANA, DSP,            |

| TMS320C5535A10 | 50 MHz                                             | 100 MHz   | 64KB             | 256KB            | Ψ(,,     |                  |                     |            | and USB              |

| TMS320C5534A05 | 50 MHz                                             | -         | 64KB             | 192KB            | V        | _(2)             | -                   | -          | ANA, DSP,<br>and USB |

| TMS320C5534A10 | 50 MHz                                             | 100 MHz   | 04ND             |                  |          |                  |                     |            |                      |

| TMS320C5533A05 | 50 MHz                                             | -         | 64KB             | 0.41/5           | <b>V</b> | -                | -                   | -          | ANA and              |

| TMS320C5533A10 | 50 MHz                                             | 100 MHz   | 04ND             | 64KB             |          |                  |                     |            | USB                  |

| TMS320C5532A05 | 50 MHz                                             | -         | CAKD             | 0KB              |          | -                | -                   | -          | ANA only             |

| TMS320C5532A10 | 50 MHz                                             | 100 MHz   | 64KB             | UNB              | -        |                  |                     |            |                      |

<sup>(1)</sup>  $\sqrt{-}$  Supported

#### 3.1 Device Characteristics

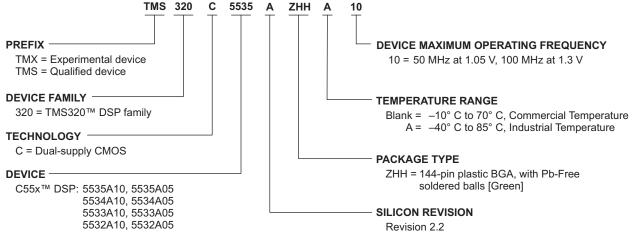

The following tables provide an overview of all the devices. The tables show significant features of each device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type with pin count. For more detailed information on the actual device part number and maximum device operating frequency, see Section 7.1.2, Device Nomenclature.

Table 3-2. Characteristics of the C5535 Processor

| НА                                                                                                    | RDWARE FEATURES                          | TMS320C5535A05, C5535A10                                                                                                                           |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Peripherals  Not all peripheral pins are available at the same time (for more detail, see Section 5). | DMA                                      | Four DMA controllers each with four channels, for a total of 16 channels                                                                           |  |  |  |  |

|                                                                                                       | Timers                                   | 2 32-Bit General-Purpose (GP) Timers 1 Additional Timer Configurable as a 32-Bit GP Timer or a Watchdog                                            |  |  |  |  |

|                                                                                                       | UART                                     | 1 (with RTS and CTS flow control)                                                                                                                  |  |  |  |  |

|                                                                                                       | SPI                                      | 1 with 4 chip selects                                                                                                                              |  |  |  |  |

|                                                                                                       | I <sup>2</sup> C                         | 1 (Master or Slave)                                                                                                                                |  |  |  |  |

|                                                                                                       | I <sup>2</sup> S                         | 4 (Two Channel, Full Duplex Communication)                                                                                                         |  |  |  |  |

|                                                                                                       | USB 2.0 (Device only)                    | High- and Full-Speed Device                                                                                                                        |  |  |  |  |

|                                                                                                       | SD                                       | 2 SD, 256-byte read and write buffer, max 50-MHz clock and signaling for DMA transfers                                                             |  |  |  |  |

|                                                                                                       | LCD Bridge                               | 1 (8-bit or 16-bit asynchronous parallel bus)                                                                                                      |  |  |  |  |

|                                                                                                       | ADC (Successive Approximation [SAR])     | 1 (10-bit, 4 -input, 16-µs conversion time)                                                                                                        |  |  |  |  |

|                                                                                                       | Real-Time Clock (RTC)                    | 1 (Crystal Input, Separate Clock Domain and Power Supply)                                                                                          |  |  |  |  |

|                                                                                                       | FFT Hardware Accelerator                 | 1 (Supports 8 to 1024-point 16-bit real and complex FFT)                                                                                           |  |  |  |  |

|                                                                                                       | General-Purpose Input/Output Port (GPIO) | 32 pins (with 1 Additional General-Purpose Output (XF) and 4<br>Special-Purpose Outputs for Use With SAR<br>Configure up to 20 pins simultaneously |  |  |  |  |

<sup>(2) - —</sup> Not supported

# Table 3-2. Characteristics of the C5535 Processor (continued)

| Н                             | ARDWARE FEATURES                                                          |                  | TMS320C5535A05, C5535A10                                                                                                                                    |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                               | Size (Bytes)                                                              |                  | 320 KB RAM, 128KB ROM                                                                                                                                       |  |  |  |  |

| On-Chip Memory                | Organization                                                              |                  | <ul> <li>64KB On-Chip Dual-Access RAM (DARAM)</li> <li>256KB On-Chip Single-Access RAM (SARAM)</li> <li>128 KB On-Chip Single-Access ROM (SAROM)</li> </ul> |  |  |  |  |

| JTAG BSDL_ID                  | JTAGID Register<br>(Value is: 0x1B8F E02l                                 | F)               | see Figure 6-5                                                                                                                                              |  |  |  |  |

| CPU Frequency                 | MHz                                                                       | 1.05-V Core      | 50 MHz                                                                                                                                                      |  |  |  |  |

|                               |                                                                           | 1.3-V Core       | 100 MHz (TMS320C5535A10 only)                                                                                                                               |  |  |  |  |

| Cycle Time                    | ns                                                                        | 1.05-V Core      | 20 ns                                                                                                                                                       |  |  |  |  |

|                               |                                                                           | 1.3-V Core       | 10 ns (TMS320C5535A10 only)                                                                                                                                 |  |  |  |  |

| Voltage                       | Core (V)                                                                  |                  | 1.05 V – 50 MHz                                                                                                                                             |  |  |  |  |

|                               |                                                                           |                  | 1.3 V – 100 MHz (TMS320C5535A10 only)                                                                                                                       |  |  |  |  |

|                               | I/O (V)                                                                   |                  | 1.8 V, 2.5 V, 2.75 V, 3.3 V                                                                                                                                 |  |  |  |  |

| LDOs                          | DSP_LDO                                                                   |                  | 1.3 V or 1.05 V, 250 mA max current for DSP CPU (CV <sub>DD</sub> )                                                                                         |  |  |  |  |

|                               | ANA_LDO                                                                   |                  | 1.3 V, 4 mA max current to supply power to PLL (V <sub>DDA_PLL</sub> ), SAR, and power management circuits (V <sub>DDA_ANA</sub> )                          |  |  |  |  |

|                               | USB_LDO                                                                   |                  | 1.3 V, 25 mA max current to supply power to USB core digital (USB_V <sub>DD1P3</sub> ) and PHY circuits (USB_V <sub>DDA1P3</sub> )                          |  |  |  |  |

| Power Characterization        | Active @ Room Temp<br>25% ADD                                             | 25°C, 75% DMAC + | 0.15 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                                                                |  |  |  |  |

|                               | Active @ Room Temp<br>25% NOP                                             | 25°C, 75% DMAC + | 0.14 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                                                                |  |  |  |  |

|                               | Standby (Master Clock<br>Temp 25°C (DARAM a<br>Mode)                      |                  | 0.26 mW @ 1.05 V<br>0.44 mW @ 1.3 V                                                                                                                         |  |  |  |  |

|                               | Standby (Master Clock<br>Temp 25°C (DARAM ir<br>SARAM in Active Mode      | n Retention and  | 0.23 mW @ 1.05 V<br>0.40 mW @ 1.3 V                                                                                                                         |  |  |  |  |

|                               | Standby (Master Clock<br>Temp 25°C (DARAM in<br>SARAM in Retention)       |                  | 0.15 mW @ 1.05 V<br>0.28 mW @ 1.3 V                                                                                                                         |  |  |  |  |

| PLL Options                   | Software Programmabl                                                      | e Multiplier     | x4 to x4099 multiplier                                                                                                                                      |  |  |  |  |

| BGA Package                   | 12 x 12 mm                                                                |                  | 144-Pin BGA (ZHH)                                                                                                                                           |  |  |  |  |

| Product Status <sup>(1)</sup> | Product Preview (PP),<br>Advance Information (A<br>or Production Data (PD |                  | PD                                                                                                                                                          |  |  |  |  |

<sup>(1)</sup> PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# Table 3-3. Characteristics of the C5534 Processor

| HA                                                                                       | RDWARE FEATURES                                                               |                 | TMS320C5534A05, C5534A10                                                                                                           |  |  |  |  |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Peripherals                                                                              |                                                                               |                 |                                                                                                                                    |  |  |  |  |

| Not all peripheral pins are available at the same time (for more detail, see Section 5). | DMA                                                                           |                 | Four DMA controllers each with four channels, for a total of 16 channels                                                           |  |  |  |  |

|                                                                                          | Timers                                                                        |                 | 2 32-Bit General-Purpose (GP) Timers 1 Additional Timer Configurable as a 32-Bit GP Timer or a Watchdog                            |  |  |  |  |

|                                                                                          | UART                                                                          |                 | 1 (with RTS and CTS flow control)                                                                                                  |  |  |  |  |

|                                                                                          | SPI                                                                           |                 | 1 with 4 chip selects                                                                                                              |  |  |  |  |

|                                                                                          | I <sup>2</sup> C                                                              |                 | 1 (Master or Slave)                                                                                                                |  |  |  |  |

|                                                                                          | I <sup>2</sup> S                                                              |                 | 4 (Two Channel, Full Duplex Communication)                                                                                         |  |  |  |  |

|                                                                                          | USB 2.0 (Device only)                                                         |                 | High- and Full-Speed Device                                                                                                        |  |  |  |  |

|                                                                                          | SD                                                                            |                 | 2 SD, 256-byte read and write buffer, max 50-MHz clock and signaling for DMA transfers                                             |  |  |  |  |

|                                                                                          | Real-Time Clock (RTC)                                                         |                 | 1 (Crystal Input, Separate Clock Domain and Power Supply)                                                                          |  |  |  |  |

|                                                                                          | General-Purpose Input/Out                                                     | put Port (GPIO) | Up to 20 pins (with 1 Additional General-Purpose Output (XF))                                                                      |  |  |  |  |

|                                                                                          | Size (Bytes)                                                                  |                 | 256KB RAM, 128KB ROM                                                                                                               |  |  |  |  |

| On-Chip Memory                                                                           |                                                                               |                 | 64KB On-Chip Dual-Access RAM (DARAM)                                                                                               |  |  |  |  |

| On-Only Wemory                                                                           | Organization                                                                  |                 | 192KB On-Chip Single-Access RAM (SARAM)                                                                                            |  |  |  |  |

|                                                                                          |                                                                               |                 | 128KB On-Chip Single-Access ROM (SAROM)                                                                                            |  |  |  |  |

| JTAG BSDL_ID                                                                             | JTAGID Register<br>(Value is: 0x1B8F E02F)                                    |                 | see Figure 6-5                                                                                                                     |  |  |  |  |

| CPU Frequency                                                                            | MHz                                                                           | 1.05-V Core     | 50 MHz                                                                                                                             |  |  |  |  |

| CFO Frequency                                                                            | IVII IZ                                                                       | 1.3-V Core      | 100 MHz (TMS320C5534A10 only)                                                                                                      |  |  |  |  |

| Cycle Time                                                                               | ns                                                                            | 1.05-V Core     | 20 ns                                                                                                                              |  |  |  |  |

| Cycle Time                                                                               | 115                                                                           | 1.3-V Core      | 10 ns (TMS320C5534A10 only)                                                                                                        |  |  |  |  |

|                                                                                          | Core (V)                                                                      |                 | 1.05 V – 50 MHz                                                                                                                    |  |  |  |  |

| Voltage                                                                                  | Cole (V)                                                                      |                 | 1.3 V - 100 MHz (TMS320C5534A10 only)                                                                                              |  |  |  |  |

|                                                                                          | I/O (V)                                                                       |                 | 1.8 V, 2.5 V, 2.75 V, 3.3 V                                                                                                        |  |  |  |  |

| LDOs                                                                                     | DSP_LDO                                                                       |                 | 1.3 V or 1.05 V, 250 mA max current for DSP CPU (CV <sub>DD</sub> )                                                                |  |  |  |  |

|                                                                                          | ANA_LDO                                                                       |                 | 1.3 V, 4 mA max current to supply power to PLL (V <sub>DDA_PLL</sub> ) and power management circuits (V <sub>DDA_ANA</sub> )       |  |  |  |  |

|                                                                                          | USB_LDO                                                                       |                 | 1.3 V, 25 mA max current to supply power to USB core digital (USB_V <sub>DD1P3</sub> ) and PHY circuits (USB_V <sub>DDA1P3</sub> ) |  |  |  |  |

| Power Characterization                                                                   | Active @ Room Temp 25°0<br>25% ADD                                            | C, 75% DMAC +   | 0.15 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                                       |  |  |  |  |

|                                                                                          | Active @ Room Temp 25°0 25% NOP                                               | C, 75% DMAC +   | 0.14 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                                       |  |  |  |  |

|                                                                                          | Standby (Master Clock Dis.<br>Temp 25°C (DARAM and S<br>Mode)                 |                 | 0.26 mW @ 1.05 V<br>0.44 mW @ 1.3 V                                                                                                |  |  |  |  |

|                                                                                          | Standby (Master Clock Dis.<br>Temp 25°C (DARAM in Re<br>SARAM in Active Mode) |                 | 0.23 mW @ 1.05 V<br>0.40 mW @ 1.3 V                                                                                                |  |  |  |  |

|                                                                                          | Standby (Master Clock Dis.<br>Temp 25°C (DARAM in Act<br>SARAM in Retention)  | ,               | 0.15 mW @ 1.05 V<br>0.28 mW @ 1.3 V                                                                                                |  |  |  |  |

| PLL Options                                                                              | Software Programmable M                                                       | ultiplier       | x4 to x4099 multiplier                                                                                                             |  |  |  |  |

| BGA Package                                                                              | 12 x 12 mm                                                                    |                 | 144-Pin BGA (ZHH)                                                                                                                  |  |  |  |  |

# Table 3-3. Characteristics of the C5534 Processor (continued)

| H                             | ARDWARE FEATURES                                                              | TMS320C5534A05, C5534A10 |  |  |  |  |

|-------------------------------|-------------------------------------------------------------------------------|--------------------------|--|--|--|--|

| Product Status <sup>(1)</sup> | Product Preview (PP),<br>Advance Information (AI),<br>or Production Data (PD) | PD                       |  |  |  |  |

(1) PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### Table 3-4. Characteristics of the C5533 Processor

| HA                                                                                       | ARDWARE FEATURES                                                               | TMS320C5533A05, C5533A10            |                                                                                                                                  |  |  |  |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Peripherals                                                                              |                                                                                |                                     |                                                                                                                                  |  |  |  |

| Not all peripheral pins are available at the same time (for more detail, see Section 5). | DMA                                                                            |                                     | Four DMA controllers each with four channels, for a total of 16 channels                                                         |  |  |  |

|                                                                                          | Timers                                                                         |                                     | 2 32-Bit General-Purpose (GP) Timers<br>1 Additional Timer Configurable as a 32-Bit GP Timer or a<br>Watchdog                    |  |  |  |

|                                                                                          | UART                                                                           |                                     | 1 (with RTS and CTS flow control)                                                                                                |  |  |  |

|                                                                                          | SPI                                                                            |                                     | 1 with 4 chip selects                                                                                                            |  |  |  |

|                                                                                          | I <sup>2</sup> C                                                               |                                     | 1 (Master or Slave)                                                                                                              |  |  |  |

|                                                                                          | I <sup>2</sup> S                                                               |                                     | 4 (Two Channel, Full Duplex Communication)                                                                                       |  |  |  |

|                                                                                          | USB 2.0 (Device only)                                                          |                                     | High- and Full-Speed Device                                                                                                      |  |  |  |

|                                                                                          | SD                                                                             |                                     | 2 SD, 256-byte read and write buffer, max 50-MHz clock and signaling for DMA transfers                                           |  |  |  |

|                                                                                          | Real-Time Clock (RTC)                                                          |                                     | 1 (Crystal Input, Separate Clock Domain and Power Supply)                                                                        |  |  |  |

|                                                                                          | General-Purpose Input/Out                                                      | put Port (GPIO)                     | Up to 20 pins (with 1 Additional General-Purpose Output (XF))                                                                    |  |  |  |

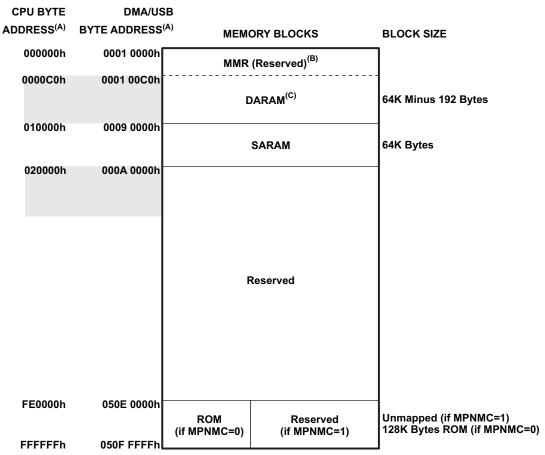

|                                                                                          | Size (Bytes)                                                                   |                                     | 128 KB RAM, 128KB ROM                                                                                                            |  |  |  |

| On Chin Momony                                                                           |                                                                                |                                     | 64 KB On-Chip Dual-Access RAM (DARAM)                                                                                            |  |  |  |

| On-Chip Memory                                                                           | Organization                                                                   |                                     | 64 KB On-Chip Single-Access RAM (SARAM)                                                                                          |  |  |  |

|                                                                                          |                                                                                |                                     | 128 KB On-Chip Single-Access ROM (SAROM)                                                                                         |  |  |  |

| JTAG BSDL_ID                                                                             | JTAGID Register<br>(Value is: 0x1B8F E02F)                                     |                                     | see Figure 6-5                                                                                                                   |  |  |  |

| CPU Frequency                                                                            | MHz                                                                            | 1.05-V Core                         | 50 MHz                                                                                                                           |  |  |  |

| Of O f requericy                                                                         | IVII IZ                                                                        | 1.3-V Core                          | 100 MHz (TMS320C5533A10 only)                                                                                                    |  |  |  |

| Cycle Time                                                                               | ns                                                                             | 1.05-V Core                         | 20 ns                                                                                                                            |  |  |  |

| Cycle Time                                                                               | 113                                                                            | 1.3-V Core                          | 10 ns (TMS320C5533A10 only)                                                                                                      |  |  |  |

|                                                                                          | Core (V)                                                                       |                                     | 1.05 V – 50 MHz                                                                                                                  |  |  |  |

| Voltage                                                                                  | Core (v)                                                                       |                                     | 1.3 V - 100 MHz (TMS320C5533A10 only)                                                                                            |  |  |  |

|                                                                                          | I/O (V)                                                                        |                                     | 1.8 V, 2.5 V, 2.75 V, 3.3 V                                                                                                      |  |  |  |

| LDOs                                                                                     | ANA_LDO                                                                        |                                     | 1.3 V, 4 mA max current to supply power to PLL (V <sub>DDA_PLL</sub> ) and power management circuits (V <sub>DDA_ANA</sub> )     |  |  |  |

|                                                                                          | USB_LDO                                                                        |                                     | 1.3 V, 25 mA max current to supply power to USB core digit (USB_V <sub>DD1P3</sub> ) and PHY circuits (USB_V <sub>DDA1P3</sub> ) |  |  |  |

| Power Characterization                                                                   | Active @ Room Temp 25°C 25% ADD                                                | C, 75% DMAC +                       | 0.15 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                                     |  |  |  |

|                                                                                          | Active @ Room Temp 25°C 25% NOP                                                | C, 75% DMAC +                       | 0.14 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                                     |  |  |  |

|                                                                                          | Standby (Master Clock Disa<br>Temp 25°C (DARAM and S<br>Mode)                  |                                     | 0.26 mW @ 1.05 V<br>0.44 mW @ 1.3 V                                                                                              |  |  |  |

|                                                                                          | Standby (Master Clock Disa<br>Temp 25°C (DARAM in Ret<br>SARAM in Active Mode) |                                     | 0.23 mW @ 1.05 V<br>0.40 mW @ 1.3 V                                                                                              |  |  |  |

|                                                                                          | Standby (Master Clock Disa<br>Temp 25°C (DARAM in Act<br>SARAM in Retention)   | 0.15 mW @ 1.05 V<br>0.28 mW @ 1.3 V |                                                                                                                                  |  |  |  |

| PLL Options                                                                              | Software Programmable Mu                                                       | ultiplier                           | x4 to x4099 multiplier                                                                                                           |  |  |  |

| BGA Package                                                                              | 12 x 12 mm                                                                     |                                     | 144-Pin BGA (ZHH)                                                                                                                |  |  |  |

| Product Status <sup>(1)</sup>                                                            | Product Preview (PP),<br>Advance Information (AI),<br>or Production Data (PD)  |                                     | PD                                                                                                                               |  |  |  |

<sup>(1)</sup> PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### Table 3-5. Characteristics of the C5532 Processor

| HA                                                                                       | RDWARE FEATURES                                                               |                 | TMS320C5532A05, C5532A10                                                                                      |  |  |  |  |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Peripherals                                                                              |                                                                               |                 |                                                                                                               |  |  |  |  |

| Not all peripheral pins are available at the same time (for more detail, see Section 5). | DMA                                                                           |                 | Four DMA controllers each with four channels, for a total of 16 channels                                      |  |  |  |  |

|                                                                                          | Timers                                                                        |                 | 2 32-Bit General-Purpose (GP) Timers<br>1 Additional Timer Configurable as a 32-Bit GP Timer or a<br>Watchdog |  |  |  |  |

|                                                                                          | UART                                                                          |                 | 1 (with RTS and CTS flow control)                                                                             |  |  |  |  |

|                                                                                          | SPI                                                                           |                 | 1 with 4 chip selects                                                                                         |  |  |  |  |

|                                                                                          | I <sup>2</sup> C                                                              |                 | 1 (Master or Slave)                                                                                           |  |  |  |  |

|                                                                                          | I <sup>2</sup> S                                                              |                 | 4 (Two Channel, Full Duplex Communication)                                                                    |  |  |  |  |

|                                                                                          | SD                                                                            |                 | 2 SD, 256-byte read and write buffer, max 50-MHz clock and signaling for DMA transfers                        |  |  |  |  |

|                                                                                          | Real-Time Clock (RTC)                                                         |                 | 1 (Crystal Input, Separate Clock Domain and Power Supply)                                                     |  |  |  |  |

|                                                                                          | General-Purpose Input/Out                                                     | put Port (GPIO) | Up to 20 pins (with 1 Additional General-Purpose Output (XF))                                                 |  |  |  |  |

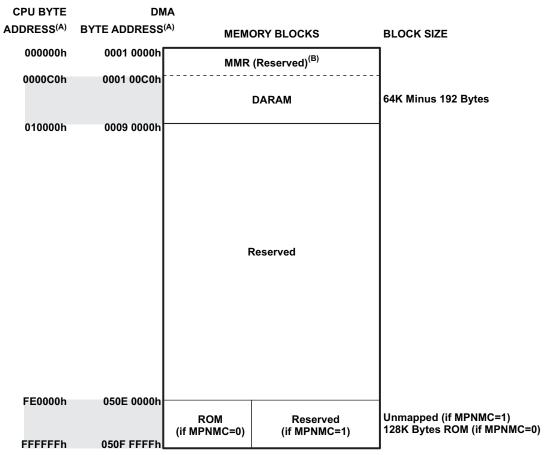

|                                                                                          | Size (Bytes)                                                                  |                 | 64KB RAM, 128KB ROM                                                                                           |  |  |  |  |

| On-Chip Memory                                                                           | Organization                                                                  |                 | <ul><li>64KB On-Chip Dual-Access RAM (DARAM)</li><li>128KB On-Chip Single-Access ROM (SAROM)</li></ul>        |  |  |  |  |

| JTAG BSDL_ID                                                                             | JTAGID Register<br>(Value is: 0x1B8F E02F)                                    |                 | see Figure 6-5                                                                                                |  |  |  |  |

| CDI I Fragues av                                                                         | NALL-                                                                         | 1.05-V Core     | 50 MHz                                                                                                        |  |  |  |  |

| CPU Frequency                                                                            | MHz                                                                           | 1.3-V Core      | 100 MHz (TMS320C5532A10 only)                                                                                 |  |  |  |  |

| Cycle Time                                                                               | 200                                                                           | 1.05-V Core     | 20 ns                                                                                                         |  |  |  |  |

| Cycle Time                                                                               | ns                                                                            | 1.3-V Core      | 10 ns (TMS320C5532A10 only)                                                                                   |  |  |  |  |

|                                                                                          | Core (V)                                                                      |                 | 1.05 V – 50 MHz                                                                                               |  |  |  |  |

| Voltage                                                                                  | Cole (V)                                                                      |                 | 1.3 V – 100 MHz (TMS320C5532A10 only)                                                                         |  |  |  |  |

|                                                                                          | I/O (V)                                                                       |                 | 1.8 V, 2.5 V, 2.75 V, 3.3 V                                                                                   |  |  |  |  |

| LDO                                                                                      | ANA_LDO                                                                       |                 | 1.3 V, 4 mA max current for PLL (V <sub>DDA_PLL</sub> ) power management circuits (V <sub>DDA_ANA</sub> )     |  |  |  |  |

| Power Characterization                                                                   | Active @ Room Temp 25°0 25% ADD                                               | C, 75% DMAC +   | 0.15 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                  |  |  |  |  |

|                                                                                          | Active @ Room Temp 25°0 25% NOP                                               | C, 75% DMAC +   | 0.14 mW/MHz @ 1.05 V, 50 MHz<br>0.22 mW/MHz @ 1.3 V, 100 MHz                                                  |  |  |  |  |

|                                                                                          | Standby (Master Clock Dis<br>Temp 25°C (DARAM and S<br>Mode)                  |                 | 0.26 mW @ 1.05 V<br>0.44 mW @ 1.3 V                                                                           |  |  |  |  |

|                                                                                          | Standby (Master Clock Dis<br>Temp 25°C (DARAM in Re<br>SARAM in Active Mode)  | ,               | 0.23 mW @ 1.05 V<br>0.40 mW @ 1.3 V                                                                           |  |  |  |  |

|                                                                                          | Standby (Master Clock Dis<br>Temp 25°C (DARAM in Ac<br>SARAM in Retention)    |                 | 0.15 mW @ 1.05 V<br>0.28 mW @ 1.3 V                                                                           |  |  |  |  |

| PLL Options                                                                              | Software Programmable M                                                       | ultiplier       | x4 to x4099 multiplier                                                                                        |  |  |  |  |

| BGA Package                                                                              | 12 x 12 mm                                                                    |                 | 144-Pin BGA (ZHH)                                                                                             |  |  |  |  |

| Product Status <sup>(1)</sup>                                                            | Product Preview (PP),<br>Advance Information (AI),<br>or Production Data (PD) |                 | PD                                                                                                            |  |  |  |  |

<sup>(1)</sup> PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### www.ti.com.cn

# 4 Terminal Configuration and Functions

# 4.1 Pin Diagram

The following figures show the bottom view of the package pin assignments.

| Р | V <sub>SS</sub>              | LCD_D[4]/<br>GP[14]        | LCD_D[6]/<br>GP[16]        | TRST                | LCD_D[8]/<br>I2S2_CLK/<br>GP[18]/<br>SPI_CLK | SD0_D1/<br>I2S0_RX/<br>GP[3] | SD0_D3/<br>GP[5]     | LCD_D[7]/<br>GP[17]            | LCD_D[10]/<br>I2S2_RX/<br>GP[20]/<br>SPI_RX | SD1_D1/<br>I2S1_RX/<br>GP[9]                | LCD_D[11]/<br>I2S2_DX/<br>GP[27]/<br>SPI_TX   | LCD_D[13]/<br>UART_CTS/<br>GP[29]/<br>I2S3_FS  | LCD_D[14]/<br>UART_RXD/<br>GP[30]/<br>I2S3_RX | V <sub>SS</sub>                |

|---|------------------------------|----------------------------|----------------------------|---------------------|----------------------------------------------|------------------------------|----------------------|--------------------------------|---------------------------------------------|---------------------------------------------|-----------------------------------------------|------------------------------------------------|-----------------------------------------------|--------------------------------|

| N | TDO                          | LCD_RW_<br>WRB/SPI_<br>CS2 | тск                        | LCD_D[0]/<br>SPI_RX | LCD_D[3]/<br>GP[13]                          | TMS                          | LCD_D[5]/<br>GP[15]  | DV <sub>DDIO</sub>             | CV <sub>DD</sub>                            | LCD_D[9]/<br>I2S2_FS/<br>GP[19]/<br>SPI_CS0 | DV <sub>DDIO</sub>                            | LCD_D[12]/<br>UART_RTS/<br>GP[28]/<br>I2S3_CLK | SD0_D2/<br>GP[4]                              | DV <sub>DDIO</sub>             |

| М | EMU1                         | LCD_CS1_E1/<br>SPI_CS1     | DV <sub>DDIO</sub>         | DV <sub>DDIO</sub>  | LCD_RS/<br>SPI_CS3                           | CV <sub>DD</sub>             | V <sub>SS</sub>      | SD0_CLK/<br>I2S0_CLK/<br>GP[0] | CV <sub>DD</sub>                            | SD0_CMD/<br>I2S0_FS/<br>GP[1]               | LCD_D[15]/<br>UART_TXD/<br>GP[31]/<br>I2S3_DX | SD1_D3/<br>GP[11]                              | SD1_D0/<br>I2S1_DX/<br>GP[8]                  | SD1_CLK/<br>I2S1_CLK/<br>GP[6] |

| L | LCD_CS0_<br>E0/SPI_CS0       | EMU0                       | LCD_EN_<br>RDB/<br>SPI_CLK | DV <sub>DDIO</sub>  | V <sub>SS</sub>                              |                              |                      |                                |                                             | V <sub>SS</sub>                             | SD1_CMD/<br>I2S1_FS/<br>GP[7]                 | SD1_D2/<br>GP[10]                              | RSV2                                          | USB_VBUS                       |

| К | LCD_D[1]/<br>SPI_TX          | TDI                        | V <sub>SS</sub>            | V <sub>SS</sub>     |                                              |                              |                      |                                |                                             |                                             | CV <sub>DD</sub>                              | RSV1                                           | USB_V <sub>DD1P3</sub>                        | USB_V <sub>SS1P3</sub>         |

| J | SD0_D0/<br>I2S0_DX/<br>GP[2] | LCD_D[2]/<br>GP[12]        | XF                         |                     |                                              |                              |                      |                                |                                             |                                             |                                               | USB_V <sub>SSA1P3</sub>                        | V <sub>SS</sub>                               | USB_DM                         |

| Н | RSV10                        | CV <sub>DD</sub>           | V <sub>SS</sub>            |                     |                                              |                              |                      |                                |                                             |                                             |                                               | USB_<br>VDDA1P3                                | USB_VSSA3P3                                   | USB_DP                         |

| G | RSV9                         | RSV12                      | CV <sub>DD</sub>           |                     |                                              |                              |                      |                                |                                             |                                             |                                               | USB_VDDA3P3                                    | USB_V <sub>DDPLL</sub>                        | USB_R1                         |

| F | RSV8                         | CV <sub>DD</sub>           | V <sub>SS</sub>            |                     |                                              |                              |                      |                                |                                             |                                             |                                               | USB_V <sub>SSREF</sub>                         | USB_V <sub>SSPLL</sub>                        | USB_V <sub>DD1P3</sub>         |

| E | RSV7                         | RSV11                      | V <sub>SS</sub>            | V <sub>SS</sub>     |                                              |                              |                      |                                |                                             |                                             | V <sub>SS</sub>                               | USB_V <sub>DD1P3</sub>                         | USB_V <sub>DDOSC</sub>                        | USB_MXI                        |

| D | CLK_SEL                      | RESET                      | CV <sub>DD</sub>           | V <sub>SS</sub>     | V <sub>SS</sub>                              |                              |                      |                                |                                             | V <sub>SS</sub>                             | CV <sub>DD</sub>                              | USB_V <sub>SSOSC</sub>                         | USB_LDOO                                      | USB_MXO                        |

| С | CLKIN                        | INT0                       | DV <sub>DDRTC</sub>        | SCL                 | V <sub>SSRTC</sub>                           | DV <sub>DDIO</sub>           | V <sub>DDA_PLL</sub> | V <sub>SS</sub>                | V <sub>SSA_ANA</sub>                        | BG_CAP                                      | CV <sub>DD</sub>                              | V <sub>SS</sub>                                | DSP_LDO_<br>EN                                | LDOI                           |

| В | ĪNT1                         | V <sub>SS</sub>            | V <sub>SS</sub>            | CV <sub>DDRTC</sub> | CV <sub>DDRTC</sub>                          | V <sub>SSA_ANA</sub>         | V <sub>DDA_ANA</sub> | GPAIN1                         | ANA_LDOO                                    | LDOI                                        | RSV5                                          | RSV3                                           | RSV6                                          | LDOI                           |

| Α | V <sub>SSA_PLL</sub>         | CLKOUT                     | RTC_CLKOUT                 | SDA                 | WAKEUP                                       | RTC_XO                       | RTC_XI               | GPAIN0                         | GPAIN2                                      | GPAIN3                                      | RSV4                                          | RSV0                                           | DSP_LDOO                                      | V <sub>SS</sub>                |

| , | 1                            | 2                          | 3                          | 4                   | 5                                            | 6                            | 7                    | 8                              | 9                                           | 10                                          | 11                                            | 12                                             | 13                                            | 14                             |

Figure 4-1. C5535 Pin Diagram

www.ti.com.cn

| Р | V <sub>SS</sub>              | GP[14]           | GP[16]              | TRST                | I2S2_CLK/<br>GP[18]/<br>SPI_CLK | SD0_D1/<br>I2S0_RX/<br>GP[3] | SD0_D3/<br>GP[5]     | GP[17]                         | I2S2_RX/<br>GP[20]/<br>SPI_RX | SD1_D1/<br>I2S1_RX/<br>GP[9]   | I2S2_DX/<br>GP[27]/<br>SPI_TX   | UART_CTS/<br>GP[29]/<br>I2S3_FS  | UART_RXD/<br>GP[30]/<br>I2S3_RX | V <sub>SS</sub>                |

|---|------------------------------|------------------|---------------------|---------------------|---------------------------------|------------------------------|----------------------|--------------------------------|-------------------------------|--------------------------------|---------------------------------|----------------------------------|---------------------------------|--------------------------------|

| N | TDO                          | SPI_CS2          | тск                 | SPI_RX              | GP[13]                          | TMS                          | GP[15]               | DV <sub>DDIO</sub>             | CV <sub>DD</sub>              | I2S2_FS/<br>GP[19]/<br>SPI_CS0 | DV <sub>DDIO</sub>              | UART_RTS/<br>GP[28]/<br>I2S3_CLK | SD0_D2/<br>GP[4]                | DV <sub>DDIO</sub>             |

| М | EMU1                         | SPI_CS1          | DV <sub>DDIO</sub>  | DV <sub>DDIO</sub>  | SPI_CS3                         | CV <sub>DD</sub>             | V <sub>SS</sub>      | SD0_CLK/<br>I2S0_CLK/<br>GP[0] | CV <sub>DD</sub>              | SD0_CMD/<br>I2S0_FS/<br>GP[1]  | UART_TXD/<br>GP[31]/<br>I2S3_DX | SD1_D3/<br>GP[11]                | SD1_D0/<br>I2S1_DX/<br>GP[8]    | SD1_CLK/<br>I2S1_CLK/<br>GP[6] |

| L | SPI_CS0                      | EMU0             | SPI_CLK             | DV <sub>DDIO</sub>  | V <sub>SS</sub>                 |                              |                      |                                |                               | V <sub>SS</sub>                | SD1_CMD/<br>I2S1_FS/<br>GP[7]   | SD1_D2/<br>GP[10]                | RSV2                            | USB_VBUS                       |

| К | SPI_TX                       | TDI              | V <sub>SS</sub>     | V <sub>SS</sub>     |                                 |                              |                      |                                |                               |                                | CV <sub>DD</sub>                | RSV1                             | USB_V <sub>DD1P3</sub>          | USB_V <sub>SS1P3</sub>         |

| J | SD0_D0/<br>I2S0_DX/<br>GP[2] | GP[12]           | XF                  |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_V <sub>SSA1P3</sub>          | V <sub>SS</sub>                 | USB_DM                         |

| Н | RSV10                        | CV <sub>DD</sub> | V <sub>SS</sub>     |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_<br>VDDA1P3                  | USB_VSSA3P3                     | USB_DP                         |

| G | RSV9                         | RSV12            | CV <sub>DD</sub>    |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_VDDA3P3                      | USB_V <sub>DDPLL</sub>          | USB_R1                         |

| F | RSV8                         | CV <sub>DD</sub> | V <sub>SS</sub>     |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_V <sub>SSREF</sub>           | USB_V <sub>SSPLL</sub>          | USB_V <sub>DD1P3</sub>         |

| E | RSV7                         | RSV11            | V <sub>SS</sub>     | V <sub>SS</sub>     |                                 |                              |                      |                                |                               |                                | V <sub>SS</sub>                 | USB_V <sub>DD1P3</sub>           | USB_V <sub>DDOSC</sub>          | USB_MXI                        |

| D | CLK_SEL                      | RESET            | CV <sub>DD</sub>    | V <sub>SS</sub>     | V <sub>SS</sub>                 |                              |                      |                                |                               | V <sub>SS</sub>                | CV <sub>DD</sub>                | USB_V <sub>SSOSC</sub>           | USB_LDOO                        | USB_MXO                        |

| С | CLKIN                        | INTO             | DV <sub>DDRTC</sub> | SCL                 | V <sub>SSRTC</sub>              | DV <sub>DDIO</sub>           | V <sub>DDA_PLL</sub> | V <sub>SS</sub>                | V <sub>SSA_ANA</sub>          | BG_CAP                         | CV <sub>DD</sub>                | V <sub>SS</sub>                  | DSP_LDO_<br>EN                  | LDOI                           |

| В | ĪNT1                         | V <sub>SS</sub>  | V <sub>SS</sub>     | CV <sub>DDRTC</sub> | CV <sub>DDRTC</sub>             | V <sub>SSA_ANA</sub>         | V <sub>DDA_ANA</sub> | NC                             | ANA_LDOO                      | LDOI                           | RSV5                            | RSV3                             | RSV6                            | LDOI                           |

| Α | V <sub>SSA_PLL</sub>         | CLKOUT           | RTC_CLKOUT          | SDA                 | WAKEUP                          | RTC_XO                       | RTC_XI               | NC                             | NC                            | NC                             | RSV4                            | RSV0                             | DSP_LDOO                        | V <sub>SS</sub>                |

|   | 1                            | 2                | 3                   | 4                   | 5                               | 6                            | 7                    | 8                              | 9                             | 10                             | 11                              | 12                               | 13                              | 14                             |

Figure 4-2. C5534 Pin Diagram

| Р | V <sub>SS</sub>              | GP[14]           | GP[16]              | TRST                | I2S2_CLK/<br>GP[18]/<br>SPI_CLK | SD0_D1/<br>I2S0_RX/<br>GP[3] | SD0_D3/<br>GP[5]     | GP[17]                         | I2S2_RX/<br>GP[20]/<br>SPI_RX | SD1_D1/<br>I2S1_RX/<br>GP[9]   | I2S2_DX/<br>GP[27]/<br>SPI_TX   | UART_CTS/<br>GP[29]/<br>I2S3_FS  | UART_RXD/<br>GP[30]/<br>I2S3_RX | V <sub>SS</sub>                |

|---|------------------------------|------------------|---------------------|---------------------|---------------------------------|------------------------------|----------------------|--------------------------------|-------------------------------|--------------------------------|---------------------------------|----------------------------------|---------------------------------|--------------------------------|

| N | TDO                          | SPI_CS2          | тск                 | SPI_RX              | GP[13]                          | TMS                          | GP[15]               | DV <sub>DDIO</sub>             | CV <sub>DD</sub>              | I2S2_FS/<br>GP[19]/<br>SPI_CS0 | DV <sub>DDIO</sub>              | UART_RTS/<br>GP[28]/<br>I2S3_CLK | SD0_D2/<br>GP[4]                | DV <sub>DDIO</sub>             |

| М | EMU1                         | SPI_CS1          | DV <sub>DDIO</sub>  | DV <sub>DDIO</sub>  | SPI_CS3                         | CV <sub>DD</sub>             | V <sub>SS</sub>      | SD0_CLK/<br>I2S0_CLK/<br>GP[0] | CV <sub>DD</sub>              | SD0_CMD/<br>I2S0_FS/<br>GP[1]  | UART_TXD/<br>GP[31]/<br>I2S3_DX | SD1_D3/<br>GP[11]                | SD1_D0/<br>I2S1_DX/<br>GP[8]    | SD1_CLK/<br>I2S1_CLK/<br>GP[6] |

| L | SPI_CS0                      | EMU0             | SPI_CLK             | DV <sub>DDIO</sub>  | V <sub>SS</sub>                 |                              |                      |                                |                               | V <sub>SS</sub>                | SD1_CMD/<br>I2S1_FS/<br>GP[7]   | SD1_D2/<br>GP[10]                | RSV2                            | USB_VBUS                       |

| К | SPI_TX                       | TDI              | V <sub>SS</sub>     | V <sub>SS</sub>     |                                 |                              |                      |                                |                               |                                | CV <sub>DD</sub>                | RSV1                             | USB_V <sub>DD1P3</sub>          | USB_V <sub>SS1P3</sub>         |

| J | SD0_D0/<br>I2S0_DX/<br>GP[2] | GP[12]           | XF                  |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_V <sub>SSA1P3</sub>          | V <sub>SS</sub>                 | USB_DM                         |

| Н | RSV10                        | CV <sub>DD</sub> | V <sub>SS</sub>     |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_<br>VDDA1P3                  | USB_VSSA3P3                     | USB_DP                         |

| G | RSV9                         | RSV12            | CV <sub>DD</sub>    |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_VDDA3P3                      | USB_V <sub>DDPLL</sub>          | USB_R1                         |

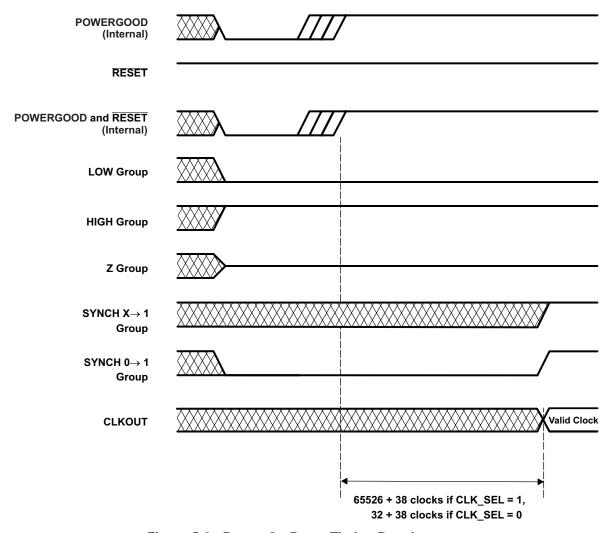

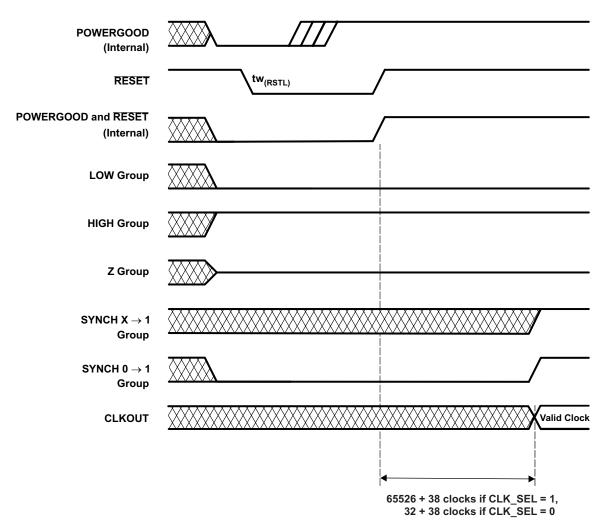

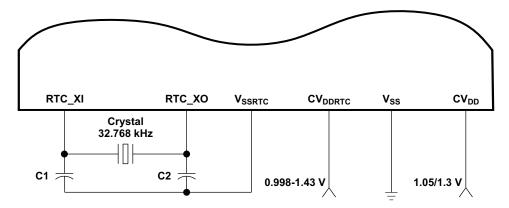

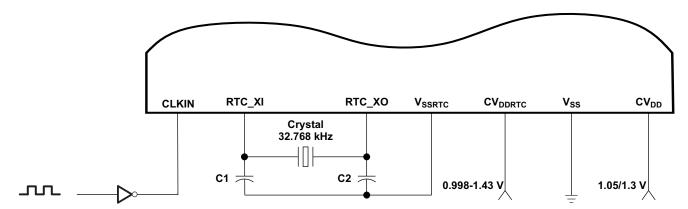

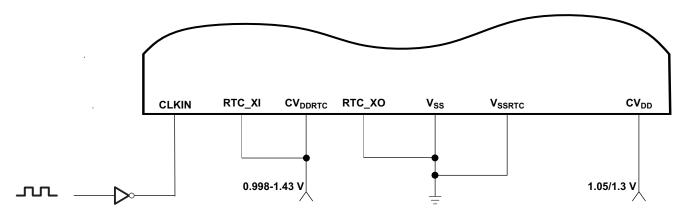

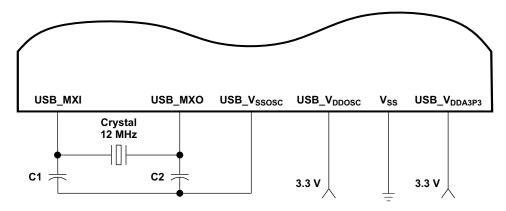

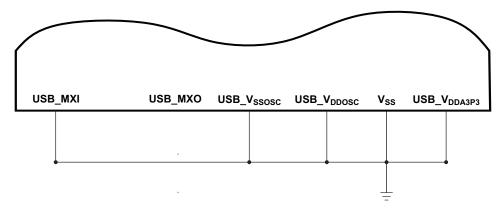

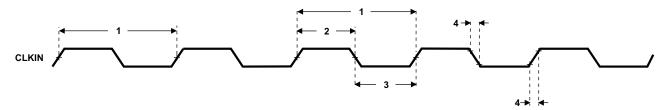

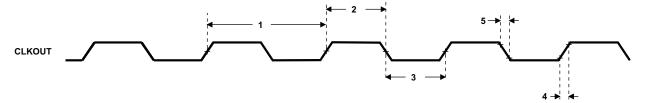

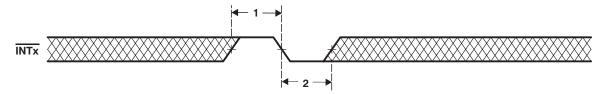

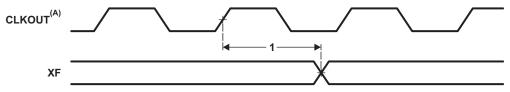

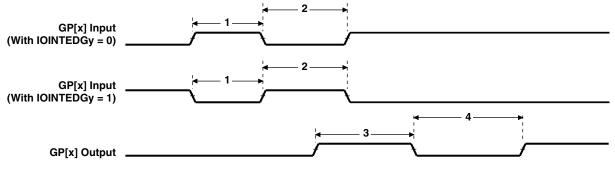

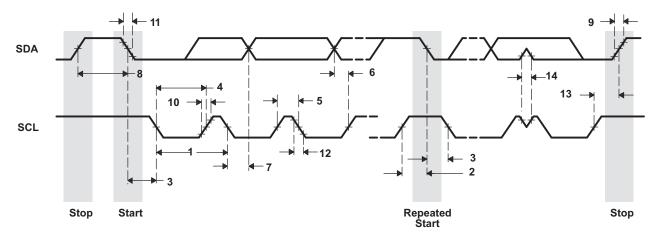

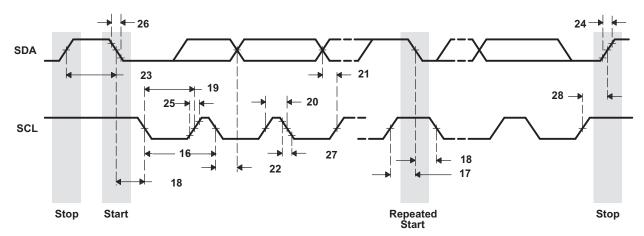

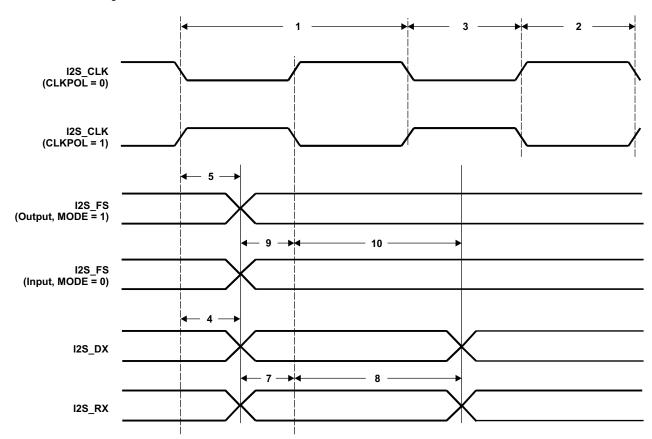

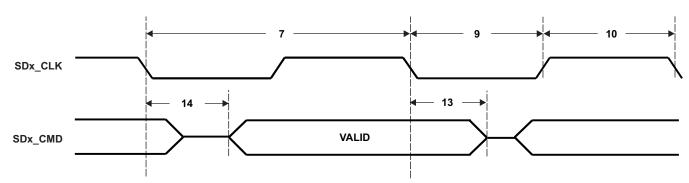

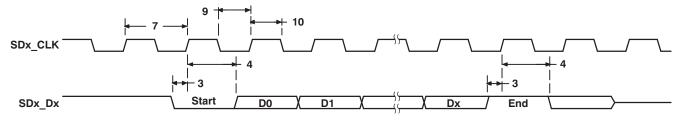

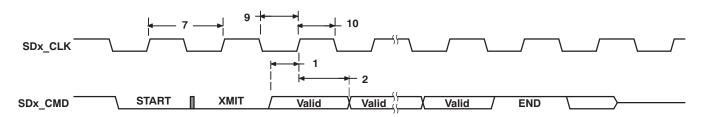

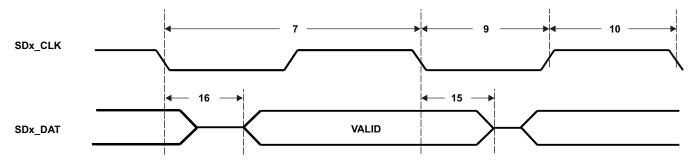

| F | RSV8                         | CV <sub>DD</sub> | V <sub>SS</sub>     |                     |                                 |                              |                      |                                |                               |                                |                                 | USB_V <sub>SSREF</sub>           | USB_V <sub>SSPLL</sub>          | USB_V <sub>DD1P3</sub>         |