TMUX6121, TMUX6122, TMUX6123 ZHCSJ87A - DECEMBER 2018 - REVISED JULY 2022

# TMUX612x ±16.5V、低电容、低漏电流、 精密双路 SPST 开关

# 1 特性

- 宽电源电压范围: ±5V 至 ±16.5V (双电源)或 10V 至 16.5V ( 单电源 )

- 所有引脚的闩锁性能都达到 100mA,符合 JESD78 II 类 A 级要求

- 低导通电容:4.2pF

- 低输入泄漏电流:0.5pA

- 低电荷注入: 0.51 pC

- 轨到轨运行

- 低导通电阻:120Ω

- 快速开关导通时间:68ns

- 先断后合开关 (TMUX6123)

- SELx 引脚可连接至带集成下拉电阻器的 Von

- 逻辑电平: 2V 至 V<sub>DD</sub>

- 低电源电流:16µA

- 人体放电模型 (HBM) ESD 保护:所有引脚上均为 ±2kV

- 业界通用的 VSSOP 封装 ٠

# 2 应用

- 工厂自动化和工业过程控制 •

- 可编程逻辑控制器 (PLC) ٠

- 模拟输入模块 ٠

- ATE 测试设备

- 数字万用表

- 电池监控系统

# 3 说明

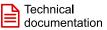

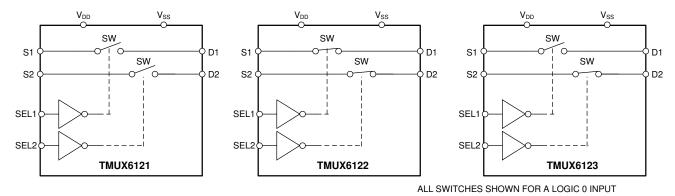

TMUX6121、TMUX6122 和 TMUX6123 是现代化的互 补金属氧化物半导体 (CMOS) 器件,具有两个独立的 可选单刀单掷 (SPST) 开关。该器件在双电源 (±5V 至 ±16.5V)、单电源(10V 至 16.5V)或非对称电源供 电时均能正常运行。所有数字输入均具有兼容晶体管到 晶体管逻辑 (TTL) 的阈值,这些阈值可确保 TTL 和 CMOS 逻辑兼容性。

逻辑 1 会打开 TMUX6121 中数字控制输入上的开关。 要打开 TMUX6122 中的开关,则需要逻辑 0。 TMUX6123 有一个开关的数字控制逻辑与 TMUX6121 类似,而另外一个开关上的逻辑则与之相反。 TMUX6123 具有先断后合开关,因此可用于交叉点开 关应用。

TMUX6121、TMUX6122、TMUX6123 是精密开关和 多路复用器器件系列的一部分。这些器件具有非常低的 漏电流和低电荷注入,因此可用于高精度测量应用。由 于具有 16µA 的低电源电流,因此这些器件可用于便携 式应用。

#### 器件信息<sup>(1)</sup>

| 器件型号     | 封装         | 封装尺寸(标称值)       |

|----------|------------|-----------------|

| TMUX6121 |            |                 |

| TMUX6122 | VSSOP (10) | 3.00mm × 3.00mm |

| TMUX6123 |            |                 |

(1)要了解所有可用封装,请参见数据表末尾的封装选项附录。

# **Table of Contents**

| 1 | 特性1                                                    |

|---|--------------------------------------------------------|

| 2 | 应用1                                                    |

| 3 | 说明1                                                    |

| 4 | Revision History2                                      |

| 5 | Pin Configuration and Functions                        |

| 6 | Specifications4                                        |

|   | 6.1 Absolute Maximum Ratings                           |

|   | 6.2 ESD Ratings 4                                      |

|   | 6.3 Thermal Information4                               |

|   | 6.4 Recommended Operating Conditions5                  |

|   | 6.5 Electrical Characteristics (Dual Supplies: ±15 V)5 |

|   | 6.6 Switching Characteristics (Dual Supplies: ±15 V)6  |

|   | 6.7 Electrical Characteristics (Single Supply: 12 V)6  |

|   | 6.8 Switching Characteristics (Single Supply: 12 V)7   |

| 7 | Parameter Measurement Information12                    |

|   | 7.1 Truth Tables                                       |

| 8 | Detailed Description13                                 |

|   | 8.1 Overview                                           |

|   | 8.2 Functional Block Diagram18                         |

| 8.3 Feature Description                 | 18              |

|-----------------------------------------|-----------------|

| 8.4 Device Functional Modes             |                 |

| 9 Application and Implementation        | 21              |

| 9.1 Application Information             | 21              |

| 9.2 Typical Application                 |                 |

| 10 Power Supply Recommendations         | <mark>23</mark> |

| 11 Layout                               | <mark>23</mark> |

| 11.1 Layout Guidelines                  |                 |

| 11.2 Layout Example                     |                 |

| 12 Device and Documentation Support     |                 |

| 12.1 Documentation Support              | 24              |

| 12.2 接收文档更新通知                           |                 |

| 12.3 支持资源                               |                 |

| 12.4 Trademarks                         |                 |

| 12.5 Electrostatic Discharge Caution    |                 |

| 12.6 术语表                                |                 |

| 13 Mechanical, Packaging, and Orderable |                 |

| Information                             |                 |

|                                         |                 |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| Cł | nanges from Revision * (D | ecember 2018) to Revision A (July 2022) | Page |

|----|---------------------------|-----------------------------------------|------|

| •  | 更新了整个文档中的表格、              | 图和交叉参考的编号格式                             | 1    |

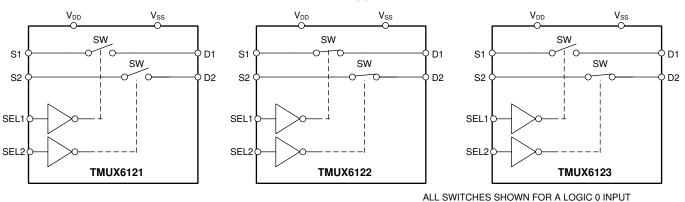

# **5** Pin Configuration and Functions

### 图 5-1. DGS Package, 10-Pin VSSOP (Top View)

### 表 5-1. Pin Functions

| PIN             |     | <b>TYPE</b> <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                     |  |

|-----------------|-----|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | NO. |                            | DESCRIPTION                                                                                                                                                                                                                                                                     |  |

| SEL1            | 1   | I                          | Logic control input 1.                                                                                                                                                                                                                                                          |  |

| S1              | 2   | I/O                        | Source pin 1. Can be an input or output.                                                                                                                                                                                                                                        |  |

| D1              | 3   | I/O                        | Drain pin 1. Can be an input or output.                                                                                                                                                                                                                                         |  |

| D2              | 4   | I/O                        | Drain pin 2. Can be an input or output.                                                                                                                                                                                                                                         |  |

| S2              | 5   | I/O                        | Source pin 2. Can be an input or output.                                                                                                                                                                                                                                        |  |

| V <sub>SS</sub> | 6   | Р                          | Negative power supply. This pin is the most negative power-supply potential. In single-supply applications, this pin can be connected to ground. For reliable operation, connect a decoupling capacitor ranging from 0.1 $\mu$ F to 10 $\mu$ F between V <sub>SS</sub> and GND. |  |

| NC              | 7   | No Connect                 | No internal connection.                                                                                                                                                                                                                                                         |  |

| GND             | 8   | Р                          | Ground (0 V) reference.                                                                                                                                                                                                                                                         |  |

| V <sub>DD</sub> | 9   | Р                          | Positive power supply. This pin is the most positive power-supply potential. For reliable operation, connect a decoupling capacitor ranging from 0.1 $\mu$ F to 10 $\mu$ F between V <sub>DD</sub> and GND.                                                                     |  |

| SEL2            | 10  | I                          | Logic control input 2.                                                                                                                                                                                                                                                          |  |

(1) I = input, O = output, P = power

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                    |                                        | MIN                   | MAX                  | UNIT |

|------------------------------------|----------------------------------------|-----------------------|----------------------|------|

| $V_{\text{DD}}$ to $V_{\text{SS}}$ |                                        |                       | 36                   | V    |

| V <sub>DD</sub> to GND             | Supply voltage                         | - 0.3                 | 18                   | V    |

| V <sub>SS</sub> to GND             |                                        | - 18                  | 0.3                  | V    |

| V <sub>DIG</sub>                   | Digital input pin (SEL1, SEL2) voltage | GND - 0.3             | V <sub>DD</sub> +0.3 | V    |

| I <sub>DIG</sub>                   | Digital input pin (SEL1, SEL2) current | - 30                  | 30                   | mA   |

| V <sub>ANA_IN</sub>                | Analog input pin (Sx) voltage          | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> +0.3 | V    |

| I <sub>ANA_IN</sub>                | Analog input pin (Sx) current          | - 30                  | 30                   | mA   |

| V <sub>ANA_OUT</sub>               | Analog output pin (Dx) voltage         | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> +0.3 | V    |

| I <sub>ANA_OUT</sub>               | Analog output pin (Dx) current         | - 30                  | 30                   | mA   |

| T <sub>A</sub>                     | Ambient temperature                    | - 55                  | 140                  | °C   |

| TJ                                 | Junction temperature                   |                       | 150                  | °C   |

| T <sub>stg</sub>                   | Storage temperature                    | - 65                  | 150                  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

| N                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>          | ±2000 | M    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Thermal Information

|                        |                                              | TMUX6121/ TMUX6122/<br>TMUX6123 |      |

|------------------------|----------------------------------------------|---------------------------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP)                     | UNIT |

|                        |                                              | 10 PINS                         |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 180.7                           | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 66.2                            | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 103.2                           | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 11.2                            | °C/W |

| Ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 101.3                           | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | N/A                             | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                     |                                                                | MIN             | NOM MAX         | UNIT |

|-------------------------------------|----------------------------------------------------------------|-----------------|-----------------|------|

| $V_{DD}$ to $V_{SS}$ <sup>(1)</sup> | Power supply voltage differential                              | 10              | 33              | V    |

| V <sub>DD</sub> to GND              | Positive power supply voltage (singlle supply, $V_{SS}$ = 0 V) | 10              | 16.5            | V    |

| V <sub>DD</sub> to GND              | Positive power supply voltage (dual supply)                    | 5               | 16.5            | V    |

| V <sub>SS</sub> to GND              | Negative power supply voltage (dual supply)                    | - 16.5          | - 5             | V    |

| V <sub>S</sub>                      | Source pins voltage <sup>(2)</sup>                             | V <sub>SS</sub> | V <sub>DD</sub> | V    |

| V <sub>D</sub>                      | Drain pin voltage                                              | V <sub>SS</sub> | V <sub>DD</sub> | V    |

| V <sub>SEL</sub>                    | Select pin (SEL1, SEL2) voltage                                | V <sub>SS</sub> | V <sub>DD</sub> | V    |

| I <sub>CH</sub>                     | Channel current ( $T_A = 25^{\circ}C$ )                        | - 25            | 25              | mA   |

| T <sub>A</sub>                      | Ambient temperature                                            | - 40            | 125             | °C   |

# 6.5 Electrical Characteristics (Dual Supplies: ±15 V)

at T<sub>A</sub> = 25°C, V<sub>DD</sub> = 15 V, and V<sub>SS</sub> = -15 V (unless otherwise noted)

|                       | PARAMETER                                  | TEST CO                                                                                    | NDITIONS                                         | MIN             | TYP   | MAX      | UNIT |

|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-------|----------|------|

| ANALOG S              | SWITCH                                     |                                                                                            |                                                  | -1              |       |          |      |

| V <sub>A</sub>        | Analog signal range                        | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                             | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$   | V <sub>SS</sub> |       | $V_{DD}$ | V    |

|                       |                                            | V <sub>S</sub> = 0 V, I <sub>S</sub> = 1 mA                                                |                                                  |                 | 120   | 135      | Ω    |

| _                     |                                            |                                                                                            |                                                  |                 | 140   | 165      | Ω    |

| R <sub>ON</sub>       | On-resistance                              | V <sub>S</sub> = ±10 V, I <sub>S</sub> = 1 mA                                              | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$  |                 |       | 210      | Ω    |

|                       |                                            |                                                                                            | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |                 |       | 245      | Ω    |

|                       |                                            |                                                                                            |                                                  |                 | 2.4   | 6        | Ω    |

| $\Delta R_{ON}$       | On-resistance mismatch<br>between channels | V <sub>S</sub> = ±10 V, I <sub>S</sub> = 1 mA                                              | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$  |                 |       | 9        | Ω    |

|                       | between channels                           |                                                                                            | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |                 |       | 11       | Ω    |

|                       |                                            |                                                                                            |                                                  |                 | 22    | 45       | Ω    |

| R <sub>ON_FLAT</sub>  | On-resistance flatness                     | V <sub>S</sub> = - 10 V, 0 V, +10 V, I <sub>S</sub><br>= 1 mA                              | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$  |                 |       | 47       | Ω    |

| _                     |                                            |                                                                                            | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |                 |       | 49       | Ω    |

| R <sub>ON_DRIFT</sub> | On-resistance drift                        | V <sub>S</sub> = 0 V                                                                       |                                                  |                 | 0.5   |          | %/°C |

|                       |                                            | Switch state is off, V <sub>S</sub> =<br>+10 V/ - 10 V, V <sub>D</sub> = - 10<br>V/ + 10 V |                                                  | - 0.02          | 0.005 | 0.02     | nA   |

| I <sub>S(OFF)</sub>   | Source off leakage current <sup>(1)</sup>  |                                                                                            | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$  | - 0.12          |       | 0.05     | nA   |

|                       |                                            |                                                                                            | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ | - 1             |       | 0.2      | nA   |

|                       |                                            | Switch state is off, V <sub>S</sub> =                                                      |                                                  | - 0.02          | 0.005 | 0.02     | nA   |

| I <sub>D(OFF)</sub>   | Drain off leakage current <sup>(1)</sup>   | +10 V/ - 10 V, $V_D = -10$                                                                 | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$  | - 0.12          |       | 0.05     | nA   |

| (- )                  |                                            | V/ +10 V                                                                                   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$   | - 1             |       | 0.2      | nA   |

|                       |                                            | Switch state is an M -                                                                     |                                                  | - 0.04          | 0.01  | 0.04     | nA   |

| I <sub>D(ON)</sub>    | Drain on leakage current                   | Switch state is on, $V_S$ = +10 V/ - 10 V, $V_D$ = - 10                                    | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$  | - 0.25          |       | 0.1      | nA   |

| -()                   |                                            | V/ +10 V                                                                                   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$   | - 1.8           |       | 0.4      | nA   |

| DIGITAL IN            | IPUT (SELx pins)                           |                                                                                            | I                                                |                 |       |          |      |

| V <sub>IH</sub>       | Logic voltage high                         |                                                                                            |                                                  | 2               |       |          | V    |

| V <sub>IL</sub>       | Logic voltage low                          |                                                                                            |                                                  |                 |       | 0.8      | V    |

| R <sub>PD(IN)</sub>   | Pull-down resistance on INx pins           |                                                                                            |                                                  |                 | 6     |          | MΩ   |

| POWER SI              | JPPLY                                      |                                                                                            | 1                                                |                 |       |          |      |

Copyright © 2022 Texas Instruments Incorporated

# 6.5 Electrical Characteristics (Dual Supplies: ±15 V) (continued)

at  $T_A = 25^{\circ}$ C,  $V_{DD} = 15$  V, and  $V_{SS} = -15$  V (unless otherwise noted)

|                 | PARAMETER                      | TEST CO                               | NDITIONS                                         | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------------|---------------------------------------|--------------------------------------------------|-----|-----|-----|------|

|                 |                                |                                       |                                                  |     | 16  | 21  | μA   |

| I <sub>DD</sub> | V <sub>DD</sub> supply current | $V_{A}$ = 0 V or 3.3 V, $V_{S}$ = 0 V | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$  |     |     | 22  | μA   |

|                 |                                |                                       | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$   |     |     | 23  | μA   |

|                 |                                |                                       |                                                  |     | 7   | 10  | μA   |

| I <sub>SS</sub> | V <sub>SS</sub> supply current | $V_{A}$ = 0 V or 3.3 V, $V_{S}$ = 0 V | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$    |     |     | 11  | μA   |

|                 |                                |                                       | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |     |     | 12  | μA   |

(1) When  $V_S$  is positive,  $V_D$  is negative, and vice versa.

# 6.6 Switching Characteristics (Dual Supplies: ±15 V)

| at $T_A = 25^{\circ}C$ , $V_{DD} = 15$ V, and $V_{SS} = -15$ V | (unless otherwise noted) |

|----------------------------------------------------------------|--------------------------|

|----------------------------------------------------------------|--------------------------|

| PARAMETER                                 |                                                 | TEST CONDITIONS                                                                         | MIN | TYP   | MAX | UNIT |

|-------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-------|-----|------|

|                                           |                                                 | $V_{S}$ = ±10 V, R <sub>L</sub> = 300 $\Omega$ , C <sub>L</sub> = 35 pF                 |     | 68    | 86  | ns   |

| t <sub>on</sub>                           | Switch turn-on time                             | $V_{S}$ = ±10 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $-$ 40°C to +85°C  |     |       | 110 | ns   |

|                                           |                                                 | $V_{S}$ = ±10 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $-$ 40°C to +125°C |     |       | 121 | ns   |

|                                           |                                                 | $V_{S}$ = ±10 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF                               |     | 57    | 76  | ns   |

| t <sub>OFF</sub>                          | Switch turn-off time                            | $V_{S}$ = ±10 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $-$ 40°C to +85°C  |     |       | 82  | ns   |

|                                           |                                                 | $V_{S}$ = ±10 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $-$ 40°C to +125°C |     |       | 85  | ns   |

| t <sub>BBM</sub>                          | Break-before-make time delay<br>(TMUX6123 Only) | $V_{S}$ = 10 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $-$ 40°C to +125°C  | 20  | 40    |     | ns   |

| QJ                                        | Charge injection                                | $V_{S}$ = 0 V, $R_{S}$ = 0 $\Omega$ , $C_{L}$ = 1 nF                                    |     | 0.51  |     | рС   |

| O <sub>ISO</sub>                          | Off-isolation                                   | $R_L$ = 50 $\Omega$ , $C_L$ = 5 pF, f = 1 MHz                                           |     | - 85  |     | dB   |

| X <sub>TALK</sub>                         | Channel-to-channel crosstalk                    | $R_L$ = 50 $\Omega$ , $C_L$ = 5 pF, f = 1 MHz                                           |     | - 110 |     | dB   |

| IL                                        | Insertion loss                                  | $R_L$ = 50 $\Omega$ , $C_L$ = 5 pF, f = 1 MHz                                           |     | - 7.7 |     | dB   |

| ACPSRR                                    | AC Power Supply Rejection                       | $R_L$ = 10 k $\Omega$ , $C_L$ = 5 pF, $V_{PP}$ = 0.62 V on $V_{DD}$ f= 1 MHz            |     | - 61  |     | dB   |

| ACPORK                                    | Ratio                                           | $R_{L}$ = 10 k $\Omega$ , $C_{L}$ = 5 pF, $V_{PP}$ = 0.62 V on $V_{SS}$ f= 1 MHz        |     | - 61  |     | dB   |

| BW                                        | −3 dB Bandwidth                                 | $R_L = 50 \ \Omega$ , $C_L = 5 \ pF$                                                    |     | 630   |     | MHz  |

| THD                                       | Total harmonic distortion + noise               | $R_L = 10 \text{ k} \Omega$ , $C_L = 5 \text{ pF}$ , f= 20 Hz to 20 kHz                 |     | 0.08  |     | %    |

| C <sub>IN</sub>                           | Digital input capacitance                       | V <sub>SELx</sub> = 0 V or V <sub>DD</sub>                                              |     | 1.2   |     | pF   |

| C <sub>S(OFF)</sub>                       | Source off-capacitance                          | V <sub>S</sub> = 0 V, f = 1 MHz                                                         |     | 1.9   | 2.5 | pF   |

| C <sub>D(OFF)</sub>                       | Drain off-capacitance                           | V <sub>S</sub> = 0 V, f = 1 MHz                                                         |     | 2.2   | 2.6 | pF   |

| C <sub>S(ON),</sub><br>C <sub>D(ON)</sub> | Source and drain on-<br>capacitance             | V <sub>S</sub> = 0 V, f = 1 MHz                                                         |     | 4.2   | 5   | pF   |

# 6.7 Electrical Characteristics (Single Supply: 12 V)

at  $T_A = 25^{\circ}$ C,  $V_{DD} = 12$  V, and  $V_{SS} = 0$  V (unless otherwise noted)

|                | PARAMETER           | TEST CONDITIONS                                  | MIN             | ТҮР | MAX      | UNIT |

|----------------|---------------------|--------------------------------------------------|-----------------|-----|----------|------|

| ANALOG S       | SWITCH              |                                                  |                 |     |          |      |

| V <sub>A</sub> | Analog signal range | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ | V <sub>SS</sub> |     | $V_{DD}$ | V    |

# 6.7 Electrical Characteristics (Single Supply: 12 V) (continued)

at  $T_A = 25^{\circ}$ C,  $V_{DD} = 12$  V, and  $V_{SS} = 0$  V (unless otherwise noted)

|                       | PARAMETER                                      | TEST CO                                                      | MIN                                                 | TYP    | MAX   | UNIT |      |

|-----------------------|------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------|--------|-------|------|------|

|                       |                                                |                                                              |                                                     |        | 230   | 265  | Ω    |

| R <sub>ON</sub>       | On-resistance                                  | V <sub>S</sub> = 10 V, I <sub>S</sub> = 1 mA                 | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$     |        |       | 355  | Ω    |

|                       |                                                |                                                              | T <sub>A</sub> = - 40°C to +125°C                   |        |       | 405  | Ω    |

|                       |                                                |                                                              |                                                     |        | 1     | 9    | Ω    |

| $\Delta R_{ON}$       | On-resistance mismatch<br>between channels     | V <sub>S</sub> = 10 V, I <sub>S</sub> = 1 mA                 | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$     |        |       | 12   | Ω    |

|                       |                                                |                                                              | T <sub>A</sub> = - 40°C to +125°C                   |        |       | 14   | Ω    |

| R <sub>ON_DRIFT</sub> | On-resistance drift                            | V <sub>S</sub> = 0 V                                         |                                                     |        | 0.48  |      | %/°C |

|                       |                                                |                                                              |                                                     | - 0.02 | 0.005 | 0.02 | nA   |

| I <sub>S(OFF)</sub>   | OFF) Source off leakage current <sup>(1)</sup> | Switch state is off, $V_S = 10$<br>V/ 1 V, $V_D = 1$ V/ 10 V | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$     | - 0.08 |       | 0.04 | nA   |

|                       |                                                |                                                              | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$      | - 0.75 |       | 0.13 | nA   |

| I <sub>D(OFF)</sub>   | Drain off leakage current <sup>(1)</sup>       |                                                              |                                                     | - 0.02 | 0.005 | 0.02 | nA   |

|                       |                                                | Switch state is off, $V_S = 10$<br>V/ 1 V, $V_D = 1$ V/ 10 V | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$     | - 0.08 |       | 0.04 | nA   |

|                       |                                                |                                                              | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$    | - 0.75 |       | 0.13 | nA   |

|                       |                                                |                                                              |                                                     | - 0.04 | 0.01  | 0.04 | nA   |

| I <sub>D(ON)</sub>    | Drain on leakage current                       | Switch state is on, $V_S$ = floating, $V_D$ = 1 V/ 10 V      | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$     | - 0.16 |       | 0.08 | nA   |

|                       |                                                |                                                              | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$    | - 1.5  |       | 0.25 | nA   |

| DIGITAL IN            | IPUT (SELx pins)                               |                                                              | 11                                                  |        |       |      |      |

| V <sub>IH</sub>       | Logic voltage high                             |                                                              |                                                     | 2      |       |      | V    |

| V <sub>IL</sub>       | Logic voltage low                              |                                                              |                                                     |        |       | 0.8  | V    |

| R <sub>PD(IN)</sub>   | Pull-down resistance on INx pins               |                                                              |                                                     |        | 6     |      | MΩ   |

| POWER S               | UPPLY                                          |                                                              |                                                     |        |       |      |      |

|                       |                                                |                                                              | $V_A$ = 0 V or 3.3 V, $V_S$ = 0 V                   |        | 11    | 14   | μA   |

| I <sub>DD</sub>       | V <sub>DD</sub> supply current                 | $V_{A}$ = 0 V or 3.3 V, $V_{S}$ = 0 V                        | $V_{A} = 0 V \text{ or } 3.3 V, V_{S} = 0 V$        |        |       | 16   | μA   |

|                       |                                                |                                                              | V <sub>A</sub> = 0 V or 3.3 V, V <sub>S</sub> = 0 V |        |       | 17   | μA   |

(1) When  $V_S$  is positive,  $V_D$  is negative, and vice versa.

# 6.8 Switching Characteristics (Single Supply: 12 V)

at  $T_A$  = 25°C,  $V_{DD}$  = 12 V, and  $V_{SS}$  = 0 V (unless otherwise noted)

|                   | PARAMETER                                    | TEST CONDITIONS                                                                                        | MIN | TYP   | MAX | UNIT |

|-------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

|                   |                                              | $V_{S}$ = 8 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF                                                |     | 74    | 82  | ns   |

| t <sub>ON</sub>   | Switch turn-on time                          | $V_{S}$ = 8 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $-$ 40°C to +85°C                   |     |       | 89  | ns   |

|                   |                                              | $V_{S}$ = 8 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $-$ 40°C to +125°C                  |     |       | 93  | ns   |

|                   |                                              | $V_{S}$ = 8 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF                                                |     | 56    | 75  | ns   |

| t <sub>OFF</sub>  | Switch turn-off time                         | $V_{\rm S}$ = 8 V, $R_{\rm L}$ = 300 $\Omega$ , $C_{\rm L}$ = 35 pF, $T_{\rm A}$ = $-$ 40°C to +85°C   |     |       | 83  | ns   |

|                   |                                              | $V_{\rm S}$ = 8 V, $R_{\rm L}$ = 300 $\Omega$ , $C_{\rm L}$ = 35 pF, $T_{\rm A}$ = $$ - 40°C to +125°C |     |       | 85  | ns   |

| t <sub>BBM</sub>  | Break-before-make time delay (TMUX6123 only) | $V_{S}$ = 8 V, $R_{L}$ = 300 $\Omega$ , $C_{L}$ = 35 pF, $T_{A}$ = $$ - 40°C to +125°C                 | 20  | 37    |     | ns   |

| QJ                | Charge injection                             | $V_{S}$ = 6 V, $R_{S}$ = 0 $\Omega$ , $C_{L}$ = 1 nF                                                   |     | 0.14  |     | рС   |

| O <sub>ISO</sub>  | Off-isolation                                | $R_L$ = 50 $\Omega$ , $C_L$ = 5 pF, f = 1 MHz                                                          |     | -85   |     | dB   |

| X <sub>TALK</sub> | Channel-to-channel crosstalk                 | $R_L$ = 50 $\Omega$ , $C_L$ = 5 pF, f = 1 MHz                                                          |     | - 115 |     | dB   |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback 7

# 6.8 Switching Characteristics (Single Supply: 12 V) (continued)

at  $T_A = 25^{\circ}$ C,  $V_{DD} = 12$  V, and  $V_{SS} = 0$  V (unless otherwise noted)

|                                            | PARAMETER                           | TEST CONDITIONS                                                               | MIN | TYP  | MAX | UNIT |

|--------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| IL.                                        | Insertion loss                      | $R_L = 50 \ \Omega$ , $C_L = 5 \text{ pF}$ , f = 1 MHz                        |     | - 15 |     | dB   |

| ACPSRR                                     | AC Power Supply Rejection<br>Ratio  | $\rm R_L$ = 10 k $\Omega$ , $\rm C_L$ = 5 pF, $\rm V_{PP}$ = 0.62 V, f= 1 MHz |     | - 61 |     | dB   |

| BW                                         | -3dB Bandwidth                      | $R_L$ = 50 Ω , $C_L$ = 5 pF                                                   |     | 500  |     | MHz  |

| C <sub>IN</sub>                            | Digital input capacitance           | V <sub>IN</sub> = 0 V or V <sub>DD</sub>                                      |     | 1.3  |     | pF   |

| C <sub>S(OFF)</sub>                        | Source off-capacitance              | V <sub>S</sub> = 6 V, f = 1 MHz                                               |     | 2.2  | 2.8 | pF   |

| C <sub>D(OFF)</sub>                        | Drain off-capacitance               | V <sub>S</sub> = 6 V, f = 1 MHz                                               |     | 2.5  | 2.8 | pF   |

| C <sub>S(ON)</sub> ,<br>C <sub>D(ON)</sub> | Source and drain on-<br>capacitance | V <sub>S</sub> = 6 V, f = 1 MHz                                               |     | 4.8  | 6.1 | pF   |

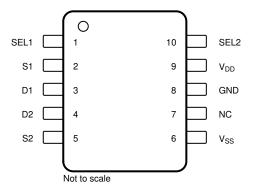

# **Typical Characteristics**

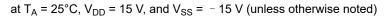

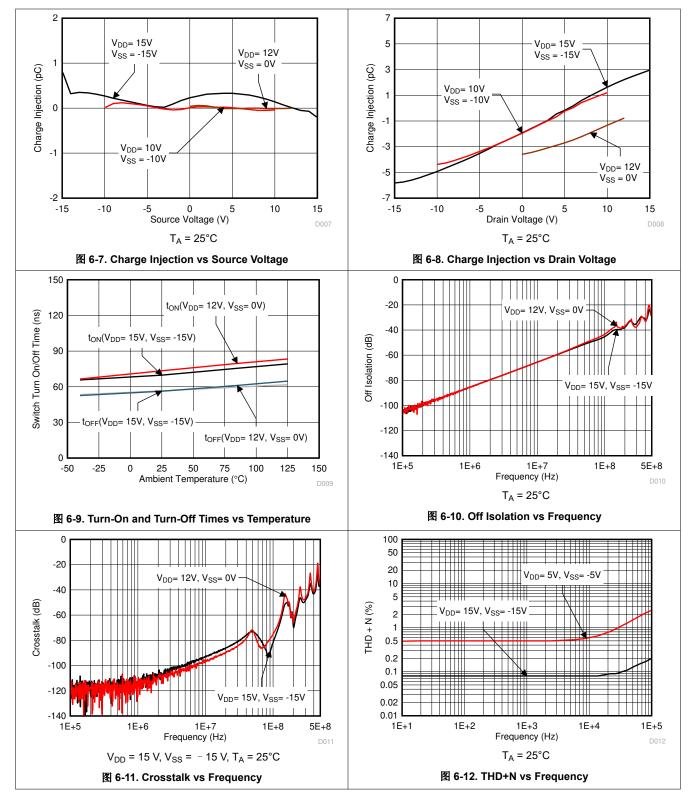

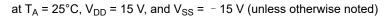

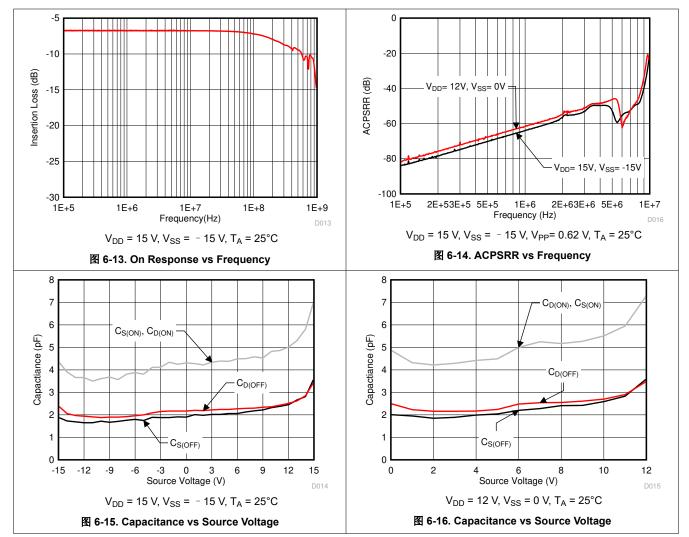

at T<sub>A</sub> = 25°C, V<sub>DD</sub> = 15 V, and V<sub>SS</sub> = -15 V (unless otherwise noted)

# **Typical Characteristics**

# **Typical Characteristics**

# 7 Parameter Measurement Information

### 7.1 Truth Tables

表 7-1, 表 7-2, and 表 7-3 show the truth tables for the TMUX6121, TMUX6122, and TMUX6123, respectively.

| 表 7-1. TMUX6121 Truth Table |                |  |  |  |  |  |  |  |  |

|-----------------------------|----------------|--|--|--|--|--|--|--|--|

| SELx STATE                  |                |  |  |  |  |  |  |  |  |

| 0                           | All Switch OFF |  |  |  |  |  |  |  |  |

| 1                           | All Switch ON  |  |  |  |  |  |  |  |  |

| 表 7-2. TMUX6122 Truth Table |               |  |  |  |  |  |  |  |

|-----------------------------|---------------|--|--|--|--|--|--|--|

| SELx STATE                  |               |  |  |  |  |  |  |  |

| 0                           | All Switch ON |  |  |  |  |  |  |  |

| 1 All Switch OFF            |               |  |  |  |  |  |  |  |

### 表 7-3. TMUX6123 Truth Table

| SELx | STATE                       |

|------|-----------------------------|

| 0    | Switch 1 OFF<br>Switch 2 ON |

| 1    | Switch 1 ON<br>Switch 2 OFF |

# 8 Detailed Description

# 8.1 Overview

The TMUX6121, TMUX6122, and TMUX6123 are 2-channel single-pole/ single-throw (SPDT) switches that support dual supplies ( $\pm$ 5 V to  $\pm$ 16.5 V) or single supply (10 V to 16.5 V) operation. Each channel of the switch is turned on or turned off based on the state of its corresponding SELx pin.  $\ddagger$  8.2 provides a top-level block diagram of the switches.

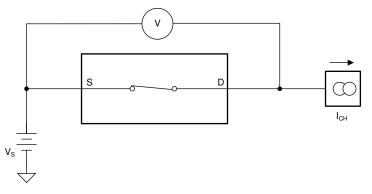

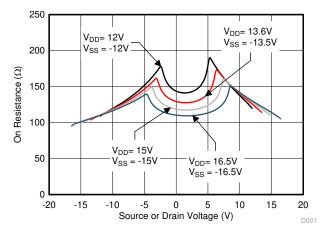

#### 8.1.1 On-Resistance

The on-resistance of the TMUX6121, TMUX6122, and TMUX6123 is the ohmic resistance across the source (Sx) and drain (D) pins of the device. The on-resistance varies with input voltage and supply voltage. The symbol  $R_{ON}$  is used to denote on-resistance. The measurement setup used to measure  $R_{ON}$  is shown in 图 8-1. Voltage (V) and current ( $I_{CH}$ ) are measured using this setup, and  $R_{ON}$  is computed as shown in 方程式 1:

图 8-1. On-Resistance Measurement Setup

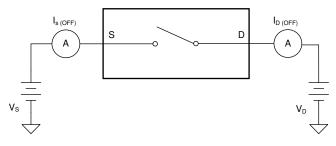

#### 8.1.2 Off-Leakage Current

There are two types of leakage currents associated with a switch during the off state:

- 1. Source off-leakage current

- 2. Drain off-leakage current

Source leakage current is defined as the leakage current flowing into or out of the source pin when the switch is off. This current is denoted by the symbol  $I_{S(OFF)}$ .

Drain leakage current is defined as the leakage current flowing into or out of the drain pin when the switch is off. This current is denoted by the symbol  $I_{D(OFF)}$ .

The setup used to measure both off-leakage currents is shown in <u>88-2</u>.

图 8-2. Off-Leakage Measurement Setup

(1)

#### 8.1.3 On-Leakage Current

On-leakage current is defined as the leakage current that flows into or out of the drain pin when the switch is in the on state. The source pin is left floating during the measurement.  $\mathbb{X}$  8-3 shows the circuit used for measuring the on-leakage current, denoted by  $I_{D(ON)}$ .

图 8-3. On-Leakage Measurement Setup

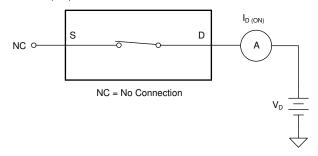

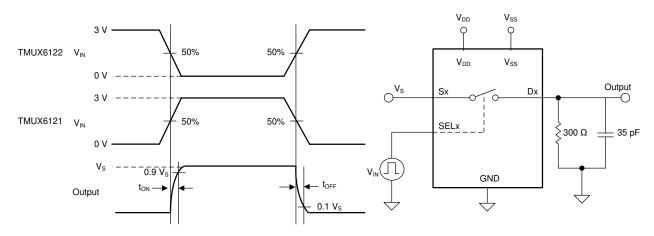

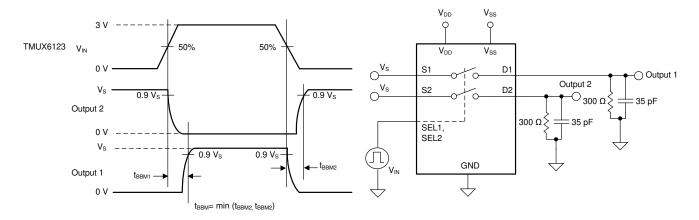

#### 8.1.4 Turn-On and Turn-Off Time

Turn-on time is defined as the time taken by the output of the TMUX6121, TMUX6122, and TMUX6123 to rise to a 90% final value after the SELx signal has risen (for NO switches) or fallen (for NC switches) to a 50% final value.  $\mathbb{X}$  8-4 shows the setup used to measure turn-on time. Turn-on time is denoted by the symbol t<sub>ON</sub>.

Turn off time is defined as the time taken by the output of the TMUX6121, TMUX6122, and TMUX6123 to fall to a 10% initial value after the SELx signal has fallen (for NO switches) or risen (for NC switches) to a 50% initial value.  $\boxed{8}$  8-4 shows the setup used to measure turn-off time. Turn-off time is denoted by the symbol t<sub>OFF</sub>.

图 8-4. Transition-Time Measurement Setup

#### 8.1.5 Break-Before-Make Delay

The break-before-make delay is a safety feature of the TMUX6123 switch. The TMUX6123's ON switches first break the connection before the OFF switches make connection. The time delay between the break and the make is known as break-before-make delay.  $\mathbb{E}$  8-5 shows the setup used to measure break-before-make delay, denoted by the symbol t<sub>BBM</sub>.

图 8-5. Break-Before-Make Delay Measurement Setup

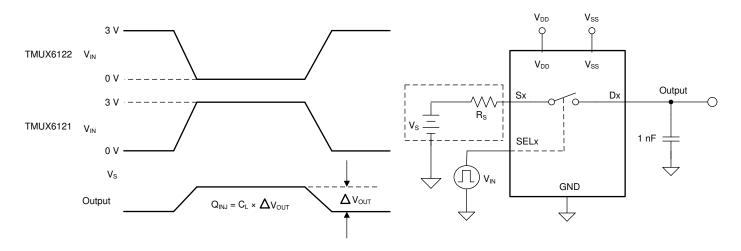

#### 8.1.6 Charge Injection

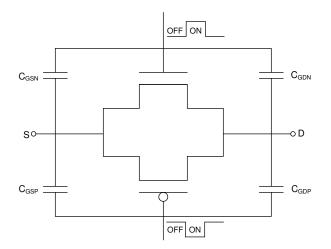

The TMUX6121, TMUX6122, and TMUX6123 have a simple transmission-gate topology. Any mismatch in capacitance between the NMOS and PMOS transistors results in a charge injected into the drain or source during the falling or rising edge of the gate signal. The amount of charge injected into the source or drain of the device is known as charge injection, and is denoted by the symbol QINJ. 🕅 8-6 shows the setup used to measure charge injection.

图 8-6. Charge-Injection Measurement Setup

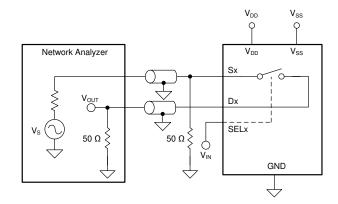

#### 8.1.7 Off Isolation

Off isolation is defined as the voltage at the drain pin (Dx) of the TMUX6121, TMUX6122, and TMUX6123 when a 1-V<sub>RMS</sub> signal is applied to the source pin (Sx) of an OFF switch. 图 8-7 shows the setup used to measure off isolation. Use 方程式 2 to compute off isolation.

#### 图 8-7. Off Isolation Measurement Setup

Off Isolation =

$$20 \cdot \text{Log}\left(\frac{V_{\text{OUT}}}{V_{\text{S}}}\right)$$

(2)

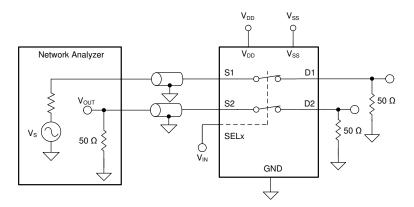

#### 8.1.8 Channel-to-Channel Crosstalk

Channel-to-channel crosstalk is defined as the voltage at the source pin (Sx) of an off-channel, when a  $1-V_{RMS}$  signal is applied at the source pin (Sx) of an on-channel. 8-8 shows the setup used to measure, and 5  $\pm$  3 is the equation used to compute, channel-to-channel crosstalk.

#### 图 8-8. Channel-to-Channel Crosstalk Measurement Setup

Channel-to-Channel Crosstalk =

$$20 \cdot Log\left(\frac{V_{OUT}}{V_S}\right)$$

(3)

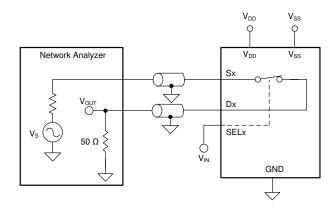

#### 8.1.9 Bandwidth

Bandwidth is defined as the range of frequencies that are attenuated by < 3 dB when the input is applied to the source pin (Sx) of an on-channel, and the output is measured at the drain pin (D) of the TMUX6121, TMUX6122, and TMUX6123. 图 8-9 shows the setup used to measure bandwidth of the switch. Use 方程式 4 to compute the attenuation.

#### 图 8-9. Bandwidth Measurement Setup

Attenuation =

$$20 \cdot \text{Log}\left(\frac{V_2}{V_1}\right)$$

(4)

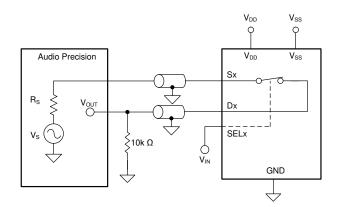

#### 8.1.10 THD + Noise

The total harmonic distortion (THD) of a signal is a measurement of the harmonic distortion, and is defined as the ratio of the sum of the powers of all harmonic components to the power of the fundamental frequency at the mux output. The on-resistance of the TMUX6121, TMUX6122, and TMUX6123 varies with the amplitude of the input signal and results in distortion when the drain pin is connected to a low-impedance load. Total harmonic distortion plus noise is denoted as THD+N. 🛛 8-10 shows the setup used to measure THD+N of the TMUX6121, TMUX6122, and TMUX6122, and TMUX6123.

图 8-10. THD+N Measurement Setup

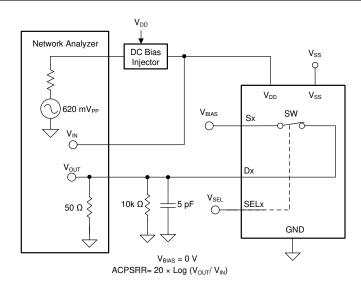

#### 8.1.11 AC Power Supply Rejection Ratio (AC PSRR)

AC PSRR measures the ability of a device to prevent noise and spurious signals that appear on the supply voltage pin from coupling to the output of the switch. The DC voltage on the device supply is modulated by a sine wave of 620 mVPP. The ratio of the amplitude of signal on the output to the amplitude of the modulated signal is the AC PSRR. 🕅 8-11 shows the setup used to measure ACPSRR of the TMUX6121, TMUX6122, and TMUX6123.

#### 图 8-11. AC PSRR Measurement Setup

<sup>†</sup> 8.2 provides a top-level block diagram of the TMUX6121, TMUX6122, and TMUX6123. The devices are 2channel, single-ended, analog switches. Each channel is turned on or turned off based on the state of the address lines and enable pin.

# 8.2 Functional Block Diagram

# 8.3 Feature Description

#### 8.3.1 Ultralow Leakage Current

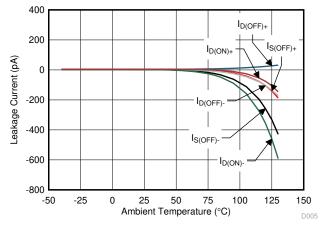

The TMUX6121, TMUX6122, and TMUX6123 provide extremely low on- and off-leakage currents. The devices are capable of switching signals from high source-impedance inputs into a high input-impedance op amp with minimal offset error because of the ultralow leakage currents. 🕅 8-12 shows typical leakage currents of the devices versus temperature.

图 8-12. Leakage Current vs Temperature

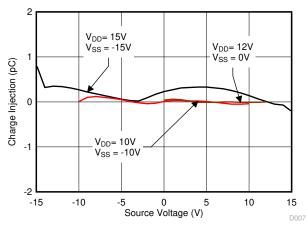

#### 8.3.2 Ultralow Charge Injection

The TMUX6121 is implemented with simple transmission gate topology, as shown in 🕅 8-13. Any mismatch in the stray capacitance associated with the NMOS and PMOS causes an output level change whenever the switch is opened or closed.

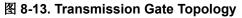

The devices utilize special charge-injection cancellation circuitry that reduces the source (Sx)-to-drain (Dx) charge injection to as low as 0.51 pC at VS = 0 V, as shown in  $\boxed{8}$  8-14.

图 8-14. Source-to-Drain Charge Injection vs Source or Drain Voltage

#### 8.3.3 Bidirectional and Rail-to-Rail Operation

The TMUX6121, TMUX6122, and TMUX6123 conduct equally well from source (Sx) to drain (Dx) or from drain (Dx) to source (Sx). Each channel of the switches has very similar characteristics in both directions. The input signal to the devices swings from  $V_{SS}$  to  $V_{DD}$  without any significant degradation in performance. The on resistance of these devices varies with input signal.

### 8.4 Device Functional Modes

Each channel of the TMUX6121, TMUX6122, and TMUX6123 is turned on or turned off based on the state of its corresponding SELx pin. The SELx pins are weakly pulled-down through an internal 6 M  $\Omega$  resistor, allowing the switches to stay in a determined state when power is applies to the devices. The SELx pins can be connected to V<sub>DD</sub>.

# 9 Application and Implementation

备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

#### 9.1 Application Information

The TMUX6121, TMUX6122, and TMUX6123 offer outstanding input/output leakage currents and ultralow charge injection. These devices operate up to 33 (dual supply) or 16.5 V (single supply), and offer true rail-to-rail input and output. The on-capacitance of the TMUX6121, TMUX6122, and TMUX6123 is low. These features makes the TMUX6121, TMUX6122, and TMUX6123 a family of precision, robust, high-performance analog multiplexer for high-voltage, industrial applications.

#### 9.2 Typical Application

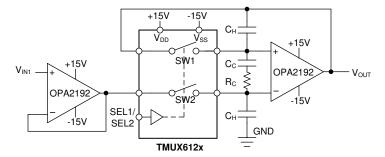

One useful application to take advantage of TMUX6121, TMUX6122, and TMUX6123's precision performance is the sample and hold circuit. A sample and hold circuit can be useful for an analog to digital converter (ADC) to sample a varying input voltage with improved reliability and stability. It can also be used to store the output samples from a single digital-to-analog converter (DAC) in a multi-output application. A simple sample and hold circuit can be realized using an analog switch like one of the TMUX6121, TMUX6122, and TMUX6123 analog switches.

图 9-1. A Sample and Hold Circuit Realized Using the TMUX611x Analog Switch

#### 9.2.1 Design Requirements

The purpose of this precision design is to implement an optimized 2-output sample and hold circuit using a 4channel SPST switch. The sample and hold circuit needs to be capable of supporting high voltage output swing up to  $\pm$  15 V with minimized pedestal error and fast settling time. The overall system block diagram is shown in  $\bigotimes$  9-1.

#### 9.2.2 Detailed Design Procedure

The TMUX6121, TMUX6122, or TMUX6123 switch is used in conjunction with the voltage holding capacitors ( $C_H$ ) to implement the sample and hold circuit. The basic operation is:

- 1. When the switch SW2 is closed, it samples the input voltage and charges the holding capacitors (C<sub>H</sub>) to the input voltages values.

- 2. When the switch SW2 is open, the holding capacitors ( $C_H$ ) holds its previous value, maintaining stable voltage at the amplifier output ( $V_{OUT}$ )

Ideally, the switch delivers only the input signals to the holding capacitors. However, when the switch gets toggled, some amount of charge also gets transferred to the switch output in the form of charge injection, resulting slight sampling error. The TMUX6121, TMUX6122, and TMUX6123 switches have excellent charge injection performance of only 0.51 pC, making them ideal choices for this implementation to minimize sampling error. Due to switch and capacitor leakage current, the voltage on the hold capacitors droops with time. The TMUX6121, TMUX6122, and TMUX6123 minimize the droops due to its ultra-low leakage performance. At 25°C, the TMUX6111, TMUX6112, and TMUX6113 have extremely tiny leakage current at 0.5 pA typical and 20 pA maximum. The TMUX6121, TMUX6122, and TMUX6123 devices also support high voltage capability. The devices support up to ± 16.5 V dual supply operation, making it an ideal solution in this high voltage sample and hold application.

A second switch SW1 is also included to operate in parallel with SW2 to reduce pedestal error during switch toggling. Because both switches are driven at the same potential, they act as common-mode signal to the opamp, thereby minimizing the charge injection effects caused by the switch toggling action. Compensation network consisting of  $R_C$  and CC is also added to further reduce the pedestal error, whiling reducing the hold-time glitch and improving the settling time of the circuit.

#### 9.2.3 Application Curve

TMUX6121, TMUX6122, and TMUX6123 have excellent charge injection performance of only 0.51 pC (typical), making them ideal choices to minimize sampling error for the sample and hold application. 9-2 shows the plot for the charge injection versus source input voltage for TMUX6121, TMUX6122, and TMUX6123.

图 9-2. Charge Injection vs. Source Voltage for TMUX6121, TMUX6122 and TMUX6123

# **10 Power Supply Recommendations**

The TMUX6121, TMUX6122, and TMUX6123 operate across a wide supply range of ±5 V to ±16.5 V (10 V to 16.5 V in single-supply mode). They also perform well with asymmetrical supplies such as  $V_{DD}$  = 12 V and  $V_{SS}$ = - 5 V. For improved supply noise immunity, use a supply decoupling capacitor ranging from 0.1 µF to 10 µF at both the  $V_{DD}$  and  $V_{SS}$  pins to ground. Always ensure the ground (GND) connection is established before supplies are ramped. As a best practice, it is recommended to ramp  $V_{SS}$  first before  $V_{DD}$  in dual or asymmetrical supply applications.

The on-resistance of the TMUX6121, TMUX6122, and TMUX6123 varies with supply voltage, as shown in ⊠ 10-1

图 10-1. On-Resistance Variation With Supply and Input Voltage

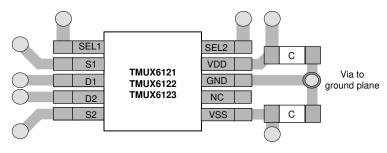

# 11 Layout

#### **11.1 Layout Guidelines**

图 11-1 shows an example of a PCB layout with the TMUX6121, TMUX6122, and TMUX6123.

Some key considerations are:

- 1. Decouple the V<sub>DD</sub> and V<sub>SS</sub> pins with a 0.1-µF capacitor, placed as close to the pin as possible. Make sure that the capacitor voltage rating is sufficient for the V<sub>DD</sub> and V<sub>SS</sub> supplies.

- 2. Keep the input lines as short as possible.

- 3. Use a solid ground plane to help distribute heat and reduce electromagnetic interference (EMI) noise pickup.

- 4. Do not run sensitive analog traces in parallel with digital traces. Avoid crossing digital and analog traces if possible, and only make perpendicular crossings when necessary.

#### 11.2 Layout Example

图 11-1. TMUX6121 Layout Example

# 12 Device and Documentation Support

### **12.1 Documentation Support**

#### 12.1.1 Related Documentation

For related documentation, see the following:

• Texas Instruments, OPAx192 36-V, Precision, Rail-to-Rail Input/Output, Low Offset Voltage, Low Input Bias Current Op Amp with e-trim™

### 12.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*订阅更新*进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

# 12.3 支持资源

TI E2E<sup>™</sup> 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解 答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 12.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

#### **12.5 Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.6 术语表

TI 术语表 本术语表列出并解释了术语、首字母缩略词和定义。

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                 |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                     |              |                |         |

| TMUX6121DGSR     | ACTIVE | VSSOP        | DGS     | 10   | 2500    | RoHS & Green | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 1Q16           | Samples |

| TMUX6122DGSR     | ACTIVE | VSSOP        | DGS     | 10   | 2500    | RoHS & Green | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 1Q26           | Samples |

| TMUX6123DGSR     | ACTIVE | VSSOP        | DGS     | 10   | 2500    | RoHS & Green | NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 1Q36           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

www.ti.com

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

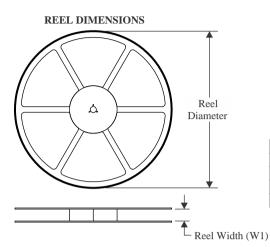

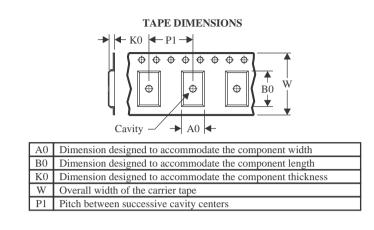

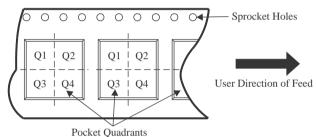

# TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TMUX6121DGSR                | VSSOP           | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TMUX6122DGSR                | VSSOP           | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TMUX6123DGSR                | VSSOP           | DGS                | 10 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com

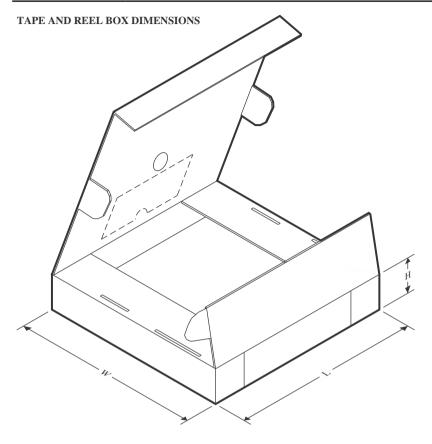

# PACKAGE MATERIALS INFORMATION

3-Jun-2022

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TMUX6121DGSR | VSSOP        | DGS             | 10   | 2500 | 366.0       | 364.0      | 50.0        |

| TMUX6122DGSR | VSSOP        | DGS             | 10   | 2500 | 366.0       | 364.0      | 50.0        |

| TMUX6123DGSR | VSSOP        | DGS             | 10   | 2500 | 366.0       | 364.0      | 50.0        |

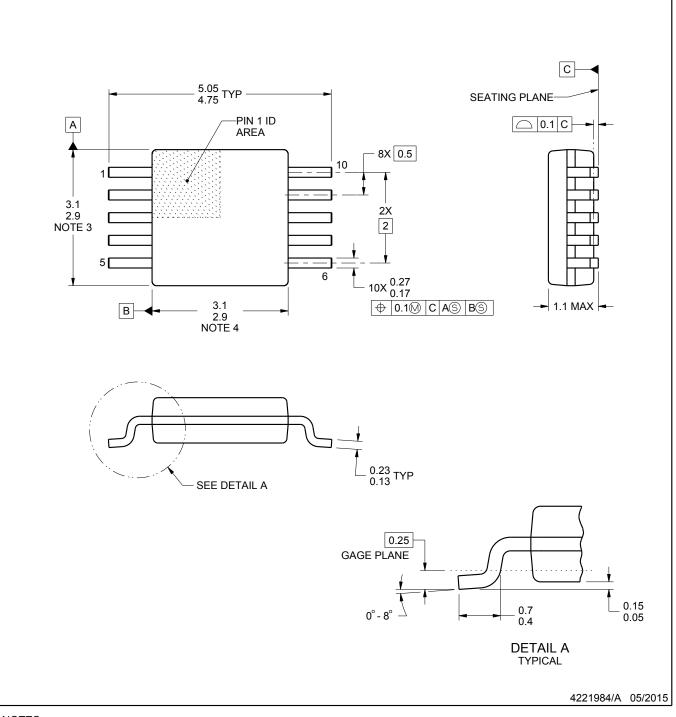

# **DGS0010A**

# **PACKAGE OUTLINE**

# VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187, variation BA.

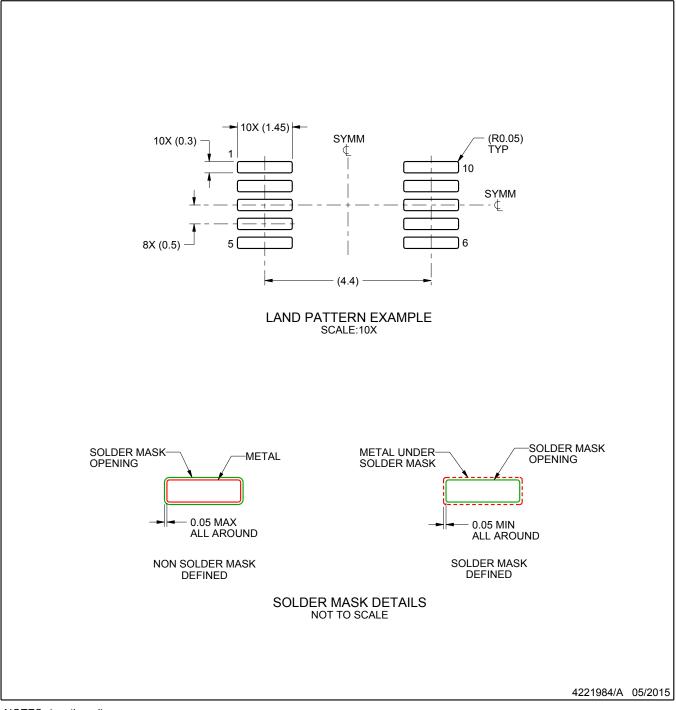

# DGS0010A

# **EXAMPLE BOARD LAYOUT**

# VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

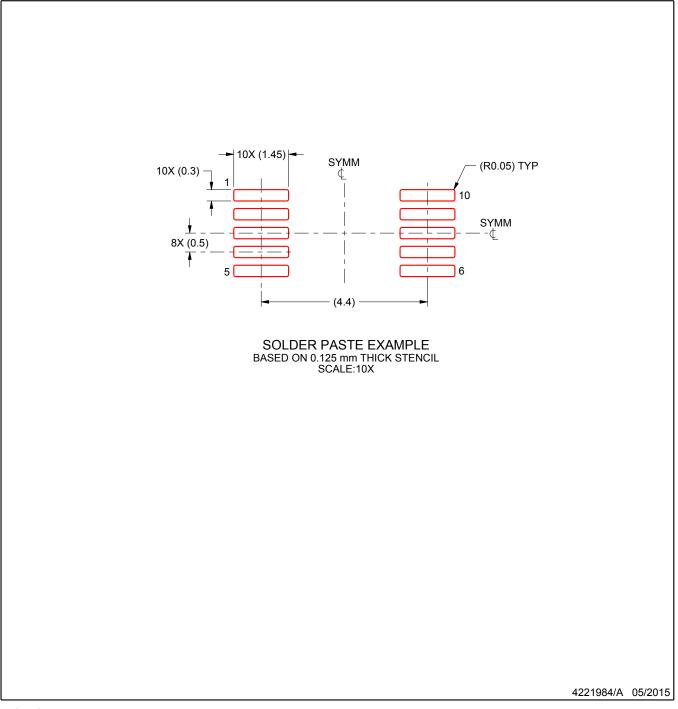

# DGS0010A

# **EXAMPLE STENCIL DESIGN**

# VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

9. Board assembly site may have different recommendations for stencil design.

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analogue Switch ICs category:

Click to view products by Texas Instruments manufacturer:

Other Similar products are found below :

FSA3051TMX NLAS5223BLMNR2G NLX2G66DMUTCG TC74HC4066AFTEL 425541DB DG403DY 099044FB MAX4762ETB+ NLAS3799BMNR2G NLAS5123MNR2G ISL84684IR PI5A4157CEX PI5A4599BCEX NLAS4717EPFCT1G PI5A3167CCEX SLAS3158MNR2G PI5A392AQE ADG714BCPZ-REEL7 DG333ALDW-T1-E3 ISL43113IB ISL43140IB ISL43140IBZ-T ISL43143IR ISL43L120IR ISL43L121IR ISL43L122IR ISL43L220IR ISL43L410IR ISL43L420IR ISL43L710IR ISL43L711IR ISL43L712IR ISL84053IA ISL84514IB ISL84516IB ISL84684IUZ-T LNLASB3157DFT2G NLAS324US NLASTV4599DFT2G TPW4053-SR WAS4642Q-24/TR ADG842YKSZ-REEL7 WAS4766C-9/TR WAS7227Q-10/TR WAS4646C-36/TR WAS4735Q-16/TR BL1532TQFN RS2233YS16 CH483M TMUX1248DCKR