ZHCS265G - OCTOBER 2011-REVISED JANUARY 2013

www.ti.com.cn

#### 限流、配电开关 双通道、

查询样品: TPS2052C, TPS2062C, TPS2062C-2, TPS2066C, TPS2066C-2, TPS2060C, TPS2064C, TPS2064C-2, TPS2002C, TPS2003C

#### 特性

- 双电源开关系列 •

- 0.5A, 1A, 1.5A, 2A 的额定电流

- 准确度为 ±20% 的电流限值容限

- 快速过流响应 2µs (典型值)

- **70m**Ω(典型值) 高侧 N 通道金属氧化物半导体场 效应晶体管 (MOSFET)

- 工作电压范围: 4.5V 至 5.5V

- 去尖峰脉冲故障报告 (FLTx)

- 所选的具有 (TPS20xxC) 和不具有 (TPS20xxC-2) • 输出放电的部件

- 反向电流阻断

- 内置软启动 .

- 与现有的 71 开关系列产品引脚到引脚相对应

- 环境温度范围: -40°C 至 85°C

#### 应用范围

- USB 端口/集线器、笔记本、台式机 •

- 高清数字电视

- 机顶盒 •

- 短路保护功能

#### 说明

TPS20xxC 和 TPS20xxC-2 双配电开关系列产品用于诸如 USB 等有可能遇到高电容负载和短路的应用。这一系列 产品为电流介于 0.5A 和 2A 之间的应用提供具有固定电流限值阀值的多种器件。

当输出负载超过电流限值阀值时,TPS20xxC 和 TPS20xxC-2 通过运行在恒定电流模式下来将输出电流限制在安全 的水平上。 这就在所有条件下提供了一个可预计的故障电流。 当输出被短接时,快速过载响应时间减轻了主 5V 电源提供稳压电源的负担。 为了大大减少打开和关闭期间的电流冲击,电源开关的上升和下降次数受到控制。

#### Table 1. Devices

| RATED CURRENT | DEVICES              |                    |                   |                   |              |

|---------------|----------------------|--------------------|-------------------|-------------------|--------------|

| RATED CORRENT | DEVICES              | MSOP-8 (PowerPad™) | SON -10           | SOIC-8            | SON-8        |

| 0.5 A         | TPS2052C             | Active             | _                 | -                 | -            |

| 1 A           | TPS2062C and 66C     | Active and Active  | _                 | Active and Active | —            |

| 1 A           | TPS2062C-2 and 66C-2 | - and Active       | _                 | -                 | Active and — |

| 1.5 A         | TPS2060C and 64C     | Active and Active  | _                 | -                 | -            |

| 1.5 A         | TPS2064C-2           | Active             | _                 | —                 | —            |

| 2 A           | TPS2002C and 03C     | —                  | Active and Active | -                 | -            |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

#### www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| MAXIMUM              |        | OUTPUT              |                     | PA            | ACKAGE DEVICES a          | nd MARKING <sup>(;</sup> | 3)             |

|----------------------|--------|---------------------|---------------------|---------------|---------------------------|--------------------------|----------------|

| OPERATING<br>CURRENT | ENABLE | OUTPUT<br>DISCHARGE | BASE PART<br>NUMBER | SOIC-8<br>(D) | MSOP-8 (DGN)<br>PowerPAD™ | SON-10<br>(DRC)          | SON-8<br>(DRB) |

| 0.5                  | High   | Y                   | TPS2052C            | -             | PYNI                      | -                        | -              |

| 1                    | Low    | Y                   | TPS2062C            | 2062C         | VRBQ                      | -                        | -              |

| 1                    | Low    | Ν                   | TPS2062C-2          | -             | -                         | -                        | PYVI           |

| 1                    | High   | Y                   | TPS2066C            | 2066C         | VRDQ                      | -                        | -              |

| 1                    | High   | Ν                   | TPS2066C-2          | -             | PYUI                      | -                        | -              |

| 1.5                  | Low    | Y                   | TPS2060C            | -             | VRAQ                      | -                        | -              |

| 1.5                  | High   | Y                   | TPS2064C            | -             | VRCQ                      | -                        | -              |

| 1.5                  | High   | Ν                   | TPS2064C-2          | -             | PYTI                      | -                        | -              |

| 2                    | Low    | Y                   | TPS2002C            | -             | -                         | VREQ                     | -              |

| 2                    | High   | Y                   | TPS2003C            | -             | -                         | VRFQ                     | -              |

#### **DEVICE INFORMATION**<sup>(1)(2)</sup>

(1) For the most current packaging and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

(2) Package code for MSOP-8 is "DGN" and for SON is "DRC".

(3) "-" indicates the device is not available in this package.

#### **ABSOLUTE MAXIMUM RATINGS**<sup>(1)(2)</sup>

|            |                                                  | VA         | UNIT   |    |  |

|------------|--------------------------------------------------|------------|--------|----|--|

|            |                                                  | MIN        |        |    |  |

| Voltage ra | nge on IN, OUTx, ENx or ENx, FLTx <sup>(3)</sup> | -0.3       | 6      | V  |  |

| Voltage ra | age range from IN to OUT -6 6                    |            |        |    |  |

| Maximum    | junction temperature, T <sub>J</sub>             | Internally | °C     |    |  |

|            | Human Body Model                                 |            | 2      | kV |  |

| ESD        | Charged Device Model                             |            | 500    | V  |  |

|            | IEC 61000-4-2, Contact / Air <sup>(4)</sup>      |            | 8 / 15 | kV |  |

(1) Absolute maximum ratings apply over recommended junction temperature range.

(2) All voltages are with respect to GND unless otherwise noted.

(3) See INPUT AND OUTPUT CAPACITANCE section.

(4) V<sub>OUT</sub> was surged on a PCB with input and output bypassing per Figure 1 (except input capacitor was 22 μF) with no device failure.

#### THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)(2)</sup>             | D      | DGN    | DRC     | DRB    | UNITS |

|-------------------------|----------------------------------------------|--------|--------|---------|--------|-------|

|                         |                                              | 8 PINS | 8 PINS | 10 PINS | 8-PINS | UNITS |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 129.9  | 57.2   | 45.4    | 50.8   |       |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 83.5   | 110.5  | 58      | 60.3   |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 70.4   | 60.7   | 21.1    | 26.3   | °C/W  |

| $\Psi_{JT}$             | Junction-to-top characterization parameter   | 36.6   | 7.8    | 1.9     | 2.1    | °C/vv |

| $\Psi_{JB}$             | Junction-to-board characterization parameter | 66.9   | 24     | 21.3    | 26.5   |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | n/a    | 14.3   | 9.1     | 9.8    |       |

(1) 有关传统和新的热度量的更多信息,请参阅/C 封装热度量应用报告, SPRA953。

(2) 有关该器件的基于印刷电路板 (PCB) 覆铜区的热评估信息, 请参阅TI PCB 热应力 计算。

www.ti.com.cn

ZHCS265G-OCTOBER 2011-REVISED JANUARY 2013

#### **RECOMMENDED OPERATING CONDITIONS**

|                     |                                                  |                                 | MIN | NOM | MAX | UNIT |

|---------------------|--------------------------------------------------|---------------------------------|-----|-----|-----|------|

| V <sub>IN</sub>     | Input voltage, IN                                |                                 | 4.5 |     | 5.5 | N/   |

| V <sub>Enable</sub> | Input voltage, ENx or ENx                        |                                 | 0   |     | 5.5 | v    |

|                     | I <sub>OUTx</sub> Continuous ouput current, OUTx | TPS2052C                        |     |     | 0.5 |      |

|                     |                                                  | TPS2062C, 62C-2, 66C, and 66C-2 |     |     | 1   | ٨    |

| OUTx                |                                                  | TPS2060C, 64Cand 64C-2          |     |     | 1.5 | A    |

|                     |                                                  | TPS2002C and 03C                |     |     | 2   |      |

| TJ                  | Operating junction temperature                   | -40                             |     | 125 | °C  |      |

| IFLTx               | Sink current into FLTx                           |                                 | 0   |     | 5   | mA   |

#### ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

| $T_J = T_A = 25^{\circ}C$ , $V_{IN} = 5 V$ , $V_{ENx} = V_{IN}$ or $V_{\overline{ENx}} = 0V$ (unless otherwise | se noted) | ess otherwise | = 0V (unless | N or VE | $V_{\text{ENY}} = V$ | = 5 V, | , V <sub>IN</sub> | = 25°C | $T_{\perp} = T_{\perp}$ |

|----------------------------------------------------------------------------------------------------------------|-----------|---------------|--------------|---------|----------------------|--------|-------------------|--------|-------------------------|

|----------------------------------------------------------------------------------------------------------------|-----------|---------------|--------------|---------|----------------------|--------|-------------------|--------|-------------------------|

|                                   | PARAMETER                                  | TEST CONDITIONS                                                                                                                                                                                                                           |                                                                                               | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| POWER                             | SWITCH                                     |                                                                                                                                                                                                                                           |                                                                                               |      |      |      |      |

|                                   |                                            | TPS2052C (0.5 A)                                                                                                                                                                                                                          | DGN                                                                                           |      | 70   | 84   |      |

|                                   |                                            | TPS2052C (0.5 A)<br>-40°C ≤ (T <sub>J</sub> , T <sub>A</sub> ) ≤ 85°C                                                                                                                                                                     | DGN                                                                                           |      | 70   | 95   |      |

|                                   |                                            | TPS2062C, 66C, and 66C-2 (1 A)                                                                                                                                                                                                            | DGN                                                                                           |      | 70   | 84   |      |

|                                   |                                            | TPS2062C, 66C, and 66C-2 (1 A), $-40^{\circ}C \le (T_J, T_A) \le 85^{\circ}C$                                                                                                                                                             | DGN                                                                                           |      | 70   | 95   |      |

|                                   |                                            | TPS2062C and 66C (1 A)                                                                                                                                                                                                                    | D                                                                                             |      | 90   | 108  |      |

| r <sub>DS(on)</sub> On-resistance | On-resistance                              | TPS2062C and 66C (1 A),<br>-40°C $\leq$ (T <sub>J</sub> , T <sub>A</sub> ) $\leq$ 85°C                                                                                                                                                    | D                                                                                             |      | 90   | 122  | mΩ   |

|                                   |                                            | TPS2062C-2 (1 A)                                                                                                                                                                                                                          | DRB                                                                                           |      | 73   | 87   |      |

|                                   |                                            | TPS2062C-2 (1 A)<br>−40°C ≤ (T <sub>J</sub> , T <sub>A</sub> ) ≤ 85°C                                                                                                                                                                     | DRB                                                                                           |      | 73   | 101  |      |

|                                   |                                            | TPS2060C, 64C, and 64C-2 (1.5 A)                                                                                                                                                                                                          |                                                                                               | 70   | 84   |      |      |

|                                   |                                            | TPS2060C, 64C, and 64C-2 (1.5 A), - $T_A$ ) ≤ 85°C                                                                                                                                                                                        | TPS2060C, 64C, and 64C-2 (1.5 A), –40°C $\leq$ (T <sub>J</sub> , T <sub>A</sub> ) $\leq$ 85°C |      |      | 95   |      |

|                                   |                                            | TPS2002C and 03C (2 A)                                                                                                                                                                                                                    |                                                                                               |      | 70   | 84   |      |

|                                   |                                            | TPS2002C and 03C (2 A), –40°C ≤ (1                                                                                                                                                                                                        | J, T <sub>A</sub> ) ≤ 85°C                                                                    |      | 70   | 95   |      |

| CURRE                             | NT LIMIT                                   |                                                                                                                                                                                                                                           |                                                                                               |      |      |      |      |

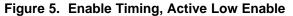

|                                   |                                            | TPS2052C (0.5 A)                                                                                                                                                                                                                          |                                                                                               | 0.75 | 1    | 1.25 |      |

|                                   | Current limit, See Figure 7                | TPS2062C, 62C-2, 66C, and 66C-2 (1 A)                                                                                                                                                                                                     |                                                                                               |      | 1.61 | 1.94 | А    |

| OS                                | Current limit, See Figure 7                | TPS2060C, 64C, and 64C-2 (1.5 A)                                                                                                                                                                                                          | 1.83                                                                                          | 2.29 | 2.75 | A    |      |

|                                   |                                            | TPS2002C and 03C (2 A)                                                                                                                                                                                                                    | 2.55                                                                                          | 3.15 | 3.77 |      |      |

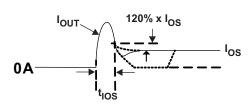

| tios                              | Short-circuit response time                | $\label{eq:VIN} \begin{array}{l} V_{\text{IN}} = 5 \ V \ (\text{see Figure 6}), \\ One-half \ full \ load \rightarrow R_{(\text{SHORT})} = 50 \ \text{m}\Omega \\ application \ to \ when \ current \ falls \ below \\ value \end{array}$ | 2, Measure from<br>120% of final                                                              |      | 2    |      | μs   |

| SUPPLY                            | CURRENT                                    |                                                                                                                                                                                                                                           |                                                                                               |      |      |      |      |

| SD                                | Supply current, device disabled            | I <sub>(OUTx)</sub> = 0 mA                                                                                                                                                                                                                |                                                                                               |      | 0.01 | 1    |      |

| S1E                               | Supply current, single switch enabled      | I <sub>(OUTx)</sub> = 0 mA                                                                                                                                                                                                                |                                                                                               |      | 60   | 75   |      |

| S2E                               | Supply current, both switches enabled      | $I_{(OUTx)} = 0 \text{ mA}$                                                                                                                                                                                                               |                                                                                               |      | 100  | 120  | μA   |

| LKG                               | Leakage current                            | $V_{OUT}$ = 0 V, $V_{IN}$ = 5.5 V, disabled, measured $I_{VIN}$                                                                                                                                                                           | TPS20xxC-2                                                                                    |      | 0.05 | 1    | P. 1 |

|                                   | Reverse leakage current                    | $V_{\text{OUT}}$ = 5.5 V, $V_{\text{IN}}$ = 0 V, measured $I_{\text{OU}}$                                                                                                                                                                 | JTx                                                                                           |      | 0.15 | 1    |      |

| OUTPU                             | T DISCHARGE                                |                                                                                                                                                                                                                                           |                                                                                               |      |      |      |      |

| R <sub>PD</sub>                   | Output pull-down resistance <sup>(2)</sup> | $V_{IN} = V_{(OUTx)} = 5 V$ , disabled                                                                                                                                                                                                    | TPS20xxC                                                                                      | 400  | 470  | 600  | Ω    |

(1)

Pulsed testing techniques maintain junction temperature approximately equal to ambient temperature These parameters are provided for reference only, and do not constitute part of TI's published device specifications for purposes of TI's (2)product warranty.

ZHCS265G - OCTOBER 2011-REVISED JANUARY 2013

#### ELECTRICAL CHARACTERISTICS

$-40^{\circ}C \le (T_J = T_A) \le 125^{\circ}C$ ,  $4.5 \text{ V} \le V_{IN} \le 5.5 \text{ V}$ ,  $V_{ENx} = V_{IN} \text{ or } V_{\overline{ENx}} = 0 \text{ V}$ ,  $I_{OUTx} = 0 \text{ A}$ , typical values are at 5 V and 25°C (unless otherwise noted)

|                     | PARAMETER                             | TEST CONDITIONS <sup>(</sup>                                                                                                 | 1)                                                                                                              | MIN  | TYP  | MAX  | UNIT |

|---------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POWER               | RSWITCH                               |                                                                                                                              |                                                                                                                 |      |      |      |      |

|                     |                                       | TPS2052C (0.5 A)                                                                                                             | DGN                                                                                                             |      | 70   | 112  |      |

|                     |                                       | TPS2062C, 66C, and 66C-2 (1 A)                                                                                               | DGN                                                                                                             |      | 70   | 112  |      |

|                     |                                       | TPS2062C and 66C (1 A)                                                                                                       | D                                                                                                               |      | 90   | 135  | -    |

| r <sub>DS(on)</sub> | On-resistance                         | TPS2062C-2 (1 A)                                                                                                             | DRB                                                                                                             |      | 73   | 115  | mΩ   |

|                     |                                       | TPS2060C, 64C, and 64C-2 (1.5 A)                                                                                             | DGN                                                                                                             |      | 70   | 112  |      |

|                     |                                       | TPS2002C and 03C (2 A)                                                                                                       |                                                                                                                 | 70   | 112  |      |      |

| ENABL               | E INPUT (ENx or ENx)                  |                                                                                                                              |                                                                                                                 |      |      |      |      |

| VIH                 | ENx (ENx), High-level input voltage   | 4.5 V ≤ VIN ≤ 5.5 V                                                                                                          |                                                                                                                 | 2    |      |      |      |

| V <sub>IL</sub>     | ENx (ENx), Low-level input Voltage    |                                                                                                                              |                                                                                                                 |      |      | 0.8  | V    |

|                     | Hysteresis                            | V <sub>IN</sub> = 5 V                                                                                                        |                                                                                                                 |      | 0.14 |      |      |

|                     | Leakage current                       | V <sub>ENx</sub> = 5.5 V or 0 V, V <sub>ENx</sub> = 0 V or 5.5                                                               | V                                                                                                               | -1   | 0    | 1    | μA   |

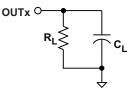

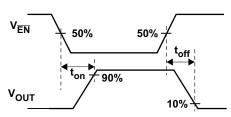

| t <sub>on</sub>     | Turn-on time <sup>(2)</sup>           | $V_{IN}$ = 5 V, C <sub>L</sub> = 1 μF, R <sub>L</sub> = 100 Ω, ENx<br>ENx ↓, See Figure 4, Figure 5, and Fig                 | $V_{IN} = 5 V, C_L = 1 \mu F, R_L = 100 \Omega, ENx \uparrow or$<br>ENx  , See Figure 4, Figure 5, and Figure 2 |      |      |      | ms   |

| -011                |                                       | 1 A, 1.5 A, 2 A Rated                                                                                                        |                                                                                                                 | 1.4  | 1.9  | 2.4  |      |

| t <sub>off</sub>    | Turn-off time <sup>(2)</sup>          | $V_{IN} = 5 V, C_L = 1 \mu F, R_L = 100 \Omega, ENx$<br>EN $\downarrow$ , See Figure 4, Figure 5, and Figu                   |                                                                                                                 |      |      |      | ms   |

| -011                |                                       | 1 A, 1.5 A, 2 A Rated                                                                                                        |                                                                                                                 | 1.95 | 2.60 | 3.25 |      |

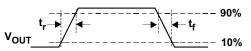

|                     | (2)                                   | $C_L = 1 \ \mu F$ , $R_L = 100 \ \Omega$ , see Figure 3                                                                      |                                                                                                                 |      |      |      |      |

| t <sub>r</sub>      | Rise time, output <sup>(2)</sup>      | 1 A, 1.5 A, 2 A Rated                                                                                                        |                                                                                                                 | 0.58 | 0.82 | 1.15 | ms   |

|                     | (2)                                   | $C_L = 1 \ \mu F$ , $R_L = 100 \ \Omega$ , see Figure 3                                                                      |                                                                                                                 |      |      |      |      |

| t <sub>f</sub>      | Fall time, output <sup>(2)</sup>      | 1 A, 1.5 A, 2 A Rated                                                                                                        |                                                                                                                 | 0.33 | 0.47 | 0.66 | ms   |

| CURRE               | NT LIMIT                              |                                                                                                                              |                                                                                                                 |      |      |      |      |

|                     |                                       | TPS2052C (0.5A)                                                                                                              | 0.7                                                                                                             | 1    | 1.3  |      |      |

|                     |                                       | TPS2062C, 62C-2, 66C, and 66C-2 (1                                                                                           | 1.12                                                                                                            | 1.61 | 2.10 |      |      |

| los                 | Current-limit, See Figure 7           | TPS2060C, 64C, and 64C-2 (1.5 A)                                                                                             | 1.72                                                                                                            | 2.29 | 2.86 | A    |      |

|                     |                                       | TPS2002C and 03C (2 A)                                                                                                       | 2.35                                                                                                            | 3.15 | 3.95 |      |      |

| t <sub>IOS</sub>    | Short-circuit response time           | $V_{IN} = 5 V$ (see Figure 6), One-half full 1<br>50 m $\Omega$ , measure from application to w<br>below 120% of final value |                                                                                                                 |      | 2    |      | μs   |

| SUPPLY              | Y CURRENT                             | •                                                                                                                            |                                                                                                                 |      |      |      |      |

| I <sub>SD</sub>     | Supply current, switch disabled       | Standard conditions, I <sub>(OUTx)</sub> = 0 mA                                                                              |                                                                                                                 |      | 0.01 | 10   |      |

| I <sub>S1E</sub>    | Supply current, single switch enabled | Standard conditions, I <sub>(OUTx)</sub> = 0 mA                                                                              |                                                                                                                 |      |      | 90   |      |

| I <sub>S2E</sub>    | Supply current, both switches enabled | Standard conditions, I <sub>(OUTx)</sub> = 0 mA                                                                              |                                                                                                                 |      |      | 150  | μA   |

| I <sub>LKG</sub>    | Leakage current                       | $V_{OUT}$ = 0 V, $V_{\text{IN}}$ = 5.5 V, disabled, measured $I_{\text{VIN}}$                                                | TPS20xxC-2                                                                                                      |      | 0.05 |      | μΛ   |

|                     | Reverse leakage current               | $V_{\text{OUT}}$ = 5.5 V, $V_{\text{IN}}$ = 0 V, measured $I_{(\text{OL}}$                                                   |                                                                                                                 | 0.20 |      |      |      |

| UNDER               | VOLTAGE LOCKOUT                       |                                                                                                                              |                                                                                                                 |      |      |      |      |

| UVLO                | Low-level input voltage, IN           | VIN rising                                                                                                                   |                                                                                                                 | 3.4  |      | 4.0  | V    |

|                     | Hysteresis, IN                        |                                                                                                                              |                                                                                                                 |      | 0.14 |      | V    |

| FLTx                |                                       |                                                                                                                              |                                                                                                                 |      |      |      |      |

|                     | Output low voltage, FLTx              | $I_{\overline{(FLTx)}} = 1 \text{ mA}$                                                                                       |                                                                                                                 |      |      | 0.2  | V    |

|                     | Off-state leakage                     | $V_{(FLTx)} = 5.5 V$                                                                                                         |                                                                                                                 |      |      | 1    | μA   |

|                     | FLTx deglitch <sup>(2)</sup>          | FLTx overcurrent assertion and deass                                                                                         | ertion                                                                                                          | 7    | 10   | 13   | ms   |

(1) Pulsed testing techniques maintain junction temperature approximately equal to ambient temperature

(2) These parameters are provided for reference only, and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

www.ti.com.cn

www.ti.com.cn

### **ELECTRICAL CHARACTERISTICS (continued)**

$-40^{\circ}C \le (T_J = T_A) \le 125^{\circ}C$ ,  $4.5 \text{ V} \le V_{IN} \le 5.5 \text{ V}$ ,  $V_{ENx} = V_{IN} \text{ or } V_{\overline{ENx}} = 0 \text{ V}$ ,  $I_{OUTx} = 0 \text{ A}$ , typical values are at 5 V and 25°C (unless otherwise noted)

| (                                          |                                                                  |                                |     |     |      |      |

|--------------------------------------------|------------------------------------------------------------------|--------------------------------|-----|-----|------|------|

| PARAMETER                                  | TEST CONDITION                                                   | TEST CONDITIONS <sup>(1)</sup> |     | TYP | MAX  | UNIT |

| OUTPUT DISCHARGE                           |                                                                  |                                |     |     |      |      |

| Output pull-down resistance <sup>(3)</sup> | $V_{IN} = 5 V$ , $V_{OUT} = 5 V$ , disabled                      | TPS20xxC                       | 300 | 470 | 800  | 0    |

|                                            | V <sub>IN</sub> = 4 V, V <sub>OUT</sub> = 5 V, disabled TPS20xx0 |                                | 350 | 560 | 1200 | Ω    |

| THERMAL SHUTDOWN                           |                                                                  |                                |     |     |      |      |

| Junction thermal shutdown threshold        | In current limit                                                 |                                | 135 |     |      | °C   |

| Sunction mermal shutdown threshold         | Not in current limit                                             | Not in current limit           |     | 155 |      |      |

| Hysteresis                                 |                                                                  |                                |     | 20  |      | °C   |

(3) These parameters are provided for reference only, and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

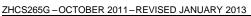

Figure 2. Output Rise / Fall Test Load

Figure 4. Enable Timing, Active High Enable

Figure 3. Power-On and Off Timing

Figure 7. Output Characteristic Showing Current Limit

Figure 6. Output Short Circuit Parameters

Copyright © 2011–2013, Texas Instruments Incorporated

ZHCS265G - OCTOBER 2011 - REVISED JANUARY 2013

www.ti.com.cn

www.ti.com.cn

ZHCS265G -OCTOBER 2011-REVISED JANUARY 2013

#### **DEVICE INFORMATION**

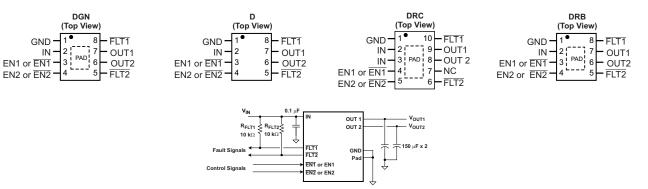

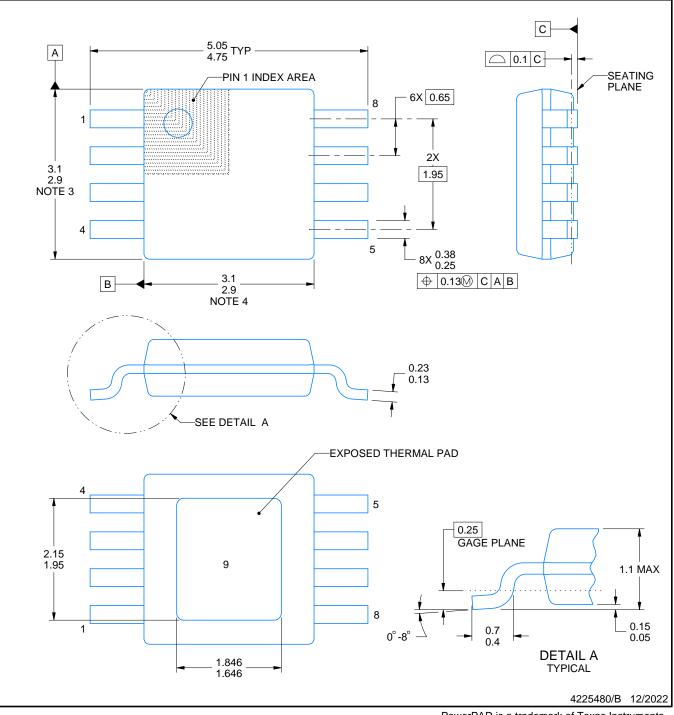

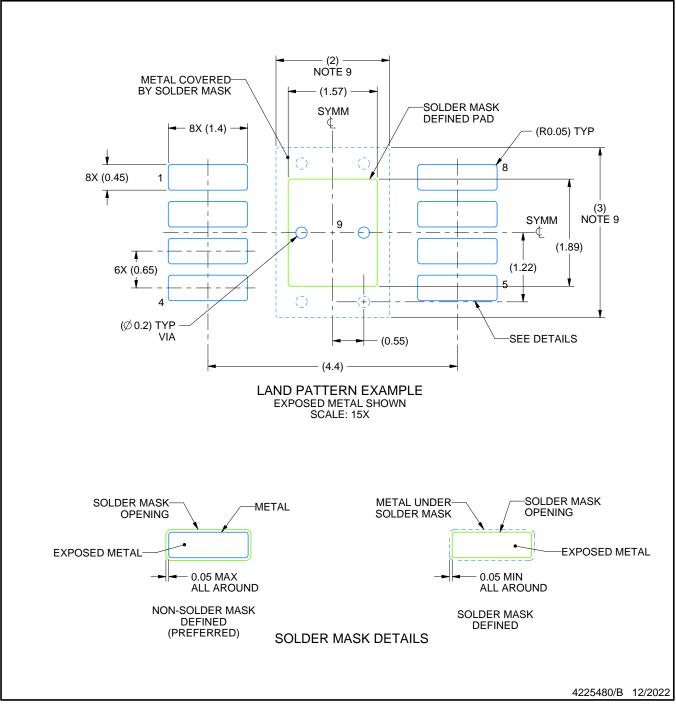

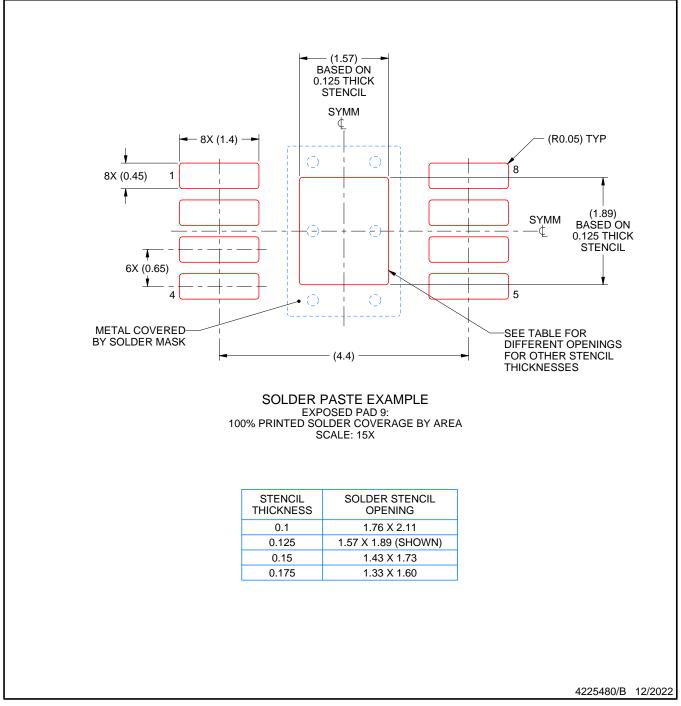

#### **PIN FUNCTIONS – MSOP-8 PACKAGES**

| NAME      | TPS2052C<br>TPS2066C<br>TPS2066C-2<br>TPS2064C<br>TPS2064C-2 | TPS2062C<br>TPS2060C | I/O | DESCRIPTION                                                                                                                  |  |

|-----------|--------------------------------------------------------------|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------|--|

| GND       | 1                                                            | 1                    | Pwr | Ground connection                                                                                                            |  |

| IN        | 2                                                            | 2                    | I   | Input voltage and power-switch drain; connect a 0.1 $\mu F$ or greater ceramic capacitor from IN GND close to the IC         |  |

| EN1       | 3                                                            | -                    | I   | Enable input channel 1, logic high turns on power switch                                                                     |  |

| EN1       | -                                                            | 3                    | I   | Enable input channel 1, logic low turns on power switch                                                                      |  |

| EN2       | 4                                                            | -                    | I   | Enable input channel 2, logic high turns on power switch                                                                     |  |

| EN2       | -                                                            | 4                    | I   | Enable input channel 2, logic low turns on power switch                                                                      |  |

| FLT2      | 5                                                            | 5                    | 0   | Active-low open-drain output, asserted during overcurrent, or overtemperature conditions on channel 2                        |  |

| OUT2      | 6                                                            | 6                    | 0   | Power-switch output channel 2, connected to load                                                                             |  |

| OUT1      | 7                                                            | 7                    | 0   | Power-switch output channel 1, connected to load                                                                             |  |

| FLT1      | 8                                                            | 8                    | 0   | Active-low open-drain output, asserted during over-current, or overtemperature conditions on channel 1                       |  |

| PowerPAD™ | PAD                                                          | PAD                  | Pwr | Internally connected to GND; used to heat-sink the part to the circuit board traces. Connect PAD to GND plane as a heatsink. |  |

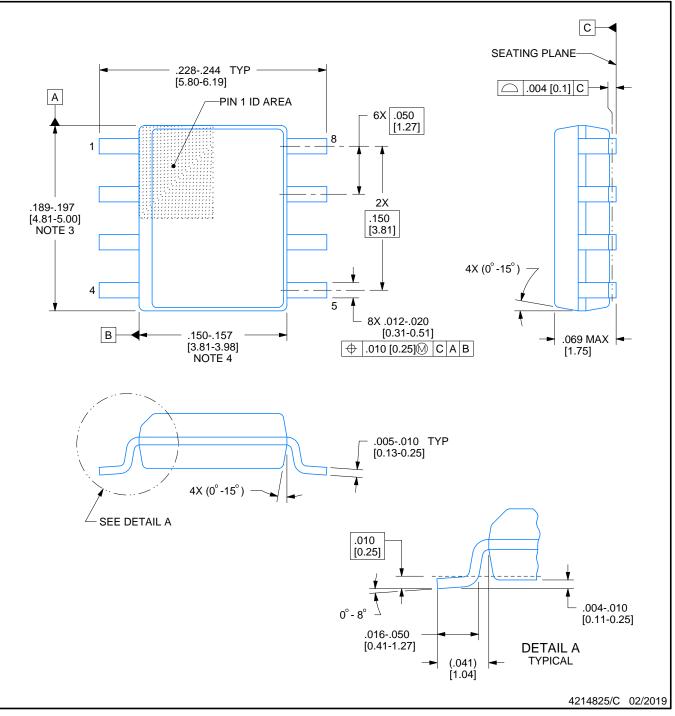

#### **PIN FUNCTIONS – SOIC-8 PACKAGES**

| NAME | TPS2066C | TPS2062C | I/O | DESCRIPTION                                                                                                             |  |

|------|----------|----------|-----|-------------------------------------------------------------------------------------------------------------------------|--|

| GND  | 1        | 1        | Pwr | Ground connection                                                                                                       |  |

| IN   | 2        | 2        | I   | Input voltage and power-switch drain; connect a 0.1 $\mu F$ or greater ceramic capacitor from IN to GND close to the IC |  |

| EN1  | 3        | -        | I   | Enable input channel 1, logic high turns on power switch                                                                |  |

| EN1  | -        | 3        | I   | Enable input channel 1, logic low turns on power switch                                                                 |  |

| EN2  | 4        | -        | I   | Enable input channel 2, logic high turns on power switch                                                                |  |

| EN2  | -        | 4        | I   | Enable input channel 2, logic low turns on power switch                                                                 |  |

| FLT2 | 5        | 5        | 0   | Active-low open-drain output, asserted during overcurrent, or overtemperature conditions on channel 2                   |  |

| OUT2 | 6        | 6        | 0   | Power-switch output channel 2, connected to load                                                                        |  |

| OUT1 | 7        | 7        | 0   | Power-switch output channel 1, connected to load                                                                        |  |

| FLT1 | 8        | 8        | 0   | Active-low open-drain output, asserted during overcurrent, or overtemperature conditions on channel 1                   |  |

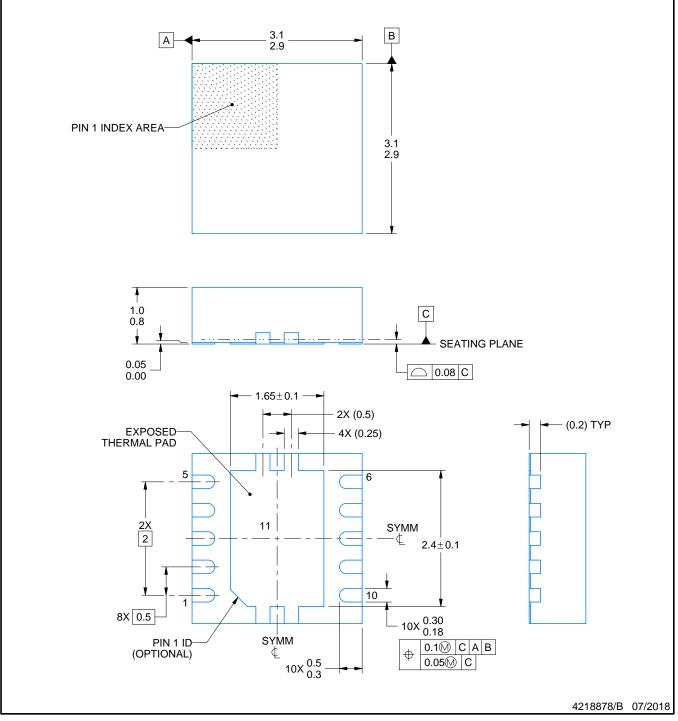

#### **PIN FUNCTIONS – SON-10 PACKAGES**

| NAME      | TPS2003C | TPS2002C | I/O | DESCRIPTION                                                                                                                   |

|-----------|----------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| GND       | 1        | 1        | Pwr | Ground connection                                                                                                             |

| IN        | 2, 3     | 2, 3     | I   | Input voltage and power-switch drain; connect a 0.1 $\mu\text{F}$ or greater ceramic capacitor from IN to GND close to the IC |

| EN1       | 4        | -        | I   | Enable input channel 1, logic high turns on power switch                                                                      |

| EN1       | -        | 4        | I   | Enable input channel 1, logic low turns on power switch                                                                       |

| EN2       | 5        | -        | I   | Enable input channel 2, logic high turns on power switch                                                                      |

| EN2       | -        | 5        | I   | Enable input channel 2, logic low turns on power switch                                                                       |

| FLT2      | 6        | 6        | 0   | Active-low open-drain output, asserted during overcurrent, or overtemperature conditions on channel 2                         |

| NC        | 7        | 7        |     | No connect – leave floating.                                                                                                  |

| OUT2      | 8        | 8        | 0   | Power-switch output channel 2, connect to load                                                                                |

| OUT1      | 9        | 9        | 0   | Power-switch output channel 1, connect to load                                                                                |

| FLT1      | 10       | 10       | 0   | Active-low open-drain output, asserted during overcurrent, or overtemperature conditions on channel 1                         |

| PowerPAD™ | PAD      | PAD      | Pwr | Internally connected to GND; used to heat-sink the part to the circuit board traces. Connect PAD to GND plane as a heatsink.  |

ZHCS265G - OCTOBER 2011 - REVISED JANUARY 2013

www.ti.com.cn

#### **PIN FUNCTIONS – SON-8 PACKAGES**

| NAME      | TPS2062C-2 | I/O | DESCRIPTION                                                                                                                     |

|-----------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------|

| GND       | 1          | Pwr | Ground connection                                                                                                               |

| IN        | 2          | I   | Input voltage and power-switch drain; connect a 0.1 $\mu F$ or greater ceramic capacitor from IN to GND close to the IC         |

| EN1       | 3          | I   | Enable input channel 1, logic low turns on power switch                                                                         |

| EN2       | 4          | I   | Enable input channel 2, logic low turns on power switch                                                                         |

| FLT2      | 5          | 0   | Active-low open-drain output, asserted during over-current, or over-temperature conditions on channel 2                         |

| OUT2      | 6          | 0   | Power-switch output channel 2, connect to load                                                                                  |

| OUT1      | 7          | 0   | Power-switch output channel 1, connect to load                                                                                  |

| FLT1      | 8          | 0   | Active-low open-drain output, asserted during over-current, or over-temperature conditions on channel 1                         |

| PowerPAD™ | PAD        | Pwr | Internally connected to GND; used to heat-sink the part to the circuit board traces.<br>Connect PAD to GND plane as a heatsink. |

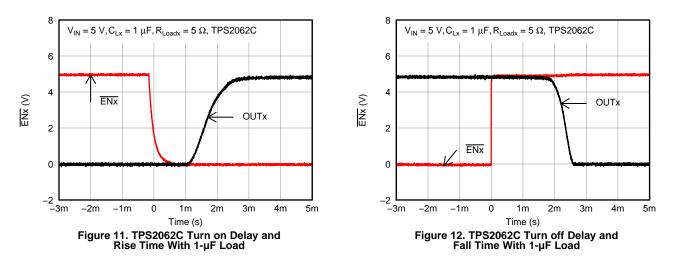

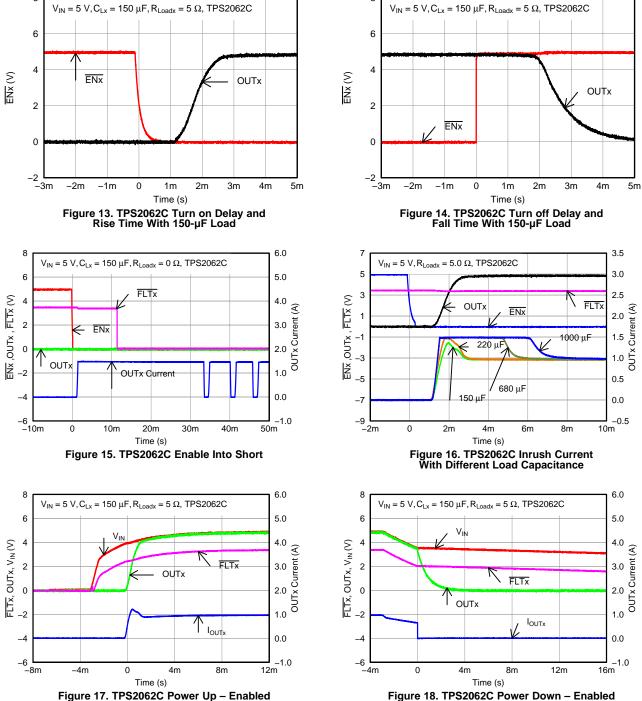

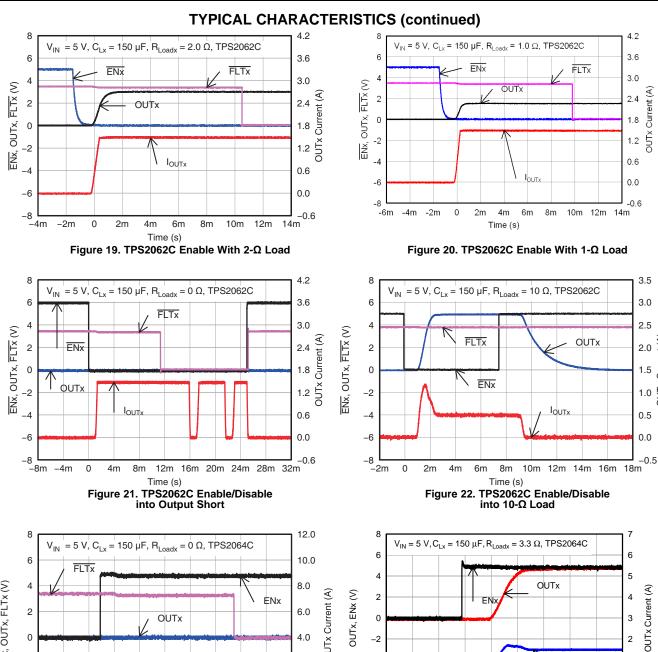

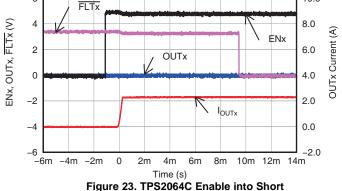

#### **TYPICAL CHARACTERISTICS**

Figure 10. Test Circuit for System Operation in Typical Characteristics Section

ZHCS265G -OCTOBER 2011-REVISED JANUARY 2013

8

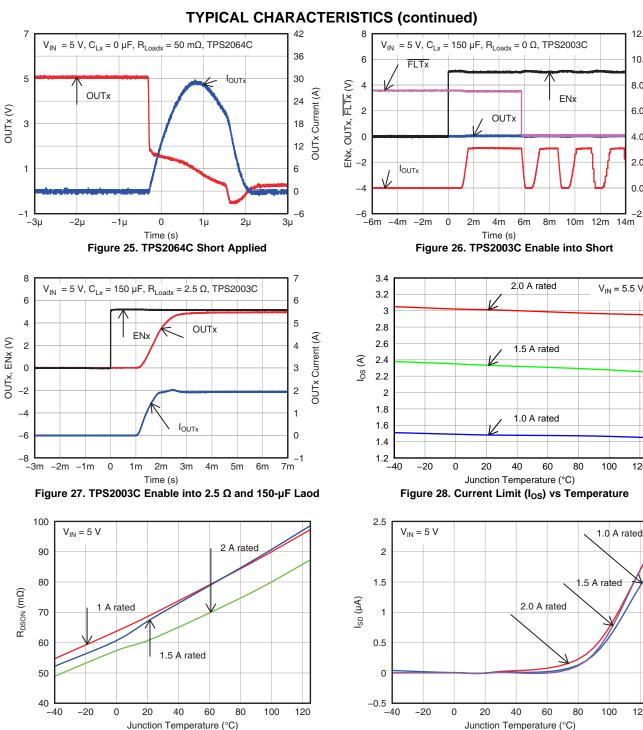

**TYPICAL CHARACTERISTICS (continued)**

Figure 18. TPS2062C Power Down - Enabled

ZHCS265G - OCTOBER 2011-REVISED JANUARY 2013

TEXAS INSTRUMENTS

www.ti.com.cn

OUTx Current (A)

-4

-6

-8

-4m

–3m –2m

-1m 0

Figure 24. TPS2064C Enable into 3.3  $\Omega$  and 150- $\mu F$  Laod

1m 2m

Time (s)

IOUT<sub>X</sub>

3m 4m 5m

0

ZHCS265G -OCTOBER 2011-REVISED JANUARY 2013

12.0

10.0

8.0

6.0

4.0

2.0

0.0

-2.0

120

120

OUTx Current (A)

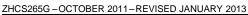

Junction Temperature (°C) Figure 30. Supply Current (Device Disable) - I<sub>SD</sub> vs Temperature

Figure 29. Input - output Resistance (R<sub>DS(ON)</sub>) vs Temperature

www.ti.com.cn

www.ti.com.cn

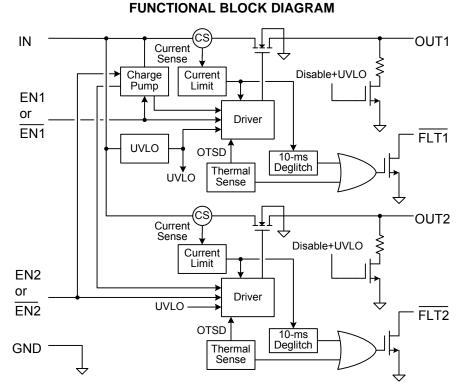

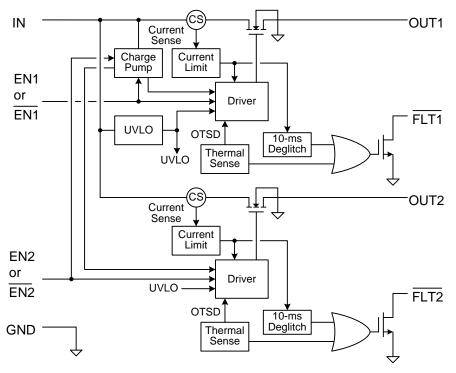

#### DETAILED DESCRIPTION

#### OVERVIEW

The TPS20xxC and TPS20xxC-2 dual are current-limited, power-distribution switches providing between 0.5 A and 2 A of continuous load current in 5-V circuits. These parts use N-channel MOSFETs for low resistance, maintaining output voltage load regulation. They are designed for applications where short circuits or heavy capacitive loads are encountered. Device features include UVLO, ON/OFF control (Enable), reverse blocking when disabled, output discharge when TPS20xxC disabled, overcurrent protection, overtemperature protection, and deglitched fault reporting. They are pin for pin with existing *TI Switch Portfolio*.

#### UNDERVOLTAGE LOCKOUT (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch when the input voltage is below the UVLO threshol<u>d. Built-in hysteresis prevents unwanted on/off cycling due to input voltage drop from large current surges. FLTx is high impedance when the TPS20xxC and TPS20xxC-2 dual are in UVLO.</u>

#### ENABLE (ENx or ENx)

The logic input of ENx or ENx disables all of the internal circuitry while maintaining the power switch OFF. The supply current of the device can be reduced to less than 1 µA when both switches are disabled. A logic low input on ENx or a logic high input on ENx enables the driver, control circuits, and power switch of corresponding channel.

The ENx or ENx input voltage is compatible with both TTL and CMOS logic levels. The FLTx is immediately cleared and the output discharge circuit is enabled when the device is disabled.

#### DEGLITCHED FAULT REPORTING

FLTx is an open-drain output that asserts (active low) during an overcurrent or overtemperature condition on each corresponding channel. The FLTx output remains asserted until the fault condition is removed or the channel is disabled. The TPS20xxC and TPS20xxC-2 dual eliminates false FLTx reporting by using internal delay circuitry after entering or leaving an overcurrent condition. The "deglitch" time is typically 10 ms. This ensures that FLTx is not accidentally asserted under overcurrent conditions with a short time, such as starting into a heavy capacitive load. Over temperature conditions are not deglitched. The FLTx pin is high impedance when the device is disabled and in undervoltage lockout (UVLO). The fault circuits are independent so that another channel continues to operate when one channel is in a fault condition.

#### OVERCURRENT PROTECTION

The TPS20xxC and TPS20xxC-2 dual responds to overloads by limiting each channel output current to the static  $I_{OS}$  levels shown in the *Electrical Characteristics* table. When an overload condition is present, the device maintains a constant current ( $I_{OS}$ ) and reduces the output voltage accordingly, with the output voltage falling to ( $I_{OS} \times R_{SHORT}$ ). Three possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before voltage is applied to IN. The device senses over-current and immediately switches into a constant-current output. In the second condition, a short or an overload occurs while the device is enabled. At the instant a short -circuit occurs, high currents may flow for several microseconds ( $t_{IOS}$ ) before the current-limit circuit reacts. The device operates in constant-current mode after the current-limit circuit has responded. In the third condition, the load is increased gradually beyond the recommended operating current. The current is permitted to rise until the current-limit threshold is reached. The devices are capable of delivering current up to the current-limit threshold without damage. Once the threshold is reached, the device switches into constant-current mode. For all of the above three conditions, the device may begin thermal cycling if the overcurrent condition persists.

#### **OVERTEMPERATURE PROTECTION**

ZHCS265G-OCTOBER 2011-REVISED JANUARY 2013

The TPS20xxC and TPS20xxC-2 dual includes per channel overtemperature protection circuitry, which activates at 135°C (min) junction temperature while in current limit. There is an overall thermal shutdown of 155°C (min) junction temperature when the TPS20xxC and TPS20xxC-2 dual are not in current limit. The device remains off until the junction temperature cools 20°C and then restarts. Thermal shutdown may occur during an overload due to the relatively large power dissipation [( $V_{IN} - V_{OUT}$ ) × I<sub>OS</sub>] driving the junction temperature up. The power switch cycles on and off until the fault is removed. This topology allows one channel to continue normal operation even if the other channel is in an over-temperature condition.

#### SOFTSTART, REVERSE BLOCKING AND DISCHARGE OUTPUT

The power MOSFET driver incorporates circuitry that controls the rise and fall times of the output voltage to limit large current and voltage surges on the input supply, and provides built-in soft-start functionality.

The TPS20xxC and TPS20xxC-2 dual power switch will block current from OUT to IN when turned off by the UVLO or disabled.

The TPS20xxC dual includes an output discharge function on each channel. A 470 $\Omega$  (typ.) discharge resistor will dissipate stored charge and leakage current on OUTx when the device is in UVLO or disabled. However as this circuit is biased from IN, the output discharge will not be active when IN voltage is close to 0 V.

The TPS20xxC-2 does not have this function. The output is be controlled by an external loadings when the device is in ULVO or disabled.

www.ti.com.cn

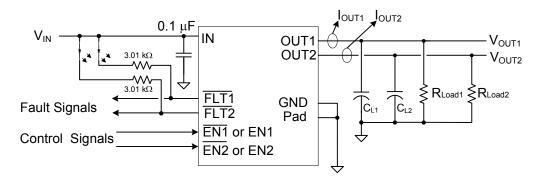

#### **APPLICATION INFORMATION**

#### INPUT AND OUTPUT CAPACITANCE

Input and output capacitance improves the performance of the device. For all applications, a 0.1  $\mu$ F or greater ceramic bypass capacitor between IN and GND is recommended as close to the device as possible for local noise de-coupling. The actual capacitance should be optimized for the particular application. This precaution reduces ringing on the input due to power-supply transients. Additional input capacitance may be needed on the input to reduce the overshoot voltage from exceeding the absolute maximum voltage of the device during heavy transients.

A 120  $\mu$ F minimum output capacitance is required when implementing USB standard applications. Typically this uses a 150  $\mu$ F electrolytic capacitor. If the application does not require 120  $\mu$ F of output capacitance, a minimum of 10  $\mu$ F ceramic capacitor on the output is recommended in order to reduce the transient negative voltage on OUTx pin caused by load inductance during a short circuit. The transient negative voltage should be less than 1.5 V for 10  $\mu$ s.

#### POWER DISSIPATION AND JUNCTION TEMPERATURE

It is good design practice to estimate power dissipation and maximum expected junction temperature of the TPS20xxC and TPS20xxC-2 dual. The system designer can control choices of package, proximity to other power dissipating devices, and printed circuit board (PCB) design based on these calculations. These have a direct influence on maximum junction temperature. Other factors such as airflow and maximum ambient temperature are often determined by system considerations.

Addition of extra PCB copper area around these devices is recommended to reduce the thermal impedance and maintain the junction temperature as low as practical.

The following procedure requires iteration because power loss is due to the two internal MOSFETs  $2 \times l^2 \times r_{DS(on)}$ , and  $r_{DS(on)}$  is a function of the junction temperature. As an initial estimate, use the  $r_{DS(on)}$  at 125°C from the typical characteristics, and the preferred package thermal resistance for the preferred board construction from the thermal parameters section.

$T_{J} = T_{A} + [(2 \times I_{OUT}^{2} \times r_{DS(on)} \times \theta_{JA}]$

Where:

$$\begin{split} I_{OUT} &= \text{rated OUT pin current (A)} \\ r_{DS(on)} &= \text{Power switch on-resistance at an assumed } T_J (\Omega) \\ T_A &= \text{Maximum ambient temperature (°C)} \\ T_J &= \text{Maximum junction temperature (°C)} \\ \theta_{JA} &= \text{Thermal resistance (°C/W)} \end{split}$$

If the calculated  $T_J$  is substantially different from the original assumption, look up a new value of  $r_{DS(on)}$  and recalculate.

If the resulting T<sub>J</sub> is not less than 125°C, try a PCB construction and/or package with lower  $\theta_{JA}$ .

Changes from Original (October 2011) to Revision A

ZHCS265G - OCTOBER 2011-REVISED JANUARY 2013

#### **REVISION HISTORY**

### Changed devices TPS2062C and TPS2066C MSOP-8 package From: Preview to Active ...... 1 Changed the I<sub>os</sub> current limit values for TPS2062C/66C (1 A). 4 Changes from Revision A (March 2012) to Revision B Page Changed device TPS2060C MSOP-8 package From: Preview To: Active ...... 1 Changes from Revision B (March 2012) to Revision C Page Changes from Revision C (June 2012) to Revision D Page Changes from Revision D (July 2012) to Revision E Page Corrected Note 2 references in the ELECTRICAL CHARACTERISTICS table ...... 4 Changed the I<sub>OS</sub> current limit values for TPS2002C and 03C (2 A). ...... 4 Changes from Revision E (August 2012) to Revision F Page Added TPS2052C, TPS2062C-2, TPS2064C-2, and TPS2066C-2 devices to Table 1 ...... 1 Added TPS2052C, TPS2062C-2, TPS2064C-2, and TPS2066C-2 devices to RECOMMENDED OPERATING

16

Page

www.ti.com.cn

### TPS2052C, TPS2062C, TPS2062C-2 TPS2066C, TPS2066C-2, TPS2060C, TPS2064C TPS2064C-2, TPS2002C, TPS2003C

ZHCS265G -OCTOBER 2011-REVISED JANUARY 2013

## Changes from Revision F (November 2012) to Revision G Page • Changed device TPS2062C-2 SON-8 packages From: Preview To: Active. 1 • Changed devices TPS2066C-2, and TPS2064C-2 MSOP-8 package From: Preview To: Active 1

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TPS2002CDRCR     | ACTIVE        | VSON         | DRC                | 10   | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | VFEQ                    | Samples |

| TPS2002CDRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | VFEQ                    | Samples |

| TPS2003CDRCR     | ACTIVE        | VSON         | DRC                | 10   | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | VRFQ                    | Samples |

| TPS2003CDRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | VRFQ                    | Samples |

| TPS2052CDGN      | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -40 to 125   | PYNI                    | Samples |

| TPS2052CDGNR     | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -40 to 125   | PYNI                    | Samples |

| TPS2060CDGN      | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 125   | VRAQ                    | Samples |

| TPS2060CDGNR     | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 125   | VRAQ                    | Samples |

| TPS2062CD        | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | 2062C                   | Samples |

| TPS2062CDGN      | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 125   | VRBQ                    | Samples |

| TPS2062CDGNR     | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 125   | VRBQ                    | Samples |

| TPS2062CDR       | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | 2062C                   | Samples |

| TPS2062CDRBR-2   | ACTIVE        | SON          | DRB                | 8    | 3000           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | PYVI                    | Samples |

| TPS2062CDRBT-2   | ACTIVE        | SON          | DRB                | 8    | 250            | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | PYVI                    | Samples |

| TPS2064CDGN      | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 125   | VRCQ                    | Samples |

| TPS2064CDGN-2    | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -40 to 125   | PYTI                    | Samples |

| TPS2064CDGNR     | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 125   | VRCQ                    | Samples |

| TPS2064CDGNR-2   | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -40 to 125   | PYTI                    | Samples |

| TPS2065CDBVR-2   | ACTIVE        | SOT-23       | DBV                | 5    | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PYQI                    | Samples |

| TPS2065CDBVT-2   | ACTIVE        | SOT-23       | DBV                | 5    | 250            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PYQI                    | Samples |

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| TPS2065CDGN-2    | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | (6)<br>NIPDAUAG               | Level-2-260C-1 YEAR  | -40 to 125   | PYRI                    | Samples |

| TPS2065CDGNR-2   | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                      | Level-2-260C-1 YEAR  | -40 to 125   | PYRI                    | Samples |

| TPS2066CD        | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM   | -40 to 125   | 2066C                   | Samples |

| TPS2066CDGN      | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | NIPDAUAG                      | Level-1-260C-UNLIM   | -40 to 85    | VRDQ                    | Samples |

| TPS2066CDGN-2    | ACTIVE        | HVSSOP       | DGN                | 8    | 80             | RoHS & Green    | NIPDAUAG                      | Level-2-260C-1 YEAR  | -40 to 125   | PYUI                    | Samples |

| TPS2066CDGNR     | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                      | Level-1-260C-UNLIM   | -40 to 125   | VRDQ                    | Samples |

| TPS2066CDGNR-2   | ACTIVE        | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green    | NIPDAUAG                      | Level-2-260C-1 YEAR  | -40 to 125   | PYUI                    | Samples |

| TPS2066CDR       | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM   | -40 to 125   | 2066C                   | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

www.ti.com

### PACKAGE OPTION ADDENDUM

11-Aug-2022

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

Texas

STRUMENTS

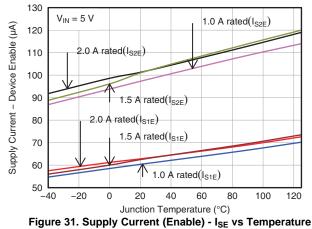

#### TAPE AND REEL INFORMATION

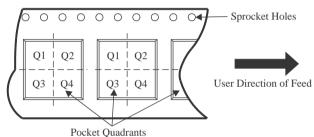

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nomina |                 |                    |    |      |                          |                          | r          |            | r          |            |           |                  |

|----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS2002CDRCR               | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2002CDRCT               | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2003CDRCR               | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2003CDRCT               | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2052CDGNR               | HVSSOP          | DGN                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2060CDGNR               | HVSSOP          | DGN                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2062CDGNR               | HVSSOP          | DGN                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2062CDR                 | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2062CDR                 | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2062CDRBR-2             | SON             | DRB                | 8  | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2062CDRBT-2             | SON             | DRB                | 8  | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2064CDGNR               | HVSSOP          | DGN                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2064CDGNR-2             | HVSSOP          | DGN                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2065CDBVR-2             | SOT-23          | DBV                | 5  | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS2065CDBVR-2             | SOT-23          | DBV                | 5  | 3000 | 178.0                    | 9.0                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| TPS2065CDBVT-2             | SOT-23          | DBV                | 5  | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

### PACKAGE MATERIALS INFORMATION

www.ti.com

16-Feb-2023

| Device         | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2065CDBVT-2 | SOT-23          | DBV                | 5 | 250  | 178.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| TPS2065CDGNR-2 | HVSSOP          | DGN                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2066CDGNR   | HVSSOP          | DGN                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2066CDGNR-2 | HVSSOP          | DGN                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS2066CDR     | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com

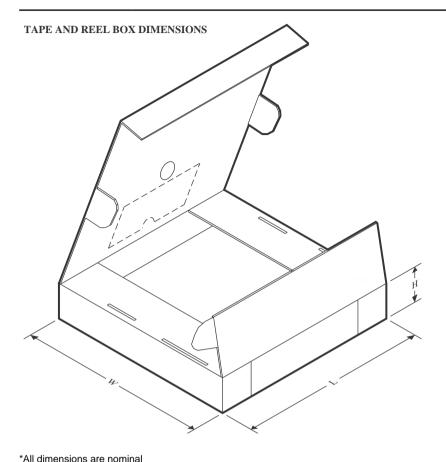

### PACKAGE MATERIALS INFORMATION

16-Feb-2023

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS2002CDRCR   | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS2002CDRCT   | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS2003CDRCR   | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS2003CDRCT   | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS2052CDGNR   | HVSSOP       | DGN             | 8    | 2500 | 366.0       | 364.0      | 50.0        |

| TPS2060CDGNR   | HVSSOP       | DGN             | 8    | 2500 | 364.0       | 364.0      | 27.0        |

| TPS2062CDGNR   | HVSSOP       | DGN             | 8    | 2500 | 364.0       | 364.0      | 27.0        |

| TPS2062CDR     | SOIC         | D               | 8    | 2500 | 340.5       | 336.1      | 25.0        |

| TPS2062CDR     | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |

| TPS2062CDRBR-2 | SON          | DRB             | 8    | 3000 | 335.0       | 335.0      | 25.0        |